#### US006721828B2

### (12) United States Patent

Verinsky et al.

#### (10) Patent No.: US 6,721,828 B2

(45) **Date of Patent:** \*Apr. 13, 2004

# (54) OPTICAL DRIVE CONTROLLER WITH A HOST INTERFACE FOR DIRECT CONNECTION TO AN IDE/ATA DATA BUS

(75) Inventors: Phil Verinsky, San Jose, CA (US);

Michael Case, Los Altos Hills, CA

(US)

(73) Assignee: Zoran Corporation, Sunnyvale, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

0.5.c. 15 1(0) 03 0 days

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 10/082,990

(22) Filed: Feb. 25, 2002

(65) **Prior Publication Data**

US 2003/0037230 A1 Feb. 20, 2003

#### Related U.S. Application Data

- (63) Continuation of application No. 09/442,866, filed on Nov. 18, 1999, now Pat. No. 6,546,440, which is a continuation of application No. 08/673,327, filed on Jun. 28, 1996, now Pat. No. 6,584,527, which is a continuation of application No. 08/264,361, filed on Jun. 22, 1994, now Pat. No. 5,581,715.

- (51) Int. Cl.<sup>7</sup> ...... G06F 13/12

- (52) **U.S. Cl.** ...... **710/62**; 710/2; 710/129

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,698,810 A | 10/1987 | Fukuda et a  |

|-------------|---------|--------------|

| 4,991,169 A | 2/1991  | Davis et al. |

| 5,261,072 A | 11/1993 | Siegel       |

| 5 295 247 A | 3/1994  | Chang et al  |

| 5,313,585 A | 5/1994  | Jeffries et al.      |

|-------------|---------|----------------------|

| 5,337,409 A | 8/1994  | Sakata 345/501       |

| 5,359,698 A | 10/1994 | Goldberg et al.      |

| 5,379,284 A | 1/1995  | Kim                  |

| 5,408,477 A | 4/1995  | Okada et al 371/37.4 |

| 5,418,910 A | 5/1995  | Siegel               |

| 5,434,722 A | 7/1995  | Bizjak               |

| 5,446,877 A | 8/1995  | Liu et al 395/180    |

| 5,485,440 A | 1/1996  | Ogino 369/44.34      |

| 5,499,252 A | 3/1996  | Watanabe             |

| 5,535,327 A | 7/1996  | Verinsky et al.      |

|             |         |                      |

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

| EP | 0689207 A1  | 12/1995 |

|----|-------------|---------|

| WO | WO 93/09500 | 5/1993  |

#### OTHER PUBLICATIONS

Oak Technology Inc.'s Claim Construction Brief re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. C97–20959 RMW and Mediatek Inc., v. Oak Technology, Inc., Case No. C97–21126 RMW, dated Jul. 19, 2002 (27 pages).

(List continued on next page.)

Primary Examiner—Thomas Lee

Assistant Examiner—Thuan Du

(74) Attorney, Agent, or Firm—Blakely, Sokoloff, Taylor &

#### (57) ABSTRACT

Zafman LLP

A compact disk drive controller to control the access of information from an optical compact disk (CD) digital data storage device by a host computer using an integrated drive electronics (IDE) data bus or an industry standard architecture (ISA) data bus is disclosed. A digital signal processor (DSP) interface to the drive electronics of the CD drive, a dynamic random access memory (DRAM) controller, an error correction code (ECC) data corrector, an error detection and correction (EDC) device employing cyclical redundancy checking techniques (EDC/CRC), and a host computer interface are described.

#### 64 Claims, 25 Drawing Sheets

#### U.S. PATENT DOCUMENTS

| 5,581,715 A | 12/1996 | Verinsky et al. |         |

|-------------|---------|-----------------|---------|

| 5,581,716 A | 12/1996 | Park            |         |

| 5,623,700 A | 4/1997  | Parks et al     | 395/873 |

| 5,701,450 A | 12/1997 | Duncan          |         |

| 5,802,398 A | 9/1998  | Liu et al       | 395/882 |

| 5.805.921 A | 9/1998  | Kikinis et al.  |         |

#### OTHER PUBLICATIONS

Oak Technology Inc.'s Response to Defendant United Microelectronics Corporation's Invalidity Contentions Dated Jun. 28, 2002 re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. C97–20959 RMW and Mediatek Inc., v. Oak Technology, Inc., Case No. C 97–21126 RMW, dated Jul. 19, 2002 (5 pages).

[Proposed] Order re Unsealing of Case File (2 pgs), Certificate of Service (Order re Unsealing of Case File) (3 pgs), Stipulation re Unsealing of Case File (3 pgs), re Oak Technology Inc. v. United Microelectronics Corporation, Case No. C97–20959 RMW and Mediatek Inc., v. Oak Technology, Inc., Case No. C 97–21126 RMW, dated Jul. 30, 2002.

Defendant United Microelectronics Corporation's Opening Brief on Claim Construction Pursuant to Apr. 15, 2002 Case Management Order (23 pgs), Declaration of James C. Otteson (7 pgs), Misc. Administrative Request of Deft. for leave to File Documents Under Seal (2 pgs), Declaration of Dale E. Buscaino (4 pgs), re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. C97–20959 RMW and Mediatek Inc., v. Oak Technology, Inc., Case No. C 97–21126 RMW, dated Jun. 28, 2002.

Defendant United Microelectronics Corporation's Invalidity Contentions (3 pgs), [Proposed] Order Granting Miscellaneous Administrative Request of Defendant United Microelectronics Corporation for Leave to File Documents Under Seal (2 pgs), Confidential Exhibits to Declaration of James C. Otteson in Support of Defendant United Microelectronics Corporation's Opening Brief on Claim Construction (1 pg), Certificate of Service (3 pgs), re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. C97–20959 RMW and Mediatek Inc., v. Oak Technology, Inc., Case No. C 97–21126 RMW, dated Jun. 21, 2002.

Lawrence J. Lamers, *Information Technology—AT Attachment Interface for Disk Drives*, Reference No. ANSI X3.221–199x, Copyright 1994, Computer and Business Equipment Manufacture Association, (75 pages).

Initial Determination, In the Matter of Certain CD-ROM Controllers and Products Containing the Same II, Inv. No. 337-TA-409, U.S. International Trade Commission, Public Version, stamp dated Jun. 11, 1999, pp. 1–315.

Recommended Determination Concerning Respondent's Motion for Sanctions, In the Matter of Certain CD–ROM Controllers and Products Containing Same—II, Inv. No. 337–TA–409, U.S. International Trade Commission, Public Version, stamped received date Oct. 22, 1999, (61 pp. total). Notice of Final Determination and attached Order, In the Matter of Certain CD–ROM Controllers and Products Containing the Same—II, Inv. No. 337–TA–409, U.S. International Trade Commission, Corrected Version, stamp dated Sep. 28, 1999, (9 pp. total).

Commission Opinion, In the Matter of Certain CD-ROM Controllers and Products Containing Same—II, Inv. No. 337-TA-409, U.S. International Trade Commission, Public Version, stamped received Oct. 20, 1999, (89 pp. total).

Denial of Motion for Sanctions; Vacatur of Recommended Determination, In the Matter of Certain CD–ROM Controllers and Products Containing Same—II, Inv. No. 337–TA–409 (2 pp.) attached Order (2 pp.) and attached Certificate of Service (1 pp.), U.S. International Trade Commission, stamp received dated Dec. 13, 1999.

Offer for Sale, letter dated May 19, 1993 to David D. Tsang, President, Oak Technology, from Masafumi Kaneko, General Manager, Optical Media Product Division, NEC Home Electronics Co., Ltd. (3 pages), Memorandum signed by David D. Tsang on May 27, 1993 and Masafumi Kaneko on May 28, 1993 (1 page).

Memorandum dated Apr. 20, 1994 to Don Bryson, cc: Scott Alberts, Mike Hetzel, From Peter Brown, Re: Barrier Plan (2 pages).

Draft Proposed American National Standard—AT Attachment Prepared by X3T9—I/O Interface, Accredited Standards Committee—X3 Information Processing System (56 pp.), Feb. 10, 1992, X.3.221–199x, X3T9.2/90–143.

Sanyo LC8950 & LDC8951, Real-Time Error Correction and Host Interface Processors for CD-I and CD-ROM Applications, Application Note No. E89, Sanyo Electric Co., Ltd. Semiconductor Division, First English edition: Apr. 1988, Revised to include LC8951: June 1989 (118 pages), Contents (i–ii), List of Figures (iii–iv), List of Tables (v).

Oak Technology, Inc. OTI-012 Overview dated Nov. 11, 1991 (2 pgs.), 5 diagrams (5 pgs.), Oak Technology, Inc. Memorandum to: Mr. Sugie @ Mitsumi Dallas Office, from: Phil Verinsky @ Oak Technology, Inc., Date: Mar. 10, 1992, CC: James Ou, Aki Tanaka, Peter Brown, Kenji Fujimoto, Subject: OTI012 Production Package (3 pp. & 2 pp. of diagrams).

Oak Technology, Incorporated Preliminary Specification OTI-012 CD-ROM Controller Chip, Mar. 20, 1992, Copyright 1992 Oak Technology, Inc. Printed in USA (72 pp.), Table of Contents (1 p.), Overview (1 p.), Appendix (A-1 to A-3).

Proposal for a Working Draft, Revision A1.3, Jun. 10, 1993, 11:32 am, ATAPI CD-ROM Standard, Deposition Exhibit 653 Shahani, Oct. 9, 1998 (130 p p.), Table of Contents (pp. 3–6), List of Tables (pp. 7–8), List of Figures (pp. 9–10).

Memorandum dated Feb. 19, 1993 pertaining to the Mitsumi prototype, To: P. Verinsky, CC: M. Case, W. Wang, From: A. Tanaka, Re: IDE Prototype Summary (4 pages).

OTI-011 IDE CD-ROM Controller Engineering Specification Rev. 1.1, Nov. 2, 1992 (19 pp.), Contents (1 p.), Overview (1 p.).

OTI-011 microcontroller controller register chart showing the OTI-011 registers for communication with a microcontroller (RX-10C; RX-16C; RX-22C, RX-153C (CD ROM Interface Status),(Apr. 21, 1993) (5 pp.).

OTI-011 IDE Interface Control Registers (from the microcontroller's perspective) (2 pp.).

Oak employee Don Smith's 2/93 design notes describing the OTI-011 registers, including the direct access feature for the PDIAG, DASPEN, and clear BSY signals (RX-20C; Verinsky 1029–1032), (1 page).

Claimed inventor Verinsky's 3/93 IDE/Host Checklist referring to an HIRQ pin for generating host interruption requests (RX–17C; Verinsky Tr. 1032–1034, H:\...Mike.Txt (2 pp.).

Order No. 16: Concerning the Declassification of Certain Filings and the Admission of Certain Exhibits, In the Matter of: Certain CD–ROM Controllers and Products Containing Same—II, Investigation No. 337–TA–409, U.S. International Trade Commission, Order signed by Sidney Harris, Administrative Law Judge Issued May 12, 1999 (5 pages).

Petition for Review of Final Initial Determination of Complainant Oak Technology, Incorporated, In the Matter of: Certain CD–ROM Controllers and Products Containing Same II, Investigation No. 337–TA–409, by Joel M. Freed, Stephen J. Rosenman, Edwin H. Wheeler, Howrey & Simon, Counsel for Complainant, Oak Technology Incorporated, U.S. International Trade Commission, stamped received May 24, 1999 (62 pages), Table of Contents (i–iii), Table of Authorities (iv–vi), Appendix to Petition for Review of Final Initial Determination of Complainant Oak Technology, Incorporated (10 pages).

Disk-Drive Controllers Automate Data Flow, R. Nass, Electronic Design Article No. 20, Oct. 1, 1992, pp. 79–80, 82, & 85.

Complaint Oak Technologies Incorporated's Response Brief Regarding the Commissioner's Review of Final Initial Determination and Order No. 15, In the Matter of: Certain CD–ROM Controllers and Products Containing Same II, Investigation No. 337–TA–409, by Joel M. Freed, Michael J. Songer, Bert C. Reiser, Howrey & Simon, Counsel for Complainant, Oak Technology Incorporated, U.S. International Trade Commission, Before the Honorable Sidney Harris Administrative Law Judge, stamped received Jul. 20, 1999 (73 pages), Table of Contents (pp. i–iv), Table of Authorities (v–viii).

IDE/ATE Disk Interface Hits the Wall, B.C Cole, Electronic Engineering Times Special Report—Design, May 3, 1993, pp. 46–50.

Compact Disc Terminology by James R. Fricks, Disc Manufacturing Inc., Rev. 1.0 6/92, 1992.

International Search Report dated Apr. 6, 1998 for PCT/US 97/21242.

US Court of Appeals for the Federal Circuit, Doc #00–1078, Oak Technology vs. Mediatek, United Microelectronics, Lite-On Technology and Aopen, Inc., 30 pages, May 2, 2001

Written Opinion, date of mailing Sep. 9, 1998, Application No. PCT/UUS97/21242, filing date 19/11/1997, Patent Classification G06F3/06.

Declaration of Robert G. Wedig, Investigation No. 337–TA–409 by the United States International Trade Commission, 57 pages.

Nonconfidential Brief of Appellant Oak Technology, Inc.; Appeal No. 00–1078; United States Court of Appeals For the Federal Circuit, Oak Technology, Inc. v. International Trade Commission and Mediatek, Inc. United Microelectronics Corp., Lite–On Technology Corp., and AOPEN, Inc.; On Appeal from the United States International Trade Commission in Investigation No. 337–TA–409; Joel M. Freed, Esq., Michael J. Songer, Esq., Christopher L. Kelley, Esq., Thomas C. Fiala, Esq., Howrey Simon Arnold & White, LLP, dated Feb. 24, 2000.

Brief Of Appellee United States International Trade Commission, United States Court of Appeals for the Federal Circuit,; Oak Tech., Inc. v. International Trade Commission and Mediatek, Inc., United Microelectronics Corp., Lite–On Technology Corp., and AOPEN, Inc.;On Appeal from the U.S. International Trade Commission in Investigation No. 337–TA–409; Appeal No. 00–1078; Timothy P. Monaghan, Attorney, Lyn M. Schlitt, James A. Toupin, Office of the General Counsel, U.S. International Trade Commission, dated Apr. 7, 2000.

Corrected Brief of Intervenors Mediatek, Inc., United Microelectronics Corp., Lite-On Tech. Corp., and AOPEN, Inc.; Appeal No. 00–1078; United States Court of Appeals for the Federal Circuit, Oak Tech., Inc. v. International Trade Commission and Mediatek, Inc., United Microelectronics Corp., Lite-On Tech. Corp. and AOPEN, Inc.; On Appeal from the U.S. International Trade Commission in Investigation No. 337–TA-409; Michael A. Landra, Esq., James C. Otteson, Esq., Lisa G. McFall, Esq., Wilson, Sonsini, Goodrich & Rosati, dated Apr. 13, 2000.

Nonconfidential Joint Appendix Volume I; pp. 1–416; Appeal No. 00–1078, United States Court of Appeals for the Federal Circuit, Oak Technology, Inc., v. International Trade Commission, Mediatek, Inc., United Microelectronics Corp., Lite–On Technology Corp., and Aopen, Inc.: On Appeal from the United States International Trade Commission in Investigation No. 337–TA–409; Joel M. Freed, Esq., Michael J. Songer, Esq., Christopher L. Kelley, Esq., Thomas C. Fiala, Esq., Howrey Simon Arnold & White, LLP. May 1, 2000.

Nonconfidential Joint Appendix Vol. II; pp. 417–913,; Appeal No. 00–1078, United States Court of Appeals for the Federal Circuit, Oak Technology, Inc., v. International Trade Commission, Mediatek, Inc., United Microelectronics Corp., Lite–On Technology Corp., and Aopen, Inc.: On Appeal from the United States International Trade Commission in Investigation No. 337–TA–409; Joel M. Freed, Esq., Michael J. Songer, Esq., Christopher L. Kelley, Esq., Thomas C. Fiala, Esq., Howrey Simon Arnold & White, LLP. May 1, 2000.

Nonconfidential Joint Appendix vol. III; pp. 914–2423: Appeal No. 00–1078, United States Court of Appeals for the Federal Circuit, Oak Technology, Inc., v. International Trade Commission, Mediatek, Inc., United Microelectronics Corp., Lite–On Technology Corp., and Aopen, Inc.: On Appeal from the United States International Trade Commission in Investigation No. 337–TA–409; Joel M. Freed, Esq., Michael J. Songer, Esq., Christopher L. Kelley, Esq., Thomas C. Fiala, Esq., Howrey Simon Arnold & White, LLP. May 1, 2000.

Reply Brief of Appellant Oak Technology, Incorporated; United States Court of Appeals for the Federal Circuit, Oak Technology, Inc., v. International Trade Commission, and Mediatek, Inc., United Microelectronics Corp., Lite—On Technology Corp., and Aopen, Inc., On Appeal from the United States International Trade Commission in Investigation No. 337–TA—409; Joel M. Freed, Esq., Michael J. Songer, Esq., Christopher L. Kelley, Esq., Thomas C. Fiala, Esq., Howrey Simon Arnold & White, LLP, dated May 11, 2000.

Letter from Howrey Simon Arnold & White, LLP, dated Oct. 30, 2000, Re Citation of Supplemental Authority—Oak Technology, Incorporated v. International Trade Commission, Appeal No. 00–1078, to The Honorable Jan Horbaly, U.S. Court of Appeals for the Federal Circuit, by Hand Deliverv.

Letter from Timothy P. Monaghan, Office of the General Counsel, United States International Trade Commission, dated Nov. 7, 2000, Re Citation of Supplemental Authority—Oak Technology, Incorporated v. International Trade Commission, Appeal No. 00–1078, to The Honorable Jan Horbaly, U.S. Court of Appeals for the Federal Circuit.

Letter dated Nov. 20, 2001 from James C. Otteson of Wilson, Sonsini, Goodrich & Rosati to the Honorable Ronald M. Whyte via hand delivery regarding Oak Technology, Inc. v. United Microelectronics Corporation, Case No. 97–20959 RMW (2 pgs).

Letter dated Nov. 13, 2001 from Michael A. Ladra of Wilson, Sonsini, Goodrich & Rosati to the Honorable Ronald M. Whyte via hand delivery regarding Oak Technology, Inc. v. United Microelectronics Corporation, Case No. 97–20959 RMW (4 pgs).

Order re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. C 97–20959 RMW (Consolidated with C 97–21126 RMW) in the United States District Court, For the Northern District of California, San Jose Division, signed by Ronald M. Whyte, United States District Judge (3 pgs).

[Proposed] First Amended Answer and Counterclaims of United Microelectronics Corporation re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. 97–20959 RMW (ARB) dated Aug. 10, 2001 (19 pgs).

Order Granting Plaintiff Oak Technology's Motion to Dismiss Declaratory Relief Claims and Denying United Microelectronics' Counter–Motion for Leave to Amend re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. 97–20959 RMW dated Oct. 10, 2001 and signed by Ronald M. Whyte, United States District Judge on Oct. 3, 2001 (15 pgs).

United Microelectronics Corporation's Opposition to Oak Technology, Inc.'s Motion for Dismissal and Notice of Counter-Motion and Counter-Motion for Leave to Amend Counterclaims re Oak Technology, Inc. v. United Microelectronics Corporation, Case No. 97-20959 RMW (ARB), dated Aug. 10, 2001 (13 pgs); [Proposed] Order Denying Oak Technology, Inc.'s Motion for Dismissal and Granting United Microelectronics Corp.'s Counter-Motion for Leave to Amend Counterclaims (unsigned) (2 pgs); Certificate of Service of United Microelectronics Corporation's Opposition to Oak Technology Inc.'s Motion for Dismissal and Notice of Counter-Motion and Counter-Motion for Leave to Amend Counterclaims and [Proposed] Order Denying Oak Technology, Inc.'s Motion for Dismissal and Granting United Microelectronics Corp.'s Counter-Motion for Leave to Amend Counterclaims, dated Aug. 13, 2001 (2 pgs).

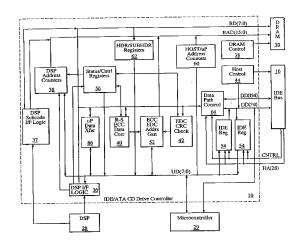

FIG. 1

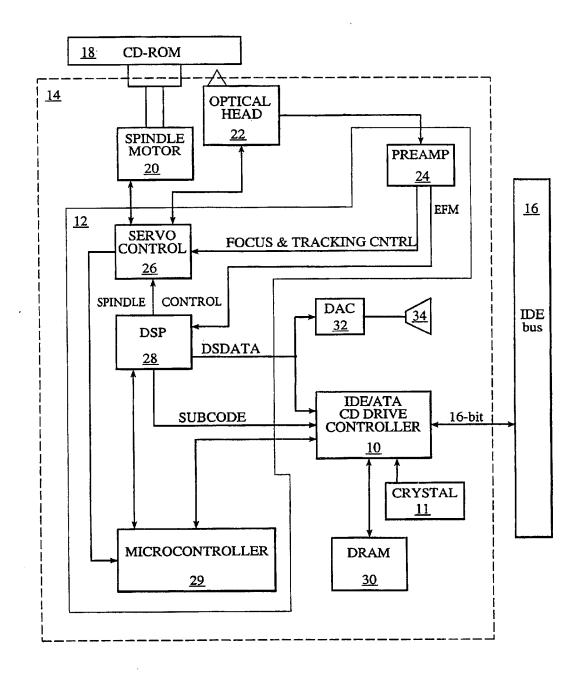

FIG. 3a

Apr. 13, 2004

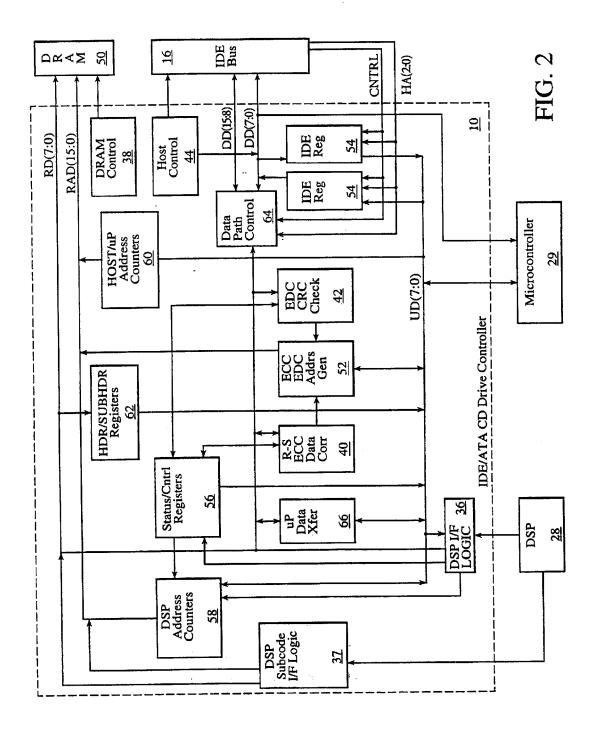

| Pin# | Pin Name | Туре | Comments           | Pin# | Pin Name | Туре | Comments             |

|------|----------|------|--------------------|------|----------|------|----------------------|

| 1    | VSSE     | P    |                    | 29   | UD6      | В    | uCOM Data Bus        |

| 2    | RAD3     | 0    | RAM Address Bus    | 30   | VSSE     | P    |                      |

| 3    | RAD11    | 0    |                    | 31   | UD7      | В    | uCOM Data Bus        |

| 4    | RAD12    | 0    |                    | 32   | URS      | I    | uCOM Register Select |

| 5    | RAD13    | 0    |                    | 33   | URD-     | I    | uCOM Read Strobe     |

| 6    | RAD15    | 0    |                    | 34   | UWR-     | I    | uCOM Write Strobe    |

| 7    | VSSE     | P    |                    | 35   | UCS-     | I    | uCOM Chip Select     |

| 8    | DLRCK    | I    | 44.1KHz L/R Strobe | 36   | UINT-    | 0    | uCOM Interrupt       |

| 9    | DSDATA   | I    | Serial Data        | 37   | HDASP-   | В    | IDE Host Interface   |

| 10   | DBCK     | I    | Serial Bit Clock   | 38   | CS3FX    | Ī    |                      |

| 11   | DC2PO    | I    | C2 Pointer Input   | 39   | CS1FX    | I    |                      |

| 12   | RDPAR    | В    | RAM Parity Data    | 40   | HA2      | I    |                      |

| 13   | MCK      | 0    |                    | 41   | VDD      | P    |                      |

| 14   | XOUT     | 0    | X'tal OSC Output   | 42   | HAO      | I    | IDE Host Interface   |

| 15   | XIN      | I    | X'tal OSC Input    | 43   | HPDIAG-  | В    |                      |

| 16   | VSSI     | P    |                    | 44   | HA1      | I    |                      |

| 17   | SBSO     | I    | Subcode Interface  | 45   | IOCS16-  | 0    |                      |

| 18   | WFCK     | I    |                    | 46   | VSSE     | P    |                      |

| 19   | SUB      | I    | •                  | 47   | HIRQ     | 0    | IDE Host Interface   |

| 20   | EXCK     | В    |                    | 48   | DMACK-   | I    |                      |

| 21   | VDD      | P    |                    | 49   | IORDY    | 0    |                      |

| 22   | UDO      | В    | uCOM Data Bus      | 50   | HRD-     | I    |                      |

| 23   | UD1      | В    |                    | 51   | VSSE     | P    |                      |

| 24   | VSSE     | P    |                    | 52   | HWR-     | I    | IDE Host Interface   |

| 25   | UD2      | В    | uCOM Data Bus      | 53   | HDRQ     | 0    |                      |

| 26   | UD3      | В    |                    | 54   | HD15     | В    |                      |

| 27   | UD4      | В    |                    | 55   | HD0      | В    | IDE Host Data Bus    |

| 28   | UD5      | В    |                    | 56   | HD14     | В    |                      |

FIG. 3b

US 6,721,828 B2

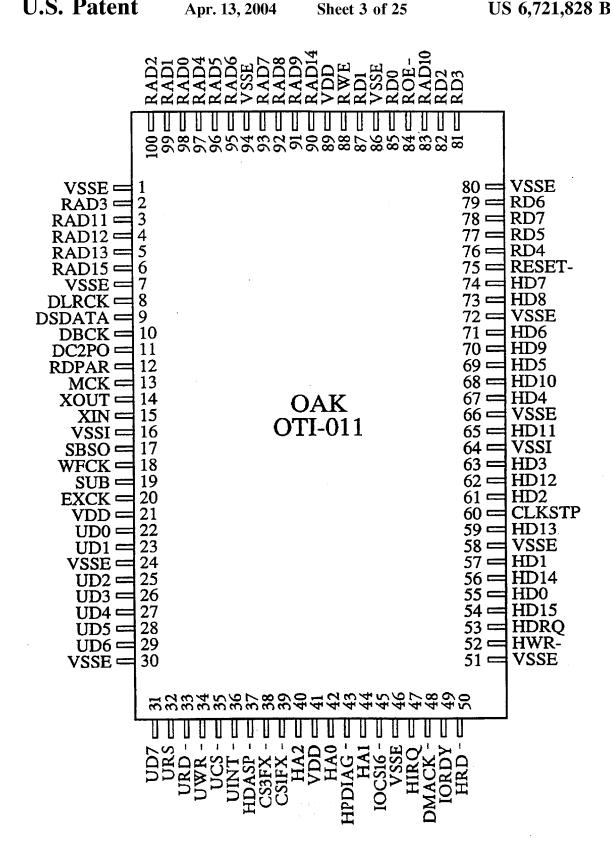

| Pin# | Pin Name | Туре | Comments          | Pin# | Pin Name | Туре | Comments         |

|------|----------|------|-------------------|------|----------|------|------------------|

| 57   | HD1      | В    | IDE Host Data Bus | 79   | RD6      | В    | RAM Data Bus     |

| 58   | VSSE     | P    |                   | 80   | VSSE     | P    |                  |

| 59   | HD13     | В    | IDE Host Data Bus | 81   | RD3      | В    | RAM Data Bus     |

| 60   | CLKSTP   | I    |                   | 82   | RD2      | В    |                  |

| 61   | HD2      | В    | IDE Host Data Bus | 83   | RAD10    | 0    | RAM Address Bus  |

| 62   | HD12     | В    |                   | 84   | ROE-     | В    | RAM Read Enable  |

| 63   | HD3      | В    | •                 | 85   | RDO      | В    | RAM Data Bus     |

| 64   | VSSI     | P    |                   | 86   | VSSE     | P    |                  |

| 65   | HD11     | В    | IDE Host Data Bus | 87   | RD1      | В    | RAM Data Bus     |

| 66   | VSSE     | P    |                   | 88   | RWE-     | 0    | RAM Write Enable |

| 67   | HD4      | В    | IDE Host Data Bus | 89   | VDD      | P    |                  |

| 68   | HD10     | В    |                   | 90   | RAD14    | 0    | RAM Address Bus  |

| 69   | HD5      | В    |                   | 91   | RAD9     | 0    |                  |

| 70   | HD9      | В    |                   | 92   | RAD8     | 0    |                  |

| 71   | HD6      | В    |                   | 93   | RAD7     | 0    |                  |

| 72   | VSSE     | P    |                   | 94   | VSSE     | P    |                  |

| 73   | HD8      | В    | IDE Host Data Bus | 95   | RAD6     | 0    | RAM Address Bus  |

| 74   | HD7      | В    |                   | 96   | RAD5     | 0    |                  |

| 75   | RESET-   | I    |                   | 97   | RAD4     | 0    |                  |

| 76   | RD4      | В    | RAM Data Bus      | 98   | RAD0     | 0    |                  |

| 77   | RD5      | В    | ]                 | 99   | RAD1     | 0    |                  |

| 78   | RD7      | В    |                   | 100  | RAD2     | 0    |                  |

FIG. 3c

| Pin Name | Pin Type           | Pin Description                                                                                                                                                                                   |

|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UD7-UD0  | I/O                | uCONTROLLER DATA BUS - Microcontroller bidirectional data bus. This bus is compatible with most microcontrollers.                                                                                 |

| URS-     | IN                 | uCONTROLLER REGISTER SELECT - Register select input. AR (address register) is selected if URS=0. Otherwise, microcontroller will access the internal register that is pointed by the AR register. |

| URD-     | IN                 | uCONTROLLER READ STROBE - Microcontroller read strobe.                                                                                                                                            |

| UWR-     | IN                 | uCONTROLLER WRITE STROBE - Microcontroller write strobe.                                                                                                                                          |

| UCS-     | IN                 | uCONTROLLER CHIP SELECT - Microcontroller chip select input.                                                                                                                                      |

| UINT-    | OUT/<br>Open-Drain | uCONTROLLER INTERRUPT - Microcontroller interrupt output. This is an open-drain ouput. This signal can be externally wired - OR with other interrupt sources.                                     |

| Pin Name   | Pin Type               | Pin Description                                                                                                                                                                                                                                          |

|------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HD15 - HD0 | I/O                    | HOST DATA BUS - Host Bidirectional Data Bus.                                                                                                                                                                                                             |

| HWR-       | IN                     | HOST WRITE STROBE - Host IO write strobe.                                                                                                                                                                                                                |

| HRD-       | IN                     | HOST READ STROBE - Host IO read strobe.                                                                                                                                                                                                                  |

| НА2-НА0    | IN                     | HOST ADDRESS - These are the 3-bit Host Addresses asserted by the host to access a register or data port in the OTI-011.                                                                                                                                 |

| IOCS16-    | OUT/<br>Open-<br>Drain | DRIVE 16-bits I/O - For PIO transfer, IOCS16- indicates to the host system that the 16-bit data port has been addressed and OTI-011 is prepared to send or receive 16-bit data word.                                                                     |

| CS1FX-     | IN                     | HOST CHIP SELECT 1 - This is the chip select signal decoded from the host address bus used to-select the Command Block registers in the OTI-011.                                                                                                         |

| CS3FX-     | IN                     | HOST CHIP SELECT 3 - This is the chip select signal decoded from the host address bus used to select the Control Block registers in the OTI-011.                                                                                                         |

| HDRQ       | OUT                    | HOST DMA REQUEST - This signal will be asserted for DMA data transfer when OTI-011 is ready to transfer data to or from the host. This signal is used in a handshake manner with DMACK When a DMA operation is enabled, data transfers are 16-bits wide. |

| DMACK-     | IN                     | HOST DMA ACKNOWLEDGE - This signal is used by the host in response to HDRQ.                                                                                                                                                                              |

| HIRQ       | OUT                    | HOST INTERRUPT - This signal is used to interrupt the host system.                                                                                                                                                                                       |

| IORDY      | OUT                    | HOST IO READY - This signal is asserted to extend the host transfer cycle of any host read access when the OTI-011 is not ready to respond to a request.                                                                                                 |

| HDASP-     | ľO                     | HOST DRIVE ACTIVE/DRIVE 1 PRESENT - This is a time-multiplexed signal which indicates that a drive is active, or that Drive 1 is present. This signal is controlled by the firmware.                                                                     |

| HPDIAG-    | ľO                     | HOST PASSED DIAGNOSTICS - This signal is asserted by Drive 1 to indicate to Drive 0 that it has completed diagnostics. This signal is controlled by the firmware.                                                                                        |

FIG. 5a

| Addresses |        |     |      |     | Func                                       | ctions          |

|-----------|--------|-----|------|-----|--------------------------------------------|-----------------|

| OCIEV     | CCSEV  | DAG | D.4. | DAG | Read (DIOR-)                               | Write (DIOW-)   |

| CS1FX-    | CS3FX- | DAZ | DAI  | DA0 | Control blo                                | ock registers   |

| N         | N      | х   | х    | х   | Data bus high impedance                    | Not Used        |

| N         | A      | 1   | 1    | 0   | Alternate ATAPI status                     | Device control  |

| N         | А      | 1   | 1    | 1   | Drive Address                              | Not Used        |

|           |        |     |      |     | Command                                    | block registers |

| A         | N      | 0   | 0    | 0   | Data                                       | Data            |

| Α         | N      | 0   | 0    | 1   | ATAPI Error Register                       | ADAPI Features  |

| A         | N      | 0   | 1    | 0   | ATAPI Interrupt Reason Register (R/W)      |                 |

| A         | N      | 0   | 1    | 1   | Not Used                                   | Not Used        |

| A         | N      | 1   | 0    | 0   | ATAPI Byte Count Register (bit 7-0) (R/W)  |                 |

| A         | N      | 1   | 0    | 1   | ATAPI Byte Count Register (bit 15-8) (R/W) |                 |

| Α         | N      | 1   | 1    | 0   | Drive Select (R/W)                         |                 |

| Α         | N      | 1   | 1    | 1   | ATAPI Status ATA Command                   |                 |

| A         | A      | х   | х    | х   | Invalid address Invalid Address            |                 |

Logic conventions are: A = signal asserted, N = signal negated

FIG. 5b

| Pin Name | Pin Type | Pin Description                                                                                                                                                                     |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSDATA   | IN       | DSP SERIAL DATA - This serial input receives the data from DSP (CIRC decoder). The DBCK pin provides the data clock to the OTI-011. The received data are stored in the buffer RAM. |

| DBCK     | IN       | DSP BIT CLOCK - This clock input receives bit clock from DSP.                                                                                                                       |

| DLRCK    | IN.      | DSP L/R CLOCK - Supplies the signal which is used to distinguish L-channel/R-channel (44.1KHz) DLRCK signal also indicates the start timing of 16 bit PCM word.                     |

| DC2PO    | IN       | DSP C2 POINTER - Supplies C2 error flag signal from DSP. When high, DC2PO indicates an error condition.                                                                             |

FIG. 6

| Pin Name | Pin Type | Pin Description                                                                                                          |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------|

| SBSO     | IN       | SUBCODE SERIAL DATA - Supplies Subcode serial data. The subcode words (P-W) will be stored into buffer RAM in the order. |

| SUB      | IN       | SUBCODE SYNC - Supplies Subcodes SYNC from DSP.                                                                          |

| EXCK     | I/O      | EXTERNAL CLOCK - Supplies Bit Clock for Subcode interface. This pin can be programmed as input or output.                |

| WFCK     | IN       | WRITE FRAME CLOCK - Supplies Write Frame Clock from DSP. (7.35KHz)                                                       |

| Pin Name       | Pin Type | Pin Description                                                                     |

|----------------|----------|-------------------------------------------------------------------------------------|

| RAD15-<br>RAD0 | OUT      | RAM ADDRESS BUS - Buffer RAM address outputs.                                       |

| RDPAR          | I/O      | RAM PARITY DATA - RAM Parity bit when RPEN = 1.                                     |

| RD7 - RD0      | I/O      | RAM DATA BUS - Buffer RAM data bus.                                                 |

| RWE-           | OUT      | RAM WRITE ENABLE - The OTI-011 forces this pin low when writing data to the RAM.    |

| ROE-           | OUT      | RAM OUTPUT ENABLE - The OTI-011 forces this pin low when reading data from the RAM. |

## FIG. 8a

| Pin Name    | Pin Function | Note                 |  |

|-------------|--------------|----------------------|--|

| RA0 - RA8   | DRAM address |                      |  |

| RA9         |              | Left Open (see note) |  |

| RA10        | CAS-         |                      |  |

| RA11 - RA13 |              | Left Open (see note) |  |

| RA14        | RAS-         |                      |  |

| RA15        |              | Left Open (see note) |  |

FIG. 8b

#### Miscellaneous Pins

| Pin Name    | Pin Type  | Pin Description                                                                                                                                                                                                                                                                                  |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN<br>XOUT | IN<br>OUT | XTAL INPUT/XTAL OUTPUT - XIN, XOUT are normally connected to a crystal. (up to 21MHz) XIN pin may be driven by the external signal. (21 MHz max. 45-55% duty) The OTI-011 contains an internal resister between XIN and XOUT, so that an external resister shall not be connected to these pins. |

| MCK         | OUT       | M CLOCK - This output supplies clock signal of one-half the crystal frequency when register bit MCK1 is low. When register bit MCK1 is high, MCK pin supplies crystal frequency.                                                                                                                 |

| CLKSTP      | IN        | CLOCK STOP - CLKSTP stops the internal clock, when it is high.                                                                                                                                                                                                                                   |

| RESET-      | IN        | RESET - Forcing this input low reset the OTI-011. OTI-011 can be reset by either this reset signal or the internal reset command (Writing RESET register). RSSTAT register shows user which reset most recently took place.                                                                      |

| VDD         |           | Supplies 5.0V+/- 5%                                                                                                                                                                                                                                                                              |

| VSSE/VSSI   |           | Ground Pins                                                                                                                                                                                                                                                                                      |

# FIG. 9

| AR - Ad | dress R | egister |       |       |       |       |       |       |       |

|---------|---------|---------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре    | Bit-7   | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| -       | R       |         |       |       | add   | ress  |       |       |       |

| -       | W       |         |       |       | add   | ress  |       |       |       |

| COMIN   | - Com | nand Pacl | ket Registe | er    |       |       |       |       |       |

|---------|-------|-----------|-------------|-------|-------|-------|-------|-------|-------|

| Address | Туре  | Bit-7     | Bit-6       | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 00h     | R     |           |             |       | bin   | ary   |       |       | •     |

| 00h     | W     | unused    |             |       |       |       |       |       |       |

FIG. 11

| IFSTAT  | IFSTAT/IFCTRL - Interface Status Register/Interface Control Register |        |         |        |       |        |       |        |       |  |

|---------|----------------------------------------------------------------------|--------|---------|--------|-------|--------|-------|--------|-------|--|

| Address | Турс                                                                 | Bit-7  | Bit-6   | Bit-5  | Bit-4 | Bit-3  | Bit-2 | Bit-1  | Bit-0 |  |

| 01h     | R                                                                    | cmdib  | dteib   | decib  | X     | dtbsyb | X     | dtenb  | X     |  |

| 01h     | W                                                                    | cmdien | deteien | decien | 0     | 0      | 0     | douten | 0     |  |

| DBCL -  | Data B | yte/Word | Counter |       |       |       |       |       |       |

|---------|--------|----------|---------|-------|-------|-------|-------|-------|-------|

| Address | Type   | Bit-7    | Bit-6   | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 02h     | R      | b7       | b6      | b5    | b4    | b3    | b2    | b1    | ъ0    |

| 02h     | W      | b7       | b6      | b5    | b4    | b3    | b2    | b1    | b0    |

# FIG. 13

| DBCH -  | Data B | yte/Word | Counter |       |       |       |       |       |       |

|---------|--------|----------|---------|-------|-------|-------|-------|-------|-------|

| Address | Туре   | Bit-7    | Bit-6   | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 03h     | R      | dtei     | dtei    | dtei  | dtei  | b11   | b10   | ь9    | b8    |

| 03h     | w      | 0        | 0       | 0     | 0     | bll   | b10   | b9    | b8    |

# FIG. 14

| HEAD0/  | DACL | - Header | Register 0 | /Data Add | iress Coun | ter   |       |       |       |

|---------|------|----------|------------|-----------|------------|-------|-------|-------|-------|

| Address | Type | Bit-7    | Bit-6      | Bit-5     | Bit-4      | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 04h     | R    |          |            | head      | er minutes | (bcd) |       |       |       |

| 04h     | w    | a7       | a6         | a5        | a4         | a3    | a2    | a1    | a0    |

| HEAD1/                     | DACL | - Header | Registers/                    | Data Addr | ess Count | er    |       |       |       |

|----------------------------|------|----------|-------------------------------|-----------|-----------|-------|-------|-------|-------|

| Address                    | Туре | Bit-7    | Bit-6                         | Bit-5     | Bit-4     | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 05h R header seconds (bcd) |      |          |                               |           |           |       |       |       |       |

| 05h                        | w    | a15      | a15 a14 a13 a12 a11 a10 a9 a8 |           |           |       |       |       |       |

FIG. 16

Apr. 13, 2004

| HEAD2/  | DTTRO                     | 3 - Heade | Registers | /Data Tran | sfer Trigge | er    |       |       |       |

|---------|---------------------------|-----------|-----------|------------|-------------|-------|-------|-------|-------|

| Address | Туре                      | Bit-7     | Bit-6     | Bit-5      | Bit-4       | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 06h     | 06h R header frames (bcd) |           |           |            |             |       |       |       |       |

| 06h     | 06h W (data unused)       |           |           |            |             |       |       |       |       |

# FIG. 17

| HEAD3/  | DTAC | K - Heade     | r Registers | /Data Trar | sfer Ackno | owledge |       |       |       |

|---------|------|---------------|-------------|------------|------------|---------|-------|-------|-------|

| Address | Type | Bit-7         | Bit-6       | Bit-5      | Bit-4      | Bit-3   | Bit-2 | Bit-1 | Bit-0 |

| 07h     | R    |               |             | head       | der mode ( | bcd)    |       |       |       |

| 07h     | W    | (data unused) |             |            |            |         |       |       |       |

# FIG. 18

| STARTING POINT       | MODE 1 (MODRQ=0) | MODE 2 (MODRQ=1) |

|----------------------|------------------|------------------|

| First Sync Byte      | FF,F0h           | FF,E8h           |

| First Header Byte    | FF,FCh           | FF,F4h           |

| First Subheader Byte | -                | FF,F8h           |

| First User Data Byte | 00,00h           | 00,00h           |

# FIG. 19

| PTL/WA  | PTL/WAL - ECC Block Pointer/Write Address Counter |       |       |       |       |       |       |       |            |  |  |  |

|---------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|------------|--|--|--|

| Address | Туре                                              | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0      |  |  |  |

| 08h     | R                                                 | a7    | a6    | a5    | a4    | a3    | a2    | al    | 0          |  |  |  |

| 08h     | W                                                 | a7    | a6    | a5    | a4    | a3    | a2    | al    | <b>a</b> 0 |  |  |  |

| PTH/WA  | H - EC | C Block | Pointer/Wr | ite Addres | s Counter |       |       |       |       |

|---------|--------|---------|------------|------------|-----------|-------|-------|-------|-------|

| Address | Туре   | Bit-7   | Bit-6      | Bit-5      | Bit-4     | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 09h     | R      | a15     | al4        | a13        | a12       | all   | a10   | a9    | a8    |

| 09h     | w      | a15     | a14        | a13        | a12       | a11   | a10   | a9    | a8    |

FIG. 21

| US           | 6,721  | .828 | <b>B2</b>    |

|--------------|--------|------|--------------|

| $\mathbf{c}$ | Uq / Z | ,040 | $D_{\omega}$ |

| WAL/C1  | RLO - | Write Add | ress Coun | ter/Contro | 0 Register | ſ     |       |       |       |

|---------|-------|-----------|-----------|------------|------------|-------|-------|-------|-------|

| Address | Type  | Bit-7     | Bit-6     | Bit-5      | Bit-4      | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 0Ah     | R     | a7        | a6        | a5         | a4         | a3    | a2    | a1    | 0     |

| 0Ah     | W     | decen     | 0         | e01rq      | autorq     | . 0   | wrrq  | qrq   | prq   |

FIG. 22

| DECEN<br>0Ah.7 | WRRQ<br>0Ah.2 | E01RQ<br>0Ah.5 | QRQ<br>0Ah.1 | PRQ<br>0Ah.0 | DECODER<br>OPERATION   | CRCOK<br>(0Ch.7) | HEAD0-3,<br>SUBHO-3<br>(04-07h,14-17TH) |

|----------------|---------------|----------------|--------------|--------------|------------------------|------------------|-----------------------------------------|

| 1              | 1             | 1.             | 1            | 1            | Q-P-correction         | Valid            | Buffer RAM                              |

| 1              | 1             | 1              | 1            | 0            | Q-correction           | Valid            | Buffer RAM                              |

| 1              | 1             | 1              | 0            | 1            | P-correction           | Valid            | Buffer RAM                              |

| 1              | 1             | х              | 0            | 0            | Write-only<br>(no ECC) | Valid            | Buffer RAM                              |

| 1              | 0             | X              | 0            | 0            | Disk-monitor           | Invalid          | Incoming data                           |

| 1              | 0             | x              | х            | 1            | Not recommended        |                  | (see note)                              |

| 1              | 0             | x              | 1            | х            | Not recommended        |                  | (see note)                              |

| 0              | x             | х              | х            | х            | Decoder disabled       | Invalid          | Invalid                                 |

| WAH/C   | ΓRL1 - | Write Ad | dress Cour | ter/Contro | l 1 Registe | r     |        |        |        |

|---------|--------|----------|------------|------------|-------------|-------|--------|--------|--------|

| Address | Туре   | Bit-7    | Bit-6      | Bit-5      | Bit-4       | Bit-3 | Bit-2  | Bit-1  | Bit-0  |

| OBh     | R      | a15      | a14        | a13        | a12         | al1   | a10    | a9     | a8     |

| 0Bh     | W      | syien    | syden      | dscren     | cowren      | modrq | formrq | mbckrq | shdren |

| STATO/I | TL - S | tatus 0 Re | gister/ECC | Block Poi | nter  |        |       |       |        |

|---------|--------|------------|------------|-----------|-------|--------|-------|-------|--------|

| Address |        |            | Bit-6      | Bit-5     | Bit-4 | Bit-3  | Bit-2 | Bit-1 | Bit-0  |

| 0Ch     | R      | crcok      | ilsync     | nosync    | lblk  | wshort | sblk  | 0     | uceblk |

| 0Ch     | w      | a7         | a6         | a5        | a4    | a3     | a2    | al    | a0     |

FIG. 25

| US           | 6,721  | .828 | <b>B2</b>    |

|--------------|--------|------|--------------|

| $\mathbf{c}$ | Uq / Z | ,040 | $D_{\omega}$ |

| SYIEN<br>0Bh.7 | SYDEN<br>0Bh.6 | SYNC<br>OPERATION            | ILSYNC<br>0Ch.6 | NOSYNC<br>0Ch.5 | LBLK<br>0Ch.4 | SBLK<br>0Ch.2 |

|----------------|----------------|------------------------------|-----------------|-----------------|---------------|---------------|

| 1              | 1              | Sync-insertion<br>+detection | active          | active          | inactive      | inactive      |

| 1              | 0              | Sync-insertion only          | inactive        | active          | inactive      | active        |

| 0              | 1              | Sync-detection only          | active          | inactive        | active        | inactive      |

FIG. 26

| RMO3<br>0Eh.7 | RMOD2<br>0Eh.6 | RMOD1<br>0Eh.5 | RMOD0<br>0Eh.4 | MODE              |

|---------------|----------------|----------------|----------------|-------------------|

| 0             | 0              | 0              | 0              | 0                 |

| 0             | 0              | 0              | 1              | 1                 |

| 0             | 0              | 1              | 0              | 2                 |

| 0             | 0              | 1              | 1              | 3                 |

| 0             | 1              | 0              | 0              | 4                 |

| 0             | 1              | 0              | 1              | 5                 |

| 0             | 1              | 1              | 0              | 6                 |

| 0             | 1              | 1              | 1              | 7                 |

| 1             | 0              | 0              | 0              | (8*N) +0          |

| 1             | 0              | 0              | 1              | (8*N) +1          |

| 1             | 0              | 1              | 0              | (8*N) +2          |

| 1             | 0              | 1              | 1              | (8*N) +3          |

| 1             | 1              | 0              | 0              | (8*N) +4          |

| 1             | 1              | 0              | 1              | (8*N) +5          |

| 1             | 1              | 1              | 0              | (8*N) +6          |

| 1             | 1              | 1              | 1              | (8*N) +7 or error |

FIG. 29

| STAT1/  | STAT1/PTH - Status 1 Register/ECC Block Pointer |       |       |       |       |       |       |       |        |  |  |  |

|---------|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------|--|--|--|

| Address | Туре                                            | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0  |  |  |  |

| 0Dh     | R                                               | 0     | 0     | 0     | hdera | 0     | 0     | 0     | shdera |  |  |  |

| 0Dh     | W                                               | a15   | al4   | a13   | a12   | all   | a10   | a9    | a8     |  |  |  |

FIG. 27

| STAT2/SFCTRL |      |       |       |       |        |       |       |        |        |  |  |

|--------------|------|-------|-------|-------|--------|-------|-------|--------|--------|--|--|

| Address      | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4  | Bit-3 | Bit-2 | Bit-1  | Bit-0  |  |  |

| 0Eh          | R    | rmod3 | rmod2 | rmodl | rmod0  | mode  | nocor | rform1 | rform0 |  |  |

| 0Eh          | W    |       |       |       | unused |       |       |        |        |  |  |

FIG. 28

| STAT3/RESET |      |        |               |       |       |       |       |       |       |  |  |  |

|-------------|------|--------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|

| Address     | Туре | Bit-7  | Bit-6         | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |  |

| 0Fh         | R    | valstb | 0             | cblk  | 0     | 0     | 0     | 0     | 0     |  |  |  |

| 0Fh         | W    |        | (data unused) |       |       |       |       |       |       |  |  |  |

FIG. 30

| CTRLW   |      |       |       |       |        |       |       |       |       |

|---------|------|-------|-------|-------|--------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4  | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 10h     | R    |       |       |       | unused |       |       |       | -     |

| 10h     | W    | 0     | swen  | sdss  | dclke  | 0     | 0     | 0     | 0     |

FIG. 31

| CRTRG   |      |       |        |       |       |       |       |       |       |  |  |

|---------|------|-------|--------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Type | Bit-7 | Bit-6  | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 11h     | R    |       | unused |       |       |       |       |       |       |  |  |

| 11h     | W    | 0     | 0      | 0     | 0     | 0     | 0     | 0     | crtrl |  |  |

FIG. 32

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4  | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|---------|------|-------|-------|-------|--------|-------|-------|-------|-------|

| 12h     | R    |       |       |       | unused |       |       |       |       |

| 12h     | W    |       |       |       | unused |       |       |       |       |

FIG. 33

| <u> </u> |      |       |       |       |        |       | · <del>-</del> |       |       |

|----------|------|-------|-------|-------|--------|-------|----------------|-------|-------|

| Address  | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4  | Bit-3 | Bit-2          | Bit-1 | Bit-0 |

| 13h      | R    |       |       |       | unused |       |                |       |       |

| 13h      | W    |       |       |       | unused |       |                |       |       |

FIG. 34

| SUBH0   |      |       |                       |       |       |       |       |       |       |  |

|---------|------|-------|-----------------------|-------|-------|-------|-------|-------|-------|--|

| Address | Туре | Bit-7 | Bit-6                 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |

| 14h     | R    |       | subheader file number |       |       |       |       |       |       |  |

| 14h     | W    |       | unused                |       |       |       |       |       |       |  |

| SUBHI   |      |       |                          |       |       |       |       |       |       |  |

|---------|------|-------|--------------------------|-------|-------|-------|-------|-------|-------|--|

| Address | Type | Bit-7 | Bit-6                    | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |

| 15h     | R    |       | subheader channel number |       |       |       |       |       |       |  |

| 15h     | W    |       | unused                   |       |       |       |       |       |       |  |

### FIG. 36

| SUBH2   |      |       |                          |       |        |                                       |       |       |       |

|---------|------|-------|--------------------------|-------|--------|---------------------------------------|-------|-------|-------|

| Address | Туре | Bit-7 | Bit-6                    | Bit-5 | Bit-4  | Bit-3                                 | Bit-2 | Bit-1 | Bit-0 |

| 16h     | R    |       | subheader submode number |       |        |                                       |       |       |       |

| 16h     | W    |       |                          |       | unused | · · · · · · · · · · · · · · · · · · · |       |       |       |

| SUBH3   |      |        |       |          |            |            |       |       |       |

|---------|------|--------|-------|----------|------------|------------|-------|-------|-------|

| Address | Туре | Bit-7  | Bit-6 | Bit-5    | Bit-4      | Bit-3      | Bit-2 | Bit-1 | Bit-0 |

| 17h     | R    |        |       | subheade | r coding i | nformation | 1     |       |       |

| 17h     | W    | unused |       |          |            |            |       |       |       |

FIG. 38

| DECODER OPERATION | REGISTER | ERASURE BYTE # | STORED BYTE#     |

|-------------------|----------|----------------|------------------|

| Disk-monitor      | SUBH0    | no erasures    | incoming byte 16 |

| Disk-monitor      | SUBH0    | byte 16        | incoming byte 20 |

| Disk-monitor      | SUBH0    | byte 16 and 20 | incoming byte 20 |

| Buffered          | SUBH0    | don't care     | buffered byte 20 |

| Disk-monitor      | SUBHI    | no erasures    | incoming byte 17 |

| Disk-monitor      | SUBH1    | byte 17        | incoming byte 21 |

| Disk-monitor      | SUBHI    | byte 17 and 21 | incoming byte 21 |

| Buffered          | SUBH1    | don't care     | buffered byte 21 |

| Disk-monitor      | SUBH2    | no erasures    | incoming byte 18 |

| Disk-monitor      | SUBH2    | byte 18        | incoming byte 22 |

| Disk-monitor      | SUBH2    | byte 18 and 22 | incoming byte 22 |

| Buffered          | SUBH2    | don't care     | buffered byte 22 |

| Disk-monitor      | SUBH3    | no erasures    | incoming byte 19 |

| Disk-monitor      | SUBH3    | byte 19        | incoming byte 23 |

| Disk-monitor      | SUBH3    | byte 19 and 23 | incoming byte 23 |

| Buffered          | SUBH3    | don't care     | buffered byte 23 |

FIG. 39

| VER/XT  | VER/XTAL |       |       |       |       |       |       |       |        |  |  |  |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|--------|--|--|--|

| Address | Type     | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0  |  |  |  |

| 1Ah     | R        | b7    | ъ6    | b5    | ъ4    | ъ3    | b2    | b1    | ъ0     |  |  |  |

| 1Ah     | w        | 0     | 0     | 0     | 0     | mckl  | 0     | 0     | xtald2 |  |  |  |

FIG. 40

| DSPSL   |      |       |        |       | _     |       |       |       |       |  |  |

|---------|------|-------|--------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Туре | Bit-7 | Bit-6  | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 1Bh     | R    |       | unused |       |       |       |       |       |       |  |  |

| 1Bh     | W    | c2ml  | sel16o | 1ch1  | 0     | 0     | sel16 | dir   | edge  |  |  |

FIG. 41

| UD7<br>c2ml | UD6<br>sel160 | UD5<br>1ch1 | UD4<br>X | UD3<br>X | UD2<br>sel16 | UD1<br>dir | UD0<br>edge | DSP<br>Type        |

|-------------|---------------|-------------|----------|----------|--------------|------------|-------------|--------------------|

| 1           | 0             | 1           | 0        | 0        | 0            | 1          | 0           | Sony CXD1135Q      |

| 1           | 1             | 0           | .0       | 0        | 0            | 1          | 1           | Philips SAA7345    |

| 0           | 0             | 1           | 0        | 0        | 1            | 0          | 0           | Sanyo LC7860K      |

| 0           | 0             | 0           | 0        | 0        | 1            | 1          | 1           | Toshiba            |

| 0           | 0             | 1           | 0        | 0        | 1            | 0          | 1           | Matsushita MN66261 |

FIG. 42

| HCON/UACL |      |       |       |       |        |       |          |                                        |       |  |

|-----------|------|-------|-------|-------|--------|-------|----------|----------------------------------------|-------|--|

| Address   | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4  | Bit-3 | Bit-2    | Bit-1                                  | Bit-0 |  |

| 1Ch       | R    |       |       |       | unused |       | <b>.</b> | *····································· |       |  |

| 1Ch       | W    | a7    | a6    | a5    | a4     | a3    | a2       | al                                     | a0    |  |

FIG. 43

| DSPSL   |      |       |        |       |        |       |                                                  |              |       |

|---------|------|-------|--------|-------|--------|-------|--------------------------------------------------|--------------|-------|

| Address | Туре | Bit-7 | Bit-6  | Bit-5 | Bit-4  | Bit-3 | Bit-2                                            | Bit-1        | Bit-0 |

| 1Bh     | R    |       |        |       | unused |       | <del>'                                    </del> | <del>1</del> |       |

| 1Bh     | W    | c1ml  | sel160 | 1ch1  | х      | х     | sel16                                            | dir          | edge  |

FIG. 44

| HCON/UACL |      |       |       |       |       |       |       |       |       |  |

|-----------|------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Address   | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |

| 1Ch       | R    | 0     | spare | spare | spare | dts   | sdrqb | 1ohi  | dma16 |  |

| 1Ch       | W    | a7    | аб    | a5    | a4    | a3    | a2    | al    | a0    |  |

FIG. 45

| UACH    |      |       |       |       |        |       |       |       |       |

|---------|------|-------|-------|-------|--------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4  | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 1Dh     | R    |       |       |       | unused |       |       |       |       |

| 1Dh     | W    | a15   | a14   | a13   | a12    | all   | a10   | a9    | a8    |

FIG. 46

| UACU    |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 2Dh     | W    | 0     | 0     | 0     | 0     | b3    | b2    | b1    | ъ0    |

FIG. 47

| RAMRE   | RAMRD/RAMWR |       |       |       |       |       |       |       |       |  |

|---------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Address | Туре        | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |

| 1Eh     | R           | rr7   | rrб   | п5    | гг4   | rr3   | rr2   | rr1   | rr0   |  |

| 1Eh     | W           | rw7   | rw6   | rw5   | rw4   | rw3   | rw2   | rwl   | rw0   |  |

FIG. 48

| HDDIR   |      |        |       |        |       |       |       |       |       |

|---------|------|--------|-------|--------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7  | Bit-6 | Bit-5  | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 1Fh     | R    | urtbsy | cs13  | 0      | 0     | 0     | 0     | hrwr  | 0     |

| 1Fh     | W    | udtrg  | udata | host16 | 0     | 1     | 1     | 0     | 0     |

FIG. 49

| Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|

| 0     | 1     | 1     | 0     | 0     |

FIG. 50

| HICTL   |      |       |         |        |        |        |       |         |          |

|---------|------|-------|---------|--------|--------|--------|-------|---------|----------|

| Address | Type | Bit-7 | Bit-6   | Bit-5  | Bit-4  | Bit-3  | Bit-2 | Bit-1   | Bit-0    |

| 20h     | W    | 0     | pdiagen | daspen | clrbsy | setbsy | scod  | iordyen | iocs16en |

FIG. 51

| SUBC2   |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 21h     | W    | 0     | 0     | 0     | 0     | nopq  | cdsp2 | cdsp1 | cdsp0 |

FIG. 52

| CDSP2<br>21h.2 | CDSP1<br>21h.1 | CDSP0<br>21h.0 | Subcode Block<br>Rate |

|----------------|----------------|----------------|-----------------------|

| 0              | 0              | 0              | 1X (75 blocks/sec)    |

| 0              | 0              | 1              | 2X (150 blocks/sec)   |

| 0              | 1              | 0              | 4X (300 blocks/sec)   |

| 1              | 0              | 0              | Reserved              |

FIG. 53

| STATS   |      |       |             |       |       |       | _     |        |       |

|---------|------|-------|-------------|-------|-------|-------|-------|--------|-------|

| Address | Type | Bit-7 | Bit-6       | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1  | Bit-0 |

| 22h     | R    |       | data unused |       |       |       | missy | sbkend | silsy |

| 22h     | W    |       | data unused |       |       |       |       |        |       |

FIG. 54

| DBACL   |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 24h     | W    | b7    | b6    | b5    | b4    | b3    | b2    | b1    | ь0    |

| DBACH   |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 25h     | W    | 0     | 0 .   | 0     | 0     | 0     | 0     | 0     | b8    |

# FIG. 56

| SBKL    | SBKL |       |       |       |       |       |       |            |       |  |  |  |

|---------|------|-------|-------|-------|-------|-------|-------|------------|-------|--|--|--|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1      | Bit-0 |  |  |  |

| 26h     | RW   | b7    | b6    | b5    | b4    | b3    | b2    | <b>b</b> 1 | ь0    |  |  |  |

## FIG. 57

| SBKH    |      |             |       |       |       |       |       |       |       |

|---------|------|-------------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7       | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 27h     | RW   | data unused |       |       |       |       |       |       | ъ8    |

## FIG. 58

| WBKL    |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 28h     | RW   | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |

| WBKH    |      | <del>. 3</del> . | -     |       |       |       |       |       |       |

|---------|------|------------------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7            | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 29h     | RW   | data unused      |       |       |       |       |       |       | ъ8    |

FIG. 60

| RAMCF   |      |       |        |       |       |       |       |       |       |  |  |

|---------|------|-------|--------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Туре | Bit-7 | Bit-6  | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 2Ah     | R    | rftyp | ramclr | ram0  | uhilo | rpen  | rcf2  | rcf1  | rcf0  |  |  |

| 2Ah     | w    | rftyp | ramclr | 0     | uhilo | rpen  | rcf2  | rcf1  | rcf0  |  |  |

| RCF2<br>2Ah.2 | RCF1<br>2Ah.1 | RCF0<br>2Ah.0 | RAM Configuration            |

|---------------|---------------|---------------|------------------------------|

| 0             | 0             | 1             | 128K DRAM (256K X 4-bit X 1) |

| 0             | 1             | 0             | 256K DRAM (256K X 4-bit X 2) |

# FIG. 62

| MEMCF   | - Men | nory Layo | ut Configu | ration Re | gister |       |        |       |       |

|---------|-------|-----------|------------|-----------|--------|-------|--------|-------|-------|

| Address | Type  | Bit-7     | Bit-6      | Bit-5     | Bit-4  | Bit-3 | Bit-2  | Bit-1 | Bit-0 |

| 2Bh     | W     | 0         | 0          | 0         | 0      | purg  | iordyf | mly1  | mly0  |

## FIG. 63

| MLY1<br>2Bh.1 | MLY0<br>2BH.0 | DRAM Memory Layout Configuration             |

|---------------|---------------|----------------------------------------------|

| 0             | 0             | Data Blocks + Last 2 Auxilary/Subcode Blocks |

| 1             | 1             | Data Blocks + All Auxilary/Subcode Blocks    |

| SUBCD   | SUBCD - Subcode Control |       |       |       |       |       |       |        |        |  |  |  |

|---------|-------------------------|-------|-------|-------|-------|-------|-------|--------|--------|--|--|--|

| Address | Type                    | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1  | Bit-0  |  |  |  |

| 2Ch     | w                       | sbxck | scen  | scbk2 | scien | exinv | exop  | sbsel1 | sbsel0 |  |  |  |

FIG. 65

| SBSEL1<br>2Ch.1 | SBSEL0 -<br>2Ch.0 | Subcode Format |

|-----------------|-------------------|----------------|

| 0               | 0                 | SMD0 (Philips) |

| 0               | 1                 | SMD1 (EIAJ-1)  |

| 1               | 0                 | SMD2 (EIAJ-2)  |

| 1               | 1                 | Undefined      |

FIG. 66

| UMISC   | UMISC - Miscellaneous Microcontroller Control |        |       |       |               |        |       |        |       |  |  |  |  |

|---------|-----------------------------------------------|--------|-------|-------|---------------|--------|-------|--------|-------|--|--|--|--|

| Address | Type                                          | Bit-7  | Bit-6 | Bit-5 | Bit-4         | Bit-3  | Bit-2 | Bit-1  | Bit-0 |  |  |  |  |

| 2Eh     | R                                             | 1      | 1     | 1     | 1             | 1      | 1     | pdiagb | daspb |  |  |  |  |

| 2Eh     | W                                             | ideien | 0     | drveb | <b>dr</b> v1b | hintrq | 0     | 0      | 0     |  |  |  |  |

FIG. 67

| RSSTAT  | RSSTAT - Reset, IDE, and Subcode Status Register |       |       |         |       |        |       |       |       |  |  |  |

|---------|--------------------------------------------------|-------|-------|---------|-------|--------|-------|-------|-------|--|--|--|

| Address | Type                                             | Bit-7 | Bit-6 | Bit-5   | Bit-4 | Bit-3  | Bit-2 | Bit-1 | Bit-0 |  |  |  |

| 2Fh     | R                                                | srst  | cmd   | diagemd | sint  | parint | rst   | urst  | hrst  |  |  |  |

FIG. 68

| ATFEA/ATERR |      |       |       |            |       |       |       |       |       |  |  |  |

|-------------|------|-------|-------|------------|-------|-------|-------|-------|-------|--|--|--|

| Address     | Туре | Bit-7 | Bit-6 | Bit-5      | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |  |

| 31h         | R    | 0     | 0     | 0          | 0     | 0     | 0     | 0     | dma   |  |  |  |

| 31h         | w    | b7    | b6    | <b>b</b> 5 | b4    | mcr   | abrt  | eom   | ili   |  |  |  |

FIG. 69

| ATINT   |      |       |       |       |       |       |       | ,     |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 32h     | RW   | 0     | 0     | 0     | 0     | 0     | 0     | io    | cod   |

FIG. 70

| ATSPA   |      |       |       |       |       |       |       |       |       |  |  |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 33h     | RW   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |  |  |

FIG. 71

| ATBLO   |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 34h     | RW   | b7    | b6    | b5    | b4    | b3    | b2    | b1    | ь0    |

FIG. 72

| ATBHI   |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 35h     | RW   | b7    | b6    | b5    | b4    | b3    | b2    | bl    | ь0    |

FIG. 73

| ATDRS   |      |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 36h     | RW   | 1     | I     | 1     | drv   | 0     | 0     | 0     | 0     |

FIG. 74

| ATCMD   | ATCMD/ATSTA |       |            |       |       |       |       |       |       |  |  |  |  |

|---------|-------------|-------|------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| Address | Туре        | Bit-7 | Bit-6      | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |  |  |

| 37h     | R           | b7    | <b>b</b> 6 | b5    | b4    | b3    | ь2    | b1    | ъ0    |  |  |  |  |

| 37h     | W           | 0     | drdy       | 0     | drc   | drq   | COIT  | 0     | check |  |  |  |  |

FIG. 75

| DFIF0   | •    |       |       |       |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 40h     | W    | b7    | b6    | b5    | b4    | b3    | b2    | bl    | ъ0    |

FIG. 76

| DFIF1   | DFIF1 |       |       |       |       |       |       |       |       |  |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Address | Туре  | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |  |

| 41h     | w     | ь7    | b6    | b5    | b4    | b3    | b2    | bl    | b0    |  |  |  |

FIG. 77

| DFIF2   |      |       |       |       |       |       |       |       |       |  |  |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 42h     | W    | b7    | b6    | b5    | b4    | ъ3    | b2    | b1    | ь0    |  |  |

FIG. 78

| DFIF3   |      |       |       |       |       |       |       |       |       |  |  |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 43h     | W    | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |  |  |

FIG. 79

| DFIF4   |      |       |       |       |       |       |       |       |       |  |  |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 44h     | w    | b7    | b6    | b5    | b4    | b3    | b2    | bl    | ь0    |  |  |

FIG. 80

| DFIF5   |      |       |       |            |       |       |       |       |       |  |  |

|---------|------|-------|-------|------------|-------|-------|-------|-------|-------|--|--|

| Address | Туре | Bit-7 | Bit-6 | Bit-5      | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 45h     | W    | b7    | b6    | <b>b</b> 5 | b4    | b3    | b2    | b1    | ь0    |  |  |

FIG. 81

| DFIF6   |      |       |       |       |       |       |       |       |       |  |  |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Address | Type | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |  |  |

| 46h     | w    | b7    | b6    | b5    | b4    | b3    | b2    | b1    | ь0    |  |  |

FIG. 82

| DFIF7   |      |       |       | •     |       |       |       |       |       |

|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Туре | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

| 47h     | w    | ь7    | b6    | b5    | b4    | ь3    | b2    | bl    | ь0    |

FIG. 83

# OPTICAL DRIVE CONTROLLER WITH A HOST INTERFACE FOR DIRECT CONNECTION TO AN IDE/ATA DATA BUS

### CROSS-REFERENCE TO RELATED APPLICATIONS