**Product Overview**

December 1991

#### OTI-040 286/386SX Core Logic Subsystem

#### **Features**

- Supports 286 and 386SX CPU for 8 MHz to 25 MHz system speed.

- Highly integrated design

- On-chip Address & Data path

- EMS 4.0 Hardware support with 2 maps of 60 registers each

- 287 support with 386SX

- Async/Sync AT Bus

- Selectable memory cycle

- 82385SX support

- PAGE and NO PAGE mode support

- Peripheral chip select signals

- Fast RESET & GATE 20

- In-circuit test mode

Reduced inventory, same design for 286 & 386SX systems. OTI-041, OTI-042, I/O Controller, 8042, 1 TTL

no external buffers

high-performance EMS driver

low cost floating point solution

flexible bus speed

supports many vendor's DRAMs

cache system support

increases performance

no external decode logic for HDD, FDD,

Video, Keyboard, Parallel port & two serial

ports

optimized for OS/2 support

simplifies board level testing

# Laptop/Notebook designs

#### **Features**

Support for local bus VGA

On-chip RTC with 128 bytes RAM

8-bit BIOS ROM

Decoupled slow Refresh

Cartridge ROM support

O/S independent Power Management

excellent graphics performance

power management programmability

saves board space

reduces power consumption

lightweight notebook design

hardware configure power savings mode,

to support power management

no need for additional BIOS development

reduces CPU clock speed with on-going

memory refresh

intelligent peripheral controller triggers power savings mode automatically by monitoring

INTERRUPT, DMA & I/O activities

pre-programmed pins to power on/off peripheral devices upon receiving signals

from the activity monitors.

well suited for Remote Data Acquisition type

of applications

CPU speed control

**Activity Monitors**

Programmable bidirectional I/O pins

Automatic Wake Up

Product Overview December 1991

#### **General Description**

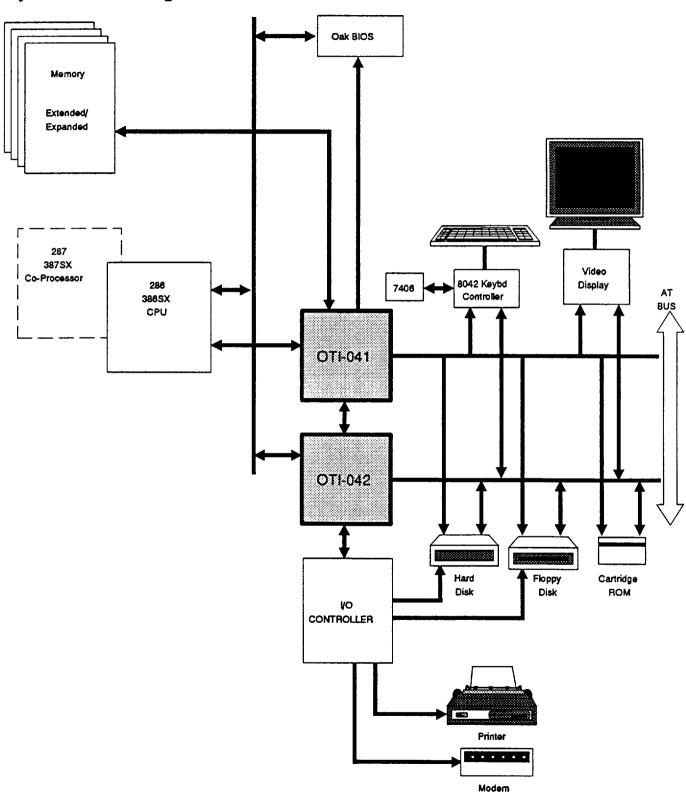

The OTI-040 system chipset is a highly integrated, semi-custom chipset designed for 80286 and 80386SX systems with clock speeds ranging from 8 MHz to 25 MHz. This chipset consists of the System Controller (OTI-041) and the Intelligent Peripheral Controller (OTI-042). Both chips are implemented with 1.2 micron HCMOS technology. The OTI-041 is packaged in a 160-pin PJQFP, and the OTI-042 is packaged in a 144-pin PJQFP.

The OTI-040 chipset brings to systems designers an optimal solution for implementing a low cost, high performance PC/AT system. With the tightly-coupled local bus support provided by the OTI-040 for the Oak Technology LCD VGA Controller, the system designer can achieve outstanding graphics performance without the addition of any external TTL components. The 2/4-way interleaving and page-mode addressing scheme of the OTI-040 allows system designers to achieve very high system performance without the need for a complicated cache system design. For those users who require the utmost performance, the OTI-040 chipset does support an external 82385SX cache controller. To implement a full function PC/AT system, all that is required would be the OTI-041, OTI-042, CPU, ROM, RAM, 8042, I/O Controller, graphics controller, and one 7406. This system provides an amazing PC board area savings. The single-chip AT solutions normally require a lot of external TTL components to complete the system design.

With the OTI-040 chipset, there is no need for any extensive BIOS development to implement your power management scheme for laptop/notebook designs. The O/S Independent Power Management Scheme and the Activity Monitors inside the OTI-040 chipset can bring the laptop/notebook system into power savings modes automatically, without any BIOS intervention.

Product Overview December 1991

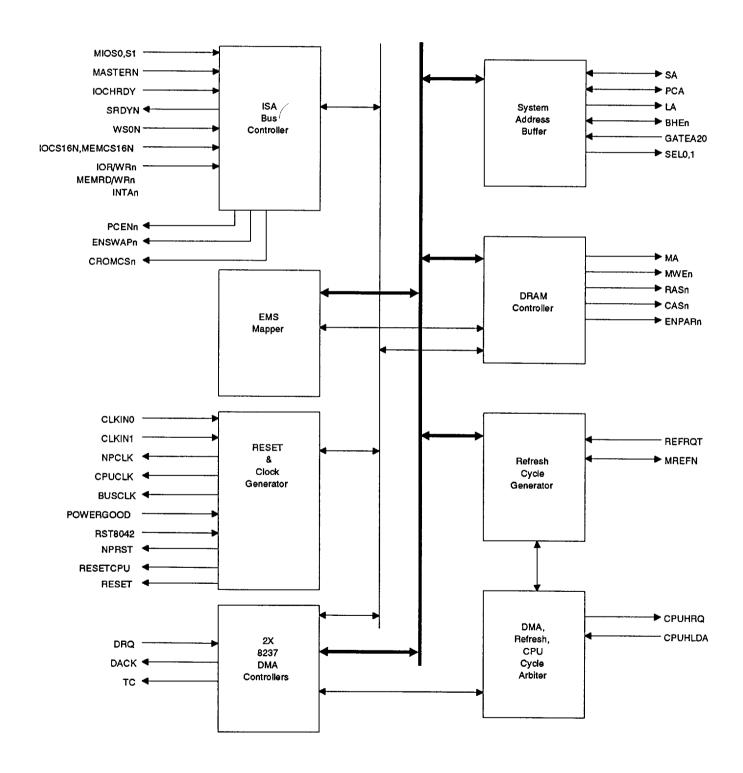

# **OTI-041 Chip Block Diagram**

**Product Overview** December 1991

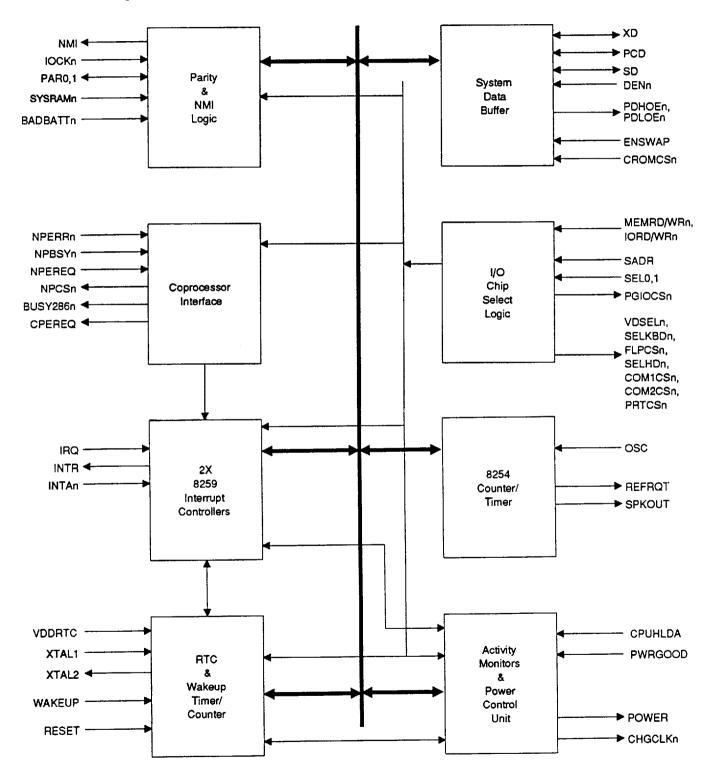

# **OTI-042 Chip Block Diagram**

**Product Overview** December 1991

# **System Block Diagram**

Product Overview December 1991

# **OTI-041 Pin Description**

| Pin<br>Name        | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                               |

|--------------------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Interface      |               |             |                                                                                                                                                                           |

| SA[23:0]           | TBA           | I           | CPU ADDRESS BUS                                                                                                                                                           |

| BHEn               | TBA           | I           | BYTE HIGH ENABLE. An active-low signal used to enable data on to the most significant half of the data bus (D15 - D8).                                                    |

| RESETCPU           | TBA           | Ο           | RESET CPU. An active-high output to reset the CPU.                                                                                                                        |

| NPRST              | TBA           | O           | CO-PROCESSOR RESET. An active-high signal to reset the numerical co-processor.                                                                                            |

| ADSn               | TBA           | I           | ADDRESS STROBE. An active-low signal coming from 80386SX. This input is also used to detect the presence of 386SX. This pin should be pulled low with a 20K-ohm resistor. |

| S1 - S0            | TBA           | I           | BUS CYCLE STATUS. These signals together with M/IO and COD/INTAn are used to decode different bus cycles. S0 and S1 are connected to W/Rm and D/Cm, respectively.         |

| M/IOn              | TBA           | 1           | MEMORY OR I/O CYCLE. An input signal from CPU indicating whether the present cycle is memory or I/O access.                                                               |

| CPUCLK             | TBA           | 0           | CPU CLOCK. A MOS driven clock signal to the 80286/80386SX CPU. The frequency is programmable through index port 0003H.                                                    |

| NPCLK              | TBA           | 0           | CO-PROCESSOR CLOCK. Clock signal for 80287 or 80387SX. This clock can be programmed to stop if co-processor is not used.                                                  |

| SRDYn              | TBA           | O           | SYSTEM READY. An active-low signal to acknowledge the CPU that the data transfer for either memory or I/O is complete.                                                    |

| DMA Interface      |               |             |                                                                                                                                                                           |

| DRQ0-3<br>DRQ5-7   | TBA           | I           | DMA REQUEST. These are asynchronous active-high channel request inputs used by peripheral devices to obtain DMA service.                                                  |

| DACK0-3<br>DACK5-7 | TBA           | 0           | DMA ACKNOWLEDGE. These are active-low signals to notify the individual peripheral that it has been granted a DMA cycle.                                                   |

| CPUHRQ             | TBA           | 0           | HOLD REQUEST. An active-high signal connected directly to HOLD of the CPU. This signal is used by the chip to request the bus from the CPU.                               |

| CPUHLDA            | TBA           | I           | HOLD ACKNOWLEDGE. An active-high signal connected directly to HLDA of CPU. This signal is used by the chip to determine if the bus request has been granted by the CPU.   |

| TC                 | TBA           | 0           | TERMINAL COUNT. An active-high output pulse signal when the terminal count for any DMA channel is reached.                                                                |

| OM TEOTHOLO   | G 1, 1110.    |             | December 1001                                                                                                                                                                            |

|---------------|---------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Name   | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                              |

| Bus Interface |               |             |                                                                                                                                                                                          |

| PCA[19:0]     | TBA           | I/O         | PC BUS ADDRESS (19-0). These are the latched version of SA(0-19) and become input during MASTER mode.                                                                                    |

| LA[23:17]     | TBA           | I/O         | UNLATCHED ADDRESS (23-17). These are the unlatched version of SA(23-17). The bus become input when MASTERn is active.                                                                    |

| PBHEn         | TBA           | I/O         | I/O CHANNEL BYTE HIGH ENABLE. An active-low signal on the I/O channel. It is a latched version of BHEn. When MASTERn is low, it becomes input.                                           |

| WS0n          | TBA           | I           | ZERO WAIT STATE. An active-low signal indicating the present cycle can be completed without any more wait state.                                                                         |

| IOCS16n       | TBA           | I           | 16-BIT I/O CHIP SELECT. An active-low input that indicates to the system that the present data transfer is a 1 wait-state, 16-bit I/O cycle.                                             |

| MEMCS16n      | TBA           | I           | 16-BIT MEMORY CHIP SELECT. An active-low input that indicates to the system that the present data transfer is a 1 wait-state, 16-bit memory cycle.                                       |

| PCALE         | TBA           | 0           | PC ADDRESS LATCH ENABLE. An active-high pulse signal during phase 2 of TS(T1p or T2 for 80386SX) of any bus cycle and is always high when the CPU is held. It is synchronized to BUSCLK. |

| IOCHRDY       | TBA           | I           | I/O CHANNEL READY. An active-high ready signal from an I/O channel. It is pulled low by a memory or I/O device to lengthen memory or I/O cycles.                                         |

| IORDn         | TBA           | ľO          | I/O READ COMMAND. An active-low command to instruct the I/O device to drive its data onto the data bus. It is input when MASTERn is active.                                              |

| IOWRn         | TBA           | ľO          | I/O WRITE COMMAND. An active-low command to instruct the I/O device to read the data present on the data bus. It is input when MASTERn is active.                                        |

| MEMRDn        | TBA           | I/O         | MEMORY READ COMMAND. An active-low signal to instruct the memory subsystem to drive its data onto the data bus. It is input when MASTERn is active.                                      |

| MEMWRn        | TBA           | ľO          | MEMORY WRITE COMMAND. An active-low signal to instruct the memory subsystem to store the data present on the data bus. It is input when MASTERn is active.                               |

| BUSCLK        | TBA           | Ο           | PC-BUS CLOCK. An MOS driven clock signal for the I/O channel.                                                                                                                            |

| Pin<br>Name     | Pin<br>Number | Pin<br>Type |                          |                               | Description                                                                                                             |

|-----------------|---------------|-------------|--------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| System Interfac | ce            |             |                          |                               |                                                                                                                         |

| INTAn/WAKEUF    | n TBA         | I/O         | enable the<br>the data b | e interrupt co                | WLEDGE. An active-low signal to<br>ntroller's interrupt-vector data onto<br>t during shutdown/sleep mode as<br>OTI-041. |

| GATEA20         | TBA           | I           | GATE A20<br>address A    |                               | nigh signal from the 8042 used to gate                                                                                  |

| RST8042n        | TBA           | I           | RESET F                  |                               | n active-low signal from the 8042 to                                                                                    |

| CHKCLKn         | TBA           | I           |                          |                               | PEED. An active-low input signal from change of system speed.                                                           |

| PCENn           | TBA           | O           | enable the               |                               | E. An active-low control signal to<br>between CPU and PC data bus.                                                      |

|                 |               |             | 1. CPU I/0               | O read/write                  | cycle, except co-processor I/O.                                                                                         |

|                 |               |             | 2. CPU m<br>ROM.         | emory read/w                  | rite cycle, except onboard RAM and                                                                                      |

|                 |               |             | 3. Interru               | pt acknowled                  | ge cycle (INTAn active).                                                                                                |

| ENSWAPn         | TBA           | О           |                          |                               | An output to control the output opping data buffer.                                                                     |

| ROMCSn          | TBA           | 0           |                          |                               | An active-low output signal used to to output data onto the data bus.                                                   |

| CROMCSn         | TBA           | О           | CARTRII                  | GE ROM CH                     | IIP SELECT. An active-low output<br>ne cartridge ROM.                                                                   |

| SEL0            | TBA           | I/O         | _                        |                               | 0. One of the two address encoding                                                                                      |

| SEL1            | TBA           | 0           | SELECT                   | FUNCTION<br>address rang      | 1. Together with SELO, encodes the es:                                                                                  |

|                 |               |             | SEL1                     | SEL0                          | FUNCTION                                                                                                                |

|                 |               |             | 0                        | 0                             | Nothing selected                                                                                                        |

|                 |               |             | 0                        | 1                             | A15 - A10 = 0 (I/O)<br>or onboard video RAM                                                                             |

|                 |               |             | 1                        | 0                             | onboard video ROM                                                                                                       |

|                 |               |             | 1                        | 1                             | I/O channel memory but within 1M                                                                                        |

| PWRGOOD         | TBA           | I           |                          | GOOD. An ac<br>power level is | tive-high signal from the power supply stable.                                                                          |

| XD[7:0]         | TBA           | I/O         | XDATA B                  | US. A bidired                 | tional data lines for accessing this                                                                                    |

| REFRQT          | TBA           | Ι           |                          | put signal fr                 | REQUEST. The memory refresh<br>om 8254 Timer channel 1 which comes                                                      |

| MREFn           | TBA           | ľO          |                          | Y REFRESH.<br>cle is going o  | An active-low signal indicating that n.                                                                                 |

|                 |               |             |                          |                               |                                                                                                                         |

| Pin<br>Name            | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                        |

|------------------------|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Interfac        | e (Continue   | ed)         |                                                                                                                                                                                                    |

| ENPARn                 | TBA           | O           | ENABLE MEMORY PARITY. An active-low output signal indicating that onboard RAM is being accessed.                                                                                                   |

| RMRDn                  | TBA           | I/O         | ROM/RAM READ. An active-low signal indicating that onboard ROM or RAM is being read. It is an input representing the signal NPBSYn when accessing 80287 operation code for 80386SX CPU.            |

| Memory Interfa         | ce            |             |                                                                                                                                                                                                    |

| MA[11:1]               | TBA           | I/O         | MEMORY ADDRESS (1-11). During memory cycles, this is a time multiplexed memory address bus for 1M memory type (for 256K memory type MA(10,11) is not used).                                        |

| RAS0n - RAS3n          | TBA           | Ο           | ROW ADDRESS STROBE (0 - 3). These are active-low control signals to the onboard DRAM to strobe the row address.                                                                                    |

| CASH0-3n -<br>CASL0-3n | TBA           | 0           | COLUMN ADDRESS STROBE (High & Low). These are active low control signals to on board DRAM to strobe the column address: CASHn for odd bytes D(15-8) and CASLn for even bytes D(7-0).               |

| MWEn                   | TBA           | 0           | MEMORY WRITE ENABLE. An active-low output used to control memory read/write cycles.                                                                                                                |

| Miscellaneous          |               |             |                                                                                                                                                                                                    |

| CLKIN0                 | TBA           | I           | CLOCK INPUT 0. A 32 MHz TTL clock input with 50% duty cycle. It is used for: the CPU clock generation with CPU running at 8 or 16 MHz, asynchronous bus clock generation, and memory refresh time. |

| CLKIN1                 | TBA           | I           | CLOCK INPUT 1. An optional 20/25/40/50 MHz CMOS clock input with 50% duty cycle. It is used for CPU clock generation with CPU running at 10, 12.5, 20, and 25 MHz.                                 |

| VDD                    | TBA           | I           | POWER: +5 V supply.                                                                                                                                                                                |

| VSS                    | TBA           | Ι           | GROUND:                                                                                                                                                                                            |

Product Overview December 1991

# **OTI-042 Pin Description**

| Pin<br>Name     | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                           |

|-----------------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Interface   |               |             |                                                                                                                                                                       |

| CPUHLDA         | TBA           | I           | CPU HOLD ACKNOWLEDGE. This input signal is active when the CPU releases the control of the bus.                                                                       |

| SD[15:0]        | TBA           | I/O         | CPU DATA BUS (0-15). The CPU data bus.                                                                                                                                |

| System Interfac | ce            |             |                                                                                                                                                                       |

| DENn            | TBA           | I           | DATA BUFFER ENABLE. An active-low input control signal to enable/disable the internal data transceiver between SD(0-15) and PCD(0-15).                                |

| PDLDIRn         | TBA           | 0           | EXTERNAL DATA BUFFER OUTPUT ENABLE. An active-low output control signal to enable output for the external data transceiver between PCD(0-7) and slot data bus(0-7).   |

| PDHDIRn         | TBA           | 0           | EXTERNAL DATA BUFFER OUTPUT ENABLE. An active-low output control signal to enable output for the external data transceiver between PCD(8-15) and slot data bus(8-15). |

| ENSWAPn         | TBA           | I           | ENABLE DATA SWAP. An active-low input signal used for enabling the byte swapping data buffer.                                                                         |

| XD[7:0]         | TBA           | ľO          | XD BUS. Bidirectional data lines to/from the XD bus for accessing onboard peripherals.                                                                                |

| IORDn           | TBA           | I           | I/O READ COMMAND. An active-low input command to instruct the I/O device to drive its data onto the data bus.                                                         |

| IOWRn           | TBA           | I           | I/O WRITE COMMAND. An active-low input command to instruct the I/O device to read the data present on the data bus.                                                   |

| MEMRDn          | TBA           | I           | MEMORY READ COMMAND. An active-low input signal to instruct the memory sub-system to drive its data onto the data bus.                                                |

| MEMWRn          | TBA           | I           | MEMORY WRITE COMMAND. An active-low input signal to instruct the memory sub-system to read the data present on the data bus.                                          |

| REFRQT          | TBA           | 0           | REFRESH REQUEST. Indicates to the arbiter in the OTI-041 that DRAM needs refreshing.                                                                                  |

| CROMCSn         | TBA           | I           | CARTRIDGE ROM CHIP SELECT. An active-low input signal from the OTI-041 indicating cartridge ROM is being accessed.                                                    |

| SEL0            | ТВА           | I/O         | SELECT FUNCTION 0. One of the two address encoding signals. It is output during refresh period as TURBO signal for the OTI-041.                                       |

| Pin<br>Name    | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                            |

|----------------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEL1           | TBA           | I           | SELECT FUNCTION 1. Together with SELO encodes the following address ranges:                                                                                                                            |

|                |               |             | SEL1 SEL0 FUNCTION                                                                                                                                                                                     |

|                |               |             | 0 0 Nothing selected 0 1 A15 - A10 = 0 (I/O) or onboard video RAM 1 0 onboard video ROM 1 I/O channel memory but within 1M and not including onboard video RAM and ROM                                 |

| ROMCSn         | TBA           | I           | ROM CHIP SELECT. An active-low signal used to enable the ROM BIOS to output data on to the data bus.                                                                                                   |

| VDPMSELn       | TBA           | Ο           | VIDEO ROM CHIP SELECT. The chip select signal for on board video ROM.                                                                                                                                  |

| VDSEL/VGAEN    | TBA           | 0           | VIDEO CHIP SELECT/VGA ENABLE. The chip select signal for on board video I/O and RAM address space, special for OAK VGA OTI-037. If IBM compatible VGA is used, this pin becomes VGA enable signal.     |

| 82385SX Suppor | t             |             |                                                                                                                                                                                                        |

| FGA20          | TBA           | 0           | FAST GATE A20                                                                                                                                                                                          |

| FLUSH          | TBA           | O           | FLUSH CACHE. This pin acts as cache flush when EMS mapper is updated.                                                                                                                                  |

| Bus Interface  |               |             |                                                                                                                                                                                                        |

| PCMEMRDn       | TBA           | O           | MEMORY READ COMMAND. An active-low signal to instruct the memory sub-system within 1M on the I/O channel to drive its data onto the data bus.                                                          |

| PCMEMWRn       | TBA           | O           | MEMORY WRITE COMMAND. An active-low signal to instruct the memory sub-system within 1M on the I/O channel to store the data present on the data bus.                                                   |

| PCAEN          | TBA           | O           | ADDRESS ENABLE. A signal to de-gate the I/O devices from the I/O channel and allow DMA transfers to take place.                                                                                        |

| MASTERn        | TBA           | I           | MASTER. This signal is used together with a DRQ line to gain control of the system.                                                                                                                    |

| PCD[15:0]      | TBA           | I/O         | I/O CHANNEL DATA BUS (0-15). The I/O channel data bus. There are two sets of data transceivers that are connected internally, (i.e., between SD(0-7) and PCD(0-7) and between SD(8-15) and PCD(8-15)). |

| SADR[9:0]      | TBA           | I           | ADDRESS BUS. The I/O channel address bus.                                                                                                                                                              |

| PBHEn          | TBA           | I           | BYTE HIGH ENABLE.                                                                                                                                                                                      |

| MREFn          | TBA           | I           | MEMORY REFRESH CYCLE. An active-low signal indicating that the system is in the memory refresh cycle.                                                                                                  |

| OAK TECHNOLOG                    | iY, INC.        |             | December 1991                                                                                                                                                                                                                                                                  |

|----------------------------------|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Name                      | Pin<br>Number   | Pin<br>Type | Description                                                                                                                                                                                                                                                                    |

| Real Time Clock                  |                 |             |                                                                                                                                                                                                                                                                                |

| XTAL1                            | TBA             | I           | XTAL INPUT FOR RTC. The crystal input for the built-in real time clock.                                                                                                                                                                                                        |

| XTAL2                            | TBA             | 0           | XTAL OUTPUT FOR RTC. The crystal output for the built-in real time clock.                                                                                                                                                                                                      |

| VDDRTC                           | TBA             | I           | POWER. Battery power for the built-in Real Time Clock.                                                                                                                                                                                                                         |

| Reset Generatio                  | n               |             |                                                                                                                                                                                                                                                                                |

| PWRGOOD                          | TBA             | I           | POWER GOOD. PWRGOOD comes from the power supply to indicate that power is stable.                                                                                                                                                                                              |

| RESET                            | TBA             | 0           | RESET. An active-high signal synchronized to the CPU clock to reset the system.                                                                                                                                                                                                |

| Timer Counter                    |                 |             |                                                                                                                                                                                                                                                                                |

| SPKOUT                           | TBA             | 0           | SPEAKER DATA OUTPUT. Speaker output data, to be connected to a speaker driver to drive the speaker or beeper.                                                                                                                                                                  |

| Interrupt Contr                  | oller           |             |                                                                                                                                                                                                                                                                                |

| IRQ1, IRQ3-7<br>IRQ9-12, IRQ14-1 | <b>TBA</b><br>5 | I           | INTERRUPT REQUEST INPUTS. asynchronous interrupt request inputs to the internal 8259 controllers.                                                                                                                                                                              |

| INTR                             | TBA             | 0           | INTERRUPT REQUEST. Interrupt request to the CPU and is generated whenever a valid IRQ is received.                                                                                                                                                                             |

| INTAn                            | TBA             | I/O         | INTERRUPT ACKNOWLEDGE. An active-low signal from the OTI-041 indicating that an interrupt acknowledge cycle is in progress. It is output during shutdown/sleep mode to pass the wakeup signal to the OTI-041, either from WAKEUP pin or from wakeup timer or from INTR signal. |

| Keyboard and M                   | louse Inter     | face        |                                                                                                                                                                                                                                                                                |

| SELKBDn                          | TBA             | 0           | SELECT KEYBOARD. An active-low signal indicating that the keyboard controller is selected.                                                                                                                                                                                     |

| Floppy Disk Cor                  | itroller        |             |                                                                                                                                                                                                                                                                                |

| FLPCSn                           | TBA             | Ο           | FLOPPY SELECT. An active-low signal used to select the floppy disk controller. This pin is multiplexed with POFF4n.                                                                                                                                                            |

| DACK2n                           | TBA             | I           | DMA ACKNOWLEDGE. An active-low signal indicating that the floppy disk controller has been granted a DMA cycle.                                                                                                                                                                 |

| Hard Disk Cont                   | roller          |             |                                                                                                                                                                                                                                                                                |

| SELHDK1n                         | ТВА             | O           | HARD DISK SELECT2. When Conner's hard disk is installed, this pin is used as one of the chip select signal decoding addresses 3F6H & 3F7H. This pin is multiplexed with POFF3n.                                                                                                |

| SELHDK0n                         | TBA             | 0           | HARD DISK SELECT1. An active-low signal to select on-board hard disk drive. This pin is multiplexed with POFF2n.                                                                                                                                                               |

| Pin<br>Name    | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                   |

|----------------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Co-processor l | Interface     |             |                                                                                                                                                                                                                                                                                                                                               |

| NPERRn         | TBA           | I           | NUMERICAL PROCESSOR ERROR. An active-low input indicating that an unmasked exception has occurred during numeric instruction execution when the co-processor interrupt is enabled.                                                                                                                                                            |

| NPBSYn         | TBA           | I           | NUMERICAL PROCESSOR BUSY. An active-low input connected directly to the BUSY signal of the co-processor.                                                                                                                                                                                                                                      |

| NPCSn          | TBA           | 0           | NUMERICAL PROCESSOR CHIP SELECT. An active-low output to select the co-processor.                                                                                                                                                                                                                                                             |

| BUSY286n       | TBA           | 0           | BUSY TO CPU. An active-low output connected directly to the BUSY input of the CPU.                                                                                                                                                                                                                                                            |

| NPPREQ         | TBA           | I           | NUMERICAL PROCESSOR REQUEST. An active-high inpindicating that the co-processor is requesting an operand transfer. This pin comes from the PEREQ output of the co-processor.                                                                                                                                                                  |

| CPEREQ         | ТВА           | Ο           | CPU REQUEST. An active-high output to the CPU indicating to the CPU that the co-processor is requesting an operand transfer.                                                                                                                                                                                                                  |

| NMI Generati   | on            |             |                                                                                                                                                                                                                                                                                                                                               |

| IOCKn          | TBA           | I           | I/O CHANNEL CHECK. An active-low input indicating that an I/O channel error condition is detected.                                                                                                                                                                                                                                            |

| PAR0 - PAR1    | TBA           | I/O         | PARITY BIT (0 - 1). The memory parity bits for even and of bytes of the memory bank. Each parity bit is generated and written during the memory write operation. Each is checked and reported on an error to the system at the end of memory read cycle. PAR0 is memory parity bit for even byte, PAR1 is the memory parity bit for odd byte. |

| SYSRAMn        | TBA           | Ι           | ENABLE MEMORY PARITY. An active-low input indicating that onboard RAM is being accessed.                                                                                                                                                                                                                                                      |

| RMRDn          | TBA           | ľO          | ROM/RAM READ. An active-low signal indicating that onboard ROM or RAM is being read. RMRDn is an output equal to NPBSYn signal when I/O address F8H is selected.                                                                                                                                                                              |

| NMI            | TBA           | O           | NON-MASKABLE INTERRUPT. An active-high output to to CPU indicating that an error has occurred in one of the following areas: memory parity error or I/O channel check signal.                                                                                                                                                                 |

| Chip Select Si | ignals        |             |                                                                                                                                                                                                                                                                                                                                               |

| PGIOCS0n       | TBA           | O           | PROGRAMMABLE I/O CHIP SELECT 0. An active-low I/O chip select signal with a programmable I/O address space.                                                                                                                                                                                                                                   |

| COM1CSn        | TBA           | 0           | SERIAL PORT 1 CHIP SELECT. An active-low I/O chip selesignal for the serial port 1. This pin is multiplexed with POFF7n.                                                                                                                                                                                                                      |

| JAK TECHNOLOG     | <del></del>   |             | December 1991                                                                                                                                                                               |

|-------------------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Name       | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                 |

| Chip Select Signs | als (Contin   | ued)        |                                                                                                                                                                                             |

| COM2CSn           | TBA           | 0           | SERIAL PORT 2 CHIP SELECT. An active-low I/O chip select signal for the serial port 2. This pin is multiplexed with POFF8n.                                                                 |

| PRTCSn            | TBA           | 0           | PRINTER PORT CHIP SELECT. An active-low I/O chip select signal for the printer port. This pin is multiplexed with POFF6n.                                                                   |

| PRTOEn            | TBA           | 0           | PRINTER PORT OUTPUT ENABLE. An active-low bidirectional printer port output enable signal. This pin is multiplexed with POFF5n.                                                             |

| Power Control S   | ignals        |             |                                                                                                                                                                                             |

| POFF0n            | TBA           | I/O         | PROGRAMMABLE BIDIRECTIONAL CONTROL SIGNALS. I/O signals to control power to peripherals or as status input to system.                                                                       |

| POFF1n-POFF8n     | TBA           | I/O         | PROGRAMMABLE BIDIRECTIONAL CONTROL SIGNALS. I/O signals to control power to peripherals or as status input to system. These pins are multiplexed with Chip Select signals.                  |

| HDDPWR            | TBA           | 0           | HARD DISK POWER. An active-high output that controls power to the hard disk.                                                                                                                |

| LCDPWR            | TBA           | 0           | LCD BACKLIGHT POWER. An active-high output that controls power to LCD backlight.                                                                                                            |

| LCDMODE0,1        | TBA           | 0           | LCD POWER SAVINGS MODES CONTROL. An active-high output that controls LCD standby mode.                                                                                                      |

| SYSPWR            | TBA           | O           | SYSTEM POWER CONTROL. An active-high output that controls power to the entire system.                                                                                                       |

| Miscellaneous     |               |             |                                                                                                                                                                                             |

| TURBOn            | TBA           | I           | TURBO SPEED SELECTION INPUT. When high (inactive), forces CPUCLK to be 8MHZ. When active low, CPUCLK will be controlled by the speed control register. This pin is multiplexed with POFF1n. |

| Miscellaneous     |               |             |                                                                                                                                                                                             |

| WAKEUPn           | TBA           | I           | WAKEUP PIN. When active high, triggers internal wakeup counter. When the wakeup counter down-counts to zero, the system is resumed from sleep or shutdown mode.                             |

| BADBATTn          | TBA           | I           | BAD BATTERY INPUT. An active-low input indicating that a bad battery status has been detected. This signal level can be readable and it can be optionally enabled to generate NMI.          |

| PWRDOWN           | TBA           | I           | POWER DOWN. An active-high external input to trigger power-down mode.                                                                                                                       |

| CHGCLKn           | TBA           | Ο           | CHANGE SYSTEM SPEED. An active-low output to OTI-041 for changing system clock frequency.                                                                                                   |

| osc               | ТВА           | I           | 14.318 MHz OSCILLATOR OUTPUT. A 14.318 MHz TTL level clock signal to generate the clock for on-chip 8254.                                                                                   |

| Pin<br>Name   | Pin<br>Number | Pin<br>Type | Description |

|---------------|---------------|-------------|-------------|

| Miscellaneous | s (Continued) |             |             |

| GND           | TBA           | I           | GROUND: 0V  |

| VCC           | TBA           | I           | POWER: +5V  |