# LCD DRIVER/CONTROLLER DATABOOK 1986

(408) 737-0204

#### **CONTENTS**

| 1 | PRODUCT LINE-UP                                            | 1  |

|---|------------------------------------------------------------|----|

| 2 | PACKAGING                                                  | 3  |

| 3 | DATA SHEET 1                                               | 1  |

|   | STATIC LCD DRIVER                                          | 3  |

|   | MSM58292GS 5 DIGIT LCD DRIVER                              | 4  |

|   | MSM5219BGS 48 DOT LCD DRIVER 2                             |    |

|   | MSM5221GS 56 DOT LCD DRIVER 3                              |    |

|   | MSM5265GS 160 DOT LCD DRIVER                               | 6  |

|   | DOT MATRIX LCD DRIVER                                      | 19 |

|   | MSM5238GS 32 DOT COMMON DRIVER 5                           | 50 |

|   | MSM5839BGS 40 DOT SEGMENT DRIVER                           | 58 |

|   | MSM5259GS 40 DOT SEGMENT DRIVER 6                          | ;5 |

|   | MSM5260GS 80 DOT COMMON/SEGMENT DRIVER                     | 4  |

|   | MSM5278GS 64 DOT COMMON DRIVER 8                           |    |

|   | MSM5979GS 80 DOT SEGMENT DRIVER                            | 19 |

|   | DOT MATRIX LCD CONTROLLER                                  | 9  |

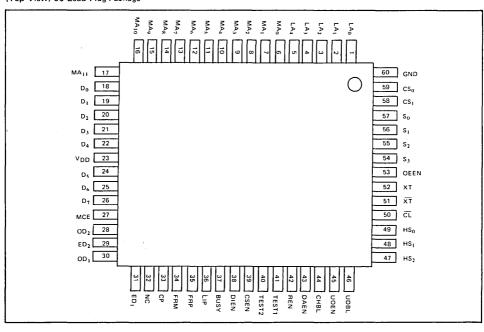

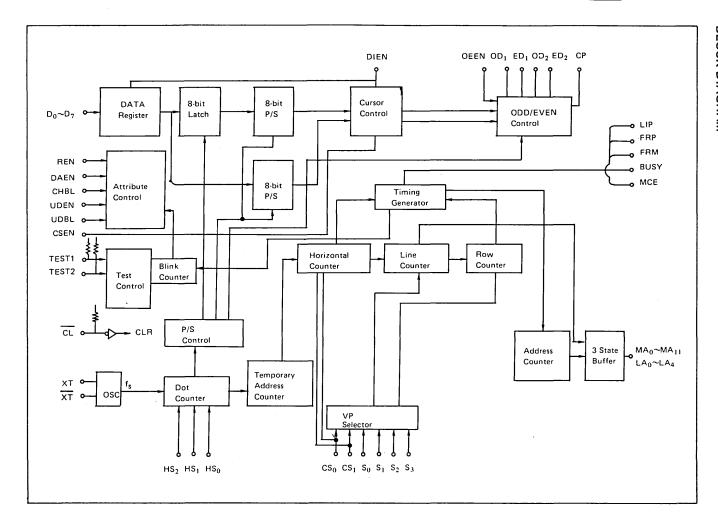

|   | MSM6222B-01GS DOT MATRIX LCD CONTROLLER WITH 16 DOT COMMON |    |

|   | DRIVER AND 40 DOT SEGMENT DRIVER10                         | 10 |

|   | MSM6240GS DOT MATRIX LCD CONTROLLER                        |    |

|   | MSM6255GS DOT MATRIX LCD CONTROLLER16                      | _  |

|   | MSM6265GS DOT MATRIX LCD CONTROLLER                        |    |

OKI makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

OKI retains the right to make changes to these specifications at any time, without notice.

# PRODUCT LINE-UP

## PRODUCT LINE-UP

| APPLICATION              | TYPE NO         | FUNCTION                     | оит        | PUT<br>SEGMENT | DUTY         | PACKAGE  | REMARKS                                                      |

|--------------------------|-----------------|------------------------------|------------|----------------|--------------|----------|--------------------------------------------------------------|

|                          | MSM58292        | static driver                | 5 digit (7 | segment)       | 1/1          | 56 FLT.  | ·                                                            |

| STATIC LCD               | MSM5219B        | static driver                | 48         | dot            | 1/1-         | 60 FLT.  |                                                              |

| DRIVER                   | MSM5221         | static driver                | 56         | dot            | 1/1          | 80 FLT.  |                                                              |

|                          | MSM5265         | static driver                | 160        | dot            | 1/1 or 1/2   | 100 FLT. |                                                              |

|                          | MSM5238         | COMMON<br>DRIVER             | 32         | -              | 1/32 — 1/128 | 44 FLT.  |                                                              |

|                          | MSM5839B        | SEGMENT<br>DRIVER            |            | 40             | 1/8 — 1/128  | 56 FLT.  |                                                              |

|                          | MSM5259         | SEGMENT<br>DRIVER            | _          | 40             | 1/1 — 1/16   | 56 FLT.  | use with<br>MSM6222B-01                                      |

| DOT MATRIX<br>LCD DRIVER | MSM5260         | COMMON/<br>SEGMENT<br>DRIVER | 80         | 80             | 1/1 — 1/128  | 100 FLT. | COMMON/<br>SEGMENT<br>selectable                             |

|                          | MSM5278         | COMMON<br>DRIVER             | 64         | -              | 1/8 — 1/128  | 80 FLT.  |                                                              |

|                          | MSM5279         | SEGMENT<br>DRIVER            | _          | 80             | 1/8 — 1/128  | 100 FLT. |                                                              |

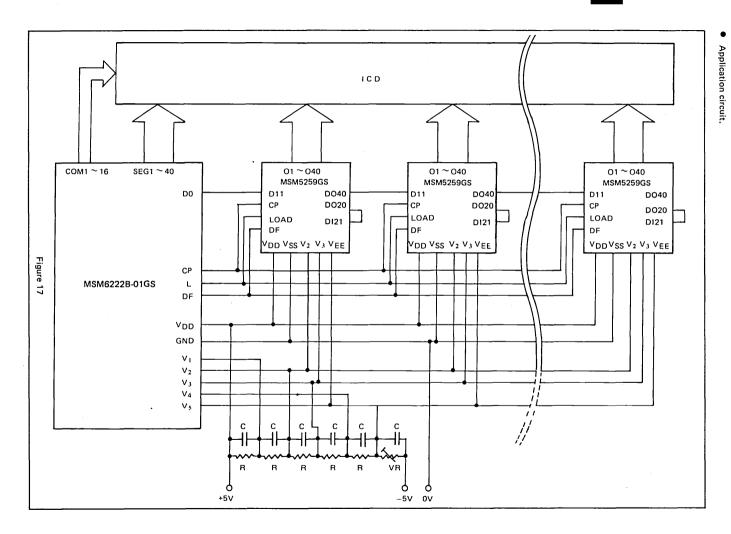

|                          | MSM6222B<br>-01 | DRIVER/<br>CON-<br>TROLLER   | 16         | 40             | 1/8 — 1/16   | 80 FLT.  | with character<br>generator<br>ROM                           |

| DOT MATRIX               | MSM6240         | CON-<br>TROLLER              | _          | _              | 1/32 — 1/144 | 60 FLT.  |                                                              |

| CONTROLLER               | MSM6255         | CON-<br>TROLLER              | _          | _              | 1/2 – 1/256  | 80 FLT.  | 512K dot                                                     |

|                          | MSM6265         | CON-<br>TROLLER              | _          | _              | 1/100 x 2    | 80 FLT.  | 512K dot<br>software<br>compatible<br>with CRT<br>Controller |

Note: 1. MSM5259 and MSM5260 can be used as static display dot drives like MSM5219B and so forth.

The duty of LCD module is determined by the performance of drivers and the material of LCD panel.So, to select suitable LCD driver for superior display, it is necessary to study the material of the LCD panel.

|                | PRODUCT     | PLASTIC FLAT<br>PACKAGE<br>(No. of Pins) | GS-K | GS-L | GS-L2 |

|----------------|-------------|------------------------------------------|------|------|-------|

|                | MSM58292    | 56 (small)                               | 0    |      |       |

| STATIC LCD     | MSM5219B    | 60                                       | 0    |      |       |

| DRIVER         | MSM5221     | 80                                       | 0    |      |       |

| ,              | MSM5265     | 100                                      | 0    |      |       |

|                | MSM5238     | 44                                       | 0    |      | 0     |

|                | MSM5839B    | 56 (small)                               | 0    |      | 0     |

| DOT MATRIX     | MSM5259     | 56 (small)                               | 0    |      | 0     |

| LCD DRIVER     | MSM5260     | 100                                      | 0    | 0    |       |

|                | MSM5278     | 80                                       | 0    |      |       |

|                | MSM5279     | 100                                      | 0    |      |       |

|                | MSM6222B-01 | 80                                       |      | 0    |       |

| DOT MATRIX     | MSM6240     | 60                                       | 0    |      |       |

| LCD CONTROLLER | MSM6255     | 80                                       | 0    |      |       |

|                | MSM6265     | 80                                       | 0    |      |       |

Note: Model names suffixed by GS denote plastic mold flat package, while -K, -L or -L2 denote the direction of the lead bent.

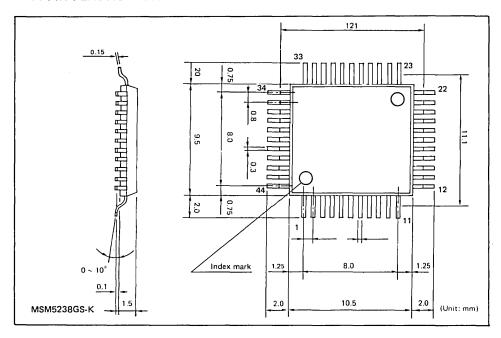

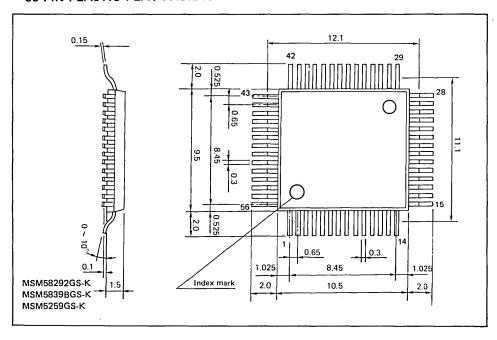

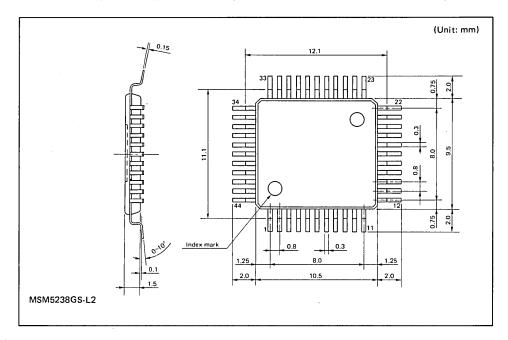

#### • 44 PIN PLASTIC FLAT PACKAGE

#### • 56 PIN PLASTIC FLAT PACKAGE

#### • 60 PIN PLASTIC FLAT PACKAGE

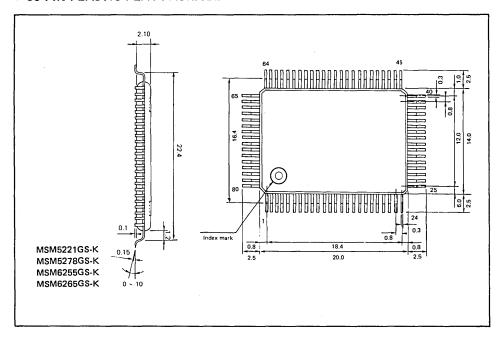

#### • 80 PIN PLASTIC FLAT PACKAGE

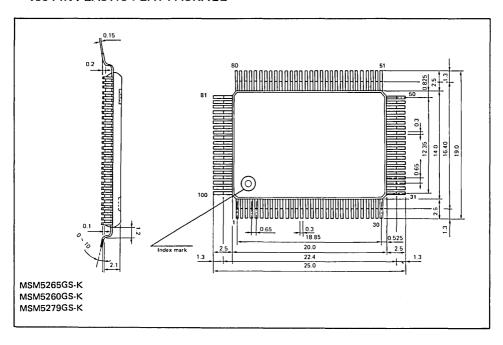

#### • 100 PIN PLASTIC FLAT PACKAGE

#### • 44 PIN PLASTIC FLAT PACKAGE (LEAD BENT OPPOSITE DIRECTION)

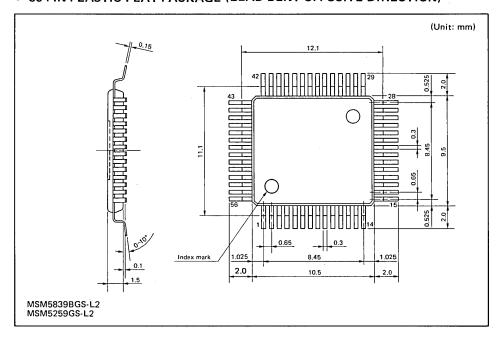

#### • 56 PIN PLASTIC FLAT PACKAGE (LEAD BENT OPPOSITE DIRECTION)

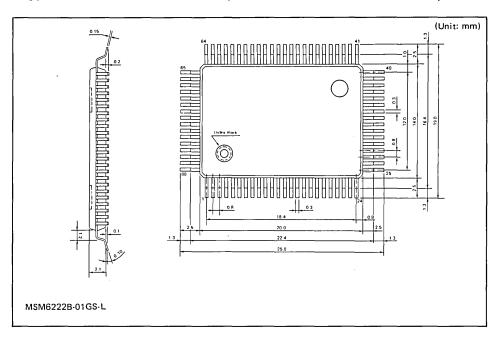

#### • 80 PIN PLASTIC FLAT PACKAGE (LEAD BENT OPPOSITE DIRECTION)

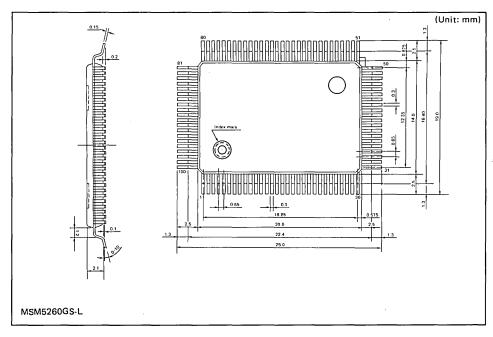

#### • 100 PIN PLASTIC FLAT PACKAGE (LEAD BENT OPPOSITE DIRECTION)

# STATIC LCD DRIVER

#### **GENERAL DESCRIPTION**

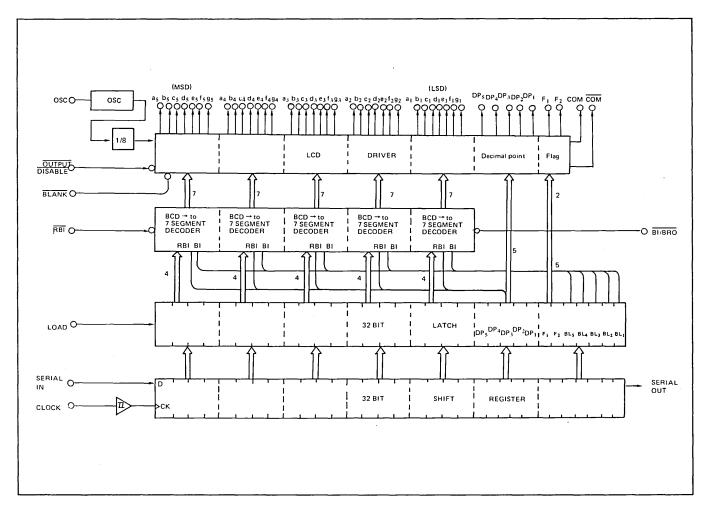

The OKI MSM58292GS is a 7-segment static LCD driver LSI which is fabricated by low power CMOS metal gate technology. This LSI consists of 32-bit shift register, 32-bit latch, 5 sets of 7-segment decoder and LCD drivers.

It receives the serial display data from the microcomputer etc, converts it to a parallel data, then output to the 7-segment LCD panel.

The input code for each digit is a 4-bot binary code. The input codes are decoded into digits 0  $\sim$  9 and alphabetic letters A  $\sim$  F, to display hexadecimal numbers. The expansion of display can be easily made by using another MSM58292GS in cascade connection.

The MSM58292GS can directly drive the LCD panel, as the AC driving circuit is integrated on the chip.

#### **FEATURES**

- 5 digit 7-segment LCD display

- Serial input from the microcomputer etc.

- Expansion of display by cascade connection

- Supply voltage: 3 ~ 7 V

- 56 pin plastic flat package

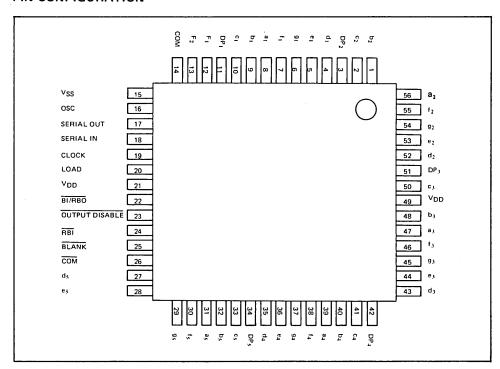

#### PIN CONFIGURATION

#### **ABSOLUTE MAXIMUM RATINGS**

| Item                | Symbol          | Condition           | Limits                 | Unit |

|---------------------|-----------------|---------------------|------------------------|------|

| Supply voltage      | V <sub>DD</sub> | $T_a = 25^{\circ}C$ | <b>-0.3 ∼ 7</b>        | V    |

| Input voltage       | V <sub>I</sub>  | 'a - 25 C           | -0.3 ∼ V <sub>DD</sub> | V    |

| Storage temperature | Tstg            |                     | _55 ~+150              | °c   |

#### **OPERATING RANGE**

| Item                  |            | Symbol          | Condition | Limits    | Unit |  |

|-----------------------|------------|-----------------|-----------|-----------|------|--|

| Supply voltage        |            | V <sub>DD</sub> | _         | 3~7       | V    |  |

| Operating temperature |            | TOP             | _         | -30 ∼ +85 | °c   |  |

|                       | BI/RBO     | N               | MOS load  | 1         | _    |  |

| Fan out               | SEDIAL OUT |                 | MOS load  | 40        | 1 -  |  |

|                       | SERIAL OUT | N               | TTL load  | 1         | _    |  |

#### **DC CHARACTERISTICS**

$(V_{DD} = 5V \pm 5\%, T_a = -30 \sim +85^{\circ}C)$

| Item                             | Symbol                           | Condition                                              | MIN          | TYP | MAX          | Unit |

|----------------------------------|----------------------------------|--------------------------------------------------------|--------------|-----|--------------|------|

| High Input voltage               | ViH                              | _                                                      | 3.6          | _   | _            | V    |

| Low Input voltage                | VIL                              | _                                                      |              | -   | 8.0          | V    |

| High Output voltage <sup>1</sup> | Voн                              | Ι <sub>Ο</sub> = –5 μΑ                                 | 4.95         | _   | _            | V    |

| Low Output voltage <sup>1</sup>  | VOL                              | Ι <sub>Ο</sub> = 5 μΑ                                  |              | _   | 0.05         | V    |

| High Output voltage <sup>2</sup> | Voн                              | Ι <sub>Ο</sub> = -40 μΑ                                | 4.2          | _   | -            | ٧    |

| Low Output voltage <sup>2</sup>  | VOL                              | I <sub>O</sub> = 1.6mA                                 |              | _   | 0.4          | V    |

| High Output voltage <sup>3</sup> | Voн                              | Ι <sub>Ο</sub> = -500 μΑ                               | 4.5          | _   | _            | ٧    |

| Low Output voltage <sup>3</sup>  | VOL                              | Ι <sub>Ο</sub> = 500 μΑ                                |              | _   | 0.5          | ٧    |

| High Output voltage <sup>4</sup> | Voн                              | I <sub>O</sub> = -250 μA                               | 4.5          | _   | -            | ٧    |

| Low Output voltage <sup>4</sup>  | VOL                              | Ι <sub>Ο</sub> = 250 μΑ                                |              |     | 0.5          | ٧    |

| Input current <sup>5</sup>       | IIH/IIL                          | $V_I = V_{DD}/V_I = 0V$                                | _            | _   | 1/1          | μΑ   |

| Output current <sup>1</sup>      | I <sub>OH</sub> /I <sub>OL</sub> | V <sub>O</sub> = 0V /V <sub>O</sub> = V <sub>DD</sub>  | -0.2/<br>0.2 | -   | -            | mA   |

| Output current <sup>2</sup>      | I <sub>OH</sub> /I <sub>OL</sub> | V <sub>O</sub> = 2.5V/V <sub>O</sub> = 0.4V            | -0.2/<br>1.6 | _   | -            | mA   |

| BI/RBO short-circuit current     | IOH/IOL                          | V <sub>O</sub> = 0 V /V <sub>O</sub> = V <sub>DD</sub> | -10/<br>10   | _   | -500/<br>500 | μΑ   |

| Dynamic current consumption      | IDD                              | f(OSC) = 360Hz no load                                 | -            | _   | 500          | μΑ   |

Note 1: Applied to the output pins excluding the SERIAL OUT, BI/RBO, COM and COM Pins.

Note 2: Applied to the SERIAL OUT pin.

Note 3: Applied to the COM pin. Note 4: Applied to the COM pin.

Note 5: Applied to the input pins excluding the OSC pin.

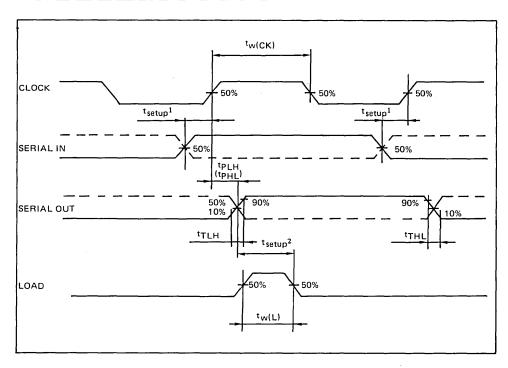

#### **SWITCHING CHARACTERISTICS**

$(V_{DD} = 5V, T_a = 25^{\circ}C, CL = 15pF)$

| ltem                                                          | Symbol                          | Condition | MIN | TYP | MAX  | Unit |

|---------------------------------------------------------------|---------------------------------|-----------|-----|-----|------|------|

| Propagation delay time<br>(for a shift in the shift register) | tPHL<br>tPLH                    | -         | _   | -   | 1000 | nS   |

| SERIAL OUT rise/fall time                                     | tTHL<br>tTLH                    | -         | -   | -   | 300  | nS   |

| Maximum clock frequency                                       | f(CK) max                       | _         | 1   | _   |      | MHz  |

| Minimum clock pulse width                                     | tw(CK)                          | _         | _   | -   | 500  | nS   |

| Minimum load pulse width                                      | tw(L)                           | _         |     | -   | 500  | nS   |

| Data setup time SERIAL IN → CLOCK                             | t <sub>setup</sub> 1            |           | -   | -   | 250  | nS   |

| Data setup time SERIAL OUT → LOAD                             | t <sub>setup</sub> <sup>2</sup> | _         | -   | -   | 500  | nS   |

#### **FUNCTION TABLE**

|                   |     |          | SEGMENT OUT (Note 1) |   |    |    |    |   |   |            |

|-------------------|-----|----------|----------------------|---|----|----|----|---|---|------------|

| Hexadecimal digit | RBI | BI/RBO   | a                    | b | С  | d  | е  | f | g | Display    |

| *                 | *   | L        | L                    | L | L. | L  | L. | L | L | (Note 3)   |

| 0                 | *   | (Note 2) | L                    | L | L  | L  | L  | L | L | (Note 4)   |

| 0                 | *   | Н        | Н                    | Н | Н  | Н  | Н  | Н | L |            |

| 1                 | *   | , н      | L                    | Н | Н  | L  | L  | L | L | <i>'</i>   |

| 2                 | *   | Н        | Н                    | Н | L  | Н  | Н  | L | Н | ĨIJĨĨ      |

| 3                 | *   | Н        | Н                    | Н | Н  | Н  | L  | L | Н |            |

| 4                 | *   | Н        | L                    | Н | Н  | Ľ. | L  | Н | Н | '-;        |

| 5                 | *   | Н        | Н                    | L | Н  | Н  | L  | Н | Н | ŪŪŪ        |

| 6                 | *   | Н        | Н                    | L | Н  | Н  | Н  | Н | Н | 5          |

| 7                 | *   | Н        | Н                    | Н | Н  | L  | L  | L | L | 7          |

| 8                 | *   | н        | Н                    | Н | Н  | Н  | Н  | Н | Н |            |

| 9                 | *   | Н        | Н                    | Н | Н  | Н  | L  | Н | Н |            |

| A                 | *   | Н        | Н                    | Н | Н  | L  | Н  | Н | Н | 17         |

| В                 | *   | Н        | L                    | L | Н  | Н  | Н  | Н | Н | ()         |

| С                 | *   | Н        | Н                    | L | L  | Н  | Н  | Н | L | 1          |

| D                 | *   | Н        | L.                   | Н | Н  | Н  | Н  | L | Н |            |

| Е                 | *   | Н        | Н                    | L | L  | Н  | Н  | Н | Н | Ξ          |

| F                 | *   | Н        | Н                    | L | L. | L  | Н  | Н | Н | Ţ <u>.</u> |

Note 1: The H indicates that the segment is displayed, and the L indicates that the segment is not displayed. The H is an antiphase output of the COM output, and the L is an in-phase output of the COM output.

Note 2: The RI/RBO pin goes to low level only when the RBI pin is at a low level and all the digit are 0 (the display is blank).

If the BI/RBO pin is forcibly turned to high level, 0 at LSD is displayed.

Note 3: If the BI/RBO pin is forcibly turned to low level, the LSD is made blank.

Note 4: If the RBI pin is turned to low level, the display is placed in the leading zero blanking status, in which the contiguous 0s preceding the MSD are made blank.

#### **FUNCTIONAL DESCRIPTION**

#### SERIAL IN

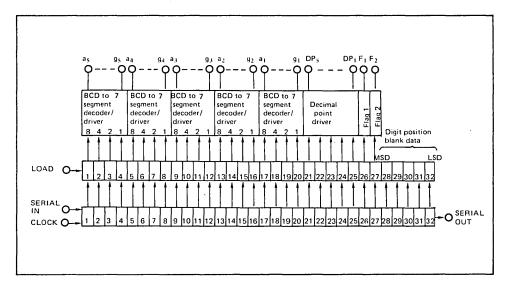

The SERIAL IN pin is a shift register data input pin. The display data are input to this pin synchronized with the clock pulses. The data are input

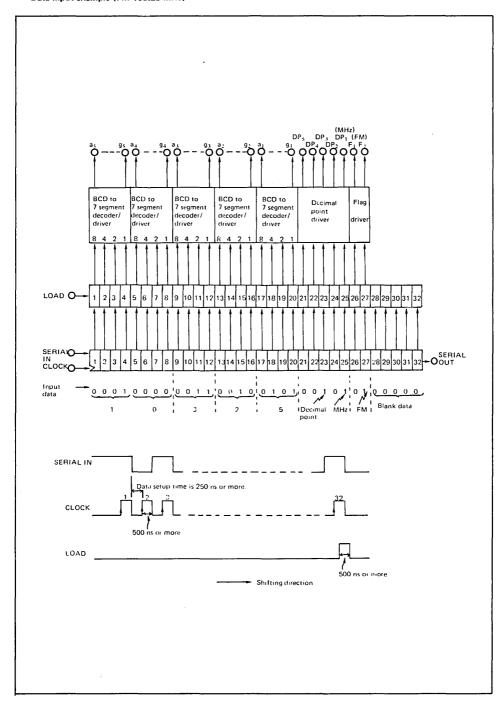

< Data input procedure >

in the order of blank data, flag data, decimal point data, then numeric data (beginning with the LSB) (positive logic).

#### SERIAL OUT

The SERIAL OUT pin is a shift register serial output pin. The data input to the SERIAL IN pin is output from this pin synchronised with the clock pulses, with a delay of the total bit count of the shift register (32 bits). This pin is used for extension of digit display capacity.

#### CLOCK

The CLOCK pin is a synchronizing pulse input pin used for data input to the shift register or data output from the shift register. The data is shifted at the rising edge (low to high) of each clock pulse. A Schmitt trigger circuit is employed as the CLOCK input circuit (the hysteresis is approximately 0.5V).

#### LOAD

The LOAD pin is an input pin for latching the shift register contents. When this pin is at high level, the shift register contents are transferred to the decoders, and when this pin is at low level, the last data to be transferred from the shift register when this pin was at high level is held, so that the display contents are not changed with the change of the shift register contents.

#### ● RBI

The  $\overline{\text{RBI}}$  PIN is an input pin for suppressing the display of leading 0s. When this pin is at high level, the leading 0s, if any, are displayed; when this pin is at a low level, contiguous 0s preceding the MSD are not displayed. The  $\overline{\text{RBI}}$  pin is connected to the decoder circuit for the MSD.

Note: The DP<sub>1</sub> through DP<sub>5</sub> are not made blank.

#### BI/RBO

The  $\overline{\text{BI/RBO}}$  pin is used for both input and output. As an input pin, the input level can forcibly be set to low regardless of the output level, since the output resistance is treat.

#### 1 For use as an output pin RBO

When the  $\overline{RBI}$  pin is turned to low level, if all the digits are 0s, the display is made blank and the  $\overline{RBO}$  pin is turned to low level. If the  $\overline{RBI}$  pin is at high level or a number including some significant digits is displayed, the  $\overline{RBO}$  pin is turned to high level. If two MSM58292GS chips are connected for extension of the digit display capacity, the  $\overline{RBO}$  pin of the first chip is connected to the  $\overline{RBI}$  pin of the second chip, which connects to the MSD of the second chip, so that all the continguous 0s preceding the MSD are made blank.

#### 2 For use as an input pin BI

The  $\overline{Bl}$  pin is connected to the decoder circuit for the LSD. Therefore, if this pin is turned to low level, only the LSD digit is made blank. Since this pin is also used as an output pin  $\overline{ROB}$ , some current indicated in the rating flows when this pin is set to low level. level.

The Bi pin may be open when not used.

Note: The DP<sub>1</sub> through DP<sub>5</sub> are not made blank.

#### • SEGMENT OUT (a<sub>1</sub>-g<sub>5</sub>, DP<sub>1</sub>-DP<sub>5</sub>, F<sub>1</sub>, F<sub>2</sub>)

The SEGMENT OUT pins are output pins for driving the seven segments of digits  $(a_1 - g_5)$ ,

decimal points  $(DP_1-DP_5)$ , and flags  $(F_1 \text{ and } F_2)$  on the display device.

The seven segment outputs (a-g) for each digit are used to display a digit 0-9 or an alphabetic letter A-F.

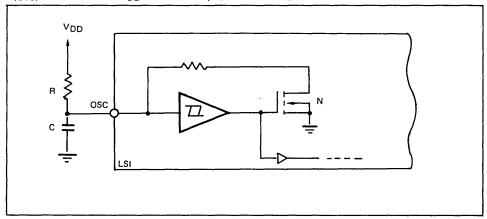

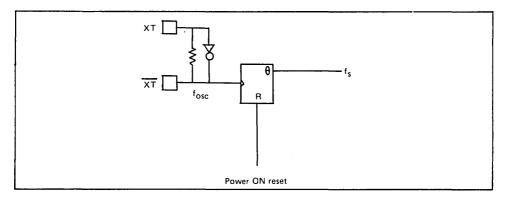

#### osc

The OSC pin is an input pin for a signal generator circuit which outputs AC signals required for driving a LCD panel. The oscillator starts to generate AC signals only by connecting a resistor and a capacitor to the OSC pin as shown in the figure below.

f(OSC) = 360 Hz when the  $V_{DD} = 5V$ ,  $C = 0.068 \mu F$ , and  $R = 100 k \Omega$

#### ● COM, COM

The COM pin is an output pin for sending an antiphase signal of the seven segment outputs required for AC-driving the LCD panel. The COM output drives the COMMON pin on the LCD panel.

The  $\overline{\text{COM}}$  pin is an output pin for sending an inphase signal of the seven segment outputs (antiphase of the COM pin). This pin is not necessary in general display.

Both the COM and  $\overline{\text{COM}}$  pins output square waves whose frequency is one eighth of the oscillator output appearing at the OSC pin (with a duty factor of 50%).

#### OUTPUT DISABLE

The OUTPUT DISABLE pin is an input pin for control of the COM pin. Setting this pin to high level places the COM pin in the normal status (the COM pin is used as an ordinary output pin), and setting this pin to low level makes the COM pin impedance high, so that the COM pin can be used as an input pin.

When two MSM58292GS chips are interconnected in a cascade, the OUTPUT DISABLE pin of the second chip is set to low level and the COM pin is used as an input pin.

#### • BLANK

The BLANK pin is an input pin for making the display blank. Setting this pin to high level makes normal display, and setting this pin to low level makes the entire display blank.

#### Blanking a specific digit position

Any given digit position of the 5 digit display can be made blank by setting the MSM58292GS to ON. A specific digit position can be made blank by setting a bit of the shift register bits 28-32, as shown in the table below.

| Shift register bit setting | Digit position which is made blank             |

|----------------------------|------------------------------------------------|

| Set bit 28 to 1            | Digit position with segments $a_5 - g_5$ (MSD) |

| Set bit 29 to 1            | Digit position with segments $a_4 - g_4$       |

| Set bit 30 to 1            | Digit position with segments $a_3 - g_3$       |

| Set bit 31 to 1            | Digit position with segments $a_2 - g_2$       |

| Set bit 32 to 1            | Digit position with segments $a_1 - g_1$ (LSD) |

#### Decimal points

A digit position for which a decimal point has been specified is not subject to zero blanking even though that digit position contains the value 0. A decimal point can be used as a flag by setting the blank bit corresponding to that digit position to 1 to suppress the a-g segment display of that digit position (when the  $\overline{\text{RBI}}$  pin is at low level).

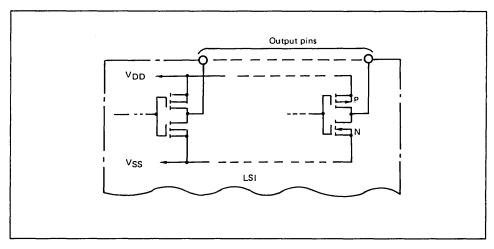

#### Output circuit

Each output pin consists of a CMOS FET, and the BI/RBO pin and SERIAL OUT pin output signals at high or low level.

The output pins for display (for segments, decimal points, and flags) output pulse signals which are antiphase of the COM pin output when displaying, and output pulse signals which are in-phase of the COM pin output when not displaying. The output pins for display can directly drive the LCD panel.

#### Application circuit

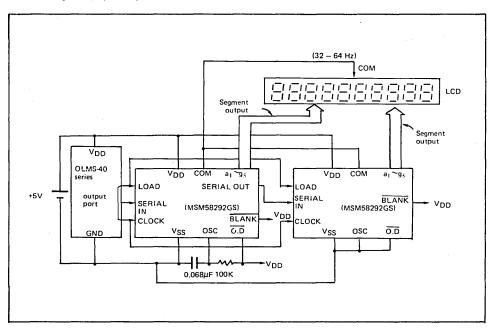

I. 10 digit display (using two MSM58292GSs, cascade connection)

Note: O.D is the abbreviation of OUTPUT DISABLE.

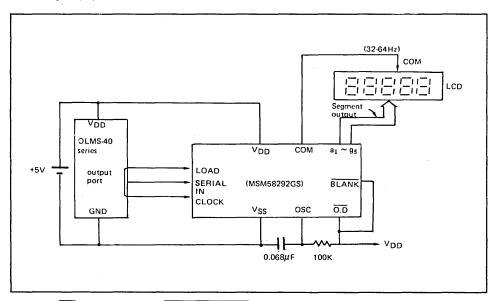

#### II. 5 digit display

Note: O.D the abbreviation of OUTPUT DISABLE.

#### Data input example (FM 103.25 MHz)

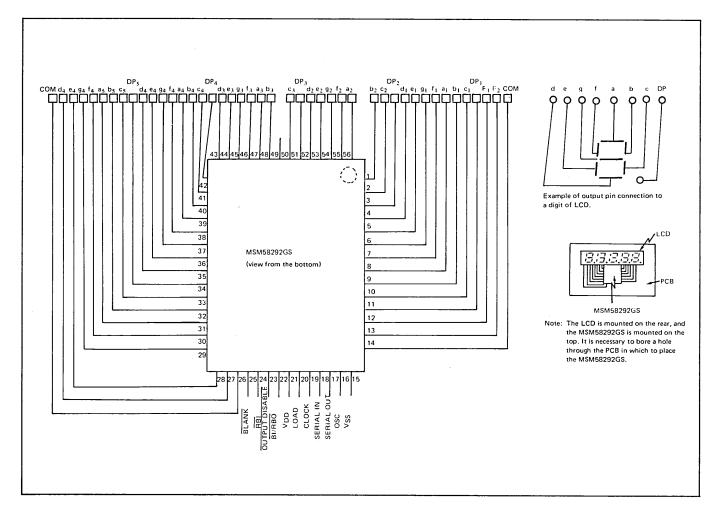

# Example of interconnection with LCD

STATIC LCD DRIVER · MSM58292GS

# **OKI** semiconductor

# **MSM5219BGS**

**48-DOT STATIC LCD DRIVER**

#### **GENERAL DESCRIPTION**

The OKI MSM5219BGS is a 48 dot static LCD driver which is fabricated by low power CMOS metal gate technology. This LSI consists of 48-bit shift register, 48-bit latch and 48-bit LCD driver. The display data, which was input to the 48-bit shift register, is shifted to the 48-bit latch by the LOAD signal. Then the data is output to the LCD panel through the 48-bit LCD driver.

#### **FEATURES**

- 48 dots static LCD driving capability

- Simple interface with microcomputer chip (controlled by three input signals)

- Bit-to-bit correspondence between the input and the output

- Cascade connection capability

- LCD driving AC frequency is directly input externally

- Applicable as an output expander

- Supply voltage: 3 ~ 7V

- 60 pin plastic flat package (bent lead)

#### PIN CONFIGURATION

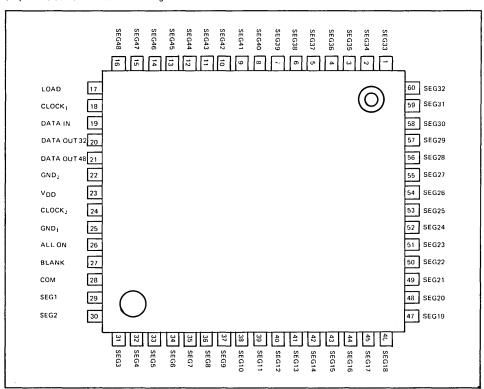

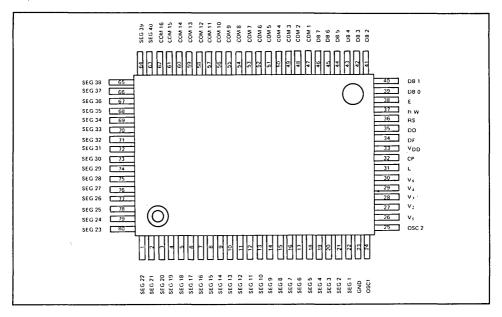

(Top View) 80 Lead Plastic Flat Package

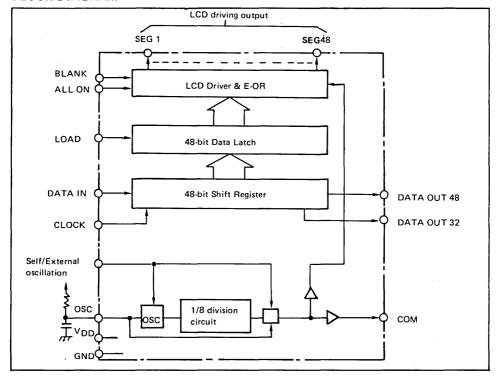

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Item                | Symbol                            | Condition             | Limits                           | Unit |

|---------------------|-----------------------------------|-----------------------|----------------------------------|------|

| Supply voltage      | V <sub>DD</sub> – V <sub>SS</sub> | T <sub>a</sub> = 25°C | -0.3 ∼+7                         | V    |

| Input voltage       | V <sub>I</sub>                    | T <sub>a</sub> = 25°C | $V_{SS} - 0.3 \sim V_{DD} + 0.3$ | V    |

| Storage temperature | T <sub>stg</sub>                  |                       | -55 ∼+150                        | °c   |

#### **OPERATING RANGE**

| Item                  | Symbol                                | Condition                | Limits           | Unit |

|-----------------------|---------------------------------------|--------------------------|------------------|------|

| C                     | , , , , , , , , , , , , , , , , , , , | Self-Oscillation circuit | 4~7              | ٧    |

| Supply voltage        | V <sub>DD</sub> – V <sub>SS</sub>     | External oscillation     | 3~7              | V    |

| Operating temperature | Тор                                   | -                        | <b>−40 ~ +85</b> | °c   |

#### **DC CHARACTERISTICS**

$(V_{DD} - V_{SS} = 5V, T_a = -40 \sim +85^{\circ}C)$

| Item                                | Symbol                             | Condition                                                 | MIN          | TYP | MAX  | Unit     |

|-------------------------------------|------------------------------------|-----------------------------------------------------------|--------------|-----|------|----------|

| "H" Input voltage*1                 | VIH                                | <del></del>                                               | 3.6          | _   | _    | <b>V</b> |

| "L" Input voltage*1                 | VIL                                | _                                                         | _            | _   | 1.0  | ٧        |

| Input leakage current*1             | IIH/IIL                            | V <sub>1</sub> = 5V/V <sub>1</sub> = 0V                   | -            | -   | 1/-1 | μΑ       |

| SEG "H" Output voltage              | Vons                               | Ι <sub>Ο</sub> =30μΑ                                      | 4.8          | -   | -    | <b>V</b> |

| SEG "L" Output voltage              | VOLS                               | ΙΟ = 30μΑ                                                 | 1            | -   | 0.2  | >        |

| COM "H" Output voltage              | VOHC                               | I <sub>O</sub> = -150μA                                   | 4.8          | -   | ı    | <b>V</b> |

| COM "L" Output voltage              | Volc                               | I <sub>O</sub> = 150μΑ                                    | -            | -   | 0.2  | ٧        |

| SEG Output current 1                | IOHS1/IOLS1                        | V <sub>OH</sub> = 4.5V/V <sub>OL</sub> = 0.5V             | -100/<br>100 | _   | _    | μΑ       |

| SEG Output current 2                | IOHS2/IOLS2                        | V <sub>OH</sub> = 1V/V <sub>OL</sub> = 4V                 | -400/<br>400 | _   | -    | μΑ       |

| COM Output current 1                | IOHC1/IOLC1                        | V <sub>OH</sub> = 4.5V/V <sub>OL</sub> = 0.5V             | -500/<br>500 | -   | -    | μΑ       |

| COM Output current 2                | OHC2/OLC2                          | V <sub>OH</sub> = 1V/V <sub>OL</sub> = 4V                 | -2/2         | _   | 1    | mΑ       |

| "H" Output voltage*2                | Voн                                | Ι <sub>Ο</sub> = -40μΑ                                    | 4.2          |     | -    | >        |

| "L" Output voltage*2                | VOL                                | I <sub>O</sub> = 1.6mA                                    | _            | _   | 0.4  | V        |

| Output current*2                    | IOH/IOL                            | V <sub>O</sub> = 2.5V/V <sub>O</sub> = 0.4V               | -0.2/<br>1.6 | -   | -    | ٧        |

| 01.1.1.1.1.11                       |                                    | *3                                                        | 5            | -   | -    |          |

| Clock pulse width                   | twφ                                | *4                                                        | 0.5          | -   | -    | μS       |

| Many alpels mules fraguency         | £ 1                                | *3                                                        | 0.1          | -   | _    | MHz      |

| Max. clock pulse frequency          | føMAX                              | *4                                                        | 1            | 1   | -    | IVITIZ   |

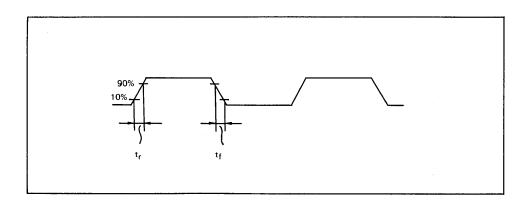

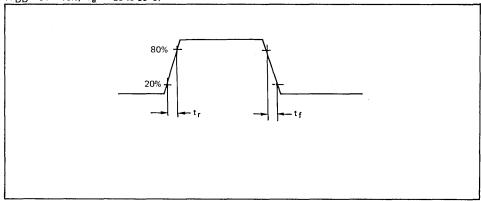

| Input signal rising/falling time    | t <sub>r</sub> φ, t <sub>f</sub> φ | *5                                                        | -            | -   | 5    | μS       |

| Static current consumption          | I <sub>DD1</sub>                   |                                                           | _            | _   | 100  | μΑ       |

| Active current consumption          | I <sub>DD2</sub>                   | No load when ROSC = 150 k $\Omega$ , COSC = 0.015 $\mu$ F | _            | _   | 2    | mA       |

| COM Frequency<br>(Self oscillation) | fсом                               | No load when V <sub>DD</sub> = 5V                         | 25           | -   | 300  | Hz       |

<sup>\*1:</sup> Applicable to all terminals except OSC. This condition is applied to OSC in the external oscillation mode.

<sup>\*2:</sup> Applicable to DATA OUT 32, DATA OUT 48.

<sup>\*3:</sup> Applicable to OSC.

<sup>\*4:</sup> Applicable to CLOCK.

<sup>\*5:</sup> Applicable to all terminals except OSC terminal.

#### **FUNCTIONAL DESCRIPTION**

#### Operational Description

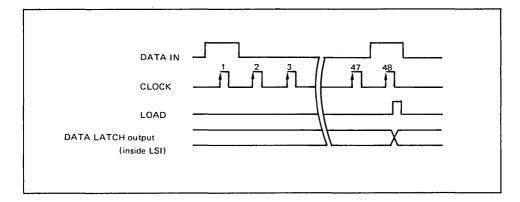

The display data is input to the shift register by the DATA IN signal and CLOCK signal. It is transferred

to the 48-bit latch by the LOAD signal and it is output to the LCD panel through 48-bit LCD driver.

#### ● CLOCK<sub>2</sub>

The clock, which is used to generate the COM signal and the LCD driving signal, is input to this pin.

#### DATA IN CLOCK:

DATA IN is a data input pin which enables the LCD to display when DATA IN pin is at high level. The 48-bit shift register is shifted at the rising edge of the CLOCK signal. Initially, the first bit of the shift register contains the current logic level of the DATA IN pin, and the bit N (N = 2  $\sim$  48) contains the data which was in bit N - 1 (N = 2  $\sim$ 48) before the start of the operation. The data which was in bit 48 before the operation start is considered invalid

#### LOAD

The data in the 48-bit shift register is shifted to the 48-bit latch when the LOAD pin set at high level, while the last data which was transferred to the latch when the LOAD pin was set at high level is constantly output when the LOAD pin is set at low level.

#### ALL SEG ON

When this pin is set at high level, all segments display turn on. This pin has the priority to the BLANK pin described as below.

#### BLANK

When this pin is set at high level, all segments display turn off. The ALL SEG ON pin has the priority over this pin.

#### SEG1 ~ SEG48

LCD driving output pins. The reversed phase of the COM signal, which is used to display the data, is output from these pins when SEG1  $\sim$  SEG48 are set at high level, while there is no display on the LCD when these pins are set at low level. The data which was input from the DATA IN pin is output from these pins to the LCD panel. The SEG N pin corresponds to the bit N of the shift register.

#### COM

Output terminal for the LCD. It is connected to the common side of the LCD.

#### DATA OUT 32, DATA OUT 48

Output pin of the shift register. It is used when the MSM5219BGS is connected in a series (cascade connection). It is connected to next MSM5219BGS's DATA IN terminal.

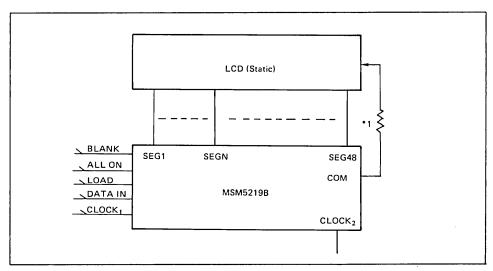

#### APPLICATION CIRCUIT

#### Single MSM5219BGS

\*1: When this IC is used under a strong external noise or large-capacity LCD load, this resistor prevents latch-up to be caused by a low output impedance of the COM pin.

The resistance is about  $100\Omega$ .

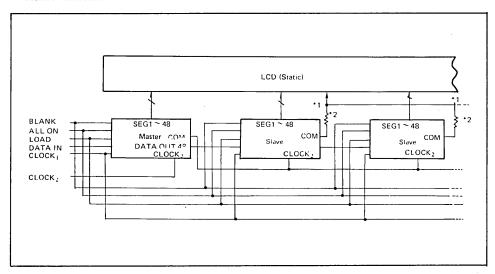

#### Cascade connection

- \*1: The COM pin of the slave MSM5219BGS can be WIRED OR.

- \*2: When this IC is used under a strong external noise or large-capacity LCD load, this resistor prevents latch-up to be caused by a low output impedance of the COM pin. The resistance is about  $100\Omega$ .

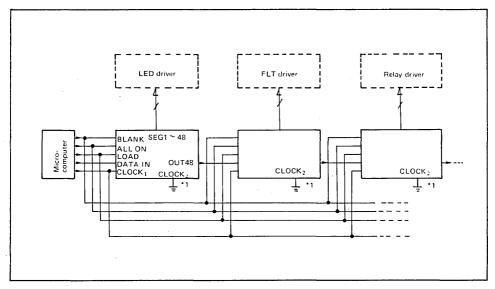

#### Output Expander

As explained above, this IC can drive the static LCD with the COM pin. In addition, it can also be

used as an output pin expander for a microcomputer with the following connections:

\*1: In this example, "H" is output by the positive logic, that is, when "H" is written from DATA IN, "H" is output with a LOAD signal. If the OSC pin is connected to V<sub>DD</sub>, the output has the negative logic, that is, the logic level input from the DATA IN pin is inverted and output.

### **OKI** semiconductor

# **MSM5221GS**

#### **56-DOT STATIC LCD DRIVER**

#### GENERAL DESCRIPTION

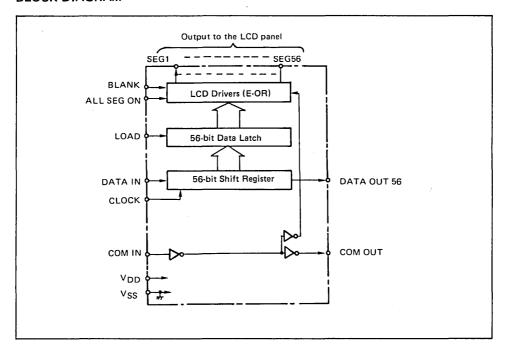

The OKI MSM5221GS is a 56 dot static LCD driver which is fabricated by low power CMOS metal gate technology. This LSI consists of 56-bit shift register, 56-bit latch and 56-bit LCD driver. The display data, which was input to the 56-bit shift register by the DATA IN signal and CLOCK signal, is transferred to the 56-bit latch by the LOAD signal and the data is output to the LCD through the 56-bit LCD driver.

#### **FEATURES**

- 56 dots static LCD driving capability

- Simple interface with microcomputer chip (controlled by three input signals).

- Bit-to-bit correspondence between the input and output

- Cascade connection capability

- · Fully controlled by the software

- LCD driving AC frequency is directly input externally

- Applicable as an output expander

- Supply voltage: 3 ~ 7V

- 80 pin plastic package (bent lead)

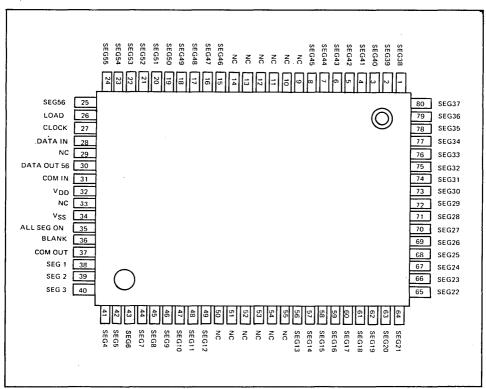

#### PIN CONFIGURATION

(Top View) 80 Lead Plastic Flat Package

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Item                | Symbol                            | Condition             | Limits                           | Unit |

|---------------------|-----------------------------------|-----------------------|----------------------------------|------|

| Supply voltage      | V <sub>DD</sub> – V <sub>SS</sub> | T <sub>a</sub> = 25°C | -0.3 ∼+7                         | V    |

| Input voltage       | V <sub>I</sub>                    | T <sub>a</sub> = 25°C | $V_{SS} - 0.3 \sim V_{DD} + 0.3$ | V    |

| Storage temperature | T <sub>stg</sub>                  | _                     | -55 ~+150                        | °c   |

#### **OPERATING RANGE**

| Item                  | Symbol                            | Condition | Limits   | Unit |

|-----------------------|-----------------------------------|-----------|----------|------|

| Supply voltage        | V <sub>DD</sub> – V <sub>SS</sub> |           | 3∼7      | V    |

| Operating temperature | TOP                               | _         | -40 ∼+85 | °c   |

#### **DC CHARACTERISTICS**

$(V_{DD} - V_{SS} = 5V, T_a = -40 \sim +85^{\circ}C)$

| Item                             | Symbol                               | Condition                                           | MIN          | TYP | MAX  | Unit |

|----------------------------------|--------------------------------------|-----------------------------------------------------|--------------|-----|------|------|

| "H" Input voltage                | VIH                                  | <del>-</del>                                        | 3.6          | _   | _    | V    |

| "L" Input voltage                | VIL                                  | _                                                   | -            | _   | 1.0  | V    |

| Input leakage current            | IH/IL                                | V <sub>I</sub> = 5V/V <sub>I</sub> = OV             | -            | _   | 1/-1 | μΑ   |

| "H" SEG Output voltage           | Vons                                 | ΙΟ = -30μΑ                                          | 4.8          | -   | _    | ٧    |

| "L" SEG Output voltage           | Vols                                 | ΙΟ = 30μΑ                                           | _            | -   | 0.2  | ٧    |

| "H" COM Output voltage           | Vohc                                 | I <sub>O</sub> = -150μA                             | 4.8          | _   | -    | ٧    |

| "L" COM output voltage           | VOLC                                 | 1 <sub>O</sub> = 150μA                              | _            | -   | 0.2  | ٧    |

| SEG Output current 1             | OHS1/IOLS1                           | V <sub>OH</sub> = 4.5V/V <sub>OL</sub> = 0.5V       | -100/<br>100 | _   | _    | μΑ   |

| SEG Output current 2             | I <sub>OHS2</sub> /I <sub>OLS2</sub> | V <sub>OH</sub> = 1V/V <sub>OL</sub> = 4V           | -400/<br>400 | -   | _    | μА   |

| COM Output current 1             | OHC1/OLC1                            | V <sub>OH</sub> = 4.5V/V <sub>OL</sub> = 0.5V       | -500/<br>500 | -   | _    | μΑ   |

| COM Output current 2             | IOHC2/IOLC2                          | V <sub>OH</sub> = 1V/V <sub>OL</sub> = 4V           | -2/2         | -   | -    | mA   |

| "H" Output voltage*1             | Voн                                  | I <sub>O</sub> = -0.1mA                             | 4.5          | -   | -    | V    |

| "L" Output voltage*1             | VOL                                  | I <sub>O</sub> = 0.1mA                              | -            | _   | 0.5  | V    |

| Clock pulse width*2              | twφ                                  | <del>-</del>                                        | 0.5          | -   | _    | μS   |

| Maximum clock pulse frequency*2  | fφMAX                                | _                                                   | 1            | _   | _    | MHz  |

| Input signal rising/falling time | t <sub>r</sub> φ, t <sub>f</sub> φ   | _                                                   | -            | _   | 5    | μs   |

| Static current consumption       | IDD                                  | V <sub>IN</sub> = V <sub>DD</sub> , V <sub>SS</sub> | _            | _   | 100  | μΑ   |

<sup>\*1:</sup> Applied to DATA OUT 56.

<sup>\*2:</sup> Applied to the clock for shift register.

# **FUNCTIONAL DESCRIPTION**

#### Operation Description

The display data is input to the shift register by the DATA IN signal and CLOCK signal. It is transferred

to the 56-bit latch by the LOAD signal and it is output to the LCD panel through 56-bit LCD driver.

#### COM IN

Input pin to generate the COM OUT signal. The same phase signal as the COM IN pin is output from the COM OUT pin.

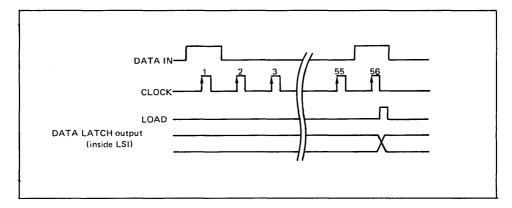

#### DATA IN, CLOCK

DATA IN is a data input in which enables the LCD to display when DATA IN signal is at high level. The 56-bit shift register is shifted at the rising edge of the CLOCK signal. Initially, the first bit of the shift register contains the current logic level of the DATA IN pin, and the bit N (N = 2  $\sim$  56) contains the data which was in bit N - 1 (N = 2  $\sim$  56) before the start of the operation. The data which was in bit 56 before the operation start is considered invalid.

#### LOAD

The data in the 56-bit shift register is shifted to the 56-bit latch when the LOAD pin is set at the high level, while the last data which was transferred to the latch when the LOAD pin was set at high level is constantly output when the LOAD is set at low level.

# ALL SEG ON

When this pin is set at high level, all segments display turn on. This pin has the priority to the BLANK pin described as below.

#### BLANK

When this pin is set at high level, all segments display turn off. The ALL SEG ON pin has the priority over this pin.

#### SEG1 ~ SEG56

LCD driving output pins. The reversed phase of the COM signal, which is used to display the data, is output from these pins when SEG1 ~ SEG56 are set at high level, while there is no display on the LCD when these pins are set at low level.

The display data which was input from the DATA IN pin is output from these pins to the LCD panel. The SEG N pin corresponds to the bit N of the shift register.

#### COM OUT

Output terminal for the LCD. It is connected to the common side of the LCD panel.

#### DATA OUT 56

Output pin of the shift register. It is used when the MSM5221GS is connected in a series (cascade connection). MSM5221GS's DATA OUT 56 is connected to the next MSM5221GS's DATA IN terminal.

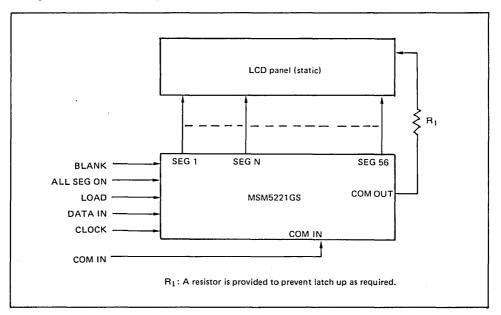

# APPLICATION CIRCUIT

# Single MSM5221GS to the LCD panel

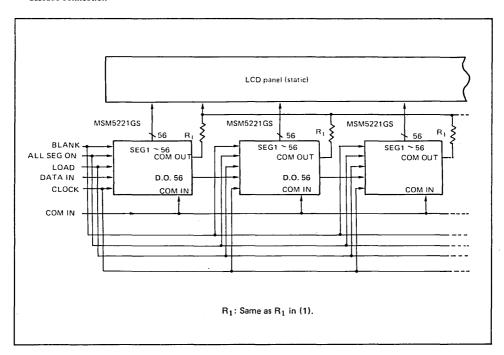

# Cascade connection

# **KI** semiconductor

# **MSM5265GS**

# 160-DOT LCD DRIVER

# GENERAL DESCRIPTION

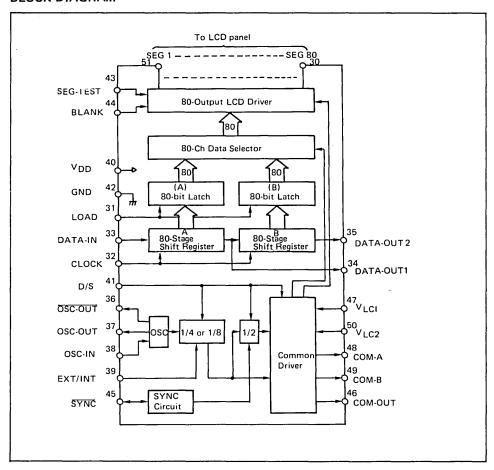

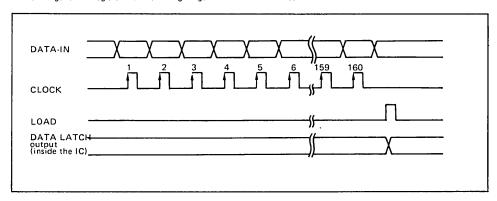

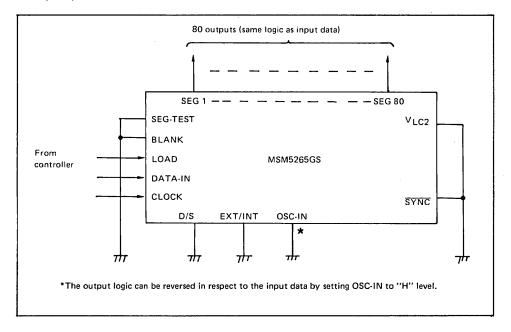

The OKI MSM5265GS is an LCD driver which can directly drive up to 80 segments in the static display mode, while it can directly drive up to 160 segments in the 1/2 duty dynamic display mode.

The MSM5265GS is fabricated by low power CMOS metal gate technology, consisting of 160-stage shift register, 160-bit latch, 80 sets of LCD driver and a common signal generator.

The display data is serially input from the DATA-IN terminal to the 160-stage shift register synchronized with the CLOCK pulse. The data is shifted to the 160-bit latch by the LOAD signal. Then the latched data is directly output to the LCD from the 80 sets of LCD driver as serial output.

The common signal can be generated by the on-chip generator, or can be externally input. The common synchronization circuit which is used in the dynamic display mode is integrated on the chip.

#### **FEATURES**

- 80 segments display drive (in the static display mode)

- 160 segments display drive (in the dynamic display

- Simple interface with microcomputer

- Bit-to-bit correspondence between input data and output data

- H: Display

- L: No display

- Cascade connection capability

- On-chip common signal generator

- Can be synchronized with the external common signal

- Testing terminals for all-on (SEG-TEST) and all-off (BLANK)

- Applicable as an output expander

- LCD driving voltage can be adjusted by the combination of V<sub>LC1</sub> and V<sub>LC2</sub>

- Supply voltage: 3.0 ~ 6.0 V

- 100 pin plastic flat package (bent lead)

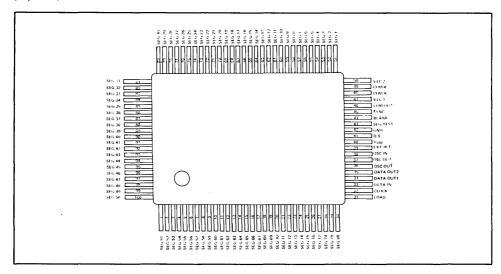

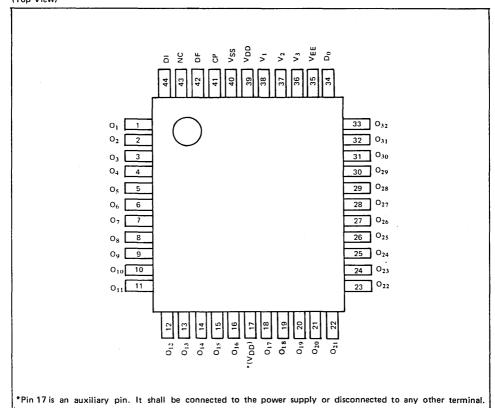

# PIN CONFIGURATION

(Top View)

# **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS

| Item                | Symbol           | Condition             | Limits                        | Unit |

|---------------------|------------------|-----------------------|-------------------------------|------|

| Supply voltage      | V <sub>DD</sub>  | $T_a = 25^{\circ}C$   | - 0.3 <b>~</b> + 6.5          | V    |

| Input voltage       | VI               | T <sub>a</sub> = 25°C | $GND - 0.3 \sim V_{DD} + 0.3$ | V    |

| Storage temperature | T <sub>stg</sub> | _                     | - 55 ~+ 150                   | °c   |

# **OPERATING RANGE**

| Item                  | Symbol                             | Condition | Limits          | Unit |

|-----------------------|------------------------------------|-----------|-----------------|------|

| Supply voltage        | V <sub>DD</sub>                    | _         | 3∼6             | V    |

| Operating temperature | T <sub>OP</sub>                    |           | <b>-40 ∼85</b>  | °c   |

| LCD driving voltage   | V <sub>DD</sub> - V <sub>LC2</sub> | _         | $3 \sim V_{DD}$ | V    |

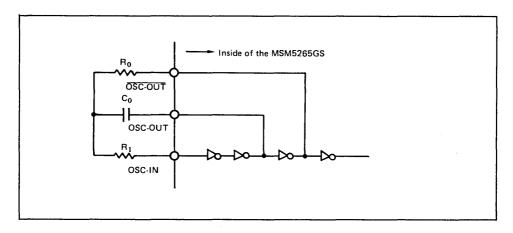

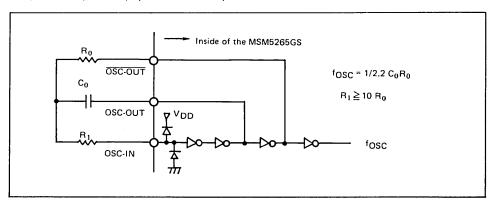

# RECOMMENDING OSCILLATION CIRCUIT CONDITION

| Item                       | Symbol         | Corresponding pin    | Condition                          | MIN   | TYP | MAX   | Unit |

|----------------------------|----------------|----------------------|------------------------------------|-------|-----|-------|------|

| Oscillator resistance      | R <sub>0</sub> | 36 OSC-OUT           | _                                  | 56    | 100 | 220   | kΩ   |

| Oscillator capacitance     | C <sub>0</sub> | 37 OSC-OUT           | Film capacitor                     | 0.001 | -   | 0.047 | μF   |

| Current limiter resistance | R <sub>1</sub> | 38 OSC-IN            | R <sub>1</sub> ≥ 10 R <sub>0</sub> | 0.56  | 1   | 2.2   | мΩ   |

| Common signal frequency    | fсом           | 48 COM-A<br>49 COM-B | _                                  | 25    | -   | 150   | Hz   |

# D.C. CHARACTERISTICS

$(V_{DD} = 5.0V T_a = -40 \sim +85^{\circ}C)$

| Item                           | Symbol           | Corresponding pin                                   | Condition                                                               | MIN | TYP | MAX | Unit        |

|--------------------------------|------------------|-----------------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|-------------|

| "H" Input<br>voltage           | VIН              | 43 SEG-TEST<br>44 BLANK<br>31 LOAD                  | _                                                                       | 3.6 |     | -   | <b>&gt;</b> |

| "L" Input<br>voltage           | ۷ĮL              | 33 DATA-IN 32 CLOCK 41 D/S                          | <del>-</del>                                                            | -   | -   | 1.0 | >           |

| Input<br>leakage<br>current    | IIL              | 39 EXT/INT<br>38 OSC-IN                             | V <sub>I</sub> = 5.0V/0V                                                | _   | _   | ±1  | μΑ          |

| "H" Output<br>voltage          | Voн              | 34 DATA-OUT1<br>35 DATA-OUT2<br>46 COM-OUT          | I <sub>O</sub> = -100μΑ                                                 | 4.5 | ı   | ı   | >           |

|                                |                  | 37 OSC-OUT<br>36 OSC-OUT                            | I <sub>O</sub> ≈ −200μA                                                 | 4.5 | 1   | -   | >           |

|                                |                  | 50 ~ 100 1 ~ 30<br>output of all segments           | $V_{LC1} = 2.5V \ V_{LC2} = 0V$<br>$I_{O} = -30\mu A$                   | 4.8 | 1   | 1   | >           |

|                                |                  | 48 COM-A<br>49 COM-B                                | V <sub>LC1</sub> = 2.5V V <sub>LC2</sub> = 0V<br>I <sub>O</sub> = 150μΑ | 4.8 | _   | 1   | <b>V</b>    |

| "M" Output<br>voltage          | V <sub>ОМ</sub>  | 48 COM-A<br>49 COM-B                                | $V_{LC1} = 2.5V \ V_{LC2} = 0V$<br>$I_{O} = \pm 150\mu A$               | 2.3 | -   | 2.7 | >           |

| "L" Output<br>voltage          | VOL              | 34 DATA-OUT1<br>35 DATA-OUT2<br>46 COM-OUT          | Ι <sub>Ο</sub> = 100μΑ                                                  | _   | -   | 0.5 | >           |

|                                |                  | 37 OSC-OUT<br>36 OSC-OUT                            | ΙΟ = 200μΑ                                                              |     | _   | 0.5 | V           |

|                                |                  | $51 \sim 100$ $1 \sim 30$<br>Output of all segments | V <sub>LC1</sub> = 2.5V V <sub>LC2</sub> = 0V<br>I <sub>O</sub> = 30μA  | _   | 1   | 0.2 | >           |

|                                |                  | 48 COM-A<br>49 COM-B                                | $V_{LC1} = 2.5V V_{LC2} = 0V$<br>$I_{O} = 150\mu A$                     | -   | -   | 0.2 | >           |

|                                |                  | 45 SYNC                                             | ΙΟ = 250μΑ                                                              | _   | _   | 0.8 | >           |

| Output<br>leakage<br>current   | LO               | 45 SYNC                                             | $V_O = 5V$ when internal Tr is off                                      | _   | _   | 5   | μΑ          |

| Segment<br>output<br>impedance | R <sub>SEG</sub> | 51 ~ 100 1 ~ 30  Output of all segments             | $V_{LC1} = (5 + V_{LC2})/2$<br>$V_{LC2} = 0 \sim 2V$                    | -   | _   | 10  | kΩ          |

| Item                             | Symbol           | Corresponding pin    | Condition                                                                                     | MIN | TYP  | мах | Unit |

|----------------------------------|------------------|----------------------|-----------------------------------------------------------------------------------------------|-----|------|-----|------|

| Common output impedance          | R <sub>СОМ</sub> | 48 COM-A<br>49 COM-B | $V_{LC1} = (5 + V_{LC2})/2$<br>$V_{LC2} = 0 \sim 2V$                                          | _   | -    | 1.5 | kΩ   |

| Static mode consumption current  | I <sub>DD1</sub> | 40 Vpp               | Set all input level<br>either "H" or "L"                                                      |     |      | 100 | μΑ   |

| Dynamic mode consumption current | I <sub>DD2</sub> | 40 V <sub>DD</sub>   | No load oscillation.<br>$R_0$ = 100 k $\Omega$ ,<br>$C_0$ = 0.01 $\mu$ F, $R_1$ = 1M $\Omega$ |     | 0.12 | 0.5 | mΑ   |

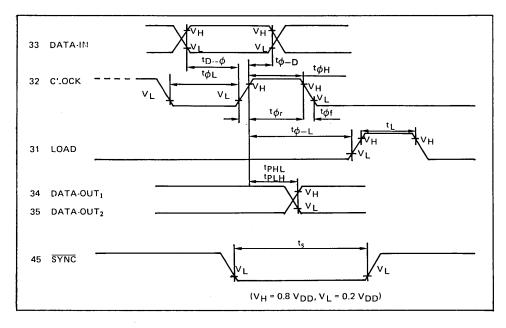

# **SWITCHING CHARACTERISTICS**

$(V_{DD} = 3.0 \sim 6.0 V T_a = -40 \sim +85^{\circ}C)$

| Item                                | Symbol                 | Corresponding pin                                                | Condition                                          | MIN | MAX | Unit |

|-------------------------------------|------------------------|------------------------------------------------------------------|----------------------------------------------------|-----|-----|------|

| Maximum clock frequency             | <sup>f</sup> φMAX      |                                                                  |                                                    | 1   | _   | MHz  |

| Clock "H" time                      | tφH                    |                                                                  | _                                                  | 0.3 | _   | μs   |

| Clock "L" time                      | tφL                    | 32 CLOCK                                                         |                                                    | 0.5 | _   | μs   |

| Clock pulse rising/<br>falling time | tφr<br>tφ <sub>f</sub> |                                                                  |                                                    | -   | 0.1 | μs   |

| Data setup time                     | tD−φ                   | 33 DATA-IN                                                       |                                                    | 0.1 | _   | μs   |

| Data hold time                      | tφ−D                   | 32 CLOCK                                                         | _                                                  | 0.1 | -   | μs   |

| "H", "L" propagation<br>delay time  | tpHL<br>tpLH           | 34 DATA-OUT <sub>1</sub><br>35 DATA-OUT <sub>2</sub><br>32 CLOCK | When 15PF output capacitors are locaded 34 and 35. | _   | 0.8 | μs   |

| LOAD "H" time width                 | tL                     | 31 LOAD                                                          |                                                    | 0.2 | _   | μs   |

| CLOCK → LOAD time                   | <sup>t</sup> φ − ∟     | 32 CLOCK<br>31 LOAD                                              | _                                                  | 0.1 | -   | μs   |

| OSC-IN Maximum input frequency      | foscmax                | 38 OSC-IN                                                        | _                                                  | 5   | -   | kHz  |

| SYNC "L" time width                 | ts                     | 45 SYNC                                                          |                                                    | 0.2 | -   | μs   |

#### **FUNCTIONAL DESCRIPTION**

# Operational description

The MSM5265GS consists of 160-stage shift register, 160-bit latch, and 80 sets of LCD driver. The display data is input from the DATA-IN terminal to the 160-stage shift register at the rising edge of the

CLOCK pulse and it is shifted to the 160-bit latch when the LOAD signal is set at "H" level, then it is directly output to the LCD panel from the 80 sets of LCD driver.

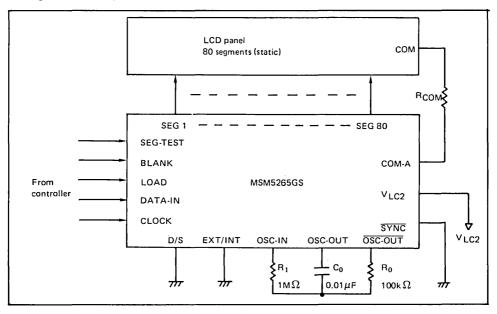

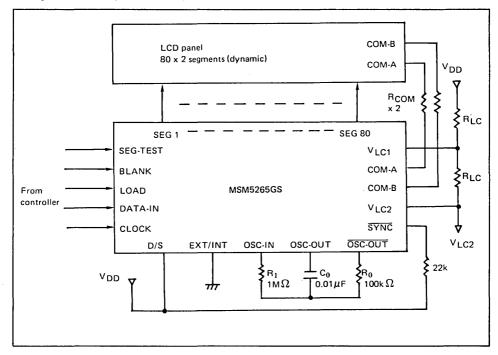

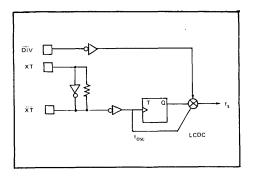

# OSC-IN, OSC-OUT, OSC-OUT

By connecting the external registors  $R_0$ ,  $R_1$  and external capacitor  $C_1$  with OSC-IN, OSC-OUT and  $\overline{OSC-OUT}$  respectively as shown in the figure below, an oscillating circuit to generate the common signal is formed.

This frequency is divided into either 1/8 or 1/4 by the internal dividing circuit. The 1/8 divided frequency is used in the static display mode, while the 1/4 divided frequency is used as the common signal in the dynamic display mode which is output from the COM-OUT terminal. (EXT/INT should be set at low level.)

The resistor  $R_1$  is to limit the current on the OSC-IN terminal's protecting diodes. The value of the  $R_1$  should be 10 times more than that of  $R_0$ .

When the external common signal is used, the EXT/ INT terminal should be set at high level and the external common signal should be input from the OSC-IN terminal.

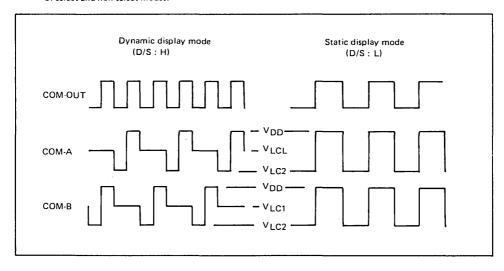

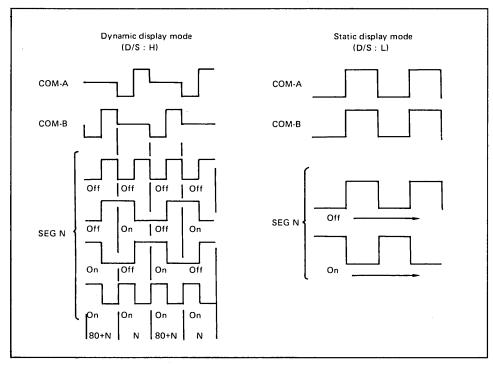

#### D/S

When this pin is set at high level, the MSM5265GS operates in the dynamic display mode, while it operates in the static display mode when this pin is set at low level.

#### EXT/INT

When the external common signal is used, this pin should be set at high level and the external common signal is to be input from the OSC-IN terminal. The input common signal is used same as the internal common signal and is output from the COM-OUT pin through the buffer.

When the on-chip common signal generator is used, this pin should be set at low level.

When the MSM5265GS is used as an output expander, this pin should be set at high level and the OSC-IN pin should be set at low level.

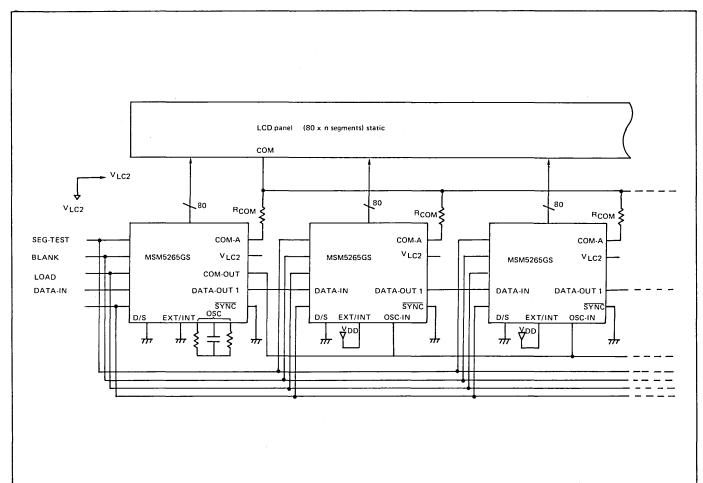

#### COM-OUT

When more than two MSM5265GSs are connected in a series (cascade connection), this pin should be connected with all of the slave MSM5265GS's OSC-IN terminal.

#### SYNC

This pin is an input/output pin which is used when more than two MSM5265GSs are used in a series (cascade connection) in the dynamic display mode. All of the involved MSM5265GS's \$\overline{SYNC}\$ pins should be connected in a same line so that they should be pulled up by the common resistor, which makes phase level of all involved MSM5265GS's COM-A terminals and COM-B terminals equal. When single MSM5265GS is used in the dynamic display mode, \$\overline{SYNC}\$ should be pulled up by the resistor.

In the static display mode including single MSM5265GS's operation, cascade connection and output expander operation, this pin should be set at ground level.

#### DATA-IN, CLOCK

The display data is serially input from the DATA-IN terminal to the 160-stage shift register at the rising edge of the CLOCK pulse. The high level of the display data is used to turn the display on, while low level of the display data is used to turn off the display.

#### DATA-OUT

The 80th stage of the shift register contents is output from this pin.

When more than two MSM5265GSs are connected in a series (cascade connection) in the static display mode, this pin should be connected to the next MSM5265GS's DATA-IN terminal.

#### DATA-OUT<sub>2</sub>

The 160th stage of the shift register contents is output from this pin.

When more than two MSM5265GSs are connected in a series (cascade connection) in the dynamic display mode, this pin should be connected to the next MSM5265GS's DATA-IN terminal.

#### LOAD

The signal for latching the shift register contents is input from this pin.

When LOAD pin is set at high level, the shift register contents is shifted to the 80 sets of the LCD driver. When this pin is set at low level, the last display data, which was transferred to the 80 sets of LCD driver when LOAD pin was set at high level, is held.

#### VLC2

Supply voltage pin for the 80 sets of LCD driver. The input level to this pin should be the low level output voltage of segment output (SEG1  $\sim$  SEG80) and common output (COM-A, COM-B).

In this case, the high level of segment output and common output is V<sub>DD</sub> level, while low level of segment output and common output is V<sub>LC2</sub> level. V<sub>LC2</sub> should be set at more than ground level.

# V<sub>LC1</sub>

Supply voltage pin for the middle level voltage of the common output. The input level of this pin is the middle level output voltage of the common output (COM-A, COM-B) in the dynamic display mode.

The value of the  $V_{LC1}$  is calculated by the following formula.

$$V_{LC1} = (V_{DD} + V_{LC2})/2$$

In the static display mode, this pin should be set at open level.

#### COM-A, COM-B

LCD driving common signal is output from these pins and these pins should be connected to the common side of the LCD panel.

- In the static display mode

Same phase pulse as COM-OUT terminal is output from both of COM-A and COM-B. In

- output from both of COM-A and COM-B. In this case high level is  $V_{\mbox{\scriptsize DD}}$  level and low level is  $V_{\mbox{\scriptsize LC2}}$  level.

- In the dynamic display mode

The COM-A and COM-B output signal are alternately changed within each COM-OUT output cycle, resulting in alternately repetition of select and non-select modes.

In the select mode the, same phase level as the COM-OUT signal is output.

In this case,  $V_{DD}$  or  $V_{LC2}$  is output at high level or low level respectively. In the non-select mode,  $V_{LC1}$  is output at the middle level. In the select mode of COM-A (non-select mode of COM-B), the 1st  $\sim$ 80th latched data contents are output from the 80 sets of LCD driver to the LCD panel.

In the select mode of COM-B (non-select mode of COM-A), the 81st  $\sim$  160th latched data contents are output from the 80 sets of LCD driver to the LCD panel.

#### ● SEG1~SEG80

LCD segment driving signal is output from these pins and these pins should be connected to the segment side of the LCD panel.

"H" level :  $V_{DD}$  level, "L" level :  $V_{LC2}$  level

In the static display mode

Since the Nth bit of the latched data contents corresponds to the SEG N, the data after 81st bit is invalid for the display in the static display mode.

The inversed phase signal as the COM-OUT signal is output to the LCD, when the display turns on, while the same phase signal is output when the display turns off.

In the dynamic display mode

Output of the SEG N corresponds as follows.

When COM-A is select mode: Nth bit of the latched data contents

When COM-B is select mode: (80 + N)th bit of the latched data contents

When the display turns on, the inversed phase signal as the common signal is output, while the same phase signal as the common signal is output when the display turns off.

# SEG-TEST

This pin is used to test the segment output (SEG1  $\sim$  SEG80). All display turn on when this pin is set at high level, while the display becomes the same condition before this pin was set at high level, when this pin is set at low level. This pin has the priority over BLANK terminal.

# BLANK

This pin is also used to test the segment output (SEG1 ~ SEG80). All display turn off when this pin is set at high level, while the display becomes the same condition before this pin was set at high level, when this pin is set at low level.

When SEG-TEST pin is set at high level, the input on this pin is invalid.

# APPLICATION CIRCUIT

1) Single MSM5265GS operation in the static display mode.

2) Single MSM5265GS operation in the dynamic display mode.

3) Cascade connection of MSM5265GSs in the static display mode.

STATIC LCD DRIVER · MSM5265GS

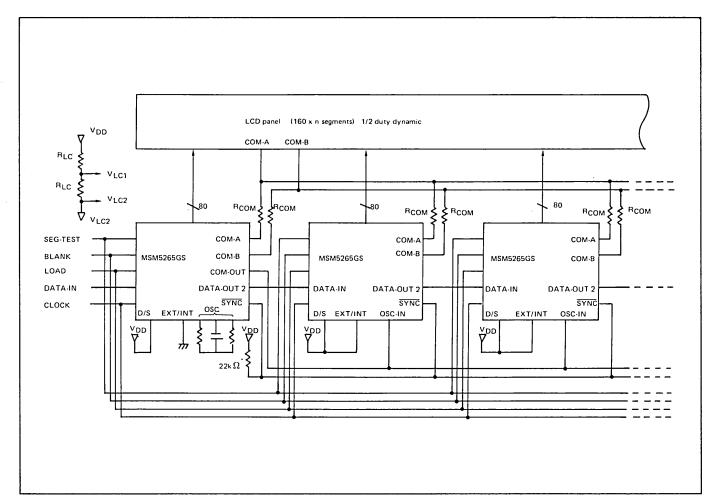

Cascade connection of MSM5265GSs in the dynamic display mode.

# 5) Output-expander

# DOT MATRIX LCD DRIVER

# **MSM5238GS**

# **DOT MATRIX LCD 32 DOT COMMON DRIVER**

# GENERAL DESCRIPTION

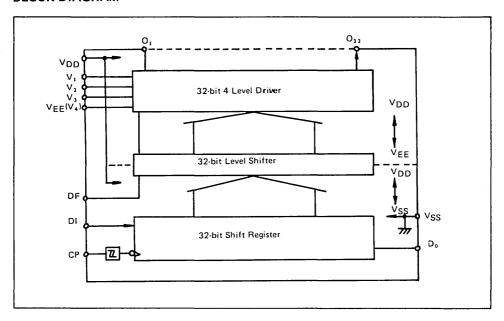

The OKI MSM5238GS is a dot matrix LCD's common driver LSI which is fabricated by low power CMOS metal gate technology. The scanning signal in one matrix display frame can be divided into up to 1/32 duty. This LSI consists of 32-bit shift register, 32-bit level shifter and 32-bit 4-level driver.

This LSI can drive a variety of LCD panel because the bias voltage, which determines the LCD driving voltage, can be optionally supplied from external source.

#### **FEATURES**

- Supply voltage: 3 ~ 7V

- LCD driving voltage: 3 ~ 16V

- Applicable LCD duty: 1/32 ~ 1/64

- (Two chips of MSM5238GS are required to drive 1/64 duty LCD panel).

- Bias voltage can be supplied externally

- 44 pin PLASTIC FLAT Package

# **PIN CONFIGURATION**

(Top View)

# **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| Item                | Symbol                            | Condition | Limits                 | Unit |

|---------------------|-----------------------------------|-----------|------------------------|------|

| Supply voltage      | V <sub>DD</sub>                   |           | <b>-0.3</b> ∼ 7        | V    |

| Supply voltage      | V <sub>DD</sub> - V <sub>EE</sub> | Ta = 25°C | 0~16                   | V    |

| Input voltage       | V <sub>I</sub>                    |           | -0.3 ~ V <sub>DD</sub> | V    |

| Storage temperature | Tstg                              | _         | -55 ~+ 150             | °c   |

# **OPERATING RANGE**

| Item                  | Symbol                            | Condition | Value   | Unit |

|-----------------------|-----------------------------------|-----------|---------|------|

| Supply voltage        | V <sub>DD</sub>                   | -         | 3~7     | V    |

| Supply voltage        | V <sub>DD</sub> – V <sub>EE</sub> | =         | 3~16    | V    |

| Operation temperature | Topr                              | _         | -40~+85 | °c   |

| Fan-out               | N                                 | MOS load  | 5       | -    |

$V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ (V_{EE})$

# D.C. CHARACTERISTICS

| Item              | Symbol                   |                        |                        | C          | ondition                                                    |             | Limits |             | Unit |

|-------------------|--------------------------|------------------------|------------------------|------------|-------------------------------------------------------------|-------------|--------|-------------|------|

|                   | <b>0</b> , <b>0</b>      | V <sub>DD</sub><br>(V) | V <sub>SS</sub><br>(V) | VEE<br>(V) |                                                             | MIN         | TYP    | MAX         | 0    |

| "H"<br>input      | *1<br>V <sub>IH1</sub> / | 5                      | 5 0 0~ -9 -            |            | 3.6/<br>4.2                                                 | -           | -      | v           |      |

| voltage           | V <sub>IH2</sub>         | 7                      | 0                      | 0 ~<br>-7  | -                                                           | 5.2/<br>6.0 | _      | _           | ľ    |

| "L"               | *1<br>V <sub>IL1</sub> / | 5                      | 0                      | 0 ~<br>_9  | -                                                           | -           | _      | 0.8/        |      |

| voltage           | VIL2                     | 7                      | 0                      | 0 ~<br>-7  | _                                                           |             |        | 1.1/<br>0.5 | V    |

| Input             | Ιн                       | 7                      | 0                      | -7         | V <sub>I</sub> = 7V                                         | -           | _      | 1           |      |

| voltage           | IIL                      | 7                      | 0                      | -7         | V <sub>I</sub> = 0V                                         | -           | _      | -1          | μΑ   |

| "H"               | *2                       | 5                      | 0                      | 0 ~<br>_9  | I <sub>0D</sub> = -40μΑ                                     | 4.2         | _      | _           |      |

| output<br>voltage | νон                      | 7                      | 0                      | 0 ~<br>-7  | I <sub>0D</sub> = -56μΑ                                     | 5.8         | -      | -           | V    |

| "L"               | *2                       | 5                      | 0                      | 0 ~<br>-9  | I <sub>0D</sub> = 0.2mA                                     | _           | -      | 0.4         |      |

| output<br>voltage | VOL                      | 7                      | 0                      | 0 ~<br>-7  | I <sub>0D</sub> = 0.3mA                                     | _           | _      | 0.4         | V    |

|                   |                          | 5                      | 0                      | 0          | V <sub>0</sub> : DRV output                                 | _           | 500    | 2000        |      |

|                   | RON                      | ກ                      | 0                      | -5         | $V_0 - V_1 = 0.25V$<br>$V_1 = V_{EE} \sim (V_{DD} - 0.25V)$ | _           | 250    | 1000        | Ω    |

|                   | $(V_1, V_4)$             | 7                      | 0                      | 0          | $V_0 - V_4 = 0.25V$                                         |             | 350    | 1400        | 32   |

| ON                |                          | ,                      | 0                      | -7         | V4(VEE): MAX 0V                                             | -           | 200    | 800         |      |

| Resistance        |                          | 5                      | 0                      | 0          | V <sub>N</sub> = V <sub>2</sub> or V <sub>3</sub>           | _           | 800    | 3200        |      |

|                   | RON                      | 3                      | 0                      | -5         | V = DRV output                                              | -           | 450    | 1800        |      |

|                   | $(V_2, V_3)$             | 7                      | 0                      | 0          | $V_0 - V_N = 0.25V$<br>$V_N = V_{EE} \sim (V_{DD} - 0.25V)$ |             | 550    | 2200        | Ω    |

|                   |                          | _ ′                    | 0                      | -7         | VN - VEE (VDD - 0.25V)                                      | -           | 350    | 1400        |      |

| OFF Lead          | 1                        | 5                      | 0                      | -9         | _                                                           | _           |        | ±5          |      |

| current           | <sup>I</sup> OFF         | 7                      | 0                      | 7          | _                                                           |             |        | ±5          | μΑ   |

| Power supply      |                          | 5                      | 0                      | -9         | _                                                           | _           | -      | 0.5         |      |

| current           | IDD                      | 7                      | 0                      | -7         | -                                                           | _           | -      | 1.0         | mA   |

| Input capacitance | CI                       |                        |                        |            | -                                                           | _           | 5      | _           | рF   |

<sup>\*1</sup>  $V_{IH_1}$  and  $V_{IL_1}$  are input pins for DI and DF, while  $V_{IH_2}$  and  $V_{IL_2}$  are input pins for CP.

<sup>\*2</sup>  $V_{OH}$  and  $V_{OL}$  are output pins for  $D_0$ .

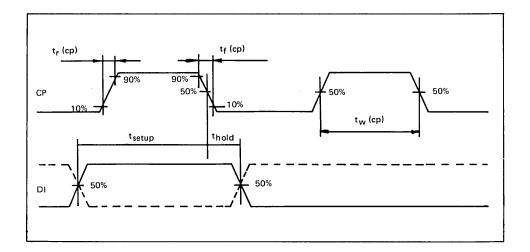

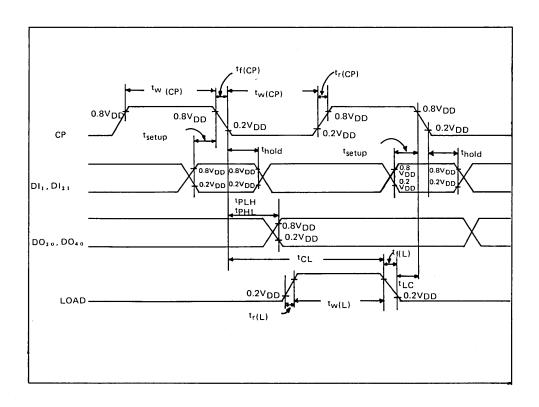

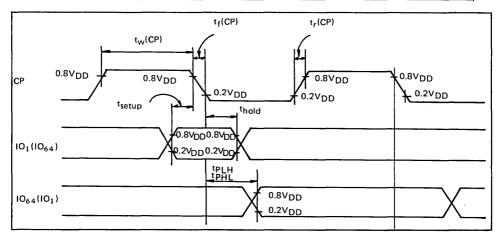

# SWITCHING CHARACTERISTICS

| Item                            | Symbol              | V <sub>DD</sub><br>(V) | Condition | MIN | TYP | мах | Unit |

|---------------------------------|---------------------|------------------------|-----------|-----|-----|-----|------|

| 14                              | . ()                | 5                      | _         | 400 | _   | _   | VII- |

| Maximum clock frequency         | t (cp)              | 7                      |           | 550 | _   | _   | KHz  |

| Clock pulse width               | t (on)              | 5                      | _         | 400 | -   | _   |      |

|                                 | t <sub>W</sub> (cp) | 7                      | -         | 300 | -   | _   | ns   |

| Data setup time (DATAIN → CP)   |                     | 5                      | -         | 100 | -   |     |      |

| Data setup time (DATAIN 7CF)    | t <sub>setup</sub>  | 7                      | _         | 50  | 1   | -   | ns   |

| Data hold time (DATAIN → CP)    | thold               | 5                      | _         | 800 | _   | _   |      |

| Data noid time (DATAIN 7CP)     | ·noia               | 7                      | -         | 500 | _   | _   | ns   |

| Clock pulse Dising/Felling time | tr (cp)             | 5                      | _         | _   | _   | 0.5 |      |

| Clock pulse Rising/Falling time | tr (cp)             | 7                      | _         | _   | _   | 0.1 | ms   |

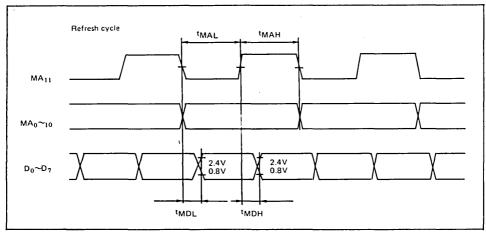

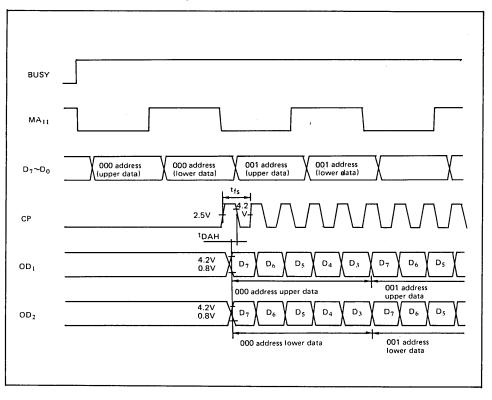

#### PIN DESCRIPTION

#### • D

The data from LCD controller LSI is input to 32-bit shift register from DI. (Positive logic)

This LSI is applicable up to 1/32 duty LCD panel because this LSI consists of 32-bit shift register.

#### CP

Clock pulse input pin for 32-bit shift register. The data is shifted to 32-bit level shifter at the falling edge of the clock pulse. A data set up time (tsetup) and data hold time (thold) is required between DI and CP signal. (Refer to SWITCHING CHARACTERICS.) Schmit circuit is included in CP input circuit.

#### DF

Alternate signal input pin for LCD driving waveform.

#### V<sub>DD</sub>, V<sub>SS</sub>

$V_{DD}$  is a supply voltage pin. Usually it is used at  $V_{DD} = 3.0 \sim 7.0 \text{V}$  Vss is a ground pin. (Vss = 0V)

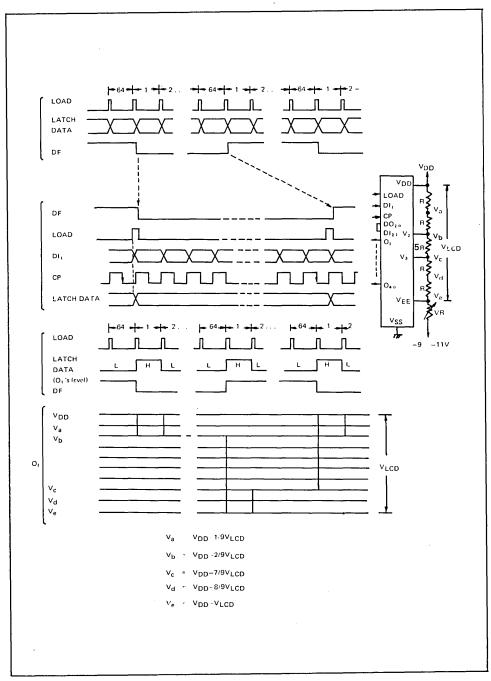

# • $O_1 - O_{32}$

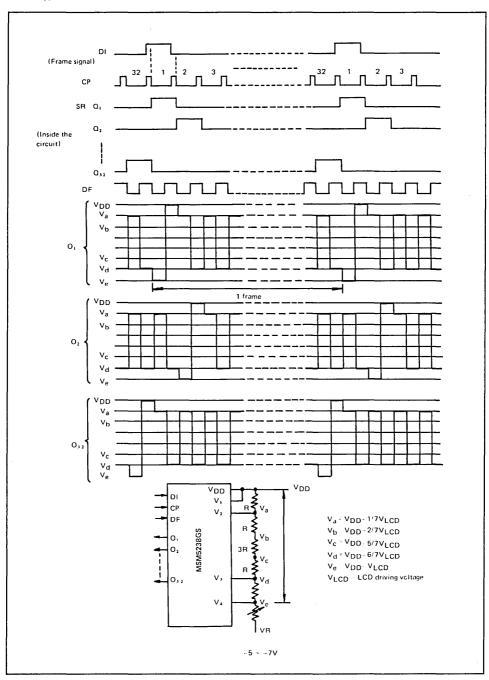

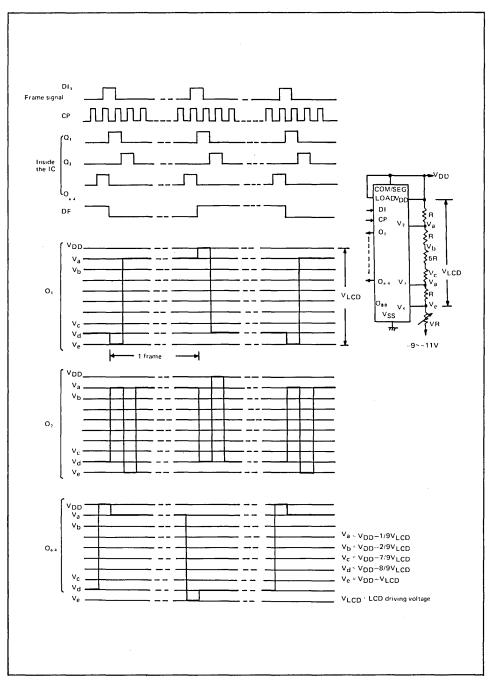

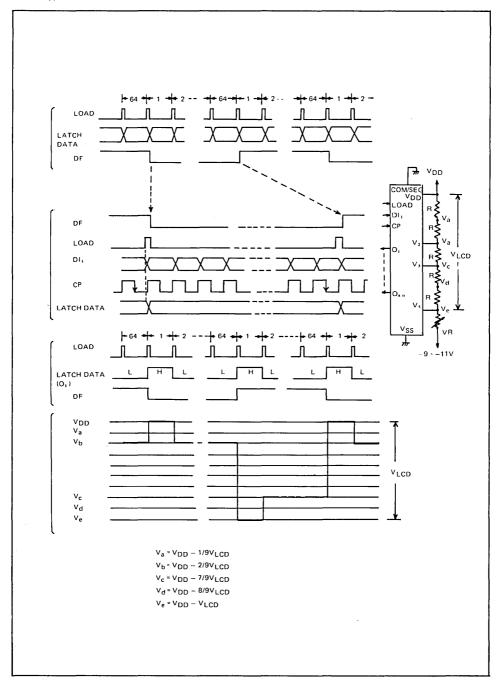

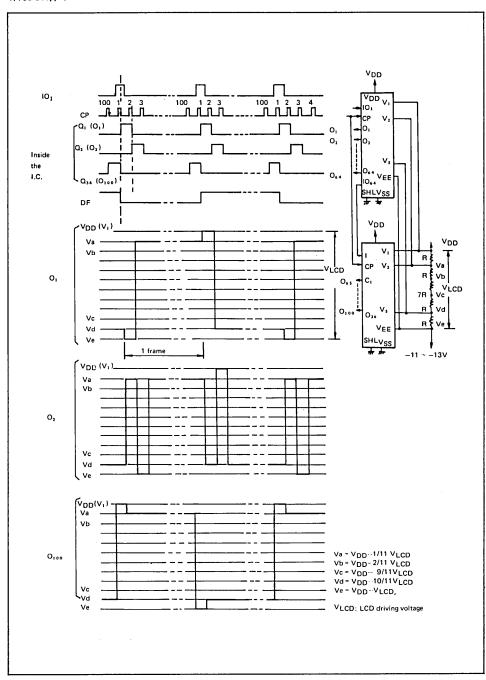

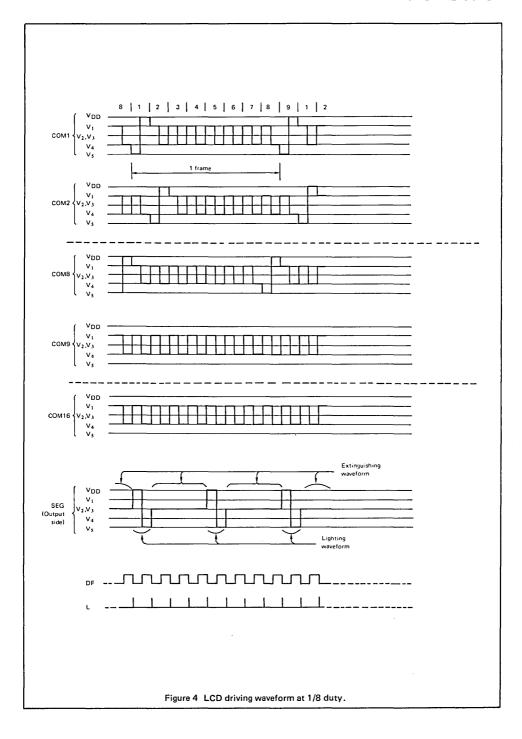

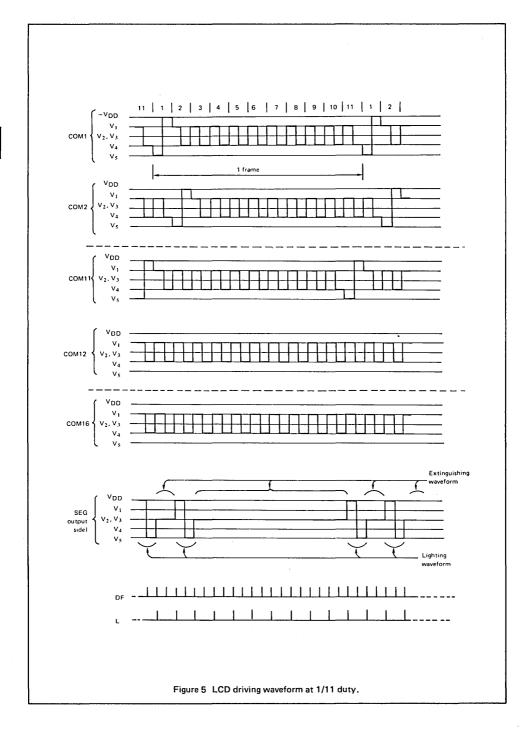

Display data output pins which correspond to each data bit in the latch. One of  $V_1$ ,  $V_2$ ,  $V_3$  and  $V_4$  is selected as a display driving voltage source according to the combination of latched data level and DF signal. Refer to the truth table and Time Chart. Output signal is a analog signal.  $O_1 - O_{32}$  are connected to the common side of the LCD panel.

| Latched data | DF | Display data output level |

|--------------|----|---------------------------|

|              | L  | V <sub>2</sub>            |

| <u>.</u>     | Н  | V <sub>3</sub>            |

| н            | L  | V <sub>4</sub>            |

| П            | Н  | V <sub>1</sub>            |

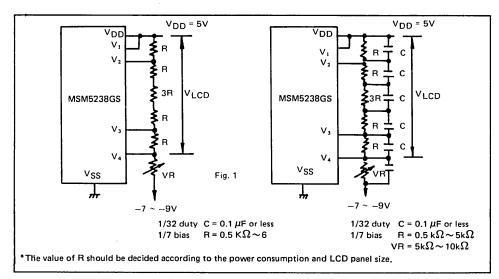

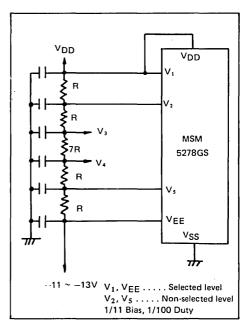

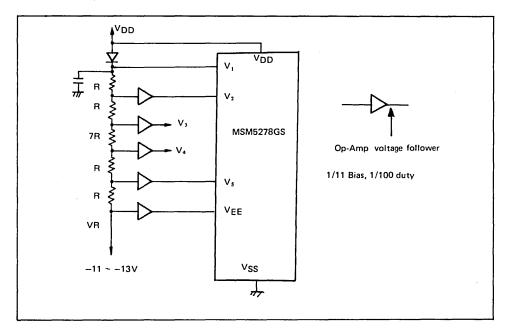

# V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub>, V<sub>4</sub>

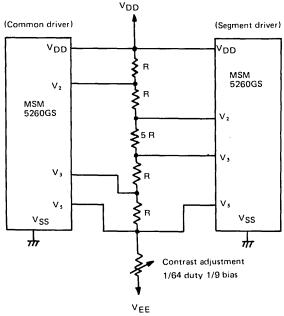

Bias supply voltage pin to drive the LCD. Bias voltage divided by the registance is usually used as supply voltage source.

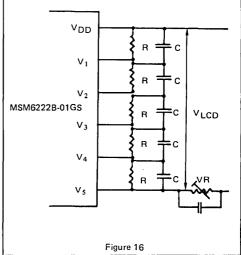

Fig. 1 shows the case when the bias voltage, which determines the LCD driving voltage, is supplied from the external source.

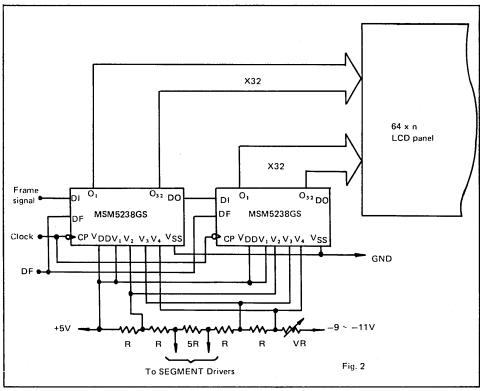

#### DO

Shift register contents output pin. The data which was input from DI is output from DO with 32 bits' delay, synchronized with the clock pulse. By connecting DO with next MSM5238GS's DI, this LSI is applicable to the LCD, the duty of which is 1/64. Refer to the Fig. 2 below.

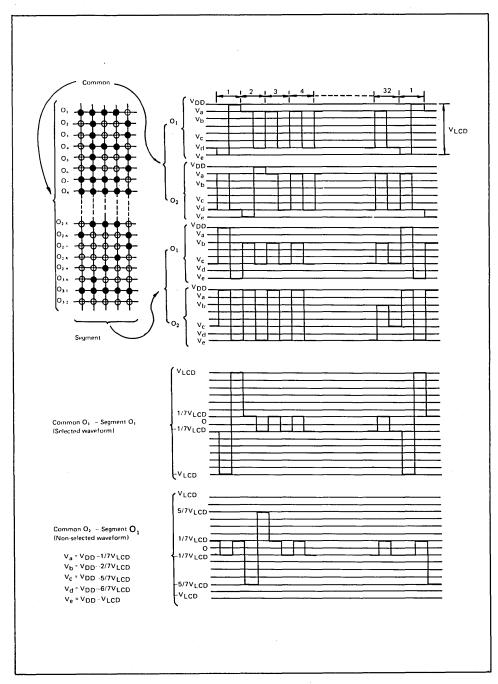

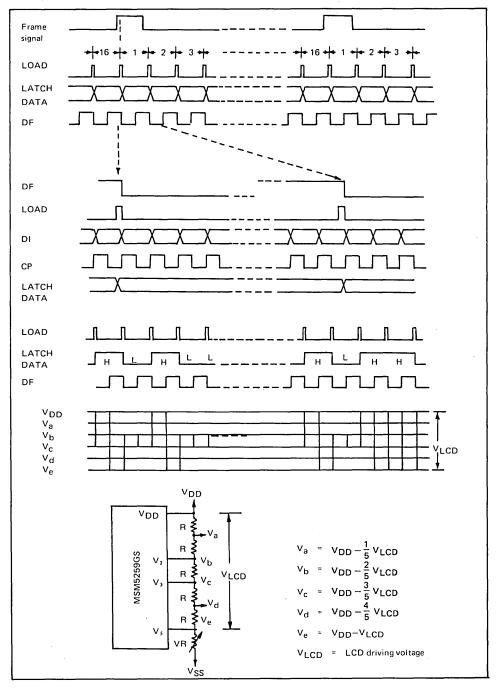

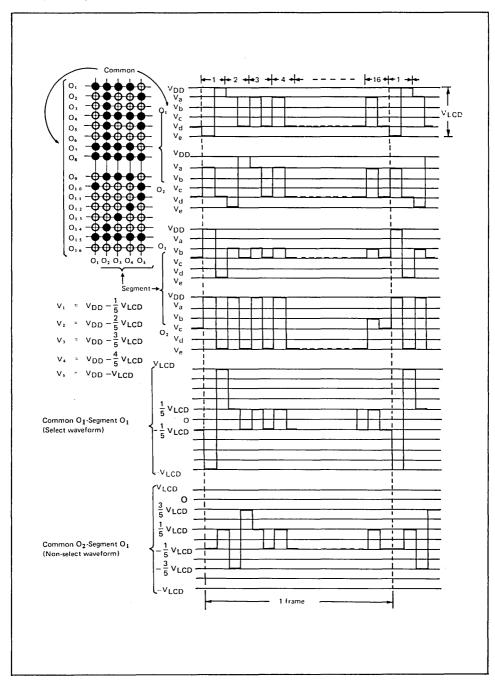

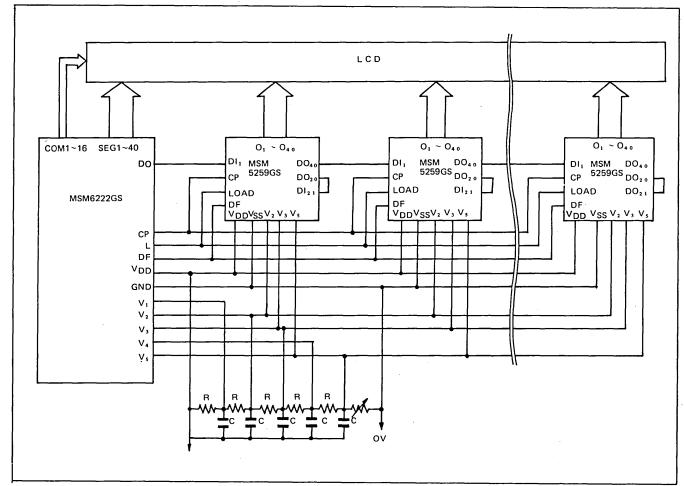

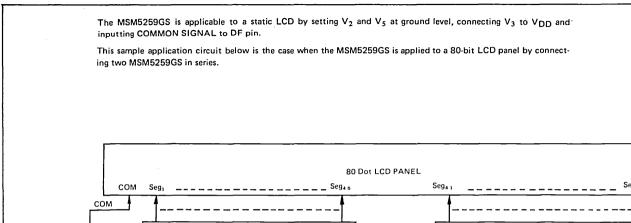

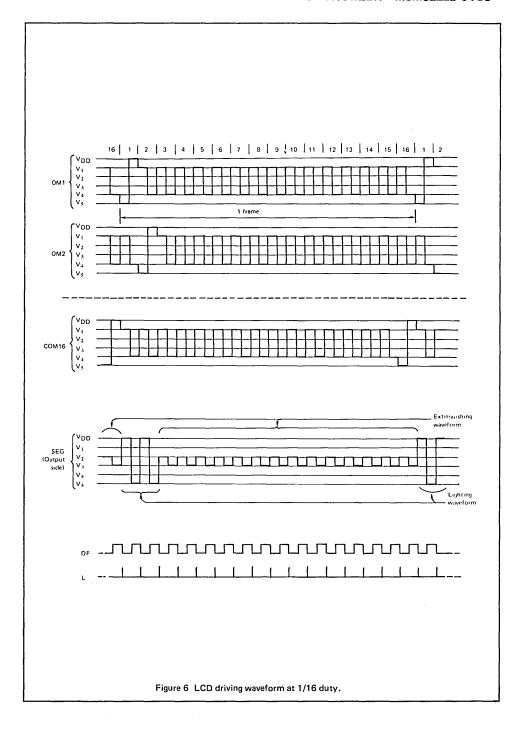

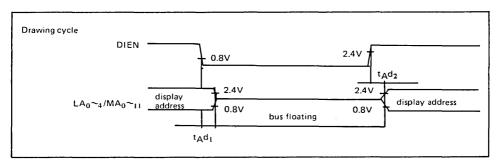

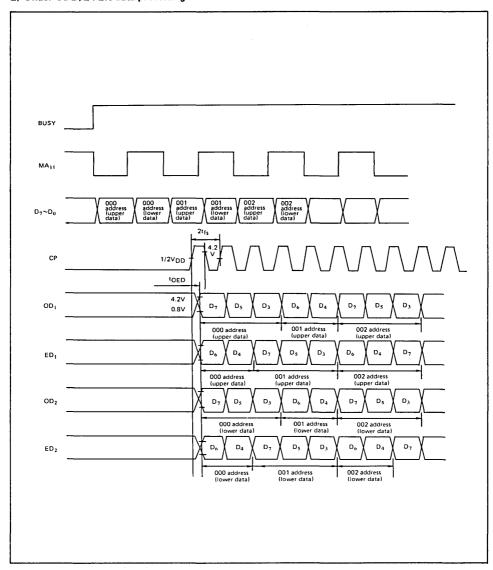

# **TIME CHART**

1/32 duty, 1/7 bias

# LCD DRIVING WAVEFORM

1/32 duty, 1/7 bias

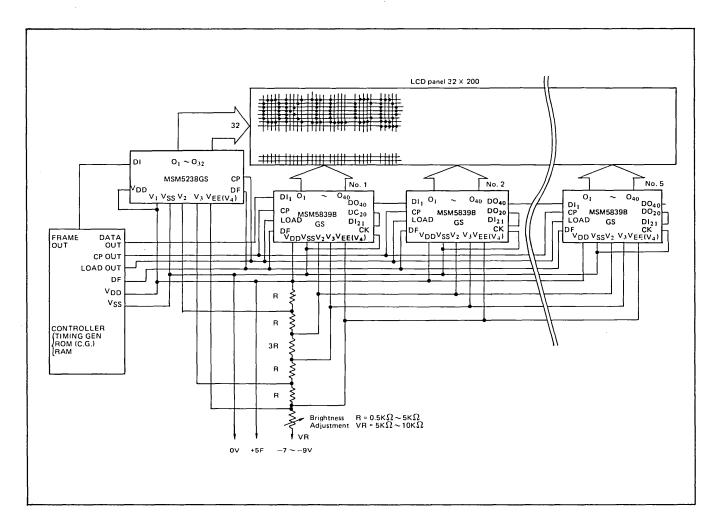

# **DOT MATRIX LCD 40 DOT SEGMENT DRIVER**

# **GENERAL DESCRIPTION**

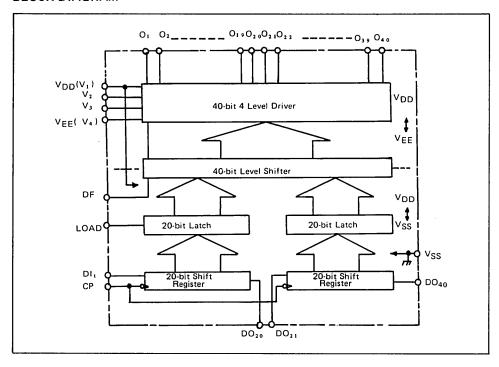

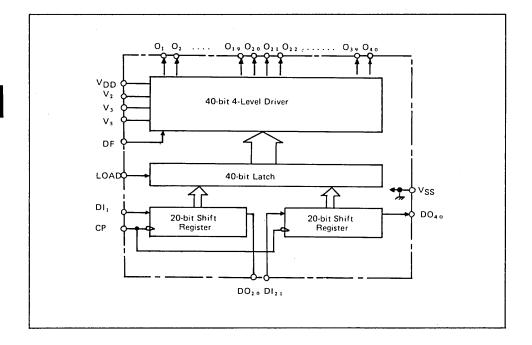

The OKI MSM5839BGS is a dot matrix LCD's segment driver LSI which is fabricated by low power CMOS metal gate technology. This LSI consists of 40-bit shift register (two 20-bit shift registers), 40-bit latch (two 20-bit latches), 40-bit level shifter and 40-bit 4-level driver.

It converts serial data, which is received from LCD controller LSI, to parallel data and outputs LCD driving waveform to the LCD panel.

This LSI can drive a variety of LCD panel because the bias voltage, which determines the LCD driving voltage, can be optionally supplied from the external source.

# **FEATURES**

- Supply voltage: 4.5 ~ 5.5V

- LCD driving voltage: 8 ~ 18V Applicable LCD duty: 1/8 ~ 1/128

- Bias voltage can be supplied externally

- 56 pin plastic flat package

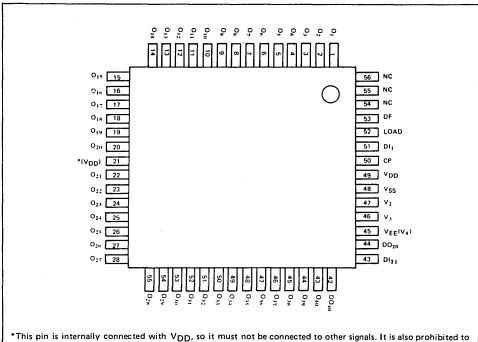

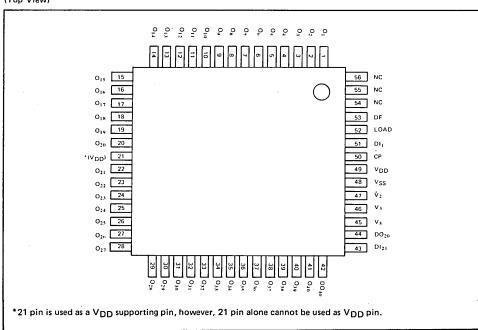

# PIN CONFIGURATION

(Top View)

use the 21 pin as a VDD independently. This pin may be used as a line reinforcing VDD.

# **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS

| Item                | Symbol                                 | Condition              | Value                        | Unit     |

|---------------------|----------------------------------------|------------------------|------------------------------|----------|

| Supply voltage (1)  | V <sub>DD</sub>                        | T <sub>a</sub> = 25°C  | -0.3 ~ 6                     | ٧        |

| S                   | V <sub>DD</sub> - V <sub>EE</sub> *1   | $T_a = 25^{\circ}C$    | 0~18                         | >        |

| Supply voltage (2)  | V <sub>DD</sub> - V <sub>EE*2</sub> *1 | T <sub>a = 25</sub> °C | 0~18                         | <b>v</b> |

| Input voltage       | V <sub>I</sub>                         | $T_a = 25^{\circ}C$    | -0.3 ~ V <sub>DD</sub> + 0.3 | ٧        |

| Storage temperature | T <sub>stg</sub>                       |                        | −55 ~+150                    | °c       |

$<sup>*1:</sup> V_{DD} > V_2 > V_3 > V_{EE}$

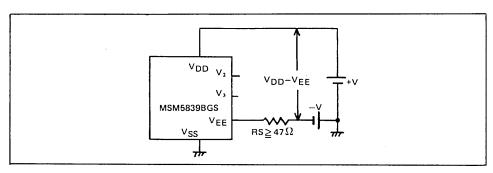

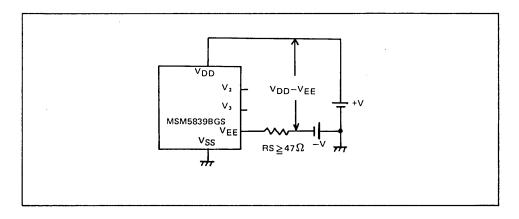

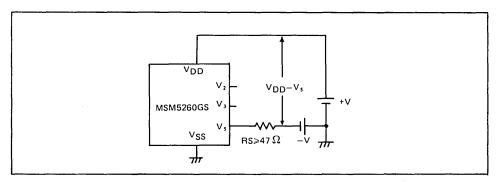

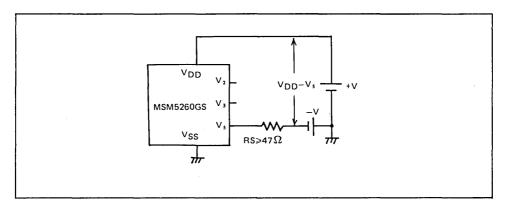

<sup>\*2 :</sup> When a series resistance of more than 47  $\Omega$  is connected as shown below.

# **OPERATING RANGE**

| Item                  | Symbol                                 | Condition | Limit             | Unit |

|-----------------------|----------------------------------------|-----------|-------------------|------|

| Supply voltage (1)    | V <sub>DD</sub>                        | _         | 4.5 ~ 5.5         | V    |

| Supply valtage (2)    | V <sub>DD</sub> - V <sub>EE</sub> *1   | _         | 8~16              | ٧    |

| Supply voltage (2)    | V <sub>DD</sub> - V <sub>EE*2</sub> *1 | -         | 8~18              | V    |

| Operating temperature | T <sub>op</sub>                        | _         | -20 <b>~</b> + 85 | °c   |

- $*1: V_{DD} > V_2 > V_3 > V_{EE}$

- \*2 : When a series resistance of more than 47 $\Omega$  is connected as shown below.

# D.C. CHARACTERISTICS

$(V_{DD} = 5V \pm 10\%, T_a = -20 \sim +85^{\circ}C)$

| Item               | Symbol             | Condition                                          | MIN                   | TYP | MAX                | Unit |

|--------------------|--------------------|----------------------------------------------------|-----------------------|-----|--------------------|------|

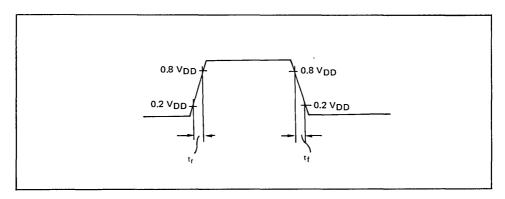

| "H" input voltage  | V <sub>IH</sub> *1 | _                                                  | 0.8V <sub>DD</sub>    | _   | _                  | ٧    |

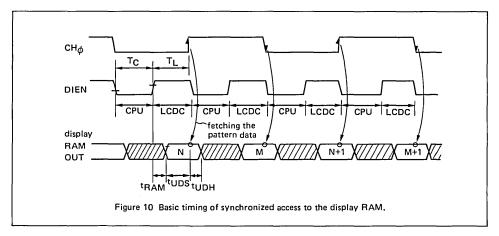

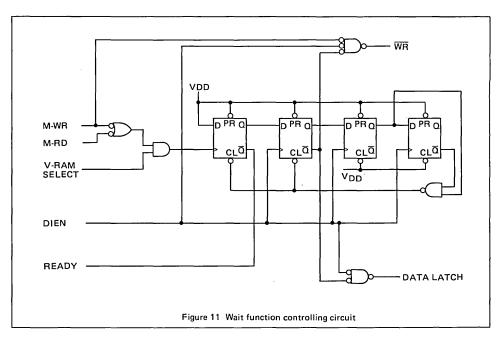

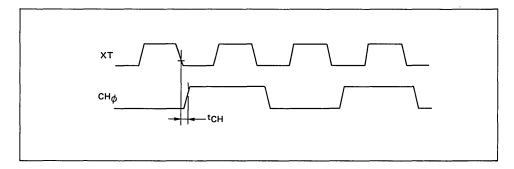

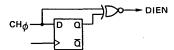

| "L" input voltage  | VIL*1              |                                                    | -                     | -   | 0.2V <sub>DD</sub> | ٧    |