# 386SX System Controller

### 1.0 Features

- · Flexible DRAM banks configuration

- Supports 256K, 1M and 4M DRAM

- · Block interleave mode operations

- Block interleaving at a block size of 512 bytes

- · BIOS shadow RAM

- Shadow RAM for system, video and adapter BIOS

- · Memory remapping

- · Flexible multiplexed DRAM address

- Programmable AT bus clock

- · Turbo switch

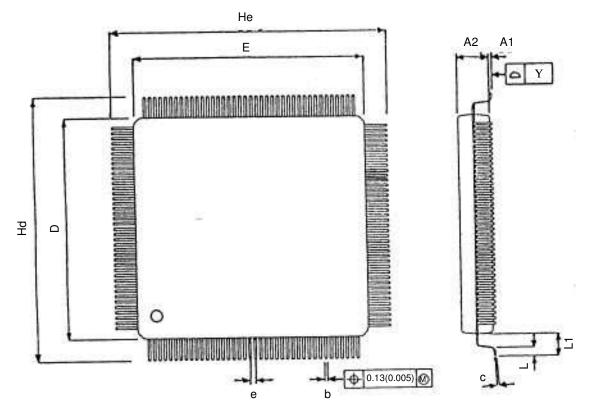

- 160-pin PQFP (Plastic Quad Flat Pack)

#### 2.0 Overview

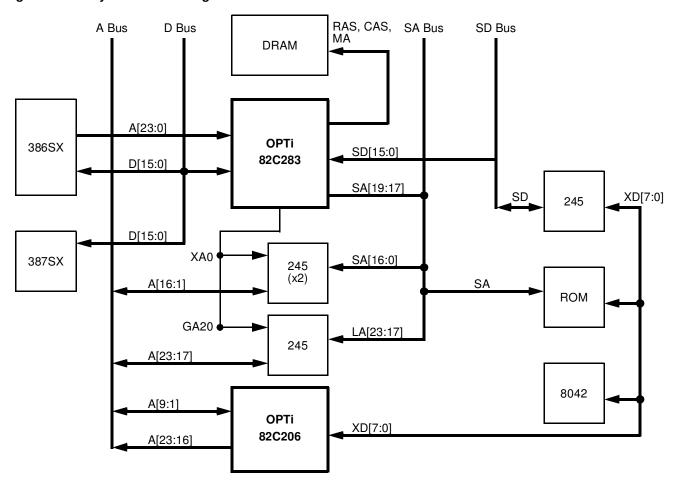

The 82C283 is a highly integrated, AT system logic VLSI chip for high-end 386SX/AT systems. It integrates a local memory controller (local memory is on-board memory), AT bus controller, and data bus controller into one chip. It is designed for systems running at 16MHz, 20MHz, 25MHz, and 33MHz\*. A high performance, compact 386SX/AT system is readily implemented with the 82C283 and a standard peripheral controller like OPTi's 82C206 or the 82C100 (with Dallas Semiconductor (DS1287).

\*Rev. B only

Figure 2-1 System Block Diagram

## 3.0 Signal Definitions

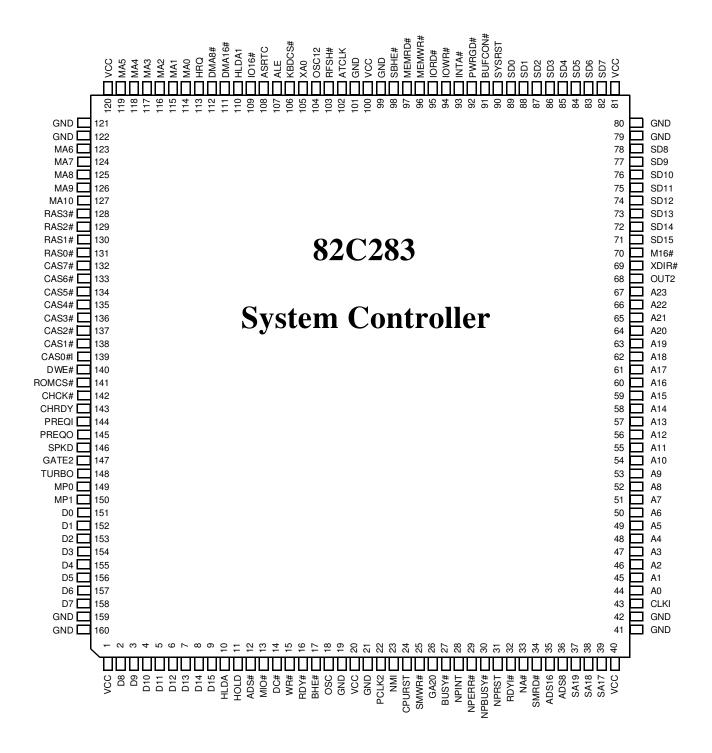

Figure 3-1 Pin Diagram

Page 2 912-3000-012

Table 3-1 Numerical Pin Cross-Reference List

| Pin No. | Pin Name |   |

|---------|----------|---|

| 1       | VCC      | Ī |

| 2       | D8       | Ī |

| 3       | D9       | Ī |

| 4       | D10      | Ī |

| 5       | D11      |   |

| 6       | D12      |   |

| 7       | D13      | Ī |

| 8       | D14      | Ī |

| 9       | D15      | Ī |

| 10      | HLDA     | Ī |

| 11      | HOLD     | Ī |

| 12      | ADS#     | Ī |

| 13      | MIO#     | Ī |

| 14      | DC#      | Ī |

| 15      | WR#      | Ī |

| 16      | RDY#     | Ī |

| 17      | BHE#     | Ī |

| 18      | OSC      |   |

| 19      | GND      | Ī |

| 20      | VCC      | Ī |

| 21      | GND      | Ī |

| 22      | PCLK2    | Ī |

| 23      | NMI      | Ī |

| 24      | CPURST   | Ī |

| 25      | SMWR#    | Ī |

| 26      | GA20     | Ī |

| 27      | BUSY#    | Ī |

| 28      | NPINT    | Ī |

| 29      | NPERR#   | Ī |

| 30      | NPBUSY#  | Ī |

| 31      | NPRST    | Ī |

| 32      | RDYI#    | Ī |

| 33      | NA#      | Ī |

| 34      | SMRD#    | Ī |

| 35      | ADS16    |   |

| 36      | ADS8     |   |

| 37      | SA19     |   |

| 38      | SA18     |   |

| 39      | SA17     |   |

| 40      | VCC      |   |

| Cross-Reference List |          |  |

|----------------------|----------|--|

| Pin No.              | Pin Name |  |

| 41                   | GND      |  |

| 42                   | GND      |  |

| 43                   | CLKI     |  |

| 44                   | A0       |  |

| 45                   | A1       |  |

| 46                   | A2       |  |

| 47                   | A3       |  |

| 48                   | A4       |  |

| 49                   | A5       |  |

| 50                   | A6       |  |

| 51                   | A7       |  |

| 52                   | A8       |  |

| 53                   | A9       |  |

| 54                   | A10      |  |

| 55                   | A11      |  |

| 56                   | A12      |  |

| 57                   | A13      |  |

| 58                   | A14      |  |

| 59                   | A15      |  |

| 60                   | A16      |  |

| 61                   | A17      |  |

| 62                   | A18      |  |

| 63                   | A19      |  |

| 64                   | A20      |  |

| 65                   | A21      |  |

| 66                   | A22      |  |

| 67                   | A23      |  |

| 68                   | OUT2     |  |

| 69                   | XDIR#    |  |

| 70                   | M16#     |  |

| 71                   | SD15     |  |

| 72                   | SD14     |  |

| 73                   | SD13     |  |

| 74                   | SD12     |  |

| 75                   | SD11     |  |

| 76                   | SD10     |  |

| 77                   | SD9      |  |

| 78                   | SD8      |  |

| 79                   | GND      |  |

| ۱ ۵۵                 | OND      |  |

80

GND

| Pin No. | Pin Name |

|---------|----------|

| 81      | VCC      |

| 82      | SD7      |

| 83      | SD6      |

| 84      | SD5      |

| 85      | SD4      |

| 86      | SD3      |

| 87      | SD2      |

| 88      | SD1      |

| 89      | SD0      |

| 90      | SYSRST   |

| 91      | BUFCON#  |

| 92      | PRWGD#   |

| 93      | INTA#    |

| 94      | IOWR#    |

| 95      | IORD#    |

| 96      | MEMWR#   |

| 97      | MEMRD#   |

| 98      | SBHE#    |

| 99      | GND      |

| 100     | VCC      |

| 101     | GND      |

| 102     | ATCLK    |

| 103     | RFSH#    |

| 104     | OSC12    |

| 105     | XA0      |

| 106     | KBDCS#   |

| 107     | ALE      |

| 108     | ASRTC    |

| 109     | IO16#    |

| 110     | HLDA1    |

| 111     | DMA16#   |

| 112     | DMA8#    |

| 113     | HRQ      |

| 114     | MA0      |

| 115     | MA1      |

| 116     | MA2      |

| 117     | MA3      |

| 118     | MA4      |

| 119     | MA5      |

| 120     | VCC      |

| Pin No. | Pin Name |

|---------|----------|

| 121     | GND      |

| 122     | GND      |

| 123     | MA6      |

| 124     | MA7      |

| 125     | MA8      |

| 126     | MA9      |

| 127     | MA10     |

| 128     | RAS3#    |

| 129     | RAS2#    |

| 130     | RAS1#    |

| 131     | RAS0#    |

| 132     | CAS7#    |

| 133     | CAS6#    |

| 134     | CAS5#    |

| 135     | CAS4#    |

| 136     | CAS3#    |

| 137     | CAS2#    |

| 138     | CAS1#    |

| 139     | CAS0#    |

| 140     | DWE#     |

| 141     | ROMCS#   |

| 142     | CHCK#    |

| 143     | CHRDY    |

| 144     | PREQI    |

| 145     | PREQO    |

| 146     | SPKD     |

| 147     | GATE2    |

| 148     | TURBO    |

| 149     | MP0      |

| 150     | MP1      |

| 151     | D0       |

| 152     | D1       |

| 153     | D2       |

| 154     | D3       |

| 155     | D4       |

| 156     | D5       |

| 157     | D6       |

| 158     | D7       |

| 159     | GND      |

| 160     | GND      |

Table 3-2 Alphabetical Pin Cross Reference List

| Pin Name | Pin No. |

|----------|---------|

| A0       | 44      |

| A1       | 45      |

| A2       | 46      |

| A3       | 47      |

| A4       | 48      |

| A5       | 49      |

| A6       | 50      |

| A7       | 51      |

| A8       | 52      |

| A9       | 53      |

| A10      | 54      |

| A11      | 55      |

| A12      | 56      |

| A13      | 57      |

| A14      | 58      |

| A15      | 59      |

| A16      | 60      |

| A17      | 61      |

| A18      | 62      |

| A19      | 63      |

| A20      | 64      |

| A21      | 65      |

| A22      | 66      |

| A23      | 67      |

| ADS#     | 12      |

| ADS8     | 36      |

| ADS16    | 35      |

| ALE      | 107     |

| ASRTC    | 108     |

| ATCLK    | 102     |

| BHE#     | 17      |

| BUFCON#  | 91      |

| BUSY#    | 27      |

| CAS0#    | 139     |

| CAS1#    | 138     |

| CAS2#    | 137     |

| CAS3#    | 136     |

| CAS4#    | 135     |

| CAS5#    | 134     |

|          | 1       |

| Pin Name | Pin No. |

|----------|---------|

| CAS7#    | 132     |

| CHCK#    | 142     |

| CHRDY    | 143     |

| CLKI     | 43      |

| CPURST   | 24      |

| D0       | 151     |

| D1       | 152     |

| D2       | 153     |

| D3       | 154     |

| D4       | 155     |

| D5       | 156     |

| D6       | 157     |

| D7       | 158     |

| D8       | 2       |

| D9       | 3       |

| D10      | 4       |

| D11      | 5       |

| D12      | 6       |

| D13      | 7       |

| D14      | 8       |

| D15      | 9       |

| DC#      | 14      |

| DMA8#    | 112     |

| DAM16#   | 111     |

| DWE#     | 140     |

| GA20     | 26      |

| GATE2    | 147     |

| GND      | 19      |

| GND      | 21      |

| GND      | 41      |

| GND      | 42      |

| GND      | 79      |

| GND      | 80      |

| GND      | 99      |

| GND      | 101     |

| GND      | 121     |

| GND      | 122     |

| GND      | 159     |

| GND      | 160     |

| HLDA     | 10      |

| HLDA1 110 HOLD 11 HRQ 113 INTA# 93 IO16# 109 IORD# 95 IOWR# 94 KBDCS# 106 M16# 70 MA0 114 MA1 115 MA2 116 MA3 117 MA4 118 MA5 119 MA6 123 MA7 124 MA8 125 MA9 126 MA10 127 MIO# 13 MP0 149 MP1 150 MEMRD# 97 MEMWR# 96 NA# 33 NMI 23 NPBUSY# 30 NPERR# 29 NPINT 28 NPRST 31 OSC 18 OSC12 104 OUT2 68 PCLK2 PREQI 144 PREQO 145 PRWGD# 92                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin Name | Pin No. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|

| HRQ 113 INTA# 93 IO16# 109 IORD# 95 IOWR# 94 KBDCS# 106 M16# 70 MA0 114 MA1 115 MA2 116 MA3 117 MA4 118 MA5 119 MA6 123 MA7 124 MA8 125 MA9 126 MA10 127 MIO# 13 MP0 149 MP1 150 MEMRD# 97 MEMWR# 96 NA# 33 NMI 23 NPBUSY# 30 NPERR# 29 NPINT 28 NPRST 31 OSC 18 OSC12 104 OUT2 68 PCLK2 22 PREQI 144 PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                      | HLDA1    | 110     |

| INTA# 93 IO16# 109 IORD# 95 IOWR# 94 KBDCS# 106 M16# 70 MA0 114 MA1 115 MA2 116 MA3 117 MA4 118 MA5 119 MA6 123 MA7 124 MA8 125 MA9 126 MA10 127 MIO# 13 MP0 149 MP1 150 MEMRD# 97 MEMWR# 96 NA# 33 NMI 23 NPBUSY# 30 NPERR# 29 NPINT 28 NPRST 31 OSC 18 OSC12 104 OUT2 68 PCLK2 22 PREQI 144 PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                              | HOLD     | 11      |

| IO16#       109         IORD#       95         IOWR#       94         KBDCS#       106         M16#       70         MA0       114         MA1       115         MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRD#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145 | HRQ      | 113     |

| IORD#       95         IOWR#       94         KBDCS#       106         M16#       70         MA0       114         MA1       115         MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRD#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                         | INTA#    | 93      |

| IOWR#       94         KBDCS#       106         M16#       70         MA0       114         MA1       115         MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                | IO16#    | 109     |

| KBDCS#       106         M16#       70         MA0       114         MA1       115         MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                       | IORD#    | 95      |

| M16#       70         MA0       114         MA1       115         MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRD#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                | IOWR#    | 94      |

| MA0       114         MA1       115         MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                      | KBDCS#   | 106     |

| MA1       115         MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                           | M16#     | 70      |

| MA2       116         MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRD#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                  | MA0      | 114     |

| MA3       117         MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                        | MA1      | 115     |

| MA4       118         MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                             | MA2      | 116     |

| MA5       119         MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                   | MA3      | 117     |

| MA6       123         MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                          | MA4      | 118     |

| MA7       124         MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMRWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                               | MA5      | 119     |

| MA8       125         MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                      | MA6      | 123     |

| MA9       126         MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                            | MA7      | 124     |

| MA10       127         MIO#       13         MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                  | MA8      | 125     |

| MIO# 13 MP0 149 MP1 150 MEMRD# 97 MEMWR# 96 NA# 33 NMI 23 NPBUSY# 30 NPERR# 29 NPINT 28 NPRST 31 OSC 18 OSC12 104 OUT2 68 PCLK2 22 PREQI 144 PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MA9      | 126     |

| MP0       149         MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                               | MA10     | 127     |

| MP1       150         MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                     | MIO#     | 13      |

| MEMRD#       97         MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                           | MP0      | 149     |

| MEMWR#       96         NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MP1      | 150     |

| NA#       33         NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MEMRD#   | 97      |

| NMI       23         NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MEMWR#   | 96      |

| NPBUSY#       30         NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NA#      | 33      |

| NPERR#       29         NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NMI      | 23      |

| NPINT       28         NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NPBUSY#  | 30      |

| NPRST       31         OSC       18         OSC12       104         OUT2       68         PCLK2       22         PREQI       144         PREQO       145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NPERR#   | 29      |

| OSC 18 OSC12 104 OUT2 68 PCLK2 22 PREQI 144 PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NPINT    | 28      |

| OSC12 104 OUT2 68 PCLK2 22 PREQI 144 PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NPRST    | 31      |

| OUT2 68 PCLK2 22 PREQI 144 PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OSC      | 18      |

| PCLK2         22           PREQI         144           PREQO         145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OSC12    | 104     |

| PREQI 144<br>PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OUT2     | 68      |

| PREQO 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PCLK2    | 22      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PREQI    | 144     |

| PRWGD# 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PREQO    | 145     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PRWGD#   | 92      |

| RAS0# 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RAS0#    | 131     |

| RAS1# 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RAS1#    | 130     |

| Pin Name | Pin No. |

|----------|---------|

| RAS2#    | 129     |

| RAS3#    | 128     |

| RDY#     | 16      |

| RDYI#    | 32      |

| RFSH#    | 103     |

| ROMCS#   | 141     |

| SA19     | 37      |

| SA18     | 38      |

| SA17     | 39      |

| SBHE#    | 98      |

| SD0      | 89      |

| SD1      | 88      |

| SD2      | 87      |

| SD3      | 86      |

| SD4      | 85      |

| SD5      | 84      |

| SD6      | 83      |

| SD7      | 82      |

| SD8      | 78      |

| SD9      | 77      |

| SD10     | 76      |

| SD11     | 75      |

| SD12     | 74      |

| SD13     | 73      |

| SD14     | 72      |

| SD15     | 71      |

| SMRD#    | 34      |

| SMWR#    | 25      |

| SPKD     | 146     |

| SYSRST   | 90      |

| TURBO    | 148     |

| VCC      | 1       |

| VCC      | 20      |

| VCC      | 40      |

| VCC      | 81      |

| VCC      | 100     |

| VCC      | 120     |

| WR#      | 15      |

| XDIR#    | 69      |

| XA0      | 105     |

Page 4 912-3000-012

# 3.1 Signal Descriptions

## 3.1.1 Clock and Reset Interface Signals

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                        |

|-------------|---------|----------------|---------------------------------------------------------------------------|

| CLKI        | 43      | I              | CLK2 input from oscillator.                                               |

| PCLK2       | 22      | I/O            | CLK2 output to 386SX and 387SX. (Bidirectional output is always enabled.) |

| OSC12       | 104     | 0              | 1.19MHz output.                                                           |

| OSC         | 18      | I              | 14.31818MHz oscillator input.                                             |

### 3.1.2 CPU Control and Interface Signals

| Signal Name | Pin No.         | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                     |

|-------------|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[23:17]    | 67:61           | I              | CPU Address Bus: Address lines 23 through 17 and 7 through 0.                                                                                                                                                                                                                          |

| A[16:8]     | 60:52           | I/O            | CPU Address Bus: Address lines 16 through 8. These signals are inputs except during DMA cycles. A[16:9] become outputs and convey DMA address 16-9 for 16-bit DMA cycles. A[15:8] become outputs and convey DMA address 15-8 for 8-bit DMA cycles. A[10:9] are outputs during refresh. |

| A[7:0]      | 51:44           | I/O            | CPU Address Bus: Address lines 7 through 0. These inputs become outputs during refresh.                                                                                                                                                                                                |

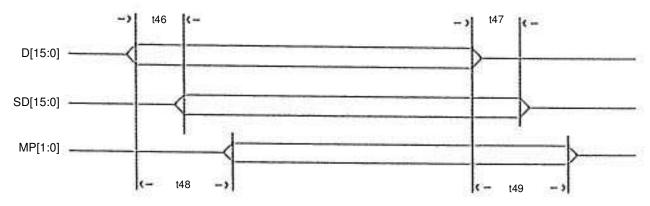

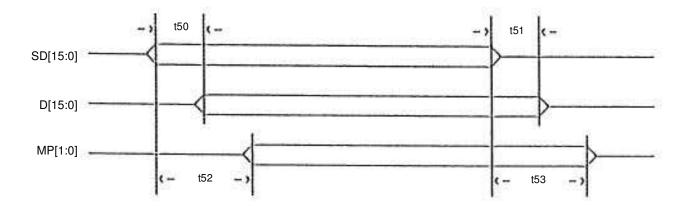

| D[15:0]     | 9:2,<br>158:151 | I/O            | Data bus to/from the CPU.                                                                                                                                                                                                                                                              |

| MP[1:0]     | 150, 149        | I/O            | Local DRAM parity bits 1 and 0.                                                                                                                                                                                                                                                        |

| RDYI#       | 32              | I              | Ready input from coprocessor Ready.                                                                                                                                                                                                                                                    |

| RDY#        | 16              | 0              | Ready output to the CPU to terminate the current cycle.                                                                                                                                                                                                                                |

| NA#         | 33              | 0              | CPU next address control signal.                                                                                                                                                                                                                                                       |

| CPURST      | 24              | 0              | CPU reset signal.                                                                                                                                                                                                                                                                      |

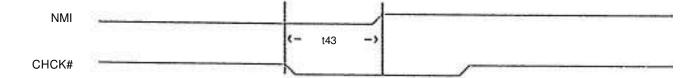

| NMI         | 23              | 0              | Non-maskable interrupt.                                                                                                                                                                                                                                                                |

| WR#         | 15              | I              | Write or Read is a bus cycle definition pin that distinguishes write cycles from reads cycles.                                                                                                                                                                                         |

| DC#         | 14              | I              | Data or Control is a bus cycle definition pin that distinguishes data cycles from control cycles.                                                                                                                                                                                      |

| MIO#        | 13              | I              | Memory or I/O is a bus cycle definition pin that distinguishes memory cycles from input/output cycles.                                                                                                                                                                                 |

| ADS#        | 12              | I              | Address status from the 386SX.                                                                                                                                                                                                                                                         |

| HOLD        | 11              | 0              | Hold request to the 386SX                                                                                                                                                                                                                                                              |

| HLDA        | 10              | I              | Hold acknowledge from the 286SX.                                                                                                                                                                                                                                                       |

| BHE#        | 17              | I/O            | Byte high enable from the CPU. It is an input during CPU cycles and an output during non-CPU cycles.                                                                                                                                                                                   |

# Signal Descriptions (Cont.)

### 3.1.3 DRAM Interface Signals

| Signal Name | Pin No.             | Signal<br>Type | Signal Description                                    |

|-------------|---------------------|----------------|-------------------------------------------------------|

| RAS[3:0]#   | 128:131             | 0              | Local DRAM row address strobe signals.                |

| CAS[7:0]#   | 132:139             | I              | Local DRAM column address strobe signals.             |

| MA[10:0]    | 127:123,<br>119:114 | 0              | Multiplexed row and column address bits 10 through 0. |

| RFSH#       | 103                 | I/O            | Refresh cycle indication signal.                      |

| DWE#        | 140                 | 0              | DRAM write/read control signal.                       |

### 3.1.4 AT Bus Interface Signals

| Signal Name | Pin No.         | Signal<br>Type | Signal Description                                                                                                                               |

|-------------|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE         | 107             | Т              | At bus address latch enable. This signal is tristated during master cycles.                                                                      |

| XA0         | 105             | I/O            | System board latched address bit 0. This signal is an output for CPU, refresh, or 16-bit DMA cycles and an input for 8-bit DMA or master cycles. |

| ATCLK       | 102             | 0              | AT system clock, ATCLK = CLK2/6 (default), ATCLK can be set to CLK2/4 by programming the internal registers.                                     |

| SBHE#       | 98              | I/O            | System byte high enable to/from the AT bus. SBHE# is an input during master cycles.                                                              |

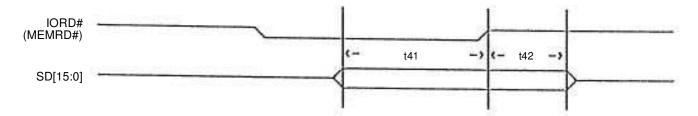

| MEMRD#      | 97              | I/O            | Memory read command signal.                                                                                                                      |

| MEMWR#      | 96              | I/O            | Memory write command signal.                                                                                                                     |

| IORD#       | 95              | I/O            | I/O read command signal.                                                                                                                         |

| IOWR#       | 94              | I/O            | I/O write command signal.                                                                                                                        |

| CHRDY       | 143             | 1              | I/O channel ready signal from the AT channel.                                                                                                    |

| IO16#       | 109             | I              | I/O data size 16 indication from AT channel.                                                                                                     |

| M16#        | 70              | I/O            | Memory data size 16 indication from the AT channel.                                                                                              |

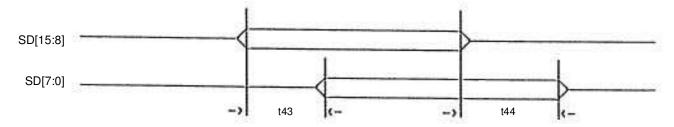

| CHCK#       | 142             | I              | Channel Check signal from the AT channel.                                                                                                        |

| SA[19:17]   | 37:39           | 0              | System address lines 19 through 17. Tristated during master cycles.                                                                              |

| SMRD#       | 34              | 0              | AT memory read command to memory below 1MB.                                                                                                      |

| SMWR#       | 25              | 0              | AT memory write command to memory below 1MB                                                                                                      |

| SD[15:0]    | 71:78,<br>82:89 | I/O            | System data bus lines 15 through 0. These signals are connected to AT data bus directly.                                                         |

Page 6 912-3000-012

## Signal Descriptions (Cont.)

### 3.1.5 DMA Interface Signals

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                   |

|-------------|---------|----------------|--------------------------------------------------------------------------------------|

| DMA8#       | 112     | I              | 8-bit DMA transfer indication.                                                       |

| DMA16#      | 111     | I              | 16-bit DMA transfer indication.                                                      |

| HRQ         | 113     | I              | Hold request from the 82C206 IPC.                                                    |

| HLDA1       | 110     | 0              | Hold acknowledge 1 indicates a CPU HLDA was caused by HRQ, not by a refresh request. |

| ADS8        | 36      | I              | 8-bit DMA transfer address strobe.                                                   |

| ADS16       | 35      | I              | 16-bit DMA transfer address strobe.                                                  |

### 3.1.6 Miscellaneous Interface Signals

|             |         |                | <del>-</del>                                                                                                                 |  |

|-------------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------|--|

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                                                           |  |

| KBDCS#      | 106     | 0              | I/O Port 60 and 64 Address decode. It is de-activated during DMA cycles.                                                     |  |

| TURBO       | 148     | I              | Turbo switch control. CPUCLK2 = ATCLK2 if TURBO pin is low when turbo switch function is enabled.                            |  |

| GATE2       | 147     | 0              | Timer 2 enable signal.                                                                                                       |  |

| SPKD        | 146     | 0              | Speaker output.                                                                                                              |  |

| INTA#       | 93      | 0              | Interrupt acknowledge cycle indication.                                                                                      |  |

| PWRGD#      | 92      | 1              | Power bad indication.                                                                                                        |  |

| SYSRST      | 90      | 0              | System reset signal.                                                                                                         |  |

| ROMCS#      | 141     | 0              | BIOS ROM output enable signal                                                                                                |  |

| GA20        | 26      | I/O            | Gate Address 20. It is an input from master card during master cycles. Connected to AT bus LA20 indirectly through a buffer. |  |

| XDIR#       | 69      | 0              | XD bus to/from SD bus direction control.                                                                                     |  |

| ASRTC       | 108     | 0              | Address strobe for real-time clock.                                                                                          |  |

| BUFCON#     | 91      | 0              | Buffer control signal. BUFCON# goes low during a master and non-refresh cycle.                                               |  |

| OUT2        | 68      | I              | Timer 2 output.                                                                                                              |  |

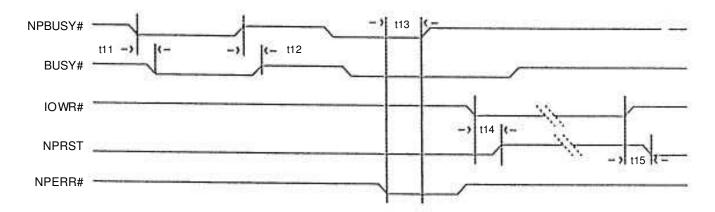

### 3.1.7 Numeric Coprocessor Interface Signals

| Signal Name | Pin No. | Signal<br>Type | Signal Description                |

|-------------|---------|----------------|-----------------------------------|

| NPBUSY#     | 30      | I              | Numeric coprocessor busy signal.  |

| NPERR#      | 29      | 1              | Numeric coprocessor error signal. |

| NPRST       | 31      | 0              | Numeric coprocessor reset.        |

**OPTi**

# Signal Descriptions (Cont.)

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                           |

|-------------|---------|----------------|--------------------------------------------------------------|

| NPINT       | 28      | 0              | Interrupt request 13 for 387SX exception.                    |

| BUSY#       | 27      | 0              | Numeric coprocessor busy and error status to CPU busy input. |

| PREQO       | 145     | 0              | Connected to the 386SX PREQ input.                           |

| PREQI       | 144     | I              | Connected to the 387SX PREQ output.                          |

### 3.1.8 Power and Ground Pins

| Signal Name | Pin<br>No.                                                      | Signal<br>Type | Signal Description      |

|-------------|-----------------------------------------------------------------|----------------|-------------------------|

| VCC         | 1, 20, 40,<br>81, 100,<br>120                                   | I              | Power connection: +5.0V |

| GND         | 19, 21, 41,<br>42, 79, 80,<br>99, 101,<br>121, 122,<br>159, 160 | I              | Ground connection       |

Page 8 912-3000-012

### 4.0 Functional Description

The following sub-sections will explain the various cycles, features, and operations of the 82C283.

### 4.1 Local Memory Controller

The 82C283 memory controller has the following features:

- Flexible DRAM banks configuration The 82C283 supports 256K, 1M, and 4M size DRAM. Total memory can be up to 16MB. Twelve memory configurations are supported as shown in Table 4-1.

- Block interleave mode operations Depending on the memory configuration, the local memory controller unit performs block interleaving at a block size of 512 bytes using 256K, 1M or 4M DRAMs.

- BIOS shadow RAM The local memory controller can shadow RAM for system BIOS, video BIOS, and adapter BIOS.

- 0F0000h-0FFFFFh is system BIOS area and can be programmed to be:

- Read during AT ROM cycles; written during local memory cycles (default).

- Read during local memory cycles with no writes allowed (write-protected).

- 0C000h-0EFFFFh contains twelve 16KB blocks, each programmable:

- Read from AT bus; write to AT bus (default).

- Read from AT bus; write to local memory.

- Read from local memory; write to local memory.

- Read from local memory and write protected.

- Memory remapping If shadow RAM is not used at memory area 0D0000h-0EFFFFh, remapping is possible. Then, local memory areas 0A0000h-0BFFFFh and 0D0000h-0EFFFFh (each 128K bytes) are mapped to the top of total memory. Memory areas 0F0000h-0FFFFFh (system BIOS) and 0C0000h-0CFFFFh (video BIOS) are reserved for shadow RAM.

- Flexible multiplexed DRAM address Table 4-2 shows how DRAM address lines are multiplexed when different size DRAM are used.

Table 4-1 DRAM Banks Configurations

| Bank 0 | Bank 1 | Bank 2 | Bank 3 | Total |

|--------|--------|--------|--------|-------|

| 256K   | 256K   |        |        | 1M    |

| 256K   | 256K   | 256K   | 256K   | 2M    |

| 1M     |        |        |        | 2M    |

| 256K   | 256K   | 1M     |        | ЗМ    |

| 1M     | 1M     |        |        | 4M    |

| 256K   | 256K   | 1M     | 1M     | 5M    |

| 1M     | 1M     | 1M     |        | 6M    |

| 1M     | 1M     | 1M     | 1 M    | 8M    |

| 256K   | 256K   | 4M     |        | 9M    |

| 1M     | 4M     |        |        | 10M   |

| 1M     | 1M     | 4M     |        | 12M   |

| 4M     | 4M     |        |        | 16M   |

| 4M*    |        |        |        | 8M    |

<sup>\*</sup>Rev. B only

Table 4-2 Address to MA Mapping

| Memory  | 25  | 6K  | 1   | М   | 4M  |     |

|---------|-----|-----|-----|-----|-----|-----|

| Address | Col | Row | Col | Row | Col | Row |

| 0       | 1   | 11  | 1   | 20  | 1   | 20  |

| 1       | 2   | 12  | 2   | 11  | 2   | 22  |

| 2       | 3   | 13  | 3   | 12  | 3   | 12  |

| 3       | 4   | 14  | 4   | 13  | 4   | 13  |

| 4       | 5   | 15  | 5   | 14  | 5   | 14  |

| 5       | 6   | 16  | 6   | 15  | 6   | 15  |

| 6       | 7   | 17  | 7   | 16  | 7   | 16  |

| 7       | 8   | 18  | 8   | 17  | 8   | 17  |

| 8       | 10  | 19  | 10  | 18  | 10  | 18  |

| 9       |     |     | 9   | 19  | 9   | 19  |

| 10      |     |     |     |     | 11  | 21  |

#### 4.2 AT Bus Controller

The AT bus controller handles all of the AT bus operations and DMA/refresh arbitration. The controller has the following features:

- Programmable AT bus clock The AT bus clock, ATCLK, is selectable from either CLK2/6 (default) or CLK2/4.

- Turbo switch The 82C283 has a turbo switch feature allowing users to change the system clock speed. Setting Register 14h, bit 1 high (to 1), enables the turbo function, whereupon the 82C283 TURBO pin selects the system clock speed as follows:

- A low on the TURBO pin causes the CPU to run at the current at bus speed (either CLK2/6 or CLK2/4).

- A high on the TURBO pin causes the CPU to run at 16, 20 or 25MHz.

- If the keyboard controlled turbo switching is desired, the TURBO pin should be kept low and the turbo configuration bit should be toggled.

### 4.3 SX/AT System Operation

The detailed operation of an 82C283-based SX/AT system design is described in the following sub-sections.

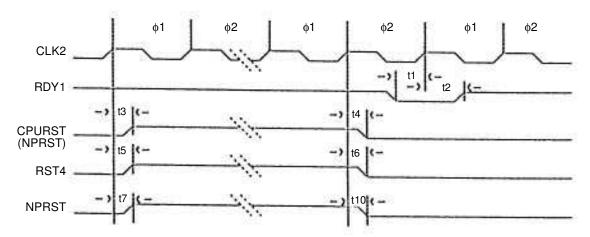

#### 4.3.1 Reset

The power supply's power good (PWRGD#) signal initializes the system when PWRGD# goes low. The 82C283 forces CPURST, NPRST high and SYSRST# low, then negates these signals 128 CLK2 cycles after PWRGD# goes high.

#### 4.3.2 Local DRAM Interfaces

Local memory (DRAM) is located on the CPU local data bus. The CPU reads data directly from local memory. Local memory latches CPU write data on the leading edge of CAS#. The memory controller asserts M16# when external master cards read local memory, and asserts DWE# when they write local memory.

For parity control, the memory controller reads the requested byte(s) and checks parity; during local memory writes, the data bus control unit generates parity, to be stored in local memory.

#### 4.3.3 System BIOS ROM

If the system BIOS ROM is not shadowed, ROM cycles are treated as AT cycles. 8-bit BIOS ROM resides on the XD bus and 16-bit BIOS ROM on the SD bus. With 16-bit ROM, ROMCS# is connected to M16# through an open collector (a driver such as a 7407), allowing the 82C283 to determine the width of the ROM data path by monitoring M16#.

#### 4.3.4 I/O Ports Located on the XD Bus

XDIR# controls the direction of I/O ports on the XD bus. Not that I/O ports 0F0h-0FFh are reserved for the coprocessor.

#### 4.3.5 Refresh Cycles

The AT bus controller arbitrates between the 82C206 hold request (HRQ) and the 82C283 refresh request, to determine who receives bus control when the CPU relinquishes it. The bus controller grants refresh requests once every 15.9µs (regular refresh) or once every 63.6µs (slow refresh). During refresh, the AT bus controller asserts RFSH# and MEMRD# and generates the refresh address.

#### 4.3.6 DMA Cycles

HRQ initiates a DMA/master transfer. When the 82C283 selects DMA (via the HRQ input) over the refresh request, after the CPU acknowledges by asserting HLDA, then the 82C283 sends HLDA1 to the 82C206 to acknowledge the request. The 82C206 asserts DMA16# and activates ADS16# to start 16-bit DMA transfers, or asserts DMA8# and activates ADS8# to start 8-bit DMA transfers.

Page 10 912-3000-012

## 5.0 Configuration Registers

There are seven Configuration Registers inside the 82C283. An indexing scheme is used to access all of these registers. Port 22h is used as the Index Register and Port 24h is the Data Register. Each access to a Configuration Register consists of a write to Port 22h, specifying the desired register in the data byte, followed by a read or write to Port 24h with the

actual register data. The index resets after every access; therefore every data access (via Port 24h) must be preceded by a write to Port 22h, even if the same register is being accessed on consecutive occasions. All reserved bits are set to zero by default.

Table 5-1 DRAM Configuration Register - Index 10h

| Bit(s) | Туре | Default | Function                                                                       |                                                                          |                                                                                    |                                    |                |                                                              |

|--------|------|---------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------|----------------|--------------------------------------------------------------|

| 7      | RO   | 0       | 82C283                                                                         | revision                                                                 | number:                                                                            |                                    |                |                                                              |

|        |      |         | 0 = Rev                                                                        | ision A                                                                  |                                                                                    |                                    | 1 = Rev        | vision B                                                     |

| 6      | R/W  | 0       | Revisio                                                                        | ed - Must                                                                | -                                                                                  | 0.                                 | 1 = Pipe       | elined                                                       |

| 5      | R/W  | 1       |                                                                                | RAM read                                                                 |                                                                                    | ait state:                         |                |                                                              |

|        |      |         |                                                                                | wait sta                                                                 |                                                                                    |                                    | 1 = One        | e wait state                                                 |

| 4      | R/W  | 1       | Local D                                                                        | RAM writ                                                                 | e cycle w                                                                          | ait state:                         |                |                                                              |

|        |      |         | 0 = Zero                                                                       | wait sta                                                                 | te                                                                                 |                                    | 1 = One        | e wait state                                                 |

| 3:0    | R/W  | 1111    | Local D                                                                        | RAM mer                                                                  | nory conf                                                                          | figuration                         | :              |                                                              |

|        |      |         | Bits 1111 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100* *Rev. B | 256K<br>256K<br>256K<br>256K<br>256K<br>1M<br>1M<br>1M<br>1M<br>1M<br>4M | Bank 1<br>256K<br>256K<br>256K<br>256K<br>256K<br>1M<br>1M<br>1M<br>4M<br>1M<br>4M | 256K<br>1M<br>1M<br>4M<br>1M<br>4M | Bank 3 256K 1M | Total  1M  2M  3M  5M  9M  2M  4M  6M  8M  10M  12M  16M  8M |

Table 5-2 Shadow RAM Control Register - Index 11h

| Bit(s) | Туре | Default | Function                                                                                                                                                                     |

|--------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | R/W  | 1       | Shadow RAM enable for system BIOS ROM at F0000h-FFFFFh:                                                                                                                      |

|        |      |         | 0 = Read only from shadow RAM<br>1 = Reads go to ROM and writes go to shadow RAM                                                                                             |

| 6      | R/W  | 1       | Adaptor ROM located at E0000h-EFFFFh:                                                                                                                                        |

|        |      |         | 0 = All accesses are to system board ROM, shadow RAM is disabled 1 = Shadow RAM is selectively enabled in 16KB blocks by CFG register 12h; other accesses are AT bus cycles. |

| 5      | R/W  | 1       | ROM located at D0000h-DFFFFh:                                                                                                                                                |

|        |      |         | 0 = All accesses are on AT bus and shadow RAM is disabled 1 = Shadow RAM is selectively enabled in 16KB blocks by CFG register 12h; other accesses are AT bus cycles.        |

| 4      | R/W  | 1       | ROM located at C0000h-CFFFFh:                                                                                                                                                |

|        |      |         | 0 = All accesses are on AT bus and shadow RAM is disabled 1 = Shadow RAM is selectively enabled in 16KB blocks by CFG register 13h; other accesses are AT bus cycles.        |

| 3      | R/W  | 0       | Shadow RAM copy enable control for C0000h-EFFFFh:                                                                                                                            |

|        |      |         | 0 = Write to AT bus<br>1 = Write to local DRAM                                                                                                                               |

| 2:0    | R/W  | 000     | Shadow RAM AT X0000h-XFFFFh read/write status:                                                                                                                               |

|        |      |         | 0 = Read/write 1 = Read only (While shadow RAM is being loaded, this bit must be set to 0; after shadow RAM is loaded, setting this bit to 1 write-protects shadow RAM.)     |

|        |      |         | Bit 2 = E0000h -EFFFFh  Bit 1 = D0000h-DFFFFh  Bit 0 = C0000h-CFFFFh                                                                                                         |

### Table 5-3 Shadow RAM Control Register - Index 12h

| Bit(s) | Туре | Default      | Function                                                                                                                                                                |                                                                                                  |  |  |  |  |

|--------|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| 7:0    | R/W  | 0000<br>0000 | This register selectively enables shadow RAM in 16KB blocks from D0000h-EFFFFh. This and the Shadow RAM Register (Index 11h) implement full system selective shadowing. |                                                                                                  |  |  |  |  |

|        |      |              | Shadow RAM for XX000h-XXFFFh segments:                                                                                                                                  |                                                                                                  |  |  |  |  |

|        |      |              | 0 = Disable                                                                                                                                                             | 1 = Enable                                                                                       |  |  |  |  |

|        |      |              | Bit 7 = EC000h-EFFFFh<br>Bit 6 = E8000h-EBFFFh<br>Bit 5 = E4000h-E7000h<br>Bit 4 = E0000h-E3FFFh                                                                        | Bit 3 = DC000h-DFFFFh<br>Bit 2 = D8000h-D8FFFh<br>Bit 1 = D4000h-D7FFFh<br>Bit 0 = D0000h-D3FFFh |  |  |  |  |

Page 12 912-3000-012

Table 5-4 Shadow RAM Control Register - Index 13h

| Bit(s) | Туре | Default | Function |         |                    |         |                                                                                               |  |

|--------|------|---------|----------|---------|--------------------|---------|-----------------------------------------------------------------------------------------------|--|

| 7:4    | R/W  | 0000    | Shado    | w RAM f | or CX000           | h-CXFFF | h segments:                                                                                   |  |

|        |      |         | 0 = Dis  | sable   |                    |         | 1 = Enable                                                                                    |  |

|        |      |         |          |         | -CFFFFh<br>-CBFFFh |         | Bit 5 = C4000h-C7000h<br>Bit 4 = C0000h-C3FFFh                                                |  |

| 3:0    | R/W  | 0000    |          |         |                    |         | ow RAM. Remaps A0000h-BFFFFh and D0000h-EFFFFh if ough 0 correspond to Address 23 through 20. |  |

|        |      |         | A23      | A22     | A21                | A20     | Remap Address                                                                                 |  |

|        |      |         | 0        | 0       | 0                  | 0       | No mapping                                                                                    |  |

|        |      |         | 0        | 0       | 0                  | 1       | 1MB                                                                                           |  |

|        |      |         | 0        | 0       | 1                  | 0       | 2MB                                                                                           |  |

|        |      |         | 0        | 0       | 1                  | 1       | 3MB                                                                                           |  |

|        |      |         | 0        | 1       | 0                  | 0       | 4MB                                                                                           |  |