# **82C842**IEEE 1394 Physical Layer Controller

# **Preliminary Data Book**

OPTi Inc. is a member of the 1394 Trade Association

i.LINK compatible

Revision: 1.0 912-2000-024 February 05, 1999

#### Copyright

Copyright © 1998, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Inc., 1440 McCarthy Blvd., Milpitas, CA 95035.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

1440 McCarthy Blvd. Milpitas, CA 95035 Tel: (408) 486-8000

Fax: (408) 486-8001 WWW: http://www.opti.com/

# **Table of Contents**

| Features                             | 1  |

|--------------------------------------|----|

| Signal Definitions                   | 3  |

| Terminology/Nomenclature Conventions |    |

| TriFire Strapping Options            |    |

| Signal Descriptions                  | g  |

| Functional Description               | 11 |

| Self-Loopback Test, Mode 4           | 11 |

| TriFire Register Space               | 18 |

| Register Pages                       | 13 |

| Electrical Ratings                   | 23 |

| Absolute Maximum Ratings             | 23 |

| Operating Conditions                 | 23 |

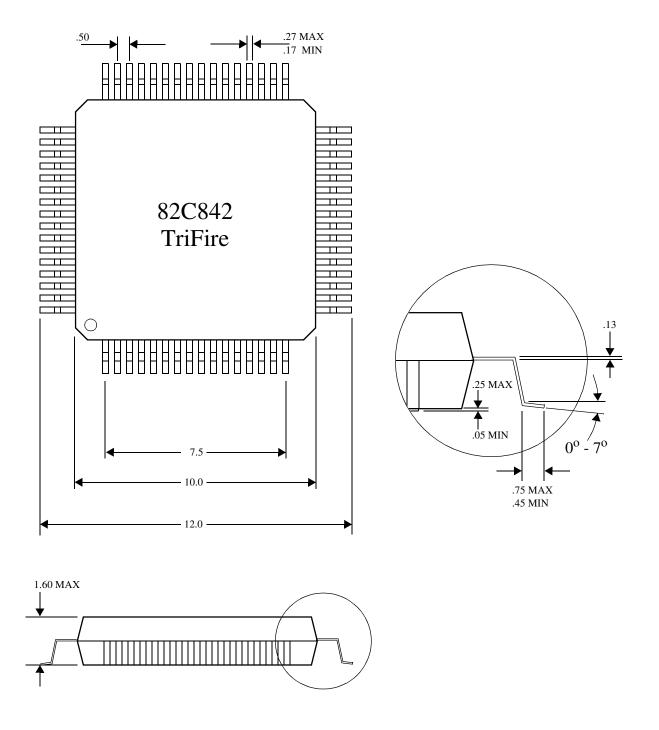

| Mechanical Package Outlines          | 27 |

Page iv 912-2000-024

Revision: 1.0

# **List of Tables**

| Signal Definitions Legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ?   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TriFire Pin Cross-Reference List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Mode 2 User Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Mode 3 User Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 112000 C C C C P 11 C P | ••• |

Page vi 912-2000-024 Revision: 1.0

# **List of Figures**

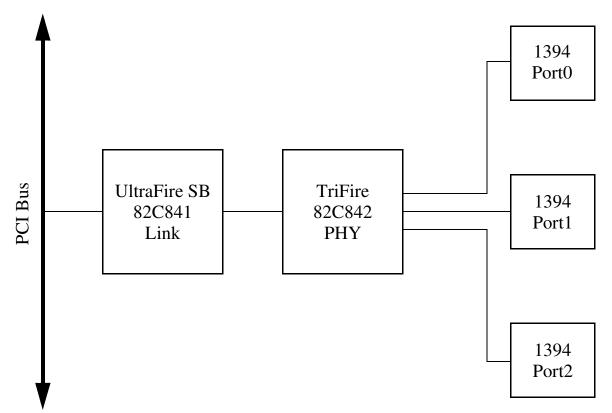

| TriFire System Block Diagram                        |  |

|-----------------------------------------------------|--|

| TriFire Functional Block Diagram                    |  |

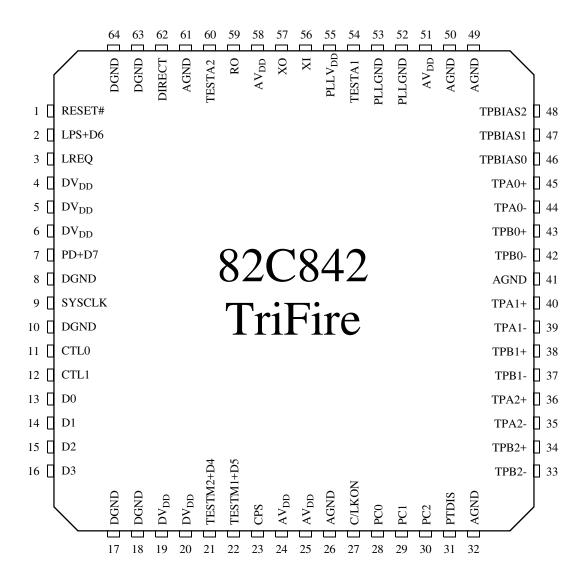

| TriFire Pin Diagram                                 |  |

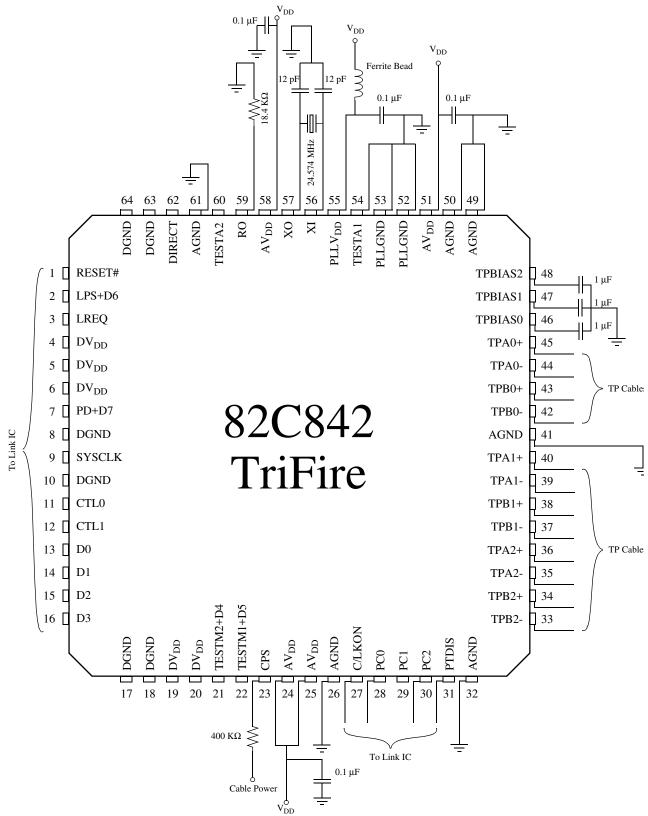

| TTriFire System Implementation Diagram              |  |

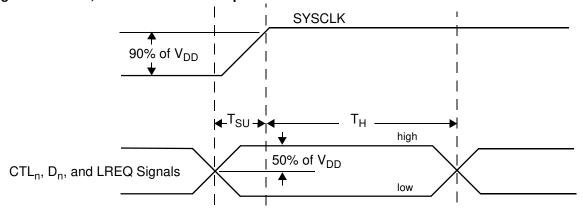

| Dn, CTLn and LREQ Setup Waveforms                   |  |

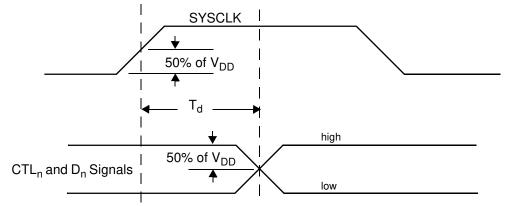

| CTLn and Dn Hold Timing Waveforms                   |  |

| 64-Pin Low Profile Quad Flat Pack (LQFP) Units = mm |  |

Page viii 912-2000-024

Revision: 1.0

# TriFire IEEE 1394 PHY Layer Controller

#### 1.0 Features

- · Conforms to the IEEE 1394 -1995 Standard.

- Three 1394 ports each with 100, 200 and 400 Mbit data transmission capabilities.

- · Differential receivers and transmitters for each port

- · Low-voltage differential signaling

- PLL synthesis of 100, 200 and 400 MHz clocks from standard 25 MHz reference crystals

- Asynchronous packet signaling that provides support for legacy hardware such as printers

- Isochronous packet signaling that provides support for multiple data streams

- Self-ID packets that provide support for power requirements signaling at start-up

- Automatic initialization and configuration of root and client nodes

- PHY-Link-layer Controller (LLC) data communications over 2, 4 or 8 lines

- Single 3.3 V power supply

- · Packaged in 64-pin Low-profile Quad Flat Pack (LQFP)

Figure 1-1 TriFire System Block Diagram

**TriFire Functional Block Diagram** Figure 1-2 CPS → TPA0+ LPS+D6 ◆→ Data Decoder → TPA0-Port 0 DIRECT -→ TPB0+ PTDIS -SYSCLK **←** → TPB0-LREQ -CTL0 ◆→ CTL1 ◆→ D0 **←** Data Encoder D1 **↔** D2 **←**▶ **←** TPA1+ PHY-LLC D3 **←**▶ Interface ←→ TPA1-Port 1 RESET \_\_\_ → TPB1+ PD+D7 ◆→ **←** TPB1-PC0 → PC1 → PC2 → C/LKON ◆→ TESTM1+D5 ◆→ **◆**TPA2+ TESTM2+D4 ◆◆ Port 2 ←► TPA2-←→TPB2+ Arbitration and Control Logic **←→**TPB2-XO **←** Clock Generator **←** RO and PLL Bias and Current **→** TPBIAS0 XI →

→ TPBIAS1 **▶** TPBIAS2

Generator

## 2.0 Signal Definitions

#### 2.1 Terminology/Nomenclature Conventions

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms "assertion" and "negation" are used extensively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term "assert", or "assertion" indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term "negate", or "negation" indicates that a signal is inactive.

Some TriFire pins have more than one function. These pins can be time-multiplexed, have strap options, or can be selected via register programming.

The tables in this section use several common abbreviations. Table 2-1 lists the mnemonics and their meanings. Note that TTL/CMOS/Schmitt-trigger levels pertain to inputs only. Outputs are driven at CMOS levels.

Table 2-1 Signal Definitions Legend

| Mnemonic | Description           |

|----------|-----------------------|

| BD       | Bidirectional         |

| CMOS     | CMOS-level compatible |

| G        | Ground                |

| I        | Input                 |

| I/O      | Input/Output          |

| 0        | Output                |

| Р        | Power                 |

| S        | Schmitt-trigger       |

| TTL      | TTL-level compatible  |

Figure 2-1 TriFire Pin Diagram

Table 1-1 TriFire Pin Cross-Reference List

| Signal Name                 | Alternative | Pin<br>No. | Pin<br>Type | Power<br>Plane |

|-----------------------------|-------------|------------|-------------|----------------|

| RESET#                      |             | 1          | I           | 3.3 V          |

| LPS                         | D6          | 2          | BD          | 3.3 V          |

| LREQ                        |             | 3          | I           | 3.3 V          |

| DV <sub>DD</sub>            |             | 4          | Р           |                |

| DV <sub>DD</sub>            |             | 5          | Р           |                |

| DV <sub>DD</sub>            |             | 6          | Р           |                |

| PD                          | D7          | 7          | BD          | 3.3 V          |

| DGND                        |             | 8          | G           |                |

| SYSCLK                      |             | 9          | 0           | 3.3 V          |

| DGND                        |             | 10         | G           |                |

| CTL0                        |             | 11         | BD          | 3.3 V          |

| CTL1                        |             | 12         | BD          | 3.3 V          |

| D0                          |             | 13         | BD          | 3.3 V          |

| D1                          |             | 14         | BD          | 3.3 V          |

| D2                          |             | 15         | BD          | 3.3 V          |

| D3                          |             | 16         | BD          | 3.3 V          |

| DGND                        |             | 17         | G           |                |

| DGND                        |             | 18         | G           |                |

| $\mathrm{DV}_{\mathrm{DD}}$ |             | 19         | Р           |                |

| DV <sub>DD</sub>            |             | 20         | Р           |                |

| TESTM2                      | D4          | 21         | BD          | 3.3 V          |

| TESTM1                      | D5          | 22         | BD          | 3.3 V          |

| CPS                         |             | 23         | 1           | Analog         |

| AV <sub>DD</sub>            |             | 24         | Р           |                |

| AV <sub>DD</sub>            |             | 25         | Р           |                |

| AGND                        |             | 26         | Р           |                |

| C/LKON                      |             | 27         | BD          | 3.3 V          |

| PC0                         |             | 28         | I           | 3.3 V          |

| PC1                         |             | 29         | I           | 3.3 V          |

| PC2                         |             | 30         | I           | 3.3 V          |

| PTDIS                       |             | 31         | 1           | 3.3 V          |

| AGND                        |             | 32         | G           |                |

| TPB2-                       |             | 33         | BD          | Analog         |

| TPB2+                       |             | 34         | BD          | Analog         |

| Signal Name        | Alternative | Pin<br>No. | Pin<br>Type | Power<br>Plane |

|--------------------|-------------|------------|-------------|----------------|

| TPA2-              |             | 35         | BD          | Analog         |

| TPA2+              |             | 36         | BD          | Analog         |

| TPB1-              |             | 37         | BD          | Analog         |

| TPB1+              |             | 38         | BD          | Analog         |

| TPA1-              |             | 39         | BD          | Analog         |

| TPA1+              |             | 40         | BD          | Analog         |

| AGND               |             | 41         | G           |                |

| TPB0-              |             | 42         | BD          | Analog         |

| TPB0+              |             | 43         | BD          | Analog         |

| TPA0-              |             | 44         | BD          | Analog         |

| TPA0+              |             | 45         | BD          | Analog         |

| TPBIAS0            |             | 46         | 0           | Analog         |

| TPBIAS1            |             | 47         | 0           | Analog         |

| TPBIAS2            |             | 48         | 0           | Analog         |

| AGND               |             | 49         | G           |                |

| AGND               |             | 50         | G           |                |

| AV <sub>DD</sub>   |             | 51         | G           |                |

| PLLGND             |             | 52         | G           |                |

| PLLGND             |             | 53         | G           |                |

| TESTA1             |             | 54         | 0           | Analog         |

| PLLV <sub>DD</sub> |             | 55         | Р           |                |

| XI                 |             | 56         | I           | Analog         |

| XO                 |             | 57         | 0           | Analog         |

| AV <sub>DD</sub>   |             | 58         | Р           |                |

| RO                 |             | 59         | 0           | Analog         |

| TESTA2             |             | 60         | 0           | Analog         |

| AGND               |             | 61         | G           |                |

| DIRECT             |             | 62         | I           | 3.3 V          |

| DGND               |             | 63         | G           |                |

| DGND               |             | 64         | G           |                |

Figure 2-2 TTriFire System Implementation Diagram

## 2.2 TriFire Strapping Options

Four modes have been implemeted in TriFire. Modes 0 and 1 are for internal debugging use only and should never be end-user configurable. Modes 2 and 3 are normal operating modes.

Strap options reflect the corresponding register bits. See Section 5 of this manual for detailed information about the registers.

Table 2-2 Mode Select

| Mode | TESTM2 (Pin 21) | TESTM1 (Pin 22)                        | Description                                     |  |

|------|-----------------|----------------------------------------|-------------------------------------------------|--|

| 0    | 0               | 0                                      | Reserved - for internal testing only            |  |

| 1    | 0               | 1 Reserved - for internal testing only |                                                 |  |

| 2    | 1               | 0                                      | Speed capability selectable                     |  |

| 3    | 1               | 1                                      | Speed 200 Mb/s compatible with the TI TSB21LV03 |  |

#### Table 2-3 Mode 2 User Options

| Pin No. | Pin Name | Corresponding Register  | Description                       |

|---------|----------|-------------------------|-----------------------------------|

| 2       | LPS+D6   | Common page FWR 2 [0:1] | LPS, PD (Speed Control):          |

| 7       | PD+D7    |                         | 00 => S400 (VCO - 400MHz)         |

|         |          |                         | 01 => S200 (VCO - 400MHz)         |

|         |          |                         | 10 => S100 (VCO - 400MHz)         |

|         |          |                         | 11 => S200 (VCO - 200MHz)         |

| 31      | PTDIS    | Page 0 Port 0 FWR 8 [7] | 1 => disable all ports            |

|         |          | Page 0 Port 1 FWR 8 [7] | 0 => enable all ports             |

|         |          | Page 0 Port 2 FWR 8 [7] |                                   |

| 28-30   | PC[0:2]  | Page 2 FWR 8 [0:2]      | Power class                       |

| 11      | CTL0     | Page 2 FWR 9 [2]        | PLL enable:                       |

|         |          |                         | 1 => enable PLL                   |

|         |          |                         | 0 => disable PLL                  |

| 12      | CTL1     | Page 2 FWR A [7]        | OSC disable:                      |

|         |          |                         | 1 => disable OSC                  |

|         |          |                         | 0 => enable OSC                   |

| 27      | C/LKON   | Page 2 FWR 8 [4]        | Contender: 1 => contender capable |

#### Table 2-4 Mode 3 User Options

| Pin No. | Pin Name | Corresponding Register | Description                       |

|---------|----------|------------------------|-----------------------------------|

| 28-30   | PC[0:2]  | Page 2 FWR 8 [0:2]     | Power class                       |

| 27      | C/LKON   | Page 2 FWR 8 [4]       | Contender: 1 => contender capable |

# 3.0 Signal Descriptions

| Signal Name                 | Pin No. | Signal Type<br>(Drive) | Signal Description                                                |

|-----------------------------|---------|------------------------|-------------------------------------------------------------------|

| AGND                        | 26      | G                      | Analog ground                                                     |

| AGND                        | 32      | G                      |                                                                   |

| AGND                        | 41      | G                      |                                                                   |

| AGND                        | 49      | G                      |                                                                   |

| AGND                        | 50      | G                      |                                                                   |

| AGND                        | 61      | G                      |                                                                   |

| $AV_{DD}$                   | 24      | Р                      | Analog power                                                      |

| $AV_{DD}$                   | 25      | Р                      |                                                                   |

| $AV_{DD}$                   | 51      | Р                      |                                                                   |

| $AV_{DD}$                   | 58      | Р                      |                                                                   |

| CPS                         | 23      | CMOS, Input            | Cable power status. Indicates a connection at the input terminal. |

| CTL0                        | 11      | BD, 8 mA               | Control I/O.                                                      |

| CTL1                        | 12      | BD, 8 mA               |                                                                   |

| D0                          | 13      | BD, 8 mA               | Data I/O.                                                         |

| D1                          | 14      | BD, 8 mA               |                                                                   |

| D2                          | 15      | BD, 8 mA               |                                                                   |

| D3                          | 16      | BD, 8 mA               |                                                                   |

| TESTM2 + D4                 | 21      | BD, 8 mA               | Mode 3: TESTM2 Mode 2: D4                                         |

| TESTM1 + D5                 | 22      | BD, 8 mA               | TESTM1 D5                                                         |

| LPS + D6                    | 2       | BD, 8 mA               | LPS D6                                                            |

| PD + D7                     | 7       | BD, 8 mA               | PD D7                                                             |

| DGND                        | 8       | G                      | Digital ground.                                                   |

| DGND                        | 10      | G                      |                                                                   |

| DGND                        | 17      | G                      |                                                                   |

| DGND                        | 18      | G                      |                                                                   |

| DGND                        | 63      | G                      |                                                                   |

| DGND                        | 64      | G                      |                                                                   |

| $\mathrm{DV}_{\mathrm{DD}}$ | 4       | Р                      | Digital power.                                                    |

| $\mathrm{DV}_{\mathrm{DD}}$ | 5       | Р                      |                                                                   |

| DV <sub>DD</sub>            | 6       | Р                      |                                                                   |

| $\mathrm{DV}_{\mathrm{DD}}$ | 19      | Р                      |                                                                   |

| DV <sub>DD</sub>            | 20      | Р                      |                                                                   |

| DIRECT                      | 62      | CMOS Input             | Link interface isolation input.                                   |

| C/LKON                      | 27      | BD, 8 mA               |                                                                   |

| Signal Name        | Pin No. | Signal Type<br>(Drive) | Signal Description                                                                                                 |  |  |

|--------------------|---------|------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| LREQ               | 3       | CMOS Input             | Link request. The Link Controller signalsTriFire for a data transfer or a service with this pin.                   |  |  |

| PC0                | 28      | CMOS Input             | Power class signals. Self-ID packets encode these inputs to indicate the                                           |  |  |

| PC1                | 29      | CMOS Input             | power class. Pull inputs high to represent a "1" and pull inputs low to represent a "0".                           |  |  |

| PC2                | 30      | CMOS Input             | 55m & 5.                                                                                                           |  |  |

| PLLGND             | 52      | Analog                 | PLL ground.                                                                                                        |  |  |

| PLLGND             | 53      | Analog                 |                                                                                                                    |  |  |

| PLLV <sub>DD</sub> | 55      | Analog                 | PLL power.                                                                                                         |  |  |

| PTDIS              | 31      | CMOS Input             | Port disable. This pin is used as a strapping option.                                                              |  |  |

| RESET#             | 1       | Input                  | Reset input. When this pin receives an active low signal, the bus on the 1394 ports and the internal logic resets. |  |  |

| RO                 | 59      | 0                      | Current setting resistor.                                                                                          |  |  |

| SYSCLK             | 9       | 8 mA                   | System clock.                                                                                                      |  |  |

| TESTA1             | 54      | Analog Output          | Analog test mode control.                                                                                          |  |  |

| TESTA2             | 60      | Analog Output          |                                                                                                                    |  |  |

| TPA0-              | 44      | Analog BD              | "A" twisted cable pairs.                                                                                           |  |  |

| TPA0+              | 45      | Analog BD              |                                                                                                                    |  |  |

| TPA1-              | 39      | Analog BD              |                                                                                                                    |  |  |

| TPA1+              | 40      | Analog BD              |                                                                                                                    |  |  |

| TPA2-              | 35      | Analog BD              |                                                                                                                    |  |  |

| TPA2+              | 36      | Analog BD              |                                                                                                                    |  |  |

| TPB0-              | 42      | Analog BD              | "B" twisted cable pairs.                                                                                           |  |  |

| TPB0+              | 43      | Analog BD              |                                                                                                                    |  |  |

| TPB1-              | 37      | Analog BD              |                                                                                                                    |  |  |

| TPB1+              | 38      | Analog BD              |                                                                                                                    |  |  |

| TPB2-              | 33      | Analog BD              |                                                                                                                    |  |  |

| TPB2+              | 34      | Analog BD              |                                                                                                                    |  |  |

| TPBIAS0            | 46      | Analog Output          | Bias twisted cable pairs. Provides a 1.86 V bias voltage for the 1394 cable                                        |  |  |

| TPBIAS1            | 47      | Analog Output          | drivers.                                                                                                           |  |  |

| TPBIAS2            | 48      | Analog Output          |                                                                                                                    |  |  |

| XI                 | 56      | Analog Input           | Crystal oscillator. These pins receive a 24.576 MHz crystal signal.                                                |  |  |

| XO                 | 57      | Analog Output          |                                                                                                                    |  |  |

912-2000-024 Page 10

## 4.0 Functional Description

The OPTi 82C842 device is a mixed signal Integrated Circuit that contains the full Physical layer implementation of the IEEE1394-1995 standard on a three-port node. This device, also called a PHY, complements the Link Layer Controller IC (LLC) on a IEEE 1394 architecture.

Each port consists of a pair of differential line transceivers and an associated circuitry to accomplish packet reception/transmission as well as perform bus arbitration. The 82C842 is capable of handling both asynchronous and isochronous packets.

An internal PLL circuit generates all necessary clocks for the correct operation under 100, 200 and 400 Mb/s speeds. Only an external 24.576MHz crystal is necessary. The 82C842 also provides the 49.152 MHz clock for communication with the LLC IC.

Some applications require a galvanic isolation between the PHY and the LLC ICs. OPTi's 82C842 implements this function in accordance with Annex J of the IEEE 1394 specification. If pin DIRECT is tied high, normal operation occurs whereas if DIRECT is sensed low, an internal differentiating logic that detects short pulses is engaged.

There are eight data lines between the PHY and the LLC. For 100Mb/s operation, only two lines are used. For 200Mb/s, 4 lines are used and for 400Mb/s, all eight lines transfer valid data between the ICs.

Because the 82C842 was designed to be interchangeable with TI's TSB21LV03x and SONY's CXD1944 PHYs which can operate only up to 200 Mb/s (four data bits used), the upper four data bits necessary for operation at 400 Mb/s were multiplexed with the following functions: PD (power down); LPS (Link Power Status); TESTM1 & TESTM2 (test mode pins). If 400 Mb/s operation is engaged, the alternate pin function is not available.

Four configuration pins are provided in order to set the PC[0:2] bits and the "C" (contender) bit in the self-identification packet The contender bit, if set to one, indicates that this node can be a bus manager. If this bit is set to zero, the node will not try to be a bus manager. The PC[0:2] bits indicate the power requirements or capabilities of the node (sink/source power).

The primary functions of the PHY IC are to serially encode and transmit data packets originated by the LLC and decode serially received data streams forwarding them to the LLC. In addition, the PHY IC has to copy any received data packets at any port to the other two ports (provided a cable is detected), performing clock/data recovery and regeneration.

The common mode voltage present on the TPA pairs is monitored by a special BIAS circuitry that determines if any cable is connected to that port and at what speed the next data packet can be transmitted.

For correct operation of the line drivers, a 112 ohm line-termination is necessary across both TPA and TPB pins. Two 56 ohm serially connected resistors are used for that. The mid-point of the resistor termination on TPA is connected to the TPBIAS voltage pin. The mid-point of the TPB resistor termination is coupled to GND though an RC network.

For complete descriptions of transmitted and received packets as well as PHY-LINK state machine operation, refer to publication number IEEE Std 1394-1995 published by the IEEE Computer Society.

### 4.1 Self-Loopback Test, Mode 4

Mode 4 can be selected through register selection (Page2, FWR09h) and can be used to transfer up to four bytes of information from one port to another. Parameters such as speed, transmitting port, data packet length, and data to be transmitted can be set. Data to be transmitted is displayed in Page3, FWR08h - FWR0Bh and data received is displayed in Page3, FWR0Ch - FWR0Fh.

## 5.0 TriFire Register Space

## 5.1 Register Pages

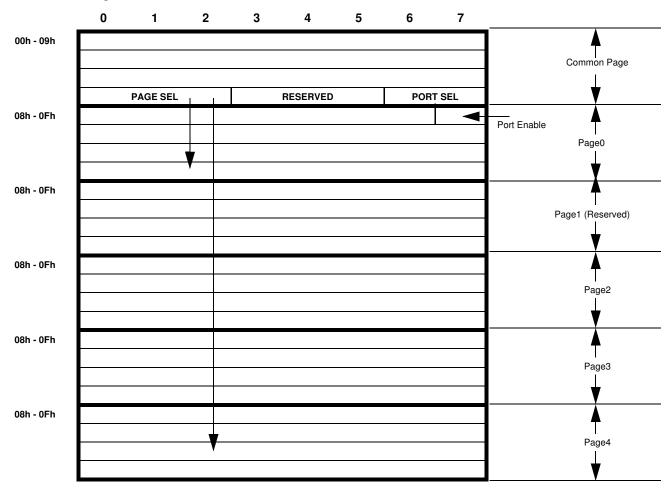

TriFire registers divide into six pages:

- · Common Page Registers

- · Page 0 Registers

- · Page 1 Registers

- · Page 2 Registers

- · Page 3 Registers

- · Page 4 Registers

The eight Common Page registers are mapped from 0h to 7h. Page 0, 1, 2, 3 and 4 share the same register address range: 08h to 0Fh. Page selection is done through the 3-bit page selection register, 07h[0:2], on the Common Page.

#### 5.1.1 TriFire Register Structure.

#### 5.1.2 Register Access Mechanism

TriFire register space maps through the 1394 link controller. Refer to the data book of the link controller for the design.

#### 5.1.3 Convention

All register bits are read/write with their default value initialized to 0 unless otherwise specified.

All reserve bits should be kept untouched.

#### 5.1.4 Register Bit Description

Section 5.1.4.1 through Section 5.1.4.6 give the bit formats for accessible registers in Trifire

**NOTE**: "(\*)" indicates the power-on strapping option.

#### 5.1.4.1 Common Page Registers

| 0                                                                                                                                  | 1                                                            | 2                                                                                        | 3                    | 4                                                                                           | 5                                                                                 | 6                                               | 7                                                         |  |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------|--|

| FWR 00h                                                                                                                            | FWR 00h Phy ID and Root Status Register Default = 0          |                                                                                          |                      |                                                                                             |                                                                                   |                                                 |                                                           |  |

|                                                                                                                                    |                                                              | Shows physic<br>(R                                                                       | al ID (000000)<br>O) |                                                                                             |                                                                                   | Shows Root:<br>0 = Not root<br>1 = Root<br>(RO) | Shows CPS Cable Power Status: 0 = Disable 1 = Enable (RO) |  |

| FWR 01h                                                                                                                            |                                                              | Ro                                                                                       | ot Hold-Off and      | Gap Count Regis                                                                             | iters                                                                             |                                                 | Default = 3Fh                                             |  |

| Selects root<br>hold-off bit:<br>0 = Disable<br>1 = Enable<br>(*)                                                                  | Initialize Bus<br>Reset:<br>0 = Disable<br>1 = Enable<br>(*) |                                                                                          |                      | •                                                                                           | gap count<br>= 111111                                                             |                                                 |                                                           |  |

| FWR 02h                                                                                                                            |                                                              | Ph                                                                                       | y Speed and Po       | rt Quantity Regis                                                                           | ters                                                                              |                                                 | Default = 23h                                             |  |

| Shows PHY speed  00 = S100 01 = S200 10 = S400 11 = Reserved (RO) (*)  Shows Enhanced Register Map: Default = 1 (RO) (*)  (RO) (*) |                                                              |                                                                                          |                      |                                                                                             |                                                                                   |                                                 |                                                           |  |

| FWR 03h                                                                                                                            |                                                              |                                                                                          | Port 0 Sta           | tus Register                                                                                |                                                                                   |                                                 | Default = 00h                                             |  |

| 00 = Data 0<br>01 = High imper<br>10 = Not used<br>11 = Data 1                                                                     | Status of Port 0  dence                                      | Shows the TPB S<br>00 = Data 0<br>01 = High impede<br>10 = Not used<br>11 = Data 1<br>(R | ence                 | Shows the status of the device attached to Port 0 0 = Parent 1 = Child or disconnected (RO) | Shows the sta-<br>tus of Port 0<br>0 = Discon-<br>nected<br>1 = Connected<br>(RO) | Res                                             | served                                                    |  |

Page 14 912-2000-024

### 5.1.4.1 Common Page Registers (cont.)

| 0                                                                                                                                                                     | 1                                                      | 2                                                                                        | 3                          | 4                                                                                                                                | 5                                                                                  | 6                                                                              | 7             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------|--|

| FWR 04h                                                                                                                                                               |                                                        |                                                                                          | Port 1 Sta                 | tus Register                                                                                                                     |                                                                                    |                                                                                | Default = 00h |  |

| Shows the TPA S  00 = Data 0  01 = High impede  10 = Not used  11 = Data 1  (R                                                                                        | ence                                                   | Shows the TPB S<br>00 = Data 0<br>01 = High impedo<br>10 = Not used<br>11 = Data 1<br>(R |                            | Shows the status of the device attached to Port1.  0 = Parent  1 = Child or disconnected (RO)                                    | Shows the sta-<br>tus of Port 1.<br>0 = Discon-<br>nected<br>1 = Connected<br>(RO) | Rese                                                                           | erved         |  |

| FWR 05h                                                                                                                                                               |                                                        |                                                                                          | Port 2 Sta                 | tus Register                                                                                                                     |                                                                                    |                                                                                | Default = 00h |  |

| Shows TPA Statu  00 = Data 0  01 = High impeded 10 = Not used 11 = Data 1  (R  FWR 06h  Shows the status Cable/Back-plane 00 = Back 01 = Cable 10 = Rese 11 = Rese (R | of the experiment: -plane experiment (Default) -prived | Shows the TPB S  00 = Data 0  01 = High impeded  10 = Not used  11 = Data 1  (R          | ence<br>O)<br>1394 Enviror | Shows the status of the device attached to Port 2.  0 = Parent 1 = Child or disconnected (RO)  mment Register number of addition | Shows the status of Port 2.  0 = Disconnected 1 = Connected (RO)                   | Reserved  Default = 49h                                                        |               |  |

| FWR 07h                                                                                                                                                               |                                                        |                                                                                          | Page and Port              | Selector Register                                                                                                                | •                                                                                  |                                                                                | Default = 00h |  |

| Page Selector:<br>000 = Pag<br>001 = Pag                                                                                                                              |                                                        | egisters (Default) Registers egisters                                                    |                            |                                                                                                                                  | d to 000                                                                           | Port Selector:<br>00 = Port 0 (I<br>01 = Port 1<br>10 = Port 2<br>11 = Reserve | Default)      |  |

# Preliminary Data Book TriFire

#### Page0 - Port Status Registers 5.1.4.2

#### Port 0 Status Register

| 0                                      | 1 | 2 | 3          | 4            | 5 | 6 | 7             |  |  |  |

|----------------------------------------|---|---|------------|--------------|---|---|---------------|--|--|--|

| FWR 08h                                |   |   | Port 0 Sta | tus Register |   |   | Default = 00h |  |  |  |

| Reserved                               |   |   |            |              |   |   |               |  |  |  |

| Register must be initialized to 000000 |   |   |            |              |   |   |               |  |  |  |

|                                        |   |   |            |              |   |   |               |  |  |  |

| FWR 09h - 0Fh Reserved                 |   |   |            |              |   |   |               |  |  |  |

#### Port 1 Status Register

| 3                                      | ь | 7 |  |  |  |  |  |  |  |  |  |

|----------------------------------------|---|---|--|--|--|--|--|--|--|--|--|

| WR 08h Port 1 Status Register          |   |   |  |  |  |  |  |  |  |  |  |

| Reserved                               |   |   |  |  |  |  |  |  |  |  |  |

| Register must be initialized to 000000 |   |   |  |  |  |  |  |  |  |  |  |

|                                        |   |   |  |  |  |  |  |  |  |  |  |

| FWR 09h - 0Fh Reserved                 |   |   |  |  |  |  |  |  |  |  |  |

| _                                      |   |   |  |  |  |  |  |  |  |  |  |

#### Port 2 Status Register

| 0                      | 1                                               | 2 | 3          | 4            | 5 | 6 | 7             |  |  |  |

|------------------------|-------------------------------------------------|---|------------|--------------|---|---|---------------|--|--|--|

| FWR 08h                |                                                 |   | Port 2 Sta | tus Register |   |   | Default = 00h |  |  |  |

|                        | Reserved Register must be initialized to 000000 |   |            |              |   |   |               |  |  |  |

| FWR 09h - 0Fh Reserved |                                                 |   |            |              |   |   |               |  |  |  |

#### 5.1.4.3 Page1 - Identification Registers

| 0           | 1                            | 2                                                      | 3             | 4               | 5 | 6 | 7             |  |  |  |  |  |

|-------------|------------------------------|--------------------------------------------------------|---------------|-----------------|---|---|---------------|--|--|--|--|--|

| FWR 08h-09h |                              |                                                        | Res           | erved           |   |   | Default = 00h |  |  |  |  |  |

|             |                              |                                                        |               |                 |   |   |               |  |  |  |  |  |

| FWR 0Ah     |                              |                                                        | Vendor ID Lov | w Byte Register |   |   | Default = 45h |  |  |  |  |  |

|             |                              |                                                        |               |                 |   |   |               |  |  |  |  |  |

|             |                              |                                                        |               |                 |   |   |               |  |  |  |  |  |

| FWR 0Bh     | Vendor ID High Byte Register |                                                        |               |                 |   |   |               |  |  |  |  |  |

|             |                              |                                                        | Vendor ID Hi  | gh Byte (RO)    |   |   |               |  |  |  |  |  |

| FWR 0Dh     |                              |                                                        | Device ID Lov | w Byte Register |   |   | Default = 42h |  |  |  |  |  |

|             |                              |                                                        | Device ID Lo  | ow Byte (RO)    |   |   |               |  |  |  |  |  |

| FWR 0Eh     |                              |                                                        | Default = 08h |                 |   |   |               |  |  |  |  |  |

|             |                              | Device ID High Byte Register  Device ID High Byte (RO) |               |                 |   |   |               |  |  |  |  |  |

Page 16 912-2000-024

## 5.1.4.3 Page1 - Identification Registers

| 0                | 1                          | 2 | 3 | 4 | 5 | 6 | 7 |  |  |

|------------------|----------------------------|---|---|---|---|---|---|--|--|

| FWR 0Fh          | Revision ID Register Defau |   |   |   |   |   |   |  |  |

| Revision ID (RO) |                            |   |   |   |   |   |   |  |  |

|                  |                            |   |   |   |   |   |   |  |  |

#### 5.1.4.4 Page2 - Vendor Dependent Registers

|                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                               | 2                                                                                                                                                                                                                                                                                        | 3                                                                                                                                           | 4                                                                                                                                 | 5                                                                                           |                                        | 6                                                                                                   | 7                                                                                                        |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| FWR             | 08h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 | Pov                                                                                                                                                                                                                                                                                      | ver Class and Co                                                                                                                            | ntender Bit Regi                                                                                                                  | isters                                                                                      |                                        |                                                                                                     | Default = 10h                                                                                            |

|                 | Node do repeat property proper | self-powered and pi<br>15W to the bus<br>self-powered and pi<br>30W to the bus.<br>self-powered and pi<br>45W to the bus.<br>ay be powered from | aracteristics: and does not  rovides a mini- rovides a mini- rocides a mini- rocides a mini- the bus and is us and is using is needed to ayers. us and is using is needed to | Link active bit in<br>self-ID Packet:<br>0 = Disable<br>1 = Enable<br>(Default)<br>(*)                                                      | Selects contender bit in self-ID packet:  0 = Disable 1 = Enable (*)                                                              | Short expiration simulation bits.  Reserved for internal use only, not for application use. |                                        | Internal simulation bits for arbitration.  Reserved for internal use only, not for application use. |                                                                                                          |

| FWR             | 09h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |                                                                                                                                                                                                                                                                                          | PLL and Deboun                                                                                                                              | ce Time Registe                                                                                                                   | rs                                                                                          |                                        |                                                                                                     | Default = 00h                                                                                            |

| trol:<br>0<br>0 | 0 = 400M<br>1 = 200M<br>0 = 100M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ock frequency con-<br>Hz (VCO=400MHz)<br>Hz (VCO=400MHz)<br>Hz (VCO=400MHz)<br>Hz (VCO=200MHz)<br>(*)                                           | Enables PLL<br>using external<br>clock source:<br>0 = Disable PLL<br>1 = Enable PLL<br>(*)                                                                                                                                                                                               | Enables fast debouncing clock used in port status debouncing circuit.  0 = Disable, using 1.52KHz clock 1 = Enable, using 6.25MHz clock (*) | Selects the number status port.  000 = 0 CLI 001 = 5 CLI 010 = 20 CI 011 = 40 CI 100 = 80 CI 101 = 200 CI 110 = 518 CI 111 = 1023 | 6.25 Ks 0us Ks 0.8u LKs 3.2u LKs 6.4u LKs 12.8 CLKs 32.0 CLKs 82.9                          | MHz 1  S 3  S 1  S 2  US 5  US 5  US 6 | uncing the 1.52KHz 0ms 3.3ms 13.1ms 26.2ms 52.4ms 131.1ms 339.5ms                                   | Register Read/Write:  Reserved for internal use only. Not for application use.  Do not program this bit. |

#### 5.1.4.4 Page2 - Vendor Dependent Registers (cont.)

| 0                                                                                                                                                 | 1                                                                                                                                                                                                       | 2                                                                                                     | 3                                                                                                                                                    | 4                                                                             | 5                                                                                                                          | 6              | 7                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|