## 82C895

# **System/Power Management Controller**

## **Data Book**

Revision 1.0 912-3000-015 September 1994

#### Copyright

Copyright © 1994, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 2525 Walsh Avenue, Santa Clara, CA 95051.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc.

All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

2525 Walsh Avenue Santa Clara, CA 95051 Tel: (408) 980-8178

Fax: (408) 980-8860 BBS: (408) 980-9774

# **Table of Contents**

| 1.0 | Fea | tures   |                                                 | 1  |

|-----|-----|---------|-------------------------------------------------|----|

| 2.0 | Ove | rview   | ***************************************         | 2  |

|     | 2.1 |         | Management                                      |    |

| 3.0 | Sig |         | initions                                        |    |

|     | 3.1 | Signal  | Descriptions                                    | 6  |

|     |     | 3.1.1   | CPU Interface Signals                           |    |

|     |     | 3.1.2   | VESA Local Bus Interface Signals                |    |

|     |     | 3,1.3   | AT Bus Interface Signals                        |    |

|     |     | 3.1.4   | Bus Arbitration Interface Signals               |    |

|     |     | 3.1.5   | Numeric Processor Interface Signals             |    |

|     |     | 3.1.6   | Cache Interface Signals                         |    |

|     |     | 3.1.7   | DRAM Interface Signals                          |    |

|     |     | 3.1.8   | DRAM and Interrupt Controller Interface Signals | 10 |

|     |     | 3.1.9   | Buffer Control Interface Signals                | 11 |

|     |     | 3.1.10  | Reset Signals                                   | 12 |

|     |     | 3.1.11  | Clock Signals                                   | 12 |

|     |     | 3.1.12  | Miscellaneous Signals                           | 12 |

|     |     | 3.1.13  | Power Management Signals                        | 13 |

|     |     | 3.1.14  | Power and Ground Pins                           | 13 |

| 4.0 | Fun | ctional | Description                                     | 15 |

|     | 4.1 | Reset I | Logic                                           | 15 |

|     | 4.2 | System  | n Clock Generation                              | 15 |

|     | 4.3 | CPU B   | urst Mode Control                               | 16 |

|     | 4.4 | L1 Writ | te-Back Timing Description                      | 16 |

|     | 4.5 | Cache   | Subsystem                                       | 16 |

|     |     | 4.5.1   | Cache Bank Interleave                           | 16 |

|     |     | 4.5.2   | Write-Back Cache                                |    |

|     |     | 4.5.3   | 4.5.2.1 Tag RAM                                 |    |

|     |     | 4.0.3   | Dirty Bit Mechanism                             | 17 |

## 82C895

| 4.6  | Local D  | PRAM Control Subsystem                     | 19 |

|------|----------|--------------------------------------------|----|

| 4.7  | Parity 0 | Generation/Detection Logic                 | 21 |

| 4.8  | Refresh  | h Logic                                    | 21 |

| 4.9  | Shadov   | w RAM and BIOS Cacheability                | 21 |

| 4.10 | System   | n ROM BIOS Cycles                          | 22 |

| 4.11 | -        | State Machine                              |    |

| 4.12 |          | bitration Logic                            |    |

| 4.13 |          | Bus Interface                              |    |

|      |          |                                            |    |

| 4.14 |          | us Conversion/Data Path Control Logic      |    |

| 4.15 | Turbo/S  | Slow Mode Operations                       | 23 |

| 4.16 | Fast GA  | ATEA20 and RESET Emulation                 | 23 |

| 4.17 | Special  | l Cycles                                   | 23 |

| 4.18 | Power    | Management Features                        | 23 |

|      | 4.18.1   | System Activity Detection                  | 23 |

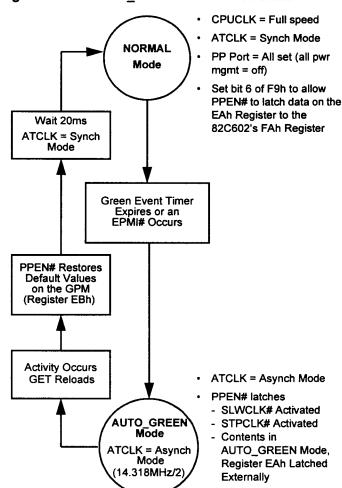

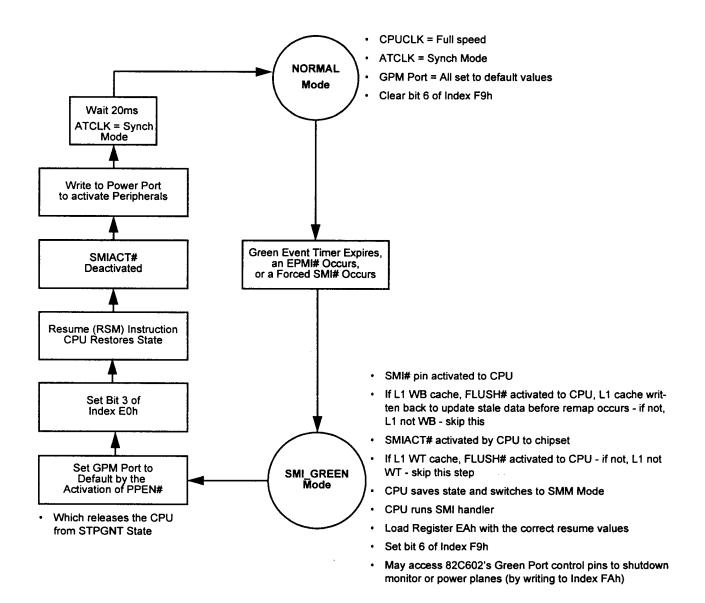

|      | 4.18.2   | Definition of Power Management Modes       | 24 |

|      |          | 4.18.2.1 NORMAL Mode                       |    |

|      |          | 4.18.2.2 AUTO_GREEN Mode                   |    |

|      |          |                                            |    |

| 4.19 | internal | l Peripherals Controller                   |    |

|      | 4.19.1   | Top Level Decoder & Configuration Register | 26 |

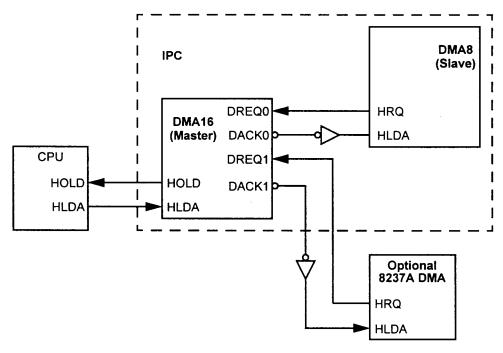

|      | 4.19.2   | DMA Subsystem                              |    |

|      |          | 4.19.2.1 DMA Operation                     |    |

|      |          | 4.19.2.1.1 Idle Mode                       |    |

|      |          | 4.19.2.1.2 Program Mode                    |    |

|      |          | 4.19.2.1.3 Active Mode                     |    |

|      |          | 4.19.2.2 DMA Transfer Modes                |    |

|      |          | 4.19.2.2.1 Single Transfer Mode            |    |

|      |          | 4.19.2.2.3 Demand Transfer Mode            |    |

|      |          | 4.19.2.2.4 Cascade Mode                    |    |

|      |          | T. 13.2.2.7 Cascade Mode                   | 20 |

|        | 4.19.2.3  | ranster ry    | /pes                                     | 29             |

|--------|-----------|---------------|------------------------------------------|----------------|

|        |           | 4.19.2.3.1    | Auto-initialization                      | 30             |

|        |           | 4.19.2.3.2    | DREQ Priority                            | 30             |

|        |           | 4.19.2.3.3    | Address Generation                       | 30             |

|        |           | 4.19.2.3.4    | Compressed Timing                        | 3 <sup>2</sup> |

| 4.19.3 | DMA Re    | gister Descri | ptions                                   | 3 <sup>2</sup> |

|        | 4.19.3.1  | Current Add   | dress Register                           | 3 <sup>4</sup> |

|        | 4.19.3.2  | Current Wo    | ord Count Register                       | 3 <sup>4</sup> |

|        |           |               | ess Register                             |                |

|        | 4.19.3.4  | Base Word     | Count Register                           | 3 <sup>4</sup> |

|        | 4.19.3.5  | Command       | Register                                 | 3 <sup>4</sup> |

|        | 4.19.3.6  | Mode Regis    | ster                                     | 32             |

|        | 4.19.3.7  | Request Re    | egister                                  | 32             |

|        | 4.19.3.8  | Request Ma    | ask Register                             | 32             |

|        | 4.19.3.9  | Status Reg    | ister                                    | 32             |

|        | 4.19.3.10 | ) Temporary   | Register                                 | 32             |

| 4.19.4 | Special ( | Commands      |                                          | 3:             |

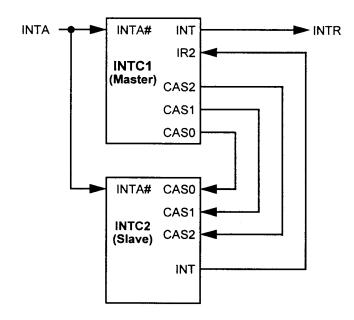

| 4.19.5 | •         |               | ubsystem                                 |                |

| 4.19.5 |           |               | ontroller Subsystem Overview             |                |

|        |           | = -           | ontroller Subsystem Overview             |                |

|        |           | •             | equence                                  |                |

|        |           | •             | rrupt (EOI)                              |                |

|        |           |               | signment                                 |                |

|        | 4. 19.5.5 | -             | <u> </u>                                 |                |

|        |           |               | Fixed Priority Mode                      |                |

|        |           |               | Specific Rotation Mode                   |                |

|        | 4 10 E 6  |               | Automatic Rotation Mode                  |                |

|        | 4.19.5.6  | -             | ng the Interrupt Controller              |                |

|        |           |               | Initialization Command Words (ICWs)      |                |

|        |           |               | Operational Command Words (OCWs)         |                |

|        |           |               | IRR, ISR, & Poll Vector                  |                |

| 4.19.6 |           | -             | /stem                                    |                |

|        | 4.19.6.1  |               | escription                               |                |

|        |           | 4.19.6.1.1    | Programming the Counter/Timer            |                |

|        |           |               | Read/Write Counter Command               |                |

|        |           |               | Counter Latch Command                    |                |

|        |           |               | Read-Back Command                        |                |

|        | 4.19.6.2  |               | peration                                 |                |

|        |           | 4.19.6.2.1    | Mode 0 - Interrupt on Terminal Count     |                |

|        |           | 4.19.6.2.2    | Mode 1 - Hardware Retriggerable One-Shot |                |

|        |           | 4.19.6.2.3    | Mode 2 - Rate Generator                  | 40             |

## 82C895

|     |     |         | 4.19.6.2.4 Mode 3 - Square Wave Generator               | 40 |

|-----|-----|---------|---------------------------------------------------------|----|

|     |     |         | 4.19.6.2.5 Mode 4 - Software Triggered Strobe           | 40 |

|     |     |         | 4.19.6.2.6 Mode 5 - Hardware Triggered Strobe           |    |

|     |     |         | 4.19.6.2.7 GATE2                                        | 40 |

| 5.0 | 82C | 895 Re  | egisters                                                | 43 |

|     | 5.1 | Regist  | ter Accessing                                           | 43 |

|     | 5.2 | Contro  | ol Register Descriptions                                | 43 |

|     | 5.3 | Power   | Management Registers Description                        | 52 |

|     | 5.4 | 82C89   | 5 Internal Peripherals Controller Register Descriptions | 61 |

|     |     | 5.4.1   | DMA Subsystem Registers                                 | 62 |

|     |     | 5.4.2   | Interrupt Controller Subsystem                          | 64 |

|     |     | 5.4.3   | Counter/Timer Subsystem                                 | 67 |

|     | 5.5 | I/O Poi | rt 60h                                                  | 69 |

|     | 5.6 | I/O Poi | rt 64h                                                  | 69 |

|     | 5.7 | Port 70 | 0h                                                      | 69 |

|     | 5.8 | Port 92 | 2h                                                      | 69 |

| 6.0 | Max | cimum   | Ratings                                                 | 71 |

|     | 6.1 | Absolu  | ute Maximum Ratings                                     | 71 |

|     | 6.2 | DC Ch   | paracteristics                                          | 71 |

|     | 6.3 | AC Ch   | naracteristics                                          | 72 |

|     |     | 6.3.1   | Cache Timing                                            | 72 |

|     |     | 6.3.2   | DRAM Timing                                             | 72 |

|     |     | 6.3.3   | Cache with DRAM Timing                                  | 73 |

|     |     | 6.3.4   | AT Bus Timing                                           | 73 |

|     |     | 6.3.5   | Reset Timing                                            | 74 |

|     |     | 6.3.6   | VL Timing                                               | 74 |

|     |     | 6.3.7   | Address and Data Bus Timing                             | 74 |

|     |     | 6.3.8   | L1 Write-back Timing                                    | 74 |

|     |     | 6.3.9   | AC Timing Waveforms                                     | 75 |

|     |     |         |                                                         |    |

| 7.0 | 82C   | 895 Te  | estability                  | 93 |

|-----|-------|---------|-----------------------------|----|

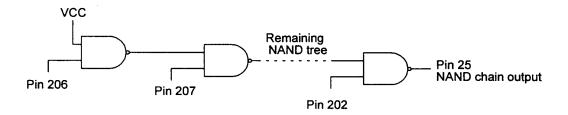

|     | 7.1   | NAND    | Tree Test                   | 9  |

|     | 7.2   | Drive I | High/Drive Low Test         | 94 |

| 8.0 | Mec   | hanica  | al Package Outline          | 9  |

| App | endix | κA.     | Accessing the BBS           | 97 |

|     | A.1   | Paging  | g the SYSOP                 | 9  |

|     | A.2   | Syster  | m Requirements              | 9  |

|     | A.3   | Calling | g In/Hours of Operation     | 9  |

|     | A.4   | Loggir  | ng On for the First Time    | 9  |

|     | A.5   | Log O   | n Rules and Regulations     | 9  |

|     | A.6   | Using   | the BBS                     | 9· |

|     |       | A.6.1   | Reading Bulletins           | 9  |

|     |       | A.6.2   | Sending/Receiving Messages  | 9  |

|     |       | A.6.3   | Finding Information         | 98 |

|     |       | A.6.4   | Downloading Files From OPTi | 98 |

|     |       | A.6.5   | Uploading Files To OPTi     | 9  |

|     |       | A.6.6   | Logging Off                 | 9  |

|     |       | A.6.7   | Logging Back on Again       | 98 |

|     | A.7   | The M   | lenus                       | 9  |

|     |       | A 7 1   | Menu Selections             | Q  |

Page viii

# **List of Figures**

| Figure 1-1  | 82C895 and 82C601/602-Based System Block Diagram | 1  |

|-------------|--------------------------------------------------|----|

| Figure 2-1  | Power Management Block Diagram                   | 2  |

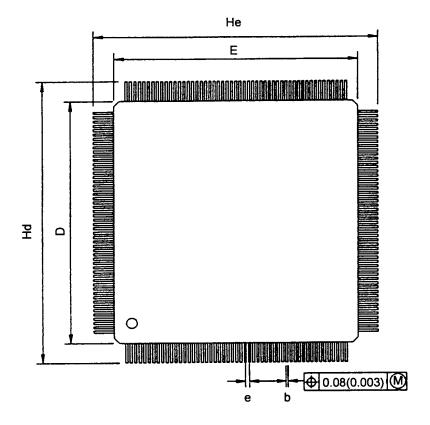

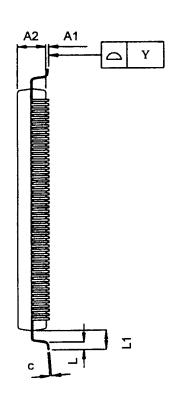

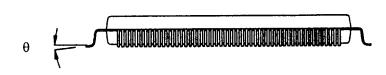

| Figure 3-1  | Pin Diagram                                      | 3  |

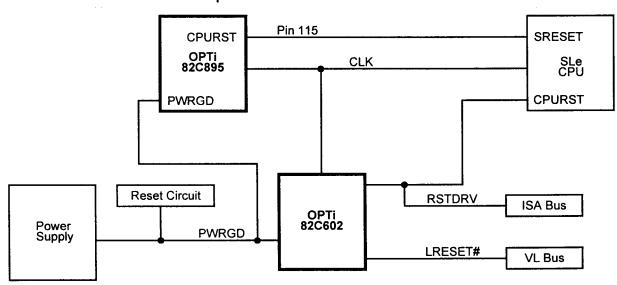

| Figure 4-1  | Reset Connection Example                         | 15 |

| Figure 4-2  | AUTO_GREEN Mode Flowchart                        | 24 |

| Figure 4-3  | SMI_GREEN Mode Flowchart                         | 25 |

| Figure 4-4  | Cascade Mode Interconnect                        | 29 |

| Figure 4-5  | Internal Cascade Interconnect                    | 33 |

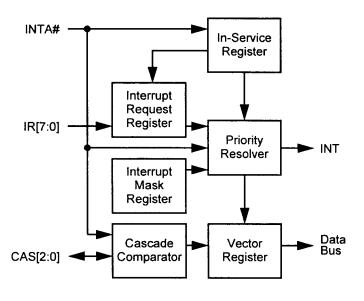

| Figure 4-6  | Interrupt Controller Block Diagram               | 34 |

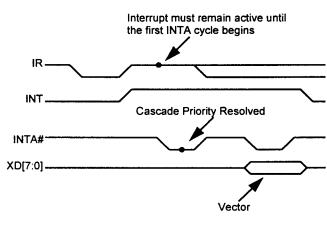

| Figure 4-7  | Interrupt Sequence                               | 34 |

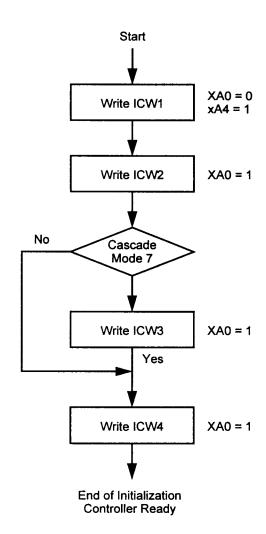

| Figure 4-8  | Initialization Sequence                          | 36 |

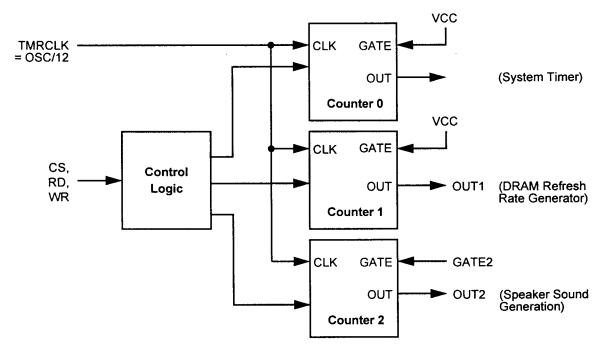

| Figure 4-9  | Counter/Timer Block Diagram                      | 38 |

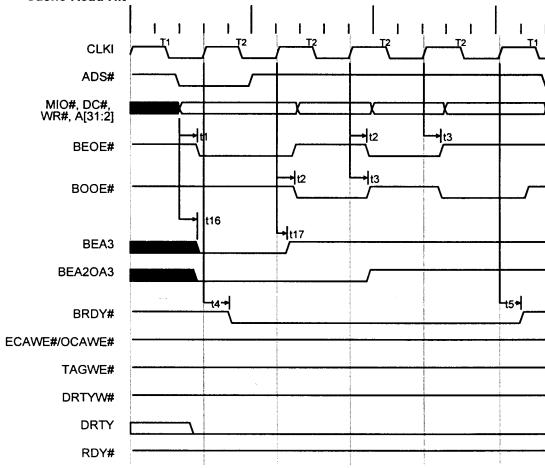

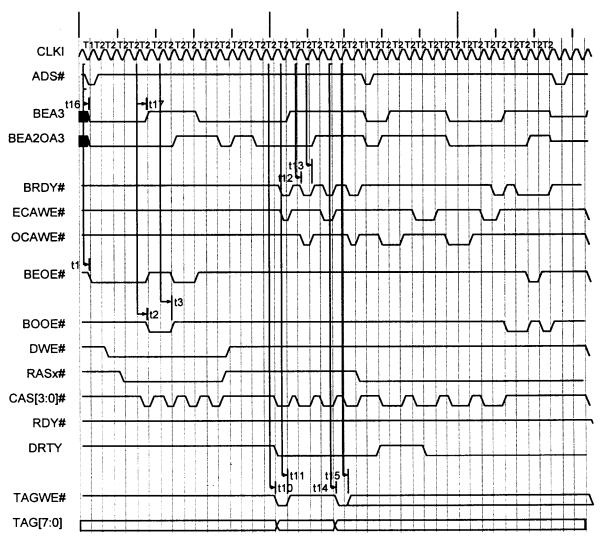

| Figure 6-1  | Cache Read Hit                                   | 75 |

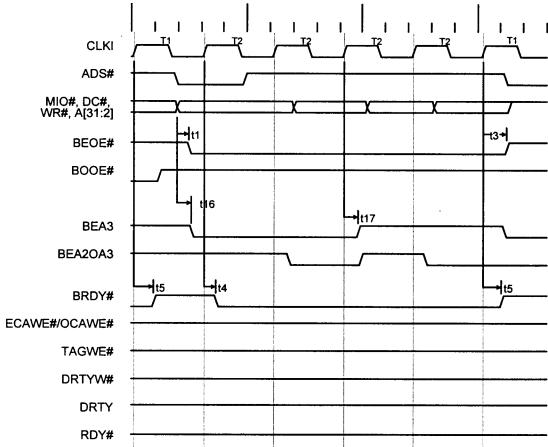

| Figure 6-2  | Cache Read Hit                                   | 76 |

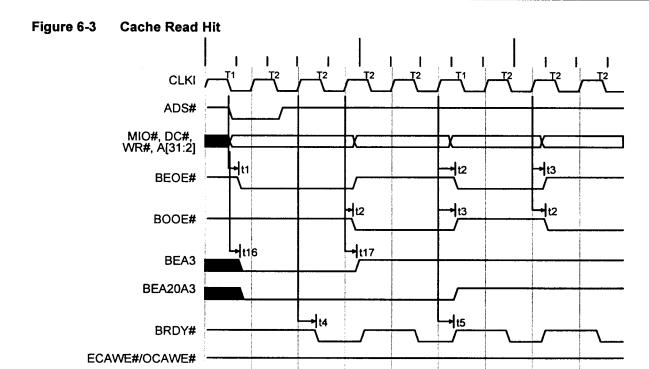

| Figure 6-3  | Cache Read Hit                                   | 77 |

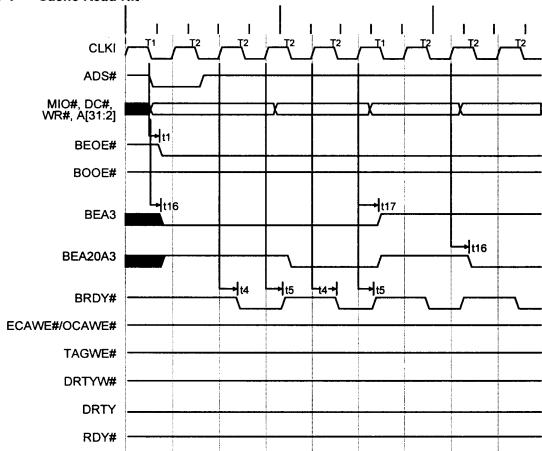

| Figure 6-4  | Cache Read Hit                                   | 78 |

| Figure 6-5  | Cache Read Miss (Dirty)                          | 79 |

| Figure 6-6  | Cache Write Hit (0WS/Not Dirty)                  | 80 |

| Figure 6-7  | Cache Write Hit (0WS/Dirty)                      | 80 |

| Figure 6-8  | Cache Write Hit (1WS/Dirty)                      | 81 |

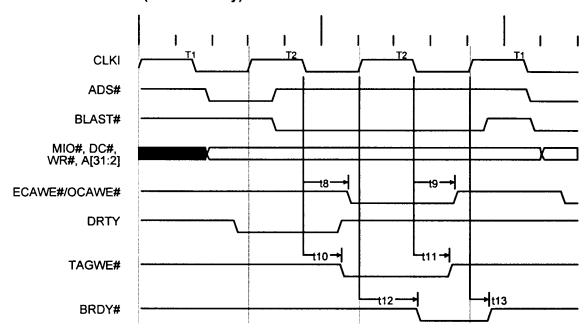

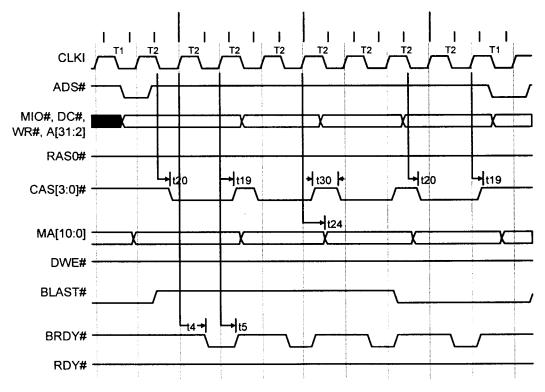

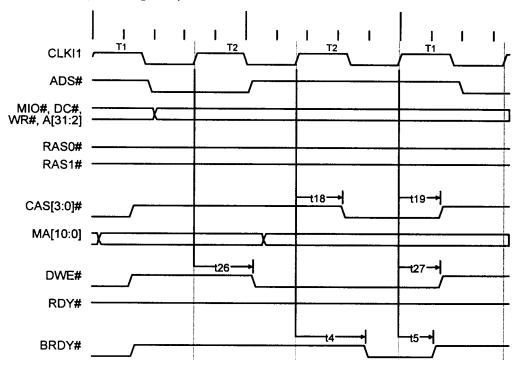

| Figure 6-9  | DRAM Read (Page Hit)                             | 81 |

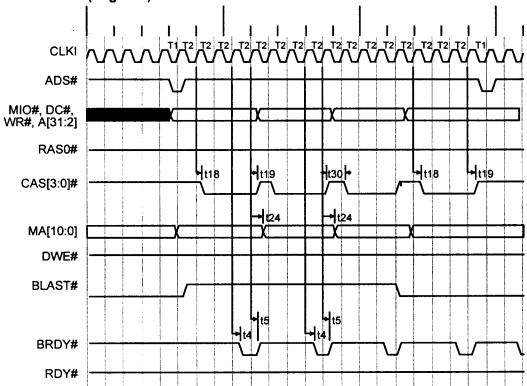

| Figure 6-10 | DRAM Read (Page Hit)                             | 82 |

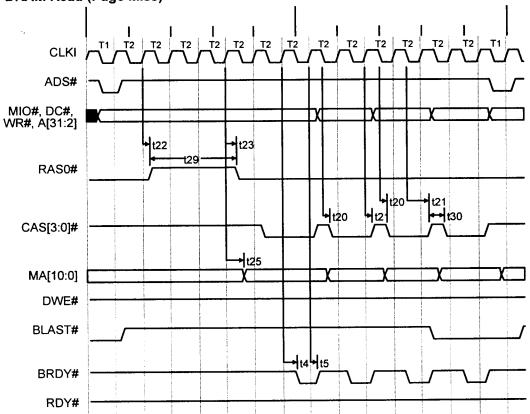

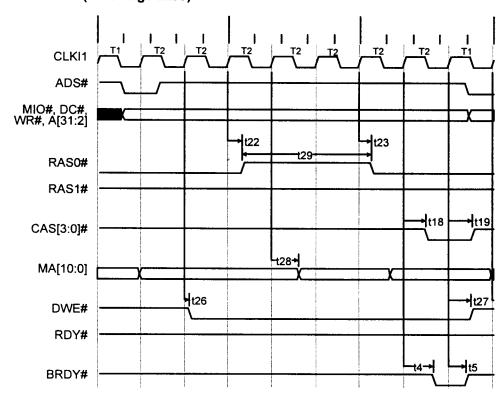

| Figure 6-11 | DRAM Read (Page Miss)                            | 83 |

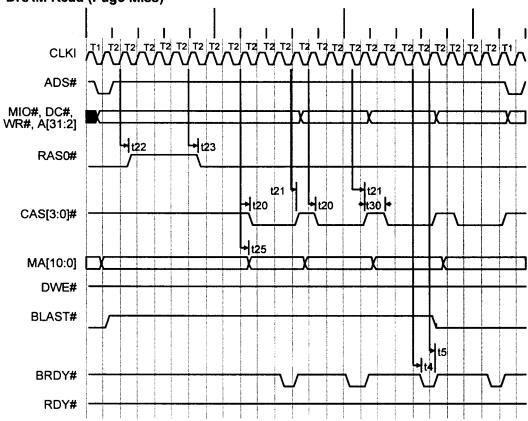

| Figure 6-12 | DRAM Read (Page Miss)                            | 84 |

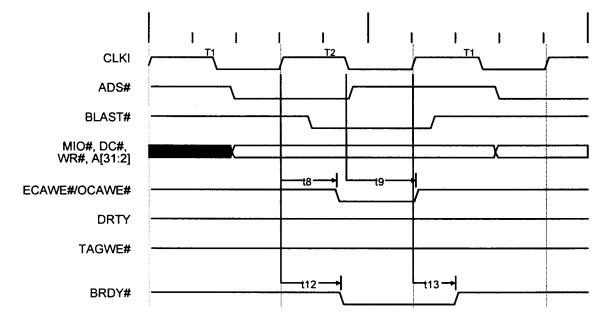

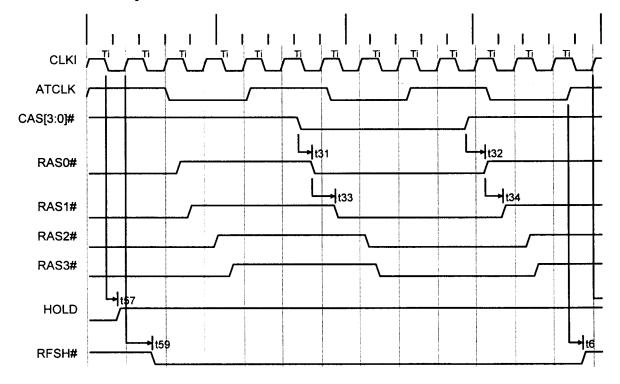

| Figure 6-13 | DRAM Write (0WS/Page Hit)                        | 85 |

| Figure 6-14 | DRAM Write (0WS/Page Miss)                       | 85 |

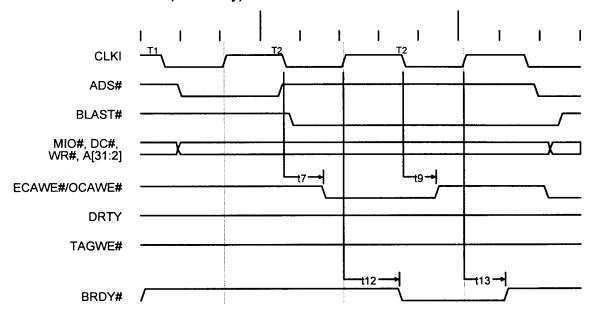

| Figure 6-15 | DRAM Write (1WS/Page Hit)                        | 86 |

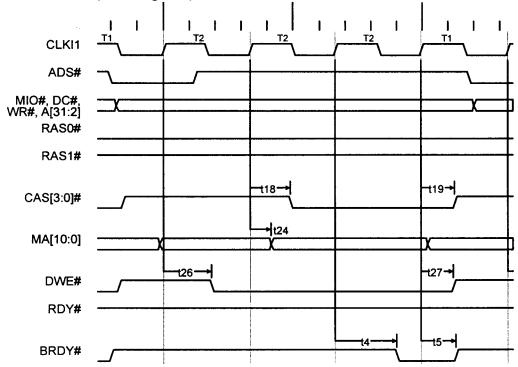

| Figure 6-16 | Refresh Cycle                                    | 86 |

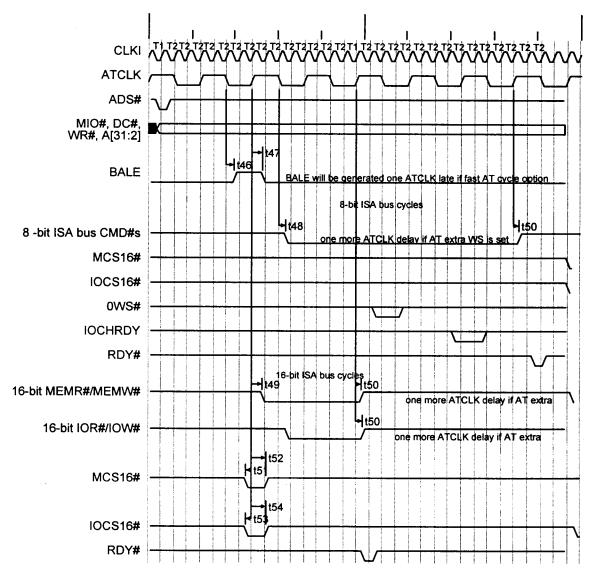

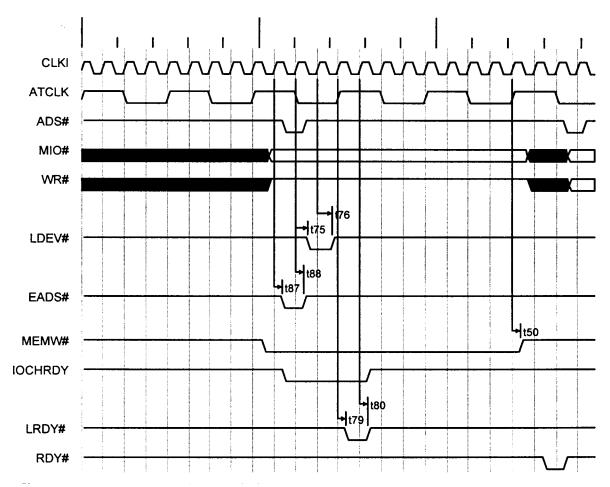

| Figure 6-17 | ISA Cycle                                        | 87 |

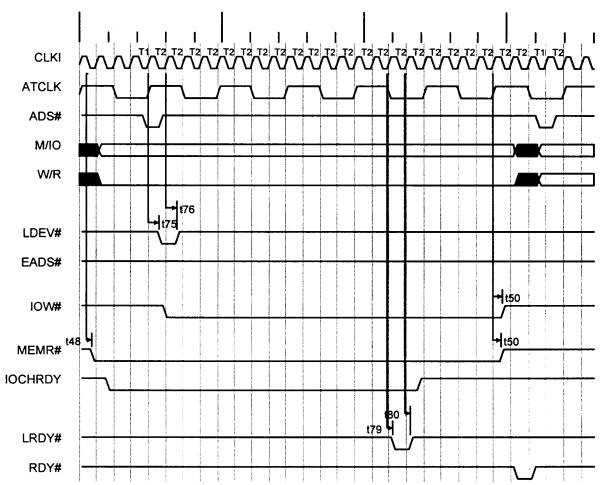

| Figure 6-18 | DMA Read Cycle                                   | 88 |

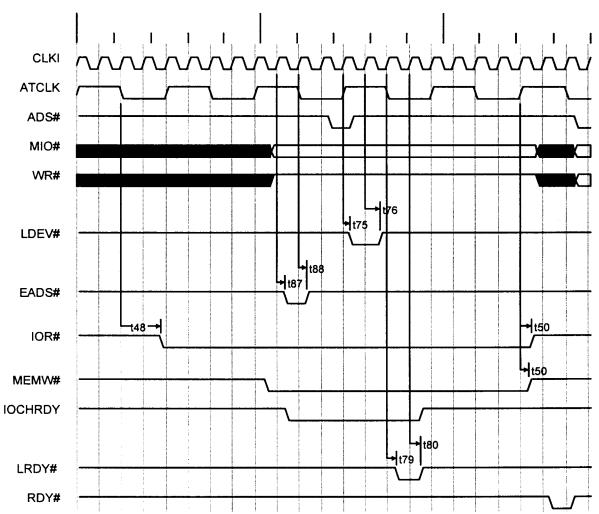

| Figure 6-19 | DMA Write Cycle                                  | 89 |

| Figure 6-20 | ISA Master Read Cycle                            | 90 |

|             |                                                  |    |

# 82C895

## List of Figures (Cont.)

| Figure 6-21 | ISA Master Write Cycle           | 91 |

|-------------|----------------------------------|----|

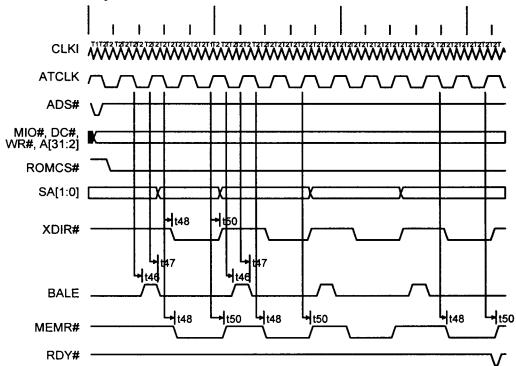

| Figure 6-22 | ROM Access Cycle                 | 92 |

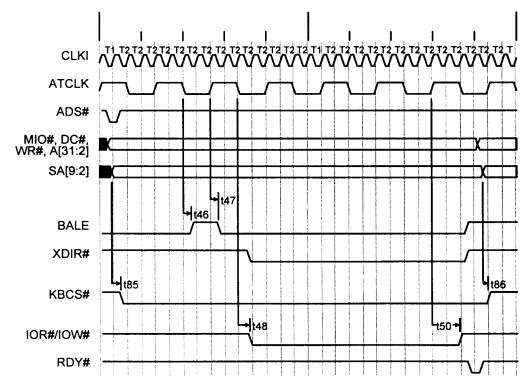

| Figure 6-23 | Keyboard Controller Access Cycle | 92 |

| Figure 7-1  | NAND Tree Block Diagram          | 94 |

| Figure 8-1  | 208-Pin Plastic Quad Flat Pack   | 95 |

| Figure A-1  | The Main Menu                    | 98 |

| Figure A-2  | The Bulletin Menu                | 98 |

| Figure A-3  | The File Menu                    | 99 |

| Figure A-4  | The Message Menu                 | 99 |

# **List of Tables**

| Table 3-1  | Numerical Pin Cross-Reference List                                 | 4              |

|------------|--------------------------------------------------------------------|----------------|

| Table 3-2  | Alphabetical Pin Cross-Reference List                              |                |

| Table 4-1  | Address to Tag Bit Mapping                                         | 17             |

| Table 4-2  | Cache Cycles                                                       | 18             |

| Table 4-3  | Cache SRAM Requirements                                            | 18             |

| Table 4-4  | SRAM Speed Requirements                                            | 19             |

| Table 4-5  | DRAM Configurations                                                | 20             |

| Table 4-6  | CPU Address to MA Bus Mapping                                      | 20             |

| Table 4-7  | DMA I/O Address Map                                                | 27             |

| Table 4-8  | Rotating Priority Scheme                                           | 30             |

| Table 4-9  | DMA Page Register I/O Address Map                                  | 3 <sup>2</sup> |

| Table 4-10 | Interrupt Request Source                                           | 33             |

| Table 4-11 | Interrupt Vector Byte                                              | 35             |

| Table 4-12 | Counter/Timer I/O Address Map                                      | 39             |

| Table 4-13 | GATE2 Pin Function                                                 | 4              |

| Table 5-1  | Control Registers Summary (Index Port 22h, Data Port 24h)          | 43             |

| Table 5-2  | Control Register 1 - Index: 20h                                    | 45             |

| Table 5-3  | Control Register 2 - Index: 21h                                    | 45             |

| Table 5-4  | Shadow RAM Control Register 1 - Index: 22h                         | 46             |

| Table 5-5  | Shadow RAM Control Register 2 - Index: 23h                         | 46             |

| Table 5-6  | DRAM Control Register 1 - Index: 24h                               | 47             |

| Table 5-7  | DRAM Control Register 2 - Index: 25h                               | 47             |

| Table 5-8  | Shadow RAM Control Register 3 - Index: 26h                         | 48             |

| Table 5-9  | Control Register 3 - Index: 27h                                    | 48             |

| Table 5-10 | Non-Cacheable Block 1 Register - Index: 28h                        | 49             |

| Table 5-11 | Non-Cacheable Block 1 Register 2 - Index: 29h                      | 49             |

| Table 5-12 | Non-Cacheable Block 2 Register 1 - Index: 2Ah                      | 49             |

| Table 5-13 | Non-Cacheable Block 2 Register 2 - Index: 2Bh                      | 50             |

| Table 5-14 | ROM Chip Select (ROMCS#) Control Register - Index: 2Dh             | 50             |

| Table 5-15 | Cacheable Address Range 1 Register - Index 2Eh                     | 5              |

| Table 5-16 | Cacheable Address Range 2 Register - Index 2Fh                     | 5              |

| Table 5-17 | Power Management Registers Summary (Index Port 22h, Data Port 24h) | 52             |

| Table 5-18 | PMU Timer and Power Management Port Enable Register - Index E0h    | 54             |

## List of Tables (Cont.)

| Table 5-19 | PMU Mode Event Timer 1 - Index E1h                                  | 55         |

|------------|---------------------------------------------------------------------|------------|

| Table 5-20 | GREEN Mode Event Timer 2 - Index E2h                                | 55         |

| Table 5-21 | GREEN Mode Event Timer 2 - Index E3h                                | 56         |

| Table 5-22 | DRQ Detection Register - Index E4h                                  | 56         |

| Table 5-23 | Video/Hard & Floppy Disk Monitor - Index E5h                        | 57         |

| Table 5-24 | Programmable I/O Address Detection - Index E6h                      | 57         |

| Table 5-25 | Programmable I/O Range Detection- Index E7h                         | 57         |

| Table 5-26 | Interrupt Trap Mask Register 1 - Index E8h                          | 58         |

| Table 5-27 | Interrupt Trap Mask Register 2- Index E9h                           | 58         |

| Table 5-28 | GREEN Mode Configuration Port - Index EAh                           | 58         |

| Table 5-29 | Return from GREEN Mode Configuration Port - Index EBh               | 58         |

| Table 5-30 | Scratch Register 1 - Index ECh                                      | 59         |

| Table 5-31 | Scratch Register 2 - Index EDh                                      | 59         |

| Table 5-32 | Index Register EEh                                                  | 59         |

| Table 5-33 | Mode Register - Index EFh                                           | 60         |

| Table 5-34 | Configuration Register (Index Port 22h, Data Port 23h) - Index: 01h | 6 <i>°</i> |

| Table 5-35 | Command Register                                                    | 62         |

| Table 5-36 | Mode Register                                                       | 62         |

| Table 5-37 | Request Register Write Format                                       | 63         |

| Table 5-38 | Request Register Read Format                                        | 63         |

| Table 5-39 | Request Mask Register Set/Reset Format                              | 63         |

| Table 5-40 | Request Mask Register Read/Write Format                             | 63         |

| Table 5-41 | Status Register                                                     | 63         |

| Table 5-42 | ICW1 Register - Address: 020h (0A0h)                                | 64         |

| Table 5-43 | ICW2 Register - Address: 021h (0A1h)                                | 64         |

| Table 5-44 | ICW3 Register - Format for INTC1 - Address: 021h                    | 64         |

| Table 5-45 | ICW3 Register - Format for INCT1 - Address: 0A1h                    | 64         |

| Table 5-46 | ICW4 Register - Address 021h (0A1h)                                 | 6          |

| Table 5-47 | OCW1 Register - Address: 021h (0A1h)                                | 65         |

| Table 5-48 | OCW2 Register - Address: 020h (0A0h)                                | 6          |

| Table 5-49 | OCW3 Register - Address 020h (0A0h)                                 | 66         |

| Table 5-50 | IIR Register - Address: 020h (0A0h)                                 | 60         |

| Table 5-51 | ISR Register - Address 020h (0A0h)                                  | 66         |

| Table 5-52 | Poll Vector - Address 200h (0A0h)                                   | 66         |

## List of Tables (Cont.)

| Table 5-53 Control Word Format (Write Only)          | 6  |

|------------------------------------------------------|----|

| Table 5-54 Counter Latch Command Format (Write Only) | 67 |

| Table 5-55 Read-Back Command Format (Write Only)     | 67 |

| Table 5-56 Status Format                             | 68 |

| Table 5-57 I/O Port 61h (Port B)                     | 69 |

| Table 7-1 NAND Tree Test Mode Pins                   | 9: |

| Table 7-2 Drive High/Drive Low Test Mode Pin         | 94 |

Page xiv

## **System Power Management Controller**

#### 1.0 Features

- · Processor interface:

- Intel® 80486SX, DX, DX2, SLe, DX4, P24T, P24D

- AMD® 486DX, DX2, DXL, DXL2, Plus

- Cyrix® DX, DX2, M7

- CPU frequencies supported 20, 25, 33, 40 and 50MHz

- · Cache interface:

- Direct Mapped Cache

- Two banks interleaved or single bank non-interleaved

- 64, 128, 256 and 512K cache sizes

- Programmable wait states for L2 cache reads and writes

- 2-1-1-1 read burst and zero wait state write @ 33MHz

- No Valid bit required

- Supports CPUs with L1 write-back support

- DRAM interface:

- Up to 128MB main memory support

- Supports 256KB, 1MB, 4MB, and 16MB single- and double-sided SIMM modules

- Read page-hit timing of 3-2-2-2 at 33MHz

- Supports hidden, slow, and CAS-before-RAS refresh

- Four RAS lines to support four banks of DRAM

- Programmable wait states for DRAM reads and writes

- Enhanced DRAM configuration map

- · Power management:

- Support for SMM (System Management Mode) for system power management implementations

- Programmable power management

- Programmable wake-up events through hardware, software and external SMI source

- Multiple level GREEN support (NESTED\_GREEN)

- STPCLK# protocol support

- One programmable GREEN event timer

- ISA interface:

- 100% IBM® PC/AT® ISA compatible

- Integrates DMA, timer and interrupt controllers

- Optional PS/2 style IRQ1 and 12 latching

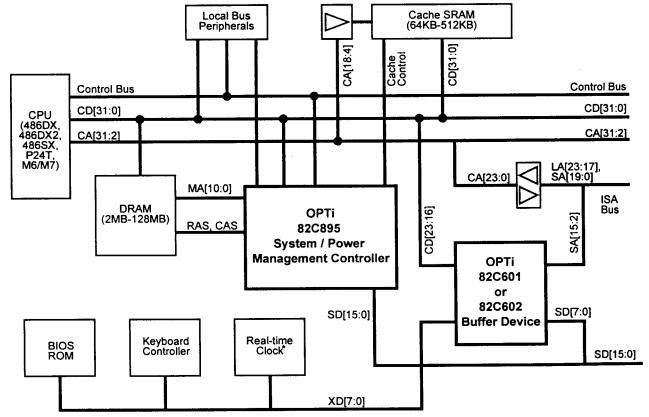

Figure 1-1 82C895 and 82C601/602-Based System Block Diagram

<sup>\*</sup>Included as a part of 82C602.

### Features (Cont.)

- VESA VL interface:

- Conforms to the VESA V2.0 specification

- Optional support for up to two VL masters

- Miscellaneous features:

- Full support for shadow RAM, write protection, L1/L2 cacheability for video, adapter and system BIOS

- Enhanced arbitration scheme

- Transparent 8042 emulation for fast CPU reset and GATEA20 generation

- · Packaging:

- Higher integration

- Reduced TTL count

- Low-power, high-speed 0.8-micron CMOS technology

- 208-pin PQFP (Plastic Quad Flat Pack)

### 2.0 Overview

The 82C895 provides a highly integrated solution for fully compatible, high performance PC/AT platforms. This chipset will support 486SX/DX/DX2/DX4 and P24T microprocessors

in the most cost effective and power efficient designs available today. For power users, this chipset offers optimum performance for systems running up to 50MHz.

Based fundamentally on OPTi's proven 82C801 and 82C802 design architectures, the 82C895 adds additional memory configurations and extensive power management control for the processor and other motherboard components.

The 82C895 supports the latest write-back processor designs from Intel, AMD, and Cyrix, as well as supporting the AT bus and VESA local bus for compatibility and performance. It also includes an 82C206-compatible Integrated Peripherals Controller (IPC), all in a single 208-pin PQFP (Plastic Quad Flat Pack) package for low cost.

#### 2.1 Power Management

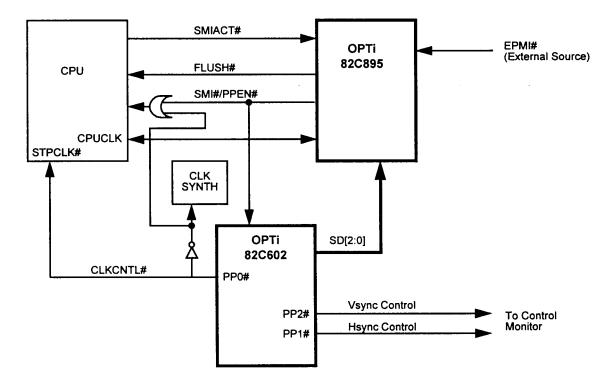

This block diagram exemplifies the flexibility of the 82C895/82C602 GREEN strategy. System designs can easily accommodate both SLe and non-SLe CPUs. If an Intel non-SLe CPU is used, SMI#, SMIACT#, and FLUSH# are no connects. One design can easily accommodate both types of processors with minimal changes for upgrades.

Figure 2-1 Power Management Block Diagram

## 3.0 Signal Definitions

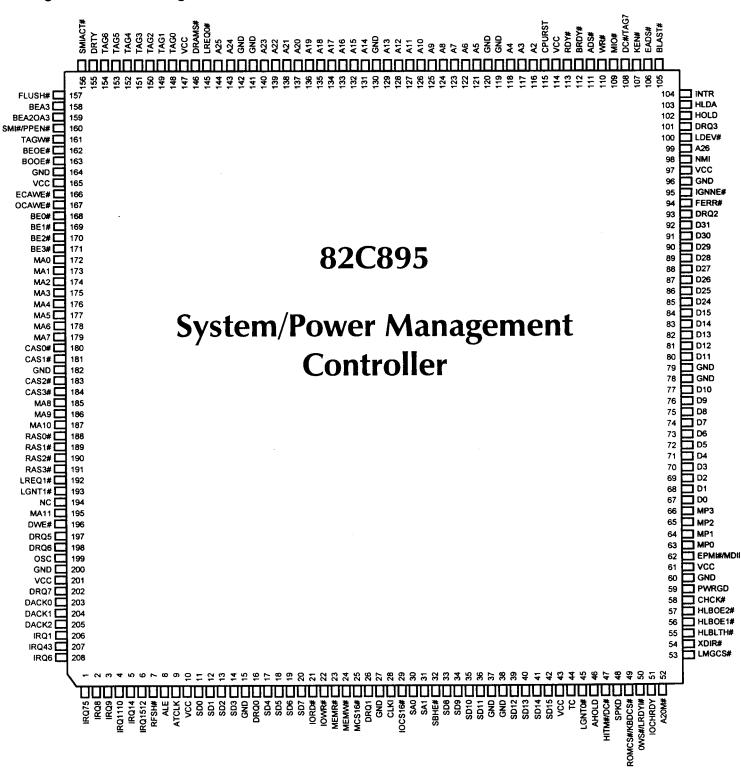

Figure 3-1 Pin Diagram

Table 3-1 **Numerical Pin**

| Table 3 | -1 Numerical  |

|---------|---------------|

| Pin No. | Pin Name      |

| 1       | IRQ75         |

| 2       | IRQ8          |

| 3       | IRQ9          |

| 4       | IRQ1110       |

| 5       | IRQ14         |

| 6       | IRQ1512       |

| 7       | RFSH#         |

| 8       | ALE           |

| 9       | ATCLK         |

| 10      | vcc           |

| 11      | SD0           |

| 12      | SD1           |

| 13      | SD2           |

| 14      | SD3           |

| 15      | GND           |

| 16      | DRQ0          |

| 17      | SD4           |

| 18      | SD5           |

| 19      | SD6           |

| 20      | SD7           |

| 21      | IORD#         |

| 22      | IOWR#         |

| 23      | MEMR#         |

| 24      | MEMW#         |

| 25      | MCS16#        |

| 26      | DRQ1          |

| 27      | GND           |

| 28      | CLK1          |

| 29      | IOCS16#       |

| 30      | SA0           |

| 31      | SA1           |

| 32      | SBHE#         |

| 33      | SD8           |

| 34      | SD9           |

| 35      | SD10          |

| 36      | SD11          |

| 37      | GND           |

| 38      | GND           |

| 39      | SD12          |

| 40      | SD13          |

| 41      | SD14          |

| 42      | SD15          |

| 43      | VCC           |

| 44      | TC            |

| 45      | LGNT0#        |

| 46      | AHOLD         |

| 47      | HITM#/DC#     |

| 48      | SPKD          |

| 49      | ROMCS#/KBDCS# |

| 50      | 0WS#/LRDYI#   |

| 51      | IOCHRDY       |

| 52      | A20M#         |

|         | <del></del>   |

| Pin No.                       | Pin Name                     |

|-------------------------------|------------------------------|

| 53                            | LMGCS#                       |

| 54                            | XDIR#                        |

| 55                            | HLBLTH#                      |

| 56                            | HLBOE1#                      |

| 57                            | HLBOE2#                      |

| 58                            | CHCK#                        |

| 59                            | PWRGD                        |

| 60                            | GND                          |

| 61                            | VCC                          |

| 62                            | EPMI#/MDIR#                  |

| 63                            | MP0                          |

| 64                            | MP1                          |

| 65                            | MP2                          |

| 66                            | MP3                          |

| 67                            | D0                           |

| 68                            | D1                           |

| 69                            | D2                           |

| 70                            | D3                           |

| 71                            | D4                           |

| 72                            | D5                           |

| 73                            | D6                           |

| 74                            | D7                           |

| 75                            | D8                           |

|                               | D9                           |

| 76<br>77                      | D10                          |

|                               | GND                          |

| 78                            |                              |

| 79                            | GND<br>D11                   |

| 80                            | D12                          |

| 81                            | D13                          |

| 82                            |                              |

| 83                            | D14                          |

| 84                            | D15                          |

| 85                            | D24                          |

| 86                            | D25                          |

| 87                            | D26                          |

| 88                            | D27                          |

| 89                            | D28                          |

| 90                            | D29                          |

| 91                            | D30                          |

| 92                            | D31                          |

| 93                            | DRQ2                         |

| 94                            | FERR#                        |

| 95                            | IGNNE#                       |

| 96                            | GND                          |

|                               | VCC                          |

| 97                            |                              |

| 98                            | NMI                          |

| 98<br>99                      | A26                          |

| 98<br>99<br>100               | A26<br>LDEV#                 |

| 98<br>99                      | A26<br>LDEV#<br>DRQ3         |

| 98<br>99<br>100<br>101<br>102 | A26<br>LDEV#<br>DRQ3<br>HOLD |

| 98<br>99<br>100<br>101        | A26<br>LDEV#<br>DRQ3         |

| Pin No. | Pin Name |

|---------|----------|

| 105     | BLAST#   |

| 106     | EADS#    |

| 107     | KEN#     |

| 108     | DC#/TAG7 |

| 109     | MIO#     |

| 110     | WR#      |

| 111     | ADS#     |

| 112     | BRDY#    |

| 113     | RDY#     |

| 114     | VCC      |

| 115     | CPURST   |

| 116     | A2       |

| 117     | A3       |

| 118     | A4       |

| 119     | GND      |

| 120     | GND      |

| 121     | A5       |

| 122     | A6       |

| 123     | A7       |

| 124     | A8       |

| 125     | A9       |

| 126     | A10      |

| 127     | A11      |

| 128     | A12      |

| 129     | A13      |

| 130     | GND      |

| 131     | A14      |

| 132     | A15      |

| 133     | A16      |

| 134     | A17      |

| 135     | A18      |

| 136     | A19      |

| 137     | A20      |

| 138     | A21      |

| 139     | A22      |

| 140     | A23      |

| 141     | GND      |

| 142     | GND      |

| 143     | A24      |

| 144     | A25      |

| 145     | LREQ0#   |

| 146     | DRAMS#   |

| 147     | vcc      |

| 148     | TAG0     |

| 149     | TAG1     |

| 150     | TAG2     |

| 151     | TAG3     |

| 152     | TAG4     |

| 153     | TAG5     |

| 154     | TAG6     |

| 155     | DRTY     |

|         | SMIACT#  |

| Pin No. | Pin Name   |

|---------|------------|

| 157     | FLUSH#     |

| 158     | BEA3       |

| 159     | BEA2OA3    |

| 160     | SMI#/PPEN# |

| 161     | TAGW#      |

| 162     | BEOE#      |

| 163     | BOOE#      |

| 164     | GND        |

| 165     | VCC        |

| 166     | ECAWE#     |

| 167     | OCAWE#     |

| 168     | BE0#       |

| 169     | BE1#       |

| 170     | BE2#       |

| 171     | BE3#       |

| 172     | MAO        |

| 173     | MA1        |

| 174     | MA2        |

| 175     | MA3        |

| 176     | MA4        |

| 177     | MA5        |

| 178     | MA6        |

| 179     | MA7        |

| 180     | CAS0#      |

| 181     | CAS1#      |

| 182     | GND        |

| 183     | CAS2#      |

| 184     | CAS3#      |

| 185     | MA8        |

| 186     | MA9        |

| 187     | MA10       |

| 188     | RAS0#      |

| 189     | RAS1#      |

| 190     | RAS2#      |

| 191     | RAS3#      |

| 192     | LREQ1#     |

| 193     | LGNT1#     |

| 194     | NC         |

| 195     | MA11       |

| 196     | DWE#       |

| 197     | DRQ5       |

| 198     | DRQ6       |

| 199     | OSC        |

| 200     | GND        |

| 201     | VCC        |

| 202     | DRQ7       |

| 203     | DACK0      |

| 204     | DACK1      |

| 205     | DACK2      |

| 206     | IRQ1       |

| 207     | IRQ43      |

| 208     | IRQ6       |

912-3000-015 Page 4

Table 3-2 Alphabetical Pin Cross-Reference List

| Table 3-2 | Alphabetica |

|-----------|-------------|

| Pin Name  | Pin No.     |

| A2        | 116         |

| A3        | 117         |

| A4        | 118         |

| A5        | 121         |

| A6        | 122         |

| A7        | 123         |

| A8        | 124         |

| A9        | 125         |

| A10       | 126         |

| A11       | 127         |

| A12       | 128         |

| A13       | 129         |

| A14       | 131         |

| A15       | 132         |

|           | 133         |

| A16       |             |

| A17       | 134         |

| A18       | 135         |

| A19       | 136         |

| A20       | 137         |

| A20M#     | 52          |

| A21       | 138         |

| A22       | 139         |

| A23       | 140         |

| A24       | 143         |

| A25       | 144         |

| A26       | 99          |

| ADS#      | 111         |

| AHOLD     | 46          |

| ALE       | 8           |

| ATCLK     | 9           |

| BEA2OA3   | 159         |

| BEA3      | 158         |

| BEOE#     | 162         |

| BEO#      | 168         |

| BE1#      | 169         |

| BE2#      | 170         |

| BE3#      | 171         |

| BLAST#    | 105         |

| BOOE#     | 163         |

|           |             |

| BRDY#     | 112         |

| CASO#     | 180         |

| CAS1#     | 181         |

| CAS2#     | 183         |

| CAS3#     | 184         |

| CHCK#     | 58          |

| CLK1      | 28          |

| CPURST    | 115         |

| D0        | 67          |

| D1        | 68          |

| D2        | 69          |

| D3        | 70          |

| D4        | 71          |

|           |             |

| Pin Cross-Reference List |           |  |  |  |

|--------------------------|-----------|--|--|--|

| Pin Name                 | Pin No.   |  |  |  |

| D5                       | 72        |  |  |  |

| D6                       | 73        |  |  |  |

| D7                       | 74        |  |  |  |

| D8                       | 75        |  |  |  |

| D9                       | 76        |  |  |  |

| D10                      | 77        |  |  |  |

| D11                      | 80        |  |  |  |

| D12                      | 81        |  |  |  |

| D13                      | 82        |  |  |  |

| D14                      | 83        |  |  |  |

| D15                      | 84        |  |  |  |

| D24                      | 85        |  |  |  |

| D25                      | 86        |  |  |  |

| D26                      | 87        |  |  |  |

| D27                      | 88        |  |  |  |

| D28                      | 89        |  |  |  |

| D29                      | 90        |  |  |  |

| D30                      | 91        |  |  |  |

| D31                      | 92        |  |  |  |

| DACK0                    | 203       |  |  |  |

| DACK1                    | 204       |  |  |  |

| DACK2                    | 205       |  |  |  |

| DC#/TAG7                 | 108       |  |  |  |

| DRAMS#                   | 146       |  |  |  |

| DRQ0                     | 16        |  |  |  |

| DRQ1                     | 26        |  |  |  |

| DRQ2                     | 93        |  |  |  |

| DRQ3                     | 101       |  |  |  |

| DRQ5                     | 197       |  |  |  |

| DRQ6                     | 198       |  |  |  |

| DRQ7                     | 202       |  |  |  |

|                          |           |  |  |  |

| DRTY                     | 155       |  |  |  |

| DWE#<br>EADS#            | 196       |  |  |  |

|                          | 106       |  |  |  |

| ECAWE#                   | 166<br>62 |  |  |  |

| EPMI#/MDIR#              |           |  |  |  |

| FERR#                    | 94        |  |  |  |

| FLUSH#                   | 157       |  |  |  |

| GND                      | 15        |  |  |  |

| GND                      | 27        |  |  |  |

| GND                      | 37        |  |  |  |

| GND                      | 38        |  |  |  |

| GND                      | 60        |  |  |  |

| GND                      | 78        |  |  |  |

| GND                      | 79        |  |  |  |

| GND                      | 96        |  |  |  |

| GND                      | 119       |  |  |  |

| GND                      | 120       |  |  |  |

| GND                      | 130       |  |  |  |

| GND                      | 141       |  |  |  |

| GND                      | 142       |  |  |  |

| GND                      | 164       |  |  |  |

| Pin Name  | Pin No. |

|-----------|---------|

| GND       | 182     |

| GND       | 200     |

| HITM#/DC# | 47      |

| HLBOE1#   | 56      |

| HLBOE2#   | 57      |

| HLBLTH#   | 55      |

| HLDA      | 103     |

| HOLD      | 102     |

| IGNNE#    | 95      |

| INTR      | 104     |

| IOCHRDY   | 51      |

| IOCS16#   | 29      |

| IORD#     | 21      |

| IOWR#     | 22      |

| IRQ1      | 206     |

| IRQ1110   | 4       |

| IRQ14     | 5       |

| IRQ1512   | 6       |

| IRQ43     | 207     |

| IRQ6      | 208     |

| IRQ75     | 1       |

| IRQ8      | 2       |

| IRQ9      | 3       |

| KEN#      | 107     |

| LDEV#     | 100     |

| LGNT0#    | 45      |

| LGNT1#    | 193     |

| LMGCS#    | 53      |

| LREQ0#    | 145     |

| LREQ1#    | 192     |

| MA0       | 172     |

| MA1       | 173     |

| MA2       | 174     |

| MA3       | 175     |

| MA4       | 176     |

| MA5       | 177     |

| MA6       | 178     |

| MA7       | 179     |

| MA8       | 185     |

| MA9       | 186     |

| MA10      | 187     |

| MA11      | 195     |

| MCS16#    | 25      |

| MEMR#     | 23      |

| MEMW#     | 24      |

| MIO#      | 109     |

| MP0       | 63      |

| MP1       | 64      |

| MP2       | 65      |

|           | 66      |

| MP3<br>NC | 194     |

| NMI       | 98      |

| 141411    |         |

| Pin Name      | Pin No. |

|---------------|---------|

| OCAWE#        | 167     |

| osc           | 199     |

| PWRGD         | 59      |

| RAS0#         | 188     |

| RAS1#         | 189     |

| RAS2#         | 190     |

| RAS3#         | 191     |

| RDY#          | 113     |

| RFSH#         | 7       |

| ROMCS#/KBDCS# | 49      |

| SA0           | 30      |

| SA1           | 31      |

| SBHE#         | 32      |

|               | 11      |

| SD0           | 12      |

| SD1           |         |

| SD2           | 13      |

| SD3           | 14      |

| SD4           | 17      |

| SD5           | 18      |

| SD6           | 19      |

| SD7           | 20      |

| SD8           | 33      |

| SD9           | 34      |

| SD10          | 35      |

| SD11          | 36      |

| SD12          | 39      |

| SD13          | 40      |

| SD14          | 41      |

| SD15          | 42      |

| SMIACT#       | 156     |

| SMI#/PPEN#    | 160     |

| SPKD          | 48      |

| TAG0          | 148     |

| TAG1          | 149     |

| TAG2          | 150     |

| TAG3          | 151     |

| TAG4          | 152     |

| TAG5          | 153     |

| TAG6          | 154     |

| TAGW#         | 161     |

| TC            | 44      |

| vcc           | 10      |

| VCC           | 43      |

| VCC           | 61      |

| VCC           | 97      |

| VCC           | 114     |

| vcc           | 147     |

| VCC           | 165     |

| VCC           | 201     |

| WR#           | 110     |

| XDIR#         | 54      |

| 0WS#/LRDY#    | 50      |

| UVVS#/LKUT#   | 1 30    |

## 3.1 Signal Descriptions

## 3.1.1 CPU Interface Signals

| Signal Name          | Pin No.                   | Signal<br>Type                                                                                                                                                                                                                                            | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[26:24]             | 99, 144,<br>143           | 1                                                                                                                                                                                                                                                         | CPU address lines 26, 25, and 24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A[23:17]             | 140:134                   | I/O                                                                                                                                                                                                                                                       | CPU address lines 23 through 17: These signals are inputs during CPU, refresh, and master cycles and are outputs during DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A[16:8]              | 133:131,<br>129:124       | I/O                                                                                                                                                                                                                                                       | CPU address lines 16 through 8: These signals are inputs during non-DMA cycles. A[16:9] become outputs which transmit DMA address lines A[16:9] by latching SD[7:0] during 16-bit DMA cycles. A[15:8] transmit DMA address lines A[15:8] by latching SD[7:0] during 8-bit DMA cycles.                                                                                                                                                                                                                                                                                                                                       |

| A[7:2]               | 123:121,<br>118:116       | 1/0                                                                                                                                                                                                                                                       | CPU address lines 7 through 2: These signals are outputs during DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DRAMS#               | 146                       | ı                                                                                                                                                                                                                                                         | DRAM controller upper address decode input. All the CPU address lines are not decoded by the 82C895. An external decoder or an upper address line should be connected to this input.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D[31:24],<br>D[15:0] | 92:85,<br>84:80,<br>77:67 | 1/0                                                                                                                                                                                                                                                       | CPU data bus bits 31 through 24 and 15 through 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BE[3:0]#             | 171:168                   | 1/0                                                                                                                                                                                                                                                       | The byte enable signals indicate active bytes during read and write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MIO#                 | 109                       | 1/0                                                                                                                                                                                                                                                       | Memory or I/O cycle definition pin: When MIO# is high, it indicates a memory cycle and, if low, an I/O cycle. MIO# becomes an output during master and DMA cycles for local device accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DC#/TAG7 108         | I/O                       | CPU data / code cycle status or Tag bit 7: As DC#, this pin is used to indicate data transfer operations when high, or control operations (code fetch, halt, etc.) when low. As TAG7, this pin is used to expand the cacheable address range of the DRAM. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                      |                           |                                                                                                                                                                                                                                                           | When MP2 is sampled high during reset, this pin operates as DC#. When MP2 is sampled low during reset, it operates as TAG7. TAG7's functionality may be ignored by setting Index Register 20h, bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                      |                           |                                                                                                                                                                                                                                                           | MP2 Function 1 D/C# 0 TAG7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HITM#/DC#            | 47                        |                                                                                                                                                                                                                                                           | L1 write-back hit or DC#: This pin is an active low input from an L1 write-back capable CPU (such as the P24T) used to indicate that the current cache inquiry address has been found in the internal cache and that dirty data exists in that cache line. This pin is either HITM#, or both HITM# and DC#. This pin can be in either configuration by the sampling of MP2 during reset. When strapped low, it functions as HITM# during inquiry cycles and DC# for all other cycles. In this configuration, the DC# and HITM# signals from the CPU must be ANDed into this pin. The strapping option also affects Pin 108. |

|                      |                           |                                                                                                                                                                                                                                                           | MP2 Function 1 HITM# 0 HITM# and DC#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Page 6 912-3000-015

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                                                                                                                                            |

|-------------|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WR#         | 110     | I/O            | Write or read cycle definition pin: If WR# is high, it indicates a write cycle and, if low, a read cycle. WR# becomes an output during master and DMA cycles for local device accesses.                       |

| ADS#        | 111     | 1/0            | Address status input indicates that a valid bus cycle definition and addresses are available on the cycle definition pins and address bus. It becomes an output during master or DMA cycles to the local bus. |

| RDY#        | 113     | 1/0            | RDY# indicates that the current non-bus cycle is complete. RDY# becomes an input during local device cycles.                                                                                                  |

| BRDY#       | 112     | 1/0            | BRDY# indicates the completion of a bus cycle.                                                                                                                                                                |

| BLAST#      | 105     | ı              | BLAST# indicates the end of a CPU burst cycle.                                                                                                                                                                |

| EADS#       | 106     | 0              | External address: EADS#, when asserted, indicates that an external address has been driven onto the CPU address lines. This address is used to perform an internal cache snoop cycle.                         |

| AHOLD       | 46      | 0              | Address Hold: This pin is driven to force the CPU to float address lines A[31:2] on the next clock cycle.                                                                                                     |

| A20M#       | 52      | 0              | Address bit 20 mask: A20M# is asserted to force the CPU for real mode operation. Up reset, this pin is driven high and can be asserted by writing to Port 92h or keyboard registers.                          |

## 3.1.2 VESA Local Bus Interface Signals

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                                                                                                                                       |

|-------------|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDEV#       | 100     | 1              | Local bus device cycle: LDEV# indicates that a local bus device has captured the current cycle. This signal is sampled by the 82C895 at the end of the first T2 or at the end of the second T2 at 50MHz. |

| LREQ0#      | 145     | ı              | Local bus request 0 input from the VESA local bus master.                                                                                                                                                |

| LGNT0#      | 45      | 0              | Local bus grant 0 output to the VESA local bus master.                                                                                                                                                   |

| LREQ1#      | 192     | ı              | Local bus request 1 input from the VESA local bus master. MP1 must be pulled down with a 1K resistor (refer to MP[3:0] signal description).                                                              |

| LGNT1#      | 193     | 0              | Local bus grant 1 output to the VESA local bus master. MP1 must be pulled down with a 1K resistor (refer to MP[3:0] signal description).                                                                 |

|             |         |                | MP1         Pin 192         Pin 193           0         LREQ1#         LGNT1#           1         Reserved         Reserved                                                                              |

|             |         |                | Function of pins 192 and 193 are dependent on MP1 sampling during reset.                                                                                                                                 |

## 3.1.3 AT Bus Interface Signals

| Signal Name | Pin No.                             | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SA[1:0]     | 31:30                               | 1/0            | ISA bus address lines 1 and 0: These pins are inputs during master cycles and outputs during CPU, DMA, or refresh cycles.                                                                                                                                                                                                                                                                                                              |

| SD[15:0]    | 42:39,<br>36:33,<br>20:17,<br>14:11 | I/O            | ISA bus data lines 15 through 0.                                                                                                                                                                                                                                                                                                                                                                                                       |

| ALE         | 8                                   | 0              | ISA bus address latch enable: When asserted, ALE indicates that the SBHE#, SA and LA lines are valid on the ISA bus.                                                                                                                                                                                                                                                                                                                   |

| SBHE#       | 32                                  | 1/0            | ISA bus byte high enable: When asserted, SBHE# indicates that a byte is being transferred on SD[15:8] of the ISA data bus. During master cycles this pin is an input, otherwise it is always an output from the 82C895.                                                                                                                                                                                                                |

| IORD#       | 21                                  | 1/0            | ISA I/O read command: This pin is an input during master cycles and an output during CPU and DMA cycles.                                                                                                                                                                                                                                                                                                                               |

| IOWR#       | 22                                  | I/O            | ISA I/O write command: This pin is an input during master cycles and an output during CPU and DMA cycles.                                                                                                                                                                                                                                                                                                                              |

| MEMR#       | 23                                  | I/O            | ISA memory read command: This pin is an input during master cycles and an output during CPU and DMA cycles.                                                                                                                                                                                                                                                                                                                            |

| MEMW#       | 24                                  | 1/0            | ISA memory write command: This pin is an input during master cycles and an output during CPU and DMA cycles.                                                                                                                                                                                                                                                                                                                           |

| LMGCS#      | 53                                  | 0              | Memory space below one megabyte indicator: This signal is asserted during ISA refresh or when the address lines 20 to 26 and DRAMS# are low. This signal should be wired OR'd externally with MEMR# and MEMW# to generate SMEMR# and SMEMW#, respectively.                                                                                                                                                                             |

| MEMCS16#    | 25                                  | I/O            | ISA 16-bit memory chip select: This is driven by an ISA slave to indicate that it is a 16-bit memory device. This is driven low during master cycles.                                                                                                                                                                                                                                                                                  |

| IOCS16#     | 29                                  | I              | ISA 16-bit I/O chip select: This is driven by an ISA slave to indicate that it supports 16-bit I/O bus cycles.                                                                                                                                                                                                                                                                                                                         |

| IOCHRDY     | 51                                  | I/O            | I/O channel ready: This input is from the ISA bus indicating that additional time is required to complete the current ISA cycle.                                                                                                                                                                                                                                                                                                       |

| 0WS#/LRDYI# | 50                                  | I              | Zero wait state input from ISA bus or local ready: This pin is either 0WS# or LRDYI# and is determined by a strapping option of MP0.  0WS is asserted by the ISA slave to indicate that the system controller can shorten the current ISA cycle. If configured as LRDYI#, the VESA local by LRDY# signal should be connected to this input. Consequently, the 82C802G will assert CPURDY# in response to the LRDY# from the VL device. |

|             |                                     |                | MP0 is sampled during reset to determine the function of this pin.  MP0 Pin 50  0 LRDYI#  1 0WS#                                                                                                                                                                                                                                                                                                                                       |

Page 8 912-3000-015

| Signal Name          | Pin No. | Signal<br>Type                                                                                                                                                                                             | Signal Description                                                                                                                                       |

|----------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROMCS#/ 49<br>KBDCS# | 0       | BIOS ROM output enable: During memory cycles, this signal is used for system BIOS ROM accesses and can be either 8- or 16-bit. It will be asserted from the end of the first T2 to the end of the last T2. |                                                                                                                                                          |

|                      |         |                                                                                                                                                                                                            | Keyboard Controller Chip Select: This is also driven during I/O accesses to port 60h or 64h and can be connected to the keyboard controller chip select. |

### 3.1.4 Bus Arbitration Interface Signals

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                                                                                                     |

|-------------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFSH#       | 7       | 1/0            | Refresh: When RFSH# is active, it indicates that a refresh cycle is in progress. As an input, this signal is driven by the ISA bus masters to initiate refresh cycles. |

| HOLD        | 102     | 0              | Hold: This signal is driven to the CPU to request the CPU bus.                                                                                                         |

| HLDA        | 103     | ı              | Hold acknowledge must be driven by the CPU to grant the CPU bus to ISA or VL devices.                                                                                  |

## 3.1.5 Numeric Processor Interface Signals

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                                                                                           |

|-------------|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FERR#       | 94      | ı              | Numeric coprocessor error: FERR# is driven by the CPU when a floating point error occurs. This active low signal is used to generate IGNNE# for the 486 CPU. |

| IGNNE#      | 95      | 0              | Ignore numeric coprocessor error: This signal goes active once FERR# is active. An I/O write to Port F0h or a CPU reset will force this signal inactive.     |

## 3.1.6 Cache Interface Signals

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                                                                                                                                         |  |

|-------------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| KEN#        | 107     | 0              | Cacheable or non-cacheable status for the 486 CPU's internal cache: KEN# is asserted if the current cycle is cacheable in the CPU internal cache.                                                          |  |

| FLUSH#      | 157     | 0              | Flush CPU internal cache: FLUSH# is driven active before an SMM occurs an during a wake up from SMI_GREEN mode to flush the CPU internal cache.                                                            |  |

| BEA3        | 158     | 0              | Cache address line A3: In the single bank cache, this pin is connected to the A3 line of the cache RAM. In the double-bank interleaved cache, it is connected to the even bank A3 line of the cache RAM.   |  |

| BEA2OA3     | 159     | 0              | Cache address line A2/A3: In the single bank cache, this pin is connected to the A2 line of the cache RAM. In the double-bank interleaved cache, it is connected to the odd bank A3 line of the cache RAM. |  |