## 1.0 REDWOOD 1 Pin List

NOTE -There are five separate and isolated VDD pins on REDWOOD 1 that can be connected to individual power sources. The number in the "GROUP" column designates which VDD power pins are used to supply power to each I/O pin. The core power pins are separate from the I/O power pins.

### 1.1 Clock and Reset Interface

| PIN NAME                       | I/O       | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                           | GROUP# | 176PIN# | 160PIN# |

|--------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|---------|

| CLK1X2X                        | I         | 1X or 2X Clock Input: This input clock is the main system clock. This option is determined by index register 100H, bit 1. If the bit is high, the input is 2X clock; if low, it is 1X clock.                                                                                                                                              | 3      | 59      | 53      |

| CPUCLKO1                       | O<br>12mA | CPU Clock Output 1: This output is always 1X clock and can be programmed to be running regardless of STOPCLK state.                                                                                                                                                                                                                       | 1      | 167     | 153     |

| CPUCLKO2                       | O<br>8mA  | CPU Clock Output 2: It can be either 1X clock for 486 type CPU or 2X clock for 386 type CPU depending upon index register 100H, bit 1. This is the output should be connected to CPU Clock input.                                                                                                                                         | 1      | 165     | 151     |

| RCRST#                         | I         | RC-RESET #: This input is used to reset the REDWOOD 1's Power Management Controller and RTC when power is first applied to the chip.                                                                                                                                                                                                      | 3      | 56      | 50      |

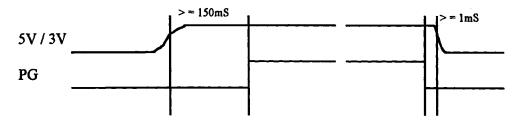

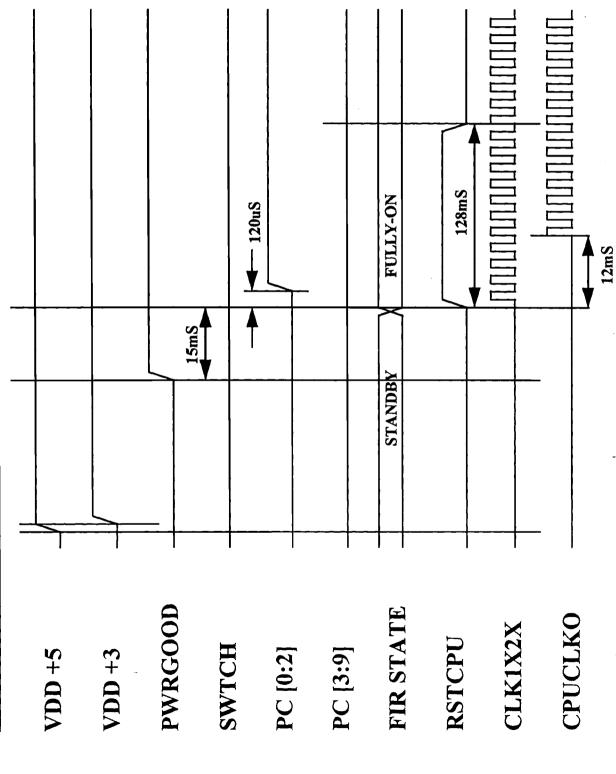

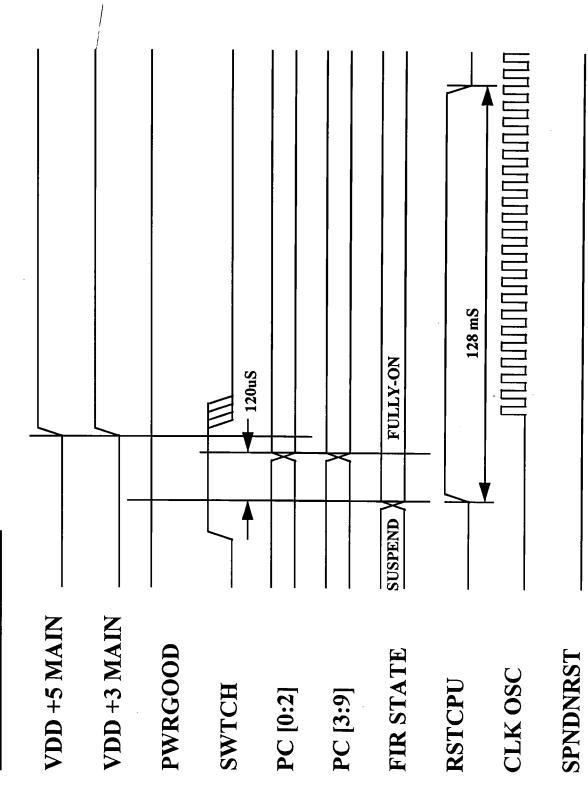

| PWRGOOD                        | I         | Power Good Input: This input causes a complete system reset. It is driven low by the PWRGOOD signal from the power supply or a reset switch. On power up, PWRGOOD going from L→H indicates external VCC is stable and will wakeup the RW core from Standby →On. If PWRGOOD goes L, it will drive the chip back to Standby.                | 3      | 55      | 49      |

| RSTDRV#                        | O<br>4mA  | AT Bus Reset Output #: This output provides a system reset.                                                                                                                                                                                                                                                                               | 3      | 65      | 59      |

| RSTCPU<br>(RSTDRV)<br>(RSTNPU) | O<br>12mA | CPU Reset Output: This is the reset output to the CPU and AT Bus. This output includes hardware generated reset only.  This pin will become numeric coprocessor interface pin RSTNPU if index register 100H, bit 1 is high (386DX mode) and index register 112H, bit 14 is also high. Note: Use SRESET for CPU with only 1 Reset Pin I/P. | 1      | 34      | 32      |

| SPNDNRST                       | O<br>4mA  | Suspend Not Reset: This output provides a reset equivalent to RSTDRV except when in Suspend Mode. Any device not powered down during Suspend Mode should use this reset.                                                                                                                                                                  | 3      | 67      | 61      |

### 1.2 CPU Interface

| PIN NAME   | I/O        | PIN DESCRIPTION                                                                                                                                            | GROUP | 176PIN#                               | 160PIN#                              |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------|--------------------------------------|

| A<31,27:2> | I/O<br>4mA | CPU/VESA local bus. They will become outputs during DMA or ISA bus master cycles.                                                                          | 1     | 172, 3:7,<br>9:15,<br>17:26,<br>28:31 | 158,1:5,7:<br>13,<br>15:24,<br>26:29 |

| BE<3:0>#   | I/O<br>4mA | CPU Byte Enables <3:0>#: These inputs control the selection of individual bytes of data. These signals become outputs during DMA or ISA bus master cycles. |       | 168:171                               | 154:157                              |

| ADS#             | I/O<br>4mA | Address Status #: This input indicates the presence of a valid address and cycle definition from the CPU/VL Bus Master. This | 1        | 155 | 141   |

|------------------|------------|------------------------------------------------------------------------------------------------------------------------------|----------|-----|-------|

|                  | 4IIIA      | signal becomes an output during DMA or ISA bus master cycles.                                                                | i:       |     |       |

| RDY#             | IVO        | Ready #: This output to the CPU indicates completion of the current                                                          | 1        | 156 | 142   |

|                  | 4mA        | bus cycle. This pin is also an input to monitor completion of any                                                            |          |     |       |

|                  |            | non-system memory cycles.                                                                                                    |          |     |       |

| BRDY#            | I/O        | Burst Ready #: This output to the 486 CPU indicates completion of                                                            | 1        | 153 | 139   |

|                  | 4mA        | the current burst access. This pin is also an input to monitor the                                                           | -        |     |       |

|                  |            | completion of local bus cycles.                                                                                              |          |     |       |

| (PEREQO)         |            | This pin will become numeric coprocessor interface pin PEREQO if                                                             |          | ı   |       |

|                  |            | index register 100H, bit 1 is high (386DX mode).                                                                             |          | 1   |       |

| BLAST#           | I/O        | Burst Last #: This input from the 486 CPU indicates that the next                                                            | 1        | 160 | 146   |

|                  | 4mA        | BRDY# will complete the current burst cycle.                                                                                 |          |     |       |

| (BUSYO#)         |            | This pin is numeric coprocessor interface pin BUSYO# if index                                                                |          |     |       |

| (- · · · · · · ) |            | register 100H, bit 1 is high.                                                                                                |          |     |       |

| M/IO#            | I/O        | Memory/IO #: This input from the CPU/VL Bus Master indicates                                                                 | 1        | 159 | 145   |

|                  | 4mA        | whether the current cycle is a Memory or I/O access. This pin is an                                                          | -        | 100 | 2.0   |

|                  |            | output during ISA Master or DMA mode.                                                                                        |          |     |       |

| D/C#             | I/O        | Data/Code #: This input from the CPU/VL Bus Master indicates                                                                 | 1        | 158 | 144   |

| Di Cii           | 4mA        | whether the current cycle is a Data or Code access. This pin is an                                                           | •        | 150 | • • • |

|                  | '          | output during ISA Master or DMA mode.                                                                                        |          |     |       |

| W/R#             | 1/0        | Write/Read #: This input from the CPU/VL Bus Master indicates                                                                | 1        | 157 | 143   |

| W/ICH            | 4mA        | whether the current cycle is a Write or Read access. This pin is an                                                          | •        | 15, | 143   |

|                  | 71123      | output during ISA Master or DMA mode.                                                                                        |          |     |       |

| EADS#            | 0          | External Address Strobe #: This output to the 486 CPU indicates                                                              | 1        | 161 | 147   |

| EADS#            | 2mA        | that a valid address has been driven onto the CPU address bus for                                                            | 1        | 101 | 14/   |

|                  | 211124     | internal cache snoop cycle.                                                                                                  |          |     |       |

| (ERRORO#)        |            | This pin will become numeric coprocessor interface pin ERROR# if                                                             |          |     |       |

| (EKKOKO#)        |            | index register 100H, bit 1 is high (386DX mode)                                                                              |          |     |       |

| KEN#             | 0          | Cache Enable #: This output to the 486 CPU indicates that the                                                                | 1        | 40  | 38    |

| KEIN#            | 2mA        | current bus cycle in cacheable.                                                                                              | 1        | 40  | 30    |

| HLDA             | I          | Hold Acknowledge: This input from the CPU indicates a Hold                                                                   | 1        | 163 | 149   |

| ILDA             | *          | Acknowledge state.                                                                                                           | 1        | 103 | 149   |

| A20M#            | 0          | Address Bit 20 Mask #: This output to the 486 CPU indicates that                                                             | 1        | 162 | 148   |

|                  | 2mA        | the CPU should mask A20 in order to emulate the 8086 address wrap                                                            |          |     |       |

|                  |            | around.                                                                                                                      |          | l   |       |

| SMIACT#          | I          | System Management Interrupt Active#: This input from some CPUs                                                               | 1        | 33  | 31    |

| Diving to 1 "    | 1          | indicates that an SMI routine is in progress.                                                                                | -        | "   | "     |

| (SMIADS#)        | I          | System Management Interrupt Address Status #: This input indicates                                                           |          |     |       |

| (OIMI IOO!!)     | 1          | the presentation of a valid SMI address and cycle definition on some                                                         |          | Ì   |       |

|                  |            | CPU's. This function can be enabled by programming index register                                                            |          |     |       |

|                  |            | 103H, bit 15 high.                                                                                                           |          |     |       |

| FLUSH#           | 0          | CPU Cache Flush #: This output drives the Flush# of the CPU and is                                                           | 1        | 35  | 33    |

| 1 EODII,         | 2mA        | used to flush CPU internal cache.                                                                                            | _        |     |       |

| (IRQ13)          |            | This pin will become numeric coprocessor interface pin IRQ13 if                                                              |          |     | 1     |

| (11(Q13)         |            | index register 100H, bit 1 and index register 112H, bit 14 are high.                                                         |          |     |       |

| SMI#             | I/O        | System Management Interrupt #: This output indicates a system                                                                | 1        | 37  | 35    |

| (PMI)            | 4mA        | management interrupt and is used to invoke the system management                                                             | <b>1</b> | ''  |       |

| (1 1411)         | 7111/3     | mode.                                                                                                                        |          |     |       |

| NIMI             | I          | Non-Maskable Interrupt input: This input from REDWOOD 2                                                                      | 1        | 173 | 159   |

| NMI              | 1          | indicates a non-maskable interrupt condition.                                                                                | 1        | 1/3 | 129   |

| (EVTACTO)        |            | EXTACTO input: This pin can be programmed to be EXTACTO                                                                      |          |     |       |

| (EXTACT0)        |            |                                                                                                                              |          |     |       |

|                  |            | input if index register 112H, bit 12 is high.                                                                                | ł        | l   | L     |

| STPCLK#          | O<br>4mA | Stop Clock #: For some CPU's, this output indicates a stop clock request to the CPU. | 1   | 38  | 36  |

|------------------|----------|--------------------------------------------------------------------------------------|-----|-----|-----|

| SRESET           | O        | Soft Reset: This output to some CPU's indicates a software                           | 1   |     | 20  |

| SICESE I         | 2mA      | generated CPU reset request. It will be also active during a hardware                | 1   | 32  | 30  |

|                  |          | generated reset condition. Note: Use this pin for CPU's with a single                |     |     |     |

|                  |          | reset pin.                                                                           |     |     |     |

| LOCK#            | I/O      | LOCK#: This input pin from the CPU indicates the current cycle is                    | 1   | 149 | 135 |

|                  | 4mA      | locked. However, this is only valid when index register 100H bit 4 is                | . • | 147 | 155 |

|                  |          | low.                                                                                 |     |     |     |

| (CA13)           |          | If index register 100H, bit 4 is high, this pin becomes output mode                  |     |     |     |

| (TAGCS#)         |          | and can be either used as CA13 (index register 110H, bit 2 high) or                  |     |     |     |

|                  |          | TAG RAM Chip Select # (index register 110H, bit 2 low)                               |     |     |     |

| (BUSYI#)         |          | This pin is numeric coprocessor interface pin BUSYI# input if index                  |     |     |     |

|                  |          | register 100H, bit 1 is high.                                                        |     |     |     |

| HITM#            | I        | HITM#: HITM# indicates the snoop cycle hits a modified line in                       | 1   | 150 | 136 |

|                  |          | the level 1 cache inside the CPU.                                                    |     |     |     |

| (ERRORI#)        |          | This pin is numeric coprocessor interface pin ERRORI# if index                       |     |     |     |

|                  |          | register 100H, bit 1 is high.                                                        |     |     |     |

| (LOCK#)          |          | If index register 110H, bit 3 is high, this pin becomes LOCK#.                       |     |     |     |

| CACHE#           | I        | CACHE#: CACHE# indicates a cache operation. Together with                            | 1   | 152 | 138 |

|                  |          | ADS# and W/R#, they mark the beginning of a write back cycle.                        |     |     |     |

| (PEREQI)         |          | This pin is numeric coprocessor interface pin PEREQI if index                        |     |     |     |

|                  |          | register 100H, bit 1 is high.                                                        |     |     |     |

| (PCD)            |          | If index register 100H, bit 4 is low, then this pin becomes PCD from                 |     |     |     |

|                  | ļ        | the CPU.                                                                             |     |     |     |

| WB/WT#           | 0        | WriteBack / WriteThrough#: This output pin is used to define a                       | 1   | 151 | 137 |

|                  | 4mA      | particular line as write back or write through. It is used to mark a                 |     |     |     |

| (A) (T) D I I II |          | write protect line as write through                                                  |     |     |     |

| (SMIRDY#)        |          | System Management Interrupt Ready #: For some CPU's, this output                     |     |     |     |

|                  |          | indicates completion of a SMI bus cycle. This function will be                       |     |     |     |

|                  | <u> </u> | enabled by index register 103H, bit 9 being low.                                     | _   |     |     |

# 1.3 DRAM Interface

| PIN NAME                    | I/O         | PIN DESCRIPTION                                                                                                                                                                                                                                     | GROUP | 176PIN#        | 160PIN#  |

|-----------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|----------|

| DRAMWE#                     | O<br>12mA   | DRAM Write Enable #: This output drives Write Enable for all DRAM's.                                                                                                                                                                                | 2     | 93             | 83       |

| RAS<2:0>#<br>(RAS<4,2,0>#)  | O<br>12mA   | Row Address Strobes <2:0>#: These outputs drive the RAS# inputs on DRAM bank pairs 2 to 0. If index register 20BH, bit 0 is high, then RAS1# becomes RAS2#, and RAS2# becomes RAS4# logically.                                                      | 2     | 104:106        | 94,95,96 |

| CAS<3:0>A#                  | O<br>12mA   | Column Address Strobes <3:0># Group A: These outputs drive the CAS# inputs on DRAM bytes 3 to 0 in even banks (banks 0,2,4).                                                                                                                        | 2     | 98,<br>100:102 | 88,90:92 |

| CAS<3:0>B#<br>(RAS<5,3,1>#) | O<br>12mA   | Column Address Strobes <3:0># Group B: These outputs drive the CAS# inputs on DRAM bytes 3 to 0 in odd banks (banks 1,3,5). If index register 20BH, bit 0 is high, then CAS0B# is RAS1#, CAS1B# is RAS3#, CAS2B# is RAS5# and CAS3B# is No Connect. | 2     | 94:97          | 84:87    |

| MA0A                        | I/O<br>12mA | Memory Address 0 A: These outputs drive the MA0 line for all DRAM's in even banks.                                                                                                                                                                  | 2     | 121            | 111      |

| MA0B                        | I/O<br>12mA | Memory Address 0 B: These outputs drive the MA0 line for all DRAM's in odd banks.                                                                                                                                                                   | 2     | 120            | 110      |

# **REDWOOD 1 Pin List**

Preliminary

| MA<11:1> | I/O<br>12mA | Memory Addresses <11:1>: These outputs drive the MA lines for all DRAM's. They are also used as RC-RESET configuration inputs during power up.        | 2 | 107:111,<br>113:118 | 97:101,<br>103:108 |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|--------------------|

| MDEN#    | O<br>4mA    | Memory Data buffer Enables: This signal is used to control the enable pins of the optional Memory Data Buffers. Use DRAMWE# as the direction control. |   | 92                  | 82                 |

## 1.4 External Cache Interface

| PIN NAME               | I/O    | PIN DESCRIPTION                                                         | GROUP | 176PIN#  | 160PIN#  |

|------------------------|--------|-------------------------------------------------------------------------|-------|----------|----------|

| CWE<1:0>#              | 0      | Cache Write Enable <1:0> #: Cache Data RAM Write Enables for            | 5     | 130, 129 | 120,119  |

|                        | 12mA   | bank 1 and bank 0.                                                      |       |          |          |

| COE<1:0>#              | 0      | Cache Output Enable <1:0>#: Cache Data RAM Output Enables for           | 1     | 42, 41   | 40,39    |

|                        | 12mA   | bank 1 and bank 0.                                                      |       |          |          |

| CCS<3:0>#              | 0      | Cache Chip Select <3:0>#: Cache Data RAM Chip Selects for 4             | 5     | 125:122  | 115:112  |

| (3:FBE#)               | 4mAO   | individual bytes. These pins can also be used as FBE# output for        |       |          |          |

| (2:ACPWR)              | I      | level 2 cache control, ACPWR, VLB and LB inputs for the power           |       |          |          |

| (1:VLB)                |        | management controller if index register 110H, bit 4 is high.            |       |          |          |

| (0:LB)                 |        |                                                                         |       |          |          |

| CA3A                   | 0      | Cache Address bit 3 A: Cache Data RAM address bit 3 for odd             | 5     | 127      | 117      |

| (CA3)                  | 8mA    | bank when cache interleave is enabled. Or it is Cache address 3 if      |       |          |          |

|                        |        | only one bank is used.                                                  |       |          |          |

| CA3B                   | 0      | Cache Address bit 3 B: Cache Data RAM address bit 3 for even            | 5     | 128      | 118      |

| (CA2)                  | 8mA    | bank when cache interleave is enabled. This pin becomes Cache           |       |          |          |

|                        | ļ      | address 2 if only single bank of SRAM is used.                          |       |          | 100 100  |

| TAGD<7:0>              | I/O    | TAG Data <7:0>: TAG RAM Data bits.                                      | 5     | 136:139, | 122:125, |

| (7:HIT#)               | 4mA    | In a non-cached system or a system with external TAG comparator         |       | 141:144  | 127:130  |

| (6:PC9)                |        | chip, these pins can be used as additional PC's (power control pins) as | l.    | ļ        |          |

| (5:PC8)                |        | defined by index register 110H, bit 5 being high.                       |       |          |          |

| (4:PC7)                |        | TAGD7 is HIT# signal from the external TAG comparator.                  |       |          |          |

| (3:PC6)                |        | TAGD<6:1> are PC<9:4>. (See section 1.6 Power Management                |       |          |          |

| (2:PC5)                |        | Interface for detailed descriptions for these pins).                    |       |          |          |

| (1:PC4)                |        |                                                                         |       |          |          |

| (0:Reserved)<br>TAGWE# | 0      | TAG RAM Write Enable # : TAG Data Write Enable is the write             | 5     | 135      | 121      |

| 1AGWE#                 | 4mA    | strobe to the TAG RAM.                                                  |       | 133      | 121      |

| DIRTY                  | I/O    | DIRTY bit: Dirty bit indicates the particular line in the level 2 cache | 5     | 146      | 132      |

| (WAKE0)                | 4mA    | contains modified data. If index register 111H, bit 4 is high and bit 5 |       | 140      | 152      |

| (WALLO)                | 111111 | is low, then this pin is redefined as WAKEO input for the wake          | 1     | 1        | l '      |

|                        |        | control logic.                                                          |       |          | 1        |

| (GPIOB0)               |        | Furthermore, if index register 111H, bits 4 and 5 are high, then this   | 1     | h        | Ì        |

| (611656)               |        | pin can be used as a general purpose IO (GPIOBO). Use index             |       |          | 1        |

|                        |        | register 014H, bits 4 and 6 to control the function of GPIOBO.          |       |          |          |

| DRTWE#                 | 1/0    | DiRTy bit Write Enable #: Dirty bit Write Enable is the write strobe    | 1     | 147      | 133      |

| (WAKE1)                | 4mA    | to the Dirty RAM.If index register 111H, bits 3 and 6 are high and      | 1     |          | h        |

| (                      |        | bit 7 is low, then this pin is redefined as WAKE1 input for the wake    |       |          | 1        |

|                        |        | control logic.                                                          | 1     |          |          |

| (GPIOB1)               |        | Furthermore, if index register 111H, bits 3, 6 and 7 are all high, then | 1     | 1        | 1        |

| <b>[</b> `             |        | this pin can be used as a general purpose IO (GPIOB1). Use index        |       |          |          |

|                        |        | register 014H, bits 5 and 7 to control the function of GPIOB1.          |       |          |          |

| (NMI)                  |        | This pin can also be used as NMI input if index 111H, bit 6 is high     |       | 1        |          |

|                        |        | and bit 3 is low.                                                       |       | L        | <u> </u> |

# **REDWOOD 1 Pin List**

Preliminary

| SRAMCE# | 0   | SRAM Chip Enable #: This pin will be used to enable the data    | 1 | 174 | 160 |

|---------|-----|-----------------------------------------------------------------|---|-----|-----|

|         | 4mA | RAM's. It will be used in conjunction with CCS<3:0># to control |   |     |     |

|         |     | the SRAM's. This pin is needed in the system using 64Kx16       |   |     |     |

|         |     | RAM's.                                                          |   |     |     |

## 1.5 AT Bus Interface and Miscellaneous Controls

| PIN NAME | 1/0 | PIN DESCRIPTION                                                         | GROUP | 176PIN# | 160PIN# |

|----------|-----|-------------------------------------------------------------------------|-------|---------|---------|

| MASTER#  | I   | Master #: This input from the AT Bus indicates that a slot Master       | 3     | 54      | 48      |

|          | _   | has taken control of the AT Bus.                                        |       |         |         |

| KBCS#    | 0   | KeyBoard controller Chip Select #: This output drives the 8042, or      | 3     | 68      | 62      |

|          | 2mA | equivalent, Keyboard Controller Chip Select.                            |       |         |         |

| ROMCS#   | 0   | ROM Chip Select #: This output drives the BIOS ROM Chip Select.         | 4 3   | 69      | 63      |

|          | 2mA |                                                                         |       |         |         |

| IRQ8#    | 1/0 | IRQ 8 # output from the internal RTC. It will become an input if        | 3     | 70      | 64      |

|          | 2mA | index register 100H, bit 11 is high (external RTC mode).                |       |         |         |

| KBRST#   | NO  | KeyBoard controller CPU ReSet #: This pin can be connected to the       | 3     | 66      | 60      |

|          | 4mA | keyboard controller as the indication of a keyboard controller          |       |         |         |

|          |     | initiated CPU reset condition if index register 111H, bit 8 is low.     |       |         |         |

| (GPIOC1) |     | If index register 111H, bits 8/9/10 are high and bit 11 is low, then    |       |         |         |

|          |     | this pin can be used as a general purpose IO pin (GPIOC1). Use          |       |         |         |

|          |     | index register 014H, bits 11 and 9 to control the function of           |       |         |         |

|          |     | GPIOC1.                                                                 |       |         |         |

| (GPCS0#) |     | If index register 111H, bits 8, 9 10 and 11 are high, then this pin can |       |         |         |

|          |     | be used as a General Purpose Chip Select (GPCS0#).                      |       |         |         |

# 1.6 Power Management Interface

| PIN NAME | I/O | PIN DESCRIPTION                                                        | GROUP | 176PIN# | 160PIN# |

|----------|-----|------------------------------------------------------------------------|-------|---------|---------|

| 32KIN    | I   | 32KHZ Input: This input is used for the internal RTC block and         | 3     | 57      | 51      |

|          |     | power management circuit.                                              |       |         |         |

| PC<0>    | 0   | Power Controls <0>: This pin provides power control for one            | 3     | 61      | 55      |

|          | 2mA | system component or power plane.                                       |       |         |         |

| PC<1>    | 0   | Power Controls <1>: This pin provides power control for one            | 3     | 62      | 56      |

|          | 2mA | system component or power plane.                                       |       |         |         |

| PC<2>    | I/O | Power Controls <2>: This output provide individual power control       | 3     | 63      | 57      |

|          | 2mA | for any system component.                                              |       |         |         |

| (GPIOC0) |     | If index register 110H, bit 8 is low (both 112H, bit 2 and 110H, bit 7 |       | ŀ       |         |

|          |     | are high), then this pin can be used as a general purpose IO pin       |       |         |         |

|          |     | (GPIOC0). Use index register 014H, bits 10 and 8 to control the        |       |         |         |

|          |     | function of GPIOC0.                                                    |       |         |         |

| (GPCS1#) |     | If index register 110H, bit 8 is also high (both 112H, bit 2 and       |       |         |         |

|          |     | 110H, bit 7 are high), then this pin is a General Purpose Chip Select  |       |         |         |

|          |     | (GPCS1#)                                                               |       |         |         |

| PC<3>       | 0   | Power Controls <3>: This output provide individual power control      | 3 | 64    | 58    |

|-------------|-----|-----------------------------------------------------------------------|---|-------|-------|

|             | 2mA | for any system component.                                             |   |       |       |

| (GPCS2#)    | 1   | If index register 112H, bit 3 and 110H, bit 9 are high, 110H, bit 10  |   |       |       |

|             |     | is low, then this pin can be used as a General Purpose Chip Select    |   |       |       |

| (HTRGOUT)   |     | (GPCS2#)Heat Regulator Output: This output can optionally be          |   |       |       |

|             |     | enabled to indicate the output function of the internal Heat          |   |       |       |

|             |     | Regulator. This function can be enabled by programming both           |   |       |       |

|             |     | 112H, bit 3 and 110H, bits 9 and 10 high.                             | - |       |       |

| GPIO<3:0>   | I/O | General Purpose I/O's <3:0>: These four I/O's are provided for        | 3 | 53:50 | 47:44 |

|             | 4mA | general purpose usage.                                                |   |       |       |

| (3:EXTACT1) |     | This pin can also be selected as the EXTACT1 input.                   |   |       |       |

| (2:RING)    | 1   | This pin can also be used as the RING input from the modem if         |   | 1     |       |

| •           |     | index register 111H, bit 14 is high and 100H, bit 0 is low.           |   |       |       |

| (2:MDEN#)   |     | This pin can also be used as the MDEN# output for the MD buffer       |   |       |       |

| ,           |     | control if index register 111H, bit 14 and 100H, bit 0 are both high. |   |       |       |

| (1:KBGA20)  | ]   | This pin can also be used as the input for KB controller GateA20      |   |       |       |

| •           |     | function if index register 111H, bit 13 is high and 112H, bit 13 is   | 1 | 1     |       |

|             |     | low.                                                                  |   |       |       |

| (1:KBCLKO)  |     | This pin can also be the KB Clock output if index register 111H, bit  |   |       |       |

|             |     | 13 and 112H, bit 13 are both high.                                    |   |       |       |

| (0:FRCSLW)  |     | FRCSLW/GPEXT: This pin may be used as Force Slow input or             | ] |       |       |

| (0:GPEXT)   |     | GPEXT ouput by programming index register 111H, bits 0 and 12.If      |   |       |       |

| ,           |     | index register 111H, bit 12 is high and bit 0 is low, then it is      |   |       |       |

|             |     | FRCSLW input. If both bits are high, then it is GPEXT ouput If        |   |       |       |

|             |     | index register 100H, bit 11 is high, an external RTC chip is used.    |   |       |       |

| (2: ASRTC,  |     | This condition will overwrite other configuration bits and            |   |       |       |

| 1: DSRTC,   |     | GPIO<2:0> will provide interface signals to the external RTC :        |   |       |       |

| 0:RWRTC)    |     | GPIO2 = ASRTC, GPIO1 = DSRTC and GPIO0 = RWRTC.                       |   |       |       |

| SWTCH       | I   | Switch: This input provides an on-off function between Fully-On       | 3 | 47    | 41    |

|             |     | and Suspend or Standby Modes.                                         |   |       |       |

# 1.7 Battery Management Interface

| PIN NAME | I/O | PIN DESCRIPTION                                                                                                                                                                                                               | GROUP |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ACPWR    | I   | AC Power: This input indicates that the power source is AC.  Note: This pin is multiplexed with CCS2#. Using index register 110H, bit 4 to select between CCS2# and AC Power Function.                                        | 5     |

| VLB      | I   | Very Low Battery: This input from the power supply indicates a very low battery condition.  Note: This pin is multiplexed with CCS1#. Using index register 110H, bit 4 to select between CCS1# and Very Low Battery Function. | 5     |

| LB       | I   | Low Battery: This input from the power supply indicates a low battery condition.  Note: This pin is multiplexed with CCS0#. Using index register 110H, bit 4 to select between CCS0# and Low Battery Function.                | 5     |

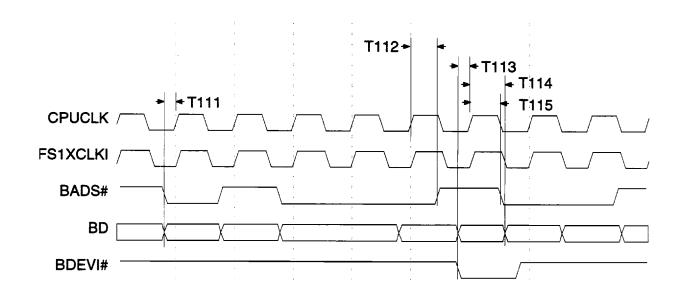

### 1.8 Burst Bus Interface

| PIN NAME | I/O | PIN DESCRIPTION                                                         | GROUP | 176PIN#  | 160PIN# |

|----------|-----|-------------------------------------------------------------------------|-------|----------|---------|

| BADS#    | I/O | Burst Bus ADS#: This is the signal used to indicate the various         | 4     | 81       | 75      |

|          | 4mA | phases of the burst bus (including the status phase, address phase,     |       |          |         |

|          |     | data transfer phase and miscellaneous information phase).               |       |          |         |

| FS1XCLK  | 0   | Fast 1X Clock: This is the fast version of the 1X clock. It can be      | 4     | 80       | 74      |

|          | 8mA | either the divided CPU clock or the undivided input clock.              | L     | <u> </u> |         |

| BD<7:0>  | I/O | Burst Data Bus <7:0>: This 8-bit bus carries different information      | 4     | 71:78    | 65:72   |

|          | 4mA | during various phases.                                                  |       |          |         |

| BDEV#    | 1/0 | Burst Device #: This is the signal all the devices on the burst bus can | 4     | 82       | 76      |

| ,        | 4mA | use to claim burst bus cycle. This signal is also used as READY         |       |          |         |

|          |     | indicator to terminate or extend the burst bus cycle.                   |       |          |         |

| BSER     | I   | Burst Serial Bus: This pin is used between REDWOOD 1 and                | 4     | 83       | 77      |

|          |     | REDWOOD 2 to indicate various activities for power management           |       |          |         |

|          |     | circuit.                                                                |       |          |         |

## 1.9 Power and Ground Pins

| PIN NAME    | I/O | PIN DESCRIPTION            | GROUP   | 176PIN#    | 160PIN#   |

|-------------|-----|----------------------------|---------|------------|-----------|

| VDDCL<1:0>  | -   | Core Logic Power Pins      |         | 39, 148    | 37,134    |

| VDDIO1      | -   | I/O Power Pins for Group 1 | 1       | 16, 36,    | 14,34,    |

|             |     |                            |         | 164        | 150       |

| VDDIO2      | 1   | I/O Power Pins for Group 2 | 2       | 99, 112    | 89,102    |

| VDDIO3      | 1   | I/O Power Pins for Group 3 | 3       | 58         | 52        |

| VDDIO4      | 1   | I/O Power Pins for Group 4 | 4       | 79         | 73        |

| VDDIO5      |     | I/O Power Pins for Group 5 | 5       | 126, 145   | 116,131   |

| VSSIO<11:0> |     | I/O Ground Pins            | _       | 8, 27, 48, | 6,25,     |

|             |     |                            |         | 49, 60,    | 42,43,54, |

|             |     |                            |         | 84, 85,    | 78,79,93, |

|             |     |                            | ļ       | 85, 103,   | 109,126,  |

|             |     |                            |         | 119, 140,  | 140,152   |

|             |     |                            | <u></u> | 154, 166   |           |

#### 1.10 Multi-Function NPU Pins

The interface control signals between a 386DX and a 387 NPU are significantly different from those used in a 486 system. In order to save pins, the signals that are unique to the 386 implementation are shared with signals that are unique to the 486. The following table indicates which pins are shared and describes the 386 function of each.

#### Multi-function Pins -- 486 vs 386DX

| 486 NAME | 386 NAME | ľO | 386 DESCRIPTION                                                                                 | PAD I/O | 176PIN# | 160PIN# |

|----------|----------|----|-------------------------------------------------------------------------------------------------|---------|---------|---------|

| EADS#    | ERRORO#  | 0  | Error output #: This pin is the modified ERROR output to the 386DX.                             | 0       | 161     | 147     |

| CACHE#   | PEREQI   | Ι  | Processor Extension Request Input: This input from a 387 indicates an NPU cycle request.        | I       | 152     | 138     |

| BRDY#    | PEREQO   | 0  | Processor Extension Request Output: This output to a 386DX indicates an NPU cycle request.      | I/O     | 153     | 139     |

| HITM#    | ERRORI#  | I  | Error Input #: This pin is the ERROR input from a 387 NPU.                                      | I       | 150     | 136     |

| BLAST#   | BUSYO#   | 0  | Busy Output #: This output to a 386DX indicates that the NPU is executing NPU cycles.           | ΙΟ      | 160     | 146     |

| RSTCPU   | RSTNPU   | 0  | Reset NPU: This output signals a reset for the 387 NPU.                                         | 0       | 34      | 32      |

| LOCK#    | BUSYI#   | I  | Busy Input #: This input from the a 387 NPU indicates that it is executing NPU cycles.          | I/O     | 149     | 135     |

| FLUSH#   | IRQ13    | 0  | IRQ13 output: This output is used by the 387 handler to cause an numeric coprocessor interrupt. | 0       | 35      | 33      |

## 2.0 REDWOOD 2 Pin List

NOTE -There are three separate and isolated VDD pins on REDWOOD 2 that can be connected to individual power sources. The number in the "GROUP" column designates which VDD power pins are used to supply power to each I/O pin. The core power pins are separate from the I/O power pins.

#### 2.1 Clock and Reset Interface

| PIN NAME | I/O | PIN DESCRIPTION                                                                                                                                                                                     | GROUP | 176PIN# | 160PIN# |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|---------|

| 14MHZIN  | I   | 14.318 MHz Input: This input is used to generate the timer clock for the 82C206 Peripheral Controller.                                                                                              | 3     | 137     | 123     |

| CPUCLK   | I   | CPU Clock Input: This will be the 1X clock input from REDWOOD1 (It should be connected CPUCLKO1). If index register 100H, bit 1 is high (386DX mode), this clock will be half of the CPU frequency. | 1     | 157     | 143     |

| RSTDRV#  | I   | Reset # Input: This is the master Reset pin for REDWOOD 2. This is an active low signal.                                                                                                            | 3     | 119     | 109     |

#### 2.2 CPU Interface

| PIN NAME  | I/O | PIN DESCRIPTION                                                      | GROUP | 176PIN#   | 160PIN#  |

|-----------|-----|----------------------------------------------------------------------|-------|-----------|----------|

| D<31:0>   | I/O | CPU Data <31:0>                                                      | 1     | 40:36,    | 38:34,   |

|           | 4mA |                                                                      |       | 34:25,    | 32:23,   |

|           | 1   |                                                                      |       | 23:14,    | 21:12,   |

|           |     |                                                                      |       | 12:9, 7:5 | 10:7,5:3 |

| RDY#      | I/O | Ready #: This output to the CPU indicates completion of the current  | 1     | 172       | 158      |

|           | 4mA | bus cycle. This pin is also an input to monitor completion of local  |       |           |          |

|           |     | bus cycles.                                                          |       |           |          |

| BRDY#     | I   | Burst Ready #: This input allows REDWOOD 2 to monitor the            | 1     | 171       | 157      |

|           |     | CPU burst cycle activity.                                            |       |           |          |

| DP<3:0>   | I/O | Data Parity <3:0>                                                    | 1     | 167:170   | 153:156  |

| GPIO<7:4> | 4mA | These pins can also be selected as additional General Purpose IO     |       |           |          |

|           |     | pins. Their function can be enabled by index register 302H, bits     |       | 1         | i        |

|           |     | <1:0> and controlled by index register 304H, bits<15:8>.             |       |           |          |

| FERR#     | I   | Floating Point Error #: This input from the 486DX CPU indicates a    | 1     | 166       | 152      |

|           |     | 486DX internal floating point error.                                 |       |           |          |

| (W/R#)    |     | This pin can also be programmed to be CPU W/R# status for parity     |       |           | 1        |

|           |     | generation circuit by index register 302H, bit 12 high.              |       |           |          |

| IGNNE#    | 0   | Ignore Numeric Error #: This output to the 486DX CPU indicates       | 1     | 165       | 151      |

|           | 2mA | that floating point errors should be ignored.                        |       | <b></b> _ |          |

| INTR      | 0   | CPU Interrupt Request from the 8259A Interrupt Controller.           | 1     | 163       | 149      |

| _         | 2mA |                                                                      |       |           |          |

| HOLD      | 0   | Hold Request: This output to the CPU indicates a request to hold the | 1     | 162       | 148      |

|           | 2mA | CPU and float its bus.                                               | ļ     |           |          |

| HLDA      | I   | Hold Acknowledge: This input from the CPU acknowledges a Hold        | 1     | 161       | 147      |

|           |     | Request.                                                             |       | L         |          |

| NMI     | 0   | Non Maskable Interrupt: This output to the CPU indicates the                                                                                                     | 1 | 160 | 146 |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|

|         | 2mA | occurrence of a Non Maskable Interrupt.                                                                                                                          |   |     |     |

| HITM#   | I   | HITM#: HITM# indicates that the snoop cycle hits a modified line in level 1 cache. REDWOOD2 uses it to decide if it needs to back off from a HOLD REQUEST cycle. | 1 | 159 | 145 |

| (IRQ13) |     | IRQ13: This pin can be used as IRQ13 input for the numeric coprocessor if index register 302H, bit 12 is high.                                                   |   |     |     |

### 2.3 VESA Bus Interface

| PIN NAME            | I/O        | PIN DESCRIPTION                                                                                                                                                                                                                                                 | GROUP | 176PIN# | 160PIN# |

|---------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|---------|

| LOCAL#              | I          | Local Device #: This input from a local bus device indicates that the local device has claimed the current CPU cycle and REDWOOD 2 should not start any ISA bus or Burst bus cycle                                                                              | 1     | 158     | 144     |

| LRDY#               | I          | Local Device READY#: This signal indicates the local device has completed the cycle.                                                                                                                                                                            | 1     | 41      | 39      |

| LREQ1#<br>(LOCAL2#) | I          | Local bus master Request1#: VESA Bus Request input from one of the two bus master devices.  LOCAL2#: This pin can also become the third LDEV# input from the VL bus. This is done by programming index register 302H, bit 5 high.                               | 1     | 173     | 159     |

| LREQ0#              | I          | Local bus master Request0#: VESA Bus Request input from one of the two bus master devices.                                                                                                                                                                      | 1     | 3       | 1       |

| LGNT1#<br>(LOCAL1#) | I/O<br>2mA | Local bus master Grant1#: VESA Bus Grant outputs to the bus master devices indicating which bus master can own the bus.  LOCAL1#: This pin can also become the second LDEV# input from the VL bus. This is done by programming index register 302H, bit 5 high. | 1     | 174     | 160     |

| LGNT0#              | O<br>2mA   | Local bus master Grant0#: VESA Bus Grant outputs to the bus master devices indicating which bus master can own the bus.                                                                                                                                         | 1     | 4       | 2       |

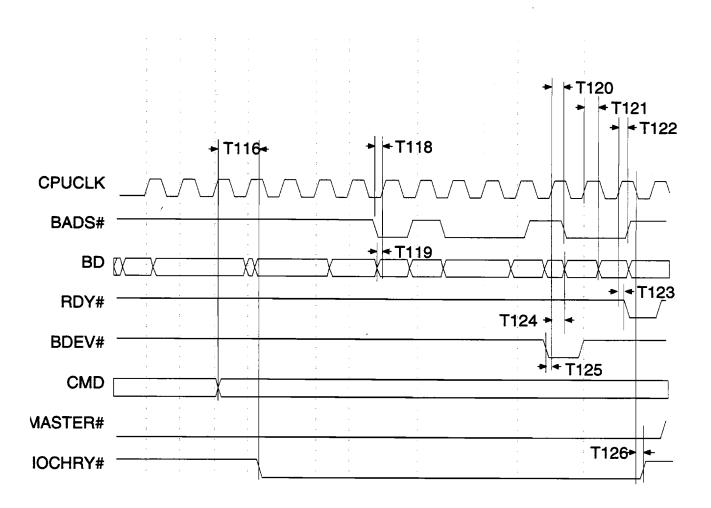

### 2.4 AT Bus Interface

| PIN NAME   | I/O  | PIN DESCRIPTION                                                     | GROUP | 176PIN#   | 160PIN# |

|------------|------|---------------------------------------------------------------------|-------|-----------|---------|

| SA<1:0>    | I/O  | Slot Addresses <1:0>: These outputs are decoded from the CPU        | 3     | 109, 108  | 99,98   |

|            | 12mA | byte enables to drive these AT Bus address lines.                   |       |           |         |

| SBHE#      | I/O  | Slot Byte High Enable #: This output to the AT Bus indicates a data | 3     | 110       | 100     |

|            | 12mA | transfer on the high byte of the Slot Data Bus.                     |       |           | Ĺ       |

| SD<7:0>    | I/O  | Slot Low Byte Data <7:0>: These I/O are the data read and write     | 3     | 61:58,    | 55:53,  |

|            | 12mA | path for the AT Bus.                                                |       | 57:53     | 51:47   |

| SD<15:8>   | I/O  | Slot High Byte Data <15:8>: These I/O are the data read and write   | 3     | 70, 68:62 | 64,     |

| (MSA<7:0>) | 12mA | path for the AT Bus. They will also drive the refresh address       |       |           | 62:56   |

|            |      | SA<7:0> during AT refresh cycles if index register 302H, bit 8 is   |       |           |         |

|            |      | programmed to high.                                                 |       |           |         |

| BALE       | 0    | Buffered Address Latch Enable: This output is driven to the AT Bus  | 3     | 123       | 113     |

|            | 12mA | where it indicates the presence of a valid address on the Bus.      |       |           |         |

| MASTER#    | I    | Master #: This input from the AT Bus indicates that a slot Master   | 3     | 116       | 106     |

|            |      | has taken control of the AT Bus.                                    |       |           |         |

| MEMR#         | I/O          | Memory Read #: This output to the AT Bus indicates a Memory                   | 3 | 112                         | 100        |

|---------------|--------------|-------------------------------------------------------------------------------|---|-----------------------------|------------|

| IVILLIVII(II  | 12mA         | Read cycle to any valid AT Bus address. This pin also acts as an              | 3 | 113                         | 103        |

|               | 12111        | input to provide for MASTER access to local DRAM.                             |   |                             |            |

| MEMW#         | I/O          | Memory Write #: This output to the AT Bus indicates a Memory                  |   |                             |            |

| INITIAL AA M  | 12mA         | Write cycle to any valid AT Bus address. This pin also acts as an             | 3 | 114                         | 104        |

|               | 1211124      | input to provide for MASTER access to local DRAM.                             |   |                             | 1          |

| SMEMR#        | 0            |                                                                               |   |                             |            |

| SMEMK#        | 1            | Slot Memory Read #: This output to the AT Bus indicates a Memory              | 3 | 49                          | 43         |

| C) (TC) (TV/4 | 12mA         | Read cycle within the 0 to 1MB address range.                                 | · |                             |            |

| SMEMW#        | 1.0.         | Slot Memory Write #: This output to the AT Bus indicates a                    | 3 | 48                          | 42         |

| 707 "         | 12mA         | Memory Write cycle within the 0 to 1MB address range.                         |   |                             |            |

| IOR#          | I/O          | I/O Read #: This output to the AT Bus indicates an I/O Read cycle.            | 3 | <b>5</b> 1                  | 45         |

|               | 12mA         |                                                                               |   |                             |            |

| IOW#          | 1/0          | I/O Write #: This output to the AT Bus indicates an I/O Write cycle.          | 3 | 50                          | 44         |

|               | 12mA         |                                                                               |   | ľ                           | <u> </u>   |

| MEMCS16#      | I            | Memory Chip Select 16 Bit #: This input from the AT Bus indicates             | 3 | 111                         | 101        |

|               |              | that the current access is to a 16 bit memory device.                         |   |                             |            |

| IOCS16#       | I            | I/O Chip Select 16 Bit #: This input from the AT Bus indicates that           | 3 | 124                         | 114        |

|               |              | the current access is to a 16 bit I/O device.                                 |   | 12,                         | 111        |

| IOCHCK#       | I            | I/O Channel Check #: This input indicates a parity error from some            | 3 | 117                         | 107        |

|               | -            | device on the AT Bus.                                                         |   | 117                         | 107        |

| IOCHRDY       | I            | I/O Channel Ready: When this input is driven low it indicates that            | 3 | 110                         | 100        |

| 10011101      | 1 1          | the device on AT Bus currently being accessed requires additional             | 3 | 118                         | 108        |

|               |              | time to complete the cycle.                                                   |   |                             |            |

| ZWS#          | I            | Zero Wait State #: This input from the AT Bus indicates that the              |   | 100                         | - 110      |

| 2415#         | 1            | device currently being accessed on complete the suit                          | 3 | 120                         | 110        |

|               |              | device currently being accessed can complete the cycle with zero wait states. |   |                             |            |

| SYSCLK        |              |                                                                               |   |                             |            |

| SISCLK        | 0            | System Clock: This output to the AT Bus provides an approximate               | 3 | 122                         | 112        |

| 4 575 7       | 12mA         | 8MHZ clock.                                                                   |   |                             |            |

| AEN           | <u>.</u> 0.  | Address Enable: This output to the AT Bus indicates that the DMA              | 3 | 115                         | 105        |

|               | 12mA         | controller has taken control of the CPU address bus and the AT Bus            |   |                             |            |

|               | <del> </del> | command lines.                                                                |   |                             |            |

| TC            | 0            | Terminal Count: Signal on the ISA bus indicating a terminal count             | 3 | 84                          | 78         |

|               | 12mA         | has reached for a given channel.                                              |   |                             |            |

| REFRESH#      | l No         | Refresh #: This output drives the AT Bus to indicate a Memory                 | 3 | 121                         | 111        |

|               | 12mA         | Refresh Cycle.                                                                |   |                             |            |

| IRQ<15:14>    | I            | Interrupt Request <15:14> Inputs: These are the ISA interrupt                 | 3 | 107, 106                    | 97,96      |

|               |              | request lines.                                                                |   | ·                           |            |

| IRQ<12:3>     | I            | Interrupt Request <12:3> Inputs: These are the ISA interrupt                  | 3 | 105, 104,                   | 95:94,     |

|               |              | request lines.                                                                |   | 102:95                      | 92:85      |

|               |              | Note: IRQ8 should be connected to IRQ8# of R1 or the external                 |   |                             |            |

|               |              | RTC.                                                                          |   |                             |            |

| IRQ<1>        | I            | Interrupt Request 1 Input: These are the ISA interrupt request lines.         | 3 | 94                          | 84         |

| DRQ<2:0>      | I            | DMA Channel <2:0> Requests: AT DMA channels <2:0> request                     | 3 | 76, 73, 71                  | 70,67,65   |

|               |              | inputs.                                                                       | , | 70, 73, 71                  | 70,07,03   |

| DRQ< 3>       | 1/0          | DMA Channel 3 Request: AT DMA channel 3 request input.                        | 3 | 79                          | 72         |

| Dite          | 4mA          | Divir channel 5 Request : At Divir channel 5 request input.                   | 3 | 19                          | 73         |

| DRQ<7:5>      | I/O          | DMA Channel <7:5> Requests : AT DMA channels <7:5> request                    |   | 92.92.00                    | 77.75      |

| DAY-1.37      |              |                                                                               | 3 | 83, 82, 80                  | 77,76,74   |

| DACW -2.0- #  | 4mA          | inputs.                                                                       |   |                             |            |

| DACK<3:0>#    | 0            | DMA Acknowledge <3:0> outputs: Each DACK output represents                    | 3 | 85, <i>7</i> 7, <i>7</i> 5, | 79,71,69,6 |

| D. 677        | 4mA          | the corresponding DMA channel acknowledge.                                    |   | 72                          | 6          |

| DACK<7:5>#    | 0            | DMA Acknowledge <7:5> outputs : Each DACK output represents                   | 3 | 92, 91, 86                  | 82,81,80   |

|               | 4mA          | the corresponding DMA channel acknowledge.                                    |   |                             |            |

## 2.5 Buffer Control

| PIN NAME | I/O  | PIN DESCRIPTION                                                       | GROUP | 176PIN# | 160PIN# |

|----------|------|-----------------------------------------------------------------------|-------|---------|---------|

| XDDIR    | 0    | XD buffer DIRection control: This pin is used to control the          | 3     | 42      | 40      |

|          | 2mA  | direction of the optional buffer between XD<7:0> and SD<7:0>.         |       |         |         |

| SAEN#    | 0    | SA buffer ENable#: This pin is the enable signal for the optional     | 3     | 127     | 117     |

|          | 2mAI | buffer between CPU address bus and SA bus. (The direction will be     | -     |         |         |

|          |      | controlled by MASTER#).                                               |       |         |         |

| (TYPE2)  |      | This pin will be used as an input to select between a 160 Pin package |       |         |         |

|          |      | and 144 Pin package. If it is high at RESET, the package type is 160  |       |         |         |

| L        |      | pins. If it is low, then it is 144 pins.                              |       |         |         |

## 2.6 Burst Bus Interface

| PIN NAME | I/O        | PIN DESCRIPTION                                                                                                                     | GROUP | 176PIN# | 160PIN# |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|---------|---------|

| BADS#    | I/O<br>4mA | Burst Bus ADS#: This is the signal used to indicate the various phases of the burst bus (including the status phase, address phase, | 4     | 144     | 130     |

|          |            | data transfer phase and miscellaneous information phase).                                                                           |       |         |         |

| FS1XCLK  | I          | Fast 1X Clock: This is the fast version of the 1X clock.                                                                            | 4     | 146     | 132     |

| BD<7:0>  | I/O        | Burst Data Bus <7:0>: This 8-bit bus carries different information                                                                  | 4     | 148:155 | 134:141 |

|          | 4mA        | during various phases.                                                                                                              |       |         |         |

| BDEV#    | I/O        | Burst Device #: This is the signal all the devices on the burst bus can                                                             | 4     | 143     | 129     |

|          | 4mA        | use to claim burst bus cycle. This signal is also used as READY                                                                     |       |         |         |

|          |            | indicator to terminate or extend the burst bus cycle.                                                                               |       |         |         |

| BSER     | 0          | Burst Serial Bus: This pin is used between REDWOOD 1 and                                                                            | 4     | 141     | 127     |

|          | 2mA        | REDWOOD 2 to indicate various activities for power management                                                                       |       |         |         |

|          |            | circuit.                                                                                                                            |       | l .     | ] ]     |

| BINT#    | I          | Burst Bus Interrupt #: This pin is used to indicate an interrupt                                                                    | 4     | 142     | 128     |

|          |            | request has happened on the burst bus.                                                                                              |       |         |         |

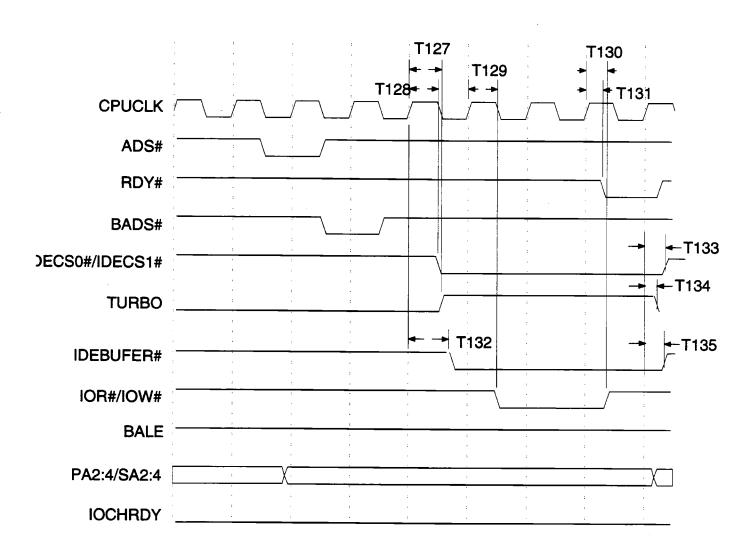

# 2.7 Miscellaneous Control Signals

| PIN NAME | I/O | PIN DESCRIPTION                                                      | GROUP    | 176PIN# | 160PIN# |

|----------|-----|----------------------------------------------------------------------|----------|---------|---------|

| SPKR     | 0   | Speaker Data Output: This pin drives the system speaker.             | 3        | 139     | 125     |

|          | 2mA |                                                                      |          |         |         |

| TURBO    | NO  | TURBO bus enable: This signal is used to isolate the commands for    | 3        | 126     | 116     |

|          | 4mA | the IDE drives from ordinary ISA devices.                            |          |         | l       |

| DETURBO  | NO  | DETURBO function: This pin is connected to the DETURBO               | 3        | 140     | 126     |

|          | 4mA | toggle switch. Whenever this button is pressed, the system will      |          |         |         |

|          |     | toggle between "Normal" mode and "DETURBO" mode".                    | <u> </u> |         |         |

| IDECS0#  | 0   | IDE Chip Select 0: This output is active when the hard drive         | 3        | 129     | 119     |

|          | 8mA | registers from 1F0H-1F7H are selected if the primary address is used |          |         | [       |

|          |     | or when 170H-177H are selected if the secondary address is used.     |          |         |         |

| IDECS1#  | 0   | IDE Chip Select 1: This output is active when the hard drive         | 3        | 130     | 120     |

|          | 8mA | registers from 3F6H-3F7H are selected if the primary address is used |          |         |         |

|          |     | or when 376H-377H are selected if the secondary address is used.     |          |         |         |

# **REDWOOD 2 Pin List**

Preliminary

| IDED7     | 4mA      | IDE Data bit 7: This pin provides data bit 7 to the IDE drive during the accesses in the address range 1F0H-1F7H, 170H-177H and 3F6H/376H. This pin is tri-stated during reading or writing addresses 3F7H and 377H. |   | 135 | 121 |

|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|

| IDEBUFEN# | O<br>4mA | IDE Buffer Enable #: This pin controls the external data buffers between the IDE drive(s) and SD bus.                                                                                                                | 3 | 136 | 122 |

# 2.8 Power and Ground Pins

| PIN NAME    | I/O | PIN DESCRIPTION            | GROUP | 176PIN#                                              | 160PIN#                                     |

|-------------|-----|----------------------------|-------|------------------------------------------------------|---------------------------------------------|

| VDDCL<1:0>  | _   | Core Logic Power Pins      |       | 78, 138                                              | 72,124                                      |

| VDDI01      |     | I/O Power Pins for Group 1 | 1     | 13, 35                                               | 11,33                                       |

| VDDIO3      | -   | I/O Power Pins for Group 3 | 3     | 47, 74,<br>103, 125                                  | 41,68,93,1<br>15                            |

| VDDIO4      |     | I/O Power Pins for Group 4 | 4     | 147                                                  | 133                                         |

| VSSIO<11:0> | -   | I/O Ground Pins            |       | 8, 24, 52,<br>58, 69,<br>81, 93,<br>112, 145,<br>156 | 6,22,46,<br>52,63,75,<br>83,102,<br>131,142 |

## 3.0 Configuration Register Specifications

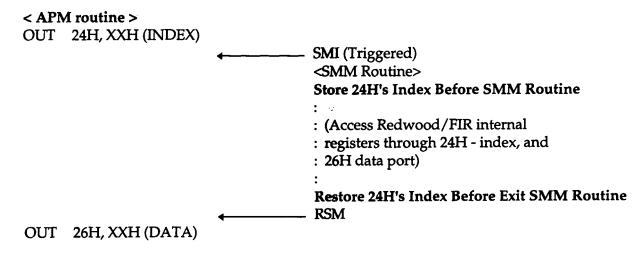

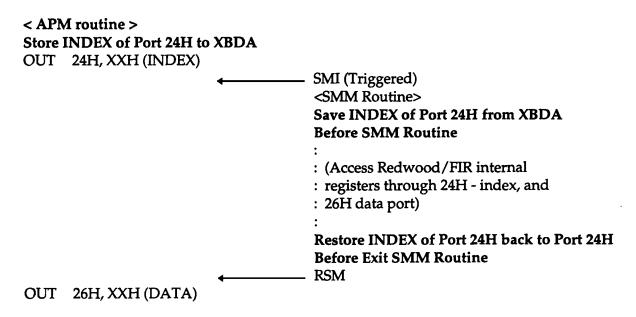

#### 3.1 Configuration Index and Data Ports

All REDWOOD Configuration Registers are indexed at address 24H and all data are accessed at address 26H. Also note that all registers are word width and must be accessed as such — they cannot be accessed by byte commands. Default values for all registers are indicated each registers description. Some bits are listed as reserved these should never be changed from their default values.

#### 3.2 Power-On Configuration

REDWOOD incorporates a power-on Configuration Register to define several fundamental system configuration variables that must be set by hardware options. It also defines several bits as miscellaneous configuration bits that may be used in conjuction with a simple BIOS routine to control system variables by jumper option. These may be defined by the system designer to control any function he desires.

The power-on register is loaded on the leading edge of the POWERGOOD pulse. This pulse should be triggered by power first being applied to the REDWOOD. At this time the present value of the memory address pins MA<11:0> will be loaded into the corresponding register bits of the power-on Register. Once set this register becomes read-only. In order to select the desired options for a particular system, each MA pin should have either a pull-up or pull-down connected. From the point of powering up the REDWOOD until slightly past the leading edge of the POWERGOOD pulse all MA pins will be floating. Thereby the pull-up or pull-down will easily set each MA pin to the appropriate high or low value. 100K resistors are recommended.

Please note that the MA pins have no internal pull-downs. Thereby every MA pin must have either a pull-up or pull-down connected externally to ensure proper Power-On sampling.

# 4.0 REDWOOD 1 Register Specifications

# 4.1 System Register Specifications

| 4.1.0 | Power-On Register | Configuration Index                                                                                                                                                                                                                               | 100H |

|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| BIT   | NAME              | FUNCTION                                                                                                                                                                                                                                          | DFLT |

| 0     | FIRSEL            | REDWOOD/FIR Select: If low, the chip is packaged as REDWOOD (160 pin package). If high, then it is in 144 pin package as FIR. This bit is sampled from MA0A on power-up and is otherwise read only.                                               | 0    |

| 1     | 386SEL            | 386 Select: High selects the 386 CPU, low selects the 486. This bit is sampled from MA1 on power-up and is otherwise read only.                                                                                                                   | 0    |

| 2     | Reserved          | This bit is sampled from MA2 on power-up and is otherwise read only                                                                                                                                                                               | 0    |

| 3     | Reserved          | This bit is sampled from MA3 on power-up and is otherwise read only                                                                                                                                                                               | 1    |

| 4     | CPUMODESEL        | CPU Mode Select: High selects CPU with L1 WB cache, low selects the other CPU types. This bit is sampled from MA4 on power-up and is otherwise read only.                                                                                         | 0    |

| 5     | Reserved          | This bit is sampled from MA5 on power-up and is otherwise read only                                                                                                                                                                               | 0    |

| 6     | Reserved          | This bit is sampled from MA6 on power-up and is otherwise read only                                                                                                                                                                               | 1    |

| 9:7   | Reserved          | This bit is sampled from MA<9:7> on power-up and is otherwise read only                                                                                                                                                                           | 000  |

| 10    | Reserved          | This bit is sampled from MA10 on power-up and is otherwise read only                                                                                                                                                                              | 0    |

| 11    | EXTRTC            | Optional External RTC: When high, it indicates an external RTC chip is used in the system and 3 GPIO pins will be used to interface to it. Otherwise, use the internal RTC. This bit is sampled from MA11 on power-up and is otherwise read only. | 0    |