# 1. INTRODUCTION

### 1.1. SUMMARY

The Rockwell C40 and L39 Microcontrollers (MCUs) are complete 8-bit microcontrollers fabricated on a single chip using CMOS silicon gate process. This MCU complements an industry standard line of R6500 and R65C00 microprocessors, as well as R6500\*/, R65CXX, C19, C29, and C39 microcomputers, and their compatible peripheral devices. This MCU family has a wide range of controller applications where high 8-bit performance, minimal chip count and low power consumption are required.

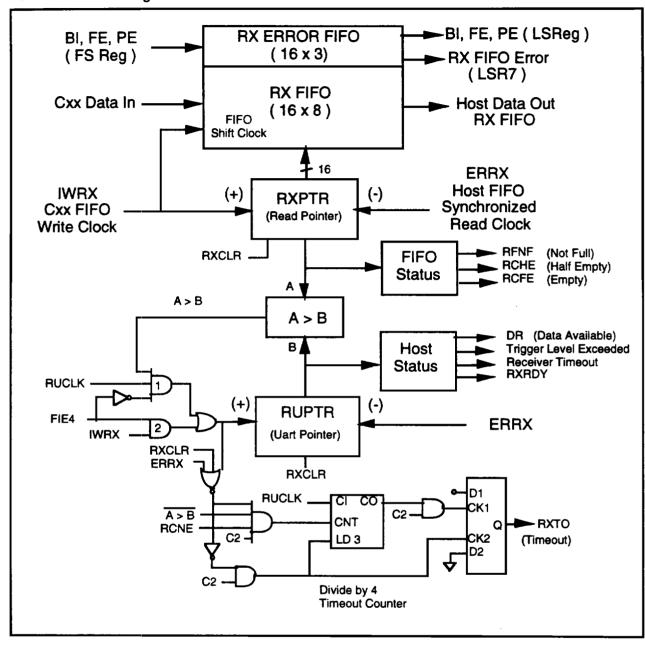

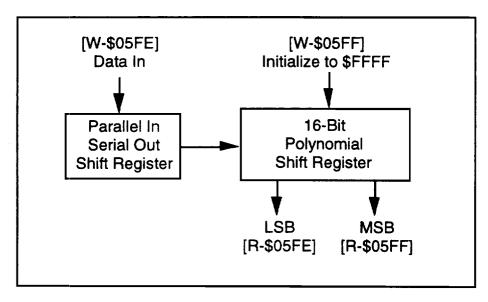

The basic C40 MCU features include an enhanced 6502 Central Processing Unit (CPU), 8k bytes of internal mask programmable read only memory (ROM), 1024 bytes of internal random access memory (RAM), two 16-bit counter/timers, two 17-bit precision timing generators, an asynchronous/synchronous USART port, a 16550A interface with FIFO and DMA handshake support, a 16-bit cyclic redundancy check (CRC), a 16-bit address/8-bit data expansion bus, 8 bank select registers for flexible memory banking control, and up to 40 general purpose input/output ports. Thirty two I/O lines can be assigned to special purpose functions under software control.

The C40 also provides improved 16550A interface operation and incorporates three internal resistors to eliminate three previously required external resistors.

In addition to the C40 enhancements, the L39 MCU provides lower voltage and power operation, a Stop Mode, and expanded internal RAM. Low voltage and power mask options include 5V power and I/O with 5V core (5/5), 5V power and I/O with 3.3V core (5/3), and 3.3V power and I/O with 3.3V core (3/3).

#### 1.2. FEATURES

- Single-chip microcomputer

- Enhanced R6502 CPU

- 8k (8192) bytes internal read-only memory (ROM)

- 1024 bytes (C40) or 1470 bytes (L39) internal random access memory (RAM)

- Two 16-bit counter/timers

- Two 17-bit precision time generators

- Universal asynchronous/synchronous receiver transmitter (USART)

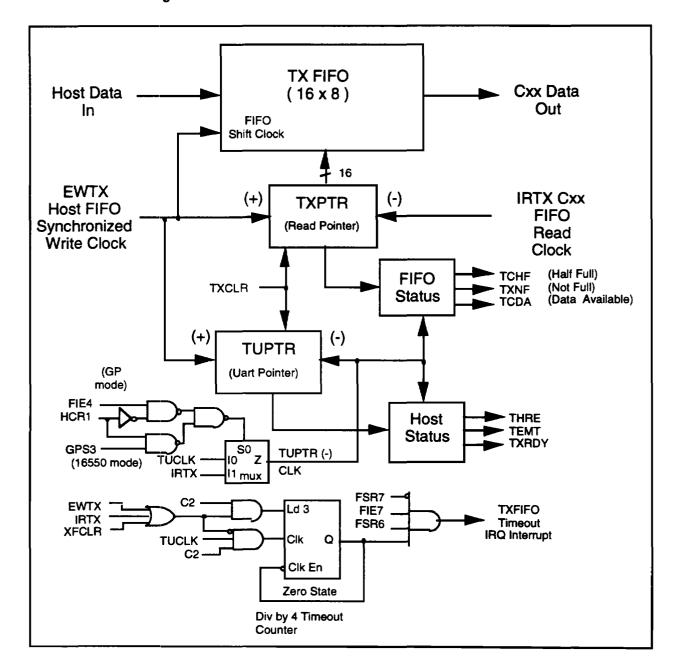

- Host bus for 16550A interface or scratchpad RAM interface with 16-byte FIFO and DMA

- Eight levels of prioritized, vectored interrupts

- High speed operation

C40: Up to 10 MHz

L39: Up to 15 MHz (3/3), 16.5 MHz (5/3) or 20.5 MHz (5/5)

- Low power sleep mode

- Ultra-low power stop mode (L39 only)

- Enhanced R6502 CPU

- 12 new bit manipulation and branching instructions to shorten code and speed up execution

- 21 new arithmetic processing instructions to optimize arithmetic processing

- 10 new direct threaded code instructions to support high level languages that compile linked machine instructions

- R6502 instruction compatible except "(indirect,X)" addressing mode changed to "(Indirect)" and "(Indirect),Y" addressing mode changed to "(Indirect),X"

- General purpose input/output (GPIO), output (GPO), or input (GPI) lines

- 28 GPIO lines with data latches and direction registers: Ports A, C, D (0-3), and E

- 8 output only lines with data latches: Port B

- 4 input only lines with data latches: Port D (4-7)

- 32 I/O lines can be assigned to special purpose functions under software control

- Two identical 16-bit programmable counter/timers with latches

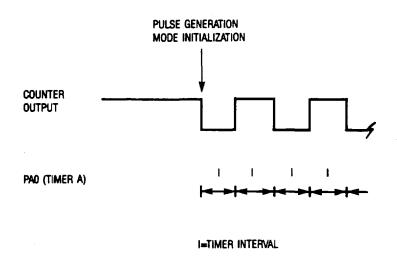

- Four modes: Interval Timer, Pulse Generation, Pulse Width Measurement, Event Counter

- Selectable divide-by-32 prescaler

- Timer interrupt can be vectored to either ROM or page 1 RAM

- I/O port interface

- Two 17-bit precision time generators (PTGs) with latches

- Increment/decrement capability with counter option (clear accumulator on overflow)

- Interrupt enables

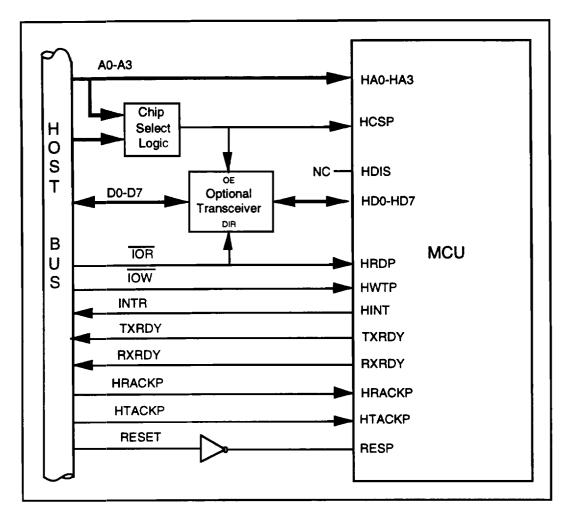

- · Selectable Host Bus for 16550A or scratchpad RAM interface

- 16550A interface (application software dependent)

- 6 bytes for 16550A registers

- 7 bytes for dual port scratch pad RAM

- 1 byte for dual port general purpose RAM

- 1 byte for dual port handshake

- 1 byte for receiver and transmitter FIFO interface (16 byte deep FIFO)

- 2 bytes for FIFO status

- 1 byte for GP FIFO status

- **DMA** interface

- General purpose dual port RAM interface

- 13 bytes for dual port scratch pad RAM

- 1 byte for dual port handshake

- 1 byte for FIFO interface (16 byte deep FIFO)

- 2 bytes for FIFO status

- 1 byte for GP FIFO status

- **DMA** interface

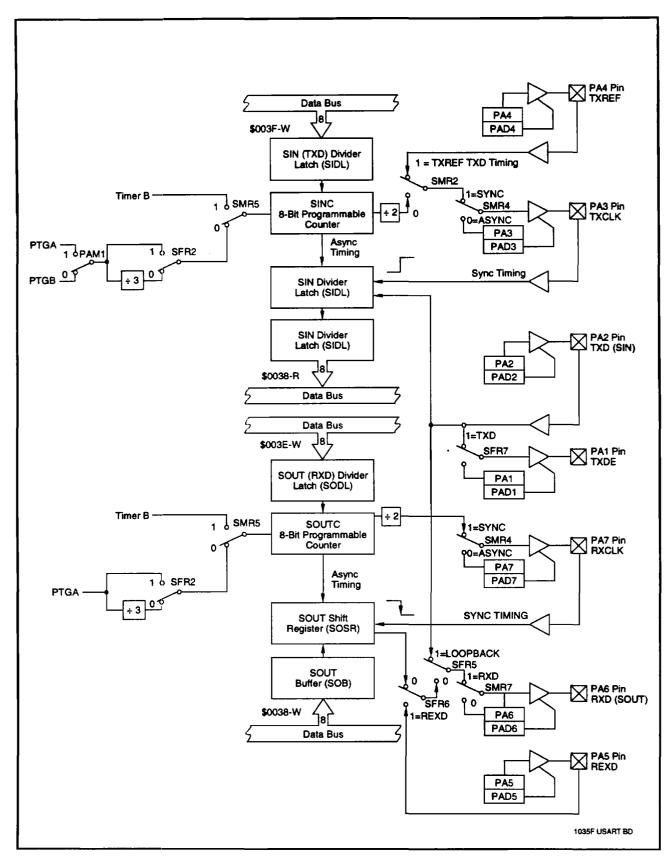

- USART Serial I/O

- Common asynchronous/synchronous features

- Full double buffering

- Serial in and serial out individually enabled

- Interrupt enables for receiver buffer full and transmitter buffer empty

- Echo modes

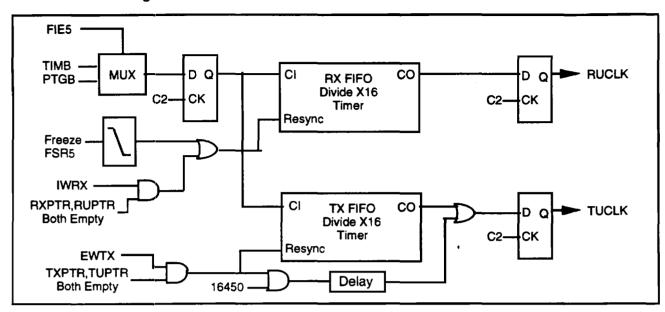

- Timer B or PTGA/PTGB timing

- Speed recognition

- Asynchronous features

- 5-, 6-, 7-, or 8-bit characters

- Even, odd, stuff or no parity bit generation and detection

- 1, 1-1/2 or 2 stop bit generation with 3/4 or 7/8 stop bit control

- False start bit detection

- Interrupt enables

- Line break generation and detection

- Synchronous features

- Transmit data (TXD) serial input timing internal, external TXCLK, or external TXREF

- Received data (RXD) serial output timing internal or external RXCLK

- 5-, 6-, 7-, or 8-bit characters

- Automatic word sync on first 1 to 0 transition

- Interrupt enables for serial input clock (TXCLK) and serial output clock (RXCLK)

- Expansion Bus

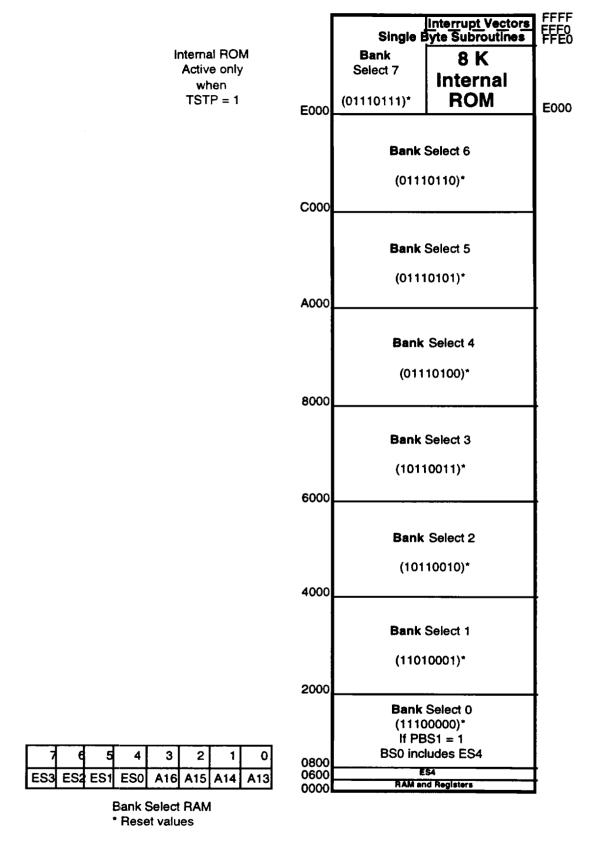

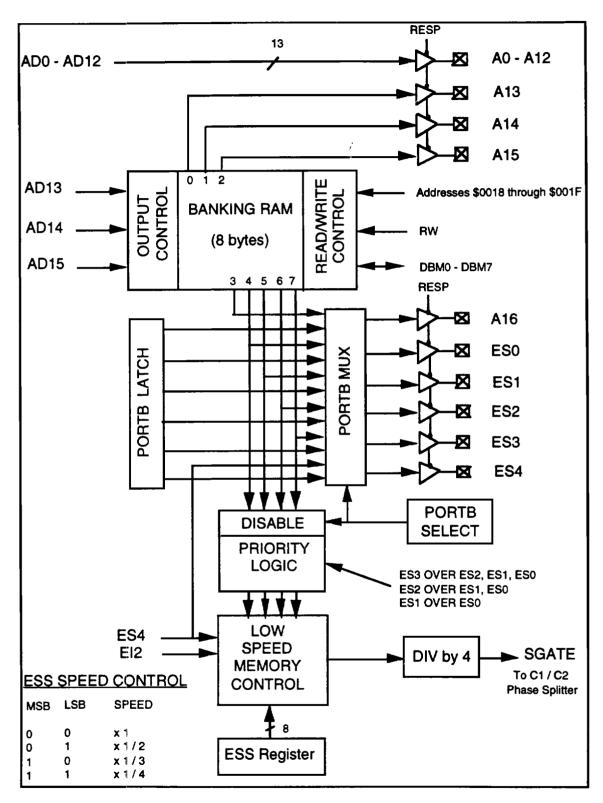

- Built-in memory banking allows up to 512k bytes of external memory to be addressed

- Eight Bank Select Registers independently control 8k-byte memory banks

- Each BSR defines address translation (A13-A15), A16 control, and chip select (ES0-ES3)

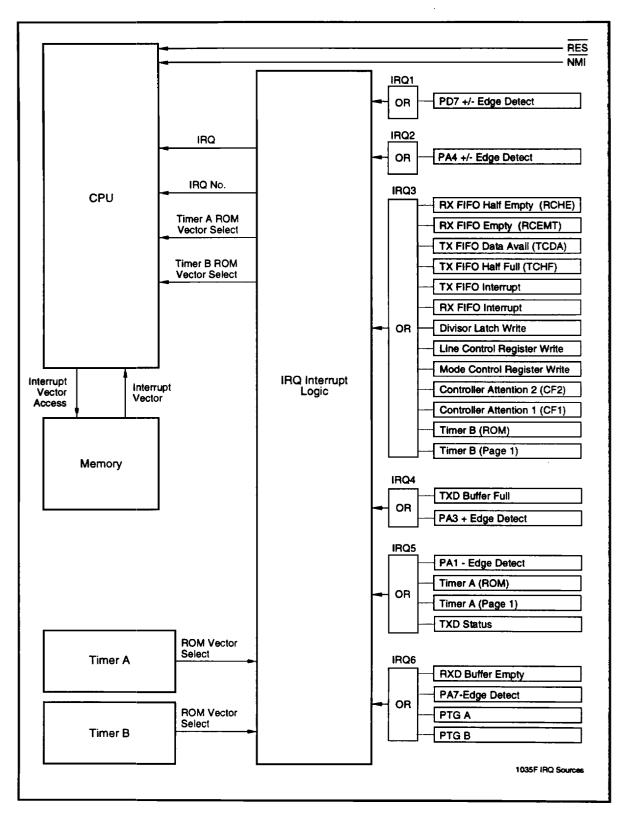

- Eight levels of prioritized, vectored interrupts

- RESP (highest priority)

- Non-mask interrupt (NMI)

- Six prioritized interrupt requests (IRQ1-IRQ6)

Six IRQ ROM vectors

Two software selectable Timer IRQ page 1 RAM vectors

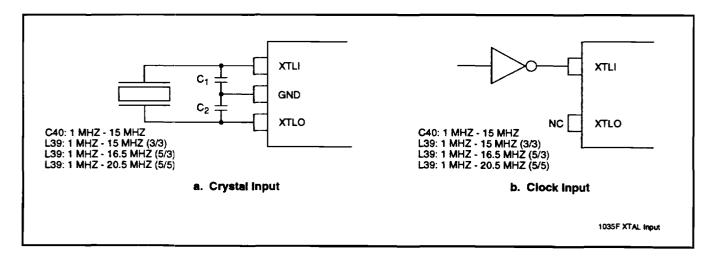

Internal clock with crystal or clock input

- Internal divide-by-1 input frequency divider

- Input Frequency

C40:1 MHz to 10 MHz

L39: 1 MHz to 15 MHz (3/3), 16.5 MHz (5/3), or 20.5 MHz (5/5) MHz

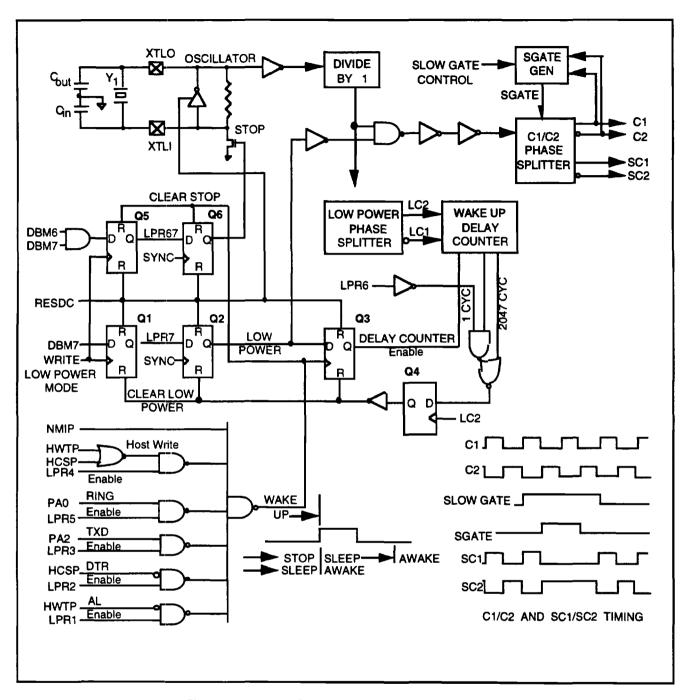

Sleep mode, software enabled,

Low power dissipation

Normal operation resumption within 2 clock cycles upon wake up condition

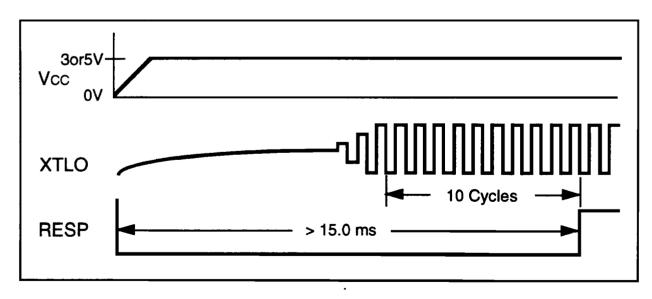

Stop mode, software enabled (L39 only))

Ultra-low power dissipation

Normal operation resumption within 12 clock cycles after power on stabilization upon wake up condition

- Flexible wake up conditions from Sleep or Stop mode

Awakened by a low on NMIP

Awakened by a high detected on PAO, software enabled

Awakened by a low detected on PA2, software enabled

Awakened by a low detected PD4, software enabled

Awakened by a low detected PD5 software enabled

Awakened by a low detected on PD4 or on PD5, software enabled

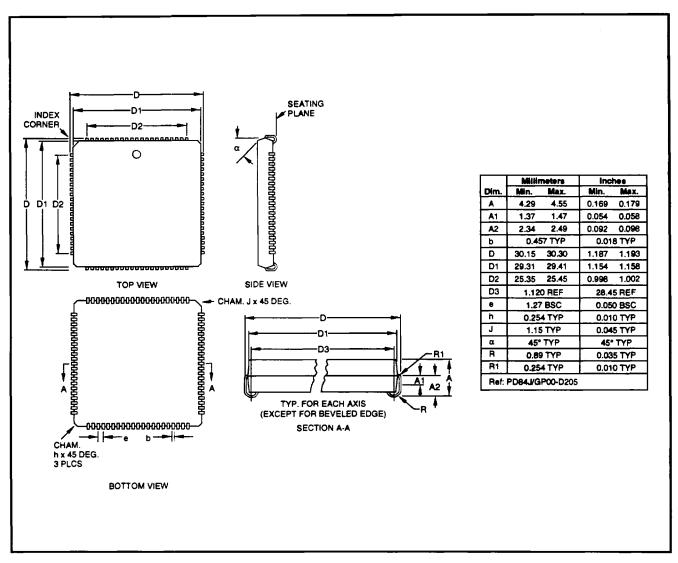

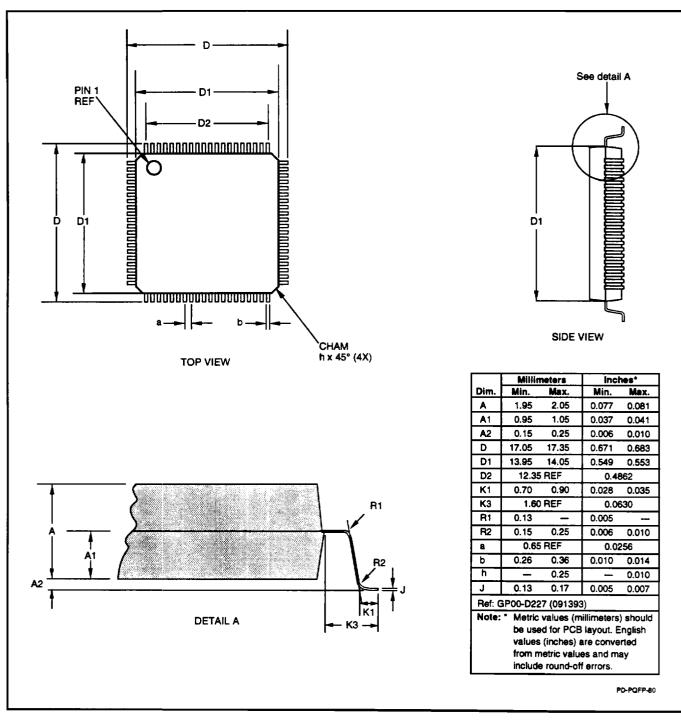

- Available in plastic leaded chip carrier (PLCC) or low profile plastic quad flat pack (PQFP) packages

- 84-pin PLCC

- 80-pin PQFP

- Flexible power supply

+5 V ±5%

+3.3 V ±0.3V (L39 only)

# 1.3. MCU FEATURE COMPARISON

The feature differences between the MCUs are summarized in Table 1-1.

Table 1-1. MCU Feature Comparison

| Feature                                                                                                                                                 | C2900     | C3900     | C4000     | L3900                | L3902                | Units | Ref.               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|----------------------|----------------------|-------|--------------------|

| Power Supply                                                                                                                                            | +5        | +5        | +5        | +5/+3.3              | +5/+3.3              | VDC   | 4.2                |

| Crystal speed divisor                                                                                                                                   | 2         | 1         | 1         | 1                    | 1                    |       | 3.3                |

| Maxiimum clock frequency                                                                                                                                | 10        | 10        | 10        | 15, 16.5, or<br>20.5 | 15, 16.5, or<br>20.5 | MHz   | 3.3                |

| ROM                                                                                                                                                     | 8k        | 8k        | 8k        | 8k                   | 8k                   | Bytes | 3.6                |

| Slow external clock firmware in internal ROM                                                                                                            | No        | No        | Yes       | Yes                  | Yes                  |       | 3.6.2              |

| RAM                                                                                                                                                     | 1024      | 1024      | 1024      | 1470                 | 1470                 | Bytes | 3.7                |

| Page 0 RAM                                                                                                                                              | 128       | 128       | 192       | 192                  | 192                  | Bytes | 3.7                |

| Page 1-3 RAM                                                                                                                                            | 768       | 768       | 768       | 768                  | 768                  | Bytes | 3.7                |

| Page 4 RAM                                                                                                                                              | 128       | 128       | 64        | 256                  | 256                  | Bytes | 3.7                |

| Page 5 RAM                                                                                                                                              | 0         | 0         | 0         | 254                  | 254                  | Bytes | 3.7                |

| 64-byte RAM on page 1 addressable on page 0                                                                                                             | Yes       | Yes       | No        | No                   | No                   |       | 3.9.6              |

| CRC Locations                                                                                                                                           | 0480-0481 | 0480-0481 | 05FE-05FF | 05FE-05FF            | 05FE-05FF            |       | Fig. 3-2b          |

| Bytes GP Scratchpad RAM                                                                                                                                 | 15        | 13        | 13        | 13                   | 13                   | Bytes | 3.14.2             |

| 16-byte FIFO                                                                                                                                            | No        | Yes       | Yes       | Yes                  | Yes                  |       | 3.14.2,<br>3.14.3  |

| Host interface                                                                                                                                          | 16450     | 16550A    | 16550A    | 16550A               | 16550A               |       | 3.14.3             |

| 16550 interface Timer B & PTGB Override                                                                                                                 | No        | No        | Yes       | Yes                  | Yes                  |       | 3.14.3             |

| Six FIFO IRQ3 interrupts added to 16550 interface                                                                                                       | No        | Yes       | Yes       | Yes                  | Yes                  |       | Table 3-5          |

| DMA handshake with RDYand ACK lines                                                                                                                     | No        | Yes       | Yes       | Yes                  | Yes                  |       | 3.14.3,<br>3.14.14 |

| Internal pull-up resistors provided on PA3 and PA4                                                                                                      | NA        | No        | Yes       | No                   | Yes                  |       | Table 2-1          |

| Enable RXD on PA6 when<br>RXD is selected (SM7 = 1);<br>overrides RXRDY on PA6<br>in 16550 mode (FCR0 = 1)                                              | No        | No        | Yes       | Yes                  | Yes                  |       | 3.12               |

| In 16550 mode (FCR0 = 1),<br>disable HTACKP on PA3<br>and HRACKP on PA4 when<br>RXD mode is selected<br>(SM7 = 1) or SYNC mode<br>is selected (SM4 = 1) | No        | No        | Yes       | No                   | Yes                  |       | 3.12               |

| USART PTG divide by 3 option                                                                                                                            | No        | No        | Yes       | Yes                  | Yes                  |       | 3.12.8             |

| USART PTGA source option for SINC                                                                                                                       | No        | No        | Yes       | Yes                  | Yes                  |       | 3.12.4             |

| Low power mode                                                                                                                                          | Sleep     | Sleep     | Sleep     | Sleep/Stop           | Sleep/Stop           |       | 3.4                |

| Data bus (D0-D7) receivers off during Sleep/Stop                                                                                                        | No        | No        | Yes       | Yes                  | Yes                  |       | Table 2-1          |

| Wake-up interrupts in low power mode                                                                                                                    | 3         | 5         | 5         | 5                    | 5                    |       | 3.16.1             |

| BRK vector                                                                                                                                              | IRQ6      | NMI       | NMI       | NMI                  | NMI                  | †     | 3.5.2              |

### 1.4. MCU DESIGN CHANGES FROM THE C39 MCU

MCU changes effecting input/output operation are summarized below.

#### 1.4.1. Design Changes Incorporated in the C40 MCU

#### A. Common to the C40, L3900, and L3902

- 1. Slow External Clock Internal Firmware Added. Firmware was added to internal masked ROM to support 8 MHz applications.

- Software Selectable 64-byte RAM Segments Deleted. The ability to select 64-byte segments of page 1

addressable on page 0 was deleted. 64 bytes are permanently reassigned to page 0 (now 192 bytes).

- 3. **LSR Flag Setting Synchronized.** The 16550 Line Status Register (LSR) error flag setting was synchronized with the data in RX FIFO to prevent erroneous operation (loss of valid data and acceptance of erroneous data) by communications software that interprets the error status flags.

- USART Timer Improved. An option to select the divide by 3 function on the USART timing source was added and an option to select the PTGA as the USART timing source for SINC was added.

- 5. **Enable RXD on PA6 in 16550 Mode Added** The ability to enable RXD on PA6 when RXD is selected (SMR7 = 1) regardless of other modes, was added.

#### B. Common to the C40 and L3902

- 1. Internal PA3 and PA4 Pull-up Resistors Added. Internal Pull-up resistors were added to the PA3 and PA4 ports to eliminate the need for external pull-up resistors.

- 2. **Disable HTACKP and HRACKP in 16550 Mode Added.** When 16550 mode is selected (FCR0 = 1), the ability to disable HTACKP on PA3 and HRACKP on PA4 when RXD mode is selected (SMR7 = 1) or SYNC mode is selected (SMR4 = 1) was added.

- 3. Internal XTLO 100 Ohm Series Resistor Added. An internal 100 ohm series resistor was added to the XTLO signal to eliminate the need for an external 100 ohm series resistor to improve oscillator start up with fast rise time power supplies. In application designs already providing an external 100 ohm resistor, the external resistor may be left in the circuit (providing 200 ohms total) with no adverse effect.

#### 4. FIFO Operation Improved.

- a. The ability of the host to read the receive buffer during the first interval after the MCU writes to an empty RX FIFO was added.

- b. A problem that can occur when the host does not read the 16450 buffer between the first and second baud interval after the MCU writes to an empty receiver FIFO was corrected.

- c. Clearing of the RX FIFO and the TX FIFO whenever the host changes the state of the FIFO Enable bit in the FIFO Control Register (FCR0) was added.

#### 1.4.2. Design Changes Incorporated in the L3900 MCU

#### A. Common to the C40, L3900, and L3902

Same As 1.4.1 Item A.

#### B. Common to the L3900 and L3902

- 1. 3.3 V Operation Option Added. The ability to operate the MCU on 3.3 V I/O and 3.3 V core (3/3) was added (mask option).

- 2. **5 V Low Power Operation Option Added.** The ability to operate the MCU with a 5 V I/O and a 3.3 V core (5/3) was added for lower power operation in addition to the 5 V I/O and 5 V core (5/5) (mask option).

- 3. **Maximum Clock Rate Raised.** The maximum clock frequency was raised to 20.5 MHz (5/5), 16.5 MHz (5/3), or 15 MHz (3/3).

- 4. Power Consumption Reduced. Circuits were improved to reduce power consumption.

- 5. Stop Mode Added. Stop mode was added with ultra-low power consumption.

- Internal RAM Enlarged. The internal RAM was enlarged from 1024 bytes to 1470 bytes.

- Data Bus Receivers Disabled in Low Power Modes. Circuitry was added to disable external memory bus data receivers in low power mode (Sleep and Stop).

#### 1.4.3. Design Changes Incorporated in the L3902 MCU

#### A. Common to the C40, L3900, and L3902

Same as 1.4.1 Item A.

#### B. Common to the C40 and L3902

Same as 1.4.1 Item B.

### C. Common to the L3900 and L3902

Same as 1.4.2 item B.

#### D. Unique to the L3902

- 1. 16550 Interface Operation Improved.

- a. The Interrupt Identifier Register (IIR) operation was changed to automatically clear the Receiver Buffer Full (Data Available) interrupt when the RX FIFO trigger level control is changed from a value lower than the RX FIFO contents to a value greater than the RX FIFO contents.

- b. The IIR operation was changed to cause the Receiver Buffer Full and Character Timeout interrupts to respond to changes to the receiver timeout event without first reading the RX FIFO.

- 2. Internal ROM Read Added. The ability to read internal ROM from address \$FE00-\$FFFF when TSTP pin is low was added.

# 1.5. REFERENCES

- 1. C39R (C40) Microcontroller PO1 Specification, Rev. NC, January 19, 1994.

- 2. L39 Microcontroller PO1 Specification, Rev. NC, February 21, 1994.

# 2. INTERFACE DESCRIPTION

# 2.1. PIN ASSIGNMENTS

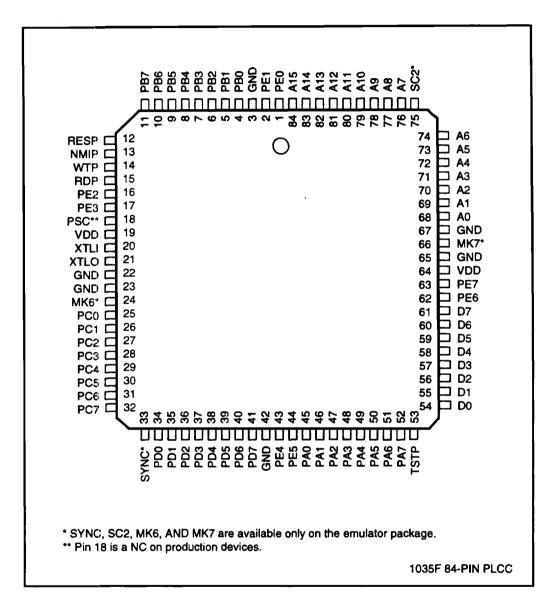

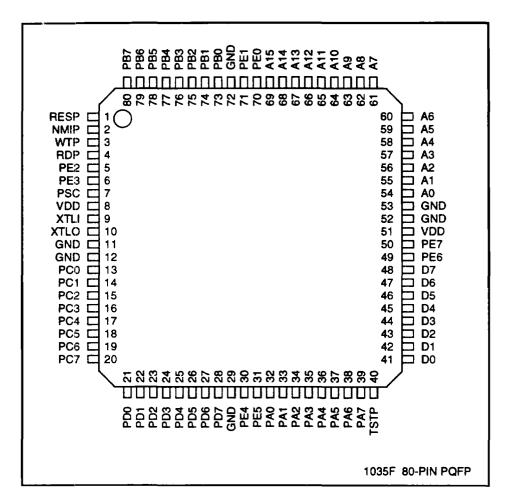

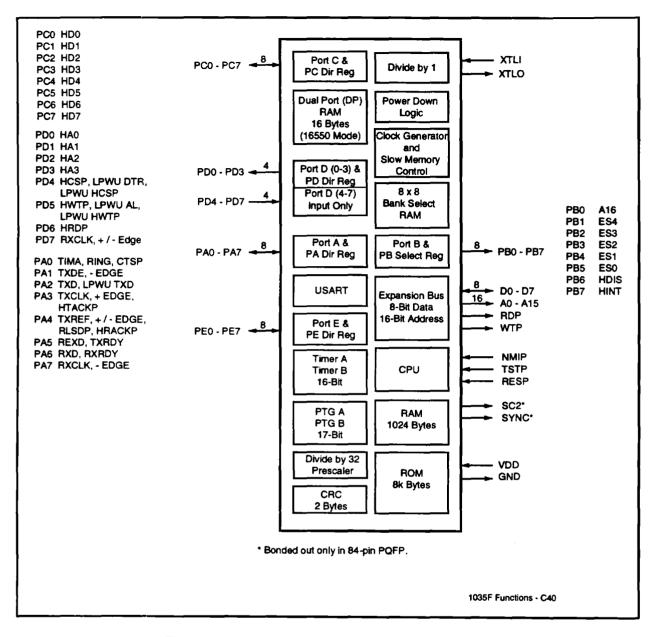

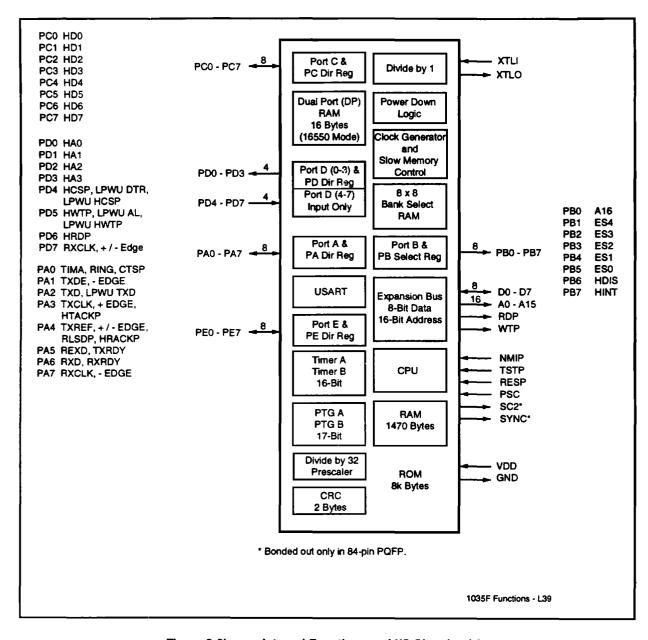

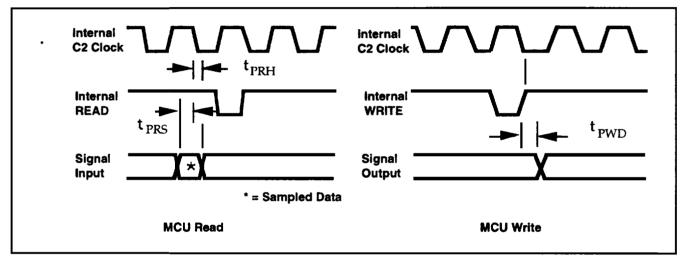

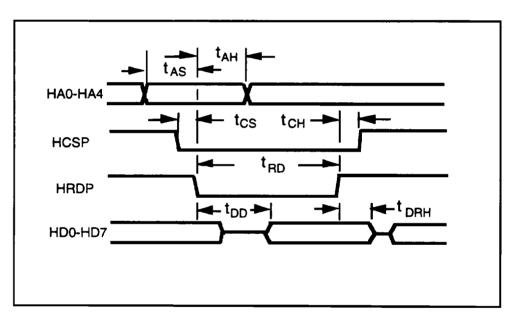

The pin assignments for the 84-pin PLCC and the 80-pin PQFP packages are shown in Figure 2-1. The t/O signals are shown in Figure 2-2 along with the major interfacing MPU functions.

Figure 2-1a. Pin Assignments - 84-Pin PLCC

Figure 2-1b. Pin Assignments - 80-Pin PQFP

Figure 2-2a. Internal Functions and I/O Signals - C40

Figure 2-2b. Internal Functions and I/O Signals - L39

# 2.2. I/O PIN SIGNALS

The I/O pin signals are defined in Table 2-1.

Table 2-1. Interface Signal Description

| Symbol                     | VO  | Name / Function                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAO-PA7                    | I/O | General Purpose 8-Bit VO Port A. All pins can be assigned special functions under software control. The Port A Direction Register (PAD) must be set appropriately for all pins in both general and special use. PA1, PA3, PA4 and PA7 have edge detect circuitry that remains active regardless of data direction. PA3 and PA4 have an internal pull-ups (C40 and L3902 and subsequent).                                        |

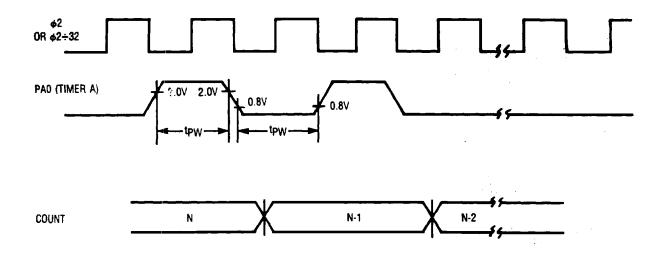

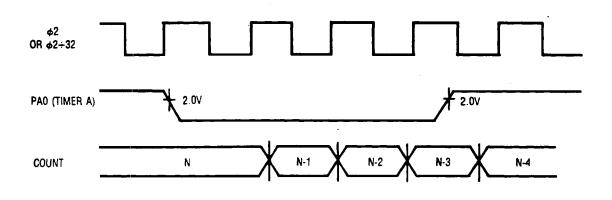

| TIMA<br>(PA0)              | 1/0 | Timer A VO. An input in Timer A Event Counter or Pulse Width Measurement mode and an output in Timer A Pulse Generation mode.                                                                                                                                                                                                                                                                                                   |

| RING<br>(PA0)              | 1/0 | Ring. An unclocked input whose positive level is used to clear the low power mode. Ring is enabled by LPR5.                                                                                                                                                                                                                                                                                                                     |

| CTSP<br>(PA0)              | 1   | Clear To Send. The negative edge of an external CTSP signal can be used to initialize the USART TXD synchronous mode word counter (SMR1 = 1).                                                                                                                                                                                                                                                                                   |

| TXDE<br>(PA1)              | 0   | Serial Input Passthrough. PA2 input is connected to the PA1 output when the serial pass through is selected (SFR7 = 1).                                                                                                                                                                                                                                                                                                         |

| <b>t</b> Edge (PA1)        | I/O | PA1 Negative Edge Detect. The PA1 edge detect flag (EIR7) is set on each detected edge and is cleared by writing a zero to register bit CI7. When the PA1 edge detect flag is set (EIR7 = 1), IRQ5 will be asserted if its enable is set (EIR4 = 1).                                                                                                                                                                            |

| TXD<br>(PA2)               | ţ   | TXD Serial Input. PA2 input is connected to the USART as the serial input stream when USART TXD mode is selected (SMR6 = 1).                                                                                                                                                                                                                                                                                                    |

| TXCLK<br>(PA3)             | I/O | TXCLK Clock. PA3 is internally connected to the serial input clock when synchronous USART operation is selected (SMR4 = 1). TXCLK can be an external signal, an internal signal, or can be internally connected to TXREF (PA4). TXD is clocked on the rising edge of TXCLK.                                                                                                                                                     |

| <b>∮</b> Edge<br>(PA3/PA2) | I/O | PA3/PA2 Positive Edge Detect. The PA3/PA2 edge detect flag (SIR6) is set on each detected edge and is cleared by writing a zero to register bit CI3. When the PA3/PA2 edge detect flag is set (SIR6 = 1), IRQ4 will be asserted if its enable is set (SIR4 = 1). A PA3 edge is detected when SFR3 = 0 and a PA2 edge is detected when SFR3 = 1.                                                                                 |

| HTACKP<br>(PA3)            | i   | Host Transmit Acknowledge. PA3 is an active low transmit acknowledge input signal asserting the host 16550 DMA TX FIFO address and chip select when host mode is enabled (HCR2 = 1), 16550/16450 DP RAM is selected (HCR1 = 1), FIFO is enabled which selects 16550 mode (FCR0 = 1), and serial mode is not selected (SMR7 = 0 and SMR4 = 0).  Note that HTACKP on PA3 and HRACKP on PA4 are disabled when RXD mode is selected |

|                            |     | (SMR7 = 1) or SYNC mode is selected (SMR4 = 1) (C40 and L3902 and subsequent).                                                                                                                                                                                                                                                                                                                                                  |

Table 2-1. Interface Signal Description (Cont'd)

| Symbol                          | VO  | Name / Function                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXREF<br>(PA4)                  | I   | External TXD Reference Clock. PA4 input is connected internally to PA3 output when synchronous USART operation is selected (SMR4 = 1) and TXREF is selected as the TXCLK source (SMR2 = 1).                                                                                                                                                                                                                                               |

| <b>f</b> or <b>t</b> Edge (PA4) | I/O | PA4 Positive/Negative Edge Detect. The PA4 edge detect flag (EIR6) is set on each detected edge and is cleared by writing a zero to register bit CI6. When the PA4 edge detect flag is set (EIR6 = 1), IRQ2 will be asserted if its enable is set (EIR3 = 1). PA4 will : etect a negative (EIR1 = 0) or a positive (EIR1 = 1) edge.                                                                                                       |

| RLSDP<br>(PA4)                  | 0   | Receiver Line Signal Detect. The negative edge of an external RLSDP signal can be used to initialize the USART RXD synchronous mode word counter (SMR1 = 1).                                                                                                                                                                                                                                                                              |

| HRACKP<br>(PA4)                 | 1   | Host Receive Acknowledge. PA4 is an active low receive acknowledge input signal asserting the host 16550 DMA RX FIFO read address and chip select when host mode is enabled (HCR2 = 1), 16550/16450 DP RAM is selected (HCR1 = 1), FIFO is enabled which selects 16550 mode (FCR0 = 1), and serial mode is not selected (SMR7 = 0 and SMR4 = 0).                                                                                          |

|                                 |     | Note that HTACKP on PA3 and HRACKP on PA4 are disabled when RXD mode is selected (SM7 = 1) or SYNC mode is selected (SM4 = 1) (C40 and L3902 and subsequent).                                                                                                                                                                                                                                                                             |

| REXD<br>(PA5)                   | l   | Serial Output Passthrough. PA5 input is internally connected to the PA6 output when serial out pass through mode is selected (SMR7 = 1, SFR5 = 0, and SFR6 = 1).                                                                                                                                                                                                                                                                          |

| TXRDY<br>(PA5)                  | 0   | Transmit Ready. PA5 is an active high transmit ready output in the host 16550 DMA TX FIFO write mode and the 16450 mode when host mode is enabled (HCR2 = 1), 16550/16450 DP RAM is selected (HCR1 = 1), FIFO is enabled which selects 16550 mode (FCR0 = 1), and serial mode is not selected (SMR7 = 0 and SMR4 = 0). When asserted, TXRDY indicates that the TX FIFO is not full, i.e., the TX FIFO can accept data to be transmitted.  |

| RXD<br>(PA6)                    | 0   | RXD Serial Output. PA6 is connected as the USART serial output stream when RXD ON is selected (SMR7 = 1). When loopback is selected (SFR5 = 1) the PA2 signal is internally connected to the PA6 output. PA6 is also modified by the serial output pass through mode (SFR6 = 1).                                                                                                                                                          |

| RXRDY<br>(PA6)                  | 0   | Receive Ready. PA6 is an active high receive ready output in the host 16550 DMA RX FIFO read mode and the 16450 mode when host mode is enabled (HCR2 = 1), 16550/16450 DP RAM is selected (HCR1 = 1), FIFO is enabled which selects 16550 mode (FCR0 = 1), and serial mode is not selected (SMR7 = 0 and SMR4 = 0). When asserted, RXRDY indicates that the RX FIFO is not empty, i.e., the RX FIFO has received data ready for transfer. |

| RXCLK<br>(PA7)                  | I/O | RXD Serial Output Clock. PA7 output is internally connected to the USART in the synchronous mode (SMR7 = 1 and SMR4 = 1). RXCLK can be an external input signal or can be generated internally and become an output signal. Serial out is clocked on the negative edge of RXCLK.                                                                                                                                                          |

| Edge<br>(PA7)                   | I/O | PA7 Negative Edge Detect. The PA7 edge detect flag (SIR5) is set on each detected edge and is cleared by writing a zero to register bit CI4. When the PA7 edge detect flag is set (SIR5 = 1), IRQ6 will be asserted if its enable is set (SIR3 = 1).                                                                                                                                                                                      |

Table 2-1. Interface Signal Description (Cont'd)

| Symbol               | VO  | Name / Function                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB0-PB7              | 0   | General Purpose 8-Bit Output Port B. All pins can be assigned special functions under software control. The Port B Selection Register (PBS) must be set appropriately for all pins in both general and special use. All Port B outputs float during reset active low.                                                                                                                          |

| A16<br>(PB0)         | 0   | A16. When PBS0 = 0, the PB0 pin becomes the A16 address function from the selected or active (i) Banking RAM register bit 4 (BRi4). Note: PB0 is an A16 address option and may not be wire bonded out in some packages.                                                                                                                                                                        |

| ES4<br>(PB1)         | 0   | ES4. When PBS1 = 0, the PB1 pin becomes the ES4 chip select signal. ES4 is active low from addresses \$0600 to \$07FF.                                                                                                                                                                                                                                                                         |

| ES3<br>(PB2)         | 0   | <b>ES3.</b> When PBS2 = 0, the PB2 pin becomes the ES3 chip select signal. ES3 is controlled by bit 7 of the selected or active (i) Banking RAM register (BRi7).                                                                                                                                                                                                                               |

| ES2<br>(PB3)         | 0   | ES2. When PBS3 = 0, the PB3 pin becomes the ES2 chip select signal. ES2 is controlled by bit 6 of the selected or active (i) Banking RAM register (BRi6). L39: Note that PB3 is a chip select option and may not be wire bonded out in some packages.                                                                                                                                          |

| ES1<br>(PB4)         | 0   | ES1. When PBS4 = 0, the PB4 pin becomes the ES1 chip select signal. ES1 is controlled by bit 5 of the selected or active (i) Banking RAM register (BRi5).                                                                                                                                                                                                                                      |

| ES0<br>(PB5)         | 0   | <b>ES0.</b> When PBS5 = 0, the PB5 pin becomes the ES0 chip select signal. ES0 is controlled by bit 4 of the selected or active (i) Banking RAM register (BRi4).                                                                                                                                                                                                                               |

| HDIS<br>(PB6)        | 0   | Host Bus Driver Disable. Active high output asserted when Host Mode is enabled (HCR2 = 1) and data is being read from the MCU host data bus. Note: It is recommended that the host bus I/O read and the chip select inputs to the MCU be ANDed and the output used as the host bus driver disable function instead of HDIS to control the host data direction through an external transceiver. |

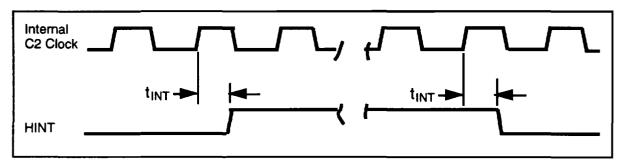

| HINT<br>(PB7)        | 0   | <b>Host Bus Interrupt.</b> Active high output asserted in both the GP host interface (HC2 = 1 and HC1 = 0) or the 16450/16550 host interface (HC2 = 1 and HC1 = 1) under various conditions.                                                                                                                                                                                                   |

| PC0-PC7              | I/O | General Purpose 8-Bit I/O Port C. All pins can be assigned in a group to host bus data lines by a software option. The Port C Direction Register (PCD) must be set appropriately for all pins.                                                                                                                                                                                                 |

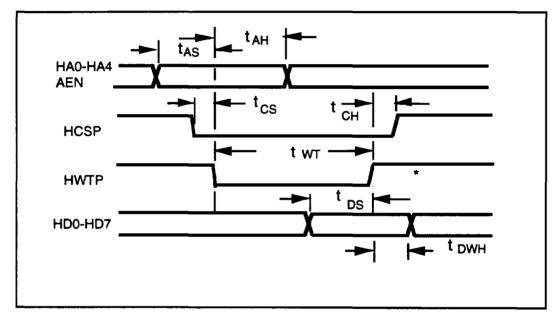

| HD0-HD7<br>(PC0-PC7) | I/O | Host Bus Data Lines. PC0-PC7 are dedicated to the host bus interface bidirectional data lines HD0-HD7, respectively, when Host Mode is enabled (HCR2 = 1). The Port C direction register must be set to the output mode in this case (HCR2 = 1).                                                                                                                                               |

Table 2-1. Interface Signal Description (Cont'd)

| Symbol                                | VO       | Name / Function                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD0-PD3<br>PD4-PD7                    | I/O<br>I | General Purpose 4-Bit VO and 4-Bit Input Port D. PD0-PD3 are general purpose I/O pins while PD4-PD7 are input only. PD0-PD3 output latch is controlled by writing bits 0-3 at address \$0003, while their direction control is contained in bits 4-7, respectively. PD0-PD6 are assigned in a group to host bus address and control lines when Host Mode is enabled (HCR2 = 1). |

| HA0-HA3<br>(PD0-PD3)                  | l        | Host Bus Address Lines. PD0-PD3 are dedicated to the host bus interface as address lines HA0-HA3, respectively, when Host Mode is enabled (HCR2 = 1, HCR1 = 0). PD3 remains a GP pin in the 16450/16550 mode (HCR2 = 1, HCR1 = 1).                                                                                                                                              |

| HCSP<br>(PD4)                         | ł        | Host Bus Chip Select. PD4 is dedicated to the host bus interface as the active low chip select input when Host Mode is enabled (HCR2 = 1).                                                                                                                                                                                                                                      |

| HWTP<br>(PD5)                         | 1        | Host Bus Write. PD5 is dedicated to the host bus interface as an active low write control input when Host Mode is enabled (HCR2 = 1).                                                                                                                                                                                                                                           |

| HRDP<br>(PD6)                         | l        | Host Bus Read. PD6 is dedicated to the host bus interface as an active low read control input when Host Mode is enabled (HCR2 = 1).                                                                                                                                                                                                                                             |

| <b>f</b> or <b>t</b><br>Edge<br>(PD7) | I        | PD7 Positive/Negative Edge Detect. The PD7 edge detect flag (EIR5) is set on each detected edge and is cleared by writing a zero to register bit CI5. When the PD7 edge detect flag is set (EIR5 = 1), IRQ1 will be asserted if its enable is set (EIR2 = 1). PD7 will detect a negative (EIR0 = 0) or a positive (EIR0 = 1) edge.                                              |

| PE0-PE7                               | 1/0      | General Purpose 8-Bit I/O Port E. The Port E Direction Register (PED) must be set appropriately for all pins.                                                                                                                                                                                                                                                                   |

Table 2-1. Interface Signal Description (Cont'd)

| Symbol                      | VO  | Name / Function                                                                                                                                                                                                                                      |

|-----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

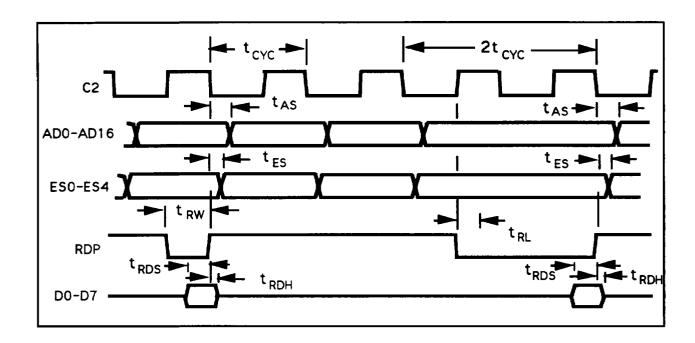

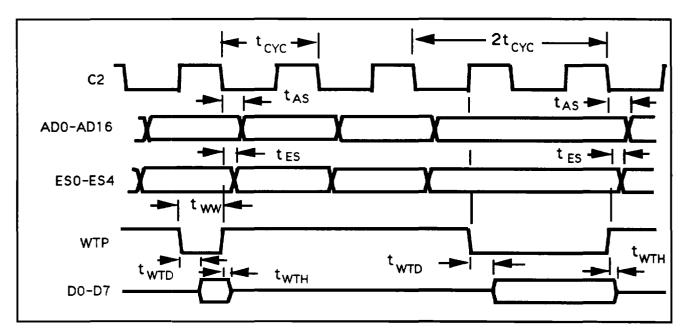

| A0-A12                      | 0   | A0-A12 . Address lines for external memory bus. These lines float during reset active.                                                                                                                                                               |

| A13-A15                     | 0   | A13-A15. Address lines for external memory bus. These lines float during reset active. Address lines A13 - A15 are generated by bits 0 - 2 (m), respectively, of the active or selected (i) Banking RAM register (BRim).                             |

| D0-D7                       | 1/0 | Expansion Bus Data. D0-D7 provide an 8-bit bi-directional data bus for interfacing to external memories. D0-D7 float during reset active. L39: The receivers are automatically disabled during low power modes (Sleep and Stop)                      |

| WTP                         | 0   | <b>Expansion Bus Write.</b> Active low write strobe for the expansion bus. When WTP is asserted, data on the expansion data bus is written into the selected peripheral device. WTP remains high during MCU reset active.                            |

| RDP                         | 0   | <b>Expansion Bus Read.</b> Active low read strobe for the expansion bus. When RDP is asserted, data is read from the selected peripheral device onto the expansion data bus. RDP remains high during MCU reset active.                               |

| RESP                        | 1   | Reset. Active low input resets all MCU circuits and registers to their initial state. MCU operation resumes when the RESP input goes high; program execution starts at the location defined by the reset address vector.                             |

| NMIP                        | 1   | Non-Maskable Interrupt. Non- Maskable negative edge sensitive interrupt input. Interrupts program execution upon completion of current instruction and jumps to interrupt service subroutine starting at location defined by the NMI address vector. |

| LPWU<br>NMIP                | 1   | Low Power Wake Up - NMIP. When the MCU is in low power mode, a low level on the NMIP pin will cause normal operation to resume.                                                                                                                      |

| LPWU Ring<br>(PA0)          | 1   | Low Power Wake Up - Ring. When the MCU is in low power mode, a high level on PA0 will cause normal operation to resume if the Wake-Up Enable for PA0 (Ring) bit is set (LPR5 = 1).                                                                   |

| LPWU HBW<br>(PD4 +<br>PD5)P | 1   | Low Power Wake Up - Host Bus Write. When the MCU is in low power mode, a low level on both PD4 and PD5 will cause normal operation to resume if the Wake-Up Enable for PD4 and PD5 (Host Bus Write and MCU Chip Select) bit is set (LPR4 = 1).       |

| LPWU TXD<br>(PA2)P          | I   | Low Power Wake Up - TXD (TXD Start Bit). When the MCU is in low power mode, a low level on PA2 will cause normal operation to resume if the Wake-Up Enable for PA2 (TXD Start Bit) bit is set (LPR3 = 1).                                            |

| LPWU DTR<br>(PD4)P          | I   | Low Power Wake Up - DTR. When the MCU is in low power mode, a low level on PD4 will cause normal operation to resume if the Wake-Up Enable for PD4 (DTR) bit is set (LPR2 = 1).                                                                      |

| LPWU AL<br>(PD5)P           | I   | Low Power Wake Up - AL. When the MCU is in low power mode, a low level on PD5 will cause normal operation to resume if the Wake-Up Enable for PD5 (AL) bit is set (LPR1 = 1).                                                                        |

Table 2-1. Interface Signal Description (Cont'd)

| Symbol | VO | Name / Function                                                                                                                                                                                                                                                                                   |  |

|--------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TSTP   | ī  | Emulator Mode. The TSTP is an input with an internal pull-up.                                                                                                                                                                                                                                     |  |

|        |    | TSTP high places the MCU in the normal operating mode:                                                                                                                                                                                                                                            |  |

|        |    | 1. Internal ROM is enabled.                                                                                                                                                                                                                                                                       |  |

|        |    | 2. RDP and WTP reflect CPU activity.                                                                                                                                                                                                                                                              |  |

|        |    | 3a. C40: Internal CPU read from pages 0, 1, 2, 3, or 4 (internal RAM and registers) do<br>not cause the internal data to appear on the expansion bus.                                                                                                                                             |  |

|        |    | 3b. L39: Internal CPU read from pages 0, 1, 2, 3, 4, or 5 (internal RAM and registers) do not cause the internal data to appear on the expansion bus.                                                                                                                                             |  |

|        |    | TSTP low places the MCU in the emulation mode:                                                                                                                                                                                                                                                    |  |

|        |    | Internal ROM is disabled and all ROM fetches are transferred to the expansion bus.                                                                                                                                                                                                                |  |

|        |    | 2a. C40: Internal bus activity on pages 0, 1, 2, 3, or 4 impact D0-D7. Internal CPU read from pages 0-4 cause the internal data to appear on D0-D7.                                                                                                                                               |  |

|        |    | 2b. L39 Internal bus activity on pages 0, 1, 2, 3,4, or 5 impact D0-D7. Internal CPU read from pages 0-5 cause the internal data to appear on D0-D7.                                                                                                                                              |  |

| SYNC   | 0  | Sync. Sync high denotes that the current cycle is an op code fetch for the next instruction (Emulator package only.)                                                                                                                                                                              |  |

| SC2    | 0  | SC2. SC2 is an output operating at the crystal frequency or slower depending upon the external memory selected and is in phase with the internal C2 clock (Emulator package only.)                                                                                                                |  |

| XTLI   | 1  | Crystal Oscillator Input Pin. Input connection from crystal or external clock circuit.                                                                                                                                                                                                            |  |

| XTLO   | 0  | Crystal Return. Oscillator output connection to an external crystal. Open when the XTLI input is connected to an external clock.                                                                                                                                                                  |  |

| PSC    | 1  | Power Supply Control (L39 Only). Input pin with internal bond wire connected to internal pad to select either a VDD = 3.3 V device with 3.3 V I/O (logic 0) or a VDD = 5 V device with an internal 3.3 V regulator for low power operation of the core logic (logic 1). MOR0 reflects the RC pad. |  |

|        |    | 5 V Part Only. Input pin can be left unconnected (NC) or connected to VDD.                                                                                                                                                                                                                        |  |

|        |    | 3.3 V Part Only. Input pin with no external connection (NC). Note: If VDD = 5 V, the receivers will work only for CMOS. MOR0 reads logic-0.                                                                                                                                                       |  |

| MK6    | NA | Factory Option Pin - MK6. Emulator only.                                                                                                                                                                                                                                                          |  |

| МК7    | NA | Factory Option Pin - MK7. Emulator only.                                                                                                                                                                                                                                                          |  |

| VDD    | ı  | Power. C40: +5 V. L39: +5 V or +3.3 V.                                                                                                                                                                                                                                                            |  |

| GND    | 1  | Ground. Signal and power ground.                                                                                                                                                                                                                                                                  |  |

# 3. SYSTEM ARCHITECTURE

### 3.1. OVERVIEW AND MEMORY MAPS

### 3.1.1. Block Diagram

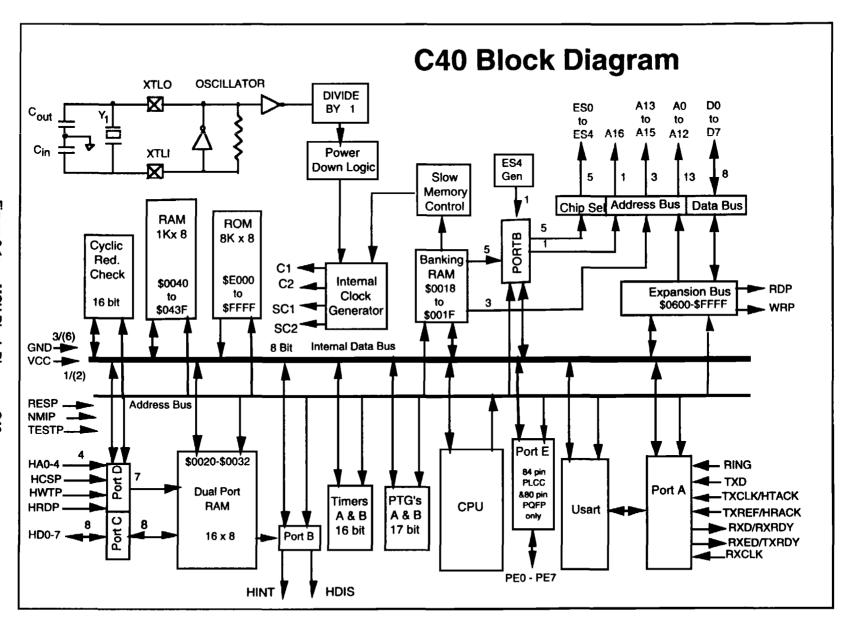

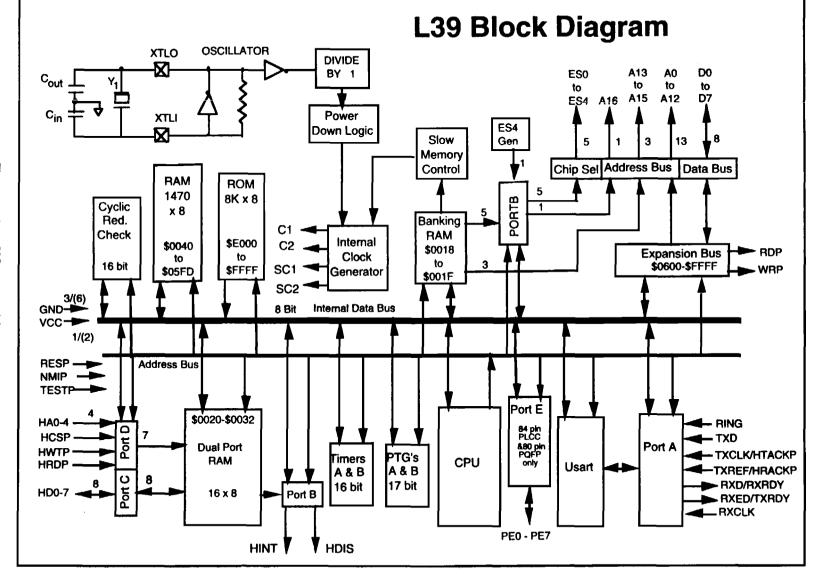

A block diagram of the MCU is shown in Figure 3-1.

### 3.1.2. Top Level Memory Map

The top level memory map in Figures 3-2 shows major boundaries between I/O, internal ROM, internal RAM, and external addresses. The individual registers are identified in Table 3-1.

**Figure** MCU Block Diagram - C40

Section 3 - System Architecture

Figure 3-1b. MCU Block Diagram - L39

Section 3 - System Architecture

| Bank Select<br>Register | Address<br>(Hex) |                                 |

|-------------------------|------------------|---------------------------------|

|                         | FFE0 - FFFF      | Interrupt/JSR Vectors (32)      |

| BSR7 (8K)               | FFDF             |                                 |

|                         | F000             | Internal ROM (8K-32), TSTP High |

|                         | <b>E0</b> 00     | Default ESS Expansion, TSTP Low |

|                         | DFFF             |                                 |

| BSR6 (8K)               | <b>D000</b>      | Default                         |

| _                       | C000             | ES3 Expansion (32K)             |

|                         | BFFF             |                                 |

| BSR5 (8K)               | B000             |                                 |

|                         | A000             |                                 |

|                         | 9FFF             |                                 |

| BSR4 (8K)               | 9000             |                                 |

|                         | 8000             |                                 |

|                         | 7FFF             |                                 |

| BSR3 (8K)               | 7000             | Default                         |

|                         | 6000             | ES1 Expansion (16K)             |

|                         | 5FFF             |                                 |

| BSR2 (8K)               | 5000             |                                 |

|                         | 4000             |                                 |

|                         | 3FFF             | Default                         |

| BSR1 (8K)               | 3000             | ES1 Expansion (8K)              |

|                         | 2000             |                                 |

|                         | 17FF             | Default                         |

| BSR0 (8K)               | 1000             | ES0 Expansion (6K)              |

|                         | 0800             | <u> </u>                        |

|                         | 0600 - 07FF      | ES4 (512)                       |

|                         | 0000 - 05FF      | RAM and Registers (1536)        |

Figure 3-2a. MCU Memory Map Overview - 0 - FFFF

| Addr. (Hex)  | C40                                   | Addr. (Hex) | L39                                   |

|--------------|---------------------------------------|-------------|---------------------------------------|

| 07FF         | Page 7 (256)                          | 07FF        | Page 7 (256)                          |

|              | Available Externally                  |             | Available Externally                  |

| <b>07</b> 00 | (Part of ES4 when PBS1 = 0)           | 0700        | (Part of ES4 when PBS1 = 0)           |

| 06FF         | Page 6 (256)                          | 06FF        | Page 6 (256)                          |

|              | Available Externally                  |             | Available Externally                  |

| <b>06</b> 00 | (Part of ES4 when PBS1 = 0)           | 0600        | (Part of ES4 when PBS1 = 0)           |

| 05FE - 05FF  | CRC Control (2)                       | 05FE - 05FF | CRC Control (2)                       |

|              |                                       | 05FD        |                                       |

|              | Page 5 Unavailable (254)              |             | Page 5 RAM (254)                      |

| 0500         |                                       | 0500        |                                       |

| 0440-04FF    | Page 4 Unavailable (192)              | 04FF        |                                       |

| 043F         | Page 4 RAM (64)                       |             | Page 4 RAM (256)                      |

| 0400         |                                       | 0400        |                                       |

| 03FF         |                                       | 03FF        |                                       |

|              | Page 3 RAM (256)                      |             | Page 3 RAM (256)                      |

| 0300         |                                       | 0300        |                                       |

| 02FF         |                                       | 02FF        |                                       |

|              | Page 2 RAM (256)                      |             | Page 2 RAM (256)                      |

| 0200         |                                       | 0200        |                                       |

| 01FF         | Page 1 RAM (256)                      | 01FF        | Page 1 RAM (256)                      |

| 0100         |                                       | 0100        |                                       |

| OOFF         |                                       | 00FF        |                                       |

| -            | Page 0 RAM (128)                      |             | Page 0 RAM (128)                      |

| 0080         |                                       | 0080        | <u></u>                               |

| 007F         | Page 0 RAM (64)                       | 007F        | Page 0 RAM (64)                       |

| 0040         |                                       | 0040        |                                       |

| 0038 - 003F  | USART Registers (8)                   | 0038 - 003F | USART Registers (8)                   |

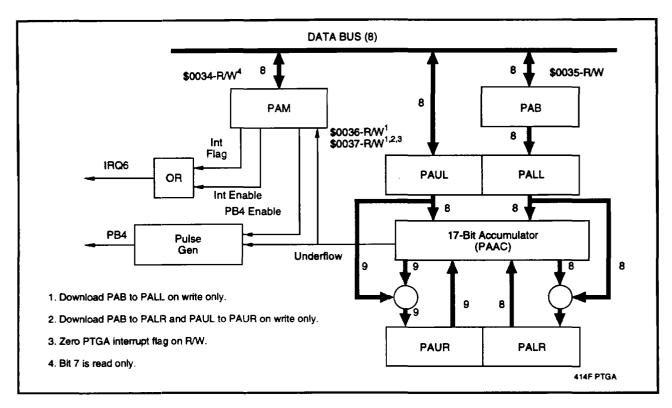

| 0034 - 0037  | Prec. Time Generator A (4)            | 0034 - 0037 | Prec. Time Generator A (4)            |

| 0033         | CS Speed Select                       | 0033        | CS Speed Select                       |

| 0020 - 0032  | 16550 I/F & DP RAM (19)               | 0020 - 0032 | 16550 I/F & DP RAM (19)               |

| 0018 - 00FF  | Bank Select Registers (8)             | 0018 - 00FF | Bank Select Registers (8)             |

| 0010 - 0017  | Timer/Counters A &B (8)               | 0010 - 0017 | Timer/Counters A &B (8)               |

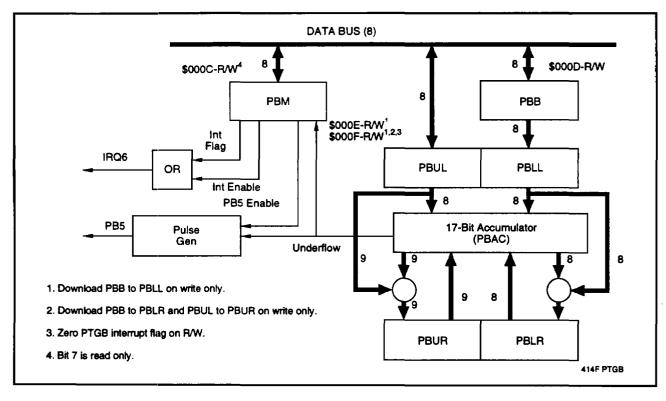

| 000C - 000F  | Prec. Time Generator B (4)            | 000C - 000F | Prec. Time Generator B (4)            |

| 0000 - 000B  | Ports A to E and Misc. Registers (12) | 0000 - 000B | Ports A to E and Misc. Registers (12) |

Figure 3-2b. MCU Memory Map Overview - 0 - 07FF

Table 3-1a. Memory Map: 0-001Fh

| Address      | Read                              | Write                                     |

|--------------|-----------------------------------|-------------------------------------------|

| 0000         | Port A                            | Port A                                    |

| 0001         |                                   | Port B (Output Only)                      |

| 0002         | Port C                            | Port C                                    |

| . 0003       | Port D                            | Port D (0-3), Direction (4-7)             |

| 0004         | -                                 | Port A Direction                          |

| 0005         | Port B Select                     | Port B Select                             |

| 0006         |                                   | Port C Direction                          |

| 0007         | Port E                            | Port E                                    |

| 8000         | Mask Option Register              | Port E Direction                          |

| 0009         | Low Power Register (LPR)          | Low Power Register (LPR)                  |

| 000A         | External Interrupt Register (EIR) | External Interrupt Register (EIR)         |

| 000B         | Clear External Interrupt          | Clear External Interrupt                  |

| 000C         | PTG B Mode (PBM)                  | PTG B Mode (PBM)                          |

| 000D         | PBB                               | PBB                                       |

| 000E         | PBUL                              | PBUL, PBB to PBLL                         |

| 000F         | PBUL, Clear Flag                  | PBUL,PBB to PBLL, Download,<br>Clear Flag |

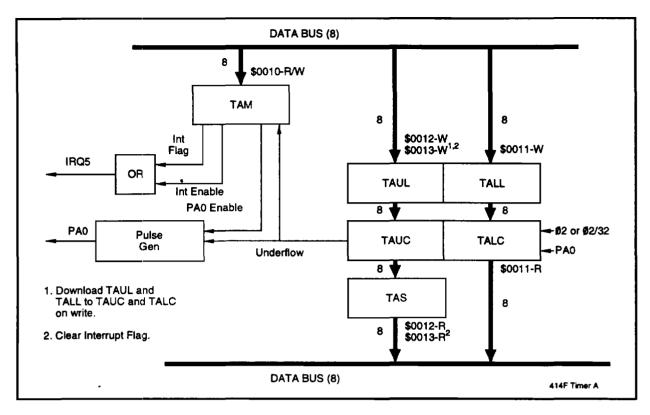

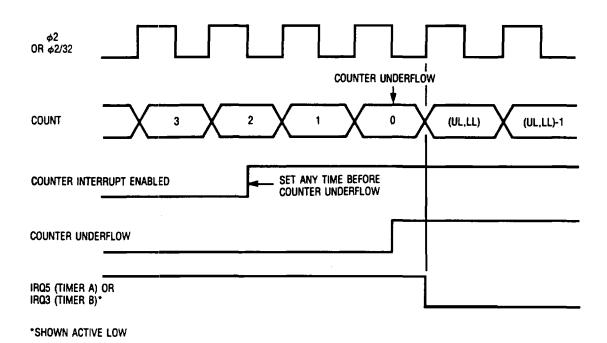

| 0010         | Timer A Mode (TAM)                | Timer A Mode (TAM)                        |

| 0011         | TALC, TAUC to TAS                 | TALL                                      |

| 0012         | TAS                               | TAUL                                      |

| 0013         | TAS, Clear Flag                   | TAUL, Download, Clear Flag                |

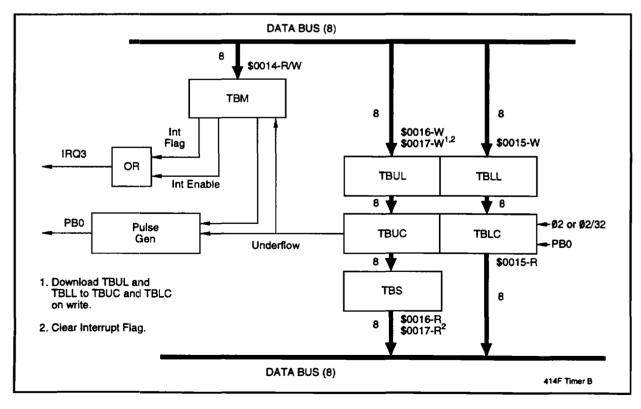

| 0014         | Tirner B Mode (TBM)               | Timer B Mode (TBM)                        |

| <b>0</b> 015 | TBLC, TBUC to TBS                 | TBLL                                      |

| 0016         | TBS                               | TBUL                                      |

| 0017         | TBS, Clear Flag                   | TBUL, Download, Clear Flag                |

| 0018         | Bank 0                            | Bank 0                                    |

| 0019         | Bank 1                            | Bank 1                                    |

| 001A         | Bank 2                            | Bank 2                                    |

| 001B         | Bank 3                            | Bank 3                                    |

| 001C         | Bank 4                            | Bank 4                                    |

| 001D         | Bank 5                            | Bank 5                                    |

| 001E         | Bank 6                            | Bank 6                                    |

| 001F         | Bank 7                            | Bank 7                                    |

Table 3-1b. Memory Map: 0020h-0032h

| _       | Host 16550A E                            | Emulation Mode                           | Host General Purpose Mode                |                                          |  |

|---------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|--|

| Address | Read                                     | Write                                    | Read                                     | Write                                    |  |

| 0020    | TX FIFO Buffer                           | RX FIFO Buffer                           | TX FIFO Buffer                           | RX FIFO Buffer                           |  |

| 0021    | Line Status Register (LSR)               | LSR1 Only                                | SP RAM 1                                 | SP RAM 1                                 |  |

| 0022    | Modern Status Register MSR)              | Modern Status Register (MSR)             | SP RAM 2                                 | SP RAM 2                                 |  |

| 0023    | Line Control Register (LCR)              | •                                        | SP RAM 3                                 | SP RAM 3                                 |  |

| 0024    | Modem Control Register (MCR)             | <del></del>                              | SP RAM 4                                 | SP RAM 4                                 |  |

| 0025    | FIFO Control Register (FCR)              | FIFO Control Register (FCR)              | SP RAM 5                                 | SP RAM 5                                 |  |

| 0026    | SP RAM 6                                 | SP RAM 6                                 | SP RAM 6                                 | SP RAM 6                                 |  |

| 0027    | SP RAM 7                                 | SP RAM 7                                 | SP RAM 7                                 | SP RAM 7                                 |  |

| 0028    | Divisor Latch LSB                        | Divisor Latch LSB                        | SP RAM 8                                 | SP RAM 8                                 |  |

| 0029    | Divisor Latch MSB                        | Divisor Latch MSB                        | SP RAM 9                                 | SP RAM 9                                 |  |

| 002A    | SP RAM A                                 | SP RAM A                                 | SP RAM A                                 | SP RAM A                                 |  |

| 002B    | SP RAM B                                 | SP RAM B                                 | SP RAM B                                 | SP RAM B                                 |  |

| 002C    | SP RAM C                                 | SP RAM C                                 | SP RAM C                                 | SP RAM C                                 |  |

| 002D    | SP RAM D                                 | SP RAM D                                 | SP RAM D                                 | SP RAM D                                 |  |

| 002E    | GP DP FIFO Status (GPFS)                 | GPFS3 Only                               | GP FIFO Status (GPFS)                    | •                                        |  |

| 002F    | Host Handshake Register (HHR)            | Host Handshake Register (HHR)            | Host Handshake Register (HHR)            | Host Handshake Register<br>(HHR)         |  |

| 0030    | FIFO Status Register (FSR)               |  |

| 0031    | FIFO Interrupt Enable<br>Register (FIER) |  |

| 0032    | Host Control Register (HCR)              |  |

Table 3-1c. Memory Map: 0033h-003Fh

| Address | Read                                | Write                                     |

|---------|-------------------------------------|-------------------------------------------|

| 0033    | Chip Select Fast/Slow               | Chip Select Fast/Slow                     |

| 0034    | PTG A Mode (PAM)                    | PTG A Mode (PAM)                          |

| 0035    | PAB                                 | PAB                                       |

| 0036    | PAUL                                | PAUL, PAB to PALL                         |

| 0037    | PAUL, Clear Flag                    | PAUL,PAB to PALL, Download, Clear<br>Flag |

| 0038    | Serial In Buffer (SIB)              | Serial Out Buffer (SOB)                   |

| 0039    | Serial Interrupt Enable (SIR)       | Serial Interrupt Enable (SIR)             |

| 003A    | Serial Mode Register (SMR)          | Serial Mode Register (SMR)                |

| 003B    | Serial Line Control Register (SLCR) | Serial Line Control Register (SLCR)       |

| 003C    | Serial Status Register (SSR)        | Serial Status Register (SSR)              |

| 003D    | Serial Form Register (SFR)          | Serial Form Register (SFR)                |

| 003E    |                                     | SOUT (RXD) Divider Latch (SODL)           |

| 003F    |                                     | SIN (TXD) Divider Latch (SIDL)            |

Table 3-1d. Memory Map: 0040h-07FFh (C40)

| Address      | Read                              | Write                               |  |  |  |  |  |  |  |

|--------------|-----------------------------------|-------------------------------------|--|--|--|--|--|--|--|

| 0040<br>00FF | Page 0 RAM (192 bytes)            |                                     |  |  |  |  |  |  |  |

| 0100<br>01FF | Page 1 RAM (256 bytes)            |                                     |  |  |  |  |  |  |  |

| 0200<br>02FF | Page 2 RAM                        | / (256 bytes)                       |  |  |  |  |  |  |  |

| 0300<br>03FF | Page 3 RAN                        | / (256 bytes)                       |  |  |  |  |  |  |  |

| 0400<br>043F | Page 4 RAI                        | Page 4 RAM (64 bytes)               |  |  |  |  |  |  |  |

| 0440<br>04FF | Page 4 Not Ava                    | ilable (192 bytes)                  |  |  |  |  |  |  |  |

| 0500<br>05FD | Page 5 Not Ava                    | ilable (254 bytes)                  |  |  |  |  |  |  |  |

| 05FE         | CRC-L                             | CRC INPUT BUFFER                    |  |  |  |  |  |  |  |

| 05FF         | CRC-H                             | INITIALIZE CRC                      |  |  |  |  |  |  |  |

| 0600<br>07FF | ES4 Active (PBS1 = 0) (512 bytes) | ES4 Inactive (PBS1 = 1) (512 bytes) |  |  |  |  |  |  |  |

| 0800<br>1FFF | Bank Select 0 (6K PBS             | :1 = 0 or 6.5K PBS1 = 1)            |  |  |  |  |  |  |  |

Table 3-1e. Memory Map: 0040h-07FFh (L39)

| Address      | Read                              | Write                               |

|--------------|-----------------------------------|-------------------------------------|

| 0040<br>00FF | Page 0 RAN                        | / (192 bytes)                       |

| 0100         | Page 1 RAN                        | A (256 bytes)                       |

| OTEF         |                                   |                                     |

| 0200         |                                   |                                     |

| 02FF         | Page 2 RAN                        | A (256 bytes)                       |

| 0300         |                                   |                                     |

| 03FF         | Page 3 HAN                        | A (256 bytes)                       |

| 0400         |                                   |                                     |

| 04FF         | Page 4 HAN                        | A (256 bytes)                       |

| 0500         |                                   |                                     |

| 05FD         | Page 5 HAM                        | / (254 bytes)                       |

| 05FE         | CRC-L                             | CRC INPUT BUFFER                    |

| 05FF         | CRC-H                             | INITIALIZE CRC                      |

| 0600         |                                   |                                     |

| 07FF         | ES4 Active (PBS1 = 0) (512 bytes) | ES4 Inactive (PBS1 = 1) (512 bytes) |

| 0800         |                                   |                                     |

| 1FFF         | Bank Select 0 (6K PBS             | 31 = 0 or 6.5K PBS1 = 1)            |

# 3.1.3. VO Register Bit Assignments

The individual I/O signal and data bits are identified in Table 3-2.

Table 3-2a. Register Bit Assignments: 0000h - 0017h

|       |                                                   | Bit                                  |                                      |                                      |                                                 |                                        |                                        |                                    |                                    |  |

|-------|---------------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------------|----------------------------------------|----------------------------------------|------------------------------------|------------------------------------|--|

| Addr. | Function                                          | 7                                    | 6                                    | 5                                    | 4                                               | 3                                      | 2                                      | 1                                  | 0                                  |  |

| 0000  | Port A Data (0-7; I/O)                            | PA7                                  | PA6                                  | PA5                                  | PA4                                             | PA3                                    | PA2                                    | PA1                                | PA0                                |  |

| 0001  | Port B Data (0-7; Output Only)                    | PB7                                  | PB6                                  | PB5                                  | PB4                                             | PB3                                    | PB2                                    | PB1                                | PB0                                |  |

| 0002  | Port C Data (0-7; I/O)                            | PC7                                  | PC6                                  | PC5                                  | PC4                                             | PC3                                    | PC2                                    | PC1                                | PC0                                |  |

| 0003  | Port D Data (0-3; I/O),<br>Port D Direction (4-7) | PDD3                                 | PDD2                                 | PDD1                                 | PDD0                                            | PD3                                    | PD2                                    | PD1                                | PD0                                |  |

| 0004  | Port C Direction (0-7)                            | PAD7                                 | PAD6                                 | PAD5                                 | PAD4                                            | PAD3                                   | PAD2                                   | PAD1                               | PAD0                               |  |

| 0005  | Port B Select (0-7)                               | PBS7                                 | PBS6                                 | PBS5                                 | PBS4                                            | PBS3                                   | PBS2                                   | PBS1                               | PBS0                               |  |

| 0006  | Port C Direction (0-7)                            | PCD7                                 | PCD6                                 | PCD5                                 | PCD4                                            | PCD3                                   | PCD2                                   | PCD1                               | PCD0                               |  |

| 0007  | Port E Data (0-7)                                 | PE7                                  | PE6                                  | PE5                                  | PE4                                             | PE3                                    | PE2                                    | PE1                                | PE0                                |  |

| 0008  | Mask Option Register (MSR)                        | Mask<br>Option<br>Bit 7<br>(MOR7)    | Mask<br>Option<br>Bit 6<br>(MOR6)    | Mask<br>Option<br>Bit 5<br>(MOR5)    | Mask<br>Option<br>Bit 4<br>(MOR4)               | Mask<br>Option<br>Bit 3<br>(MOR3)      | Mask<br>Option<br>Bit 2<br>(MOR2)      | Mask<br>Option<br>Bit 1<br>(MOR1)  | Mask<br>Option<br>Bit 0<br>(MOR 0) |  |

| 0009  | Low Power Register<br>(LPR)                       | Low<br>Power<br>Mode<br>Enable       | Low<br>Power<br>Mode                 | Wake up<br>Enable<br>PA0<br>(Ring)   | Wake up<br>Enable<br>PD4 (Wrt)<br>&<br>PD5 (CS) | Wake up<br>Enable<br>PA2<br>(TXD)      | Wake up<br>Enable<br>PD4<br>(DTR)      | Wake up<br>Enable<br>PD5<br>(AL)   | Not Used                           |  |

| 000A  | External Interrupt Register<br>(EIR)              | External<br>Interrupt<br>Flag<br>PA1 | External<br>Interrupt<br>Flag<br>PA4 | External<br>Interrupt<br>Flag<br>PD7 | External<br>Interrupt<br>Enable<br>PA1          | External<br>Interrupt<br>Enable<br>PA4 | External<br>Interrupt<br>Enable<br>PD7 | Edge<br>Detect<br>Polarity<br>PA4  | Edge<br>Detect<br>Polarity<br>PD7  |  |