## Microelectronics Divisions Rockwell International

Marketing Services

P.O. Box 3669 3430 Miraloma Avenue Anaheim, California 92803 (714) 632-3729 Telex Via TWX 910-591-1179 January 10, 1975

In response to your request, we are pleased to enclose information on our family of PPS Microprocessor devices. We are presently de-

livering large production quantities of PPS-4 devices.

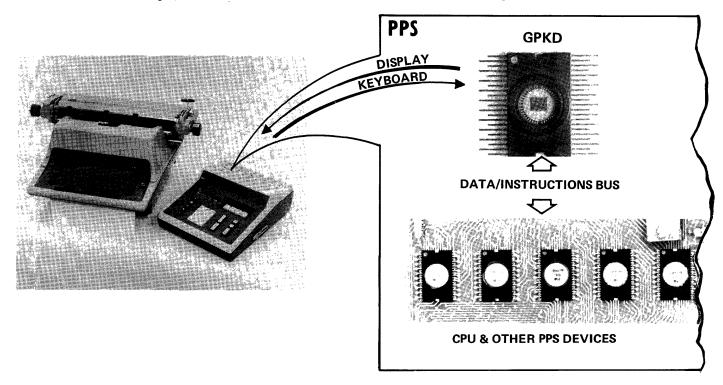

Our Microprocessor system is unique in that we have several standard I/O devices (General Purpose I/O, General Purpose Keyboard and Display, Printer Controller and 1200 bps Modem), which interface directly between the internal bus structure and various peripherals without additional circuits.

If your application is presently in the development stage, you may find one or more of our Evaluation and Development modules useful. These popular prototyping "tools" are described in the enclosed document, No. 29003N11. The modules are moderately priced and can be furnished 30 days after receipt of your order.

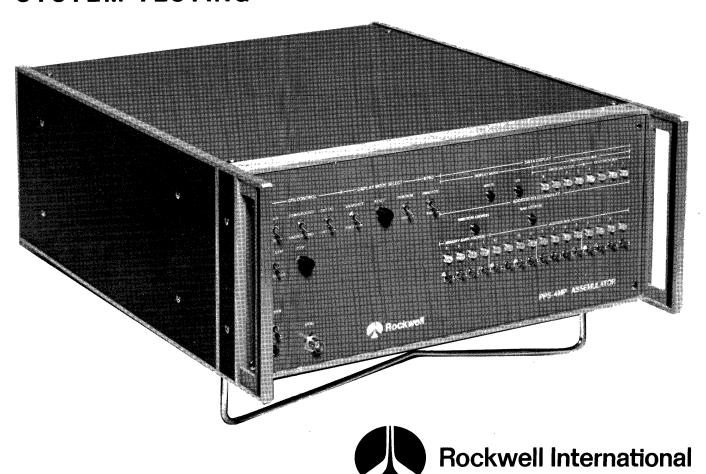

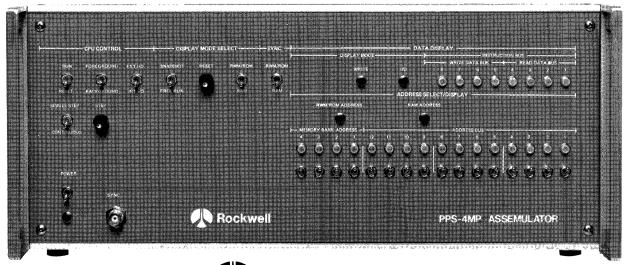

An alternate prototyping approach, which you may prefer, would be to purchase a PPS-4MP Assemulator described in the enclosed literature. Because of a special arrangement with the supplier, the price has been reduced to \$2,495, if purchased directly from Rockwell. Delivery is 60 days after receipt of order. Assemulator options are also available at nominal costs.

Start today by sending your purchase order to the above address.

Very truly yours,

Ronald F. Voigt

Director

Customer Services

Enclosure

#### SAMPLE PRICES

#### PPS MICROPROCESSOR CIRCUITS

#### FOR MICROCOMPUTERS

|               | Part Number                           |           | Prices Each |

|---------------|---------------------------------------|-----------|-------------|

|               | Quantities:                           | 1-24 *    |             |

| 10660         | CPU                                   |           | \$ 92       |

| 10432         | RAM $(256 \times 4)$                  |           | \$ 70       |

| <b>107</b> 06 | CLOCK                                 |           | \$ 29       |

| 10788         | KEYBOARD/DISPLAY I/O                  | 8 g - 3 % | \$ 95       |

| 10789         | PRINTER CONTROLLER I/O                |           | \$ 90       |

| 10696         | GP I/O                                | e, tell   | \$ 41       |

| 10371         | 1200 BPS MODEM - UART (TDI)           |           | \$180       |

| 10738         | BUS INTERFACE                         |           | \$ 45       |

| A05           | ROM (1K x 8)                          | *         | \$ 22 **    |

| A52           | ROM 2K (2K x 8)                       |           | \$ 23.50 ** |

| A08           | $ROM/RAM (704 \times 8/116 \times 4)$ | * · •     | \$ 22.**    |

| A07           | ROM/RAM (1K x 8/116 x 4)              | *         | \$ 23.50 ** |

#### PROTOTYPING HARDWARE

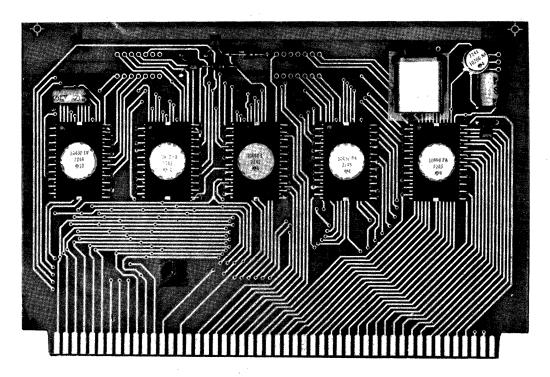

| PPS EVALUATION BOARD (Includes CPU, 2 RAM, 2 I/O, Clock), PN 20102 D02 | \$500 Each<br>(\$550 outside U.S.A.) |

|------------------------------------------------------------------------|--------------------------------------|

| PPS INTERFACE KITS (Includes 2 bus interface devices, PN 10738)        | :                                    |

| 1. TTL Bus Interface Module, PN 20102 D27                              | \$140 Each                           |

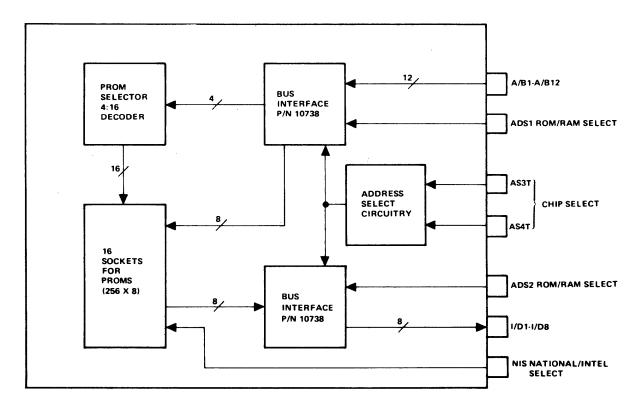

| 2. SOS/ROM Interface Module, PN 20102 D30                              | \$175 Each                           |

| 3. PROM Interface Module, PN 20102 D33                                 | \$180 Each                           |

| GP I/O MODULE, PN 20102 D36                                            | \$375 Each                           |

| RAM ASSEMBLY BOARD (INCLUDES 8 RAMs, PN 10432), PN 20102 D17           | \$600 Each                           |

| ROM ASSEMBLY BOARD (ROMs NOT INCLUDED), PN 20102 D19                   | \$ 45 Each                           |

All prices f.o.b. Anaheim, California.

Prices and specifications subject to change without notice. 1 Sept. 1974

<sup>\*</sup>Higher quantities - quote.

\*\*Available only in minimum quantities of 1,000 as part of a PPS set.

## DATA SHEET

# PARALLEL PROCESSING SYSTEM (PPS-4) MICROCOMPUTER

A 4-BIT DATA WORD/8-BIT INSTRUCTION WORD MICROCOMPUTER

#### **PPS-4 BASIC DEVICES:**

| CENTRAL PROCESSOR (CPU)                  |  | P/N 10660 |

|------------------------------------------|--|-----------|

| RANDOM ACCESS MEMORY (RAM)               |  | P/N 10432 |

| READ ONLY MEMORY (ROM)                   |  | P/N A05   |

| READ ONLY MEMORY (ROM)                   |  | P/N A52   |

| READ ONLY/RANDOM ACCESS MEMORY (ROM/RAM) |  | P/N A07   |

| READ ONLY/RANDOM ACCESS MEMORY (ROM/RAM) |  | P/N A08   |

| GENERAL PURPOSE INPUT/OUTPUT (GPI/O)     |  | P/N 10696 |

| CLOCK                                    |  | P/N 10706 |

#### **CONTENTS**

| ntroduction                                                   |       |               |      |     |    |   | • | 1  |

|---------------------------------------------------------------|-------|---------------|------|-----|----|---|---|----|

| Description                                                   |       |               |      |     |    |   |   | 3  |

| Description—Central Processing Unit (CPU),                    | P/ľ   | V 10          | 660  |     |    |   |   | 4  |

| Description—Random Access Memory (RAM                         | 1), I | P/N           | 104  | 32  |    |   |   | 6  |

| Description—Read Only Memory (ROM), P/I                       | N A   | ٠05           |      |     |    |   |   | 7  |

| Description—Read Only Memory (ROM), P/I                       | N A   | \ <b>52</b> - |      |     |    |   |   | 8  |

| Description—Read Only Memory/Random A<br>(ROM/RAM), P/N A07—— | CCE   | ess N         | /lem | ory |    |   |   | 8  |

| Description—Read Only Memory/Random A<br>(ROM/RAM), P/N A08—— |       | ess N         | /lem | ory |    | • |   | 9  |

| Description—General Purpose Input/Output                      | (1/0  | 0), 1         | P/N  | 106 | 96 |   |   | 10 |

| Description—Clock Generator, P/N 10706                        |       |               |      |     |    |   |   | 11 |

| Special Interface Consideration                               |       |               |      |     |    |   |   | 12 |

| Basic System Operation                                        |       |               |      |     |    |   |   | 14 |

| Instruction List                                              |       |               |      |     |    |   |   | 16 |

| Electrical Specifications                                     |       |               |      |     |    |   |   | 22 |

| DC and Operating Characteristics                              |       |               |      |     |    |   |   | 23 |

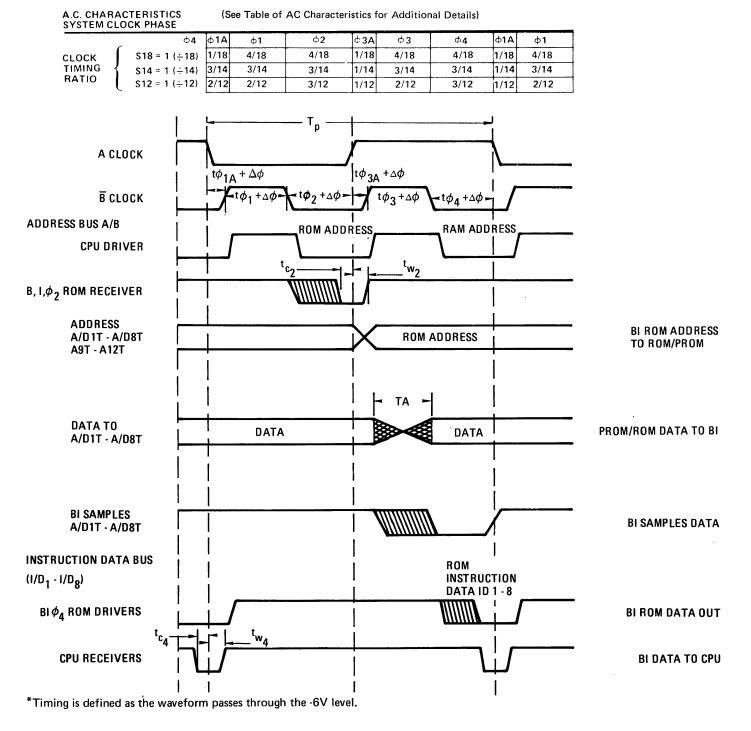

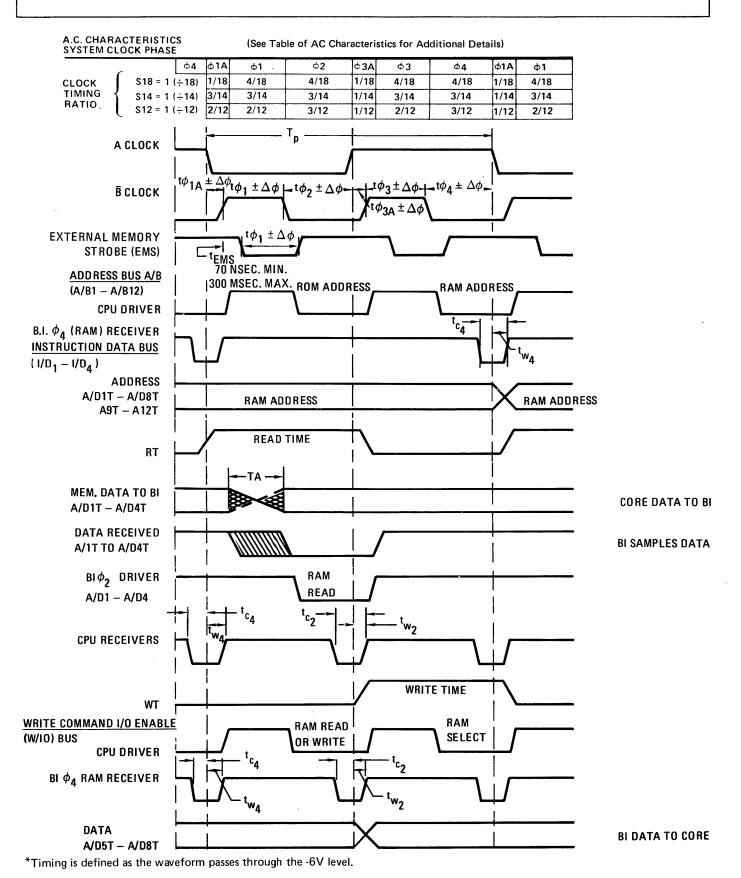

| System Input and Output Timing                                |       |               |      |     |    |   |   | 24 |

| Timing Diagram *                                              |       |               |      |     |    |   |   | 25 |

| Customers Support – General                                   |       |               |      |     |    |   |   | 26 |

| Customers Support — Software                                  |       |               |      |     |    |   |   | 26 |

| Customers Support — PPS-4 Documentation                       |       |               |      |     |    |   |   | 27 |

| Customers Support – Hardware                                  |       |               |      |     |    |   |   | 27 |

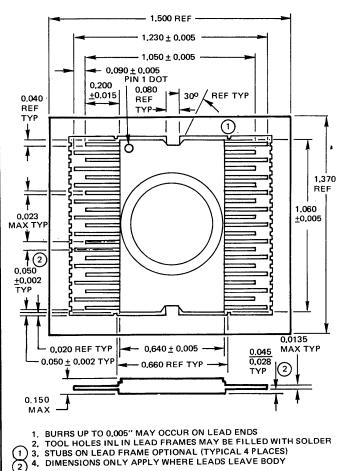

| Standard Packages                                             |       |               |      | •   |    |   |   | 30 |

|                                                               |       |               |      |     |    |   |   |    |

#### NOTICE

Information provided in this Data Sheet is for reference purposes only and is subject to change without notice.

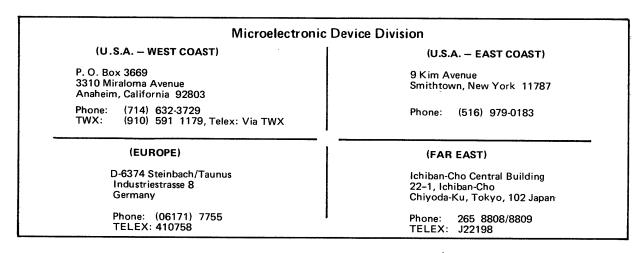

For specific detail information on this device or any of our other advanced microelectronic devices please contact the nearest Rockwell International Microelectronic Device Division Office.

#### Microelectronic Device Division

ROCKWELL INTERNATIONAL

c/o ROCKWELL INTERNATIONAL OVERSEAS CORPORATION

#### EUROPE

Rockwell International GmbH D-6374 Steinbach/Taunus Industriestrasse 8 Germany Phone (06171) 7755 Rockwell International Overseas Corp. Ichiban-Cho Central Building 22-1, Ichiban-Cho Chiyoda-Ku, Tokyo, 102 Japan Phone 265 8808 8809

**JAPAN**

U.S.A.

P.O. BOX 3669

3310 Miraloma Ave.

Anaheim, California 92803

714 632-3729

TWX (910) 591-1179, Telex: Via TWX

#### INTRODUCTION

#### **SCOPE**

This data sheet describes the basic circuits of the Rockwell 4-bit word Parallel Processing System (PPS-4) microcomputer. These basic circuits, and associated special purpose input/output circuits and memory devices are listed in Table I. This data sheet also describes system characteristics, timing and interface requirements, and the design software and hardware aids offered by Rockwell.

#### **GENERAL**

The PPS-4 system is a set of modular MOS/LSI circuits which provides equipment designers with a low cost means of developing a range of versatile, powerful, custom programmed microcomputer systems.

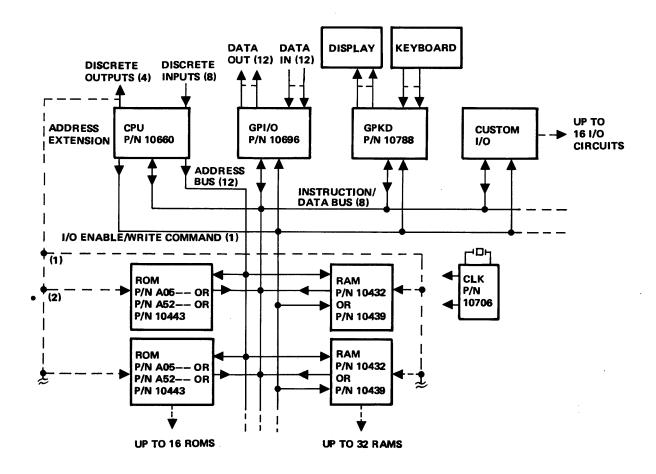

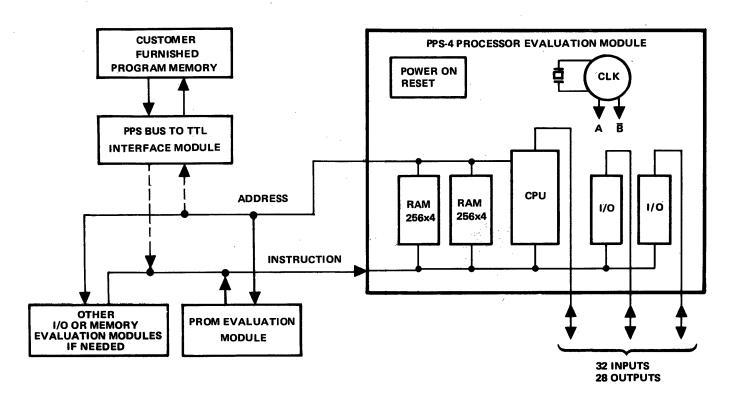

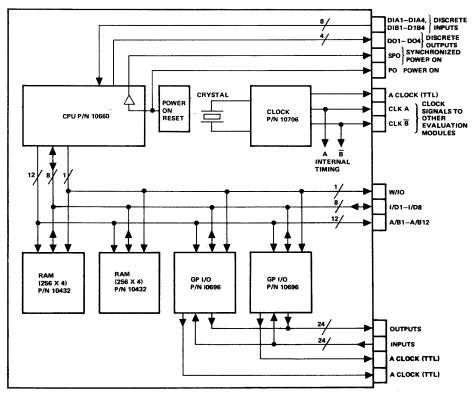

A minimum PPS-4 system can be made from only two MOS/LSI circuits and a clock circuit. The modular design of the PPS-4 circuits allows designers to create very powerful systems by simply adding additional Rockwell memory and/or I/O circuits. The typical system shown in Figure 1 delineates these expansion parameters. The many different types of available I/O and memory circuits enhances the economics and versatility of the PPS-4.

The PPS-4 has a high throughput and fast execution speed which enables the PPS-4 to economically implement many functions normally thought to require 8-bit or larger processors. High throughput is demonstrated by the PPS-4 strobing and transferring data from the I/O to RAM at a rate of 36  $\mu$ sec per 8-bit byte, and fast execution is demonstrated by the addition of two 8-bit decimal numbers in 240  $\mu$ sec.

Other design advantages include simpler programming with less program steps, quicker turn-around in system prototyping, the use of fewer components to implement systems, and the capability of Rockwell to design and produce custom I/O devices to suit a user's unique requirements.

#### **FEATURES**

#### **Functional Power:**

- 50 Instructions, which include-

- Arithmetic and Logic Operations

- Conditional and Unconditional Transfers

- Direct and Indirect Subroutine Calls

- Direct and Indirect RAM Addressing

- Input/Output Commands

- 4-bit data words/8-bit instruction words

- Hardware/software subroutine stacking unlimited nesting.

- Implementable Interrupt

#### Performance Power:

- 21-line parallel bus structure.

- Fast execution time adds two 8-digit decimal numbers in 240 μsec.

- High throughout parallel data transfer RAM to I/O or I/O to RAM:

- 4-bit byte/28 μsec

- 8-bit byte/36 μsec

- 12-bit byte/56  $\mu$ sec

- Decimal and binary arithmetic modes.

- Directly addressable up to 16 1Kx8 ROMs or 16 2Kx8 ROMs, and 32 256x4 RAMs (294,912-bit memory capacity).

- Directly addresses up to 16 I/O circuits.

- Advanced MOS/LSI Non-Volatile RAM and Electrically Alterable ROM circuits.

#### Design/Production Economics:

- No external interface circuitry required between CPU, memories, and I/O circuits.

- Eight LSI interface/control circuits including a direct bus-to-TTL memory circuit, direct Keyboard and Display control circuit, and a MODEM/UART circuit on a single chip.

- Custom designed I/O devices for special applications.

- All I/O circuits are TTL compatible

- Single power supply

- ROM/RAM (one chip) for production of two chip (plus clock) minimum systems.

- Four-phase dynamic operation for low power and high speed

- No memory refresh circuitry required

- Complete software and hardware development support

#### **INTRODUCTION (CONT)**

Table 1. PPS Circuit Devices

| Devices                                                              | Function                                                                                                                                                                                                     | Availability    |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BASIC DEVICES                                                        |                                                                                                                                                                                                              |                 |

| Central Processor Unit (CPU),<br>P/N 10660                           | Provides the arithmetic and control circuitry. Functions as 4-bit parallel data processor, and when combined with other devices forms the control center of the PPS-4 microcomputer.                         | Now             |

| Clock Generator, P/N 10706                                           | Generates the basic 4-phase clock signals A and $\overline{B}$ .                                                                                                                                             | Now             |

| General Purpose Input/Output,<br>P/N 10696 (GPI/O)                   | Connects the PPS-4 instruction data bus lines to external MOS or TTL circuits. Provides 12 discrete inputs and 12 discrete static outputs.                                                                   | Now             |

| 1K Read Only Memory<br>(ROM), P/N A05——                              | Stores the custom programs. Provides 8192 bits in an 8 x 1024 bit configuration.                                                                                                                             | Now             |

| 2K Read Only Memory<br>(ROM), P/N A52——                              | Functionally the same as the 1K ROM, but provides twice the storage capacity on a single chip, (16,384 bits).                                                                                                | Now             |

| Random Access Memory<br>(RAM), P/N 10432                             | General working and memory register for data storage. Provides 1024 bits in a 4 x 256 configuration.                                                                                                         | Now             |

| ROM/RAM, P/N A08——                                                   | Provides both the ROM and the RAM function on one chip for systems requiring limited memory with minimum cost $(704 \times 8/76 \times 4)$ .                                                                 | Now             |

| ROM/RAM, P/N A07                                                     | Same function as the A08—— except the A07—— offers more memory (1024 x 8/116 x 4).                                                                                                                           | Now             |

| OTHER MEMORY DEVICES                                                 | ,                                                                                                                                                                                                            |                 |

| Electrically Programmable ROM (EPAROM), P/N 10443                    | Provides block-eraseable, non-volatile program storage for 256<br>8-bit words.                                                                                                                               | 1st Qtr<br>1975 |

| Non-Volatile RAM<br>(NV RAM), P/N 10439                              | Provides word-eraseable, non-volatile data storage for 256<br>4-bit words.                                                                                                                                   | 1st Qtr<br>1975 |

| SPECIAL PURPOSE INPUT/OUTPUT DEVICES                                 |                                                                                                                                                                                                              |                 |

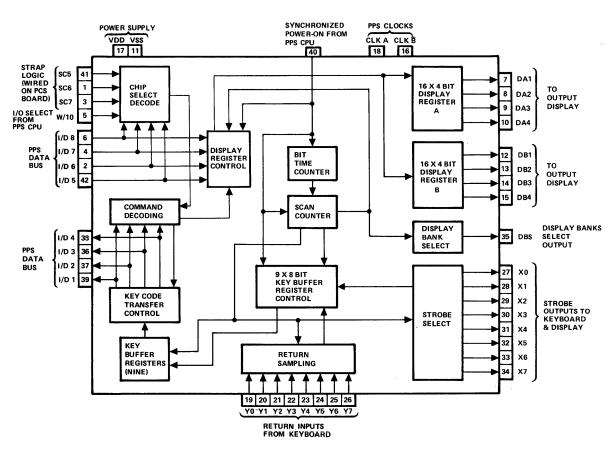

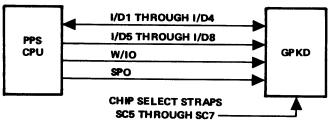

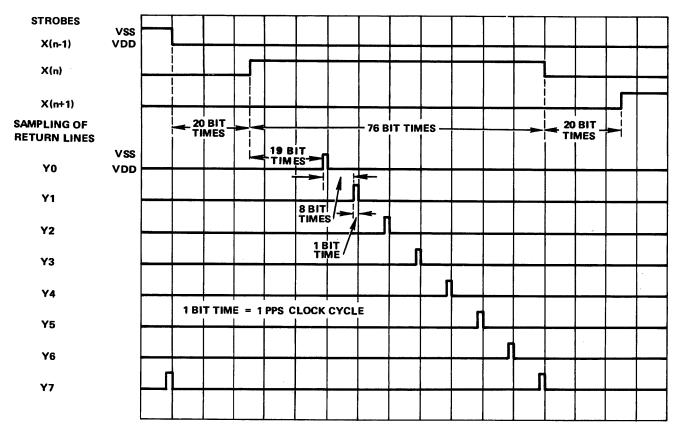

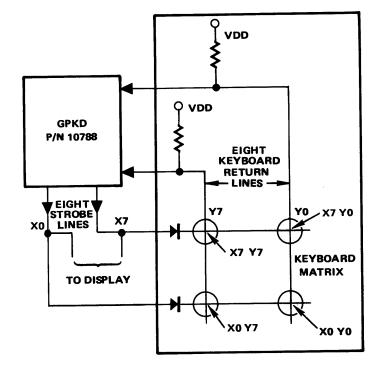

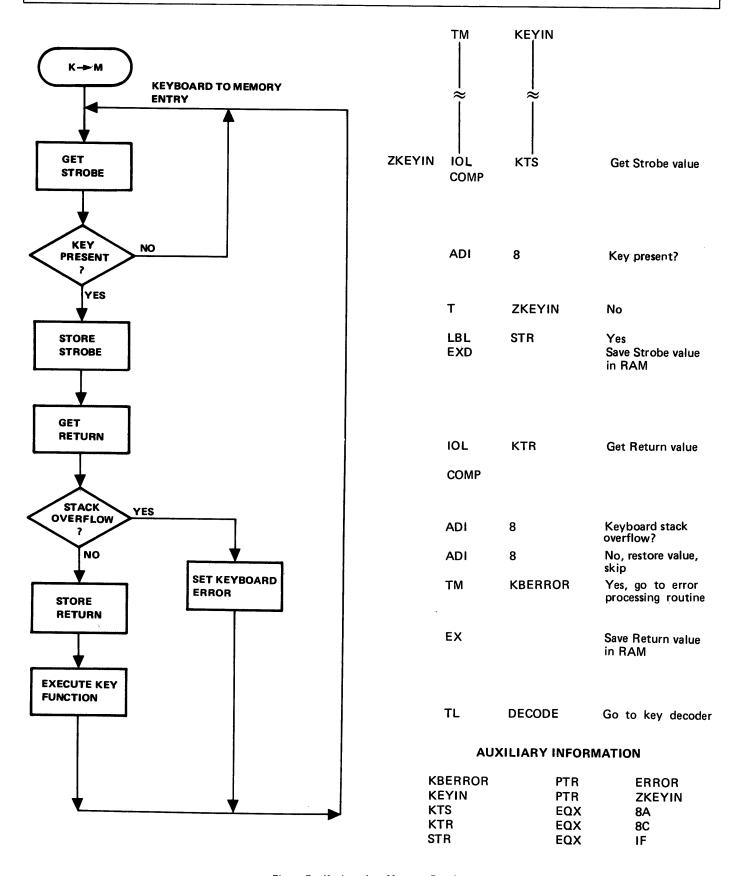

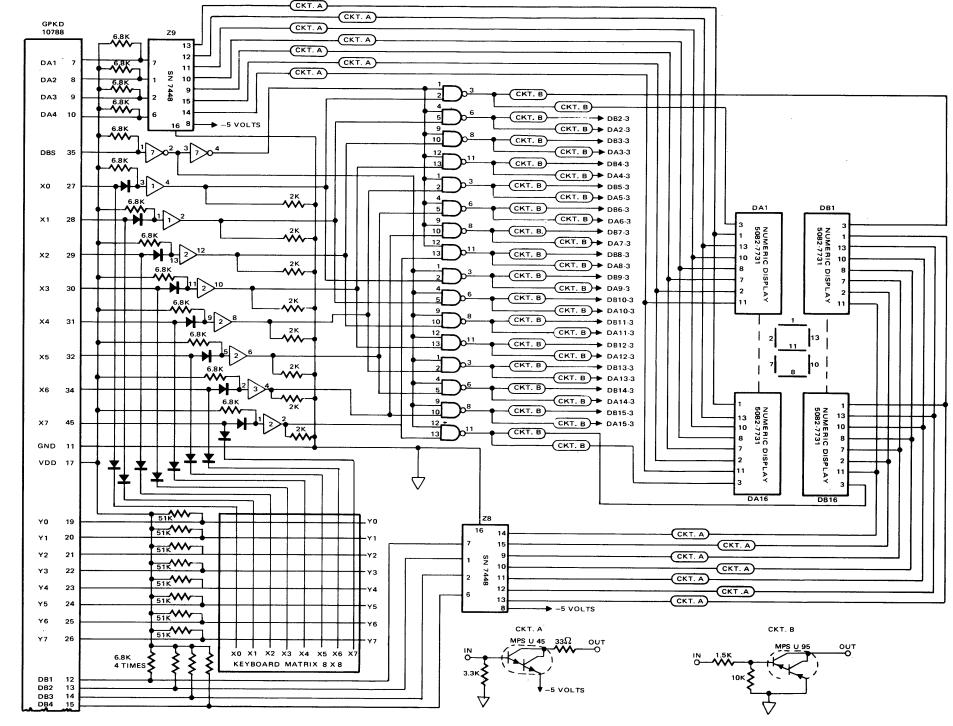

| General Purpose Keyboard and<br>Display Control, (GPKD)<br>P/N 10788 | Provides 64 key strobing, key debounce, 2 key rollover protection, 9 key buffering, and two 16 4-bit character display buffers with automatic refresh.                                                       | Now             |

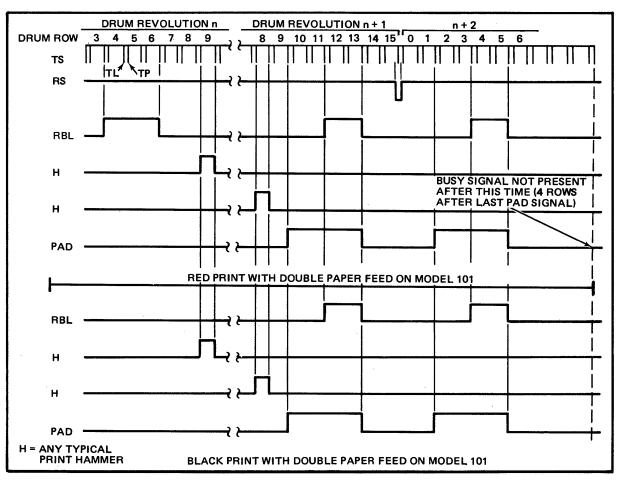

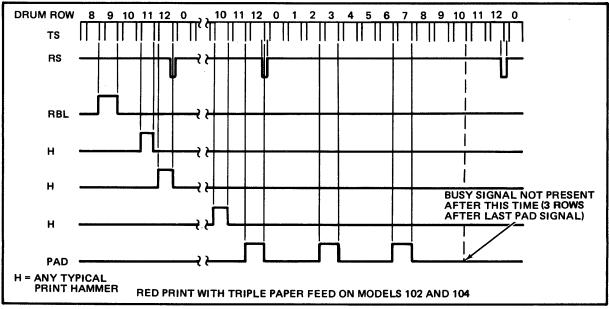

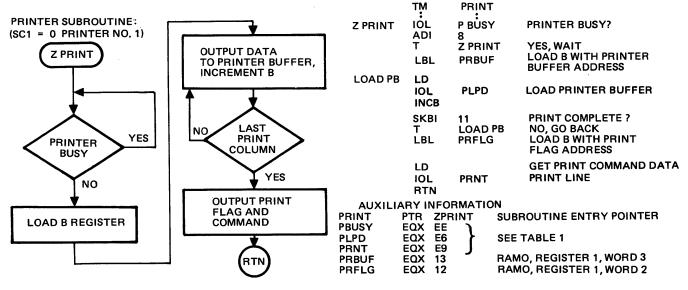

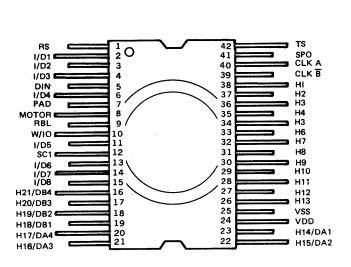

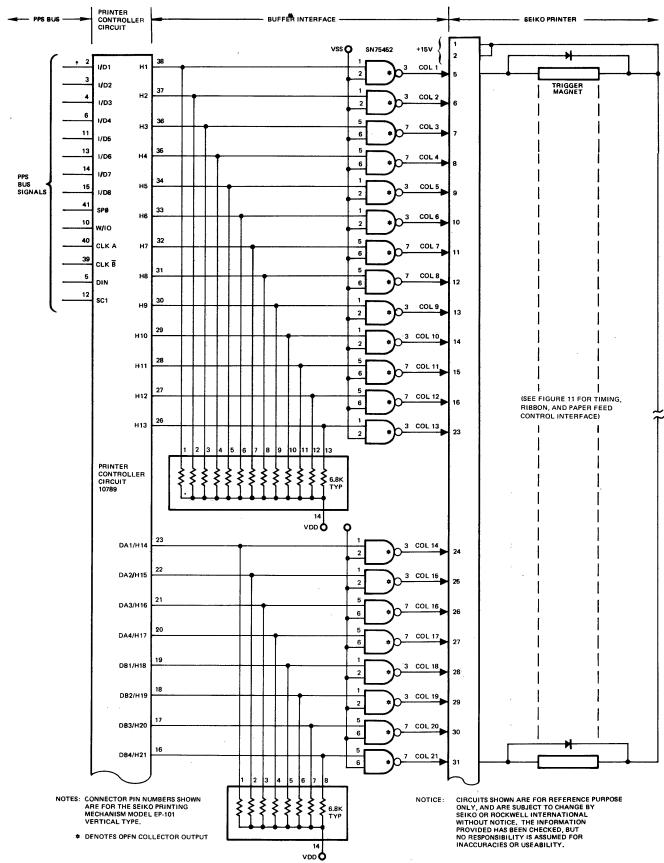

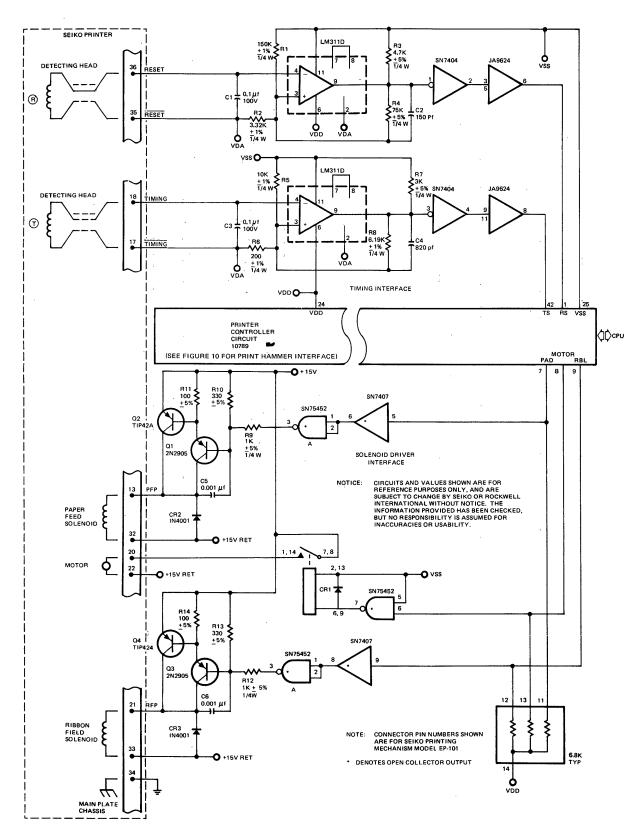

| Printer Controller, (PC),<br>P/N 10789                               | Provides 21 4-bit character print buffer and automatic control and timing for the Seiko 101, 102, and 104 printers.                                                                                          | Now             |

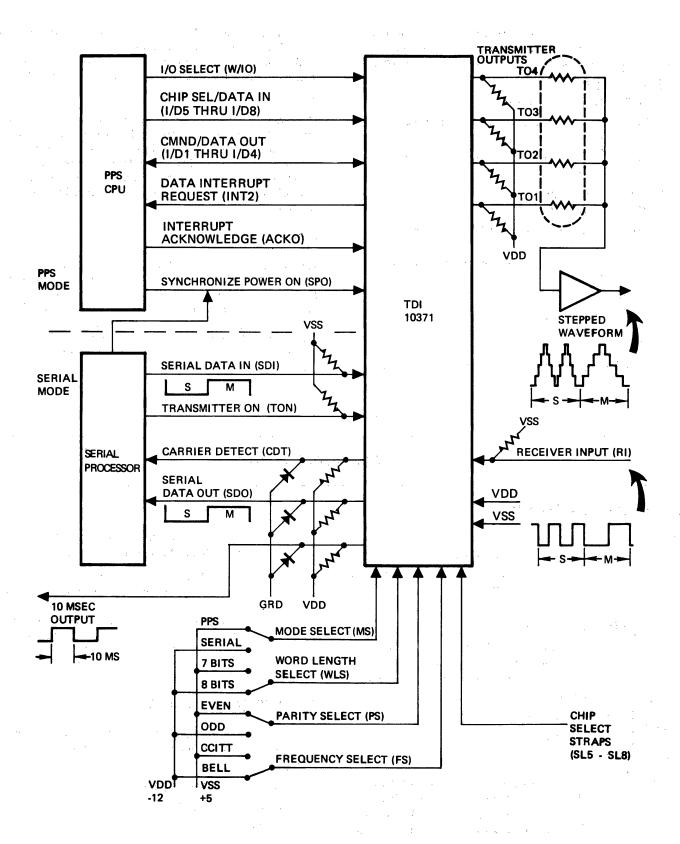

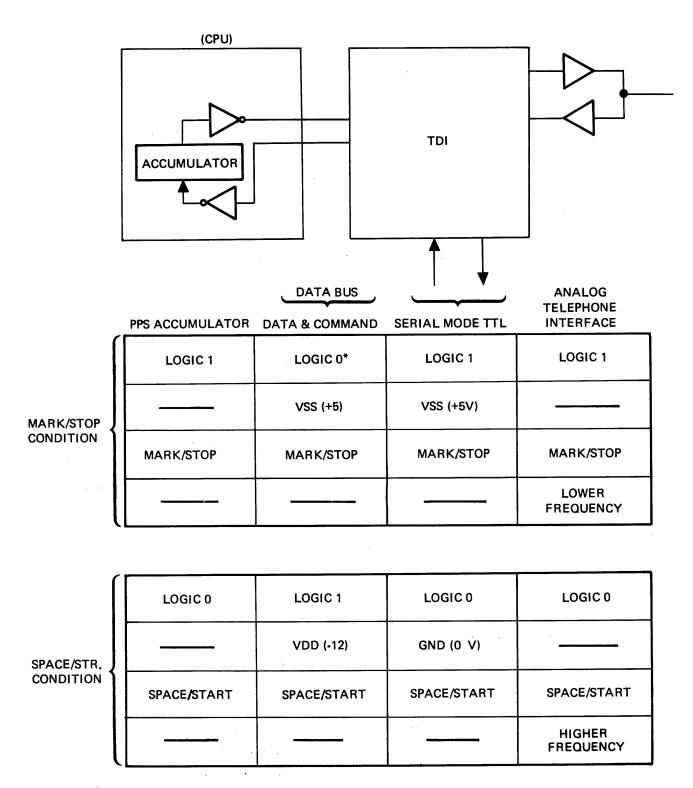

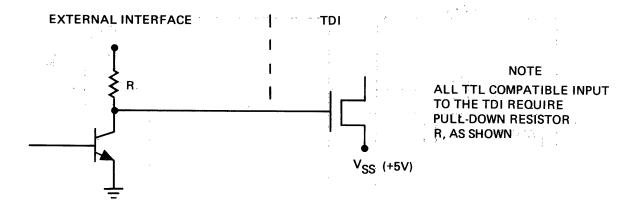

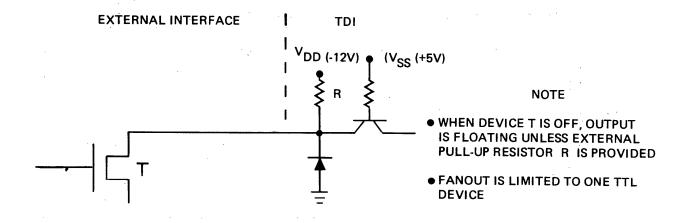

| Telecommunications Data<br>Interface, (TDI),<br>P/N 10371            | 1200 BPS data transmission. Full duplex operation including two<br>8-bit transmit buffers and two 8-bit receive buffers for complete UART<br>functions. Compatible with either the Bell 202 or CCITT systems | Now             |

| Keyboard/Printer Controller,<br>(KPC), P/N 10815                     | Provides complete control of the Seiko 320 printer and the capability of reading a 64-key keyboard.                                                                                                          | 4th Qtr<br>1974 |

| Display Controller, (DC)<br>P/N 10814                                | Provides control of a 16 digit display. Uses internal buffer, decode logic and output strobes.                                                                                                               | 4th Qtr<br>1974 |

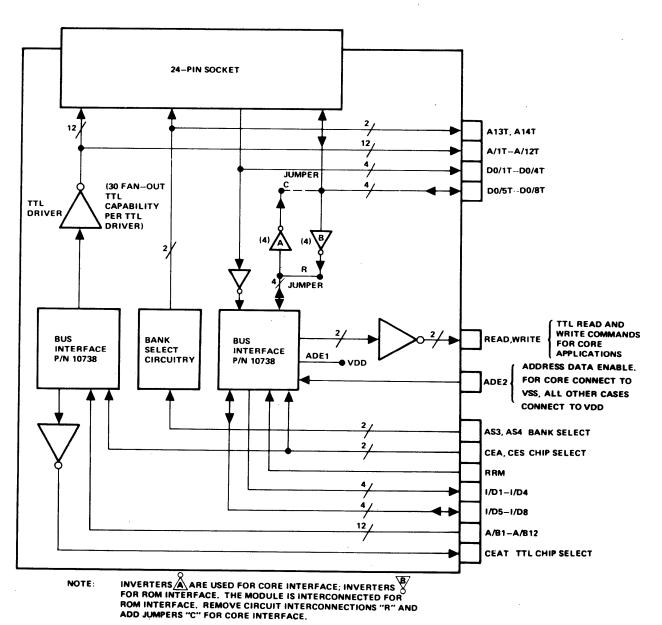

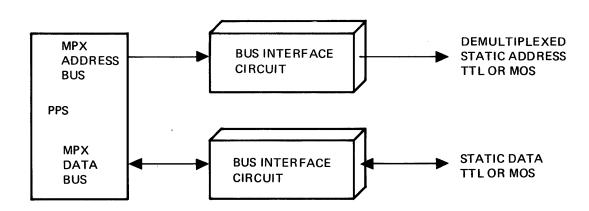

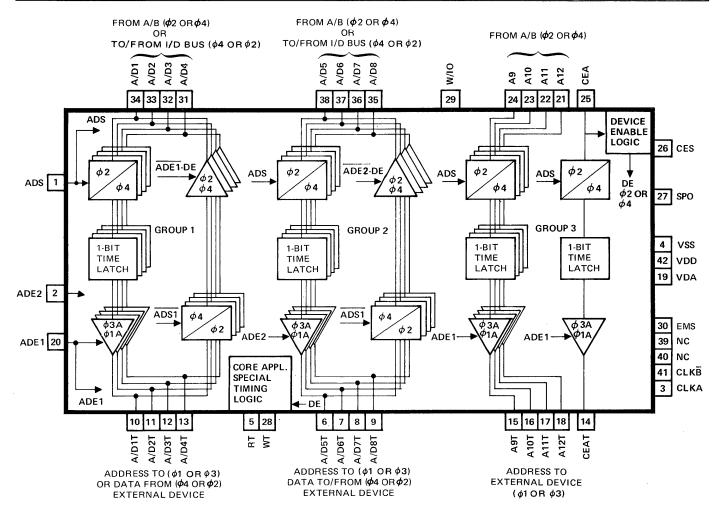

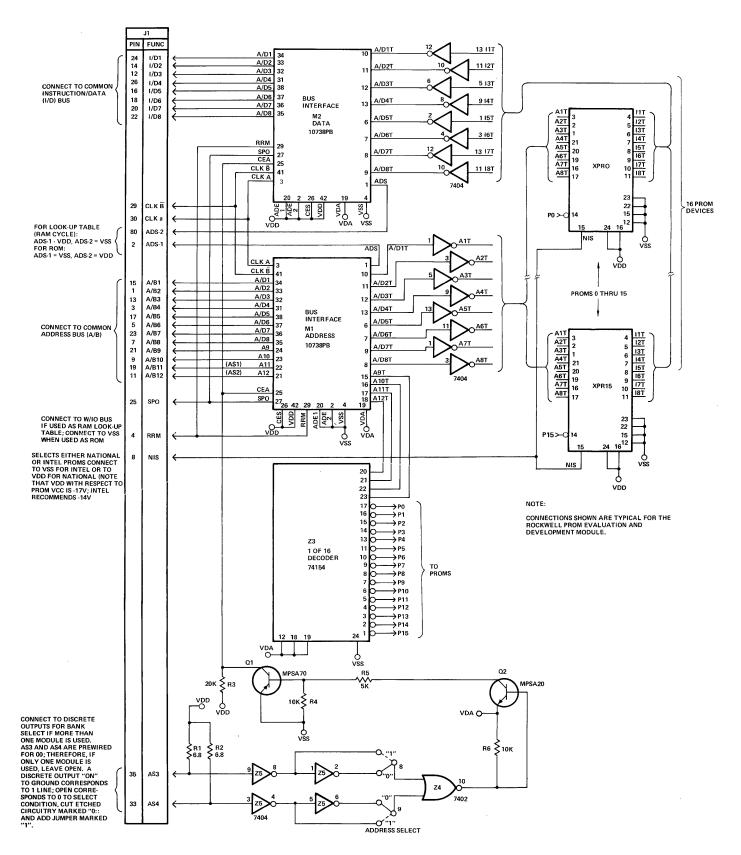

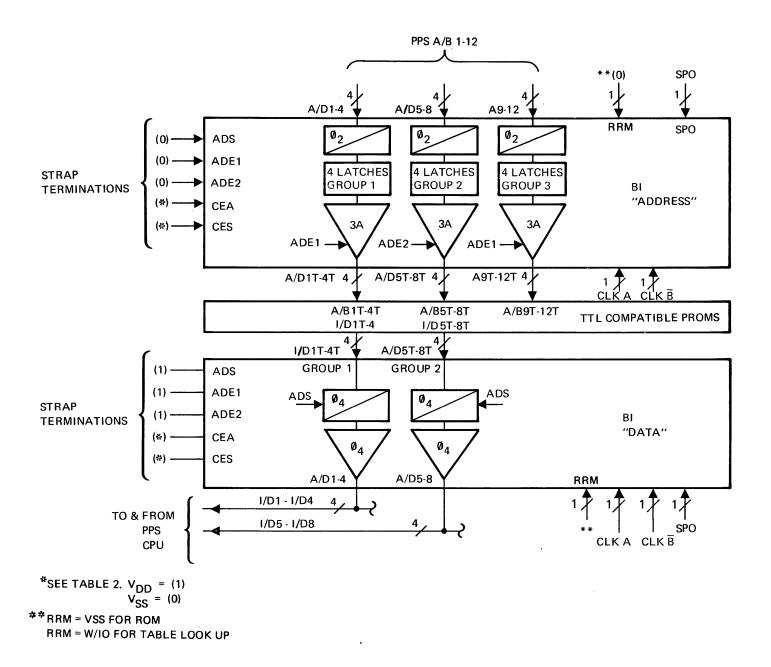

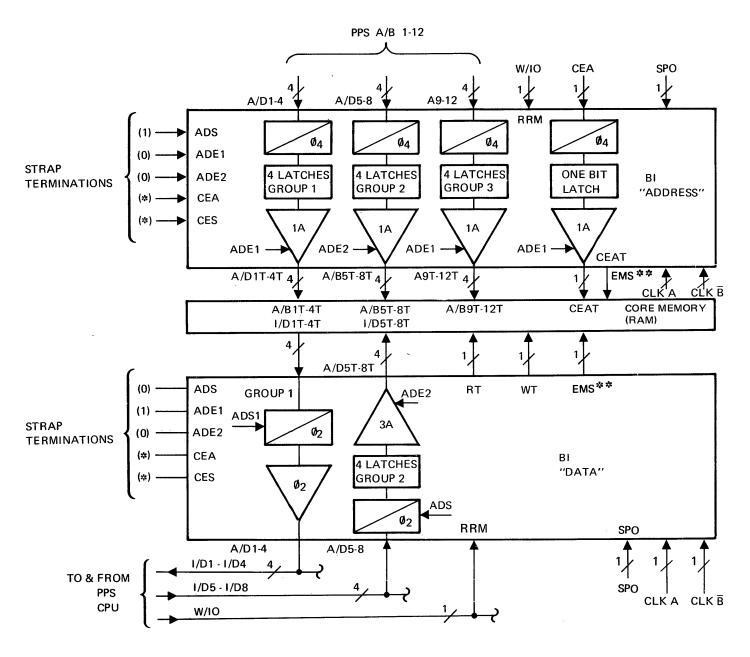

| Bus Interface Circuit, (BI)<br>P/N 10738                             | Permits core, static memories, and TTL I/O access to the PPS<br>Bus.                                                                                                                                         | Now             |

| Serial Data Controller<br>(SDC) P/N 10930                            | Full duplex, 0 thru 12 KBPS, asynchronous data trans-<br>mission. Provides odd/even parity and one or two stop bits<br>selection. EIA RS-232-C compatible.                                                   | 2nd Qtr<br>1975 |

#### DESCRIPTION

#### **GENERAL DESCRIPTION**

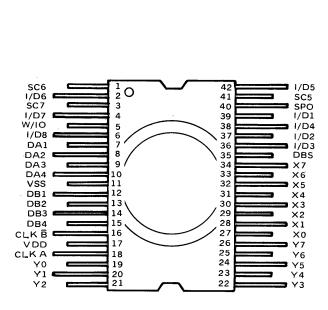

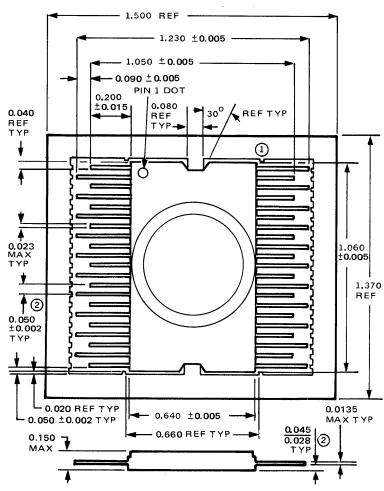

Each of the PPS-4 circuits (except for the clock) are packaged in 42-pin flat packs to provide maximum interfacing capability. A complete system can consist of only two 42-pin packages (the CPU and a ROM or combination ROM/RAM) plus the 4-phase clock generator. The PPS-4 circuits have been designed as a compatible group and each has been configured to maximize circuit density and processing speed, and to minimize power consumption. The CPU with its 12-bit parallel address bus and 8-bit parallel instruction/data bus directly addresses 4K of 8-bit instruction (ROM) words and 4K of 4-bit data (RAM) words while simultaneously the ROM outputs instruction words to the CPU in the form of 8-bit parallel information and the RAM transmits and receives 4 bits of data in parallel

during the same one cycle time. It is this parallel organization, along with a sophisticated time sharing technique, which results in an unusually high data rate.

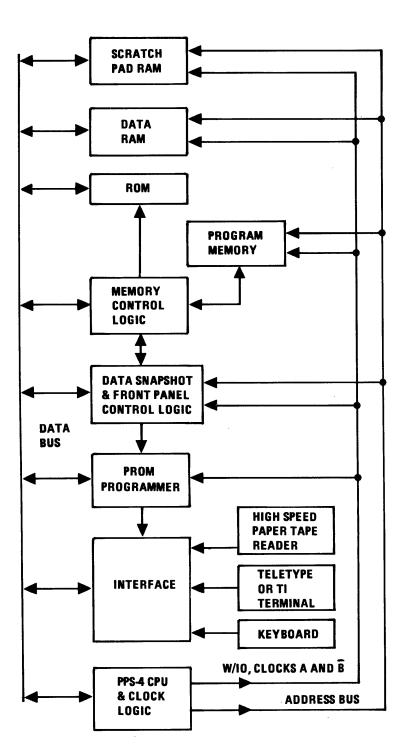

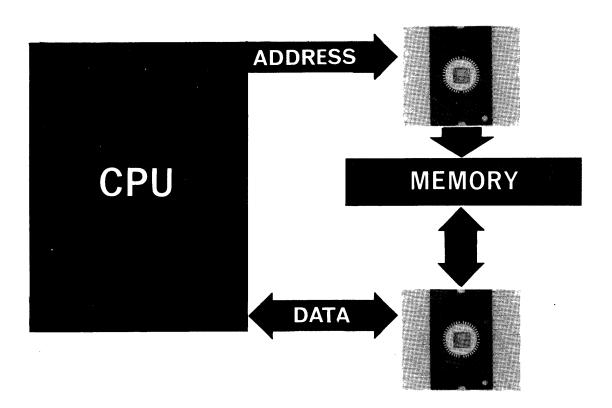

The implementation of a broad class of digital equipment is possible because of the one chip central processing unit (CPU) which receives and decodes an 8-bit instruction word to perform all required arithmetic and logic operations. The large number of instruction words to which the CPU responds gives it the capability of a 4-bit parallel minicomputer. These instruction words (referred to as micro instructions) are stored in ROMs for rapid accessing while RAMs are used to provide register files and storage of working data. An input/output buffer and multiphase clock generator complete the basic circuits required to configure a total system. Figure 1 illustrates a typical PPS-4 organization.

Figure, 1. Typical System Block Diagram.

#### DESCRIPTION - CENTRAL PROCESSING UNIT (CPU), P/N 10660

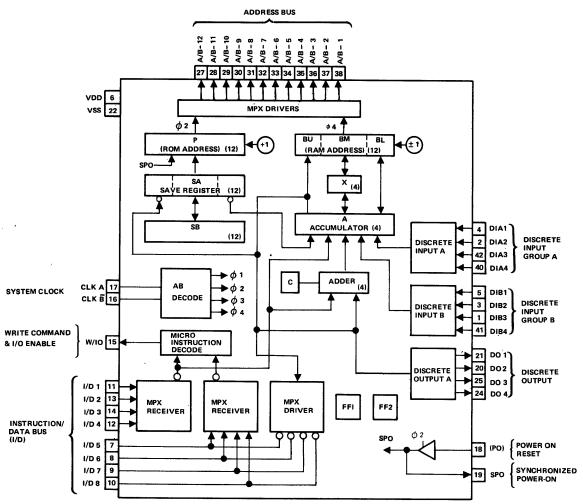

Figure 2. Central Processing Unit Block Diagram.

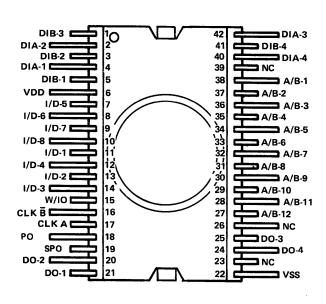

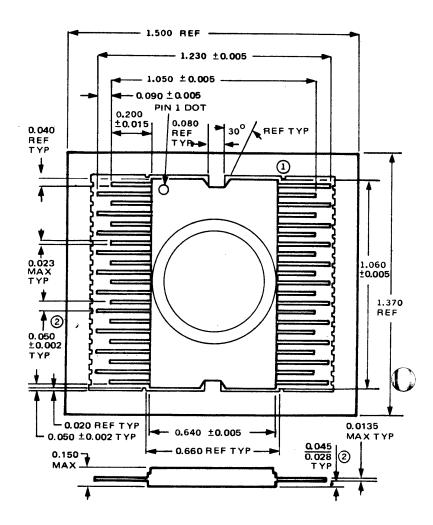

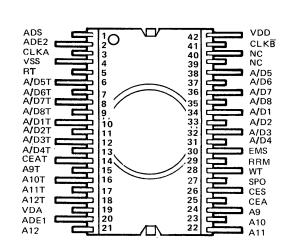

Figure 3. Central Processing Unit (CPU) Pin Configuration.

The Central Processing Unit (CPU) shown in Figure 2 is a 4-bit parallel processor. The CPU, through time sharing, utilizes an 8-bit parallel I/D bus to transfer 8-bit word instructions from ROM to CPU and I/O and also as a dual bidirectional 4-bit parallel data bus to transfer data between the CPU and RAMs and I/Os.

For memory expansion, software interrupt, or direct access with peripheral equipment, the CPU includes 8 discrete input and 4 discrete output lines.

The CPU contains: (a) microinstruction decoding necessary to receive and decode 50 basic instructions, (b) 4-bit parallel adder-accumulator for arithmetic and logic operations, (c) 12-bit (B) register for creating and storing addresses for RAM, (d) 12-bit (P) register and two 12-bit "Save" registers for creating and storing addresses for ROM, (e) 8 discrete input synchronizers, (f) 4 discrete output static drivers, (g) two individual control flip-flops and (h) multiplexed receivers and drivers for interfacing with the 12-bit parallel address bus and the 8-bit parallel data/instruction bus, and W/IO control line.

#### DESCRIPTION — CENTRAL PROCESSING UNIT (CPU) P/N 10660 (CONT)

#### (a) Micro-Instruction Decode

The decode portion of the chip interprets the instructions to control data transfers, arithmetic operations, and set up logical sequences. Instructions are coded in one byte (8 bits) and grouped as arithmetic, logical, data transfer, control transfer, input/output and special instructions. Direct subroutine calls, unconditional transfers, direct RAM address modifications, and the Input/Output command are considered long instructions because they require two bytes of ROM storage. However, the indirect subroutine call and indirect RAM address modification require only one byte of ROM storage. All instructions are executed in one cycle time of the "A" clock except long and indirect instructions and the I/O instruction which are executed in two cycle times. The instructions to which the CPU responds are listed on Pages 17 through 21.

#### (b) Adder-Accumulator

The adder is a 4-bit parallel binary adder with an internally connected carry FF for implementing precision arithmetic operations. The adder together with the 4-bit accumulator form the Arithmetic Logic Unit (ALU) secion of the CPU. Functionally, the CPU has ten microinstructions dedicated to arithmetic and logical operations. All are one-cycle instructions and enable direct arithmetic operation between the accumulator and the data stored in RAM or ROM memory.

In addition to its arithmetic functions, the accumulator is the primary working register in the CPU and is the central data interchange point for almost all data transfer operations occurring in the Parallel Processing System.

During internal data transfer the accumulator is the interfacing data register for both RAM and ROM. For external data exchanges (Input/Output) the accumulator is the source of the output data and the receiver register for the input data.

Because of the high usage of the accumulator, a secondary (extra) X-register has been included in the CPU. The X-register is a 4-bit register and is used in conjunction with the accumulator for temporary storage of data.

#### (c) RAM Address Register

This 12-bit B register, consists of three 4-bit registers (BU, BM and BL), which contain the address location to be accessed in RAM. Register BL is a counter and can be incremented or decremented by 1 through program control providing the ability to sequence through RAM registers serially by 4-bit character. The upper 8-bits (BU and BM) of RAM address can be set to special values by program control during a transfer operation of data to or from a distant RAM location into the working storage area indicated by the 4-bits of BL. During RAM address modification operations it is also possible to use accumulator A and register X for temporary storage of the upper 8 bits of the new address retrieval from RAM without destroying the current RAM address pointer.

#### (d) Program Counter and Save Register

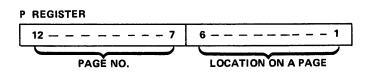

The 12-bit P-register and counter contains the address of the next program instruction. The lower 6-bits is a counter which is automatically incremented each cycle time during normal operation. The most significant 6-bits give the ROM number and page location. These six bits are only modified by the unconditional transfer (TL) or subroutine call (TML and TM) instructions. The SA and SB registers are two "Save" registers which provide a two level stack for holding instruction addresses during branching. This gives a direct two level nesting capability for storing program subroutine addresses in hardware; however, unlimited nesting is available via instruction CYS. This instruction recirculates register SA and accumulator A and, therefore, provides for saving ROM program addresses in RAM. Since RAM can be used for storing program addresses, subroutine nesting becomes limited only by the amount of dedicated storage allocated for this purpose.

#### (e) Control Flip-Flop (FF) and Discrete Input/Output (I/O)

There are two control flip-flops, FF1 and FF2, which can be set, reset, and tested by program control. There are also 8 discrete inputs which can be copied directly into the accumulator as two separate 4-bit groups. These groups are identified as discrete inputs group A (DIA) and discrete inputs group B (DIB). These inputs are intended to be used for inputting special signals, switch positions flags or interrupt line from circuitry external to the PPS. The contents of the accumulator can be outputted directly to circuits external to the PPS via a special 4-bit parallel output register (DOA) with individual output drivers. These outputs can be used to extend the ROM and RAM addressing beyond 4K. See special interface considerations on page 12 for more information on discrete inputs and outputs.

#### (f) Multiplex Drivers and Receivers

The multiplex driver and receiver circuits in the CPU provide direct interfacing with the system address and instruction data bus. The bus is time multiplexed and uses a unique precharge technique to achieve an unusually high system fan out. Systems containing up to 30 circuits can be mechanized without the need for external drivers.

#### (g) Power-On Reset

During power turn-on it is necessary to initialize the CPU P-counter to a known state such that the proper sequence of events can occur. This initialization is accomplished by inputting a negative pulse for a time duration of 10 msec or greater. This pulse is generated external to the PPS and as long as the pulse is a logic 1, the P-counter is held reset. The CPU, at the same time, generates a synchronized Power-on output signal which can be used to initialize other circuits.

#### DESCRIPTION - RANDOM ACCESS MEMORY (RAM), P/N 10432

\* THIS INPUT IS A SEPARATE VDD SOURCE FOR THE OUTPUT DRIVERS. THIS IS USEFUL FOR ISOLATING INDIVIDUAL CIRCUITS DURING DEVICE TESTING AND FOR FAULT ISOLATION WHEN MULTIPLE CIRCUITS ARE CONNECTED TO THE DATA BUS.

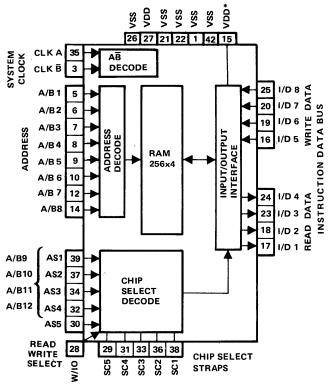

Figure 4. Random Access Memory (RAM), Block Diagram.

Figure 5. 256 x 4 Random Access Memory Pin Configuration.

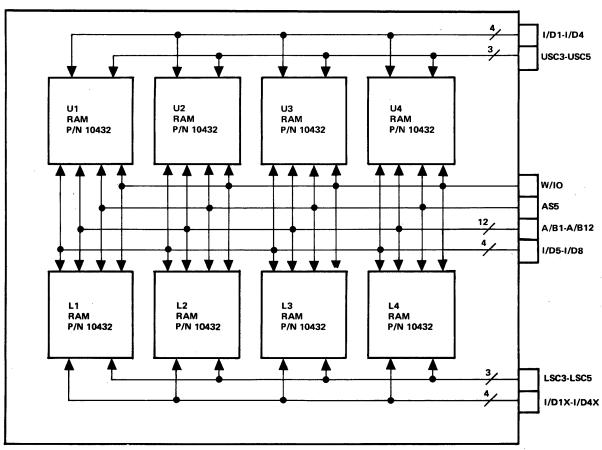

The Random Access Memory (RAM) P/N 10432, shown in Figure 4, is a 1024-bit Random Access Memory organized in a 256  $\times$  4-bit configuration. It has been designed as a dynamic memory with automatic refresh logic for use as a general working and memory register storage of data within a PPS set.

The Central Processing Unit (CPU), with its 12-bit parallel address outputs can directly address up to 16 RAM chips or 4096 words of 4-bit data. The RAM, with its 8 parallel address and 5 chip select inputs, provides for direct selection of up to 32 RAM chips or 8192 words of data. The one additional chip select input on the RAM chip (which cannot be addressed by the 12 bit address bus) can be used for memory expansion greater than 4096 word locations. For large systems the AS5 chip select input can be addressed by an output from an I/O circuit or a discrete output from the CPU. For systems with RAM memory capacity of 4096 words or smaller, the AS5 chip select input must be terminated at VSS.

The unique time sharing design of the PPS address and data buses is such that the contents of a given location in RAM can be exchanged with the contents of the accumulator in the CPU during one clock phase time. This is possible because when the RAM is addressed, it shifts the 4-bit data contents of the addressed location to the RAM output registers which place the data on one of the 4-bit parallel data buses. At the same time, if the write/RAM select input to the RAM is enabled, the RAM captures the data on the other 4-bit parallel data bus and copies it into memory location being addressed. In order for this to work, the CPU has placed the contents of the accumulator into its output register (which is the data being written into the RAM) and copies the data output from the RAM into the accumulator. This timing and data exchange capability is a major key to the high data rate and predictable performance of the PPS.

| RAM CH                | RAM CHIP ADDRESS SELECTION |      |      |      |      |  |  |

|-----------------------|----------------------------|------|------|------|------|--|--|

| CHIP SELECT           |                            |      |      |      |      |  |  |

| CHIP NO.              | SC 5                       | SC 4 | SC 3 | SC 2 | SC 1 |  |  |

| CHIP NO.              | S                          | Ñ    | S    | S    | - S  |  |  |

| o                     | 0                          | 0    | О    | 0    | o    |  |  |

| 1                     | 0                          | 0    | 0    | 0    | 1    |  |  |

| 2                     | 0                          | 0    | 0    | 1    | 0    |  |  |

| 3                     | 0                          | 0    | 0    | 1    | 1    |  |  |

| 4                     | 0                          | 0    | 1    | 0    | 0    |  |  |

| •                     |                            |      |      |      |      |  |  |

| •                     |                            |      |      |      |      |  |  |

| 31                    | 1                          | 1    | 1    | 1    | 1    |  |  |

| WHERE 1 = VDD, 0 = VS | s                          |      | '    | ' '  |      |  |  |

Figure 6. RAM Chip Address Selection Format.

#### DESCRIPTION - READ ONLY MEMORY (ROM), P/N A05---

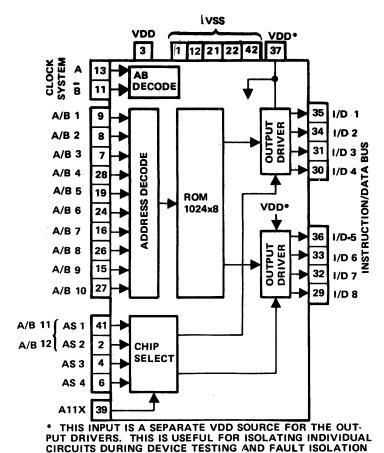

Figure 7. Read Only Memory (ROM) Block Diagram, P/N A05——

BUS.

WHEN MULTIPLE CIRCUITS ARE CONNECTED TO THE DATA

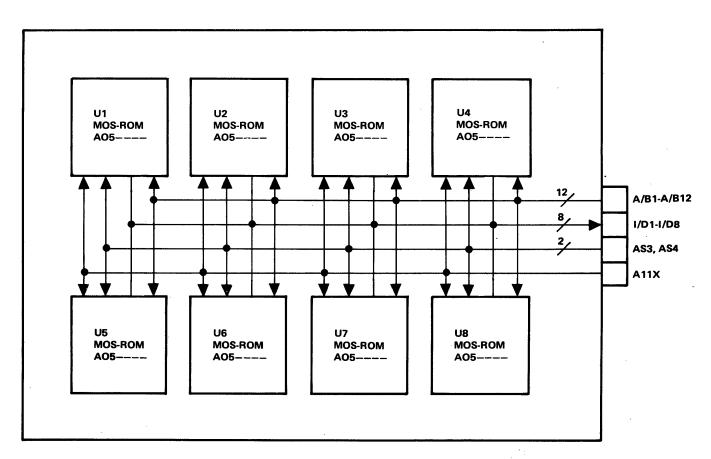

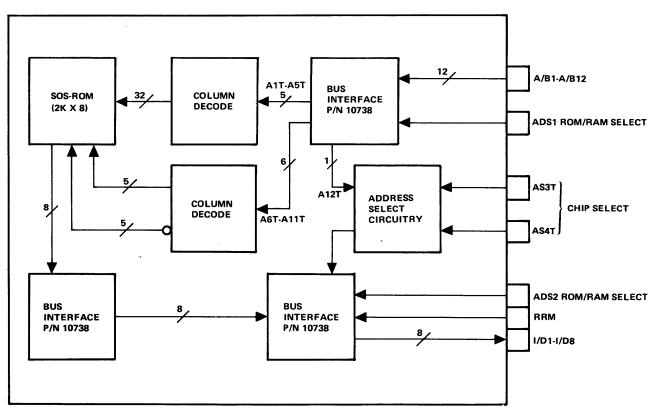

The Read Only Memory P/N A05--, shown in Figure 7, is a 8192-bit Read Only Memory organized in a 1024 x 8-bit configuration. It has been designed with dynamic address decode logic for interface compatibility with the PPS CPU. The ROM is programmed with a custom mask and is primarily intended to be used to store 8-bit micro-instruction routines for control and sequencing of data within a PPS set. The Central Processing Unit with its 12-bit parallel address outputs, can directly address up to 4 ROM chips or 4096 words of microinstruction. The ROM, with its 10 address and 4 chip select inputs, provides the direct selection of up to 16 ROM chips or 16,384 words of microinstruction. The two additional chip select inputs on the ROM chip (which cannot be addressed by the 12-bit address bus) can be used for memory expansion greater than 4096. A detailed discussion of the ROM system expansion can be found in the programers manual. If not used, the extra inputs (AS3 and AS4) should be tied to VSS.

In addition to its primary function of storing microprograms, the ROM is designed such that it can be encoded, during the mask operation, to respond to Read Out during the RAM time interval. This means that a selected ROM can be used as a Read Only RAM for code conversion or a table look-up operation. When used in this application, the selected ROM responds to the RAM address and transmits 4-bits of data to the data bus. The 8 parallel outputs from the ROM are externally connected together to form a 4-bit parallel output. The A11X address term is used to select the upper or lower 4 bits of the 8-bit output. This has the effect of creating a 2048 x 4-bit organization for the storage of permanent data which is easily addressed and accessed by the RAM data transfer instructions. For example A11X=0 selects I/D5—I/D8 and A11X=1 selects I/D4—I/D1.

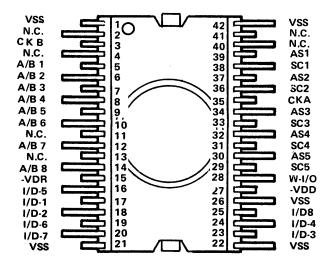

Figure 8. Read Only Memory Pin Configuration, P/N A05—-

#### DESCRIPTION - READ ONLY MEMORY (ROM), P/N A52--

The Read Only Memory P/N A52--, shown in Figure 9 is a 16,384-bit read only memory organized in a 2048 x 8-bit configuration. Functionally, the A52-- ROM is identical to the A05-- ROM except that the A52-- ROM provides twice as much storage capacity. The pin-outs and internal circuitry is similar

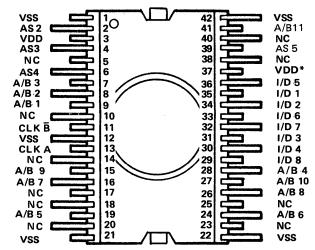

**VSS VDD** 3 22 37 DECODE 35 A/B 1 I/D -1 OUTPUT DRIVER 34 1/D 2 A/B 2 1/D 3 8 31 A/B 3 DECODE A/B 4 28 A/B 5 19 ROM ADDRESS VDD\* A/B 6 24 2048 16 A/B 7 36 I/D-5 OUTPUT DRIVER A/B 8 26 33 1/D 6 🔽 A/B 9 15 32 I/D 7 A/B 10 29 I/D 8 A/B 11 A/B 12 AS 2 2 CHIP SELECT AS 3 AS 4 6 AS 5 THIS INPUT IS A SEPARATE VDD SOURCE FOR THE OUT-PUT DRIVERS. THIS IS USEFUL FOR ISOLATING INDIVIDUAL CIRCUITS DURING DEVICE TESTING AND FAULT ISOLATION

Figure 9. Read Only Memory (ROM) Block Diagram.

WHEN MULTIPLE CIRCUITS ARE CONNECTED TO THE DATA

except that addressing inputs A/B11 on pin 41 goes to the Address Decode circuits instead of the Chip Select circuits and input A11X becomes AS5. These addressing input changes provide for addressing the additional memory.

It has been designed with dynamic address decode logic for interface compatibility with the PPS CPU. The ROM is programmed with a custom mask and is primarily intended to be used to store 8-bit microinstruction routines for control and sequencing of data within a PPS set. The Central Processing Unit with its 12-bit parallel address outputs, can directly address up to 2 ROM chips or 4096 words of microinstruction. The ROM, with its 11 address and 4 chip select inputs, provides for direct selection of up to 16 ROM chips or 32,768 words of microinstruction. The three additional chip select inputs on the ROM chip (which cannot be addressed by the 12-bit address bus) can be used for memory expansion greater than 4096. A detailed discussion of the ROM system expansion can be found in the programers manual. If not used, the extra inputs (AS3, AS4 and AS5) should be tied to VSS.

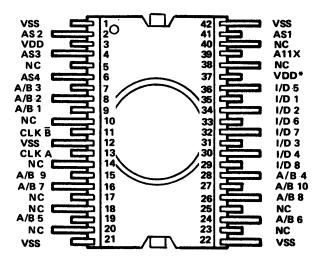

Figure 10. Read Only Memory Pin Configuration.

## DESCRIPTION — READ ONLY MEMORY/RANDOM ACCESS MEMORY (ROM/RAM), P/N A07——

Read Only Memory/Random Access Memory (ROM/RAM) P/N A07-- is similar to ROM/RAM P/N A08-- except that the A07-- provides 8192 bits of ROM storage and 464 bits of RAM storage which is considerably greater than the storage in the A08--. Like the A08--, the A07-- is uniquely designed for use with the PPS-4, and is especially adaptable for production of low cost microcomputer systems since both the ROM and RAM are a single circuit. Application of this device is common in controllers, small cash registers, electronic weighing scales, fast food service terminals, etc.

The ROM section is organized as 1024 x 8 words and the RAM section is organized as 116 x 4 words. The block dia-

gram shown in Figure 11 is valid for ROM/RAM A07--, and the pin configurations and address formats in Figures 12 and 13 are also valid for the A07--.

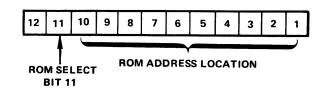

Two A07-- ROM/RAM's may be used in a single system, or one A07-- may be combined with one A08-- in a single system. The ROM function is selected by A/B11, and the RAM function is selected by A/B7. Both A/B7 and A/B11 can be masked so that either is activated by a logic one or zero. During the RAM function time A/B9 and A/B10 must be at "O",

## DESCRIPTION — READ ONLY MEMORY/RANDOM ACCESS MEMORY (ROM/RAM), P/N A08 ——

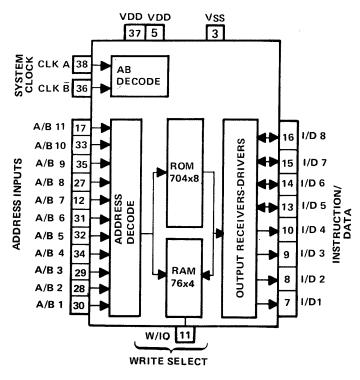

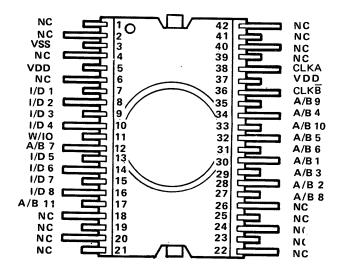

Figure 11. ROM/RAM Block Diagram P/N A08--- and P/N A07--

The Read Only Memory/Random Access Memory P/N A08--, shown in Figure 11, is a circuit containing a mask programmable MOS ROM as well as a RAM. It is uniquely designed to interface with the PPS CPU address and data bus and, as such, is useful in equipments requiring only a relatively small amount of ROM and RAM. The ROM section is organized as 704 x 8 words (5,632 bits) while the RAM section is organized as 76 x 4 words (304 bits). The chip interfaces with the common address bus and contains a single address decoder section. Internal clock timing is generated such that the decoded address is routed to the RAM section or the ROM section as a function of "A" and "B" clock inputs. In a like manner, the outputs drive or receive data from the 8-bit instruction/data bus in the PPS as a function of clock timing and control signals. From the users' point of view, this single chip provides the same functions as the ROM chip, P/N A05-- and the RAM chip, P/N 10432, except for the smaller amount of ROM and RAM.

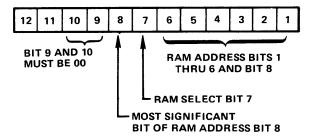

The addressing mask option provides for up to two A08--ROM/RAM's in a single system. Specifically, the ROM function is selected by A/B11, and the RAM function selected by A/B7. Both A/B7 and A/B11 can be masked so that either is activated by a logic one or zero. During the RAM function time A/B9 and A/B10 must be at "0".

Figure 12. ROM/RAM Configuration.

#### RAM ADDRESS FORMAT (B REGISTER)

#### **ROM ADDRESS FORMAT (P REGISTER)**

Figure 13. RAM Address Format.

#### DESCRIPTION - GENERAL PURPOSE INPUT/OUTPUT (I/O), P/N 10696

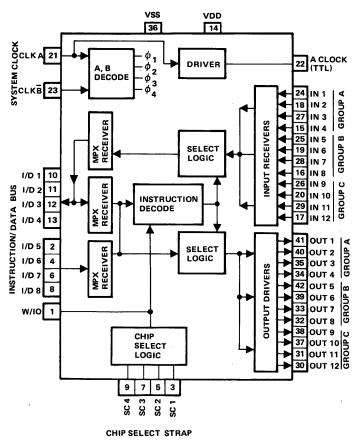

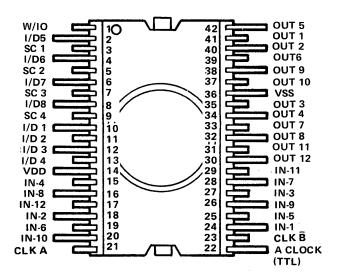

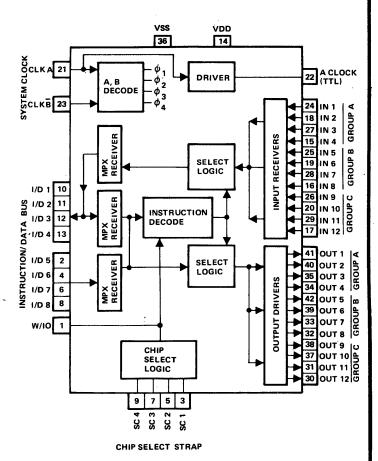

Figure 14. General Purpose Input/Output Device Block Diagram.

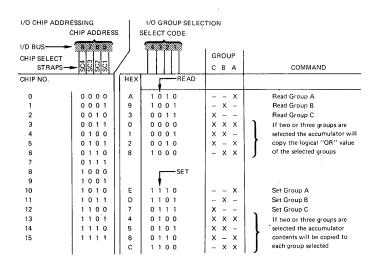

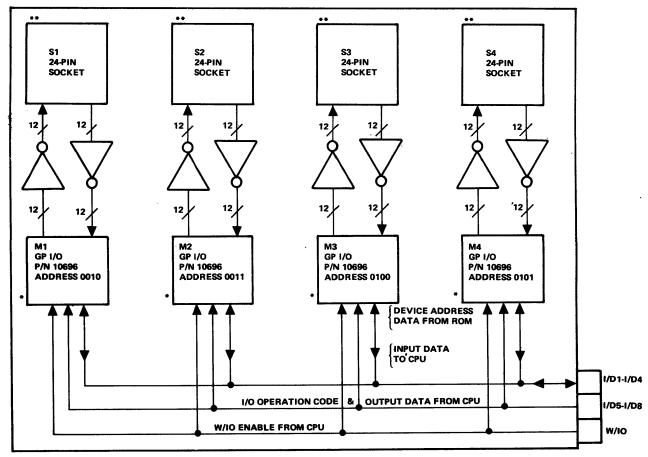

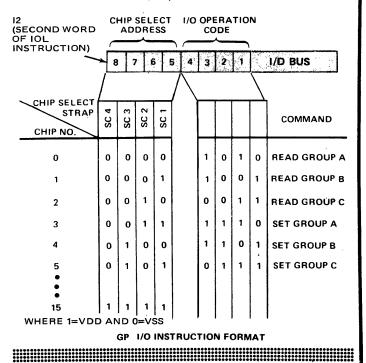

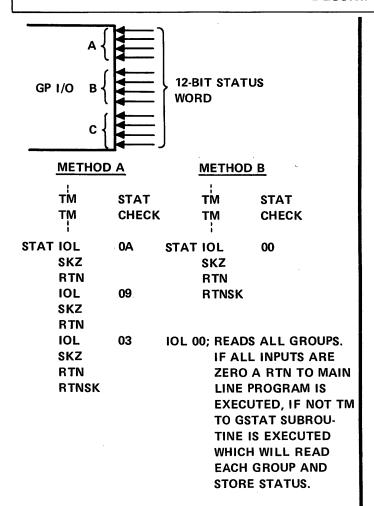

The General Purpose Input/Output device P/N 10696, shown in Figure 14. provides 12 discrete inputs and 12 discrete static outputs. This device is used for direct data exchange or status and control functions with an external peripheral device. The GPI/O circuit uses special interface circuitry to directly interface with TTL circuitry. A schematic of the recommended TTL interface is shown on page 12, Special Interface Considerations. Direct addressing for up to sixteen of these circuits is possible by the use of 4 chip address straps that can be terminated, by the user, to create each chip address. The I/O is accessed with an I/O enable signal from the CPU and a simultaneous 8-bit instruction from ROM. Four bits of the instruction are used to address the particular I/O chip; the other four bits define the I/O operation.

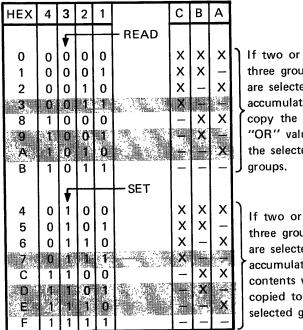

The 4-bit operation code is interpreted by the I/O to either copy the contents of the accumulator into one of the three 4-bit parallel output registers (A, B or C) or transfer data from one of the 4-bit parallel input receivers (A, B or C) into the accumulator of the CPU. The output drivers are static outputs and data remains in the output registers until altered. Bits 1 through 4 of the instruction word are commands to the I/O while bits 5 through 8 are used to address 1 of 16 possible I/O chips. The four I/O select inputs terminated by the user, create the addresses for each I/O circuit. The I/O coding is shown below.

Data is transferred through the GPI/O from input groups A, B or C to I/D 1-4 and output groups A, B or C to I/D 5-8 most significant to most significant and least significant to least significant. For Signal Polarity see special interface considerations Page 12.

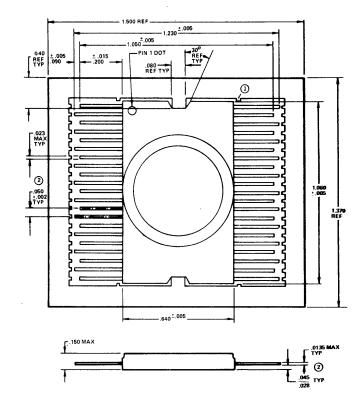

Figure 15. General Purpose Input/Output Pin Configuration.

NOTE: Any one of the I/O chips may be used to read or set any group (A, B, or C) or combination of groups.

Figure 16. GPI/O Instruction Format.

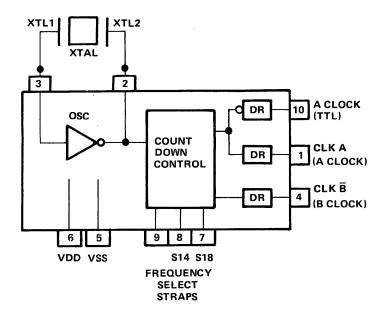

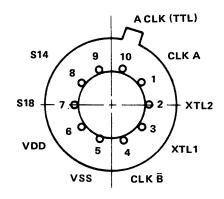

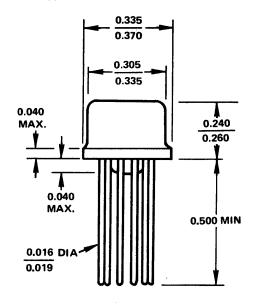

#### **DESCRIPTION - CLOCK GENERATOR, P/N 10706**

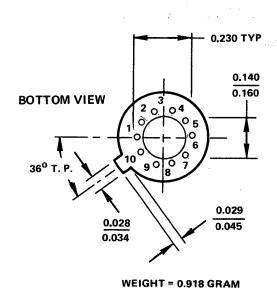

NOTE: PIN 5 IS INTERNALLY TIED TO THE CASE

Figure 17. Clock Generator Block Diagram

**BOTTOM VIEW**

Figure 18. Clock Generator Pin Configuration, P/N 10706NB.

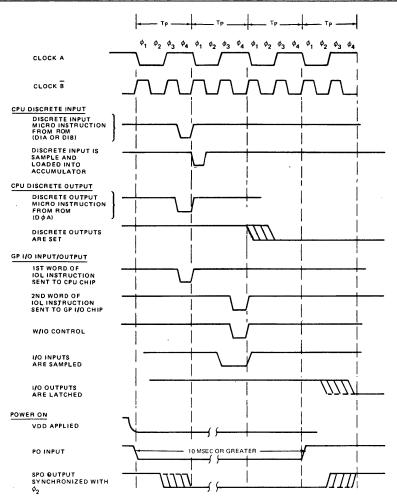

The Clock Generator circuit P/N 10760, shown in Figure 17, generates the "A" and "B" clock waveforms required by circuits in the PPS. The combined A and  $\overline{B}$ clocks provide the unique 4-phase dynamic timing shown in Figure 23 and described in the associated text on page 14. The Clock Generator has an internal oscillator which is stabilized by connecting a quartz crystal to the appropriate inputs. The crystal is a 3.579545 MHz color TV crystal which is low in cost and readily available. The "A" clock output is a square wave and considered the primary clock. Output "B" is a pulse output occurring during each phase of the "A" clock and has unique timing features required by the circuits within the PPS set. The "A" clock is also provided through an output which drives to ground such that TTL levels can be easily achieved for synchronizing equipment external to the PPS.

The input straps provide a countdown of the oscillator frequency equal to the number associated with the strap: i.e., S14 divides by 14 and S18 input results in a countdown by 18. Thus, with a crystal frequency of approximately 3.58 MHz and input S18 terminated to V<sub>DD</sub>, the "A" clock output frequency will be 358 ÷ 18 = 199 kHz. This is the recommended mode of operation when used in the PPS set.

#### Crystal Specifications (3.57954 MHz)

| Max Series Resistance | 150 $\Omega$     |

|-----------------------|------------------|

| Excitation Level      | 10 <u>+</u> 1 Mw |

| Shunt Capacity        | 7 Pf Max         |

| Load Capacity         | 16 Pf + 0.5 Pf   |

#### **FREQUENCY SELECTION**

| SELECT<br>STRAPS<br>DIVISION | S14 | <b>\$18</b> | CLOCK<br>FREQ |

|------------------------------|-----|-------------|---------------|

| ÷ 18                         | 0   | 1           | 199 kHz       |

| ÷14                          | 1   | 0           | 256 kHz       |

WHERE 1= VDD, 0 = VSS

Figure 19. Frequency Selection Format.

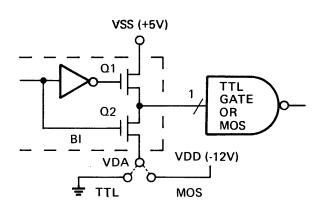

#### SPECIAL INTERFACE CONSIDERATION

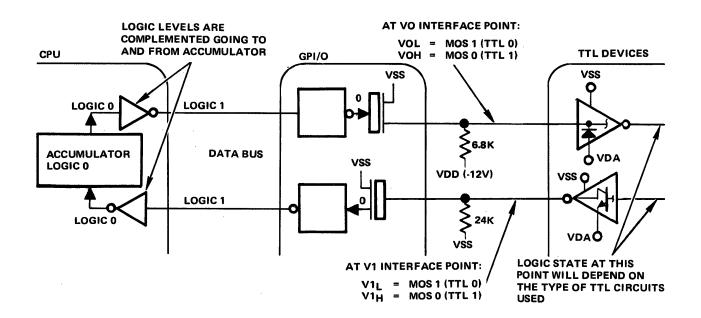

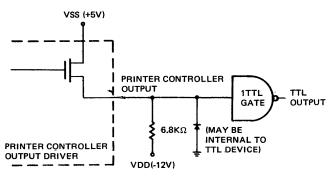

#### GPI/O Outputs and "A Clock TTL Output"

The GPI/O outputs are open drain buffers which when turned on will drive the GPI/O output to VSS with a maximum resistance of 1K ohms and a maximum current capacity of 2.7 mA. When turned off the GPI/O output will float, hence a pull down resistor to VDD is required. A logic 1 on a data bus will turn the corresponding driver off and a logic 0 will turn the driver on. These circuits can be used for either TTL or MOS levels. Shown is the circuit termination for a TTL interface. The diode, which is internal to the TTL device, prevents a reverse breakdown of the TTL gate. The transfer of data through the GPI/O is done without any signal inversions. However, data bus signals are inverted from the I/D bus to the CPU accumulator and from the CPU accumulator to the I/D bus.

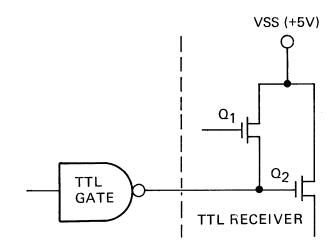

#### **GPI/O Inputs**

The GPI/O inputs are a low threshold design which will respond to the TTL voltage levels. A recommended circuit for TTL to MOS interface is shown in Figure 20. For optimum performance, the TTL device should have an open collector output. The window of voltage values with respect to VSS where the device will change state internally is between -1.5V and -4.2V.

The transfer of data through the GPI/O is done without signal inversions. However, data bus signals are inverted from the I/D bus to the CPU accumulator and from the CPU accumulator to the I/D bus.

NOTE: VSS, VDA, AND VDD VOLTAGE RELATIONS ARE AS FOLLOWS:

| NAME | MOS GND<br>REFERENCE | TTL GND<br>REFERENCE |

|------|----------------------|----------------------|

| vss  | ٥V                   | +5V                  |

| VDA  | -5V                  | ov                   |

| VDD  | -17V                 | -12V                 |

Figure 20. Typical GPI/O Interface Logic.

#### SPECIAL INTERFACE CONSIDERATION (CONT)

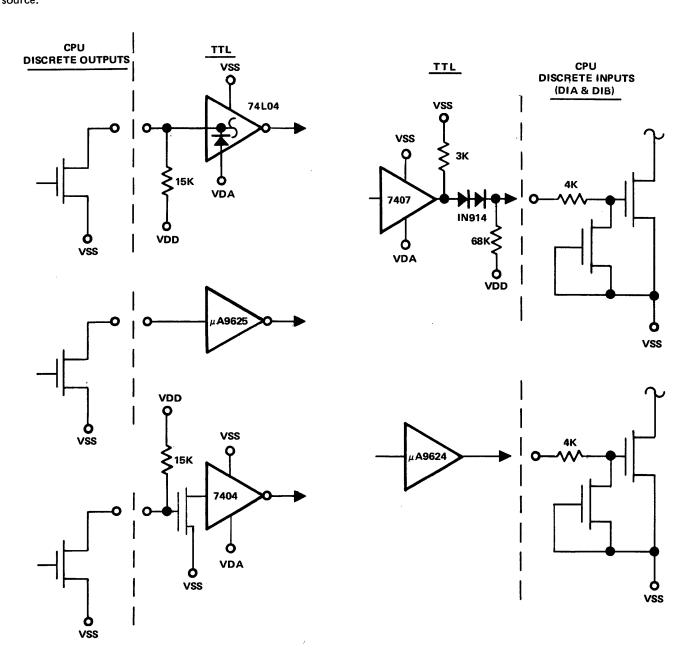

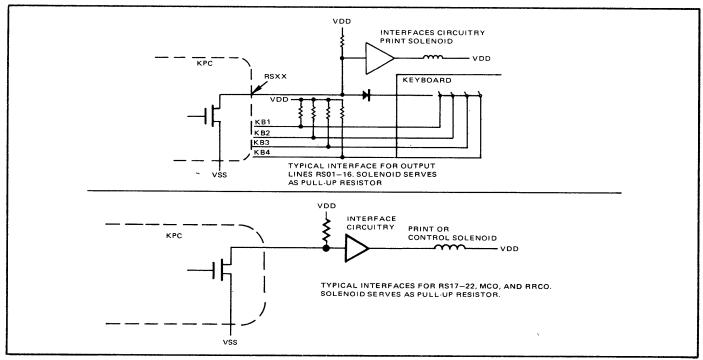

#### **CPU Discrete Outputs (See Figure 21)**

These outputs are designed to work with circuitry external to the MOS circuitry. This type of output is an open drain MOS transistor to VSS. In the "ON" state, the output is driven to VSS with a maximum resistance of 1.25K and a maximum current capacity of 1.25 mA. In the off state, the output is floating.

The term float means a minimum of 5 megohms to any source.

#### CPU Discrete Inputs (See Figure 22)

The inputs are internally synchronized to the clock so that regardless of the timing or speed of the input signal, all of the internal logic connected to this signal will accept the signal as a good true or a good false at the same bit time. The window of voltage values with respect to VSS where the device will change states internally will be between -2.5V and -7.5V.

Figure 21. Typical CPU Discrete Output Circuits.

Figure 22. Typical Discrete Input Circuits.

#### BASIC SYSTEM OPERATION

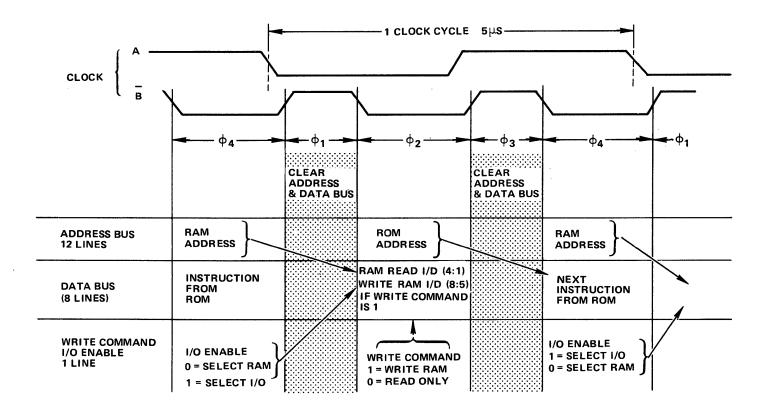

The Parallel Processing System has a repertoire of 50 basic CPU instructions and 16 instructions for each I/O circuit. These instructions control the operation of the PPS microcomputer, and are the key to the versatility of the systems.

During each program counter bit time the CPU will address the ROM, read and decode the instruction, execute the instruction, increment the ROM program counter, and load the RAM program counter in preparation for the next instruction. This bit time or single cycle instruction fetch and execution time is 5  $\mu$ sec. The proprietary architecture and multiphase clock timing techniques of the PPS result in this unusually high data handling rate from a relatively slow external clocking system.

#### (a) System Timing

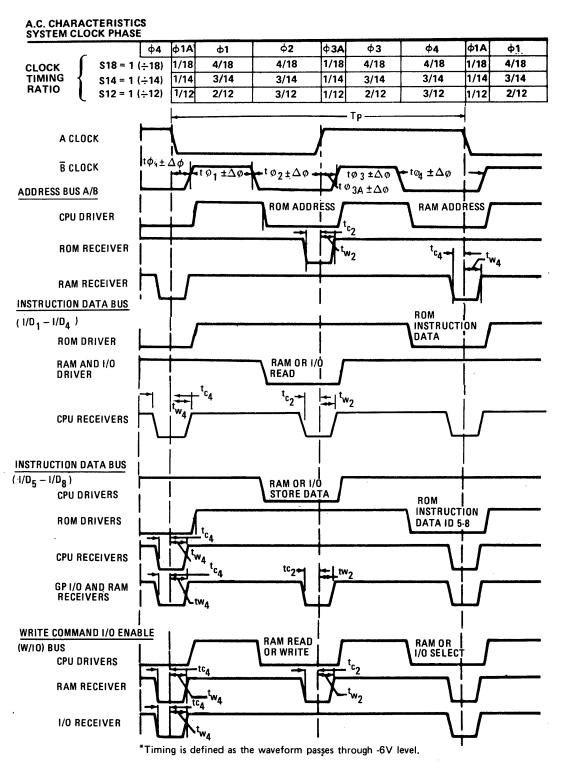

The PPS circuits are controlled from a crystal controlled clock generator which provides two synchronized and phased

clock signals. These signals, designated as A and  $\overline{B}$ , are received by the CPU and logically divided into four phases, such that the internal signals are being manipulated at four times the frequency of the A clock. For example, if the A clock is 200 kHz, logic signal flow within the CPU is occurring at 800 kHz. The basic clock timing is shown in Figure 23.

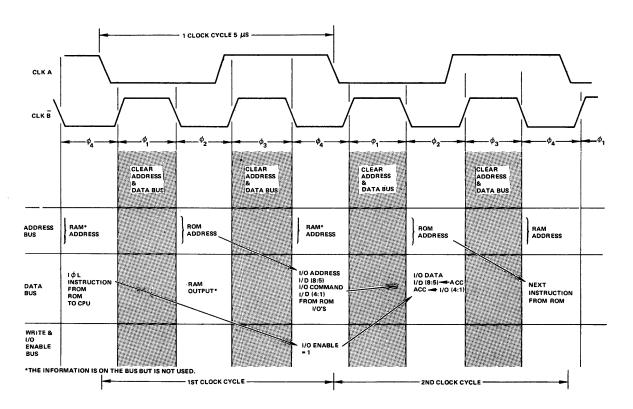

The PPS parallel bus transfer lines are synchronized by A and  $\overline{B}$  clock signals so that data and address transfer occurs only at  $\phi 2$  and  $\phi 4$  time as shown in Figures 23 and 24. During the alternate phase times,  $\phi 1$  and  $\phi 3$ , the address and data bus lines are automatically cleared to zero. This unique interface timing enables the system to drive high capacitive loads normally associated only with larger and more complex systems. In fact, systems with up to 30 PPS devices can reliably share the PPS bus without the need for additional buffering or drive circuitry.

Figure 23. Parallel Processing System Basic Bus Timing

#### **BASIC SYSTEM OPERATION (CONT)**

#### (b) Logic Levels

A negative logic notation is used in the PPS system. That is, a logic one (1) is defined as the most negative voltage, while a logic zero (0) is defined as the most positive voltage. For example, assuming a -17 volt power supply where  $V_{DD} = -17$  volts and  $V_{SS} = 0$  volts; a logic 0 is defined as  $\geqslant -1.9$  volts while a logic 1 is defined as  $\leqslant -7.5$  volts.

#### (c) Multiplex System Data Transfer

In addition to the power and clock signals there are 21 multiplexed lines interconnecting the CPU with ROM, RAM and I/O circuits. These lines are functionally grouped as follows:

12 parallel address lines

8 parallel data lines

1 write command and I/O enable line

The twelve address lines originate at the CPU and are time multiplexed within the CPU to provide direct addressing capability for up to 4096 locations on both the ROM and RAM. In addition to the twelve direct address lines, the ROM, P/N A05—, circuit has two chip select inputs and the RAM, P/N 10432, circuit has one chip select input. These chip select lines may be directly controlled by discrete outputs from CPU or I/O circuits for memory expansion without the need for auxiliary circuitry. Memory expansion is more fully explained in the description of the ROM and RAM. Like the address lines the eight data bus lines are time-shared lines from the

CPU. During  $\phi_2$  a logical "one" on the write enable line is interpreted by the RAM's as a write enable command and data on the bus will be written into RAM. The RAM is a non-destructive read-out device and, therfore, is always programmed to read; however, it must be instructed to "write." Because the 8 data lines are functioning as a dual 4-bit bidirection data bus during  $\phi_2$ , it is possible for RAM to read 4 bits from the designated address out to the data bus and, during the same cycle time, write 4 bits from the data bus into the designated RAM address location.

The same line providing the write command to RAM during  $\phi_2$  time serves as an I/O enable signal during  $\phi_4$  time of the input/output instruction (IOL). If the I/O enable is on (logical 1) at  $\phi_4$  the RAM will be disabled during the next  $\phi_2$  time, and the data bus will be used to transfer information between accumulator in the CPU and I/O circuits.

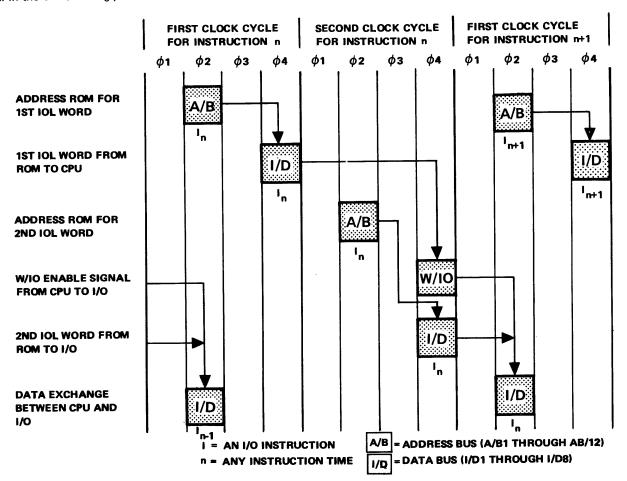

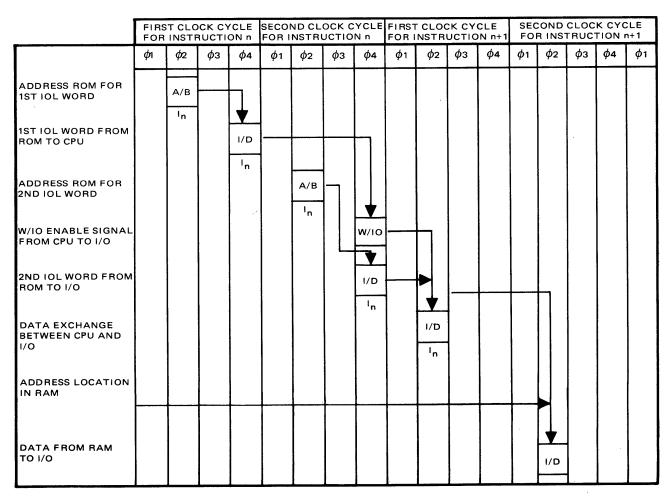

The input/output instruction (IOL) is a special application of the bus timing and requires two clock cycles and two successive ROM memory locations. During the first clock cycle the "IOL" instruction is received from ROM and decoded in the CPU. During the second clock cycle the I/O enable line will alert all the I/O circuits and at the same time an I/O address and command is transmitted from ROM turning on the selected I/O circuit. Data transfer between the selected I/O circuit and accumulator in the CPU will occur during  $\phi_2$  of the next clock cycle.

A timing diagram of the IOL instruction is shown in Figure 24.

Figure 24. I/O Instruction PPS Timing.

#### **INSTRUCTION LIST**

The following pages provide a listing of the 50 instructions which can be used to control generation of ROM and RAM address as well as manipulation and transfer of data between the CPU and RAM and I/O. Definitions of symbology

used in the instruction list is also provided such that a programmer can easily understand the instruction list and begin to visualize how the PPS may be used for a given application.

#### **DEFINITIONS OF SYMBOLIC NOTATION**

| Symbols                           |                                                                            |

|-----------------------------------|----------------------------------------------------------------------------|

| Α                                 | Accumulator Register, A(4:1)                                               |

| A/Bn                              | Line n of Address Bus                                                      |

| В                                 | RAM Address Register, B(12:1)                                              |

| С                                 | Carry Link Flip-Flop                                                       |

| FF <sub>1</sub> , FF <sub>2</sub> | General Flip-Flop 1, General Flip-Flop 2                                   |

| 1                                 | Instruction (Typically 8-bit Field)                                        |

| I/Dn                              | Line n of Instruction/Data Bus                                             |

| <b>I</b> n                        | Byte n of Long Instruction (i.e. $I_1 = 1^{st}$ byte, $I_2 = 2^{nd}$ byte) |

| M                                 | RAM Memory Contents Designated by Register B                               |

| m                                 | General Numeric Designator, m = 1, 2, 3,                                   |

| n                                 | General Numeric Designator, n = 1, 2, 3,                                   |

| Р                                 | ROM Program Counter Register, P (12:1)                                     |

| BL                                | Lower Field of Register B (4:1)                                            |

| BM                                | Middle Field of B Register B (8:5)                                         |

| BU                                | Upper Field of B Register, B (12:9)                                        |

| R(n)                              | Bit n of General Register R                                                |

| R(m:n)                            | Bits m thru n of General Register R inclusive [e.g., R(12:7)]              |

| SA                                | Upper Stack of Save Registers, SA(12:1)                                    |

| SB                                | Lower Stack of Save Registers, SB(12:1)                                    |

| W/IO                              | Write Command and I/O Enable Line                                          |

| · X                               | Secondary Accumulator Register, X(4:1)                                     |

| Digit                             | Four Bit Field (sometimes referred to as Data or Character)                |

| Byte                              | Eight Bit Field                                                            |

| Page                              | ROM Block of 64 Bytes (*)                                                  |

| ← →                               | Replaces                                                                   |

| $\longleftrightarrow$             | Exchange                                                                   |

|                                   | 1's Complement (e.g., $\overline{A}$ is 1's complement of A)               |

| V                                 | Logical Inclusive OR                                                       |

| ₩.                                | Logical Exclusive OR                                                       |

| ٨                                 | Logical and                                                                |

| +                                 | Algebraic Add                                                              |

| -                                 | Algebraic Subtract                                                         |

<sup>\*</sup>A page is defined in the PPS as 64 ROM address locations. The page number is specified by the six (6) most significant bits of the 12-bit P register. The locations within a page are defined by the six (6) least significant bits.

#### ARITHMETIC INSTRUCTIONS

| Mnemonics | I/D Bus<br>OP Code<br>Hex & Binary      | Name                                              | Description                                                                                                                                                                                                                                                                                                                                                                            | Symbolic<br>Equation                                                                                            |

|-----------|-----------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| AD        | OB<br>0000 1011                         | Add<br>(1 cycle)                                  | The result of binary addition of contents of accumulator and 4-bit contents of the RAM currently addressed by B register, replaces the contents of accumulator. The resulting carry-out is loaded into C flip-flop.                                                                                                                                                                    | C, A ← A+M                                                                                                      |

| ADC       | OA<br>0000 1010                         | Add with carry-in (1 cycle)                       | Same as AD except the C flip-flop serves as a carry-in to the adder.                                                                                                                                                                                                                                                                                                                   | C,A ← A+M+C                                                                                                     |

| ADSK      | O9<br>0000 1001                         | Add and skip on<br>carry-out<br>(1 cycle)         | Same as AD except the next ROM word will be skipped (ignored) if a carry-out is generated.                                                                                                                                                                                                                                                                                             | C, A ← A+M<br>Skip if C = 1                                                                                     |

| ADCSK     | O8<br>0000 1000                         | Add with carry-in and skip on carry-out (1 cycle) | Same as ADSK except the C flip-<br>flop serves as a carry-in to the<br>adder.                                                                                                                                                                                                                                                                                                          | C, A ← A+M+C<br>Skip if C = 1                                                                                   |

| ADI       | 60-6E<br>*0110 <u>xxxx</u><br>Except 65 | Add immediate and skip on carry-out (1 cycle)     | The result of binary addition of contents of accumulator and 4-bit immediate field of instruction word replaces the contents of accumulator. The next ROM word will be skipped (ignored) if a carry-out is generated. This instruction does not use or change the C flip-flop. The immediate field I(4:1) of this instruction may not be equal to binary 0000 or 1010 (See CYS and DC) | A $\leftarrow$ A+[I(4:1)]<br>Skip if carry-out = one<br>I(4:1) $\neq$ '0000<br>I(4:1) $\neq$ 1010<br>See Note 3 |

| DC ,      | 65<br>0110 0101                         | Decimal Correction<br>(1 cycle)                   | Binary 1010 is added to contents of accumulator. Result is stored in accumulator. Instruction does not use or change carry flip-flop or skip.                                                                                                                                                                                                                                          | A ← A+1010                                                                                                      |

|           |                                         | LOGICAL II                                        | NSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                 |

| AND       | OD<br>0000 1101                         | Logical AND<br>(1 cycle)                          | The result of logical AND of accumulator and 4-bit contents of RAM currently addressed by B register replaces contents of accumulator.                                                                                                                                                                                                                                                 | A← A∧M                                                                                                          |

| OR        | OF<br>0000 1111                         | Logical OR<br>(1 cycle)                           | The result of logic OR of accumulator and 4-bit contents of RAM currently addressed by B register replaces contents of accumulator.                                                                                                                                                                                                                                                    | A←A∨M                                                                                                           |

| EOR       | OC<br>0000 1100                         | Logical Exclusive-<br>OR (1 cycle)                | The result of logic exclusive-OR of accumulator and 4-bit contents of RAM currently addressed by B register replaces contents of accumulator.                                                                                                                                                                                                                                          | A ← A ♥ M                                                                                                       |

| COMP      | OE<br>0000 1110                         | Complement<br>(1 cycle)                           | Each bit of the accumulator is logically complemented and placed in accumulator.                                                                                                                                                                                                                                                                                                       | A←Ā                                                                                                             |

\*xxxx Indicates restrictions on bit patterns allowable in immediate field as specified in the symbolic equation description.

#### **DATA TRANSFER INSTRUCTIONS**

| Mnemonics | I/D Bus<br>OP Code<br>Hex & Binary | Name                                                                           | Description                                                                                                                                                                                                                    | Symbolic<br>Equation                                                           |

|-----------|------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| SC        | 20<br>0010 0000                    | Set Carry flip-flop<br>(1 cycle)                                               | The C flip-flop is set to 1.                                                                                                                                                                                                   | C ← 1                                                                          |

| RC        | 24<br>0010 0100                    | Reset Carry flip-flop<br>(1 cycle)                                             | The C flip-flop is set to 0.                                                                                                                                                                                                   | C ← 0                                                                          |

| SF1       | 22<br>0010 0010                    | Set FF1<br>(1 cycle)                                                           | Flip-flop 1 is set to 1.                                                                                                                                                                                                       | FF1 ← 1                                                                        |

| RF1       | 26<br>0010 0110                    | Reset FF1<br>(1 cycle)                                                         | Flip-flop 1 is set to 0.                                                                                                                                                                                                       | FF1 ← 0                                                                        |

| SF2       | 21<br>0010 0001                    | Set FF2.<br>(1 cycle)                                                          | Flip-flop 2 is set to 1.                                                                                                                                                                                                       | FF2 ← 1                                                                        |

| RF2       | 25<br>0010 0101                    | Reset FF2<br>(1 cycle)                                                         | Flip-flop 2 is set to 0.                                                                                                                                                                                                       | FF2 ← 0                                                                        |

| LD        | 30-37<br>0011 0                    | Load Accumulator<br>from Memory<br>(1 cycle)                                   | The 4-bit contents of RAM currently addressed by B register are placed in the accumulator. The RAM address in the B register is then modified by the result of an exclusive-OR of the 3-bit immediate field I(3:1) and B(7:5). | $A \leftarrow M;$ $B(7:5) \leftarrow B(7:5) \forall$ $[I(3:1)]$ See Note 3     |

| EX        | 38-3F<br>0011 1                    | Exchange Accumulator and Memory (1 cycle)                                      | Same as LD except the contents of accumulator are also placed in currently addressed RAM location.                                                                                                                             | $A \leftrightarrow M$ $B(7:5) \leftarrow B(7:5) \forall$ $[I(3:1)]$ See Note 3 |

| EXD       | 28-2F<br>0010 1                    | Exchange Accumulator<br>and Memory and<br>decrement BL (1 cycle)<br>See Note 3 | Same as EX except RAM address in B register is further modified by decrementing BL by 1. If the new contents of BL is 1111, the next ROM word will be ignored.                                                                 | A ↔ M<br>B(7:5) ← B(7:5) ♥<br>[I(3:1)];<br>BL ← BL-1<br>Skip on BL=1111        |

| LDI       | 70-7F<br>0111                      | Load Accumulator<br>Immediate (1 cycle)                                        | The 4-bit contents, immediate field I(4:1), of the instruction are placed in accumulator. (See Note below)                                                                                                                     | A ← [I(4:1)]<br>See Note 3                                                     |

| LAX       | 12<br>0001 0010                    | Load Accumulator<br>from X register<br>(1 cycle)                               | The 4-bit contents of the X register are placed in the accumulator.                                                                                                                                                            | A ← X                                                                          |

| LXA       | 1B<br>0001 1011                    | Load X Register from<br>Accumulator (1 cycle)                                  | The contents of the accumulator are transferred to the X register.                                                                                                                                                             | X← A                                                                           |

| LABL      | 11<br>0001 0001                    | Load Accumulator with BL (1 cycle)                                             | The contents of BL register are transferred to the accumulator.                                                                                                                                                                | A ← BL                                                                         |

| LBMX      | 10<br>0001 0000                    | Load BM with X<br>(1 cycle)                                                    | The contents of X register are transferred to BM register.                                                                                                                                                                     | BM ← X                                                                         |

| LBUA      | 04<br>0000 0100                    | Load BU with A<br>(1 cycle)                                                    | The contents of accumulator are transferred to BU register. Also, the contents of currently addressed RAM are transferred to accumulator.                                                                                      | BU ← A, A ← M                                                                  |

NOTE

Only the first occurrence of an LDI in a consecutive string of LDI's will be executed. The program will ignore the remaining LDI's and execute next valid instruction.

#### DATA TRANSFER INSTRUCTIONS (CONT)

| Mnemonics | I/D Bus<br>OP Code<br>Hex & Binary                   | Name                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                          | Symbolic<br>Equation                                                                                                              |

|-----------|------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| XABL      | 19<br>0001 1001                                      | Exchange Accumulator and BL (1 cycle)        | The contents of accumulator and BL register are exchanged.                                                                                                                                                                                                                                                                                                                                                           | A ↔ BL                                                                                                                            |

| XBMX      | 18<br>0001 1000                                      | Exchange BM and X<br>(1 cycle)               | The contents of BM register and X register are exchanged.                                                                                                                                                                                                                                                                                                                                                            | X ↔ BM                                                                                                                            |

| XAX       | 1A<br>0001 1010                                      | Exchange Accumulator and X (1 cycle)         | The contents of accumulator and X register are exchanged.                                                                                                                                                                                                                                                                                                                                                            | $A \leftrightarrow X$                                                                                                             |

| XS        | 06<br>0000 0110                                      | Exchange SA and SB (1 cycle)                 | The 12-bit contents of SA register and SB register are exchanged.                                                                                                                                                                                                                                                                                                                                                    | SA ↔ SB                                                                                                                           |

| CYS       | 6F<br>0110 1111                                      | Cycle SA register and accumulator. (1 cycle) | A 4-bit right shift of the SA register takes place with the four bits which are shifted off the end of SA being transferred into the accumulator. The contents of the accumulator are placed in the left end of SA register.                                                                                                                                                                                         | $A \leftarrow SA(4:1)$<br>$SA(4:1) \leftarrow SA(8:5)$<br>$SA(8:5) \leftarrow SA(12:9)$<br>$SA(12:9) \leftarrow A$                |

| LB **     | CO-CF<br>1st word<br>1100<br>2nd word<br>from page 3 | Load B Indirect<br>(2 cycles)                | Sixteen consecutive locations on ROM page 3 (I2) contain data which can be loaded into the eight least significant bits of the B register by use of any LB instruction. The four most significant bits of B register will be loaded with zeros. The contents of the SB register will be destroyed. This instruction takes two cycles to execute but occupies only one ROM word. (Automatic return) (See Note below.) | SB← SA, SA ← P<br>P(12:5)←00001100<br>P(4:1) ← I1(4:1)<br>BU ← 0000<br>B(8:1) ← [I2(8:1)]<br>P ← SA, SA ← SB<br>See Notes 3 and 4 |

| LBL       | 00<br>1st word<br>0000 0000<br>2nd word              | Load B Long<br>(2 cycles)                    | This instruction occupies two ROM words, the second of which will be loaded into the eight least significant bits of the B register. The four most significant bits of B (BU) will be loaded with zeros. (See Note below)                                                                                                                                                                                            | BU ← 0000<br>B(8:1) ← [I2(8:1)]<br>See Note 3                                                                                     |

| INCB      | 17<br>0001 0111                                      | Increment BL<br>(1 cycle)                    | BL register (least significant four bits of B register) is incremented by 1. If the new contents of BL is 0000, then the next ROM word will be ignored.                                                                                                                                                                                                                                                              | BL ← BL+1<br>Skip on BL=0000                                                                                                      |

| DECB      | 1F<br>0001 1111                                      | Decrement BL<br>(1 cycle)                    | BL register is decremented by 1. If the new contents of BL is 1111, then the next ROM word will be ignored.                                                                                                                                                                                                                                                                                                          | BL ← BL-1<br>Skip on BL = 1111                                                                                                    |

#### NOTE

Only the first occurrence of an LB or LBL instruction in a consecutive string of LB or LBL will be executed. The program will ignore the remaining LB or LBL and execute the next valid instruction. Within subroutines the LB instruction must be used with caution because the contents of SB have been modified.

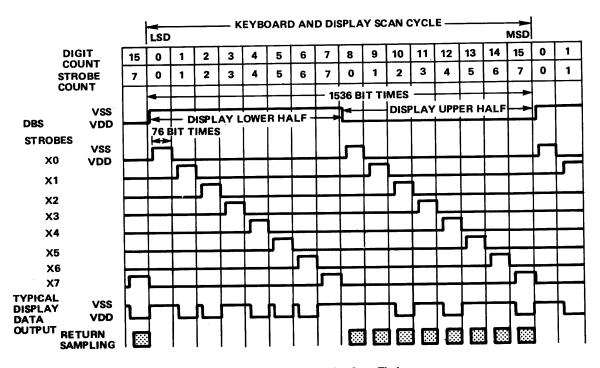

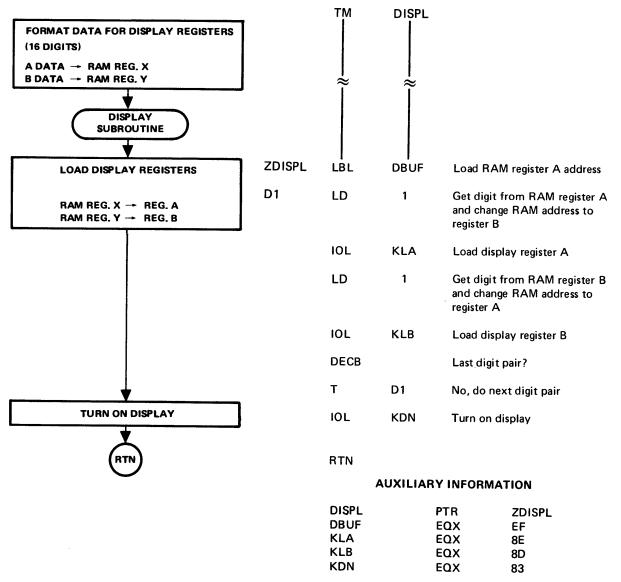

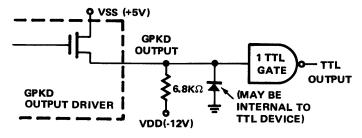

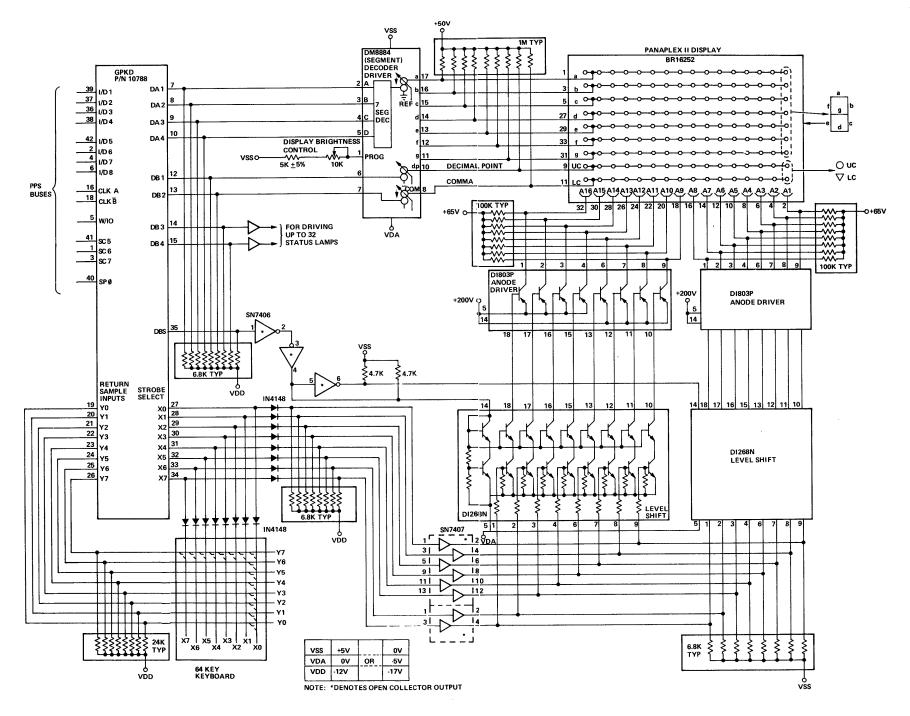

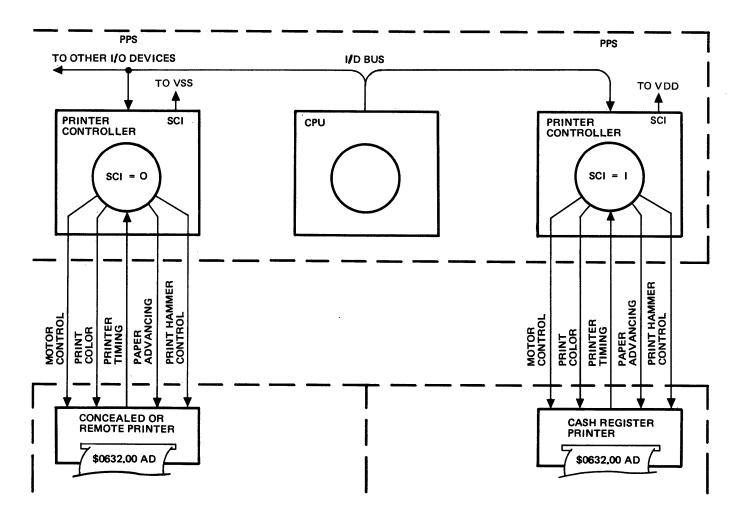

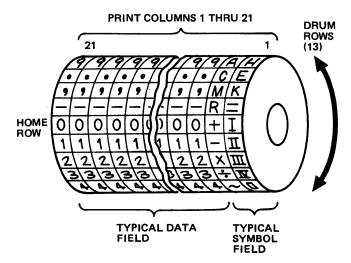

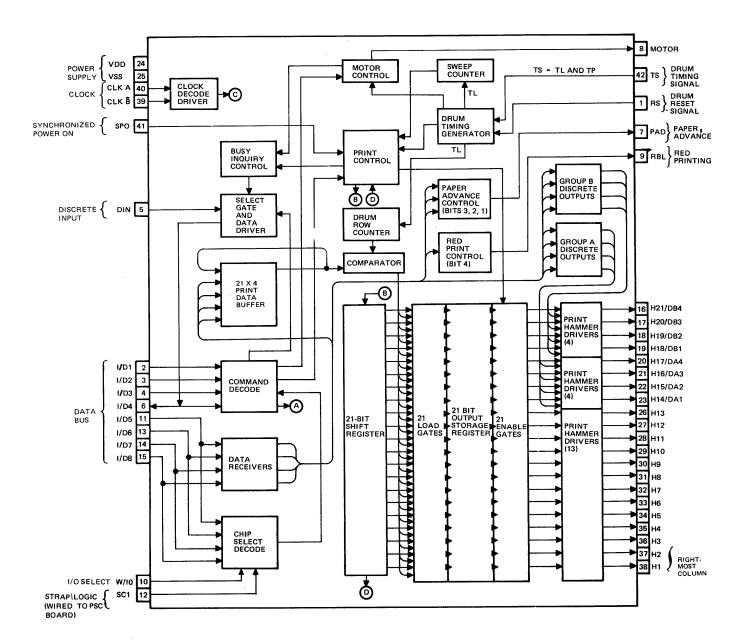

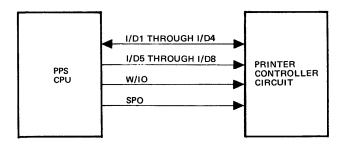

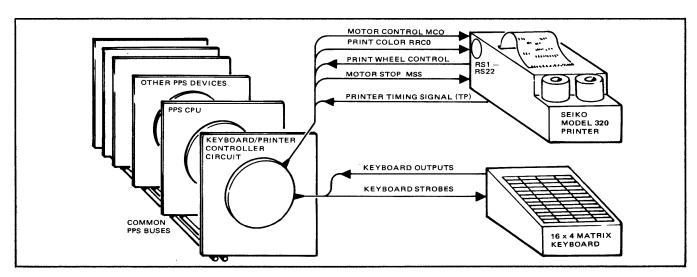

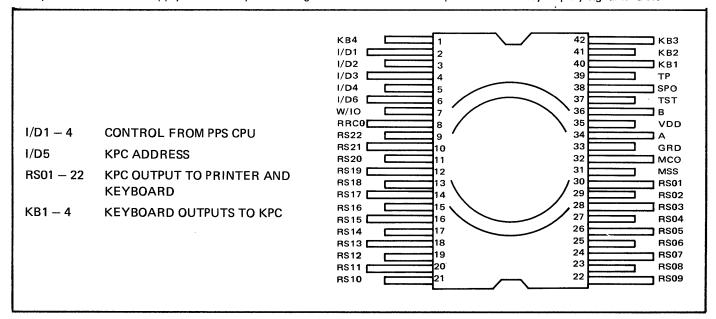

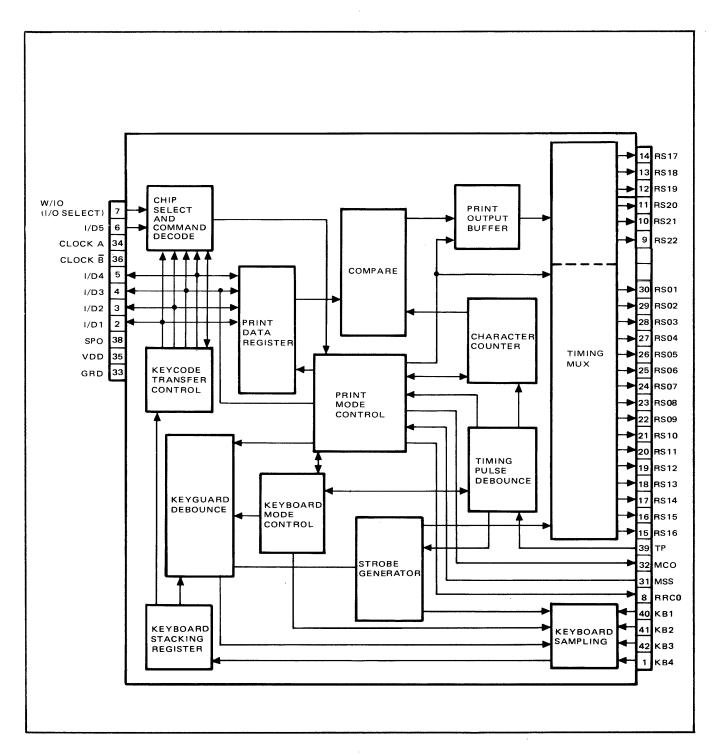

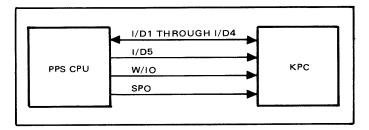

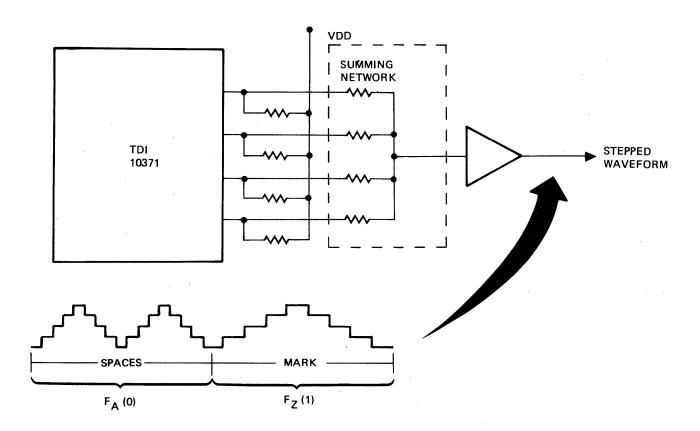

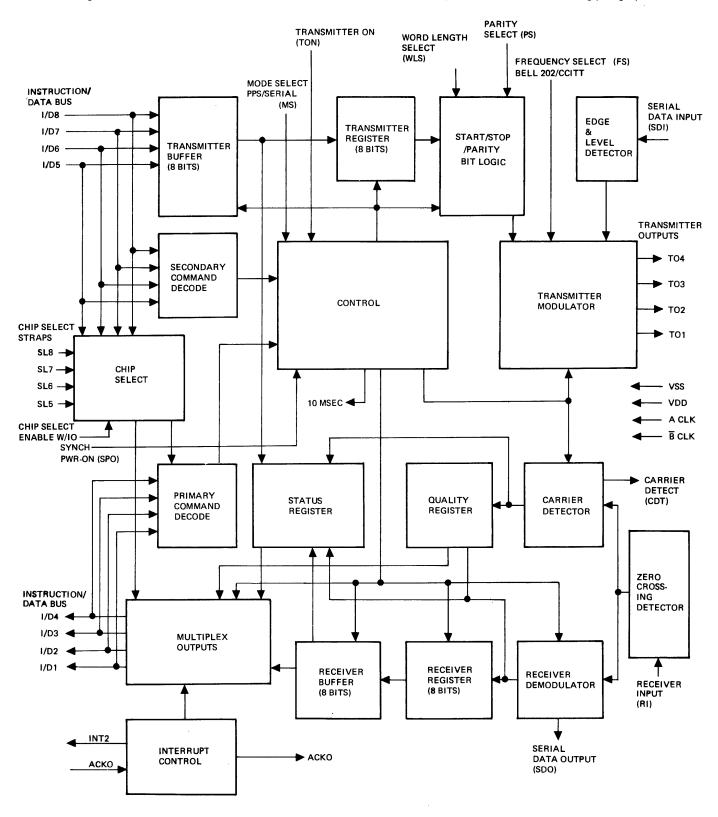

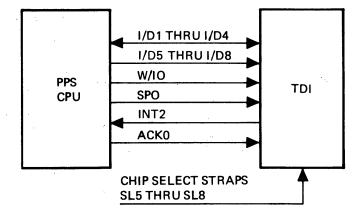

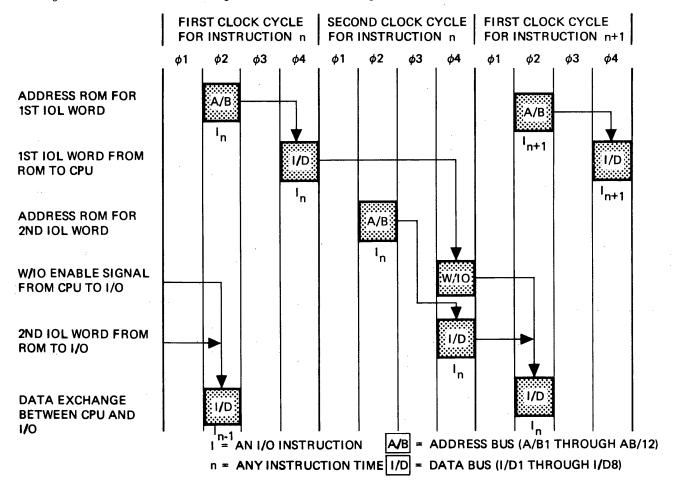

#### CONTROL TRANSFER INSTRUCTIONS