## ROCKWELL PARALLEL PROCESSING SYSTEM (PPS)

PPS-4/1 ONE-CHIP MICROCOMPUTERS PRODUCT DESCRIPTION

AUGUST 1978

REVISION: 5

DOCUMENT NO. 29410 N41

# SERIES MM76 ONE-CHIP MICROCOMPUTERS

#### **PPS-4/1 SUPPORTING DOCUMENT**

The following documents provide related design information aiding implementation of this device in your system:

- MM76 Programming Manual Document No. 29410N44

- PPS-4/1 Prototyping using the PROM Evaluation Module Document #29410N20

- PPS-4/1 Operator's Manual for Universal Assemulator Document #29400N37

### TABLE OF CONTENTS

Page

| PPS-4/1, SERIES MM76 SINGLE CIRCUIT MICROCOMPUTER SYSTEMS |

|-----------------------------------------------------------|

| Introduction                                              |

| Features                                                  |

| System Description                                        |

| Accumulator and Arithmetic Logic Unit (A. ALU, and C)     |

| A Ruffer                                                  |

| Driver and Receiver Circuits                              |

| B Buffer                                                  |

| 16 x 8 Decode Matrix                                      |

| S Register - Serial Input/Output - Shift Counter          |

| Discrete Input/Output Ports (DI/O0 through DI/O9)         |

| Conditional Interrupts (INTO and INT1)                    |

| Channel 1                                                 |

| Channel 2                                                 |

| Program Counter (P)                                       |

| SA Register                                               |

| Read Only Memory (ROM)                                    |

| Instruction Decode                                        |

| Data Address Register (BU and BU)                         |

| Data Memory (RAM)                                         |

| Clock Control (VC, CLKIN, EXCLK, and Oscillator)4         |

| PPS-4/1 Testability (Test)                                |

| Power Supply                                              |

| Power On Reset (PO)                                       |

| PPS-4/I MM76 Instructions                                 |

| Multifunction Instructions                                |

| Decimal Addition                                          |

| Example                                                   |

| Electrical Interface                                      |

| Discrete I/O Ports                                        |

| Discrete I/O Ports                                        |

| Parallel I/O Ports (RIO1-RIO4)                            |

| Parallel I/O Ports (RIO5-RIO8)                            |

| Parallel Input Ports (PI1-PI4)                            |

| Parallel Input Ports (PI5-PI8)                            |

| Conditional Interrupts (INTO and INT1)                    |

| Serial 1/O                                                |

| Mask Options                                              |

| Interrupt Options                                         |

| Programmable Logic Array (PLA) Options                    |

| System Development Aids                                   |

| Assemulator                                               |

| XPO-1                                                     |

| Development Circuit and Evaluation Modules                |

| Software and Training                                     |

| The Ultimate Lowest Cost System                           |

| The PPS-4/1 Application Areas                             |

| Potential Applications                                    |

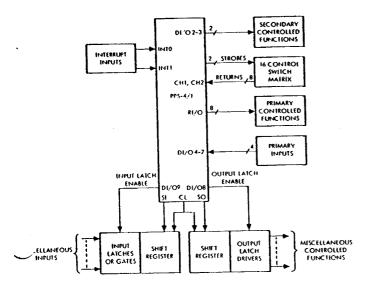

| General Purpose Monitor/Controller                        |

| Input Examples                                            |

| Output Examples                                           |

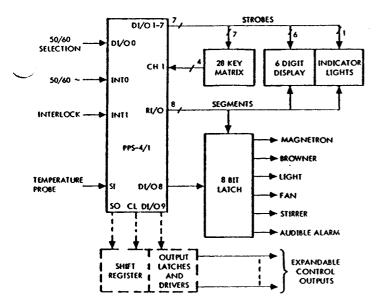

| Microwave Oven Controller                                 |

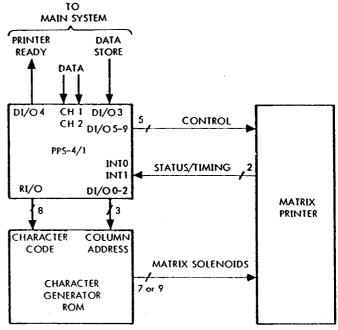

| Matrix Printer Controller                                 |

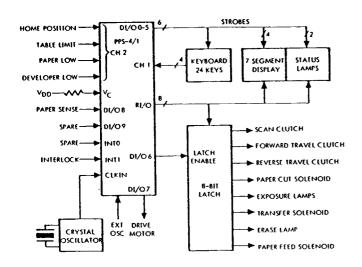

| Copier Controller                                         |

| Credit Checking Terminal                                  |

| Analog Interface                                          |

| Low Cost Cash Register                                    |

| Applications Summary                                      |

| Appreciations somming                                     |

## TABLE OF CONTENTS (continued)

|                                                                                                                                                                                                                                                                                                                                 | Page                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| APPENDIX A - MM76E EXTENDED INSTRUCTION MEMORY VERSION                                                                                                                                                                                                                                                                          |                                               |

| Introduction                                                                                                                                                                                                                                                                                                                    | A-1<br>A-1<br>A-1                             |

| APPENDIX B - MM75 28-PIN PACKAGE VERSION                                                                                                                                                                                                                                                                                        |                                               |

| Introduction  MM75 Modified Features  S Register - Serial Input/Output - Shift Counter  Discrete Input/Output Ports  Conditional Interrupts  Channel 2  Clock Control  MM75 Development Aids  Electrical Interface                                                                                                              | B-1<br>B-1<br>B-1<br>B-1<br>B-1               |

| APPENDIX C - MM76C HIGH SPEED COUNTER VERSION                                                                                                                                                                                                                                                                                   |                                               |

| Introduction.  MM76C Additional/Modified Features  System Description  General  Counter Operation and Control  Control Flip-Flops Operation.  Control Register Functions.  Clock Control (XTLIN, XTLOUT, XPWR, and Oscillator.  PPS-4/1 MM76C Instructions  Electrical Interface.  MM76C System Development Aids.  Applications | C-1<br>C-3<br>C-4<br>C-5<br>C-6<br>C-7<br>C-9 |

| APPENDIX D - MM76L AND MM76EL LOW VOLTAGE, LOW POWER VERSIONS                                                                                                                                                                                                                                                                   |                                               |

| Introduction                                                                                                                                                                                                                                                                                                                    | D-1<br>D-1                                    |

## LIST OF ILLUSTRATIONS

| igure |                                                        | Page   |

|-------|--------------------------------------------------------|--------|

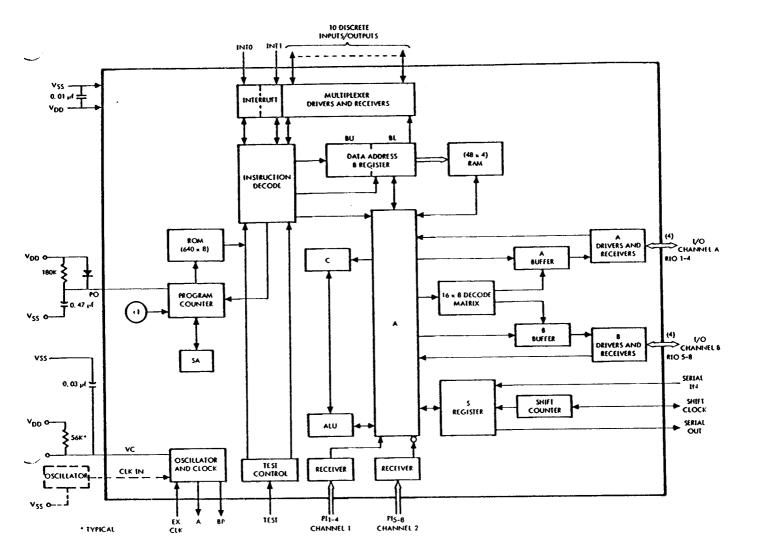

| 1     | PPS-4/1 MM76 System Block Diagram                      | . 2    |

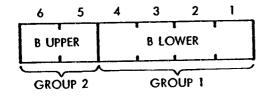

| 2     | Address Register Organization                          | . 9    |

| 3     | Data Memory Map for PPS-4/1 MM76                       | . 10   |

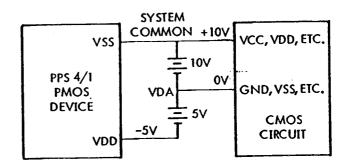

| 4     | Typical PMOS to CMOS Power Interface                   | . 12   |

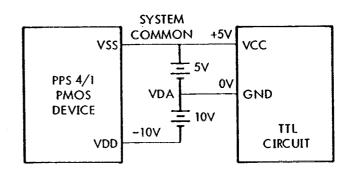

| 5     | Typical PMOS to TTL Power Interface                    | . 12   |

| 6     | TTL to PPS-4/1 Synchronized Input Receiver Interface   | . 14   |

| 7     | PPS-4/1 Output Driver to TTL Interface                 | . 14   |

| 8     | Timing of Serial Data Input/Output                     | . 16   |

| 9     | Typical Clock Waveforms with External 56K Ohm Resistor | . 16   |

| 10    | PPS-4/1 General Purpose Monitor/Controller             | . 22   |

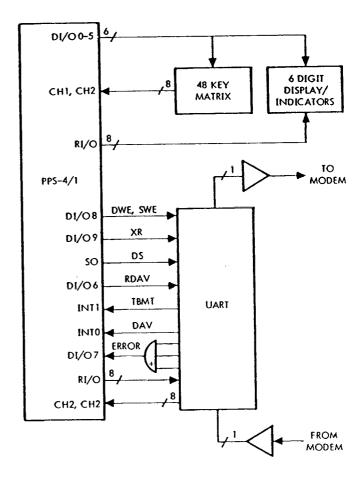

| 11    | PPS-4/1 Microwave Oven Controller                      | . 23   |

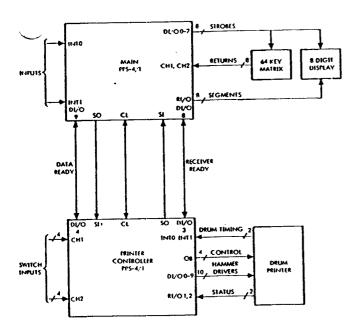

| 12    | PPS-4/1 Matrix Printer Controller                      | . 23   |

| 13    | PPS-4/1 Copier Controller                              | . 24   |

| 14    | PPS-4/1 Credit Checking Terminal (Parallel Interface)  | . 24   |

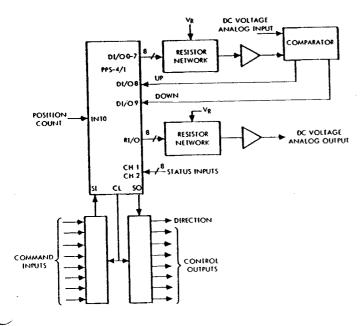

| 15    | PPS-4/1 Analog Interface                               | . 25   |

| 16    | PPS-4/1 Low Cost Cash Register                         | . 26   |

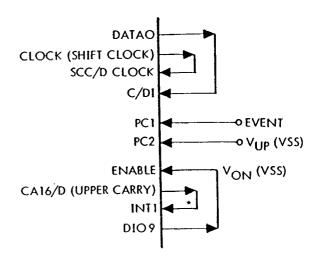

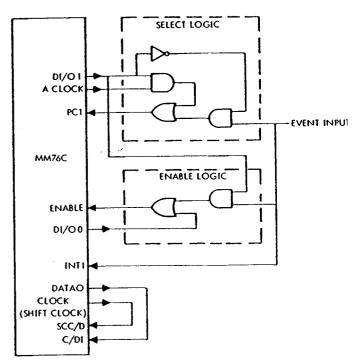

| C-1   | PPS-4/1 MM76C Block Diagram                            | . C-2  |

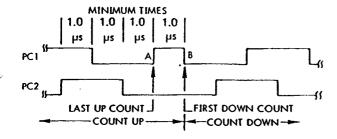

| C-2   | Count Reversal Timing                                  | . C-3  |

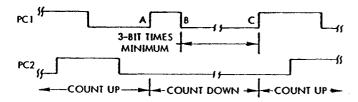

| C-3   | Count Double Reversal Timing                           | . C-3  |

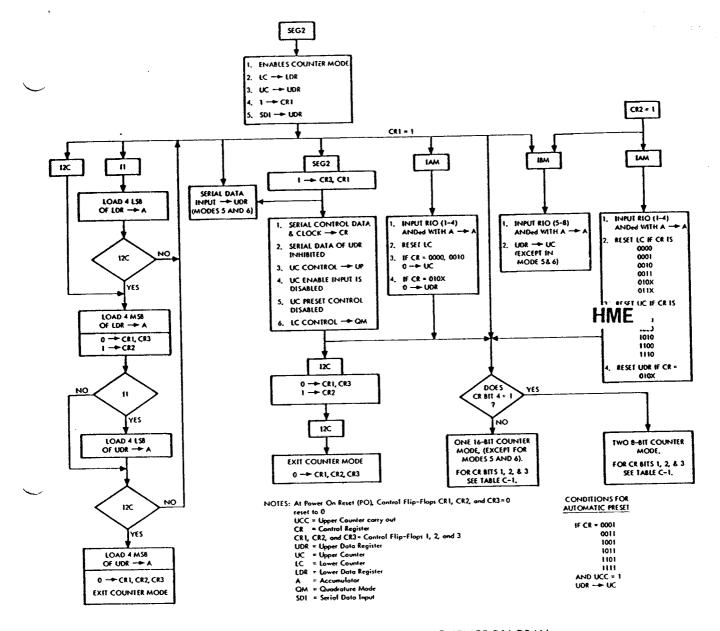

| C-4   | Operation Example, Sequence Diagram                    | . C-4  |

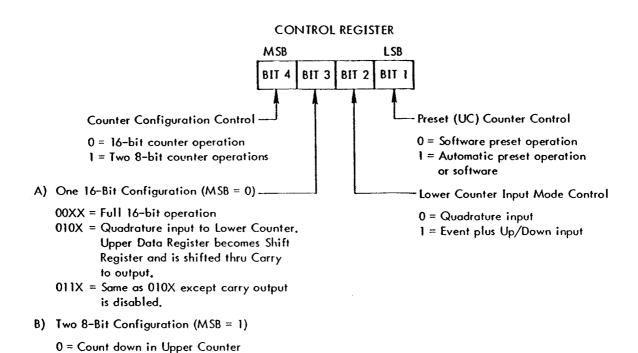

| C-5   | Control Register Operation                             | . C-5  |

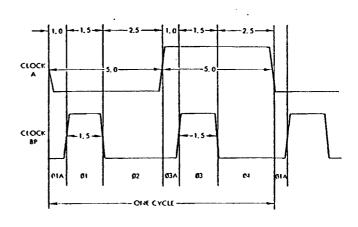

| C-6   | Typical Clock Waveform                                 | . C-/  |

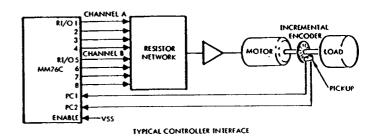

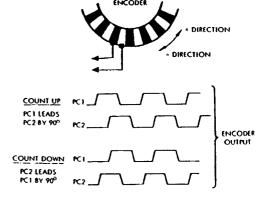

| C-7   | Motor Speed/Position Controller                        | . C-13 |

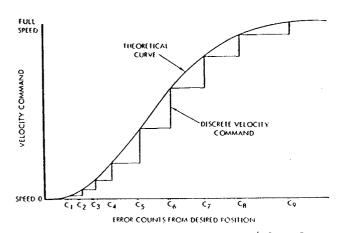

| C-8   | DC Motor Velocity/Position Deceleration Profile        | . C-13 |

| C-9   | Event and Extended Event Counter                       | . C-14 |

| C-10  | High-Low Frequency Counter                             | . C-15 |

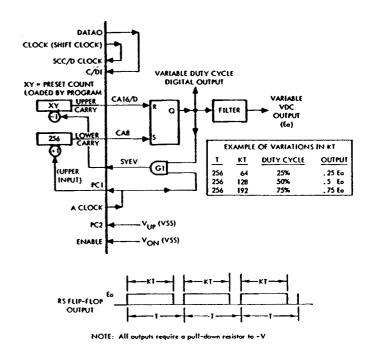

| C-11  | Variable Duty Cycle Setup                              | . C-17 |

| D-1   | MM76L and MM76EL Pin Configuration                     |        |

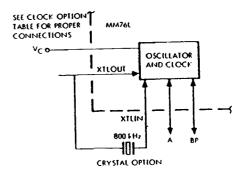

| D-2   | MM76L and MM76EL Clock Circuit                         | . D-1  |

### LIST OF TABLES

| able |                                                                              | Page  |

|------|------------------------------------------------------------------------------|-------|

| 1    | PPS-4/1 MM76 Instruction Set                                                 | . 5   |

| 2    | Data Address Modification                                                    | . 9   |

| 3    | ROM Map                                                                      | . 11  |

| 4    | MM76 Electrical Specifications                                               | . 13  |

| 5    | PPS-4/1 MM76 Signals ( Part No. A76XX)                                       | . 17  |

| 6    | PPS-4/1 MM76 Personality Module Development Circuit Signals (Part No. A7699) | . 18  |

| 7    | PPS-4/1 Development Circuit Signals (Part No. A7698)                         | . 19  |

| B-1  | MM75 Electrical Specifications                                               | . B-2 |

| B-2  | PPS-4/1 MM75 Signals (Part No. A75XX)                                        | . B-3 |

| C-1  | Description of the 14 Modes of Counter Operation                             | . C-6 |

| C-2  | PPS-4/1 MM76C Input/Output Instruction Set                                   | . C-/ |

| C-3  | PPS-4/1 MM76C Electrical Specifications                                      | . C-7 |

| C-4  | PPS-4/1 MM76C Signals (Part No. A79XX)                                       | . C-1 |

| C-5  | PPS-4/1 MM76C Development Circuit (Part No. A7999) Signals                   | . C-1 |

| D-1  | MM76L and EL Electrical Specifications                                       | . D-1 |

| D-2  | PPS-4/1 MM76L/MM76EL Signals (Part Nos. B76XX, B86XX)                        | . U-4 |

| D-3  | PPS-4/1 MM76L/MM76EL Development Circuit Signals (Part No. B7699)            | . D-5 |

| D-4  | PPS-4/1 MM76L/MM76EL Development Circuit Signals (Part No. B7698)            | . D-6 |

## PPS-4/1, SERIES MM76 SINGLE CIRCUIT MICROCOMPUTER SYSTEMS

#### INTRODUCTION

The PPS-4/1 microcomputers, Series MM76 are members of a growing family of single circuit microcomputers from Rockwell International. The circuits contain a read only memory for the program memory functions, a random access memory for data, parameter and working storage, and a sophisticated input/output capability which provides a high degree of flexibility for microcomputer and controller applications. The MM76 is the basic device described. The appendices describe the dedicated features of other devices in this series.

#### **FEATURES**

- MM76 640 8-bit bytes of program memory (5120 bits)

- 48 4-bit data words (192 bits)

- Automatic code conversion

- Two 4-bit input channels

- Two 4-bit input/output channels

- 10 discrete input/output lines

- Clocked simultaneous serial input/output capability

- Externally controlled serial input/output capability

- Pulse output capability

- Two interrupt request input lines

- TTL and CMOS compatible

- Arithmetic logic unit and three working registers

- On-chip resistor controlled 80 kHz (nominal) clock generator which may be externally synchronized

- One clock cycle execution (nominal 12.5 microseconds) for most instructions

- Large instruction set over 50 instructions

- Multifunction instructions increase throughput

- Single power supply operation (15 volts ±5%)

- Compact quad-in-line 42-pin package

- Sophisticated development aids

- General Electric Software Assembler

- Development Circuit with PROM Module for Program Memory

- PPS Universal Assemulator with PPS-4/1 Personality

Board for Program and Hardware Development

- XPO-1, PPS-4/1 Emulator

(System Development Microcomputer)

- Scheduled and Special Training Courses

- International Applications Engineering Support

- Low power (75 milliwatts typical, 125 milliwatts max)

#### SYSTEM DESCRIPTION

The PPS-4/1, Series MM76 circuits have been designed to be used by themselves, in conjunction with other PPS-4/1 circuits, or in conjunction with other PPS families of circuits (PPS-4/2, PPS-4, or PPS-8). The series MM76 may be used as compact stand-alone microcomputers, as a low cost special controller, as a programmable peripheral controller for one of the larger PPS systems, as a sophisticated appliance controller, or as a universal logic element. The series MM76 as a universal logic element can economically perform functions such as counting, time delays, comparisons, sequencing, function generating, etc., to control a set of output lines based upon conditions presented on a set of input lines.

Any of the PPS-4/1 systems may be operated in tandem to perform parallel processing functions in multi-microcomputer configurations.

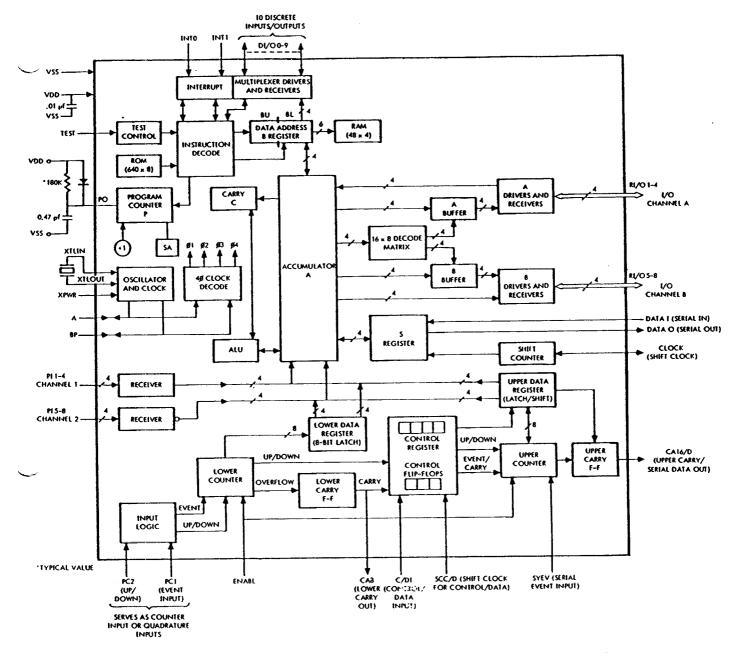

A block diagram of the PPS-4/1 MM76 is shown in Figure 1.

## ACCUMULATOR AND ARITHMETIC LOGIC UNIT [A. ALU, AND C]

The primary working register in the PPS-4/1 MM76 is the Accumulator (A Register). It is the Accumulator which ties with the Arithmetic Logic Unit (ALU) and the carry flip-flop (C) to perform either binary or decimal arithmetic. Constants may be loaded into the Accumulator by appropriate instructions from the read only memory or variable data may be loaded from, or exchanged with the rondom access memory (RAM) under control of the Data Address Register (B). The Accumulator is also the primary path for 4-bit parallel or serial input or output data although the S Register may also be involved.

#### A BUFFER

The contents of the Accumulator may be output for control or data transfer purposes through the A Buffer via the Output A command. The A Buffer consists of four latched open drain circuits which will hold the data output until new data is output or power is turned off. The electrical characteristics of these and other signal lines are in the section on Electrical Interface.

Note: The evaluation circuit for the PPS-4/1 (Part No. A7699) is identical to the PPS-4/1 MM76 production circuits (Part No. A76XX) except that, in place of the ROM, terminals are brought out to an external memory and control system.

Figure 1. PPS-4/1 MM76 SYSTEM BLOCK DIAGRAM

#### DRIVER AND RECEIVER CIRCUITS

The outputs of each of the latches in the A Buffer, B Buffer and discrete input output flip-flops are through open drain drivers which drive to either the VSS logic level or float. When power is applied, the power on reset circuit (PO) causes all of the outputs to be automatically set to a float condition. (All output flip-flops are reset.)

out signals may share the same lines as outputs for the and B channels (RI/O 1-8) and the discrete input/output lines. To use one of these lines as an input, it is necessary to set the output on that line into a float condition. The external signal may then either take the

line high to VSS or to the appropriate low logic level. The input command, in effect, samples the logic level on the pin and inputs it appropriately.

The mechanization of the PPS-4/1 MM76 allows a software masked input capability. To mask out any input bits, the Accumulator bit in that bit position is set to 0. The external input in that position will always be input as a zero while other bits input to bit positions pre-conditioned by a 1 in the Accumulator will be at logic one or zero levels as determined by the external system. This is in effect a logical AND between the initial contents of the Accumulator and the input signal.

#### **B BUFFER**

The output B instruction causes the contents of the Accumulator to be transferred to the B Buffer. The B Buffer comprises four latches which will output the last bit pattern loaded until either a new Output B command is executed or power is turned off. The power on reset signal resets all of the latches so the outputs float.

#### 16 x 8 DECODE MATRIX

The MM76 microcomputer can output any of 16 eight-bit codes, as determined by the four-bit contents of the addressed memory and the two's complement of those four bits in the Accumulator. The carry flip-flop may also be used to set one of the output terms. The 16 eight-bit codes in the decode matrix are specified by the user at the time he orders the microcomputer.

The SEG1 and SEG2 instructions cause the lower and upper four bits of the selected decode matrix term to be output on I/O Channels A and B, respectively.

The four-bit contents of the addressed memory and its complement in the Accumulator are decoded to select which of the 16 eight-bit will be output by the SEG1 and SEG2 instruction.

The MM76 development circuits (A7698, A7699, A7999, B7698 and B7699) have a BCD-to-seven-segment-display conversion mask programmed in the decode matrix. Hexadecimal digits F,E,...1,0 in memory and their associated complements 0,1...F in the Accumulator produce segment control signals for 0 through 9, A, -, P, d, E and "blank", respectively. In the development circuits, the carry flip-flop controls RI/O8.

#### S REGISTER - SERIAL INPUT/OUTPUT - SHIFT COUNTER

The S Register is a 4-bit parallel-in/parallel-out, serial shift register which is used as either an auxiliary storage register or a buffer for the simultaneous serial-in/serial-out capabilities in the microcomputer. The 4 bits to be serially output are loaded into the S Register either by exchanging the contents of the Accumulator and the S Register or directly loading the S Register from the Accumulator. The state of the serial output line is immediately set by the contents of the most significant bit position. When an Input/Output Serial instruction is executed, or an external shift clock input is provided the four bit contents of the S Register are shifted out (most significant bit first). The data shift rate is under control of the Shift Counter, and is one-half the rate of the internal clock frequency when the IOS instruction is used. The Input/Output Serial instruction also causes the Shift Counter to provide four shift clock signals to the external system. Under external shift control on the same shift clock line, the shift rate may be any value at or below the clock frequency. Both the serial data and shift clock outputs are open drain drivers which are set to the float state when power is turned on.

At the same time that the 4-bit data is being shifted out through the serial output line, 4 bits of data are shifted into the S Register from the serial input line. An exchange of the Accumulator and S Register brings the 4 bits of serial input data into the Accumulator where it can be processed or stored. The S Register may be simultaneously reloaded if more than 4 bits of data are being transmitted.

When the external clocking mode is used it may be necessary for the system designer to establish a handshake protocol to establish when data is to be moved and when the move is completed.

## DISCRETE INPUT/OUTPUT PORTS (DI/OO THROUGH DI/O9)

There are ten discrete input or output lines. Buffer flip-flops associated with all ten of these channels may be individually set, or reset under program control. They are all reset when power is applied. There is a buffer flip-flop associated with each of these channels which is selected by the least significant 4 bits of the Data Address (B) Register. A Set Output Selected instruction causes the selected output to be at the VSS level and a Reset Output Selected instruction causes it to float. When the output is floating, an input signal level on that port may be tested by a Skip on Input Selected Low instruction. When the Buffer flip-flops are not used specifically for input/output functions, they may be used as one bit status registers. In this case external pull up resistors connected to VDD must be used.

#### CONDITIONAL INTERRUPTS (INTO AND INT1)

The conditional interrupt request lines may be used in a number of different ways. These ports are different from the discrete input/output channels in that they may be addressed directly and not by the B Lower portion of the B Register.

To test the state of the signal on the input line it is not necessary to set a flip-flop to any predetermined state as there is no output driver on these signal lines. The level on these two lines may be tested directly by an INTOL or INT1H instruction for INTO and INT1 inputs respectively without any pre-conditioning. This gives the PPS-4/1 a pseudo interrupt capability by allowing a direct test of the input signal. The INTOL instruction causes the next instruction to be skipped if the input on INTO is low and the INT1H instruction will cause it to skip if the signal on the INT1 line is high.

Another difference in these two signals is that they may be used to detect a pulse input of a duration longer than one clock cycle. In this case, for INT1 the associated flip-flop is preset to the set state by testing so that any subsequent incoming negative transition pulse on INT1 which lasts longer than one clock cycle will reset the flip-flop. The state of the flip-flop may then be tested by addressing it with a DIN1 instruction which will cause the next instruction to be skipped if the flip-flop is reset. Testing the

p-flop automatically restores it to the set state so that is ready for the next test via the DIN1 instruction.

'NO instruction similarly may be used to test for a strave transition or pulse on INTO.

#### IANNEL 1

nannel 1 is a 4-bit input port which automatically loads a input value to the contents of the Accumulator.

#### ANNEL 2

nannel 2 is a 4-bit input port which on command replaces e contents of the Accumulator with the complement of e value on the input lines. If the input value is from L or CMOS logic, the inversion causes the equivalent live to appear in the Accumulator.

#### OGRAM COUNTER (P)

e 10-bit Program Counter is set to a specific initial value exadecimal address ICO) when power is applied to the crocomputer. The contents of the Program Counter dresses read-only memory to identify the specific struction to be executed. Then, unless the instruction a transfer instruction, the contents of the Program ounter are incremented so that the next instruction may

rected. This process repeats until a transfer or transfer or transfer or transfer instruction is executed. The transfer instruction in the sex significant 6 bits in the leaving the upper bits fixed or may set the implete 10 bits with a Transfer Long (TL) instruction.

milar alternatives are available for the transfer and mark structions which are used to call subroutines. The TM struction selects one of 64 locations in a specific area at the TML sets the complete 10 bits. These instructions, owever, mark a return location so that the subroutines ay return to the next instruction location after the one lat called it. This is accomplished by incrementing the ogram Counter prior to setting the new value into it, and saving the incremented value in the SA Register.

#### **A REGISTER**

then a subroutine call is executed by one of the transfer nd mark instructions, the contents of the SA Register are eplaced by the incremented value of the Program Counter.

When a return instruction is executed in the subroutine, ne contents of the SA Register are popped into the Program Jounter.

#### \_\_D ONLY MEMORY (ROM)

he Read Only Memory (ROM) provides the storage for nstructions and constants (as immediate field portions of

instructions) for the microcomputer. It contains 640 instruction bytes of 8 bits each. It is controlled by the Program Counter to read out each instruction to be executed.

#### INSTRUCTION DECODE

The instructions are decoded in the Instruction Decode circuits which then issue control signals to all appropriate portions of the microcomputer as necessary to perform the desired operations.

#### DATA ADDRESS REGISTER (BU AND BL)

The Data Address Register is 6 bits in length and is made up of two segments, B Upper (BU) and B Lower (BL). Data memory in RAM is addressed by all 6 bits and discrete input/output ports are addressed by the 4 bits in BL when the value in B Upper is three.

The BL portion may be automatically incremented or decremented and tested for overflow or underflow by the Exchange Increment and Skip, Exchange Decrement and Skip, Increment B, or Decrement B instructions.

#### DATA MEMORY (RAM)

The Random Access Memory (RAM) used for data memory consists of 48 characters of 4 bits each. This memory is used to buffer input or output values, hold intermediate results and also may be used as registers used for timers, counters, comparators, etc. when the microcomputer is used as a universal logic element.

## CLOCK CONTROL (VC, CLKIN, EXCLK, AND OSCILLATOR)

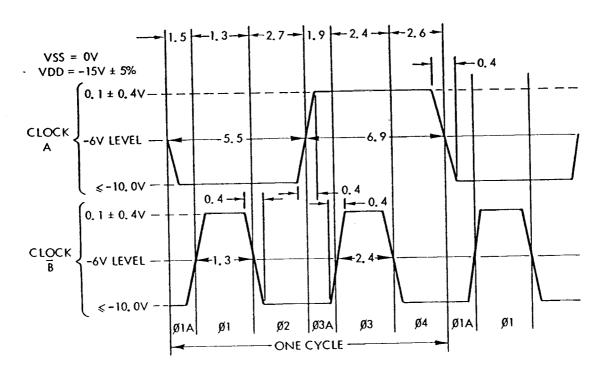

The microcomputer may be driven by either its internal clock or an external clock source. Regardless of the source, a resistor must be connected between the VC input and VDD. The resistor value may be used to slightly vary the operating frequency; typical values are 56K ohms for 80 kHz and 47K ohms for 100 kHz.

The nominal 80 kHz internal clock may be used to drive the microcomputer in systems where precise timing is not required. The internal clock is selected by tying the CLKIN pin to VDD and the EXCLK pin to VSS. The A and  $\overline{B}$  clock terms are brought out so external logic can be synchronized.

An external frequency reference in the range 40 kHz to 100 kHz may be used in systems when precise timing is required. When the EXCLK pin is tied to VDD, the microcomputer will be driven by an external square wave oscillator input through the CLKIN pin.

A specific definition of the clock waveforms is discussed in the section on Electrical Interface.

#### PPS-4/1 TESTABILITY (TEST)

Another advantage of the PPS-4/1 microcomputer family is testability both at the factory and user levels. When a test state is indicated by the TEST input line, the PPS-4/1 goes into a test mode which tests ROM and allows testing of the RAM and instruction logic.

#### **POWER SUPPLY**

When inputs and outputs interface with other PMOS devices, or CMOS devices, VSS = GND and VDD =  $-15V \pm 5\%$  provide proper interface levels. When interfacing with TTL devices, VSS should be +5 and VDD at -10 volts.

#### POWER ON RESET [PO]

The PO signal is derived from an external resistor, diode, and capacitor pulse shaping network which is tied to the power supply as shown in Figure 1. When power comes on, this circuit automatically sets the Program Counter to a fixed starting location and all outputs are set to a "float" (-V) state. The Program Counter then initiates the first instruction (which must be a Set Carry, Reset Carry or NOP instruction) to be read from the read only memory (ROM) into the instruction decode logic. After executing the first instruction the Program Counter increments so that the second and subsequent instructions may be recalled from memory and executed.

#### PPS-4/1 MM76 INSTRUCTIONS

The PPS-4/1 MM76 has an extremely sophisticated instruction set which is summarized in Table 1.

Table 1. PPS-4/1 MM76 INSTRUCTION SET

| Op Code          | Bytes        | Cycles | Description                                                                                                                          |

|------------------|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| RAM Addressing   | Instructions |        |                                                                                                                                      |

| XAB              | 1            | 1      | Exchange Accumulator with B Lower (least significant 4 bits)                                                                         |

| LBA              | 1            | 1      | Load B Lower from Accumulator                                                                                                        |

| *LB**            | 1            | 1      | Load B Upper with zero and B Lower with immediate field                                                                              |

| *EO8**           | 1            | 1      | Exclusive OR B-Upper with two bit immediate field                                                                                    |

| †*LBL**          | 2            | 2      | Load B Register Long with 6 bits (4 bits 1st byte, 2 bits 2nd byte) immediate field. This instruction should not be skipped.         |

| †*INCB           | 2            | 2      | Increment B Lower and modify B Upper with 2 bit immediate field;<br>Skip if BL counts to 0. This instruction should not be skipped.  |

| †*DECB           | 2            | 2      | Decrement B Lower and modify B Upper with 2 bit immediate field;<br>Skip if BL counts to 15. This instruction should not be skipped. |

| Bit Manipulation | Instructions |        |                                                                                                                                      |

| * SB             | 1            | 1      | Set bit in word in memory. Specific bit designated by 2 bit immediate field and specific word addressed by B Register                |

| *RB              | 1            | 1      | Reset bit in word in memory. Specific bit designated by 2 bit immediate field and specific word addressed by B Register              |

| * SKBF           | 1            | 1      | Skip on designated bit in addressed memory when bit is false (zero).  Bit is selected by 2-bit immediate field.                      |

Table 1. PPS-4/1 MM76 INSTRUCTION SET (continued)

| Op Code            | Bytes           | Cycles   | Description                                                                                                                                |  |

|--------------------|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| Kegister to Regist | er Instructions | <u> </u> |                                                                                                                                            |  |

| XAS                | 1               | 1        | Exchange Accumulator and S Register contents                                                                                               |  |

| LSA                | 1               | 1        | Load S Register from Accumulator                                                                                                           |  |

| Register Memory    | Instructions    |          |                                                                                                                                            |  |

| *[                 | 1               | 1        | Load Accumulator from memory and modify B Upper with 2-bit immediate field                                                                 |  |

| *X                 | 1               | 1        | Exchange Accumulator with memory and modify B Upper with 2-bit immediate field                                                             |  |

| *XDSK              | 1               | 1        | Exchange Accumulator with memory and modify B Upper with 2-bit immediate field; Decrement B Lower and skip if BL counts to 15              |  |

| *XNSK              | 1               | 1        | Exchange Accumulator with memory and modify B Upper with 2-bit immediate field; increment B Lower and skip if BL counts to 0               |  |

| Arithmetic Instru  | ctions          |          |                                                                                                                                            |  |

| Α                  | 1               | 1        | Add memory to Accumulator (carry not used or set)                                                                                          |  |

| AC                 | 1               | 1        | Add memory and carry to Accumulator; form sum and carry                                                                                    |  |

| ACSK               | 1               | 1.       | Add memory and carry to Accumulator; skip if No carry is generated                                                                         |  |

| ASK                | 1               | 1        | Add memory to Accumulator and skip if No overflow occurs (carry not used or set)                                                           |  |

| DC                 | 1               | 1        | Decimal correct (same as AISK 6 so it must always be followed by NOP)                                                                      |  |

| COM                | 1               | 1        | Complement Accumulator                                                                                                                     |  |

| RC                 | 1               | 1        | Reset carry                                                                                                                                |  |

| \$C                | 1               | 1        | Set carry                                                                                                                                  |  |

| SKNC               | 1               | 1        | Skip on no carry                                                                                                                           |  |

| *LAI***            | 1               | 1        | Load Accumulator with contents of immediate field                                                                                          |  |

| *AISK              | 1               | 1        | Add accumulator and immediate field, skip on no overflow. No carry is set or used.                                                         |  |

| ROM Addressing     | Instructions    | <u> </u> |                                                                                                                                            |  |

| RT                 | 1               | 2        | Return from subroutine                                                                                                                     |  |

| RTSK               | 1               | 2        | Return from subroutine and Skip first instruction of one or two bytes in length. Do not skip macro instructions marked with a <sup>†</sup> |  |

| _ т                | 1               | 2        | Transfer on–page to 6 bit immediate field location                                                                                         |  |

| NOP                | 1               | 1        | No operation                                                                                                                               |  |

|                    | 1               | 1        |                                                                                                                                            |  |

Table 1. PPS-4/1 MM76 INSTRUCTION SET (continued)

| Op Code           | Bytes            | Cycles    | Description                                                                                           |

|-------------------|------------------|-----------|-------------------------------------------------------------------------------------------------------|

| ROM Addressing    | Instructions (co | ontinued) |                                                                                                       |

| TL .              | 2                | 3         | Transfer Long off page to pages 0 through 7 (addresses #000 thru #1FF)                                |

| тм                | 1                | 2         | Transfer and Mark to special subroutine pages SRO (addresses #3CO thru #3FF)                          |

| TML               | 2                | 3         | Transfer and Mark Long to subroutine on pages 0 through 7 (addresses #000 thru #1FF)                  |

| Logical Comparis  | on Instructions  |           |                                                                                                       |

| SKMEA             | 1                | 1         | Skip on memory equals Accumulator                                                                     |

| *SKBEI            | 2                | 2         | Skip on B Lower equals immediate field                                                                |

| *SKAEI            | 2                | 2         | Skip on Accumulator equals immediate field                                                            |

| Input/Output Inst | ructions         |           |                                                                                                       |

| sos               | 1                | 1         | Set output, bit selected by B Lower (B Upper = 3) to VSS                                              |

| ROS               | 1                | ī         | Reset output, bit selected by B Lower (B Upper = 3) to -V                                             |

| SKISL             | 1                | 1         | Skip on Input Selected Low on bit selected by B Lower (B Upper = 3) Bit sampled during prior cycle.   |

| IBM               | 1                | 1         | Input Channel B ANDed with Accumulator, results to Accumulator                                        |

| ОВ                | 1                | 1         | Output from Accumulator to Channel B                                                                  |

| IAM               | 1                | 1         | Input Channel A, ANDed with Accumulator, results to Accumulator                                       |

| OA                |                  |           | Output from Accumulator to Channel A                                                                  |

| 108               | 1                | 1         | Serial input and output from S — shifting takes 8 cycles concurrent with other instruction operations |

| 11                | 1                | 1         | Input Channel 1 to Accumulator                                                                        |

| I2C               | 1                | 1         | Input Channel 2 to Accumulator and complement                                                         |

| INT IH            | 1                | 1         | Skip on INT1 equals VSS on input pad                                                                  |

| DINI              | 1                | 1         | Skip if INT1 flip-flop is reset and set INT1 flip-flop                                                |

| INT0L             | 1                | 1         | Skip on INTO equals –V on input pad                                                                   |

| DINO              | 1                | 1         | Skip if INTO flip-flop is reset and set INTO flip-flop                                                |

| SEG1              | 1                | 1         | Decode combined memory, Carry flip-flop, and Accumulator and output 4 bits to Channel A               |

| SEG2              | 1                | 1         | Decode combined memory, Carry flip-flop, and Accumulator and output 4 bits to Channel B               |

Table 1. PPS-4/1 MM76 INSTRUCTION SET (continued)

| Op Code           | Bytes           | Cycles | Description                                               |

|-------------------|-----------------|--------|-----------------------------------------------------------|

| Conditional Trans | fer Instruction | ns†    |                                                           |

| † TC              | 2               | 3-2    | Transfer within page on Carry Set                         |

| † TNC             | 3               | 4-3    | Transfer within page on No Carry Set                      |

| † TLC             | 3               | 4-3    | Transfer Long on Carry Set                                |

| † TLNC            | 4               | 5-3    | Transfer Long on No Carry Set                             |

| † TBF             | 3               | 4-3    | Transfer within page on Bit in Memory False               |

| † TBT             | 2               | 3-2    | Transfer within page on Bit in Memory True                |

| † TLBF            | 4               | 5-3    | Transfer Long on Bit in Memory False                      |

| † TLBT            | 3               | 4-3    | Transfer Long on Bit in Memory True                       |

| † TE              | 3               | 4-3    | Transfer within page on Accumulator Equals Memory         |

| † TNE             | 2               | 3-2    | Transfer within page on Accumulator Not Equal Memory      |

| † TLE             | 4               | 5-3    | Transfer Long on Accumulator Equals Memory                |

| † TLNE            | 3               | 4-3    | Transfer Long on Accumulator Not Equal Memory             |

| † TIH             | 2               | 3-2    | Transfer within page if input selected by B Lower is High |

| † TIL             | 3               | 4-3    | Transfer within page if input selected by B Lower is Low  |

| † TLIH            | 3               | 4-3    | Transfer Long on Input Selected High                      |

| † TLIL            | 4               | 5-3    | Transfer Long on Input Selected Low                       |

<sup>\*</sup>The immediate field (IF) is two, four or six bits which are included as part of the 8-bit instruction. If not specified otherwise the immediate field is 4 bits.

<sup>\*\*</sup>When LB, EOB or LBL instructions appear in sequence as a string of LB, EOB or LBL or mixtures of LB and LBL instructions only the first one of them will be executed. The remainder of the LB, EOB or LBL instructions in the sequence will be ignored except that the first EOB after an executed LB instruction will also be executed.

<sup>\*\*\*</sup>When more than one LAI instruction occurs in sequence, only the first LAI instruction encountered will be executed.

The remainder of the LAI instructions in the string will be ignored.

<sup>†</sup>These are all macro instructions which must not be preceded by an instruction which executes a skip. For the conditional transfer instructions the first number in the cycles column indicates number of cycles when condition is met and second number indicates number of cycles when the condition for transfer is not met.

<sup>#</sup> Numbers preceded by # are hexadecimal numbers.

Note 1: Whenever an instruction is skipped (i.e., ignored) the number of cycles required is equal to the number of bytes in the skipped instruction (e.g. TL takes two cycles to skip).

Note 2: A subroutine called by a TM may not execute an SKBEI or SKAEI when they are followed by a transfer from SRO to SRO or from SR1 to SRO prior to executing the return (RT or RTSK) instruction.

#### **MULTIFUNCTION INSTRUCTIONS**

Much of the power of the PPS-4/1 MM76 instruction set comes from a group of multifunction instructions which in addition to performing a basic function such as load or exchange also set up the next address and perhaps test to see if the function is complete so a computational loop may be terminated automatically.

To understand these instructions it is necessary to understand the operation of the Data Address Register B. The B Register has two segments, B Upper and B Lower. B Lower is four bits in capacity and B Upper is two as shown in Figure 2. The bits in the B Register may be modified in groups of 2, 4 or 6 bits as shown in Table 2. It can be seen from the data memory map (Figure 3), that B Upper addresses a row and B Lower selects the column within that row.

Figure 2. ADDRESS REGISTER ORGANIZATION

Suppose that a number is in a register, REGISTER 2, which occupies Row 2 Columns 0 through 5. The program to initially set the B Register address to Row 2, Column 5, and then shift the contents of the register left 1 decimal place with a zero loaded into the vacated position is as follows:

| FOUR | Ţ    | LSFT        |

|------|------|-------------|

| LSFT | XDSK | 0           |

| TWO  | LAI  | 0           |

| ONE  | LBL  | <b>#2</b> 5 |

Instruction ONE sets the B Register to hexadecimal 25 (the symbol indicates a hexadecimal number rather than a decimal number). Instruction TWO loads zero into the Accumulator. The instruction in location LSFT (XDSK) causes the contents of the Accumulator to be exchanged with the addressed memory cell (initially \$25), decrements the B Lower address to point to \$24 and leaves the B Upper register alone since 0 Exclusively ORed with anything leaves it unchanged.

The XDSK instruction also tests to see if the complete register has been shifted by checking the decremented B Lower. If B Lower decrements from zero to \*F, then the next instruction will be skipped. Since, after completion of the 1st XDSK instruction, B Lower is 4, no skip occurs. Consequently the transfer instruction is not skipped and the

| Table 7 DATA ADDRESS MODIFICATIO | Table 2 | DATA ADDRESS MODIFICATIO | N |

|----------------------------------|---------|--------------------------|---|

|----------------------------------|---------|--------------------------|---|

| Instruction |                 | Address                   | Condition to<br>Automatically |                      |

|-------------|-----------------|---------------------------|-------------------------------|----------------------|

| Op Code     | Immediate Field | Group 2<br>2 Bits of BU** | Group 1<br>BL                 | Terminate<br>Process |

| XAB*        |                 | -                         | Exchanged with A              |                      |

| LBA*        |                 | <u> </u>                  | Replaced with A               | _                    |

| LBL         | Upper/Lower     | Replaced (2nd)            | Replaced (first)              |                      |

| LB          | Lower           | Zero                      | Replaced                      |                      |

| EOB         | Upper           | Exclusive OR              | No Change                     |                      |

| INCB*       | 2 bit Upper     | Exclusive OR              | Increment and Test for 0      | BL counts to 0       |

| DECB*       | 2 bit Upper     | Exclusive OR              | Decrement and Test for #F     | BL counts to #f      |

| 1           | 2 bit Upper     | Exclusive OR              | No Change                     |                      |

| X           | 2 bit Upper     | Exclusive OR              | No Change                     |                      |

| XDSK*       | 2 bit Upper     | Exclusive OR              | Decrement and Test for #F     | BL counts to #f      |

| XNSK*       | 2 bit Upper     | Exclusive OR              | Increment and Test for 0      | BL counts to 0       |

<sup>\*</sup>In the cycle immediately following these instructions, the contents of BU and BL Registers are correct as modified. However, in the cycle immediately following the address and modification instruction, instructions which address memory will have B Upper modifications completed but the old value of BL will be used in forming the effective memory address.

<sup>\*\*</sup>RAM-DIO Timing. When changing BU from addressing RAM (0, 1, or 2) to DIO (3), the B Register value is updated in the cycle immediately following the modification instruction, but neither RAM nor DIO accessing instructions are valid. In the second cycle following, the DIO selected by the modified BU and BL may be set, reset, or tested. When changing BU from addressing DIO (3) to RAM (0, 1, or 2) the B Register value is updated in the cycle immediately following the modification and RAM addressing instructions are valid (subject to the timing related to changing BL) except for SB, RB, SKBF instructions. During the one cycle immediately following changing BU the SB and RB instructions will set or reset a bit in RAM as well as the DIO bit. The SKBF instruction is undefined during this cycle. In the second cycle following, these three instructions are valid.

rocess is repeated. The prior contents of #25 which are not the Accumulator are exchanged with #24 and the address accemented and tested again. Subsequently the ents of #24 are moved to #23, #23 to #22, #22 to #21 and #21 to #20. Note that when this last operation is performed the B Lower register will decrement from 0 to #F ausing the transfer instruction to be skipped and the process terminated.

iuppose that the contents of REGISTER 2 are to be complenented and moved to the register called REGISTER 1 in low 1. The program to do this follows:

| ONE   | LBL  | <b>1</b> 25 | Point to hex 25              |

|-------|------|-------------|------------------------------|

| TWO   | L    | 3           | Load and point to hex 15     |

| THREE | COM  |             | Complement                   |

| FOUR  | XDSK | 3           | Exchange, Point to #24, test |

| FIVE  | T    | TWO         | Not thru, repeat             |

The Exclusive OR function between 11 from the immediate field of instruction TWO (L 3) and 10 in bits 6 and 5 of the B Register converts the B Register address to 01 0101 15) as well as loading the Accumulator. Similarly the 11 in the immediate field of the instruction in location FOUR causes the 01 bits in locations 6 and 5 to be converted to 10 (2) and the B Lower is also decremented and tested in addition to performing the exchange. Consequently, the B Register at the conclusion of this ruction is 10 0100 (124) which is pointing at the next as to be complemented.

The process is repeated again until the complemented value of memory cell #20 is stored in #10 and then the process automatically terminates because B Lower will decrement from 0 to #F after the exchange.

|            |   |          | 8 LOWER (COLUMN) |          |          |          |          |          |          |          |          |        |   |             |             |   |   |

|------------|---|----------|------------------|----------|----------|----------|----------|----------|----------|----------|----------|--------|---|-------------|-------------|---|---|

|            |   | 0        | 1                | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | A      | В | c           | D           | E | F |

| <b>(</b> ) | 0 |          |                  |          |          |          |          |          |          |          |          |        |   |             |             |   |   |

| ROW)       | ł | 7        | REG              | STER     | 1-       |          | -        |          |          |          |          |        |   |             |             |   |   |

| UPPER      | 2 | -        |                  | ISTER    |          |          | -        |          |          |          |          |        |   |             |             | l |   |

| <b>6</b> 0 | 3 | DIO<br>0 | DIO<br>-         | 01O<br>2 | DIO<br>3 | DIO<br>4 | DIO<br>5 | DIO<br>6 | DIO<br>7 | DIO<br>8 | 010<br>9 | $\geq$ | X | $\boxtimes$ | $\boxtimes$ | X | X |

Figure 3. DATA MEMORY MAP FOR PPS-4/1 MM76

A program to move the data from REGISTER 2 to REGISTER 1 is as follows:

The same program will move 16 four-bit words if the process is started at #2F instead of #25:

The PPS-4/1 MM76 is particularly efficient for using subroutines which may operate for different lengths of data registers in memory. For instance if it is desired to use one subroutine with two entry points to either move 6 characters or 16 characters respectively, the following program may be used:

| RETN | TM<br>[NEXT | MOVF<br>INSTR] | subroutine call to<br>move 16 characters |

|------|-------------|----------------|------------------------------------------|

| MOVF | LBL         | # 2F           |                                          |

| MOV6 | LBL         | #25            |                                          |

| MOVE | L           | 3              |                                          |

|      | XDSK        | 3              |                                          |

|      | Ţ           | MOVE           |                                          |

|      | RT          |                |                                          |

The PPS-4/1 ignores LBL instructions in a string except for the first one executed. Consequently, for this example, the B Register is loaded with #2F and the LBL #25 is ignored so 16 bytes will be moved. A TM MOV6 instruction would load the B Register with #25 so that 6 characters would be moved. After moving the 16 or 6 characters the T MOVE instruction will be ignored and the RT instruction causes the program counter to return to the next instruction after the TM MOVF or TM MOV6 instruction so that the main program can continue from that point. If more than one subroutine call is used in the program (the usual case for subroutines) the program will always continue with the next instruction after the specific one which called the subroutine when the subroutine has completed its process.

There are two types of unconditional transfer instructions (T and TL) and two types of transfer and mark instructions (TM and TML). The ROM Map Table (Table 3) will help explain their usage.

There are 64 program memory bytes on a page. An unconditional transfer to another location on the same page requires a one byte T instruction which contains as part of the instruction the specific location for the next instruction to be executed. If the next instruction is not on the same page and is not in the primitive subroutine page, then a two byte instruction TL is used.

The subroutine call instruction TML is similar. However, the TML instruction is used when the first instruction of the subroutine is on any of the general program area pages (even if it is the same page).

The TM instruction operates differently. The TM instruction is one byte long and always transfers to a subroutine on page SRO of the primitive subroutine area. The primitive subroutine area (SRO and SR1) is special in that it comprises two 64 byte sections, 15 and 14 respectively. One byte transfers are used to go between

the two sections. This area is intended for easy access to primitive subroutines which are often used.

The subroutine may be self-contained within that area or the subroutine may perform an unconditional transfer to anywhere in memory via a TL instruction.

The PPS-4/1 MM76 conserves ROM by allowing these simplified one byte subroutine calls to be used for the high usage subroutines. This is a unique capability in the PPS family which effectively increases the amount of ROM available for other functions.

A more complete description of programming techniques are shown in the PPS-4/1 Programming and Applications Manual. Features of the assembly, editing, and emulation capabilities on the PPS Universal Assemulator development hardware are discussed in the PPS-4/1 Operators Manual for Universal Assemulator. An assembly capability for the MM76 is also available in FORTRAN IV and on the General Electric Information Services system. That assembler is described in the PPS-4/1 Single Circuit Microcomputer Series Programming Manual.

Table 3. ROM MAP

| Page No. | Program Memory (ROM) Allocation                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------|

| 0        | 64 bytes general program area                                                                                   |

| 1        | 64 bytes general program area                                                                                   |

| 2<br>3   | 64 bytes general program area on page transfers                                                                 |

| 3        | 64 bytes general program area (T) — one byte Substitute collection and the TAN are leasted                      |

| 4        | 64 bytes general program area  Subroutines called by TML are locate in this area                                |

| 5        | 64 bytes general program area off page transfers                                                                |

| 6<br>7   | 64 bytes general program area (TL) — two bytes                                                                  |

| 7        | byte 0 = power on location — remainder general area                                                             |

| 8-13     | Not used                                                                                                        |

| 14 (SR1) | Extension of primitive subroutine area from page SRO (15)                                                       |

| 15 (SRO) | TM address area (1 byte subroutine calls start here and extend to page SR1 (14) or to other sections of memory) |

Note: The development circuit for the PPS-4/1 MM76 (Part No. A7699) can use all 1024 addressable bytes for developing programs. Consequently, pages 8 through 13 may be used as necessary during the development and the final programs condensed to the addresses shown above for the production program.

#### **ECIMAL ADDITION**

#### **MPLE**

of further illustrate the flexibility and efficiency of the PS-4/1 MM76 instruction set, a decimal addition subsutine which has multiple entry points will be discussed. hese different entry points allow the contents of different emory registers to be added together and the resulting m left in the designated one of the two registers wolved in the addition and also illustrate decimal ddition with differing numbers of decimal digits. In the PS-4/1 system the same subroutine may be used for both opes of functions. This decimal add subroutine is as allows:

| )IIOM2:    |      |      |                                                                                          |

|------------|------|------|------------------------------------------------------------------------------------------|

| .D10       | LB   | #29  | Entry to Add 10 digit register<br>Pair 1*                                                |

| .D12       | LBL  | # 1B | Entry to Add 12 digit Register<br>Pair 2*                                                |

| D5         | LBL. | #14  | Entry to Add 5 digit Register<br>Pair 3*                                                 |

| ADD        | RC   |      | Reset carry for initial digit add                                                        |

| OOP        | L    | 3    | Load digit from 1st register and point to 2nd                                            |

|            | AISK | 6    | Decimal correct (add 6)                                                                  |

|            | NOP  |      | Always is skipped                                                                        |

| <i>_</i> ' | ACSK |      | Add digit from 2nd register, skip if no carry is generated                               |

|            | T    | STOR | Answer is correct so transfer to store digit                                             |

|            | AISK | 10   | Recorrect if no carry (add 10 with no carry - bypassed if a carry from ACSK instruction) |

| STOR       | XDSK | 3    | Store answer digit point to next digit in first register, skip if BL=15                  |

|            | T    | LOOP | Repeat until last digit added                                                            |

|            | RT   |      | Through so return from subroutine to next location after subroutine call                 |

<sup>\*</sup>Register pair 1 adds Register #20-#29 to #10-#19 and puts answer in #10-#19.

Register pair 2 adds Register #10–#1B to #20–#2B and puts answer in #20–#2B.

Register pair 3 adds Register  $^{\#}10^{-\#}14$  to  $^{\#}20^{-\#}24$  and puts answer in  $^{\#}20^{-\#}24$ .

DADD is a general subroutine entry which may be used to add from 1 to 16 decimal digits in rows 2 to 1 or 1 to 2. The specific registers and the number of decimal digits to added are dependent upon the initial value in the Register.

#### **ELECTRICAL INTERFACE**

This section and Table 4 defines the electrical specifications.

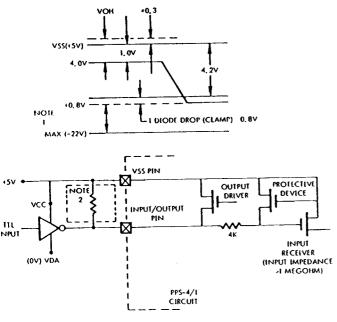

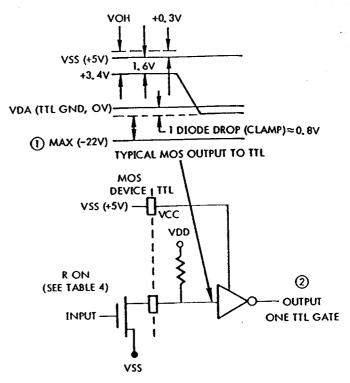

The power supply for the PPS-4/1 microcomputer requires a 15 volt  $\pm 5\%$  supply. This may be obtained by a single 15 volt or  $\pm 10$ , 0,  $\pm 5$  volt supply when the input/output system is interfacing with CMOS as shown in Figure 4 or may be obtained from  $\pm 5$ , 0,  $\pm 10$  volt supply when interfacing with TTL circuits as shown in Figure 5.

NOTE: The PPS-4/1 VSS must be connected to most positive CMOS terminal.

The PPS-4/1 requires a 15 volt supply. CMOS operates with an 8V to 15V input. (If CMOS is only receiving PMOS inputs, the input can range from 3V to 15V.)

Figure 4. TYPICAL PMOS TO CMOS POWER INTERFACE

NOTE: The PPS-4/1 requires a 15 volt supply.

TIL uses a 5 volt supply.

Figure 5. TYPICAL PMOS TO TTL POWER INTERFACE

#### **OPERATING CHARACTERISTICS**

Supply Voltage:

VDD = -15 Volts ±5%

(Logic "1" = most negative voltage VIL and VOL.)

VSS = 0 Volts (GND)

(Logic "0" = most positive voltage VIH and VOH.)

System Operating Frequencies:

80 kHz ± 50% with external resistor

**Device Power Consumption:**

75 mw, typical

Input Capacitance:

<5 pf

Input Leakage:

<10 µa

Open Drain Driver Leakage (R OFF):

<10 µa at −30 Volts

Operating Ambient Temperature (TA):

OPC to 70°C (TA = 25°C unless otherwise specified)

Storage Temperature:

-55°C to 120°C

ABSOLUTE MAXIMUM VOLTAGE RATINGS

(with respect to VSS)

Maximum negative voltage on any pin -30 volts.

Maximum positive voltage on any pin +0.3 volts.

|                                  |            | Lin          | nits (VS | S = 0)      | Limi   | ts (VSS | = +5V)               | Timing<br>(Sample/ | Test                       |

|----------------------------------|------------|--------------|----------|-------------|--------|---------|----------------------|--------------------|----------------------------|

| Input/Output                     | Symbol     | Min          | Тур      | Max         | Min    | Тур     | Мах                  | Good)              | Conditions                 |

| Supply Current (Average) for VDD | IDD        |              | 5 ma     | 8 ma        |        | 5 ma    | 8 ma                 |                    | VDD = -15, 75V<br>T = 25°C |

| Discrete I/O's                   | VIH        | -1.0\        |          | 404         | +4.0V  |         | .0.0\/               | ø3 & ø4            |                            |

| DI/O0-DI/O9                      | VIL        | <b></b>      |          | -4.2V       | •••    |         | +0.8V                |                    |                            |

| DI/O0-5                          | RON        |              |          | 500 ohms    |        |         | 500 ohms<br>400 ohms | Ø2*                | 3, 0 ma max.               |

| DI/O6-9                          | RON        |              |          | 400 ohms    | .5.61/ |         | 400 ohms             |                    |                            |

| Channel 1 Input<br>PI1-PI4       | VIH<br>VIL | -1.5V        |          | -4.2V       | +3.5V  |         | +0.8V                | Ø١                 |                            |

| Channel 2 Input<br>PI5-PI8       | VIH<br>VIL | -1.5V        |          | -4.2V       | +3.5V  |         | +0.8V                | ø3                 |                            |

| I/O Channel A<br>RI/O1-RI/O4     | VIH        | -1.5V        |          | -4.2V       | +3.5V  |         | +0.8V                | ø3                 |                            |

| KIJ O I-KIJ O4                   | RON        | <del> </del> |          | 250 ohms    |        |         | 250 ohms             | Ø2*                | 6, 0 ma max.               |

| I/O Channel B                    | VIH        | -1.5V        |          | 250 014113  | +3.5V  |         | 250 011113           | <u> </u>           | 0, 0 1110 1110/11          |

| RI/O5-RI/O8                      | VIL<br>VIH | -1.54        |          | -4.2V       | 13.5 4 |         | +0.8V                | ø3                 |                            |

| ki/ 05-ki/ 08                    | RON        | }            |          | 250 ohms    |        |         | 250 ohms             | Ø2*                | 6. 0 ma max.               |

| DATAI                            | VIH        | -1.0V        |          | 250 0111113 | +4.0V  |         | 250 011113           |                    | 0.0                        |

| DAIAI                            | VIL        | ""           |          | -4.2V       |        |         | +0.8V                | Ø4                 |                            |

| DATAO                            | RON        | <del> </del> |          | 500 ohms    |        |         | 500 ohms             | Ø4**               | 3, 0 ma max.               |

| INTO                             | VIH        | -1.5V        |          | 000 0111113 | +3.5V  |         |                      | <u> </u>           |                            |

| 11410                            | VIL        | ""           |          | -4.2V       |        |         | +0.8V                | ø3                 |                            |

| INTI                             | VIH        | -1.5V        |          |             | +3.5V  |         |                      |                    |                            |

|                                  | VIL        | ""           |          | -4.2V       |        |         | +0.8V                | ØI                 |                            |

| Clock                            | VOH        | -1.0V        |          |             | +4.0V  |         |                      |                    | CL=50 pf (ma               |

| A, BP, $(\overline{B})$          | VOL        | "            |          | -10.0V      |        |         | -5.0V                | -5.0V              | ' `                        |

| EXCLK                            | VIH        | -1.5V        |          |             | +3.5V  |         |                      | 4.004              | F max. = 80 kH             |

|                                  | VIL        |              |          | -9.0V       |        |         | -4.0V                | -4.0V              |                            |

| CLK IN                           | VIH        | -1.00        |          |             | +4.0V  |         |                      | 1                  | 1                          |

|                                  | VIL        |              |          | -10.0V      |        |         | -5.0V                |                    |                            |

| Shift Clock                      | VIH        | -1.0V        |          |             | +4.0V  |         |                      | go o gu            | 1                          |

| Clock                            | VIL        |              |          | -4.2V       |        |         | +0.8V                | Ø3 & Ø4            |                            |

|                                  | RON        | 1            |          | 500 ohms    |        |         | 500 ohms             | Ø4**               | 2.0 ma max.                |

| VC***                            | VIH        |              |          |             |        |         |                      | 1                  | E ( V   E0/                |

|                                  | VIL        |              |          | •           | [      |         |                      |                    | 56K ±5%                    |

| PO                               | VIH        | -2.0V        |          |             | +3.0V  |         |                      |                    | ]                          |

|                                  | VIL        |              |          | -6.0V       | 1      |         | -1.0\                |                    | Special circui             |

<sup>\*</sup>State established by  $\emptyset 2$  (minimum impedance after  $\emptyset 4$ ).

<sup>\*\*</sup>Same as above except Ø4 minimum at Ø2 of next cycle.

<sup>\*\*\*</sup>Connect VC to VDD through a resistor:  $56K\Omega$  for 80 kHz or  $47K\Omega$  for 100 kHz.

#### **SCRETE I/O PORTS**

he ten discrete I/O ports (DI/O0 through DI/O9) are ated by setting B Upper of the B Register to three and wwer to the appropriate value (i.e., #31 will select I/O 1). Issuing a Set Output Selected (SOS) instruction vill connect the output port to VSS through 500 ohms (or 00 ohms) maximum. Issuing a Reset Output Selected (ROS) nstruction will cause the output to float, allowing an external resistance to pull the output to a -V level. The sutput will be stable by \$2 of the following instruction. Ainimum impedance is reached after \$4. The output circuit s capable of sinking 3 ma maximum when all the output ircuits are in use. To use as an input, the port must be elected by BL and the Skip on Input Selected Low instrucion issued. A skip will be produced if the input is more regative, relative to VSS, than -4.2 volts. The inputs are ully synchronized so that an asynchronous input signal may ne used. The sampling occurs during phase 3 (see Figure 9). he technique for interfacing with TTL logic is shown in igures 6 and 7.

#### ARALLEL I/O PORTS (RIO1-RIO4)

The parallel input/output ports RIO1 through RIO4 provide a masked input capability and an output capability either from the 16 x 8 matrix or directly from the Accumulator. In either event the A Buffer is loaded via a SEG1 or an OA instruction. When used as an output a "1" in any bit position in the A Buffer will cause the corresponding output

#### NOTES:

- Maximum voltage which may be applied to any input/autput pin is -30 volts relative to VSS.

- Only an Open Collector Driver requires the Pull-Up Resistor.

Figure 6. TTL to PPS-4/1 SYNCHRONIZED INPUT RECEIVER INTERFACE

#### NOTES:

- Maximum voltage which may be applied to any input/output pin is -30V relative to VSS.

- SOS command causes gate output to be low.

"1" in A or S causes the gate output to be high.

Figure 7. PPS-4/1 OUTPUT DRIVER TO TTL INTERFACE

bit to float, while a "0" in the A Buffer will cause the output to be connected to VSS through 250 ohms maximum. The outputs will be stable by the following \$\textit{\gamma}2\$ time and the impedance to VSS when the output is in the high state will be less than 250 ohms after \$\textit{\gamma}4\$. The outputs are buffered through a register such that any state will be held until another exchange is executed. The output drivers will sink 6 milli-amperes when all circuits are sinking a current.

In order to use any bit position as an input, the corresponding bit of the output buffer must be loaded with a "1" before the operation is performed so that the output driver will be floated and may be set high or low by the external signal to be input. The contents of the Accumulator provide a masking capability. The contents of the Accumulator must be set to one in each bit position to be input. A zero in the Accumulator masks the input bit so that independent of the RIO signal the resulting value in the Accumulator is zero. The inputs are fully synchronized (sampled at  $\emptyset 3$  time) and will recognize a voltage more negative than -4. 2 volts (related to VSS) as a "1" and a voltage between +0.3 and -1.5 as a "0". The outputs will be initialized to the float state with power on.

#### PARALLEL I/O PORTS (RIO5-RIO8)

The parallel input/output ports RIO5 through RIO8 work in exactly the same manner except OB, SEG2, and IBM instructions are used.

#### PARALLEL INPUT PORTS (PI1-PI4)

The parallel input ports PI1 through PI4 will be loaded into the Accumulator upon execution of an input channel 1 instruction (I1). The inputs are fully synchronized during phase 1 and are ITL compatible. An input signal more negative then -4. 2 volts will be a logic "1" and a "0" range is from +0.3 to -1.5 volts.

#### PARALLEL INPUT PORTS (PI5-PI8)

The inverted state of the parallel inputs PI5 through PI8 will be copied into the Accumulator upon receipt of an I2C instruction. The inputs are synchronized during phase 3 and are TTL compatible.

#### CONDITIONAL INTERRUPTS (INTO AND INT1)

The conditional interrupt ports may be utilized in two different ways. The first way is that the input logic level can be tested directly by means of the conditional interrupt 0 or conditional interrupt 1 instructions, INTOL or INT1H. A skip will be produced when the INTO signal is a -V and when the INT1 signal is at VSS.

The second way of using the conditional interrupt capability is to test the state of a flip-flop associated with each input in a manner similar to the discrete I/O ports. The flip-flops are selected and set by DINO for INTO and DIN1 for INT1. If the flip-flop for INTO is in the set state and a transition occurs on the input from the -V state to the VSS state for one bit time or more, the flip-flop will be reset. Consequently, the signal to activate a conditional interrupt may be a pulse as long as it is at least one clock period long.

The state of the flip-flop may then be tested and set by the DINO command. If the next instruction skips, it will indicate that a -V to VSS level pulse did occur even though the VSS level has gone away. The INT1 signal performs in the same manner except that a transition from a VSS level to a -V level for one bit time will cause the flip-flop to be reset so that it may be tested and set by the DIN1 command.

The inputs are sampled at phase 1 for INT1 and phase 3 for INT0 and are TTL level compatible as shown in Figure 6.

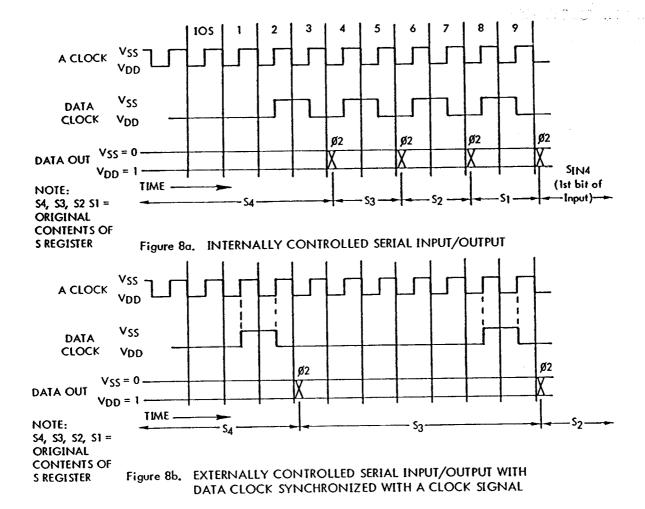

#### SERIAL 1/0

A serial register, designated S Register, is built into the circuit which may be used as a serial IN/OUT buffer and may also be used for parallel exchange with the Accumulator. Data to be output is loaded into the Accumulator and transferred to the serial register by the Exchange A and S (XAS) command. The serial I/O (IOS) command causes the data to be shifted out along with a clock for clocking external devices. Each bit of data is presented at the output for two bit times and a data clock pulse is provided as shown in Figure 8a for clocking external shift registers. Data may be input at the same time and then transferred to the Accumulator.