### PRODUCT DESCRIPTION PRELIMINARY

# PARALLEL PROCESSING SYSTEM (PPS-8) MICROCOMPUTER

## INTRODUCTION AND DESCRIPTION PARALLEL PROCESSING SYSTEM (PPS-8)

### **NOTICE**

Information provided in this Product Description is for reference purposes only, and is subject to change without notice.

For specific detail information on these devices or for information on any of our other advanced microelectronic devices, please contact the nearest Rockwell International Microelectronic Device Division office.

### TABLE OF CONTENTS

| Section 1 - INTRODUCTION               | 1-1           |

|----------------------------------------|---------------|

| Section 2 - DESCRIPTION                | 2-1           |

| General                                | 2-1           |

| System Characteristics                 | 2-1           |

| Throughput                             | 2-1           |

| Instruction Repertoire                 | 2-2           |

| Instruction Memory (ROM)               | 2-2           |

| Read/Write Memory (RAM)                | 2-2           |

| Input/Output                           | 2-2           |

| Physical/Electrical                    | 2-3           |

| Support Equipment                      | 2-3           |

| Functional Description                 | 2-4           |

| Central Processor Unit (CPU)           | 2-4           |

| Read Only Memory Device (ROM)          | 2-7           |

| Random Access Memory Device (RAM)      | 2-8           |

| Clock Generator                        | 2-9           |

| General Purpose Input/Output (GPI/O)   | 2-10          |

|                                        | 2-11          |

| Direct Memory Access Controller (DMAC) | 2-21          |

| Special Purpose Input/Output Devices   | 2-27          |

| special rulpose input/ output bevices  | 2-21          |

| Section 3 - PRINCIPLES OF OPERATION    | 3-1           |

| Basic System Operation                 | 3-1           |

| System Timing                          | 3-1           |

| Logic Levels                           | 3-1           |

| Multiplex System Data Transfer         | 3-1           |

| Instruction Repertoire                 | 3-3           |

|                                        | 3 <b>-</b> 13 |

|                                        | 3-16          |

|                                        | 3-10 $3-17$   |

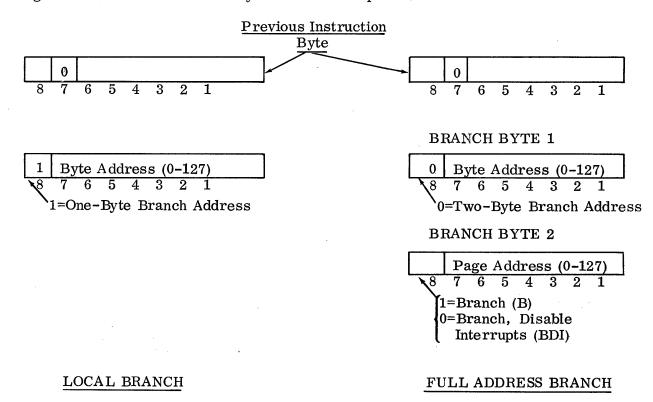

| Branching                              | 3-17          |

|                                        | 3-18          |

| Operand Addressing                     | 3-10          |

| 1                                      | 3-20<br>3-20  |

|                                        | 3-20<br>3-22  |

|                                        | 3-22<br>3-24  |

|                                        |               |

|                                        | 3-24          |

|                                        | 3-26          |

|                                        | 3-27          |

|                                        | 3-27          |

|                                        | 3-28          |

| <u> </u>                               | 3-29          |

| Input/Output                           | 3-30          |

|                                        |               |

### Microelectronic Device Division

ROCKWELL INTERNATIONAL

c/o ROCKWELL INTERNATIONAL OVERSEAS CORPORATION

(U.S.A. - WEST COAST)

(U.S.A. - EAST COAST)

(EUROPE)

(FAR EAST)

P. O. Box 3669

3310 Miraloma Avenue

D-6374 Steinbach/Taunus Industriestrasse 8

Germany

Ichiban-Cho Central Building 22-1, Ichiban-Cho

Anaheim, California 92803

9 Kim Avenue Smithtown, New York 11787

Phone: (06171) 7755

Chiyoda-Ku, Tokyo, 102 Japan

(714) 632-3698 TWX: (910) 591-1179, Telex: Via TWX Phone: (516) 979-0183

TELEX: 410758

Phone: 265 8808/8809 TELEX: J22198

### Section 1. INTRODUCTION

The Rockwell 8-bit Parallel Processing System (PPS-8) is an advanced design, modular, microcomputer system which uses a unique 4-phase clock timing system for logic functions and control. Proven P-channel MOS technology is used to implement the PPS-8 system byte (8-bit) oriented architecture. Rockwell MOS technology and the unique design of the PPS-8 offers superior performance for less cost over a wide range of applications. Some of these applications include point-of-sale equipment, data entry terminals, and peripheral/process control. The wide range of applications and performance is achieved by high system throughput, efficient character-oriented instructions, flexible input/output capabilities, and system modularity/expandability.

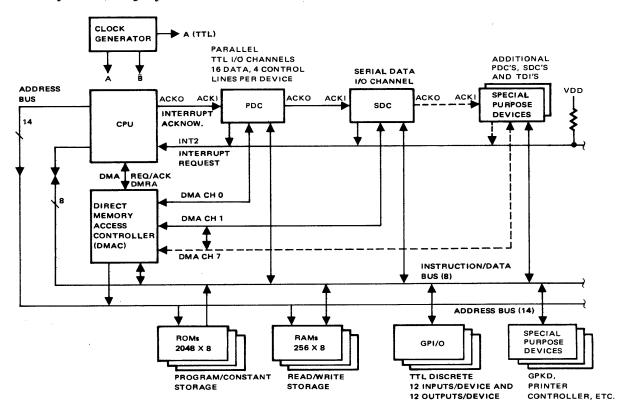

The standard PPS-8 system is shown in Figure 1-1. The standard PPS-8 system consists of a Central Processor Unit (CPU) device, Random Access Memory(s) (RAM) device, Read Only Memory(s) (ROM) device, Multiphase Clock Generator, Direct Memory Access Controller (DMAC) device, Parallel Data Controller (PDC) device and Serial Data Controller (SDC) device.

The basic system can be supplemented with special purpose and custom input/output devices as required for specific applications. For example, a 1200 baud Telecommunications Data Interface device, a printer controller device, a bus-interface device, and a keyboard/display controller device are available.

Figure 1-1. PPS-8 Microcomputer System

### Section 2. DESCRIPTION

### GENERAL

The various MOS devices used to make up the PPS-8 are all packaged in identical standard 42-lead plastic packages with the exception of the Clock Generator which is in a TO 100 package. The overall dimensions of the body of the plastic package, exclusive of the leads, are 0.640 inches in width, 1.060 inches in length, and 0.15 inches in thickness. This standardization in packaging provides optimum flexibility when designing and packaging a specific PPS-8 System

A functional description of each of the below listed devices is provided in this section.

| PPS-8 BASIC DEVICES                         | Part Number |

|---------------------------------------------|-------------|

| Central Processor Unit (CPU)                | 10806       |

| Read Only Memory (ROM)                      | A52         |

| Clock Generator                             | 10706       |

| General Purpose Input/Output (GPI/O)        | 10696       |

| Parallel Data Controller (PDC)              | 10453       |

| Direct Memory Access Controller (DMAC)      | 10817       |

| Random Access Memory (RAM)                  | 10809       |

| SPECIAL PURPOSE DEVICES                     | Part Number |

| Printer Controller Circuit                  | 10789       |

| Telecommunication Data Interface (TDI)      | 10371       |

| General Purpose Keyboard and Display (GPKD) | 10788       |

| Bus Interface (B/I)                         | 10733       |

| Serial Data Controller (SDC)                | 10930       |

### SYSTEM CHARACTERISTICS

The following paragraphs provide a summarization of the characteristics and capabilities of the basic PPS-8 system.

### THROUGHPUT

| • | Instruction Access -            | $2~\mu \mathrm{s}$ |

|---|---------------------------------|--------------------|

| • | Operand Access -                | $2~\mu \mathrm{s}$ |

| • | Complete Instruction Cycle -    | 4 μs               |

| • | Decimal Addition —              | 12 μs/digit        |

| • | Decimal Subtraction -           | 12 μs/digit        |

| • | Block Data Moving -             | $12 \mu s/byte$    |

| • | Table Search –                  | $12 \mu s/byte$    |

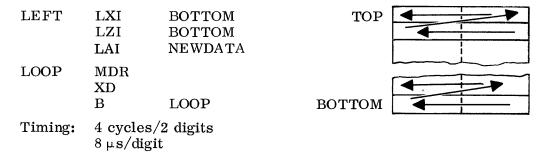

| • | Digit (4-bit) String Shifting - | 8 µs/digit         |

### INSTRUCTION REPERTOIRE

- Over 90 Instructions

- Digit (4-bit) and Byte (8-bit) Manipulation

- Decimal and Binary Arithmetic

- Bit Setting/Resetting/Testing

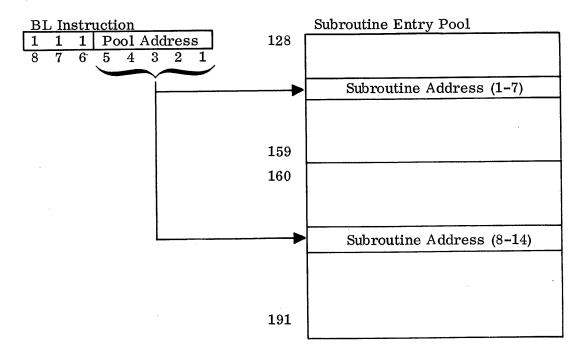

- Single Byte Subroutine Call

- Data Stacking

- Common Data "Pools"

### INSTRUCTION MEMORY (ROM)

- 2048 x 8 RCM devices

- Local Page Addressing to 128 Bytes

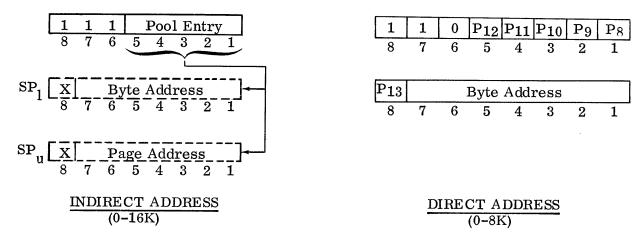

- Direct Addressing to 16,384 Bytes

- Bank Select Addressing to 32K Without External Circuitry

- Indirect, Auto-increment Addressing

### READ/WRITE MEMORY (RAM)

- 256 x 8 RAM devices

- Direct Addressing to 16,384 Bytes

- Bank Select Addressing to 32K Without External Circuitry

- 3 RAM Addressing Registers

- Auto-Increment and Auto-Decrement Addressing

### INPUT/OUTPUT

- Priority Interrupt System

- Power-Fail Detect Real Time Clock

- I/O Device Service

- Direct Memory Access

- Up to 8 Prioritized Channels

- 250K Bytes/sec

- Program Controlled I/O

- Byte (8-bit) or Digit (4-bit)

- 75K Bytes/sec

- General Purpose TTL-Compatible Interface

- Static Discretes

- Bi-directional 8 or 16 Bit Parallel Bus(es)

- Buffered Serial (standard communications format)

- Full "Handshaking"

- PPS-4 I/O Compatibility

- Special Purpose I/O Devices

- Telecommunications Data Interface (TDI)

- General Purpose Keyboard and Display (GPKD)

- Printer Controller

- Bus Interface (B/I)

- Serial Data Controller (SDC)

### PHYSICAL/ELECTRICAL

- Single -17 volt Power Supply

- Low Power 4-Phase Dynamic Logic

- 42-Pin Plastic Packages

### SUPPORT EQUIPMENT

- Assembler on Tymshare, GE Information Services, and Rockwell TSO Operating System

- Interactive Simulator on Tymshare, GE Information Services, and Rockwell TSO Operating System

- Batch Assembler (Fortran)

- Batch Simulator (Fortran)

- Rockwell PPS-8 Assemulator (Assembler and Emulator)

- Pre-Packaged Evaluation Boards

- Processor I (CPU, RAM(2), GPIO(2), Clock)

- Processor II (CPU, RAM(2), PDC(2) DMAC, Clock)

- RAM (RAM (8))

- PROM

- GPIO

- TTL

- ROM

### FUNCTIONAL DESCRIPTION

### CENTRAL PROCESSOR UNIT (CPU)

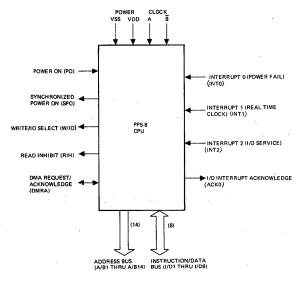

The PPS-8 Central Processor Unit, Part No. 10806, shown in Figures 2-1 and 2-2 is a complete 8-bit parallel processor implemented on a single MOS chip. The CPU uses four-phase dynamic logic for operation, and all power requirements are met from a single 17-volt power supply.

### The CPU contains:

- (a) Logic necessary to receive and decode the instructions

- (b) 8-bit parallel adder-accumulator for arithmetic and logical operations

- (c) 14-bit P-Register for sequencing through the ROM program

- (d) 16-bit L-Register for subroutine linkage, RAM operand addressing, and ROM indirect addressing

- (e) Three 8-bit registers, (X, Y and Z) for RAM operand addressing

- (f) 5-bit stack pointer S for addressing a dedicated RAM area

- (g) Logic for processing a priority interrupt structure

- (h) Direct memory access (DMA) mode

- (i) Multiplexed receivers and drivers for interfacing with the 14-bit multiplexed address bus and the 8-bit bi-directional data/instruction bus.

The CPU, through time multiplexing, utilizes an 8-bit bi-directional bus to transfer instructions from ROM to CPU (and I/O) during Ø4, and to transfer data between the CPU, RAMs and I/O devices during Ø2.

### Instruction Decode

The decode portion of the chip contains logic to decode the instructions, sense interrupt or DMA requests, and provide signals to control data transfer, arithmetic, logical, and indexing operations. Instructions are either one, two, or three bytes in length and require from one to three cycles for execution.

### Accumulator Register and Arithmetic Logic Unit (ALU)

The adder is an 8-bit parallel binary adder with an internally connected carry flip-flop (C) for implementing extended precision arithmetic operations. In addition, the adder has built-in capability to facilitate packed BCD (decimal) arithmetic and manipulation of hexadecimal data. Circular shifting of the accumulator contents right and left with carry linkage is also provided. The adder, with the 8-bit Accumulator Register (A), and associated logic circuits forms the Arithmetic and Logical Unit (ALU) section of the CPU.

Figure 2-1. PPS-8 CPU Interface

Figure 2-2. Central Processor Unit Block Diagram

In addition to its arithmetic functions, the A-Register is the primary working register in the CPU and is the central data interchange point for most data transfer operations.

### P-Register (14-bits)

The P-Register contains the address of the instruction currently being executed, and automatically increments (least significant 7-bits) to fetch the next byte from instruction memory (ROM). It may be altered during the execution of Branch, Return or Skip instructions.

### L-Register (16 Bits)

The L-Register is used to save the return address after a subroutine call or an interrupt. It is also used as an address register for indirect ROM operands. It can also be used as an alternate RAM address register or as a general purpose programming register.

### Z-Register (8-bits)

This register holds the 7 most significant bits of the 14-bit RAM operand address or may be used as a general purpose programming register.

### X-Register (8-bits)

The X-Register holds the 7 least significant bits of the 14-bit RAM operand address. The most significant bit (8th bit) is used as an upper RAM address control bit. If the upper address control bit is:

- Logic 1 the Z-Register contents are output for the most significant 7 bits of the RAM address.

- Logic 0 logic zero is output for the most significant 7 bits of the RAM address.

This register may be loaded, stored, auto-incremented, or auto-decremented under program control.

### Y-Register (8-bits)

The Y-Register is used as an alternate lower RAM address register and as a "loop counter" or it may be used as a general purpose programming register.

### S-Register (5-bit)

The 5-bit up-down counter register S is used as an address pointer to a 32 byte "stack" in RAM. This stack pointer is automatically incremented each time a byte is "pushed" into the stack and decremented each time a byte is "popped" from the stack.

### W-Register (8-bit)

The W-register serves primarily as an internal buffer register. Additionally, it is used in conjunction with the LAL and PSHL instructions.

### Power-On Reset (PO)

The Power-on input signal is used to initialize the CPU to a known starting address and state during a power-on sequence. The Power-on (PO) Signal is generated external to the CPU. The CPU receives this signal, initializes the internal logic states, and at the same time, generates a Synchronized Power-on Output (SPO) Signal which is used to initialize other circuits of the PPS-8.

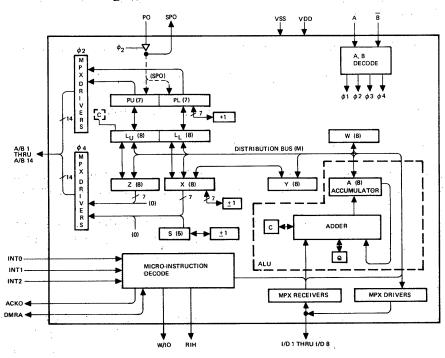

### READ ONLY MEMORY DEVICE (ROM)

The Read Only Memory (ROM), Part No. A52--, shown in Figure 2-3, is a 16,384 bit ROM organized in a 2048 x 8-bit configuration. It is designed for compatibility with the PPS-8 system, operating from a single 17-volt power supply and the A and  $\overline{B}$  system clocks. The access time is 1.8  $\mu$ s. It is intended to be used to store 8-bit instructions and constant program data within a PPS-8 system.

The 8-bit CPU, with its 14-bit parallel address outputs, can directly address up to 16,384 bytes. The ROM provides an additional address select input (AS5) that can be used in systems requiring more than 16,384 bytes of ROM storage. With this line, alternate banks of 16K ROM can be selected to provide up to 32K bytes.

The unique time-sharing design of the PPS address and data bus is such that information on the I/D bus is treated as 8 bits of microinstruction during clock phase 4 and RAM or I/O data during clock phase 2. The ROM is designed to accept addresses during phase 2 and supply instructions or data to the data bus during phase 4.

Figure 2-3. Read Only Memory (ROM)

Block Diagram

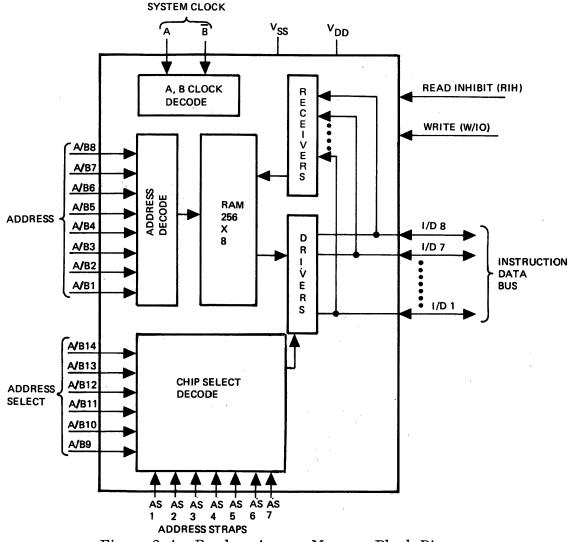

### RANDOM ACCESS MEMORY DEVICE (RAM)

The Random Access Memory (RAM), Part No. 10809, shown in Figure 2-4, is a 2048 bit RAM organized in 256 x 8-bit configuration. It is designed for compatibility with the PPS-8 system, operating from a single 17-volt power supply and the A and  $\overline{B}$  system clocks. It is a dynamic memory with automatic refresh logic and a 1.8  $\mu s$  access time. It is intended to be used as the read/write data storage device for the PPS-8 system.

The CPU, with its 14-bit parallel address outputs can directly address up to 16,384 8-bit bytes of data. The RAM, with its eight parallel address lines and six-chip select inputs, provides for direct selection of up to 64 RAM devices. The one additional chip select input on the RAM chip can be used for memory expansion greater than 16,384 word locations. For large systems, the AS7 chip select input can be addressed by an output from an I/O circuit. For systems with RAM memory capacity of 16,384 words or smaller, the AS7 chip select input must be terminated at VSS.

Figure 2-4. Random Access Memory Block Diagram

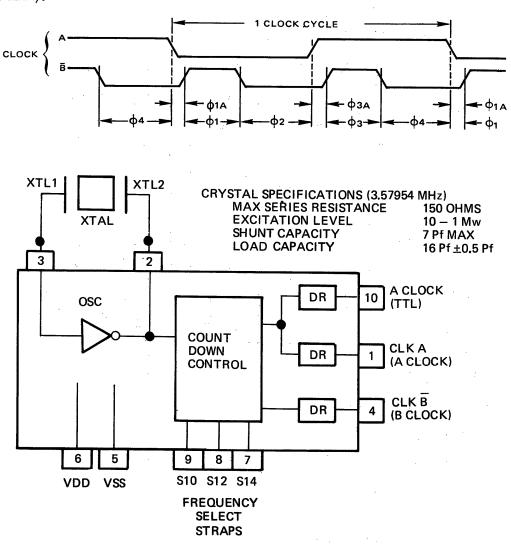

### CLOCK GENERATOR

The Clock Generator circuit, Part No. 10706, shown in Figure 2-5, generates the "A" and "B" clock waveforms required by circuits in the PPS. The Clock Generator has an internal oscillator which is stabilized by connecting a quartz crystal to the appropriate inputs. The crystal is a 3.579545 MHz color TV crystal which is low in cost and readily available. The clock A output is a square wave and considered the primary clock. Output B is a pulse output occurring during each phase of clock A and has unique timing features required by the circuits within the PPS system. Clock A is also provided through an output which drives to ground such that TTL levels can be easily achieved for synchronizing equipment external to the PPS.

The input straps provide a countdown of the oscillator frequency equal to the number associated with the strap: i.e., S10 divides by 10, S12 input results in a countdown by 12, and S14 by 14. Thus, with a crystal frequency of approximately 3.58 MHz and input S14 terminated to  $V_{DD}$ , the clock A output frequency is 256 kHz, (3.58 MHz  $\div$  14 = 256 kHz).

Figure 2-5. Clock Generator Block Diagram

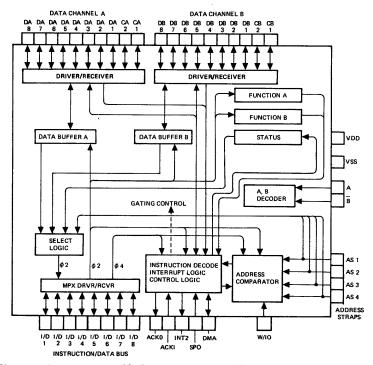

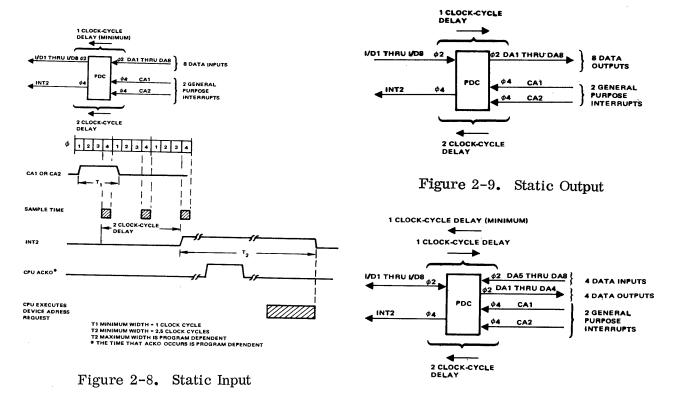

Figure 2-7. Parallel Data Controller Block Diagram

Figure 2-10. Static I/O

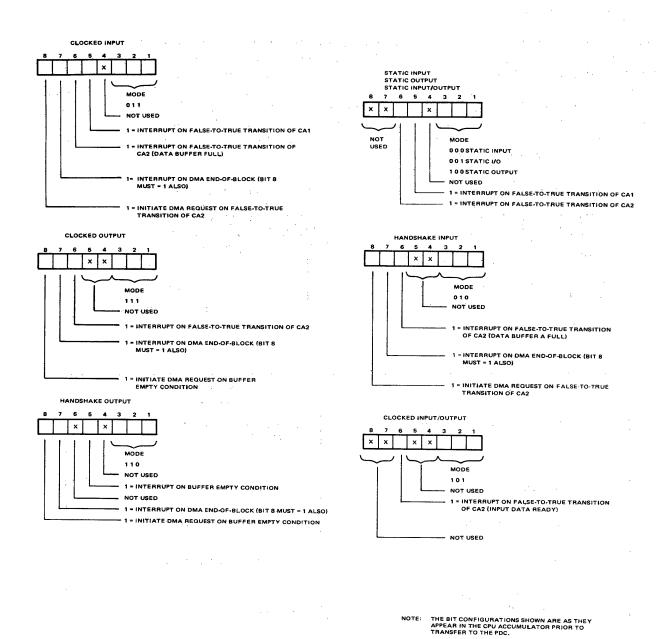

### Clocked Output (Figure 2-12)

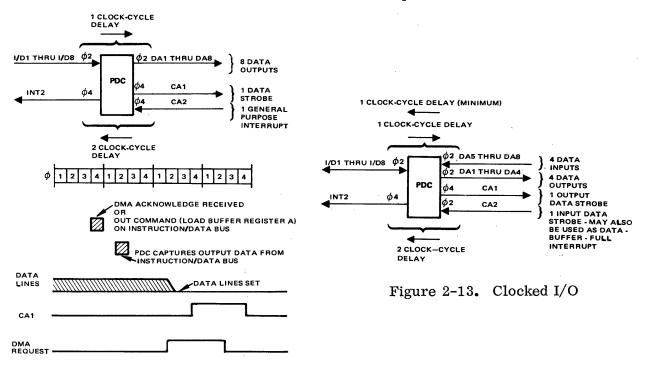

The data lines are driven continuously from the data buffer. The CPU can load the data buffer at any time. A positive pulse is generated on CA1 each time the data buffer is loaded by the CPU or (Channel A only) via DMA. Control line CA2 is selectable as a CPU interrupt. Interrupt timing for CA2 is identical to that for Static Input (Figure 2-8).

### Clocked I/O (Figure 2-13)

Data lines DA5 through DA8 are copied into the high order four bits of the data buffer on a TTL false-to-true transition of CA2 (same as for Clocked Input, Figure 2-11). Data lines DA1 through DA4 are driven continuously from the low order four bits of the data buffer. A positive pulse is generated on CA1 each time the data buffer is loaded by the CPU (same as for Clocked Output, Figure 2-12). The CPU can load or read the data buffer at any time. When the data buffer is loaded, only the low order four bits are modified. Control line CA2 is selectable as a CPU interrupt; interrupt timing for CA2 is identical to that shown for Clocked Input (Figure 2-11).

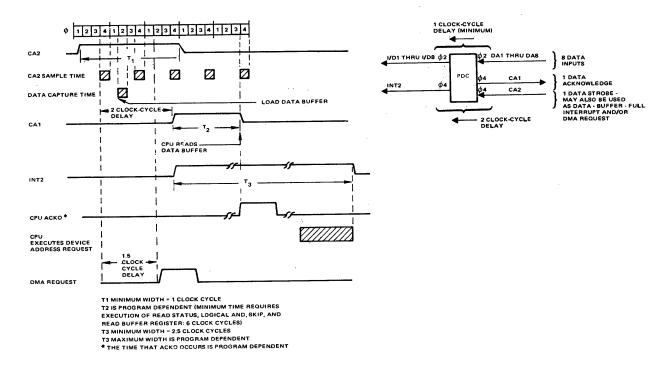

### Handshake Input (Figure 2-14)

Control lines CA1 and CA2 are both initially at a TTL false level. The data lines are then copied into the data buffer on a TTL false-to-true transition of CA2. Control line CA1 is set to a TTL true level immediately after loading the input data into the data buffer. The CPU may read the data buffer at any time after CA2 has made the false-to-true transition. CA1 is set to a TTL false level when the data buffer is read by the CPU (or stored in RAM via DMA), provided that CA2 has returned to TTL false level. Control line CA2 is selectable as a CPU interrupt and/or (Channel A only) a DMA request. Interrupt timing for CA2 is shown in Figure 2-14.

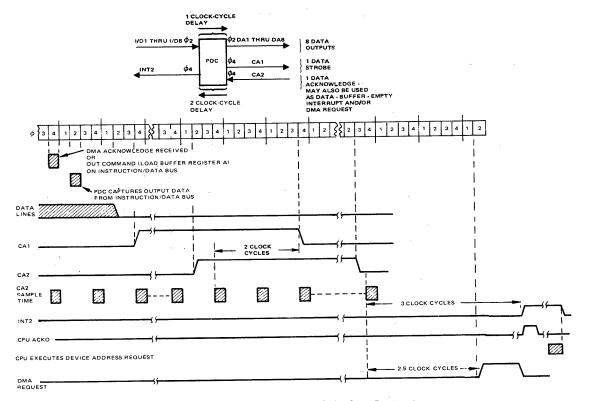

### Handshake Output (Figure 2-15)

The data lines are driven continuously from the data buffer. Control lines CA1 and CA2 are both initially at a TTL false level. Control line CA1 is then set to a TTL true level when the data buffer is loaded by the CPU or (Channel A only) via DMA. CA1 is set false on a TTL false-to-true transition of CA2. The data buffer may be reloaded any time after CA2 has returned false. Control line CA2 is selectable as a CPU interrupt and/or (Channel A only) a DMA request. Interrupt timing for CA2 is shown in Figure 2-15.

### Direct Memory Access

Four of the modes (Clocked Input, Clocked Output, Handshake Input and Handshake Output) allow optional DMA operation on Channel A.

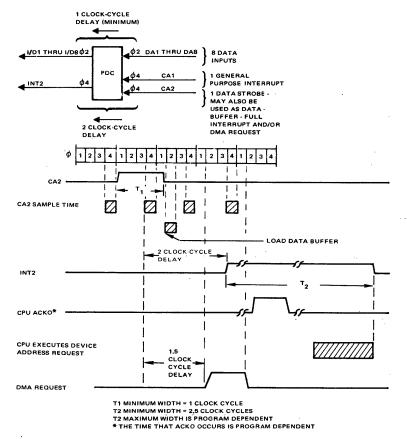

When the DMA option is selected for the Clocked Input mode or the Handshake Input mode, each DMA request is initiated 1.5 clock cycles after detection of the false-to-true transition of CA2 (see Figures 2-11 and 2-14).

When the DMA option is selected for the Clocked Output mode, the initial request is initiated immediately after Function Register A is loaded with the control data selecting the mode and option. The second and subsequent requests are initiated during  $\phi 2$  preceding the TTL true period of CA1 (see Figure 2-12). These requests will continue to be generated with each output until the PDC is automatically informed of an end-of-block condition by the Direct Memory Access Controller.

Figure 2-11. Clocked Input

Figure 2-12. Clocked Output

Figure 2-14. Handshake Input

Figure 2-15. Handshake Output

When the DMA option is selected for the Handshake Output mode, the initial request is initiated immediately after Function Register A is loaded with the control data selecting the mode and option. The second and subsequent DMA requests are initiated following completion of the Handshake Output cycle, i.e., during the third  $\emptyset$ 2 following the TTL true-to-false transition of CA2 (see Figure 2-15).

### **Function Registers**

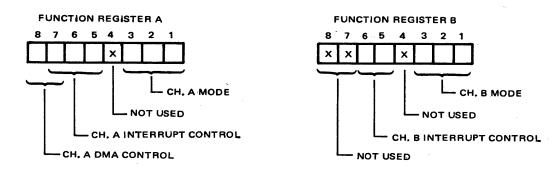

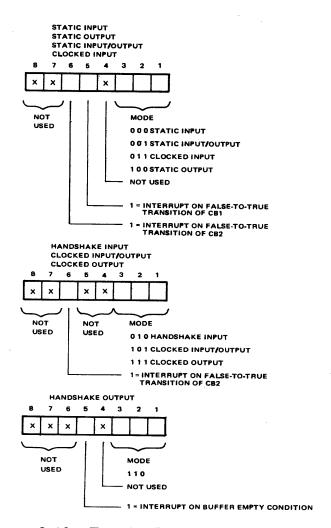

The functions (modes) of each channel are programmable and are controlled by the associated function register. Each register is loaded with a control word under CPU program control. Figure 2-16 shows the fields in each of the function registers. As indicated in Figure 2-16, each channel provides eight basic I/O modes; different modes can be programmed and operated simultaneously on the two channels. Figures 2-17 and 2-18 shows the bit meanings for Function Register A and Function Register B, respectively. Channels A and B have similar modes; however, only Channel A can initiate direct memory access requests.

| в≬т | FUNCTION REGISTER A                | FUNCTION REGISTER B                   |

|-----|------------------------------------|---------------------------------------|

| 1-3 | ESTABLISHES 1 OF 8 BASIC           | ESTABLISHES 1 OF 8 BASIC<br>I/O MODES |

| 4   | NOT USED                           | NOT USED                              |

| 5   | CA1 INTERRUPT CONTROL              | CB1 INTERRUPT CONTROL                 |

| 6   | CA2 INTERRUPT CONTROL              | CB2 INTERRUPT CONTROL                 |

| 7   | DMA END-OF-BLOCK INTERRUPT CONTROL | NOT USED                              |

| 8   | DMA ENABLE                         | NOT USED                              |

Figure 2-16. Function Register Fields

Figure 2-17. Function Register A Bit Interpretation

Figure 2-18. Function Register B Bit Interpretation

Figure 2-19. PDC Status Register Format

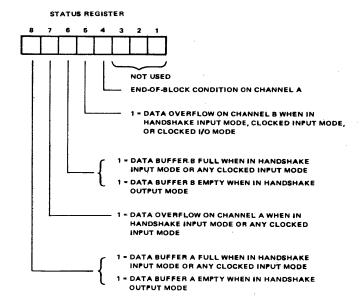

### Status Register

The contents of the Status Register can be copied into the CPU accumulator under program control. Figure 2-19 shows the format of the information contained in the Status Register.

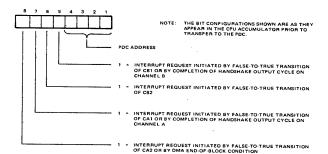

### Interrupt Status Word

NOTE: Refer to Section 3 for a description of the interrupt system.

When the PPS-8 CPU executes a Read Interrupt Status command, the PDC will transmit an interrupt status word to the CPU accumulator provided that the following two conditions are both met.

- 1) The PDC is requesting interrupt service (INT2 true).

- 2) The PDC has received the ACKI acknowledge pulse from the CPU.

Note that in a PPS-8 system containing multiple PDC devices, the above conditions will be true for only one device at any given time.

Figure 2-20 shows the format and information contained in the interrupt status word. The exact meaning of this information depends upon the current PDC mode (see Table 2-1).

### PDC Instruction Set

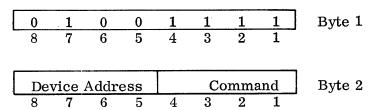

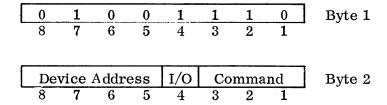

The PDC responds to eight commands from the PPS-8 CPU. Four of these are of the output (OUT) type and are described below.

1) LFRA – Load Function Register A

This command loads Function Register A with the contents of the CPU accumulator and resets bits 4, 7 and 8 of the status register.

2) LFRB – Load Function Register B

This command loads Function Register B with the contents of the CPU accumulator and resets bits 5 and 6 of the status register.

3) LBRA - Load Buffer Register A

This command loads Buffer Register A with the contents of the CPU accumulator and resets bit 8 of the status register.

4) LBRB – Load Buffer Register B

This command loads Buffer Register B with the contents of the CPU accumulator and resets bit 6 of the status register.

The remaining four commands are of the input (IN) type and are described below.

5) RBRA – Read Buffer Register A

The contents of Buffer Register A are placed in the CPU accumulator and bit 8 of the status register is reset.

Figure 2-20. Interrupt Status Word

|                                             | INTERPRETATION                         |                                                            |                                        |                                                            |  |  |  |  |

|---------------------------------------------|----------------------------------------|------------------------------------------------------------|----------------------------------------|------------------------------------------------------------|--|--|--|--|

|                                             | CH, A INTE                             | RRUPT STATUS                                               | CH. B INTERRUPT STATUS                 |                                                            |  |  |  |  |

| MODE                                        | Bit 8 = 1                              | Bit 7 = 1                                                  | Bit 6 = 1                              | Bit 5 = 1                                                  |  |  |  |  |

| Static Input<br>Static Output<br>Static I/O | CA2 Interrupt                          | CA1 Interrupt                                              | CB2 Interrupt                          | CB1 Interrupt                                              |  |  |  |  |

| Clocked Input<br>Without DMA                | CA2 Interrupt<br>(Data Buffer<br>Full) | CA1 Interrupt                                              | CB2 Interrupt<br>(Data Buffer<br>Full) | CB1 Interrupt                                              |  |  |  |  |

| Clocked Input<br>with DMA                   | End-of-Block<br>Interrupt              | CA1 Interrupt                                              |                                        |                                                            |  |  |  |  |

| Clocked Output<br>Without DMA               | CA2 Interrupt                          |                                                            | CB2 Interrupt                          |                                                            |  |  |  |  |

| Clocked Output<br>With DMA                  | End-of-Block<br>Interrupt              |                                                            |                                        |                                                            |  |  |  |  |

| Clocked I/O                                 | CA2 Interrupt<br>(Input Data<br>Ready) |                                                            | CB2 Interrupt<br>(Input Data<br>Ready) |                                                            |  |  |  |  |

| Handshake Input<br>Without DMA              | CA2 Interrupt<br>(Data Buffer<br>Full) |                                                            | CB2 Interrupt<br>(Data Buffer<br>Full) |                                                            |  |  |  |  |

| Handshake Input<br>With DMA                 | End-of-Block<br>Interrupt              |                                                            |                                        |                                                            |  |  |  |  |

| Handshake Output<br>Without DMA             |                                        | Channel A<br>Handshake<br>Cycle Com-<br>plote<br>Interrupt |                                        | Channel B<br>Handshake<br>Cycle Com-<br>plete<br>Interrupt |  |  |  |  |

| Handshake Output<br>With DMA                | End-of-Block<br>Interrupt              |                                                            |                                        |                                                            |  |  |  |  |

NOTE: Bit bit polarities shown are as they appear in the CPU accumulator after transfer from the PDC.

Table 2-1. Interrupt Status Word Interpretation

### 6) RBRB - Read Buffer Register B

The contents of Buffer Register B are placed in the CPU accumulator and bit 6 of the status register is reset.

### 7) RSR - Read Status Register

The contents of the Status Register are placed in the CPU accumulator and bits 5 and 7 of the status register are reset.

### 8) RIS - Read Interrupt Status

If the appropriate conditions are met (see text: Interrupt Status Word), the contents of the Interrupt Status Word are placed in the CPU accumulator. (This command is unique in that it always contains a device address of 0.)

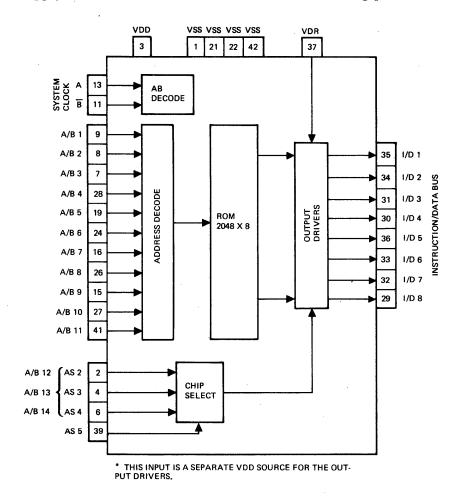

### DIRECT MEMORY ACCESS CONTROLLER (DMAC)

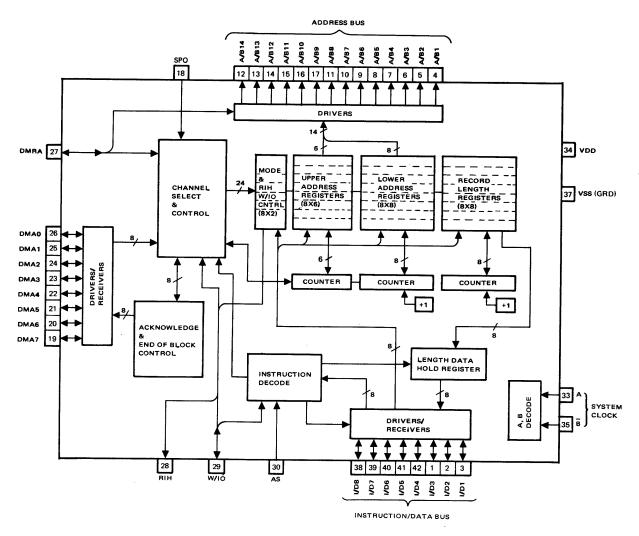

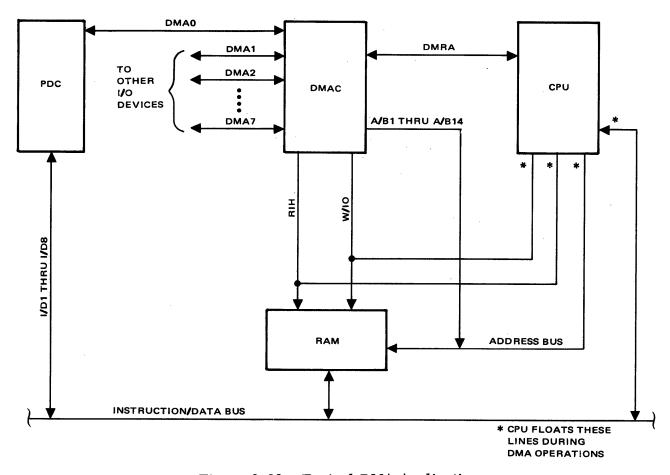

The Direct Memory Access Controller (DMAC), Part No. 10817, allows PPS-8 I/O devices to access RAM on a cycle-steal basis without disturbing CPU program execution. The DMAC (Figure 2-21) provides control of the Address Bus (A/B1 through A/B14) and two memory control signals (RIH and W/IO) during direct memory access (DMA) operations. Control for eight separate DMA channels is provided by a single DMAC.

Eight DMA request/acknowledge lines (DMA0 through DMA7) provide bidirectional communication between the I/O devices and the DMAC. Bidirectional communication over a single line is accomplished through the use of time multiplexing and pulse coding techniques. Each DMA line (channel) has a fixed position in a priority structure used to resolve simultaneous requests. The channels are numbered in order of priority, with DMA0 having the highest priority. An additional DMA request/acknowledge line (DMRA) provides bidirectional communication between the DMAC and the CPU.

Eight 14-bit address registers and eight 8-bit record length registers are included in the DMAC; one address register and one record length register are associated with each of the eight DMA channels. Each register can be loaded under CPU program control. Two additional control bits are provided for each of the DMA lines. One of these control bits specifies whether the RAM is to read or to write when a DMA request occurs on the associated DMA line. The other control bit is used to select a special cycle mode; the purpose of this mode is described under Record Cycle Mode.

A holding register, associated with the record length registers, allows the CPU to sample the contents of any record length register. When any record length register is loaded by the CPU, the previous contents of that register are transferred to the holding register. The contents of the holding register may be read under CPU program control.

Figure 2-22 shows a typical DMAC application. For simplicity, only a single I/O device, a Parallel Data Controller (PDC), is shown connected to the DMAC. When the PDC requires DMA service, it transmits a pulsed DMA request over DMAO. The DMAC forwards the DMA request to the CPU over DMRA. The CPU acknowledges the DMA request at the completion of the current instruction, provided that the instruction is a non-I/O type. If the CPU is executing an I/O instruction, it will continue program execution until it has completed a non-I/O instruction, at which time it will acknowledge the DMA request. The CPU then enters a "wait" mode, during which it floats its Address Bus drivers, Data Bus drivers, RIH and W/IO. This wait mode is retained until completion of the DMA operations.

When the DMAC receives the CPU acknowledge signal, the following operations occur:

- 1) The DMAC drives an acknowledge signal over the highest priority line currently requesting service.

- 2) The DMAC drives the Address Bus with the contents of the appropriate address register.

Figure 2-21. Direct Memory Access Controller Block Diagram

- 3) The DMAC drives RIH and W/IO false or true, depending upon whether the addressed RAM is to read or write.

- 4) The I/O device either drives data onto or captures data from the I/D Bus.

After each byte is transferred, the DMAC increments the appropriate address register and record length register. The DMA operations continue until one of the following events occurs.

- 1) The I/O device ceases to request DMA service.

- 2) The record length register makes a transition from 255 to zero.

- 3) The lower address register makes a transition from all ones to zeros.

- 4) CPU interrupt 0 is triggered.

- 5) The DMAC receives a request on a higher priority channel than that currently being serviced.

Figure 2-22. Typical DMA Application

The effects of each of the above five events are described in the following five paragraphs.

When the I/O device ceases to request DMA service, the DMAC, in turn, drops its request to the CPU (provided that no other DMA requests are present) and the CPU resumes program execution. If additional DMA requests are present, the DMAC maintains its request to the CPU and automatically switches to the highest priority channel requesting service.

When the record length register makes the transition from 255 to zero, the requesting I/O device is informed of the end-of-block condition (via a pulse-coded signal transmitted over the DMA line) and the DMAC drops its request to the CPU, allowing resumption of CPU program execution. If the I/O device continues to request DMA service after being informed of the end-of-block condition, the DMAC delays for three clock cycles and then again requests DMA service from the CPU. Thus, when the record length register makes the transition from 255 to zero, the CPU is allowed to execute instructions for a minimum of three clock cycles before the DMA request is again honored. (The CPU will not honor the DMA request at the completion of the current instruction if that instruction is an I/O command; i.e., the CPU will continue to execute instructions until it has executed a non-I/O command, at which time it will honor the request.)

When the lower address register makes a transition from all ones to all zeros, a carry is propagated through the lower address register and into the upper address register. That is, when the lower address register goes from all ones to all zeros, the upper address register is incremented by one. Each time this operation occurs, the DMAC drops the acknowledge signal to the I/O device and the request signal to the CPU. One clock cycle later (assuming that the I/O device is still requesting DMA service), the DMAC again requests DMA service from the CPU.

When CPU interrupt 0 (INTO) is triggered, the DMAC is allowed to complete the byte transfer currently in progress; thereafter, the CPU ignores the state of DMRA and resumes program execution. When power is restored, SPO clears all DMA acknowledge signals and no further DMA operations occur until another DMA request is received.

When the DMAC receives a DMA request on a higher priority DMA channel than that currently being serviced, it completes the byte transfer currently in progress and then drops the acknowledge signal on the original (lower priority) channel. The DMAC then automatically switches to the higher priority channel and continues the DMA operation.

### Record Cycle Mode

A control bit associated with each of the address registers is used to command a special Record Cycle Mode. This mode is available for any of the first seven channels. The control bit is loaded from the CPU: when the control bit is set (1), normal operation (as previously described) occurs; when the control bit is reset (0), the Record Cycle Mode is commanded. When an I/O device requests DMA service and the channel associated with the I/O device is in the Record Cycle Mode, the bytes are transferred as in normal operation until the lower address register (8 bits) makes the transition from 255 to zero. At this time, the contents of the Channel 7 record length register, address register, and control register (2 bits) are automatically transferred to the corresponding registers of the channel operating in the Record Cycle Mode. That is, the address register, record length register, and control register of the channel operating in the Record Cycle Mode are reset to the values stored in the corresponding Channel 7 registers. DMA operation then continues as previously described. Typical use of the Record Cycle Mode involves loading the Channel 8 registers with the same data that is initially loaded into the registers of the channel that is to operate in the Record Cycle Mode; thus, as long as the DMA request is present, the record (beginning at the address specified by the initial contents of the address register and ending at the next address boundry, modulo 256) will be repeatedly transferred between RAM and the I/O device. It should be noted that use of Channel 7 for DMA service is precluded when any channel is in the Record Cycle Mode.

### DMA Instruction Set

The DMAC responds to four commands from the PPS-8 CPU. Three commands are of the OUT type and one is of the IN type. These commands are described in Table 2-2. (The basic IN/OUT command format is discussed in Section 3.) As indicated in Section 3, the second byte of the two-byte IN/OUT command contains a 3-bit command field and a 4-bit address field. The command code is interpreted and executed by the addressed I/O device. Normally, the address of an I/O device is

Table 2-2. DMAC Instructions

| INSTRUCTION                        |          |                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                               | MNEMONIC | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |

| Load<br>Address Register,<br>Lower | LARL     | Transfers contents of CPU accumulator to lower DMAC address register N (where N is the number coded in the lower 3 bits of the instruction address field)                                                                                                                                                                                                                                                        |

| Load<br>Address Register,<br>Upper | LARU     | Transfers contents of CPU accumulator (bits 1 through 6) to corresponding bits of the upper DMAC address register N (where N is the number coded in the lower 3 bits of the instruction address field). Bit 7 of CPU accumulator is transferred to Channel N mode control bit (1 = Normal Mode; 0 = Record Cycle Mode). Bit 8 of CPU accumulator is transferred to Read/Write control bit (0 = Read; 1 = Write). |

| Load Record<br>Length Register     | LRLR     | Transfers contents of CPU accumulator to record length register N (where N is the number coded in the lower 3 bits of the instruction address field). Previous contents of record length register N are transferred to holding register.                                                                                                                                                                         |

| Read Holding<br>Register           | RHR      | Transfers contents of the record length holding register to CPU accumulator.                                                                                                                                                                                                                                                                                                                                     |

unique and, therefore, there is no possibility of an I/O device interpreting and executing an I/O command intended for some other I/O device. However, the DMAC has a single address strap; only the most significant bit of the 4-bit address field is used to address the DMAC (the lower three bits of the device address field in this case refer to the DMA channel number). Thus, if the address strap (AS) is connected to VSS (logic level zero), the DMAC will respond to any address in the range of zero to seven. Conversely, if AS is connected to VDD (logic level one), the DMAC will respond to any address in the range of 8 to 15. Therefore, care should be taken to ensure that any I/O device whose address falls within the selected DMAC address range does not share any common command codes with the DMAC. (At the time of this writing, the only I/O device that shares common command codes with the DMAC is the TDI. The TDI should not be assigned an address that falls within the selected DMAC address range.)

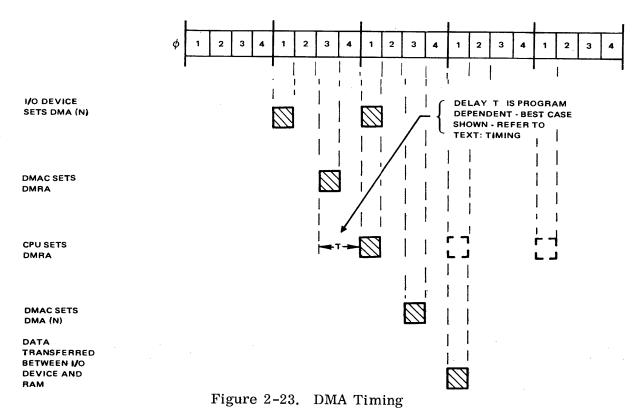

### Timing

Figure 2-23 shows the DMA timing. As shown, there is a one-half clock cycle delay from the time that the DMAC receives a request from an I/O device until the time that the DMAC requests service from the CPU. The CPU response time is variable. depending upon the instruction being executed at the time that it receives the DMA request. The best-case condition exists when the current instruction is a non-I/O type whose execution will be completed during the clock cycle following that in which the request is received; in this case, there is a one-half clock cycle delay from the time that the CPU receives the request until the time that it sends an acknowledge pulse to the DMAC. The worst-case condition exists when the CPU is executing an I/O command (or a series of I/O commands). The CPU will continue program execution until it has executed a non-I/O command before it will acknowledge the DMA request. Completion of the I/O command may take one, or two clock cycles; completion of the following command may take one, two or three clock cycles. Thus, if the CPU is executing an I/O command at the time that it receives the DMA request, the maximum delay before it acknowledges the request will be four and one-half clock cycles (assuming that the command following the I/O command is a non-I/O type).

There is a one-half clock cycle delay from the time that the DMAC receives the acknowledge pulse from the CPU until the time that the DMAC, in turn, transmits an acknowledge pulse on the highest priority DMA channel requesting service. Thus, the total delay from the time that an I/O device requests DMA service until it receives an acknowledge pulse is from one and one-half to five and one-half clock cycles (assuming that no higher priority devices are requesting DMA service and that the CPU is not executing a series of I/O commands).

### SPECIAL PURPOSE INPUT/OUTPUT DEVICES

The high degree of flexibility found in the PPS-8 allows the use of a wide variety of special purpose input/output devices. Up to 16 of these special devices, in various combinations, may be directly connected to the PPS-8 at the same time, and through appropriate addressing the various devices can be utilized by the PPS-8 to control many different functions concurrently.

Each of the special purpose input/output devices is discussed in the following paragraphs. If additional detail information is required on any of these devices, refer to the applicable data sheet for the specific device.

### Printer Controller Circuit

The Printer Controller Circuit device, Part No. 10789, is used for control of the SEIKO 101, 102, and 104 printers. The printer controller interfaces directly to the PPS system without additional components. Printer control is accomplished in a stand-alone manner. That is, after the print data has been loaded from the PPS system, the printer controller circuit controls the printer without additional attention from the PPS system. Features of the printer controller circuit are:

- Up to 21 columns of print data.

- Up to 8 discrete outputs if less than 21 columns of print data are required.

- Red/black color control.

- Automatic generation of from one-to-eight paper feeds.

- Busy signal generation for informing the PPS system as to when a new print line may be initiated.

- One discrete input.

- Address strap to allow two printer controller circuits in the same system.

- Motor on/off control.

- Motor "up-to-speed" detection.

### Telecommunications Data Interface (TDI) Circuit

The Telecommunications Data Interface (TDI) circuit, Part No. 10371, together with external filters, gain circuitry, and an approved telephone network access arrangement, can provide either full-duplex or half-duplex, asynchronous data transmission. Transmission can be made over nonconditioned, voice-grade telephone lines. This device can be operated as a bit-serial universal modem or as an integral part of the Rockwell Parallel Processing System (PPS). Features of this device are listed below:

- Full-duplex operation

- Zero to 1200 bps transmission rate.

- Frequency modulation with controllable choice of two sets of modulation frequencies:

- CCITT (mark = 1300 Hz; space = 2100 Hz)

- Bell 202 (mark = 1200 Hz; space = 2200 Hz)

- TTL-compatible interface

- Controllable choice of two basic operating modes:

- Serial Mode: Operates as universal modem with no internal data formatting, buffering, etc.

- PPS Mode: Operates as part of PPS and as such has the following additional features

- -- Data buffering

- -- Automatic formatting: Unformatted, serial 8-bit words; character-formatted 8-bit words; variable-length words

- -- Interrupt-controlled transfers

- -- Controllable choice of even/odd parity

- -- Strap-selectable choice of 15 possible addresses (1 to 15)

### Bus Interface (B/I) Circuit

The Bus Interface (B/I) Circuit, Part No. 10738, is a multipurpose circuit designed to serve as an interface between the PPS address and data bus dynamic MOS level signals and static commercially available MOS or TTL peripheral memory devices. The B/I circuit can also be used to interface with core memories in those systems which must have a non-volatile memory. The B/I circuit is multipurpose in that it can be appropriately strapped at four input pins to act as an interface for 12 bits of the 14-bit address bus as well as the 8-bit instruction/data bus.

The B/I circuit provides the following features which involve timing, impedance, and logic level interfacing:

- Identical circuits for both instruction/data bus and address bus interface.

- Direct interface no external components needed.

- MOS-compatible interface.

- TTL-compatible interface.

- Static outputs.

### General Purpose Keyboard and Display (GPKD)

The General Purpose Keyboard and Display (GPKD) device, Part No. 10788, provides interfacing between the PPS-8 and a wide variety of keyboard and display devices. The GPKD connects directly with the PPS data bus and is initialized by the Synchronized Power-On (SPO) signal from the PPS-8 CPU.

The GPKD can strobe keyboards with up to 64 single-pole, single-throw momentary switches on an 8 x 8 matrix. A Nine-level, 8-bit key buffer allows up to nine key inputs to be stored until the PPS processes them. Inputs can be entered at an operating speed of 7.68 microseconds per character.

Up to 16 characters of display data can be controlled. The GPKD uses two hexadecimal outputs for data display, (eight outputs). A typical application of the data display is to use 4 bits, (one hexadecimal character) for numeric display, 2 bits for display of decimal point and comma, and the remaining 2 bits for display of up to 32 status indicators.

The following features are found in the GPKD:

### KEYBOARD

- Nine-Key Buffering

- Two-Key Rollover

- 7.68 msec Key Debounce Delay

- Handle up to 64 keys on 8 x 8 matrix

- Chip Address Strap Encoded

- Initialized at Power On (SPO)

### DISPLAY

- Display up to 16 characters

- 32 Digits of Display Possible

- Two 16-Digit Display Buffers

- Two Sets of Hexadecimal Code Outputs for Display

- TTL Compatible Interface

- Five Percent (5%) Duty Cycle

### Serial Data Controller (SDC)

The Serial Data Controller (SDC), Part No. 10930, is a digital receiver-transmitter that interfaces the PPS-8 (or PPS-4) Instruction/Data Bus (eight parallel lines) to a serial communications channel. The SDC is capable of full-duplex or half-duplex operation at synchronous rates up to 250K-bits per second and asynchronous rates up to 18K-Baud. Input/output signals are directly compatible with TTL, MOS and CMOS. Significant features of the SDC are listed below.

- Full-Duplex or Half-Duplex Operation

- Synchronous or Asynchronous Operation

- Fully Programmable All Control Stored in Internal Control Registers

- Interrupt Request on Receiver Buffer Full, Transmitter Buffer Empty, DMA End-of-Block, and Character Compare

- DMA Request on Receiver Buffer Full or Transmitter Buffer Empty

- Automatic Error Detection (Parity, Receiver Overrun, Framing and Carrier Detect Dropout)

- Receive and Transmit Simultaneously at Different Rates if Desired

- Programmable Transmission Codes:

- Character Length of 5, 6, 7, or 8 Bits

- Even Parity, Odd Parity or No Parity

- One or Two Stop Bits (1 7/16 Stop Bits when 5-Bit Character and X16 Clock Asynchronous Operation are Selected)

- Double Buffered Data Input and Output

- Transmitter Clock Output (Output Clock at Transmitted Bit Rate)

- Three Discrete Inputs and Two Discrete Outputs

- Automatic Status Generation

- Programmable Character Search Mode Facilitates Party Line Operation

- Strap-Selectable 4-Bit or 8-Bit Operation for Compatibility with PPS-4 and PPS-8

### Section 3. PRINCIPLES OF OPERATION

### BASIC SYSTEM OPERATION

During each program counter bit time, the CPU will address the instruction memory, (ROM), read and decode the instruction, execute the instruction, increment (or load) the program counter in preparation for the next instruction. This bit time or a single cycle instruction execution time is 4  $\mu s$  at a 250 KHz frequency. The proprietary instruction architecture and multiphase clocking scheme of the 8-bit CPU result in unusually high data handling rates for a relatively slow external clocking system.

### SYSTEM TIMING

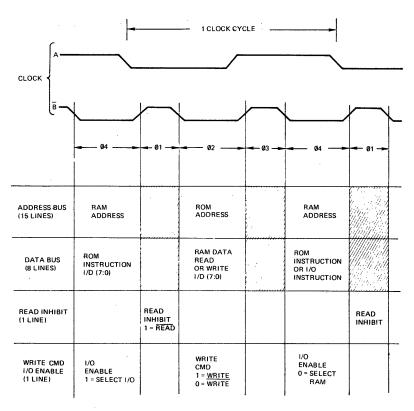

The PPS circuits are controlled from a crystal controlled clock generator which provides two synchronized and phased clock signals. These signals, designated A and  $\bar{B}$ , are received by the CPU and they are logically divided into four phases, such that the internal signals are being manipulated at four times the frequency of the external A clock. For example, assume A clock is 250 KHz, logic signal flow within the CPU would occur at 1 MHz. The basic clock timing is shown in Figure 3-1.

The PPS parallel bus transfer lines are synchronized by the A and  $\bar{B}$  clock signals such that data transfer occurs only during  $\emptyset 2$  and  $\emptyset 4$  time as depicted by Figure 3-1.

### LOGIC LEVELS

A negative logic notation is used in the PPS-8 system. That is, a logic one (1) is defined as the most negative voltage, while a logic zero (0) is defined as the most positive voltage.

### MULTIPLEX SYSTEM DATA TRANSFER

In addition to the power and clock signals, there are 24 multiplexed lines interconnecting the CPU with ROM, RAM, and I/O devices. These lines are functionally grouped as follows:

- 14 Parallel Address Lines (A/B 1 through 14)

- 8 Parallel Bidirectional Data Lines (I/D 1 through 8)

- 1 Write Command/I/O Enable Line (W/I O)

- 1 Read Inhibit (RIH)

The fourteen address lines originate from the CPU and are time multiplexed within the CPU to provide direct addressing capability for up to 16,384 8-bit bytes of ROM and 16,384 bytes of RAM.

As are the address lines, the eight data bus lines are time shared lines between the CPU, ROM, RAM and I/Os.

Figure 3-1. Parallel Processing System Bus Timing

During \$\psi2\$, a logical one (1) on the write enable line is interpreted by the RAMS as a write enable command and the data on the bus will be written into RAM using the preceding \$\psi4\$ address. During the preceding \$\psi1\$, the RAM would be commanded not to read via the Read Inhibit Command (logical 1). The RAM is a non-destructive readout device and is always programmed to read unless instructed not to by the "read inhibit" command.

The same line providing the write command to RAM during  $\emptyset 2$  time serves as an I/O Enable signal during  $\emptyset 4$  time when communication is desired to (or from) an I/O device addressed on the data bus. If the I/O enable is on (logical 1) at  $\emptyset 4$ , the "Read Inhibit" line will be used to disable the RAM during the  $\emptyset 2$  transmittal of information between the CPU and the addressed I/O device.

### INSTRUCTION REPERTOIRE

The PPS-8 has an extensive instruction repertoire for performing a variety of arithmetic, logical, and data manipulation functions in a manner which is efficient, both in instruction memory required and speed of execution. Most instruction types require only a single 8-bit byte, but 2 and 3 byte formats are also included to provide extended addressing/functional capability.

The instructions are listed in Table 3-1. In the table, reference is made to notes. The applicable notes are listed following the table.

The symbology used in the instruction descriptions in Table 3-1 is defined below.

| <i>y</i>                          | •                                                         |

|-----------------------------------|-----------------------------------------------------------|

| Symbol                            | Symbolic Notation Item or Function                        |

| A                                 | Accumulator Register A(1:8)                               |

| X                                 | RAM Address Register and Index, X(1:8)                    |

| Y                                 | RAM Address Register Y(1:8)                               |

| ${f Z}$                           | RAM Address Register Z(1:8)                               |

| f L                               | Link Register L(1:16)                                     |

| P                                 | Program Counter Register P(1:14)                          |

| S                                 | Stack Pointer Register                                    |

| W                                 | The W Register                                            |

| C                                 | Carry Flip-Flop                                           |

| IC                                | Intermediate state of Carry Flip-Flop                     |

| Q                                 | Intermediate Carry Flip-Flop                              |

| I                                 | Instruction I(1:8)                                        |

| I1                                | First byte of multiple byte instruction I1(1:8)           |

| I2                                | Second byte of multiple byte instruction I2(1:8)          |

| I3                                | Third byte of multiple byte instruction 13(1:8)           |

| M                                 | RAM memory contents                                       |

| R(n)                              | Bit n of Register R                                       |

| R(n:m)                            | Bit n through m of R, inclusively                         |

| W/IO                              | Write and I/O Enable Control Line                         |

| RIH                               | Read Inhibit Control Line                                 |

| Byte                              | Eight-bit Data Field                                      |

| Digit                             | Four-bit Data Field                                       |

| Page                              | Block of 128 bytes                                        |

|                                   | Replaces (or ← )                                          |

| R                                 | Exchange                                                  |

|                                   | 1's complement of state R.                                |

| ^<br>V                            | Logical Product (AND)                                     |

| <b>∀</b>                          | Logical Sum (Inclusive OR)                                |

| _                                 | Logical (Exclusive OR) Algebraic Subtract                 |

| +                                 | Algebraic Add                                             |

|                                   | Greater than                                              |

| > <                               | Less than                                                 |

| =                                 | Equal to                                                  |

| I/D(8:1)                          | Instruction/Data Bus (lines 1 through 8)                  |

| (L)                               | ROM memory contents addressed by L                        |

| $SP_{\mathbf{u}}$                 | Byte from upper address portion of Subroutine Entry Pool  |

| g D                               | Byte from lower address portion of Subroutine Entry Pool  |

| $^{\mathrm{SP}}_{1}^{\mathrm{T}}$ | Dyte from lower address portion of publicatine many 1 our |

Table 3-1. List of Instructions

|          |                                                       |       | ,      | DESCRIPTION                                                                                    |                                                                     |              |

|----------|-------------------------------------------------------|-------|--------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------|

| MNEMONIC | NAME                                                  | BYTES | CYCLES | VERBAL                                                                                         | SYMBOLIC                                                            | NOTES        |

| Ļ        | Load A                                                | 1     | 1 .    | The current RAM operand is placed in the accumulator                                           | A←M                                                                 | 1            |

| LN       | Load A, Increment<br>Address                          | 1     | 1      | Same as L. Additionally, the X register is incremented                                         | A <b>←</b> M<br>X <b>←</b> X+1, skip if X=0                         | 1,2,8        |

| LD       | Load A, Decrement<br>Address                          | 1     | 1      | Same as L. Additionally, the X register is decremented                                         | A ← M<br>X ← X-1,<br>skip if X=127                                  | 1,2,8        |

| LNXL     | Load A, Increment<br>Address, Exchange L              | 1     | 1      | Same as LN. Additionally, the contents of the L register and the Z & X registers are exchanged | A ← M<br>X ← X+1, skip if X=0<br>Z, X ← L                           | 1,2,8        |

| LDXL     | Load A, Decrement<br>Address, Exchange L              | 1     | 1 .    | Same as LD. Additionally, the contents of the L register and the Z & X registers are exchanged | A ← M<br>X ← X-1,<br>skip if X=127<br>Z,X ← L                       | 1,2,8        |

| LNCX     | Load A, Increment<br>& Compare Address,<br>Exchange L | 1     | 1      | Same as LNXL. Additionally, the next instruction is skipped if X = Y                           | A ← M<br>X ← X+1<br>Skip if X=0 or X=Y<br>Z,X ← L                   | 1,2,8,<br>19 |

| LDCX     | Load A, Decrement &<br>Compare Address,<br>Exchange L | 1     | 1      | Same as LDXL. Additionally,<br>the next instruction is skipped if<br>X = Y                     | A ← M<br>X ← X-1<br>Skip if X=127 or X=Y<br>Z,X ← ► L               | 1,2,8,<br>19 |

| LNXY     | Load A, Increment<br>Address, Exchange Y              | 1     | 1      | Same as LN. Additionally, the contents of the X & Y registers are exchanged                    | A ← M<br>X ← X+1, skip if X=0<br>X ← Y                              | 1,2,8        |

| S        | Store A                                               | 1     | 1      | The contents of the accumulator are stored in the current RAM operand address                  | M <b>←</b> A                                                        | 1            |

| SN       | Store A, Increment<br>Address                         | 1     | 1      | Same as S. Additionally, the X register is incremented                                         | M <b>←</b> A<br>X <b>←</b> X+1, skip if X=0                         | 1,2,8        |

| SD       | Store A, Decrement<br>Address                         | 1     | 1      | Same as S. Additionally, the X register is decremented                                         | M ← A<br>X ← X-1,<br>skip if X=127                                  | 1,2,8        |

| SNXL     | Store A, Increment<br>Address, Exchange L             | 1 .   | 1      | Same as SN. Additionally, the contents of the L register and the Z & X registers are exchanged | M ← A<br>X ← X+1, skip if X=0<br>Z,X ← ► L                          | 1,2,8        |

| SDXL     | Store A, Decrement<br>Address, Exchange L             | 1     | 1      | Same as SD. Additionally, the contents of the L register and the Z & X registers are exchanged | M <b>←</b> A<br>X <b>←</b> X-1,<br>skip if X=127<br>Z,X <b>←</b> ►L | 1,2,8        |

Table 3-1. List of Instructions (Continued)

|          |                                                         |       |        | DESCRIPTI                                                                                                                                      | DN                                              |                |

|----------|---------------------------------------------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------|

| MNEMONIC | NAME                                                    | BYTES | CYCLES | VERBAL                                                                                                                                         | SYMBOLIC                                        | NOTES          |

| SNCX     | Store A, Increment<br>& Compare Address,<br>Exchange L  | 1     | 1      | Same as SNXL. Additionally, the next instruction is skipped if X = Y                                                                           | M←A<br>X←X+1<br>Skip if X=0 or X=Y<br>Z,X←►L    | 1,2,8,<br>19   |

| SDCX     | Store A, Decrement<br>& Compare Address,<br>Exchange L  | 1     | 1      | Same as SDXL. Additionally, the next instruction is skipped if X = Y                                                                           | M←A, X←X-1<br>Skip if X=127 or X=Y<br>Z,X←►L    | 1,2,8,<br>19   |

| SNXY     | Store A, Increment<br>Address, Exchange Y               | 1     | 1      | Same as SN. Additionally, the contents of the X and Y registers are exchanged                                                                  | M ← A<br>X ← X+1, skip if X=0<br>X ← Y          | 1,2,8          |

| Х        | Exchange                                                | 2     | 2      | These instructions are identical to the corresponding store instructions except that the accumulator and the current RAM operand are exchanged | A <b>≪→</b> M                                   | 1,6            |

| XN       | Exchange, Increment<br>Address                          | 2     | 2      |                                                                                                                                                | A◀►M<br>X◀─X+1, skip if X=0                     | 1,2,6,8        |

| XD       | Exchange, Decrement<br>Address                          | 2     | 2      |                                                                                                                                                | A◀►M<br>X◀─X-1,<br>skip if X=127                | 1,2,6,8        |

| XNXL     | Exchange, Increment<br>Address, Exchange L              | 2     | 2      |                                                                                                                                                | A → M<br>X → X+1, skip if X=0<br>Z,X → L        | 1,2,6,8        |

| XDXL     | Exchange, Decrement<br>Address, Exchange L              | 2     | 2      |                                                                                                                                                | A→M<br>X→X-1,<br>skip if X=127<br>Z,X→►L        | 1,2,6,8        |

| XNCX     | Exchange, Increment &<br>Compare Address,<br>Exchange L | 2     | 2      |                                                                                                                                                | A→M<br>X←-X+1<br>Skip if X=0 or X=Y<br>Z,X←►L   | 1,2,6,8,<br>19 |

| XDCX     | Exchange, Decrement<br>& Compare Address,<br>Exchange L | 2     | 2      | These instructions are identical to the corresponding store instructions except that the accumulator and the current RAM operand are exchanged | A→M<br>X→-X-1<br>Skip if X=127 or X=Y<br>Z,X→-L | 1,2,6,8,<br>19 |

Table 3-1. List of Instructions (Continued)

| ٠.       |                                            |       |        | DESCRIPTION                                                                                                                                    | l l                                    |         |

|----------|--------------------------------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------|

| MNEMONIC | NAME                                       | BYTES | CYCLES | VERBAL                                                                                                                                         | SYMBOLIC                               | NOTES   |

| XNXY     | Exchange, Increment<br>Address, Excahnge Y | 2     | 2      | These instructions are identical to the corresponding store instructions except that the accumulator and the current RAM operand are exchanged | A ←►M<br>X ←─X+1, skip if X=0<br>X ←►Y | 1,2,6,8 |

| LX       | Load X                                     | 1,2   | 2      | The current RAM operand is placed in the X register                                                                                            | X <b>←</b> M                           | 4       |

| LY       | Load Y                                     | 1,2   | 2      | The current RAM operand is placed in the Y register                                                                                            | Y <b>←</b> M                           | 4       |

| LZ       | · Load Z                                   | 1,2   | 2      | The current RAM operand is placed in the Z register                                                                                            | Z <b>←</b> M                           | 4       |

| LAI      | Load A Immediate                           | 1-3   | 3      | The specified literal operand is placed in the accumulator                                                                                     | A <b></b> ←13                          | 3,4     |

| LXI      | Load X Immediate                           | 1-3   | 3      | The specified literal operand is placed in the X register                                                                                      | X <b>←</b> I3                          | 3,4     |

| LYI      | Load Y Immediate                           | 1-3   | 3      | The specified literal operand is placed in the Y register                                                                                      | Y <b>4</b> —I3                         | 3,4     |

| LZI      | Load Z Immediate                           | 1-3   | 3      | The specified literal operand is placed in the Z register                                                                                      | Z <b>4</b> −13                         | 3,4     |

| LAL      | Load A through Link                        | 1,2   | 3      | The ROM operand addressed by the L register is placed in the accumulator                                                                       | W ← A,<br>A ← (L)<br>L ← L+1           | 4,5,14  |

| LXL      | Load X through Link                        | 1,2   | 3      | The ROM operand addressed by the L register is placed in the X register                                                                        | X <b>←</b> −(L)<br>L <b>←</b> −L+1     | 4,5     |

| LYL      | Load Y through Link                        | 1,2   | 3      | The ROM operand addressed by the L register is placed in the Y register                                                                        | Y <b>←</b> -(L)<br>L <b>←</b> -L+1     | 4,5     |

| LZL      | Load Z through Link                        | 1,2   | 3      | The ROM operand addressed by the L register is placed in the Z register                                                                        | Z <b>←</b> -(L)<br>L <b>←</b> -L+1     | 4,5     |

| LXA      | Load X from A                              | 1     | 1      | The contents of the accumulator are placed in the X register                                                                                   | X <b>⊸</b> A                           | 16      |

| LYA      | Load Y from A                              | 1     | 1      | The contents of the accumulator are placed in the Y register                                                                                   | Y <b>←</b> A                           | 16      |

| LZA      | Load Z from A                              | 1     | 1      | The contents of the accumulator are placed in the Z register                                                                                   | Z <b>←</b> A                           | 16      |

Table 3-1. List of Instructions (Continued)

|          |                            |       |        | DESCRIPTIO                                                                            | N                                |       |

|----------|----------------------------|-------|--------|---------------------------------------------------------------------------------------|----------------------------------|-------|

| MNEMONIC | NAME                       | BYTES | CYCLES | VERBAL                                                                                | SYMBOLIC                         | NOTES |

| LLA      | Load L from A              | 1     | 1      | The contents of the accumulator are placed in the upper 8 bits of the L register      | L(16:9) <b>←</b> A               | 16    |

| XY       | Exchange Y                 | 1     | 1      | The contents of the X and Y register are exchanged                                    | X <b>∢→</b> Y                    |       |

| XL       | Exchange L                 | 1     | 1      | The contents of the L register and the Z & X registers are exchanged                  | L <b>∢→</b> Z,X                  |       |

| XAX      | Exchange A and X           | 1     | 1      | The contents of the X register and the accumulator are exchanged                      | A <b>∢→</b> X                    |       |

| XAY      | Exchange A and Y           | 1     | 1      | The contents of the Y register and the accumulator are exchanged                      | A <b>∢→</b> Y                    |       |

| XAZ      | Exchange A and Z           | 1     | 1      | The contents of the Z register and the accumulator are exchanged                      | A <b>∢→</b> Z                    |       |

| XAL      | Exchange A and L           | 1     | 1      | The contents of the upper half of the L register and the accumulator are exchanged    | A <b>→</b> L(16:9)               |       |

| INCX     | Increment X                | 1     | 1      | The X register is incremented by one                                                  | X← X+1<br>Skip if X=0            | 2     |

| DECX     | Decrement X                | 1     | 1      | The X register is decremented by one                                                  | X <b>←</b> X-1<br>Skip if X=127  | 2     |

| INXY     | Increment X,<br>Exchange Y | 1.    | 1      | The X register is incremented and the contents of the X and Y registers are exchanged | X← X+1, skip if X=0<br>X←→Y      | 2     |

| DEXY     | Decrement X,<br>Exchange Y | 1     | 1      | The X register is decremented and the contents of the X and Y registers are exchanged | X← X-1,<br>skip if X=127<br>X←→Y | 2     |

| INCY     | Increment Y                | 2     | 2      | The Y register is incremented by one                                                  | Y <b>←</b> Y+1<br>Skip if Y=0    | 2,7,8 |

| DECY     | Decrement Y                | 2     | 2      | The Y register is decremented by one                                                  | Y <b>←</b> Y-1<br>Skip if Y=127  | 2,7,8 |

| PSHA     | Push A                     | 1,2   | 2      | The contents of the accumulator are pushed into the stack                             | A→ (S)<br>S ← S+1                | 4,13  |

| PSHX     | Push X                     | 1,2   | 2      | The contents of the X register pushed into the stack                                  | X-►(S)<br>S <b>-</b> S+1         | 4,13  |

| PSHY     | Push Y                     | 1,2   | 2      | The contents of the Y register are pushed into the stack                              | Y→ (S)<br>S ← S+1                | 4,13  |

| PSHZ     | Push Z                     | 1,2   | 2      | The contents of the Z register are pushed into the stack                              | Z→(S)<br>S←-S+1                  | 4,13  |

Table 3-1. List of Instructions (Continued)

|          |                                  |       |        | DESCRIPTIO                                                                                                     | N                                                                                                                     |        |

|----------|----------------------------------|-------|--------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------|

| MNEMONIC | NAME                             | BYTES | CYCLES | VERBAL                                                                                                         | SYMBOLIC                                                                                                              | NOTES  |

| PSHL     | Push L                           | 1     | 3      | The contents of the L register are pushed into the stack and replaced by the contents of the A and W registers | L → (S+1,S)<br>A,W → L<br>S ← S+2                                                                                     | 13,14  |