# R6500 Microcomputer System DATA SHEET

# Asynchronous Communication Interface Adapter (ACIA)

The R6551 Asynchronous Communication Interface Adapter (ACIA) provides a program-controlled interface between 8-bit microprocessor-based systems and serial communication data sets and modems.

With its on-chip baud rate generator, the R6551 is capable of transmitting at 15 different program-selectable rates between 50 baud and 19,200 baud, and receiving at either the transmit rate or at 16 times an external clock rate. The R6551 has programmable word lengths of 5, 6, 7, or 8 bits; even, odd or no parity; 1, 1-1/2 or 2 stop bits.

With the R6551, a crystal is the only required external support component — eliminating the multiple-component support that is typically needed.

In addition, the R6551 is designed for maximum programmed control from the CPU, to simplify hardware implementation. A control register and a separate command register permit the CPU to easily select the R6551's operating modes and check data, parameters and status.

#### **FEATURES**

- Compatible with 8-bit microprocessors

- Full duplex or half duplex operation with buffered receiver and transmitter

- 15 programmable Baud Rates (50 to 19,200)

- Receiver data rate may be identical to baud rate or may be 16 times the external clock input

- Data set/modem control functions

- Programmable word lengths, number of stop bits, and parity bit generation and detection

- Programmable interrupt control

- Software reset

- Program-selectable serial echo mode

- Two chip selects

- 2 MHz or 1 MHz clock rate

- Single +5V ±5% power supply

- 28-pin plastic or ceramic DIP

- Full TTL compatibility

| Ordering Information |                                                                                                                                                               |                                                    |                                                                                       |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Order                | Package                                                                                                                                                       | Frequency                                          | Temperature                                                                           |  |  |  |  |

| Number               | Type                                                                                                                                                          |                                                    | Range                                                                                 |  |  |  |  |

| R6551P               | Plastic                                                                                                                                                       | 1 MHz                                              | 0°C to +70°C                                                                          |  |  |  |  |

| R6551AP              | Plastic                                                                                                                                                       | 2 MHz                                              | 0°C to +70°C                                                                          |  |  |  |  |

| R6551C               | Ceramic                                                                                                                                                       | 1 MHz                                              | 0°C to +70°C                                                                          |  |  |  |  |

| R6551AC              | Ceramic                                                                                                                                                       | 2 MHz                                              | 0°C to +70°C                                                                          |  |  |  |  |

|                      | VSS   1<br>CSO   2<br>CST   3<br>RES   4<br>RxC   5<br>XTL1   6<br>XTL0   7<br>RTS   8<br>CTS   9<br>TxD   10<br>DTR   11<br>RxD   12<br>RSO   13<br>RS1   14 | 27 0 26 0 25 0 24 0 23 0 22 0 19 0 18 0 17 16 0 16 | R/W<br>#2<br>IRQ<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0<br>DSR<br>DCD<br>VCC |  |  |  |  |

**R6551 Pin Configuration**

DATA TRANSMIT CTS DO-D7 <8 CONTROL BUFFERS TRANSMIT DATA & TxD INTERRUP SHIFT IRO LOGIC REGISTERS DCD STATUS R/W REGISTER DSA ഭവ 1/0 CS1 BAUD CONTROL RSO XTLI GENERATOR RS1 - XTLO CONTROL REGISTER Ø2 TIMING & CONTROL DTR RES LOGIC COMMAND REGISTER RTS RECEIVE VCC DATA & RxD SHIFT VSS REGISTERS RECEIVE CONTROL

R6551 Interface Diagram

<sup>©</sup> Rockwell International Corporation 1981 All Rights Reserved Printed in U.S.A.

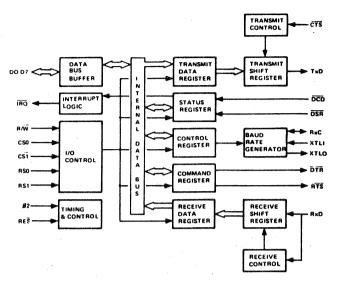

#### INTERNAL ORGANIZATION

R6551 Block Diagram

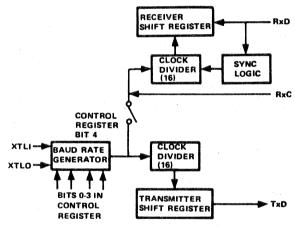

#### Transmitter/Receiver

Bits 0-3 of the Control Register select the divisor used to generate the baud rate for the Transmitter. If the Receiver clock is to use the same baud rate as the Transmitter, then RxC becomes an output pin and can be used to slave other circuits to the R6551.

Transmitter/Receiver Clock Circuits

#### Transmit and Receive Data Registers

These registers are used as temporary data storage for the 6551 Transmit and Receive circuits. The Transmit Data Register is characterized as follows:

- Bit 0 is the leading bit to be transmitted.

- Unused data bits are the high-order bits and are "don't care" for transmission.

The Receive Data Register is characterized in a similar fashion:

- Bit 0 is the leading bit received.

- Unused data bits are the high-order bits and are "0" for the receiver.

- Parity bits are not contained in the Receive Data Register, but are stripped-off after being used for external parity checking.

Parity and all unused high-order bits are "0".

# **Control Register**

The Control Register selects the desired baud rate, frequency source, word length, and the number of stop bits.

**R6551 Control Register**

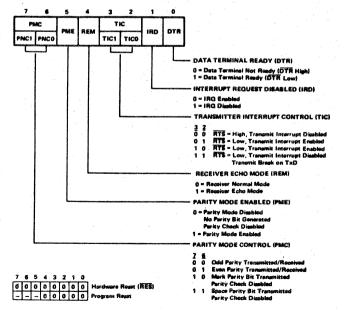

#### **Command Register**

The Command Register controls specific modes and functions.

R6551 Command Register

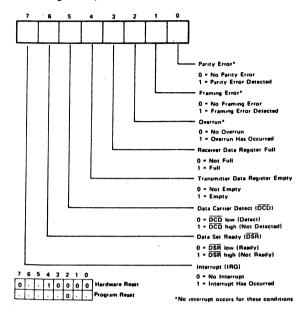

#### Status Register

The Status Register reports the status of various R6551 functions

R6551 Status Register

#### INTERFACE SIGNAL DESCRIPTION

#### RES (Reset)

During system initialization a low on the  $\overline{\text{RES}}$  input will cause internal registers to be cleared.

#### **Ø2** (Input Clock)

The input clock is the system Ø2 clock and is used to synchronize all data transfers between the system microprocessor and the R6551.

# R/W (Read/Write)

The  $R/\overline{W}$  is generated by the microprocessor and is used to control the direction of data transfers. A high on the  $R/\overline{W}$  pin allows the processor to read the data supplied by the R6551. A low on the  $R/\overline{W}$  pin allows a write to the R6551.

# IRQ (Interrupt Request)

The  $\overline{IRQ}$  pin is an interrupt output from the interrupt control logic. It is an open drain output, permitting several devices to be connected to the common  $\overline{IRQ}$  microprocessor input. Normally a high level,  $\overline{IRQ}$  goes low when an interrupt occurs.

### D0-D7 (Data Bus)

The D0-D7 pins are the eight data lines used to transfer data between the processor and the R6551. These lines are bi-directional and are normally high-impedance, except during Read cycles when the R6551 is selected.

#### CS0, CS1 (Chip Selects)

The two chip select inputs are normally connected to the processor address lines either directly or through decoders. The R6551 is selected when CS0 is high and  $\overline{\text{CS1}}$  is low.

#### RS0, RS1 (Register Selects)

The two register select lines are normally connected to the processor address lines to allow the processor to select the various R6551 internal registers. The following table indicates the internal register select coding:

| RS1 | RS0 | Write                                           | Read                      |  |  |

|-----|-----|-------------------------------------------------|---------------------------|--|--|

| 0   | 0   | Transmit Data<br>Register                       | Receiver Data<br>Register |  |  |

| 0   | 1   | Programmed<br>Reset (Data is<br>''Don't Care'') | Status Register           |  |  |

| 1   | 0   | Command Register                                |                           |  |  |

| 1   | 1   | Control Register                                |                           |  |  |

Note that only the Command and Control registers are read/write. The Programmed Reset operation does not cause any data transfer, but is used to clear Bits 0 through 4 in the Command Register and Bit 2 in the Status Register. The Programmed Reset is slightly different from the Hardware Reset (RES); these differences are described in the individual register definitions.

#### ACIA/Modem Interface Signal Description

#### XTLI, XTLO (Crystal Pins)

These pins are normally directly connected to the external crystal (1.8432 MHz) used to derive the various baud rates. Alternatively, an externally generated clock may be used to drive the XTLI pin, in which case the XTLO pin must float. XTLI is the input pin for the transmit clock.

#### TxD (Transmit Data)

The TxD output line is used to transfer serial NRZ (non-return-to-zero) data to the modem. The LSB (least significant bit) of the Transmit Data Register is the first data bit transmitted and the rate of data transmission is determined by the baud rate selected, or under control of an external clock (as selected by the Control Register).

#### RxD (Receive Data)

The RxD input line is used to transfer serial NRZ data into the ACIA from the modem, LSB first. The receiver data rate is either the programmed baud rate or the rate of an externally generated receiver clock (as selected by the Control Register).

#### RxC (Receive Clock)

The RxC is a bi-directional pin which serves as either the receiver 16x clock input or the receiver 16x clock output. The latter mode results if the internal baud rate generator is selected for receiver data clocking.

#### RTS (Request to Send)

The  $\overline{RTS}$  output pin is used to control the modem from the processor. The state of the  $\overline{RTS}$  pin is determined by the contents of the Command Register.

#### CTS (Clear to Send)

The CTS input pin is used to control the transmitter operation. The enable state is with CTS low. The transmitter is automatically disabled if CTS is high.

#### DTR (Data Terminal Ready)

This output pin is used to indicate the status of the R6551 to the modern. A low on DTR indicates the R6551 is enabled and a high indicates it is disabled. The processor controls this pin via bit 0 of the Command Register.

#### DSR (Data Set Ready)

The DSR input pin is used to indicate to the R6551 the status of the modem. A low indicates the "ready" state and a high, "not-ready". DSR is a high-impedance input, and must be connected. If unused, it should be driven high or low, but not switched.

#### DCD (Data Carrier Detect)

The DCD input pin is used to indicate to the R6551 the status of the carrier-detec: output of the modem. A low indicates that the modem carrier signal is present and a high, that it is not. Like DSR, DCD is a high-impedance input, and must be connected.

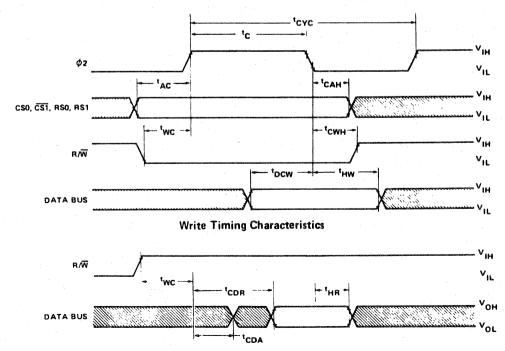

# READ/WRITE CYCLE CHARACTERISTICS

(V<sub>CC</sub> = 5.0V  $\pm$ 5%, T<sub>A</sub> = 0 to 70°C, unless otherwise noted)

|                                | Symbol           | 1 MHz |     | 2 MHz |     |      |

|--------------------------------|------------------|-------|-----|-------|-----|------|

| Characteristic                 |                  | Min   | Max | Min   | Max | Unit |

| Cycle Time                     | †CYC             | 1.0   | 40  | 0.5   | 40  | μs   |

| 02 Pulse Width                 | tC               | 400   |     | 200   | -   | ns   |

| Address Set-Up Time            | †AC              | 120   | -   | 70    | _   | ns   |

| Address Hold Time              | tCAH .           | 0     | _   | 0     | _   | ns   |

| R/W Set-Up Time                | twc              | 120   | -   | 70    | -   | ns   |

| R/W Hold Time                  | tcwH             | 0     |     | 0     | _   | ns   |

| Data Bus Set-Up Time           | tDCW             | 150   | -   | 60    | _   | ns   |

| Data Bus Hold Time             | tHW              | 20    | _   | 20    | _   | ns   |

| Read Access Time (Valid Data)  | tCDR             | _     | 200 | -     | 150 | ns   |

| Read Hold Time                 | -tHR             | 20    |     | 20    | _   | ns   |

| Bus Active Time (Invalid Data) | <sup>t</sup> CDA | 40    |     | 40    | _   | ns   |

$(t_r \text{ and } t_f = 10 \text{ to } 30 \text{ ns})$

**Read Timing Characteristics**

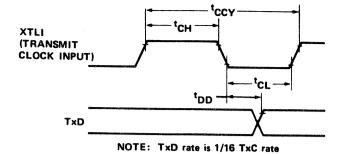

# TRANSMIT/RECEIVE CHARACTERISTICS

|                                     |                  | 1 MHz |     | 2 MHz |     |      |

|-------------------------------------|------------------|-------|-----|-------|-----|------|

| Characteristic                      | Symbol           | Min   | Max | Min   | Max | Unit |

| Transmit/Receive<br>Clock Rate      | tccy             | 400*  | -   | 400*  | -   | nş   |

| Transmit/Receive<br>Clock High Time | <sup>t</sup> CH  | 175   | -   | 175   | _   | ns   |

| Transmit/Receive<br>Clock Low Time  | <sup>t</sup> CL  | 175   | -   | 175   | _   | ns   |

| XTLI to TxD<br>Propagation Delay    | <sup>t</sup> DD  | -     | 500 | -     | 500 | ns   |

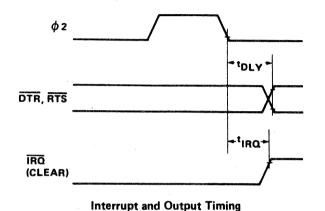

| RTS Propagation<br>Delay            | <sup>t</sup> DLY | _     | 500 | _     | 500 | ns   |

| IRQ Propagation<br>Delay (Clear)    | <sup>t</sup> IRQ | _     | 500 | _     | 500 | ns   |

The baud rate with external clocking is: Baud Rate =  $\frac{1}{16 \times T_{CCY}}$

Transmit Timing with External Clock

t<sub>CH</sub> (INPUT)

NOTE: RxD rate is 1/16 RxC rate

**Receive External Clock Timing**

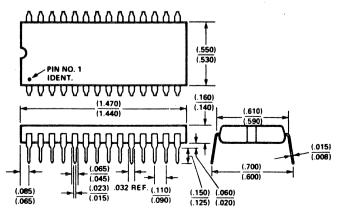

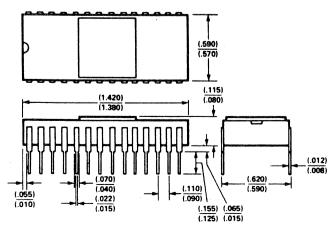

# **PACKAGE OUTLINES**

# 28 LEAD CERAMIC

# 28 LEAD PLASTIC

RxC