Streams Processor Unified Memory S

Processor UMA Unified Notreams Processor UMA Unified Notreams Processor UMA Unified Memory S

Processor UMA Unified Notreams Processor UMA Unified Note Note 1980 No

Trio64UV+

MultiMeDia Acceleration Cooperative Accelerator Architecture

March 1996

S3 Incorporated 2770 San Tomas Expressway P.O. Box 58058 Santa Clara, CA 95052-8058

### NOTATIONAL CONVENTIONS

The following notational conventions are used in this data book:

Signal names are shown in all uppercase letters. For example, XD.

A bar over a signal name indicates an active low signal. For example,  $\overline{\text{OE}}$ .

n-m indicates a bit field from bit n to bit m. For example, 7-0 specifies bits 7 through 0, inclusive.

n:m indicates a signal (pin) range from n to m. For example D[7:0] specifies data lines 7 through 0, inclusive

Use of a trailing letter H indicates a hexadecimal number. For example, 7AH is a hexadecimal number.

Use of a trailing letter b indicates a binary number. For example, 010b is a binary number.

When numerical modifiers such as K or M are used, they refer to binary rather than decimal form. Thus, for example, 1 KByte would be equivalent to 1024, not 1,000 bytes.

#### **NOTICES**

© Copyright 1996 S3 Incorporated. All rights reserved. If you have received this document from S3 Incorporated in electric form, you are permitted to make the following copies for business use related to products of S3 Incorporated: one copy onto your computer for the purpose of on-line viewing, and one printed copy. With respect to all documents, whether received in hard copy or electronic form, other use, copying or storage, in whole or in part, by any means electronic, mechanical, photocopying or otherwise, is permitted without the prior written consent of S3 Incorporated, P.O. Box 58058., Santa Clara CA 95052-8058. S3 and True Acceleration are registered trademarks of S3 Incorporated. The S3 Corporate Logo, S3 on Board, S3 on Board design, S3d design, Vision968, Trio, Trio64, Trio64V+, Trio64UV+, ViRGE, ViRGE/VX, S3d, Scenic, Scenic/MX1, Scenic/MX2, Scenic Highway, Sonic, Sonic/AD, Aurora64V+, DuoView, Cooperative Accelerator Architecture, Streams Processor, MIC, Galileo, Native-MPEG, No Compromise Integration, No Compromise Acceleration and Innovations in Acceleration are trademarks of S3 Incorporated. Other trademarks referenced in this document are owned by their respective companies. The material in this document is for information only and is subject to change without notice. S3 Incorporated reserves the right to make changes in the product design without reservation and without notice to its users.

Additional information may be obtained from:

S3 Incorporated, Literature Department P.O. Box 58058, Santa Clara, CA 95052-8058.

Telephone: 408-980-5400, Fax: 408-980-5444

### **Table of Contents**

| List o                   | of Figures iv                                                                                                      | Section 4: Register Changes from Trio64V+                                                                         |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| List o                   | f Tables v                                                                                                         | 4.1 REGISTERS CHANGED 4-7 4.2 NEW REGISTERS 4-4-4                                                                 |

| Secti                    | on 1: Introduction 1-1                                                                                             | 0 ti 5 . B                                                                                                        |

| 1.1<br>1.2<br>1.3        | OVERVIEW 1-2 ADVANCED ARCHITECTURE/ FEATURE SET 1-2 UNIFIED MEMORY ARCHITECTURE (UMA) 1-2                          | Section 5: Programming Considerations                                                                             |

| 1.4<br>1.5<br>1.6<br>1.7 | STREAMS PROCESSOR SUPPORT 1-2 MULTIMEDIA SUPPORT FEATURES 1-3 FEATURES ADDED TO Trio64V+ 1-3 FEATURES REMOVED FROM | Section 6: Electrical Data 6-1 6.1 MAXIMUM RATINGS 6-6 6.2 DC SPECIFICATIONS 6-7                                  |

| 1.8                      | Trio64V+                                                                                                           | 6.3 AC SPECIFICATIONS 6-6 6.3.1 RAMDAC AC Specifications 6-6 6.3.2 Clock Timing 6-6 6.3.3 Input/Output Timing 6-9 |

| Secti                    | on 2: Pins 2-1                                                                                                     | ololo impayoutput immig i i i i i i o i                                                                           |

| 2.1<br>2.2<br>2.3        | PIN DESCRIPTIONS 2-3                                                                                               | Section 7: Mechanical Data 7-1 7.1 THERMAL SPECIFICATIONS 7-7 7.2 MECHANICAL DIMENSIONS 7-7                       |

| Secti                    | on 3: Functional Changes                                                                                           |                                                                                                                   |

|                          | Trio64V+                                                                                                           |                                                                                                                   |

## **List of Figures**

| #   | Title P                           | age |

|-----|-----------------------------------|-----|

| 2-1 | Pinout                            | 2-2 |

| 3-1 | System and Memory Interface       |     |

|     | Block Diagram                     | 3-1 |

| 3-2 | Memory Map                        | 3-2 |

| 3-3 | Address Translation               | 3-3 |

| 3-4 | VUMA-Style Low Priority           |     |

|     | Arbitration                       | 3-4 |

| 3-5 | S3 3-Pin Arbitration              | 3-5 |

| 3-6 | 2-Pin Arbitration                 | 3-5 |

| 3-7 | Early Withdrawal of the Bus Grant | 3-6 |

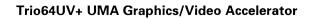

| 5-1 | BIOS Initialization Process       | 5-1 |

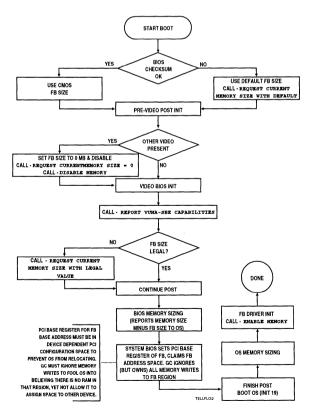

| 5-2 | Mode Setting                      | 5-2 |

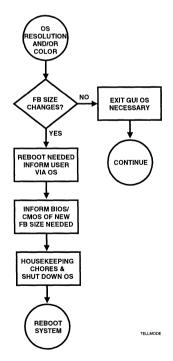

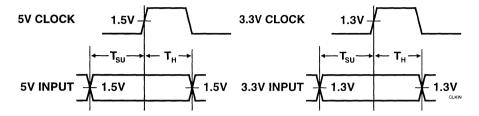

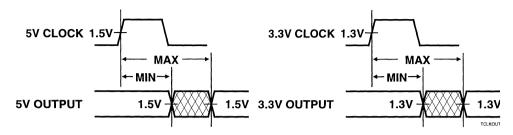

| 6-1 | Clock Waveform Timing             | 6-4 |

| 6-2 | Input Timing                      | 6-5 |

| 6-3 | Output Timing                     | 6-7 |

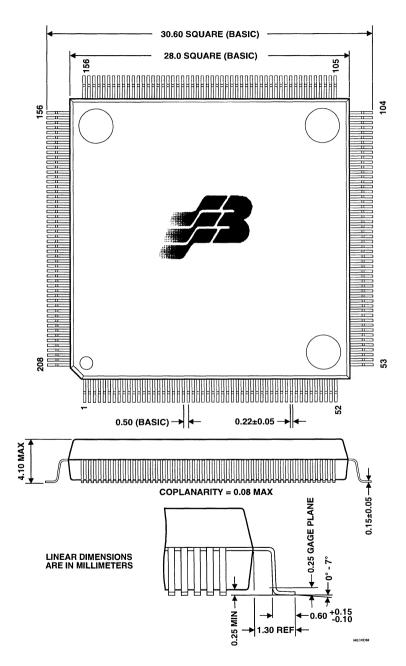

| 7-1 | 208-pin PQFP Mechanical           |     |

|     | Dimensions                        | 7-2 |

### **List of Tables**

| #    | Title                             | Page |

|------|-----------------------------------|------|

| 2-1  | Pin Descriptions                  | 2-3  |

| 2-2  | Alphabetical Pin Listing          | 2-8  |

|      | Numerical Pin Listing             | 2-10 |

| 3-1  | Operating Modes                   | 3-7  |

| 6-1  | Absolute Maximum Ratings          | 6-1  |

| 6-2  | RAMDAC/Clock Synthesizer DC       |      |

|      | Specifications                    | 6-1  |

| 6-3  | RAMDAC Characteristics            | 6-1  |

| 6-4  | Digital DC Specifications         | 6-2  |

| 6-5  | RAMDAC AC Specifications          | 6-3  |

| 6-6  | RAMDAC Output Specifications .    | 6-3  |

| 6-7  | Clock Waveform Timing             | 6-4  |

| 6-8  | SCLK-Referenced Input Timing .    | 6-5  |

| 6-9  | LCLK-Referenced Input Timing .    | 6-5  |

| 6-10 | MCLK-Referenced Input Timing .    | 6-6  |

| 6-11 | ACLK-Referenced Input Timing .    | 6-6  |

| 6-12 | SCLK-Referenced Output Timing     | 6-7  |

| 6-13 | LCLK-Referenced Output Timing     | 6-7  |

| 6-14 | MCLK-Referenced Output Timing     | 6-8  |

| 6-15 | ACLK-Referenced Output Timing     | 6-8  |

| 6-16 | Feature Connector Timing - Output | ıt   |

|      | from Trio64UV+ to Feature         |      |

|      | Connector                         | 6-8  |

| 6-17 | Feature Connector Timing - Outpu  | ıt   |

|      | from Feature Connector to         |      |

|      | Trio64UV+                         | 6-9  |

### **Section 1: Introduction**

## High-Performance Integrated Graphics/Video Accelerator

- High-performance 64-bit graphics engine

- Integrated 24-bit RAMDAC with 135 MHz output pixel rate and programmable dual-clock synthesizer

- Unique S3 Streams Processor for hardware-assisted video playback

- S3 Scenic Highway for direct interface to live video and MPEG-1 peripherals

#### S3 Streams Processor Features

- Supports on-the-fly stretching and blending of primary RGB stream and RGB or YUV/YCbCr (video) secondary stream

- Each stream can have different color depths

- YUV data is color space converted on the fly

#### **Advanced Playback Capabilities**

- High-quality hardware-assisted video playback (up to 1024x768x8 bits/pixel)

- Support for Indeo, Cinepak, and software-accelerated MPEG-1 video playback

### **Game and Presentation Effects**

- Hardware double-buffering support for high-quality tear-free playback

- 2-D scrolling and sprite plane support

- Color and chroma keying for overlaying of graphics onto video and video onto graphics

Arithmetic blending of two pixel streams for fade-in/fade-out transition effects

### **Unified Memory Architecture (UMA)**

- UMA shares system memory between the host CPU and the graphics/video subsystem

- System memory arbitration compatible with all major core logic vendors

- 64-bit DRAM memory interface

- 0.5-, 1-, 1.5 or 2-MByte configurable frame buffer

- Fast page and EDO mode memory support

#### Mixed Voltage Support

- 5V core, 5V or 3.3V memory bus operation

- Compatible with 5V or 3.3V memories

- Compatible with 5V or 3.3V UMA core logic

### S3 Scenic Highway Interface

- Philips SAA7110/SAA7111 video digitizers

- S3 Scenic/MX2 MPEG-1 audio/video decoder

### **High Resolution Non-Interlaced Screen Support**

- 1280x1024x256 colors

- 1024x768x256 colors

- 800x600x64K colors

- 640x480x16.7M colors

#### Glueless PCI 2.1 Bus Support

### Multimedia Support Hooks

- 8-bit bidirectional feature connector

- S3 Scenic Highway

- I<sup>2</sup>C bus

### **Full Software Support**

Drivers for Windows 3.11, Windows NT, Windows 95, OS/2 2.1 and 3.0 (Warp), SCO UNIX

### Green PC/Monitor Plug and Play Support

- Full hardware and BIOS support for VESA Display Power Management Signaling (DPMS) monitor power savings modes

- Extensive static/dynamic power management

- DDC monitor communications support

### Industry-Standard 208-pin PQFP package

### 1.1 OVERVIEW

The S3® Trio64UV+™ UMA graphics/video accelerator (hereinafter referred to as the Trio64UV+) is the newest member of the extremely successful Trio™ family of products. Based on the Trio64V+™ integrated graphics/video accelerator, Trio64UV+ adds Unified Memory Architecture (UMA) support allowing system memory to be shared between the host CPU and the graphics/video subsystem. UMA support provides a full-featured solution for motherboard designs that dramatically reduces the graphics subsystem cost and footprint. Trio64UV+ is targeted at entry-level Intel® Pentium™ systems and equivalents. It has been developed in conjunction with all major PC system core logic vendors

and will be supported in many next generation Pentium/PCI core logic designs.

## 1.2 ADVANCED ARCHITECTURE/FEATURE SET

Trio64UV+ provides a 64-bit high performance graphics engine and a 64-bit DRAM interface. The full 64-bit memory data path is used in all frame buffer configurations, which range in size from 0.5 to 2 MBytes. Fast-page and EDO mode DRAMs are supported.

# 1.3 UNIFIED MEMORY ARCHITECTURE (UMA)

Trio64UV+ is the first product offered by S3 to support UMA operation. This architecture reserves a portion of main system memory as graphics memory, thus eliminating the need for a separate graphics frame buffer. This allows system manufacturers to dramatically reduce the graphics subsystem cost. Since the graphics memory is now an integral part of the host memory bus, CPU accesses to graphics memory are no longer constrained by PCI bandwidth limitations. This drastically reduces the software overhead of many common graphics operations.

## 1.4 STREAMS PROCESSOR SUPPORT

The S3 Streams Processor™ technology processes data from the graphics frame buffer, composes it and outputs the result to the internal DACs for generation of the analog RGB outputs to the monitor. Data is composed from up to 3 independent streams: (1) Primary Stream—RGB graphics data; (2) Secondary Stream—RGB or YUV/YCbCr (video) data from another region within the frame buffer; and (3) a 64x64x2 hardware cursor.

Arithmetic blending of a primary graphics stream and secondary graphics/video enables dramatic transition effects for game and multimedia applications. Color and chroma keying allow opaque or transparent overlays of one stream on the other.

Simultaneous display of graphics and video of different color depths is provided. For example, it is possible to display true color (24-bit) video data on top of an 8-bit graphics background. This can improve video quality and frame rates while reducing memory bandwidth and storage requirements.

## 1.5 MULTIMEDIA SUPPORT FEATURES

Trio64UV+ supports the S3 Scenic Highway™ local peripheral bus for direct connection to video input devices like the S3 Scenic/MX2™ Audio/Video MPEG decoder and the Philips® video digitizers. The Streams Processor and Scenic Highway are tightly coupled to provide optimal live video playback. The hardware automatically switches capture and display buffers without software intervention.

### 1.6 FEATURES ADDED TO Trio64V+

- Arbitration logic for UMA memory

- Support for system memory DRAMs [FP and EDO SIMMs]

- Support for 0.5- and 1.5-MByte frame buffers

- Optional disabling of DRAM refresh (core logic refreshes DRAM instead)

- Mixed voltage operation

## 1.7 FEATURES REMOVED FROM Trio64V+

- VL-Bus<sup>TM</sup> support

- Trio64™ -compatible mode

- Trio64-type VAFC feature connector support (multiplexed on PD lines)

- 16-bit VAFC feature connector on the LPB

- Video 8 In/Out LPB mode

- Video 16 LPB mode

- CL-480 support

- 4-MByte memory support

- 1-cycle EDO operation

Relocation of Serial Port register to I/O port via power-on strapping

### 1.8 INTRODUCTION TO THIS DATA BOOKLET

This data booklet largely describes the areas in which Trio64UV+ differs from Trio64V+. It does contain complete pin descriptions and electrical and mechanical specification sections. Otherwise, the Trio64V+ data book must be used in conjunction with this data booklet.

### **Section 2: Pins**

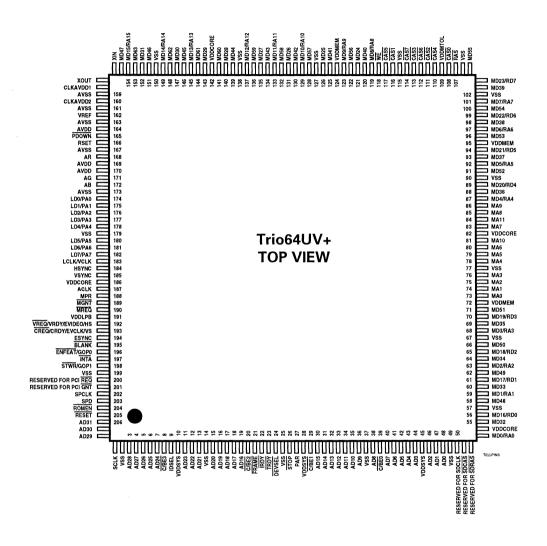

### 2.1 PINOUT DIAGRAMS

Trio64UV+ comes in a 208-pin PQFP package. The pinout is shown in Figure 2-1.

Figure 2-1. Pinout

### 2.2 PIN DESCRIPTIONS

The following table provides a brief description of each pin on Trio64UV+. The following abbreviations are used for pin types.

- I Input signal

- O Output signal

- B Bidirectional signal

Table 2-1. Pin Descriptions

| Symbol         | Туре              | Description                                                                                                                                                               |  |  |

|----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCI BUS INTERI | PCI BUS INTERFACE |                                                                                                                                                                           |  |  |

| Address        | and Data          |                                                                                                                                                                           |  |  |

| AD[31:0]       | В                 | Multiplexed Address/Data Bus. A bus transaction (cycle) consists of an address phase followed by one or more data phases.                                                 |  |  |

| C/BE[3:0]      | 1                 | Bus Command/Data Byte Enables. These signals carry the bus command during the address phase and the byte enables during the data phase.                                   |  |  |

| Bus Con        | trol              |                                                                                                                                                                           |  |  |

| SCLK           | 1                 | PCI System Clock.                                                                                                                                                         |  |  |

| ĪNTĀ           | 0                 | Interrupt Request.                                                                                                                                                        |  |  |

| ĪRDY           | l                 | Initiator Ready. A bus data phase is completed when both IRDY and TRDY are asserted on the same cycle.                                                                    |  |  |

| TRDY           | 0                 | Target Ready. A bus data phase is completed when both $\overline{\text{IRDY}}$ and $\overline{\text{TRDY}}$ are asserted on the same cycle.                               |  |  |

| DEVSEL         | 0                 | Device Select. Trio64UV+ drives this signal active when it decodes its address as the target of the current access.                                                       |  |  |

| IDSEL          | 1                 | Initialization Device Select. This input is the chip select for PCI configuration register reads/writes.                                                                  |  |  |

| RESET          | I                 | System Reset. Asserting this signal forces the registers and state machines to a known state.                                                                             |  |  |

| FRAME          | I                 | Cycle Frame. This signal is asserted by the bus master to indicate the beginning of a bus transaction. It is deasserted during the final data phase of a bus transaction. |  |  |

| PAR            | 0                 | Parity. Trio64UV+ asserts this signal to verify even parity during reads.                                                                                                 |  |  |

| STOP           | 0                 | Stop. Trio64UV+ asserts this signal to indicate a target disconnect.                                                                                                      |  |  |

Table 2-1. Pin Descriptions (continued)

| Symbol                                     | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLOCK CONTI                                |             |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| between be input very as AVDD. (dot clock) |             | Reference Frequency Input. If an external crystal is used, it is connected between XOUT and this pin. A stable external frequency source can also be input via this pin. If this is done, the input voltage must be the same as AVDD. If MD11 is strapped high at power-on, this becomes the DCLK (dot clock) input, bypassing the internal oscillator. This is normally only used for test purposes. |  |  |

| XOUT                                       | 0           | Crystal Output. If an external 14.318 MHz crystal is used, it is connected between XIN and this pin. This pin drives the crystal via an internal oscillator.                                                                                                                                                                                                                                          |  |  |

| DISPLAY MEM                                | ORY INTER   | RFACE                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Addre                                      | ss and Data |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| MA[11:0]                                   | 0           | Memory Address Bus. The memory row and column addresses are multiplexed on these lines.                                                                                                                                                                                                                                                                                                               |  |  |

| MD[63:0]                                   | В           | Memory Data Bus Lines.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Memo                                       | ry Control  |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| RAS                                        | 0           | Row Address Strobe                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| CAS[7:0]                                   | 0           | Column Address Strobes.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| WE                                         | 0           | Write Enable                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Arbitra                                    | ation       |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| MREQ                                       | 0           | Memory Bus Request.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| MGNT                                       |             | Memory Bus Grant.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| MPR                                        | 0           | Priority. Trio64UV+ asserts this signal to indicate a high priority bus request. This is not used with 2-pin arbitration schemes.                                                                                                                                                                                                                                                                     |  |  |

| ACLK                                       | 1           | Clock. This input is normally connected to the host CPU clock. It is used by Trio64UV+ to synchronize the memory bus arbitration with the host system. It may also be used as the system MCLK.                                                                                                                                                                                                        |  |  |

| VIDEO INTERI                               | FACE        |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PDOWN                                      |             | Power Down. Asserting this signal turns off the RGB analog output from the DACs.                                                                                                                                                                                                                                                                                                                      |  |  |

| VREF                                       |             | Voltage Reference. This pin is tied to $V_{SS}$ through a 0.1 $\mu F$ capacitor.                                                                                                                                                                                                                                                                                                                      |  |  |

| RSET                                       |             | Reference Resistor. This pin is tied to V <sub>SS</sub> through an external resistor to control the full-scale current value.                                                                                                                                                                                                                                                                         |  |  |

| AR                                         | 0           | Analog Red. Analog red output to the monitor.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| AG                                         | 0           | Analog Green. Analog green output to the monitor.                                                                                                                                                                                                                                                                                                                                                     |  |  |

| AB                                         | 0           | Analog Blue. Analog blue signal to the monitor.                                                                                                                                                                                                                                                                                                                                                       |  |  |

### Table 2-1. Pin Descriptions (continued)

| Symbol  | Туре | Description                                                                                                                                                                                                                    |  |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ENFEAT  | 0    | Enable Feature Connector. Setting SRD_0 to 1 drives this signal low when SR1C_1-0 are 00b. This also enables all feature connector operations.                                                                                 |  |

| BLANK   | В    | Video Blank.                                                                                                                                                                                                                   |  |

| ESYNC   | 1    | External SYNC. When ESYNC is driven low, HSYNC, VSYNC and BLANK become inputs. When ESYNC is high, HSYNC, VSYNC and BLANK become outputs.                                                                                      |  |

| EVIDEO  | 1    | External Video. When this input is high, PA[7:0] are outputs to the feature connector.                                                                                                                                         |  |

| EVCLK   | 1    | External VCLK. When this input is asserted low, VCLK is an input to the internal RAMDAC. When this input is high, VCLK is output to the feature connector.                                                                     |  |

| VCLK    | В    | Video/Pixel Clock. When EVCLK is high, this signal is an output to the feature connector. When EVCLK is low, this becomes an input used only for test purposes.                                                                |  |

| HSYNC   | В    | Horizontal Sync. When ESYNC is high, this is the horizontal sync output.<br>When ESYNC is low, this is an input from the feature connector.                                                                                    |  |

| VSYNC   | В    | Vertical Sync. When ESYNC is high, this is the vertical sync output. When ESYNC is low, this is an input from the feature connector.                                                                                           |  |

| PA[7:0] | В    | Pixel Address Lines [7:0]. The PA[7:0] function is enabled on the pins indicated for PCI configurations when LPB feature connector operation is enabled. When EVIDEO is high, PA signals are outputs to the feature connector. |  |

Table 2-1. Pin Descriptions (Continued)

| Symbol        | Type   | Description                                                                                                                                                                                                                                                                                              |  |

|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MISCELLANEO   |        |                                                                                                                                                                                                                                                                                                          |  |

|               |        | and Serial Ports                                                                                                                                                                                                                                                                                         |  |

| RA[15:0]      | 0      | ROM Address Bus. These signals provide the address for BIOS ROM reads. They are multiplexed with MD signals. Programmers must ensure that the memory bus is inactive when reading the ROM. This function is only used in test mode.                                                                      |  |

| RD[7:0]       | 1      | ROM Data Bus. These signals carry data for BIOS ROM reads. They are multiplexed with MD signals. Programmers must ensure that the memory bus is inactive when reading the ROM. This function is only used in test mode.                                                                                  |  |

| ROMEN         | 0      | ROM Enable. This signal provides the chip output enable input for BIOS ROM reads. This function is only used in test mode.                                                                                                                                                                               |  |

| GOP[1:0]      | 0      | General Output Port Bits 1-0. If SR1C_1 is set to 1, the value of CR5C_0 is output on pin 196 (GOP0) and the value of CR5C_1 is output on pin 198 (GOP1).                                                                                                                                                |  |

| STWR          | 0      | Strobe Write. If SR1C_1 is cleared to 0, this signal is asserted whenever a write is made to CR5C. It is used to enable a General Output Port latch.                                                                                                                                                     |  |

| SPCLK         | I/O    | Serial Port Clock. This is the clock for serial data transfer, either for I <sup>2</sup> C on DDC2 monitor data communications. As an output, it is programmed via MMFF20_0. As an input, its status is read via MMFF20_2. In either case the serial port must be enabled by setting MMFF20_4 to 1.      |  |

| SPD           | I/O    | Serial Port Data. This is the data signal for serial data transfer, either for I <sup>2</sup> C or DDC2 monitor data communications. As an output, it is programmed via MMFF20_1. As an input, its status is read via MMFF20_3. In either case the serial port must be enabled by setting MMFF20_4 to 1. |  |

| SCENIC        | HIGHWA | Υ                                                                                                                                                                                                                                                                                                        |  |

| Scenic/MX2 Mo | ode    |                                                                                                                                                                                                                                                                                                          |  |

| LD[7:0]       | I/O    | LPB Data. This is the Scenic Highway data bus and carries compressed data to Scenic/MX2 and video data from Scenic/MX2.                                                                                                                                                                                  |  |

| LCLK          | ı      | LPB Clock. This clock controls transactions between Trio64UV+ and Scenic Highway peripherals                                                                                                                                                                                                             |  |

| VREQ/VRDY     | 0      | Video Request/Ready. This signal is part of the the Scenic Highway data transfer protocol between Trio64UV+ and Scenic/MX2.                                                                                                                                                                              |  |

| CREQ/CRDY     |        | Scenic/MX2 Request/Ready. This signal is part of the the Scenic Highway data transfer protocol between Trio64UV+ and Scenic/MX2.                                                                                                                                                                         |  |

| ENFEAT        | 0      | Enable Feature Connector. This signal is connected to Scenic/MX2 chip enable input such that Scenic/MX2 is disabled when feature connector operation is enabled.                                                                                                                                         |  |

| Video 8 Mode  |        |                                                                                                                                                                                                                                                                                                          |  |

| LD[7:0]       | I      | LPB Data Bus [7:0]. This is the Scenic Highway data bus and carries video data input.                                                                                                                                                                                                                    |  |

| HS            | ı      | HSYNC. HSYNC input signaling the transition from one line to the next.                                                                                                                                                                                                                                   |  |

| VS            |        | VSYNC. VSYNC input signaling the transition from one frame to the next                                                                                                                                                                                                                                   |  |

### Table 2-1. Pin Descriptions (Continued)

| Symbol       | Туре             | Description                                                                                                          |  |  |

|--------------|------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| POWER        | POWER AND GROUND |                                                                                                                      |  |  |

| VDDCORE      |                  | Core digital power supply                                                                                            |  |  |

| VDDLPB       | 11               | LPB power supply                                                                                                     |  |  |

| VDDMEM       | 1                | Memory subsystem digital power supply (3.3V or 5V - see Section 3.4 for more information on mixed voltage operation) |  |  |

| VDDMTOL      | 1                | 3.3V or 5V tolerance for memory subsystem (see Section 3.4 for more information on mixed voltage operation)          |  |  |

| VDDSYS       |                  | PCI Bus subsystem digital power supply                                                                               |  |  |

| AVDD         | 1                | Analog power supply (RAMDAC). This must be the same voltage as VDDCORE.                                              |  |  |

| CLKAVDD[1:2] | I                | Analog power supply (clock synthesizer, 1 = MCLK, 2 = DCLK). This must be the same voltage as VDDCORE.               |  |  |

| VSS          | I                | Digital ground                                                                                                       |  |  |

| AVSS         | 1                | Analog ground                                                                                                        |  |  |

### 2.3 PIN LISTS

Table 2-2 lists all pins alphabetically. Table 2-3 lists all pins in numerical order.

Table 2-2. Alphabetical Pin Listing

|              | PIN(S)                                                                  |

|--------------|-------------------------------------------------------------------------|

| Name         |                                                                         |

| AB           | 172                                                                     |

| ACLK         | 187                                                                     |

| AD[31:16]    | 206, 207, 208, 3, 4, 5, 6, 7, 11, 12, 13, 15,16, 17, 18, 19             |

| AD[15:0]     | 30, 31, 32, 33, 34, 35, 36, 38, 40, 41, 42, 43, 44, 46, 47, 48          |

| AG           | 171                                                                     |

| AR           | 168                                                                     |

| AVDD         | 164, 169, 170                                                           |

| AVSS         | 159, 161, 163, 167, 173                                                 |

| BLANK        | 195                                                                     |

| CAS[7:0]     | 114, 112, 117, 110, 113, 111, 116, 108                                  |

| C/BE[3:0]    | 8, 20, 29, 39                                                           |

| CLKAVDD[1:2] | 158, 160                                                                |

| CREQ/CRDY    | 193                                                                     |

| DEVSEL       | 24                                                                      |

| ENFEAT       | 196                                                                     |

| ESYNC        | 194                                                                     |

| EVCLK        | 194                                                                     |

| EVIDEO       | 192                                                                     |

| FRAME .      | 21                                                                      |

| RA[15:0]     | 154, 149, 145, 137, 133, 129, 123, 119, 101, 97, 92, 87, 68, 63, 59, 53 |

| RD[7:0]      | 104, 99, 94, 89, 70, 65, 61, 56                                         |

| GOP[1:0]     | 198, 196                                                                |

| HS           | 192                                                                     |

| HSYNC        | 184                                                                     |

| IDSEL        | 9                                                                       |

| ĪNTĀ         | 197                                                                     |

| ĪRDY         | 22                                                                      |

| LCLK         | 183                                                                     |

| LD[7:0]      | 182, 181, 180, 178, 177, 176, 175, 174                                  |

| MA[11:0]     | 84, 81, 86, 85, 83, 80, 79, 78, 76, 75, 74, 73                          |

| MD[63:48]    | 153, 148, 144, 141, 136, 132, 128, 122, 5, 100, 96, 91, 71, 66, 62, 58  |

| MD[47:32]    | 155, 151, 146, 139, 134, 130, 125, 120, 103, 98, 93, 88, 69, 64, 60, 55 |

| MD[31:16]    | 152, 147, 143, 140, 135, 131, 126, 121, 104, 99, 94, 89, 70, 65, 61, 56 |

| MD[15:0]     | 154, 149, 145, 137, 133, 129, 123, 119, 101, 97, 92, 87, 68, 63, 59, 53 |

Table 2-2. Alphabetical Pin Listing (Continued)

|                  | PIN(S)                                                                    |

|------------------|---------------------------------------------------------------------------|

| Name             |                                                                           |

| MGNT             | 189                                                                       |

| MPR              | 188                                                                       |

| MREQ             | 190                                                                       |

| PA[7:0]          | 182, 181, 180, 178, 177, 176, 175, 174                                    |

| PAR              | 27                                                                        |

| PDOWN            | 165                                                                       |

| RAS              | 107                                                                       |

| RESERVED         | 50, 51, 52, 200, 201                                                      |

| RESET            | 205                                                                       |

| ROMEN            | 204                                                                       |

| RSET             | 166                                                                       |

| SCLK             | 1                                                                         |

| SPCLK            | 202                                                                       |

| SPD              | 203                                                                       |

| STOP             | 26                                                                        |

| STWR             | 198                                                                       |

| TRDY             | 23                                                                        |

| VCLK             | 183                                                                       |

| VDDCORE          | 54, 82, 142, 186                                                          |

| VDDLPB           | 191                                                                       |

| VDDMEM           | 72, 95, 124                                                               |

| VDDMTOL          | 109                                                                       |

| VDDSYS           | 10, 28, 45                                                                |

| <b>VREQ/VRDY</b> | 192                                                                       |

| VREF             | 162                                                                       |

| VS               | 193                                                                       |

| VSS              | 2, 14, 25, 37, 49, 57, 67, 77, 90, 102, 106, 115, 127, 138, 150, 179, 199 |

| VSYNC            | 185                                                                       |

| WE               | 118                                                                       |

| XIN              | 156                                                                       |

| XOUT             | 157                                                                       |

Table 2-3. Numerical Pin Listing

| Number | Pin    | Number | Pin      |

|--------|--------|--------|----------|

| 1      | SCLK   | 43     | AD4      |

| 2      | VSS    | 44     | AD3      |

| 3      | AD28   | 45     | VDDSYS   |

| 4      | AD27   | 46     | AD2      |

| 5      | AD26   | 47     | AD1      |

| 6      | AD25   | 48     | AD0      |

| 7 .    | AD24   | 49     | VSS      |

| 8      | C/BE3  | 50     | RESERVED |

| 9      | IDSEL  | 51     | RESERVED |

| 10     | VDDSYS | 52     | RESERVED |

| 11     | AD23   | 53     | MD0      |

| 12     | AD22   | 54     | VDDCORE  |

| 13     | AD21   | 55     | MD32     |

| 14     | VSS    | 56     | MD16     |

| 15     | AD20   | 57     | VSS      |

| 16     | AD19   | 58     | MD48     |

| 17     | AD18   | 59     | MD1      |

| 18     | AD17   | 60     | MD33     |

| 19     | AD16   | 61     | MD17     |

| 20     | C/BE2  | 62     | MD49     |

| 21     | FRAME  | 63     | MD2      |

| 22     | ĪRDY   | 64     | MD34     |

| 23     | TRDY   | 65     | MD18     |

| 24     | DEVSEL | 66     | MD50     |

| 25     | VSS    | 67     | VSS      |

| 26     | STOP   | 68     | MD3      |

| 27     | PAR    | 69     | MD35     |

| 28     | VDDSYS | 70     | MD19     |

| 29     | C/BE1  | 71     | MD51     |

| 30     | AD15   | 72     | VDDMEM   |

| 31     | AD14   | 73     | MA0      |

| 32     | AD13   | 74     | MA1      |

| 33     | AD12   | 75     | MA2      |

| 34     | AD11   | 76     | MA3      |

| 35     | AD10   | 77     | VSS      |

| 36     | AD9    | 78     | MA4      |

| 37     | VSS    | 79     | MA5      |

| 38     | AD8    | 80     | MA6      |

| 39     | C/BE0  | 81     | MA10     |

| 40     | AD7    | 82     | VDDCORE  |

| 41     | AD6    | 83     | MA7      |

| 42     | AD5    | 84     | MA11     |

Table 2-3. Numerical Pin Listing (Continued)

| Number | Pin     | Number | Pin      |

|--------|---------|--------|----------|

| 85     | MA8     | 127    | VSS      |

| 86     | MA9     | 128    | MD57     |

| 87     | MD4     | 129    | MD10     |

| 88     | MD36    | 130    | MD42     |

| 89     | MD20    | 131    | MD26     |

| 90     | VSS     | 132    | MD58     |

| 91     | MD52    | 133    | MD11     |

| 92     | MD5     | 134    | MD43     |

| 93     | MD37    | 135    | MD27     |

| 94     | · MD21  | 136    | MD59     |

| 95     | VDDMEM  | 137    | MD27     |

| 96     | MD53    | 138    | VSS      |

| 97     | MD6     | 139    | MD44     |

| 98     | MD38    | 140    | MD28     |

| 99     | MD22    | 141    | MD60     |

| 100    | MD54    | 142    | VDDCORE  |

| 101    | MD7     | 143    | MD29     |

| 102    | VSS     | 144    | MD61     |

| 103    | MD39    | 145    | MD13     |

| 104    | MD23    | 146    | MD45     |

| 105    | MD55    | 147    | MD30     |

| 106    | VSS     | 148    | MD62     |

| 107    | RAS     | 149    | MD14     |

| 108    | CAS0    | 150    | VSS      |

| 109    | VDDMTOL | 151    | MD46     |

| 110    | CAS4    | 152    | MD31     |

| 111    | CAS2    | 153    | MD63     |

| 112    | CAS6    | 154    | MD15     |

| 113    | CAS3    | 155    | MD47     |

| 114    | CAS7    | 156    | XIN      |

| 115    | VSS     | 157    | XOUT     |

| 116    | CAS1    | 158    | CLKAVDD1 |

| 117    | CAS5    | 159    | AVSS     |

| 118    | WE      | 160    | CLKAVDD2 |

| 119    | MD8     | 161    | AVSS     |

| 120    | MD40    | 162    | VREF     |

| 121    | MD24    | 163    | AVSS     |

| 122    | MD56    | 164    | AVDD     |

| 123    | MD9     | 165    | PDOWN    |

| 124    | VDDMEM  | 166    | RSET     |

| 125    | MD41    | 167    | AVSS     |

| 126    | MD25    | 168    | AR       |

Table 2-3. Numerical Pin Listing (Continued)

| Number | Pin                 |

|--------|---------------------|

| 169    | AVDD                |

| 170    | AVDD                |

| 171    | AG                  |

| 172    | AB                  |

| 173    | AVSS                |

| 174    | LD0/PA0             |

| 175    | LD1/PA1             |

| 176    | LD2/PA2             |

| 177    | LD3/PA3             |

| 178    | LD4/PA4             |

| 179    | VSS                 |

| 180    | LD5/PA5             |

| 181    | LD6/PA6             |

| 182    | LD7/PA7             |

| 183    | LCLK/VCLK           |

| 184    | HSYNC               |

| 185    | VSYNC               |

| 186    | VDDCORE             |

| 187    | ACLK                |

| 188    | MPR                 |

| 189    | MGNT                |

| 190    | MREQ                |

| 191    | VDDLPB              |

| 192    | VREQ/VRDY/HS/EVIDEO |

| 193    | CREQ/CRDY/VS/EVCLK  |

| 194    | ESYNC               |

| 195    | BLANK               |

| 196    | ENFEAT/GOP0         |

| 197    | ĪNTĀ                |

| 198    | STWR/GOP1           |

| 199    | VSS                 |

| 200    | RESERVED            |

| 201    | RESERVED            |

| 202    | SPCLK               |

| 203    | SPD                 |

| 204    | ROMEN               |

| 205    | RESET               |

| 206    | AD31                |

| 207    | AD30                |

| 208    | AD29                |

### Section 3: Functional Changes from Trio64V+

### 3.1 RESET/POWER-ON STRAPPING

The logic levels on PD[28:0] are latched in register bits for Trio64V+ and these pins are pulled up internally. However, only the logic value on MD11 is latched in a register bit (CR37\_3) for Trio64UV+ and all MD pin pull-ups are removed. MD11 can only be strapped in a test configuration (to allow use of external MCLK and DCLK) and must never be strapped in an operational system.

The default values for some of the former (Trio64V+) power-on strapping bits have been changed so that Trio64UV+ will power up in a standard, operational configuration, e.g., in fast page memory mode using internal MCLK and DCLK.

### 3.2 MEMORY INTERFACE

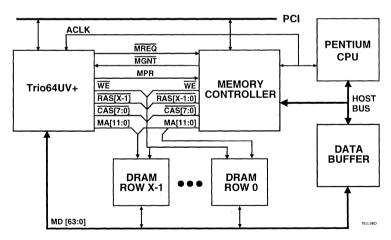

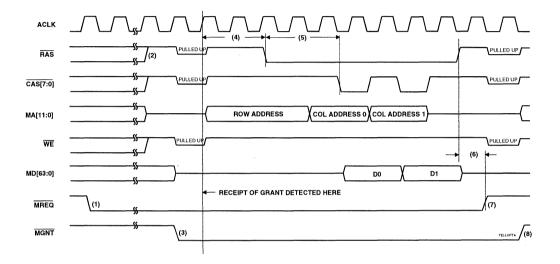

Trio64UV+ system and memory interface is shown in Figure 3-1.

Figure 3-1. System and Memory Interface Block Diagram

### Note to Figure 3-1

1. Trio64UV+ drives MA[11:0] only to DRAM row x-1. This is the first (physically) installed bank. The DRAM assigned to Trio64UV+ is then mapped by the core logic to the highest area of memory.

### 3.2.1 Memory Map

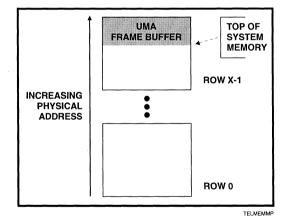

Trio64UV+ UMA frame buffer is located at the very top of physical memory. This is illustrated by Figure 3-2.

### 3.2.2 Address Translation

Address translation for MA[11:0] varies among core logic companies. Trio64UV+ supports a number of these variations as shown in Figure 3-3. The blank cells are for addresses above A20. These are always driven high by Trio64UV+ because it is always located at the top of the memory address space. The desired map is selected via CR81 6-4.

### 3.2.3 DRAM Types Supported

Trio64UV+ supports Fast Page and EDO memory in SIMM configuration, with EDO strongly preferred for its higher bandwidth. SDRAM pins are reserved for future use.

### 3.3 MEMORY ARBITRATION

### 3.3.1 Protocol Description

The arbitration scheme allows the core logic and Trio64UV+ to share memory resources effectively while minimizing performance degradation. The core logic is the memory owner; Trio64UV+ requests the memory when it needs access. In order to communicate the urgency of

Figure 3-2. Memory Map

### Notes to Figure 3-2

- "Top of system memory" refers to top of memory as reported to the operating system. The UMA frame buffer is located above that (and could be mapped by the core logic to a higher, non-contiguous location).

- 2. The UMA frame buffer is not accessible to the Operating System as system memory, but device drivers could access this region through the core logic memory controller (MC). This region must be made non-cacheable as no bus snooping is done.

- 3. PCI masters can access the UMA frame buffer only through Trio64UV+. Therefore:

- A. The MC must ignore PCI master accesses with the UMA frame buffer as the target (the MC cannot claim the cycle)

- B. Trio64UV+ must implement a standard PCI base address for the UMA frame buffer.

### VUMA standard (symmetric and asymmetric x9 and x10)

|     | MA11 | MA10 | MA9 | MA8 | MA7 | MA6 | MA5 | MA4 | MA3 | MA2 | MA1 | MA0 |

|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Row |      |      |     | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

| Col |      |      |     | A11 | A10 | A9  | A8  | A7  | A6  | A5  | A4  | А3  |

### VUMA (asymmetric x8)

|     | MA11 | MA10 | MA9 | MA8 | MA7 | MA6 | MA5 | MA4 | МАЗ | MA2 | MA1 | MAO |

|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Row |      |      | A11 | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

| Col |      |      |     |     | A10 | A9  | A8  | A7  | A6  | A5  | A4  | A3  |

### Alternate A (10x10, 11x10)

|     | MA11 | MA10 | MA9 | MA8 | MA7 | MA6 | MA5 | MA4 | MA3 | MA2 | MA1 | MA0 |

|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Row |      |      |     | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

| Col |      |      | A11 |     | A10 | A9  | A8  | A7  | A6  | A5  | A4  | А3  |

#### Alternate B (11x11)

|     | MA11 | MA10 | MA9 | MA8 | MA7 | MA6 | MA5 | MA4 | МАЗ | MA2 | MA1 | MA0 |

|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Row |      |      |     | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

| Col |      | A11  |     |     | A10 | A9  | A8  | A7  | A6  | A5  | A4  | АЗ  |

### Alternate C (12x8, 12x10)

|     | MA11 | MA10 | MA9 | MA8 | MA7 | MA6 | MA5 | MA4 | MA3 | MA2 | MA1 | MAO |

|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Row | A11  |      |     | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

| Col |      |      |     |     | A10 | A9  | A8  | A7  | A6  | A5  | A4  | АЗ  |

Figure 3-3. Address Translation

a given request, there are two types of requests: high priority and normal (i.e., low priority). A four pin interface controls this communication:

MREQ - Memory Request indicates to the core logic that Trio64UV+ wants control of the memory.

MGNT - Memory Grant indicates to the Trio64UV+ that access to the memory has been granted.

MPR - *Memory Priority* indicates the priority of a given request. A high state indicates a high priority request, while a low state indicates a normal request. This pin has no meaning when MREQ is

not asserted. It also has no meaning when a 2-pin arbitration scheme is selected via CR81\_1-0.

ACLK - Arbitration Clock provides timing for these arbitration signals, all of which are sampled on the rising edge. This is the same clock as the host clock.

### 3.3.2 Arbitration Timing Diagrams

Trio64UV+ supports several protocols for both normal and high priority memory arbitration. The timing diagrams for the VUMA protocols are presented in this section. The Intel SMBA proto-

col is also supported. Contact Intel for the specifications.

Figure 3-4 illustrates the basic (low priority) VUMA-style synchronous arbitration protocol for a 2-cycle EDO read. This protocol is selected when CR81 1-0 = 00b.

Figure 3-4. VUMA-Style Low Priority Arbitration

#### Notes to Figure 3-4

- 1. Trio64UV+ asserts MREQ to access memory when necessary, for example a graphics engine command or as the display FIFO begins to empty.

- 2. The core logic responds by driving RAS, CAS[7:0] and WE high for at least one clock.

- 3. The core logic alerts Trio64UV+ that it has granted the bus by asserting MGNT. RAS, CAS[7:0], and WE float for one clock, after which Trio64UV+ takes over by driving the row address. Note that the floating signals are held high by internal or external pull-ups.

- 4. The time between recognition of the grant and assertion of RAS is programmable via CR83\_3-2.

- 5. The RAS to CAS time is programmable (CR58\_7 and CR83\_4).

- The time between RAS high and MREQ high is programmable via CR83\_1-0. A value of 1 cycle is shown.

- One clock after Trio64UV+ has finished its memory accesses, it deasserts MREQ and floats RAS, CAS[7:0] and WE for one clock. RAS, CAS[7:0] and WE must have been held high for one clock prior to this time. The MA and MD busses are both tri-stated.

- 8. The core logic responds by deasserting MGNT one cycle later.

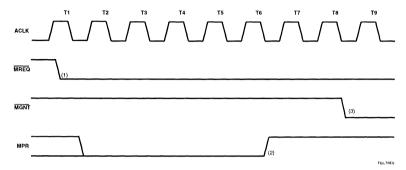

Figure 3-5 shows the operation of a high priority request using the S3 3-pin arbitration (CR81\_1-0 = 10b).

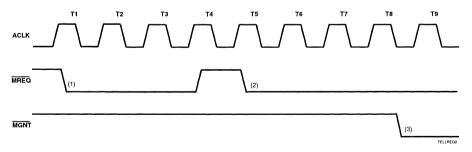

Figure 3-6 shows a high priority request using 2-pin arbitration (see CR81\_1-0).

Figure 3-5. S3 3-Pin Arbitration

#### Notes to Figure 3-5

- 1. Trio64UV+ requests memory control.

- 2. If the core logic does not respond with MGNT soon enough, causing the display FIFO to hit its near-empty watermark, Trio64UV+ raises the priority of its request by asserting MPR, and keeping it asserted until memory is granted.

- 3. The core logic asserts MGNT soon thereafter in response to the high priority request. Note that the request could have been issued as high priority from its onset if necessary. The worst-case latency for the core logic to respond to a high priority request is defined as 35 ACLKs in the VUMA specification.

Figure 3-6. 2-Pin Arbitration

#### Notes to Figure 3-6

- 1. Trio64UV+ requests memory control. The request is low priority.

- If the core logic does not respond with MGNT soon enough, causing the FIFO to hit its nearempty watermark, Trio64UV+ pulses the MREQ signal. This coverts the request to high priority.

- 3. The core logic asserts MGNT soon thereafter in response to the high priority request. The worst-case latency for the core logic to respond to a high priority request is defined as 35 ACLKs in

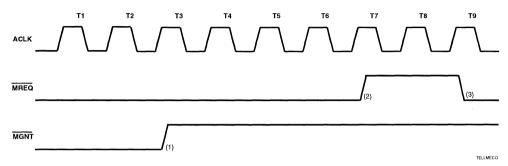

Figure 3-7 shows a situation where the core logic needs memory control back before Trio64UV+ is done.

Figure 3-7. Early Withdrawal of the Bus Grant

#### Notes to Figure 3-7

- 1. This example begins with Trio64UV+ having memory control. The core logic deasserts MGNT when it needs memory control (e.g., for DRAM refresh) before Trio64UV+ is done.

- 2. Trio64UV+ must respond to this request as soon as possible by deasserting MREQ.

The worst-case latency for Trio64UV+ to respond is screen resolution dependent. The worst case is approximately 80 ACLKs, but this is not quaranteed.

- 3. After giving up memory control in this way, it is likely that Trio64UV+ will immediately start requesting again since it presumably has unfinished tasks which need access to memory. MREQ needs to be deasserted for at least two full clock cycles.

### 3.4 MIXED VOLTAGE SUPPORT

Trio64UV+ is designed as an OEM selectable 5V/3.3V voltage part in order to interface with forthcoming 3.3V memories and core logic. Trio64UV+ has two isolated digital power planes as described below.

- All core functions in Trio64UV+ are still 5V, and are powered by VDDCORE. The LPB is also 5V and is powered by VDDLPB. The PCI subsystem is 5V and is powered by VDDSYS.

- The memory interface unit is powered by VDDMEM. VDDMEM can be connected to a 5V or 3.3V source, and all output levels from this portion of Trio64UV+ will be driven to the VDDMEM source level. The affected signals are MD[63:0], MA[11:0], CAS[7:0], RAS and WE.

If 5V memories are used with 3.3V core logic, VDDMEM for Trio64UV+ must be set to 3.3V and VDDMTOL must be set to 5V. If 3.3V memories are used with 3.3V core logic, both VDDMEM and VDDMTOL must be set to 3.3V. With 5V core logic and memories, both VDDMEM and VDDMTOL must be set to 5V.

A single digital ground plane is used.

### 3.5 OPERATING MODES

Trio64UV+ supports two operating modes as shown in Table 3-1.

Table 3-1. Operating Modes

| UMA<br>Arbitration | DRAM<br>Refresh<br>Owner | Operating<br>Mode    |

|--------------------|--------------------------|----------------------|

| Enabled            | CPU                      | UMA mode<br>(Note 1) |

| Disabled           | Trio64UV+                | Test<br>(Note 2)     |

### Notes

- UMA Mode is the "normal" operational mode. This mode is selected when CR82\_1-0 = 00b.

- Test mode is used for validation when Trio64UV+ operates out of a private memory bank. In addition, UMA arbitration is turned off, giving Trio64UV+ unlimited access to memory. This mode also allows Trio64UV+ to operate as a standalone Trio64V+ with virtually complete functionality. This mode is selected when CR82\_1-0 = 11b.

## Section 4: Register Changes from Trio64V+

### 4.1 REGISTERS CHANGED

| Register  | Bit(s) | Description                                                                                                                                                                                                                                                                                                     |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRA       | 6      | Reserved (RAS1 eliminated)                                                                                                                                                                                                                                                                                      |

| SRD       | 1      | 0 = Reserved (Trio64-compatible VAFC feature connector eliminated)                                                                                                                                                                                                                                              |

| SR1C      | 1-0    | The VL-Bus selections are eliminated.                                                                                                                                                                                                                                                                           |

| CR2E      | 7-0    | New chip ID = 14H                                                                                                                                                                                                                                                                                               |

| CR2F      | 7-0    | Revision ID = xxH                                                                                                                                                                                                                                                                                               |

| CR34      | 4      | Reserved (CR3B not used)                                                                                                                                                                                                                                                                                        |

| CR36      | 1-0    | Reserved - Hardwired to boot in PCI mode                                                                                                                                                                                                                                                                        |

| CR36      | 3-2    | MD pin values are not latched into these bits on reset. The default value is 11b (fast page mode DRAM operation). 1-cycle EDO operation is not supported.                                                                                                                                                       |

| CR36      | 4      | Reserved (no VL-Bus)                                                                                                                                                                                                                                                                                            |

| CR36      | 7-5    | 000 = Reserved (4 MBytes not supported)<br>101 = 1.5 MBytes<br>111 = 0.5 MByte                                                                                                                                                                                                                                  |

| CR37      | 0      | Reserved (no VL-Bus)                                                                                                                                                                                                                                                                                            |

| CR37      | 2      | Reserved (no VL-Bus)                                                                                                                                                                                                                                                                                            |

| CR37      | 3      | An MD pin value is not latched into this bit on reset. The default value is 1 (use internal clocks).                                                                                                                                                                                                            |

| CR37      | 4      | Reserved (no VL-Bus)                                                                                                                                                                                                                                                                                            |

| CR3B      | 7-0    | Reserved (Replaced by CR85_1-0)                                                                                                                                                                                                                                                                                 |

| CR40      | 4      | Reserved (no VL-Bus)                                                                                                                                                                                                                                                                                            |

| CR53      | 4-3    | No VL-Bus power-on default                                                                                                                                                                                                                                                                                      |

| CR58      | 1-0    | 11 = Reserved (no 4-MByte window). For a 0.5 MByte frame buffer, the linear addressing window size should be set to 1 MByte. For a 1.5 MByte frame buffer, the linear addressing window size should be set to 2 MBytes. In either case, software must not write beyond the size specified for the frame buffer. |

| CR58      | 3      | Reserved (no VL-Bus)                                                                                                                                                                                                                                                                                            |

| CR59,CR5A | 15-0   | No VL-Bus power-on default. No 4-MByte window.                                                                                                                                                                                                                                                                  |

| CR5D      | 6      | Reserved (CR3B not used)                                                                                                                                                                                                                                                                                        |

| CDCO   | 1.0   | AAD air and a second data data data data data data data da                                                                                                                                                                                                                                                                                                                                                            |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR68   | 1-0   | MD pin values are not latched into these bits on reset. The default value is 11b (no stretch).                                                                                                                                                                                                                                                                                                                        |

| CR68   | 2     | An MD pin value is not latched into this bit on reset. The default value is 1 (3.5 MCLKs).                                                                                                                                                                                                                                                                                                                            |

| CR68   | 3     | An MD pin value is not latched into this bit on reset. The default value is 1 (2.5 MCLKs).                                                                                                                                                                                                                                                                                                                            |

| CR68   | 7     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                              |

| CR69   | 4     | Reserved (2 MByte maximum memory)                                                                                                                                                                                                                                                                                                                                                                                     |

| CR6A   | 5     | Reserved (2 MByte maximum memory)                                                                                                                                                                                                                                                                                                                                                                                     |