LC89510

CMOS LSI

Error Correction and Host-interface IC for CD-ROM and CD-I Players

### **OVERVIEW**

The LC89510 is an error correction and host-interface IC for CD-ROM and CD-I players that integrates real-time error detection and correction with erasure correction and host-interface data transfer functions into a single chip.

The LC89510 features an 8-Kbit erasure-correction RAM, on-chip command and status FIFOs, and a buffer memory interface that supports up to 64 Kbytes of external SRAM. The buffer memory interface allows the LC89510 to buffer up to 27 sectors of data when connected to a slow host. The LC89510 can correct two errors per symbol with erasure correction. Also, the command FIFO supports 8-byte commands, making CD-ROM systems using a SCSI bus easier to design.

The LC89510 is pin- and software-compatible with the LC8951, although the LC8951 is available in QIP-80A packages. It improves upon the LC8951 through modification of one section of the internal registers and the addition of the erasure-correction RAM.

The LC89510 operates from a 5 V supply and is available in 80-pin QIPs.

## **FEATURES**

- CD-ROM (Mode 1) and CD-I (Mode 2 Form 1 and Form 2) formats supported

- Real-time error detection and correction in hardware

- 2.3 Mbyte/s (18.4 Mbit/s) maximum data throughput and transfer rates

- · Corrects two errors per symbol with erasure correction

- 8 Kbit of erasure-correction RAM

- 8-byte command FIFO and 12-byte status FIFO

- Up to 64 Kbyte of external buffer SRAM

- · Buffers up to 27 sectors of data

- Pin- and software-compatible with the LC8951

- 5 V supply

- 80-pin QIP

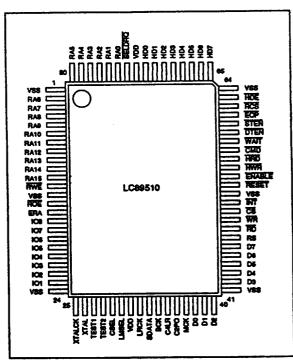

### **PINOUT**

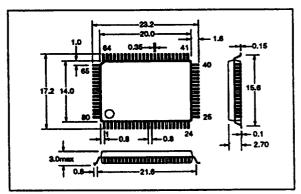

## PACKAGE DIMENSIONS

Unit: mm

3174-QIP80E

Specifications and information herein are subject to change without notice.

SANYO Electric Co., Ltd. Semiconductor Division atsume Bldg., 18-6, 2-chome, Yushima, Bunkyo-ku, TOKYO 113 JAPAN Natsume Bldg., 18-6, 2-chome,

4032JN No. 3958---1/6

## LC89510

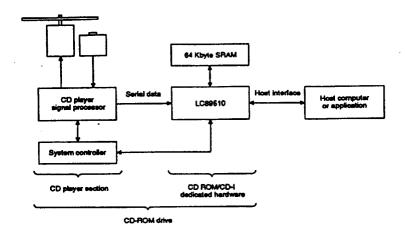

# SYSTEM BLOCK DIAGRAM

# PIN DESCRIPTION

| Number                | Name         | Description                                                                           |

|-----------------------|--------------|---------------------------------------------------------------------------------------|

| 1, 13, 24, 41, 52, 64 | VSS          | Ground                                                                                |

| 2 to 11, 75 to 80     | RAO to RA15  | Buffer RAM and erasure flag RAM address bus output lines                              |

| 12                    | RWE          | Buffer RAM write enable output                                                        |

| 14                    | ROE          | Buffer RAM output enable output                                                       |

| 15                    | ERA          | Single-bit, bidirectional erasure flag RAM data line                                  |

| 16 to 23              | 101 to 108   | 8-bit, bidirectional buffer RAM data bus lines with internal pull-up resistors        |

| 25                    | XTALCK       | Crystal oscillator input                                                              |

| 26                    | XTAL         | Crystal oscillator output                                                             |

| 27, 28                | TEST1, TEST2 | Test inputs. Should be fed LOW.                                                       |

| 29                    | CSEL.        | Serial data clock phase select input                                                  |

| 30                    | LMSEL        | Serial data mab-first/fish-first bit-order select input                               |

| 31, 73                | VDD          | 5 V supply                                                                            |

| 32                    | LRCK         | 44.1 kHz left- and right-channel separator strobe input                               |

| 33                    | SDATA        | Serial data input                                                                     |

| 34                    | BCK          | Buffer clock input                                                                    |

| 36                    | C4LR         | C2 error flag pointer strobe input                                                    |

| 36                    | CSPO         | CD player interface C2-flag pointer input                                             |

| 37                    | MCK          | CD player interface reference clock output                                            |

| 36 to 40, 42 to 46    | DO to D7     | 8-bit, bidirectional microprocessor data bus lines                                    |

| 47                    | RS           | Register select input                                                                 |

| 48                    | RD           | Active-LOW data read input                                                            |

| 49                    | WR           | Active-LOW data write input                                                           |

| 50                    | হৈ           | Active-LOW chip select input                                                          |

| 51                    | INT          | Active-LOW interrupt request output. Open-drain output with internal pull-up resistor |

| 53                    | RESET        | Active-LOW, Schmitt-trigger reset input                                               |

No. 3958-2/6

| Number   | Name       | Description                                        |

|----------|------------|----------------------------------------------------|

| 54       | ENABLE     | Active-LOW, host-interface enable input            |

| 55       | HWH        | Active-LOW, host-interface data write input        |

| 56       | HAD        | Active-LOW, host-interface data read input         |

| 57       | СМБ        | Active-LOW, host command/data select input         |

| 58       | WAIT       | Active-LOW, data transfer WAIT/DRQ signal output   |

| 59       | DTEN       | Active-LOW, data enable output                     |

| 60       | STEN       | Active-LOW status enable output                    |

| 61       | EOP        | End of process flag output                         |

| 62       | RCS        | Buffer RAM chip-select output                      |

| 63       | HDE        | Tristate, host data erasure flag output            |

| 65 to 72 | HD0 to HD7 | 8-bit, bidirectional host-interface data bus lines |

| 74       | SELDRO     | WAIT/DRQ control data transfer mode select input   |

#### Note

All VDD and VSS pins should be connected to supply and ground, respectively.

## **SPECIFICATIONS**

## **Absolute Maximum Ratings**

| Parameter                   | Symbol          | Reting                        | Unit |

|-----------------------------|-----------------|-------------------------------|------|

| Supply voltage range        | V <sub>DD</sub> | -0.3 to 7.0                   | ٧    |

| Input voltage range         | V <sub>I</sub>  | -0.3 to V <sub>00</sub> + 0.3 | ٧    |

| Output voltage range        | Vo              | -0.3 to V <sub>DO</sub> + 0.3 | ٧    |

| Power dissipation           | Po              | 350                           | mW   |

| Operating temperature range | Teps            | 30 to 70                      | ~℃   |

| Storage temperature range   | Tele            | -55 to 125                    | •℃   |

| Soldering temperature       | T <sub>8</sub>  | 260 (l = 10 s)                | •℃   |

# **Recommended Operating Conditions**

T. = 25 °C

| Paramotor              | Symbol          | Rating     | Unit |

|------------------------|-----------------|------------|------|

| Supply voltage         | V <sub>DD</sub> | 5          | ٧    |

| Supply voltage range . | V <sub>DO</sub> | 4.5 to 5.5 | γ    |

## **Electrical Characteristics**

$V_{DD} = 4.5$  to 5.5 V,  $V_{SS} = 0$  V,  $T_a = -30$  to 70 °C

| Parameter                                                                           | O                | Condition |      | Unit |     |      |

|-------------------------------------------------------------------------------------|------------------|-----------|------|------|-----|------|

| Parameter                                                                           | Symbol           | Condition | समेत | typ  | mex | Cint |

| Input voltage range                                                                 | VI               |           | 0    | -    | Voo | ٧    |

| RESET, RD, WR, HRD, HWR, CMD,<br>CS, ENABLE and bus pins LOW-level<br>input voltage | V <sub>IL1</sub> |           | -    | -    | 0.6 | ٧    |

|                                                                                      | 0                | Condition                                           |     | Unit |     |      |

|--------------------------------------------------------------------------------------|------------------|-----------------------------------------------------|-----|------|-----|------|

| Parameter                                                                            | Symbol           | Condition                                           | min | typ  | mex | Unit |

| LOW-level input voltage for all other input pins except XTALCK                       | V <sub>K.2</sub> |                                                     | -   | -    | 0.8 | v    |

| RESET, RD, WR, HRD, HWR, CMD,<br>CS, ENABLE and bus pins<br>HIGH-level input voltage | V <sub>IH1</sub> |                                                     | 2.5 | -    | -   | ٧    |

| HIGH-level input voltage for all other input pins except XTALCK                      | Valz             |                                                     | 22  | -    | _   | V    |

| INT LOW-level output voltage                                                         | Voli             | Open-drain output with pull-up resistor, lot = 3 mA | -   | -    | 0.4 | ٧    |

| LOW-level output voltage for all other output pins except XTAL                       | V <sub>OL2</sub> | loL = 3 mA                                          | **  | -    | 0.4 | ٧    |

| HIGH-level output voltage for all output pins except INT and XTAL                    | V <sub>OH</sub>  | I <sub>OH</sub> = 3 mA                              | 24  | -    | -   | ٧    |

| INT and bus pins pull-up resistance                                                  | Rup              |                                                     | 10  | 20   | 40  | kΩ   |

| Input leakage current                                                                | l <sub>L</sub>   | V <sub>i</sub> = V <sub>SS</sub> or V <sub>DD</sub> | -25 | -    | 25  | μΑ   |

### **FUNCTIONAL DESCRIPTION**

The LC89510 comprises three main blocks—a CD player interface and data input block, an error detection and correction circuit, and a host interface—that operate in parallel. The LC89510 performs pipelined data input and decoding, simultaneous input data buffering, error detection and correction, and data transfer to a host processor.

# CD Player Interface and Data Input

The input data passes through the synchronization stage, is then decoded and written to buffer RAM. The input data can be in one of three formats selected using CSEL and LMSEL.

The synchronization stage comprises a sync detector and a sync interpolator. The sync detector detects the sync pattern in each sector of data and the sync interpolator generates the synchronization pulses. The detector and interpolator can be individually enabled and disabled using the control microprocessor.

After decoding, each full sector of data—2352 bytes comprising the sync, header, sub-header and parity fields—is written contiguously to the buffer RAM in units comprising eight data bits and their corresponding C2 error flag from the CD player signal processor. If erasure correction is not required, the C2 error flag write can be disabled and the data written in 8-bit rather than 9-bit units.

MCK can be used as the reference clock for the CD player signal processor, eliminating the need for a separate oscillator circuit. In this case, the LC89510 clock frequency should be double the signal processor clock frequency.

#### Error Detection and Correction Circuit

Error detection and correction is performed on each sector after it is written to buffer RAM.

The LC89510 uses the C2 error flag data to perform erasure correction, before error correction. Since the LC89510 has an on-chip 8-Kbit erasure-correction RAM, erasure correction can be performed with as little as 8 Kbytes of external buffer RAM.

The standard error detection algorithm can be programmed for a range of processes, including repeat correction and QP/PQ correction.

After the error correction code (ECC) is decoded, the 32-bit error detection code (EDC) CRC error check is performed. The sector header and sub-header are then copied to the LC89510.

After the CRC check, the LC89510 issues a decode-complete interrupt to the control microprocessor. The microprocessor then reads the decoder status, the sector header and sub-header, and the sector start address from the LC89510 into buffer RAM.

#### Host Interface

#### Command and status FIFOs

The FIFOs communicate between the host processor and the control microprocessor. There are no restrictions on the commands and status codes that can be used, since the LC89510 ignores the contents of the FIFOs. This provides the CD-ROM application-system designer with the maximum flexibility for incorporating the LC89510 into existing designs.

No. 3958--4/6

When HWR goes LOW, the host processor writes a command of up to 8 bytes in length into the command FIFO. The LC89510 then issues a command interrupt to the control microprocessor, which then reads the command.

The microprocessor transfers decoder and CD-ROM status to the host processor by writing to the 12-byte status FIFO. The host processor can then read status information from the FIFO when STEN is LOW. STEN goes HIGH when the last byte is read.

### Data transfer

The control microprocessor transfers blocks of data to the host by writing the block start address and the number of bytes to be transferred into the LC89510 registers. It then issues a ready signal to the LC89510 data transfer start-trigger register and waits until the transfer is completed.

The LC89510 signals the start of data transfer to the host by setting DTEN LOW. While DTEN is LOW, the host reads the data from the LC89510 by repeatedly strobing HRD. For fast hosts, HRD should be held LOW while the LC89510 WAIT output is LOW to ensure that data is read correctly.

Taking SELDRQ LOW selects the DRQ (data request) transfer mode, which is similar to DMA operation. Each time the LC89510 outputs a data request signal by setting DTEN LOW, the host processor strobes HRD once.

When the last byte is transferred, EOP goes LOW while HRD is LOW and then DIEN goes HIGH. When DIEN goes HIGH, the LC89510 issues a data transfer complete interrupt to the control microprocessor, which then informs the host that transfer has been completed.

## **Control Registers**

## Read registers

|    |   |     |      | Reg | loter  |        | Sit podilos |                |        |        |             |        |           |        |

|----|---|-----|------|-----|--------|--------|-------------|----------------|--------|--------|-------------|--------|-----------|--------|

| RS |   | Add | 7000 |     | Number | Hemo   | 7           | . 8            | 5      | 4      | 3           | 2      | 1         | ٠      |

| 0  | × | ×   | ×    | ×   | -      | AR     | •           | 0              | •      | 0      | A\$         | A2     | At        | A0     |

|    | • | 0   | 0    | 0   | RO     | COMM   | ***         |                |        |        |             |        |           | lab    |

|    | • | 0   | •    | 1   | Rt     | IFSTAT | CMDI        | <u> ग्र</u> ाह | DECI   | 1      | DTBSY       | STRSY  | DTEN      | STEN   |

|    | • | 0   | 1    | •   | P2     | DBCL   | 87          | >=             | 86     | M      | <b>83</b>   | 82     | 81        | 90     |

|    | • | ۰   | 1    | 1   | Rs.    | DBCH   | отв         | отв            | DTE    | OIB    | <b>B</b> 11 | B10    | <b>39</b> | 86     |

|    | • | 1   | •    | •   | R4     | HEADO  | meb         |                |        |        |             |        |           | lab    |

|    | • | 1   | •    | 1   | PIS    | HEADI  | meb         |                |        |        |             |        |           | lab    |

|    | • | 1   | 1    | .0  | 766    | HEADS  | meb         |                |        |        |             |        |           | lab .  |

|    | • | 1   | 1    | 1   | 907    | HEAD8  | meb         |                |        |        |             |        |           | 140    |

| 1  | 1 | •   | •    | •   | m      | PN.    | A7          | AS             | A5     | м      | AS          | A2     | Al        | AO     |

|    | 1 | •   | •    | 1   | 700    | PTH    | A15         | A14            | A13    | A12    | A11         | A10    | AS        | AS     |

|    | 1 | •   | 1    | •   | R10    | WAL    | A7          | AB             | AS     | м      | A3          | A2     | Al        | A0     |

|    | 1 | •   | 1    | 1   | PHI    | WAH    | A16         | A14            | A19    | A12    | A11         | A10    | A9        | AB     |

|    | 1 | 1   | •    | •   | P12    | STATO  | CROOK       | RESYNC         | HOSYNC | LBLK   | WSHORT      | SBUK   | ENBLK     | UCEBLK |

|    | 1 | 1   | •    | 1   | R18    | STAT1  | MENERA      | SECERA         | BUCEPA | MODERA | SHOERA      | SHIERA | SHZERA    | SHOERA |

|    | 1 | 1   | 1    | 0   | R14    | STATE  | FMCC8       | FIMODE         | FIMODI | PMCD0  | MODE        | HOCOR  | RFORM1    | RECEMO |

|    | 1 | 1   | 1    | 1   | R15    | STATS  | VALST       | WLONG          | CBLK   | ×      | ×           | ×      | ×         | ×      |

Note

$\times$  = don't care

#### LC89510

### Write registers

| RS |          |          |       | Reg | Polar       |         | Sit position |       |        |        |         |         |         |         |

|----|----------|----------|-------|-----|-------------|---------|--------------|-------|--------|--------|---------|---------|---------|---------|

|    |          | Add      | prime |     | Humber      | Name    | 7            |       | 8      | 4      | 3       | 2       | 1       | •       |

| 0  | ×        | ×        | ×     | ×   | -           | AR      | ×            | ×     | ×      | ×      | A3      | A2      | Al      | AO      |

|    | •        | 0        | •     | 0   | NO.         | TVOGE   | meb          |       |        |        |         |         |         | inb     |

|    | 0        | 0        | •     | 1   | Rt          | IFCTRL. | CMIDIEN      | DEFEN | DECIEN | CMOBK  | DTWAI   | STWAI   | DOUTEN  | SOUTEN  |

|    | 0        | 0        | 1     | ٥   | R2          | DBCL    | 87           | 24    | BS     | 84     | 83      | B2      | 81      | 80      |

|    | 0        | 0        | 1     | 1   | RB          | DBCH    | ×            | ×     | ×      | ×      | 811     | B10     | B0      | B8      |

|    | •        | 1        | 0     | 0   | M           | DACL    | A7           |       | AS     | м      | A9      | A2      | Al      | AO      |

|    | 0        | 1        | 0     | 1   | <b>9</b> 15 | DACH    | A15          | A14   | A13    | A12    | A11     | A10     | A9      | A8      |

|    | 0        | 1        | 1     | 0   | R6          | DTTRG   | ×            | ×     | ×      | ×      | ×       | ×       | ×       | ×       |

| ١, | 0        | 1        | 1     | 1   | 917         | DTACK   | ×            | ×     | ×      | ×      | ×       | ×       | ×       | ×       |

| •  | 1        | ٥        | 0     | 0   | Rit         | WAL     | A7           | A     | AS     | м      | A3      | A2      | A1      | A0      |

|    | 1        | ۰        | ۰     | 1   | Re          | WAH     | A15          | A14   | A13    | A12    | A11     | A10     | AB      | AB      |

| Ì  | <u>'</u> | •        | 1     | •   | R10         | CTRLO   | DECEN        | ×     | E01RQ  | AUTORQ | ERAMPIQ | WRRQ    | ORQ     | PRQ     |

| ŀ  | 1        | 0        | 1     | 1   | R11         | , CTRL1 | SYIEN        | SYDEN | DSCREN | COWREN | MODRO   | FORMAQ  | MBCKRQ  | SHOREN  |

|    | 1        | 1        | •     | 0   | R12         | PTL     | AZ           | AB    | AS     | м      | A3      | A2      | Al      | Α0      |

| Ī  | 1        | 1        | •     | 1   | R13         | PTH     | A1S          | A14   | A13    | A12    | A11     | A10     | A9      | A8      |

|    | 1        | 1        | 1     | ۰   | R14         | CTRL2   | ×            | ×     | ×      | ×      | ×       | ERAMBL. | SIENCIL | STENTRO |

|    | 1        | <u> </u> | 1     | '   | R15         | REBET   | ×            | ×     | ×      | ×      | ×       | ×       | ж       | ×       |

#### Note

x = don't care

#### Control register 2 (CTRL2)

CTRL2 comprises the ERAMSL, STENCTL and STENTRG register bits and five unassigned bits.

ERAMSL controls the internal erasure-correction RAM operation. When ERAMSL is 0, the RAM is enabled and when 1, disabled. ERAMSL is set to 0 following a

STENCTL controls the STEN output mode. When STENCTL is 0, STEN goes LOW after the controlling microprocessor has written one byte to the status FIFO. This is the same as LC8951 operation. When STENCTL is 1, STEN goes LOW only when the controlling microprocessor writes 0 to the STENTRG register, usually after the microprocessor has written multiple bytes to the status FIFO. STENTRG is automatically set to 1 and STEN set HIGH after the host computer reads the last byte from the status FIFO.

STENCTL is set to 0 following a reset.

information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

No. 3958---6/6