Circuit diagrams are included as a means of illustrating typical applications, and complete information for construction purposes is not necessarily given. The information presented here has been carefully checked, and is believed to be entirely reliable, but no responsibility is assumed for inaccuracies. Furthermore, no responsibility is assumed by SEEQ Technology, Inc., for its use; nor for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication, or otherwise, under any patent or patent rights of SEEQ Technology, Inc.

SEEQ Technology makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

SEEQ retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of SEEQ Technology and may only be used to identify SEEQ products:

Silicon Signature™ EDLC™ DiTrace™ MCC™

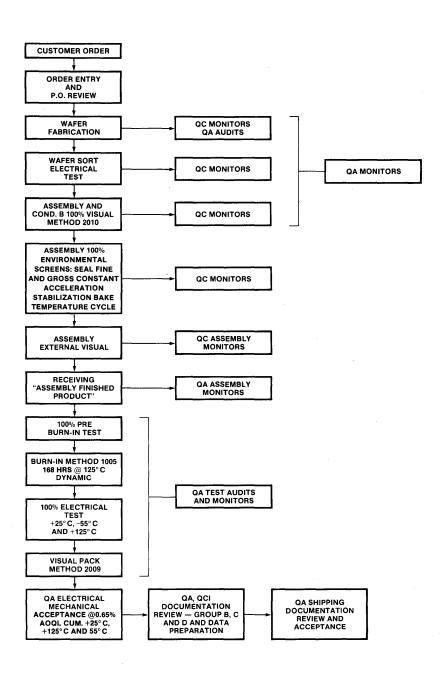

Assembly locations: Military products are assembled at SEEO's offshore (Korea, Philippines, Taiwan) and stateside assembly plants. The assembly plants are identified by a designated alpha code as part of the device backside marking. The alpha codes used are: Korea = K, Philippines = P, Taiwan = T, United States = U.S.A.

Additional copies of this manual or other SEEQ literature may be obtained from:

SEEQ Technology Incorporated Literature Department 1849 Fortune Drive San Jose, CA 95131

#### **Table of Contents**

|                                            | Programmat | ole Read Only Memories)                                   |

|--------------------------------------------|------------|-----------------------------------------------------------|

| DATA SHEETS                                | CAIZ       |                                                           |

| 2764(5133)                                 |            | 1-1                                                       |

| 27128(5143)                                |            | 1-1                                                       |

| 27C256                                     |            | CMOS 1-6                                                  |

| 27256                                      | 256K       | 1-16                                                      |

| SECTION 2                                  |            |                                                           |

| E2ROMS (Electrically                       | Erasable P | rogrammable Read Only Memories)                           |

| CROSS REFERE                               | NCE GUIDI  | E 2-1                                                     |

| SEEQ'S E <sup>2</sup> ROM I<br>DATA SHEETS | FAMILY CO  | NFIGURATION 2-2                                           |

|                                            | 101/       | Times 10K avales/b.ta                                     |

| 2816A/2816H                                | 16K        | Timer, 10K cycles/byte                                    |

| 5516A                                      | 16K        | Timer, 1M cycles/byte2-4                                  |

| 2817A/2817H                                | 16K        | Timer, rdy/busy, 10K cycles/byte 2-5                      |

| 5517A/5517H                                | 16K        | Timer, rdy/busy, 1M cycles/byte 2-9                       |

| 2864/2864H                                 | 64K        | Timer, rdy/busy 2-14                                      |

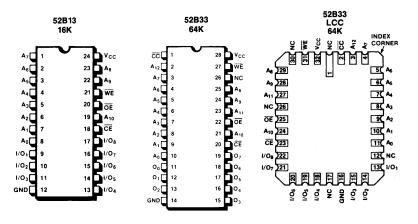

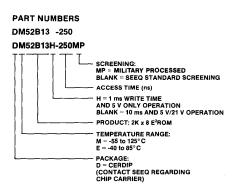

| 52B13/52B13H                               | 16K        |                                                           |

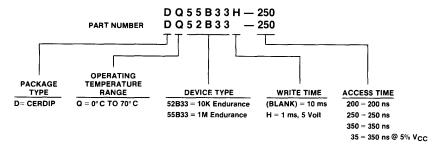

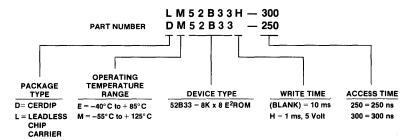

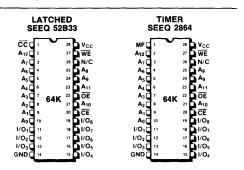

| 52B33/52B33H                               | 64K        | Latched E, 10K cycles/byte 2-27                           |

| 55B33/55B33H                               | 64K        |                                                           |

| SECTION 3<br>MICRO/LAN                     |            |                                                           |

| DATA SHEETS                                |            |                                                           |

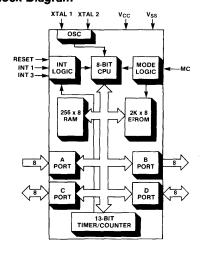

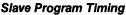

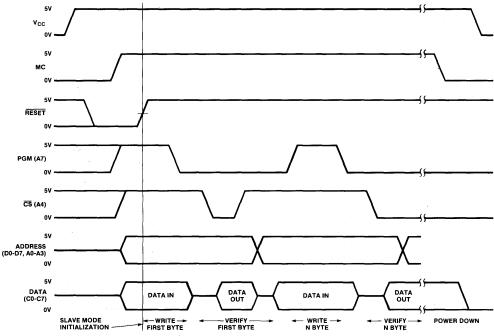

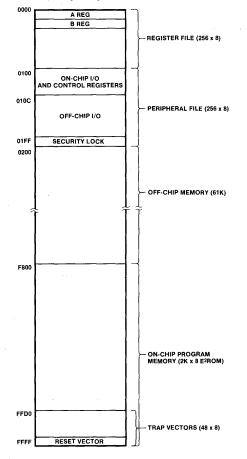

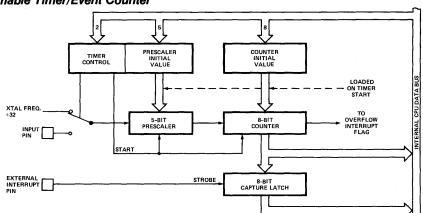

| 72720                                      | Self A     | Adaptive E <sup>2</sup> ROM Single Chip Microcomputer 3-1 |

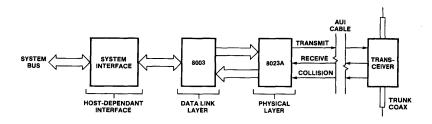

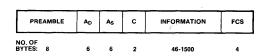

| 8003                                       | EDLO       | C Ethernet Data Link Controller 3-6                       |

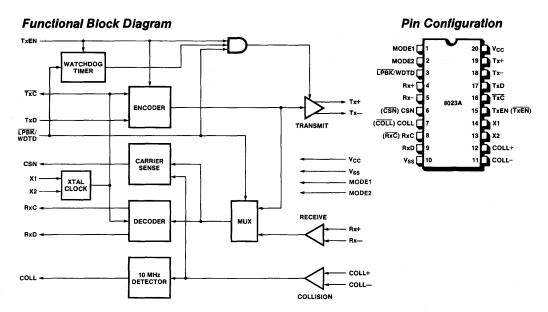

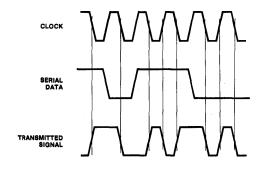

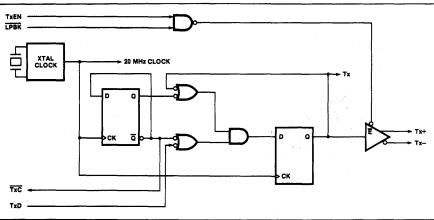

| 8023A                                      |            | Manchester Code Converter 3-17                            |

|                                            |            | •                                                         |

| SECTION 4                                  |            |                                                           |

| MILITARY AND INDU                          | JSTRIAL TI | EMPERATURE RANGE                                          |

| DATA SHEETS—                               | EPROM      |                                                           |

| M2764/E27128                               | 16K        | 4-1                                                       |

| M27128/E27128                              | 64K        | 4-1                                                       |

| M27256                                     | 256K       | 4-9                                                       |

| M27C256                                    | 256K       | CMOS 4-16                                                 |

| DATA SHEETS—                               |            |                                                           |

| M2816A                                     |            | Timer E 4-24                                              |

| M2817A                                     |            | Timer E, rdy/busy pin                                     |

|                                            |            | Timer E, rdy/busy pin                                     |

| M2864/M2864H                               |            |                                                           |

| M52B13/M52B13I                             |            | Latched E                                                 |

| E52B13/E52B13H                             |            | Latched E (-40 to 85°C) 4-41                              |

| M52B33/M52B33I                             |            | Latched E 4-48                                            |

| E52B33                                     |            | Latched E (-40 to 85°C) 4-48                              |

| MILITARY QUALI                             | ITY ASSUR  | ANCE PROGRAM 4-54                                         |

| SECTION 5                                  |            |                                                           |

| RELIABILITY/APPLIC                         | ATION NO   | TES                                                       |

| RELIABILITY RE                             |            | · <del>- ·</del>                                          |

| 1A                                         |            | ORY PRODUCTS RELIABILITY REPORT AUGUST 1985 5-1           |

| APPLICATION N                              |            | ONI PRODUCTS RELIABILITY REPORT AUGUST 1903 3-1           |

|                                            |            | CORROCCIONOR INTEREACINO WITH REFORM                      |

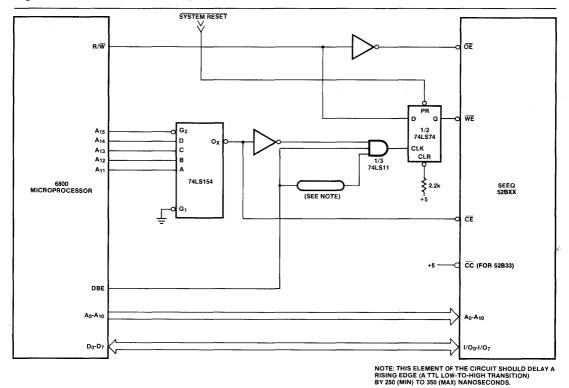

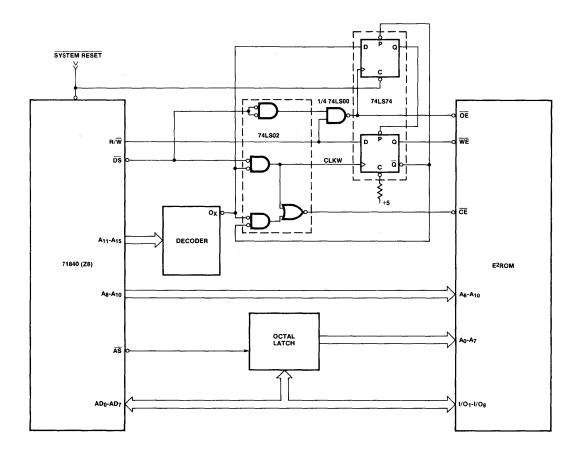

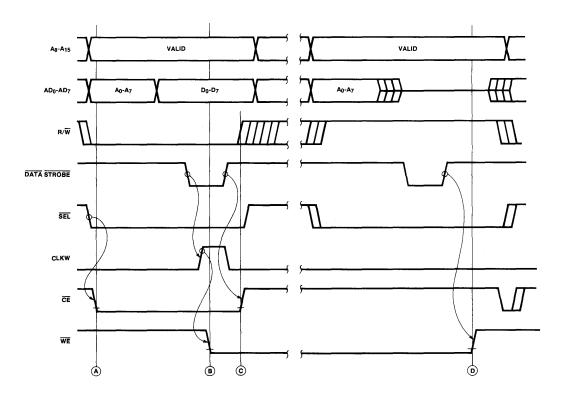

| 2A                                         |            | ROPROCESSOR INTERFACING WITH SEEQ'S                       |

|                                            | LATO       | CHED E <sup>2</sup> ROM 5-8                               |

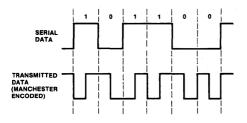

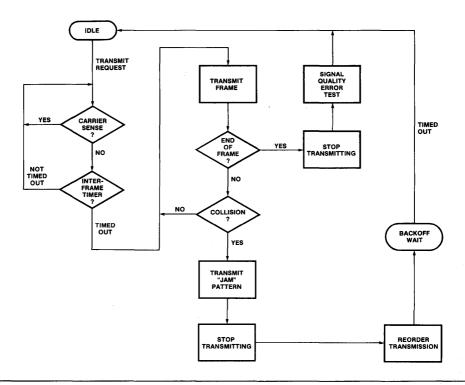

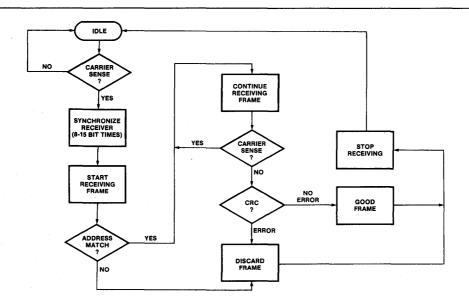

| 3A                                         |            | CHESTER ENCODING AND DECODING                             |

|                                            |            | LOCAL AREA NETWORKS 5-18                                  |

| 5A                                         |            | RFACING THE 8003 EDLC TO A 16-BIT BUS 5-26                |

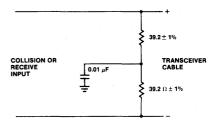

| 6A                                         |            | INTERCONNECTION TO THE 8003 EDLC 5-34                     |

| 8A                                         | E2RO       | M INTERFACING 5-43                                        |

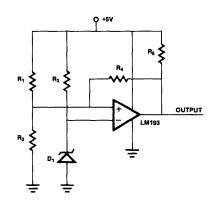

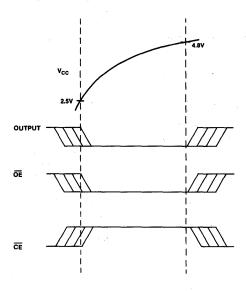

| 10A                                        |            | FR-LIP/DOWN WITH SEEO'S F2ROM 5-61                        |

## Table of Contents (Continued)

| SECTION 6                   |                                         |     |

|-----------------------------|-----------------------------------------|-----|

| SALES OFFICE LISTING        |                                         |     |

| DOMESTIC SALES OFFICES      | • • • • • • • • • • • • • • • • • • • • | 6-1 |

| INTERNATIONAL SALES OFFICES | 8                                       | 6-2 |

## **SECTION 1**

# **EPROMS**

(Erasable Programmable Read Only Memories)

2764 (5133) 64K ÈPROM 27128 (5143) *128K EPROM* April 1985

#### **Features**

- 200 ns Access Times at 0 to 70°C

- Programmed Using Intelligent Algorithm

- 21 V VPP

- 2 Minutes for 27128 (5143)

- 1 Minute for 2764 (5133)

- JEDEC Approved Bytewide Pin Configuration

- 2764 8K x 8 Organization

- 27128 16K x 8 Organization

- Low Power Dissipation

- 100 mA Active Current

- 30 mA Standby Current

- Extended Temperature Range Available

- Silicon Signature™

#### Description

SEEQ's 2764 (5133) and 27128 (5143) are ultraviolet light erasable EPROMs which are organized 8K x 8 and 16K x 8 respectively. They are pin for pin compatible to JEDEC approved 64K and 128K EPROMs in all operational/programming modes. Both devices have access times as fast as 200 ns over the 0 to 70°C temperature and V<sub>CC</sub> tolerance range. The access time is achieved without sacrificing power since the maximum active and standby currents are 100 mA and 30 mA respectively. The 200 ns allows higher system efficiency by eliminating the need for wait states in today's 8- or 16-bit microcomputers.

Initially, and after erasure, all bits are in the "1" state. Data is programmed by applying 21 V to VPP and a TTL "0" to pin 27 (program pin). The 2764 (5133) and 27128 (5143) may be programmed with an intelligent

(continued on page 2)

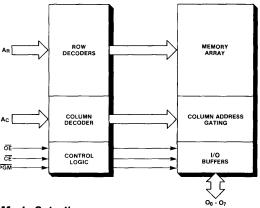

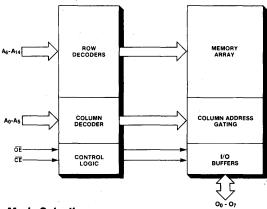

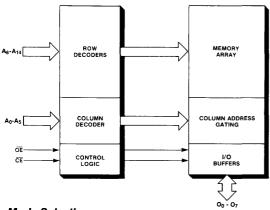

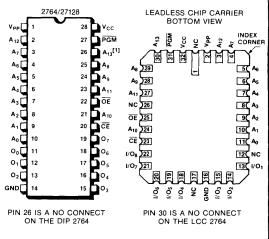

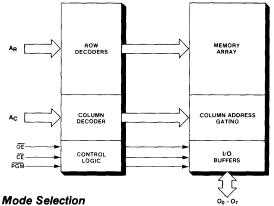

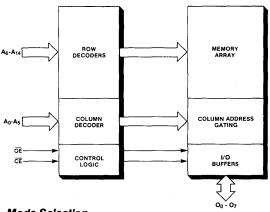

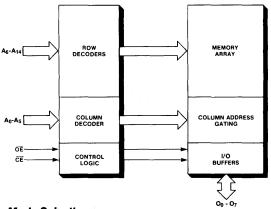

#### Block Diagram

#### Mode Selection

| PINS                | CE<br>(20) | ŌE<br>(22) | PGM<br>(27) | V <sub>PP</sub> (1) | V <sub>CC</sub><br>(28) | Outputs<br>(11-13, 15-19) |

|---------------------|------------|------------|-------------|---------------------|-------------------------|---------------------------|

| Read                | VIL        | ViL        | ViH         | Vcc                 | Vcc                     | Dout                      |

| Output Disable      | Χ          | Viн        | Vcc         | Vcc                 | Vcc                     | High Z                    |

| Standby             | ViH        | Х          | Х           | Vcc                 | Vcc                     | High Z                    |

| Program             | VIL        | ViH        | VIL         | Vpp                 | Vcc                     | DiN                       |

| Program Verify      | VIL        | ViL        | ViH         | VPP                 | Vcc                     | Dout                      |

| Program Inhibit     | VIH        | Х          | Х           | Vpp                 | Vcc                     | High Z                    |

| Silicon Signature™* | VIL        | VIL        | VIH         | Vcc                 | Vcc                     | Encoded<br>Data           |

X can be either VIL or VIH

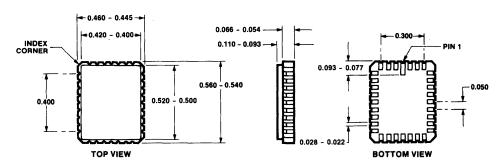

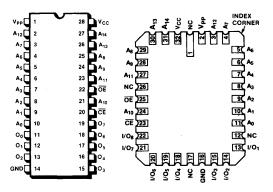

#### Pin Configuration

ON THE 2764.

#### Pin Names

| Ac                              | ADDRESSES — COLUMN (LSB) |

|---------------------------------|--------------------------|

| AR                              | ADDRESSES - ROW          |

| CE                              | CHIP ENABLE              |

| OE                              | OUTPUT ENABLE            |

| O <sub>0</sub> - O <sub>7</sub> | OUTPUTS                  |

| PGM                             | PROGRAM                  |

<sup>\*</sup> For Silicon Signature\*\*: Ao is toggled, A9 = 12V, and all other addresses are at a TTL low. Silicon Signature™ is a registered trademark of SEEQ Technology.

## 2764 (5133) 27128 (5143)

algorithm that is now available on commercial programmers. The programming time is typically 5 ms/byte or 2 minutes for all 16K bytes of the 27128. The 2764 requires only half of this time, about a minute for 8K bytes. This faster time improves manufacturing throughput time by hours over conventional 50 ms algorithms. Commercial programmers (e.g. Data I/O, Pro-log, Digelec, Kontron, and Stag) have implemented this fast algorithm for SEEQ's EPROMs. If desired, both EPROMs may be

programmed using the conventional 50 ms programming specification of older generation EPROMs.

Incorporated on SEEQ's EPROMs is Silicon Signature™. Silicon Signature contains encoded data which identifies SEEQ as the EPROM manufacturer, the product's fab location, and programming information. This data is encoded in ROM to prevent erasure by ultraviolet light.

#### Absolute Maximum Ratings

| Temperature                             |

|-----------------------------------------|

| Storage65° C to +150° C                 |

| Under Bias10° C to +80° C               |

| All Inputs or Outputs with              |

| Respect to Ground+7V to -0.6V           |

| V <sub>PP</sub> During Programming with |

| Respect to Ground+22V to -0.6V          |

| Voltage on A <sub>9</sub> with          |

| Respect to Ground +15.5V to -0.6V       |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Recommended Operating Conditions (27XX = 2764 and 27128)[1]

|                                    | 27XX-20, 27XX-25<br>27XX-30, 27XX-45 | 27XX<br>27XX-2, 27XX-3, 27XX-4 |

|------------------------------------|--------------------------------------|--------------------------------|

| Vcc Supply Voltage[2]              | 5 V ± 10%                            | 5 V ± 5%                       |

| Temperature Range (Read Mode)      | 0 to 70° C                           | 0 to 70° C                     |

| V <sub>PP</sub> During Programming | 21 ± 0.5 V                           | 21 ± 0.5 V                     |

#### DC Operating Characteristics During Read or Programming

|                     |                            |            | Li   | Limits  |      |                                        |

|---------------------|----------------------------|------------|------|---------|------|----------------------------------------|

| Symbol              | Parameter                  |            | Min. | Max.    | Unit | Test Conditions                        |

| lin                 | Input Leakage C            | urrent     |      | 10      | μΑ   | VIN = VCC Max.                         |

| lo                  | Output Leakage             | Current    |      | 10      | μΑ   | Vout = Vcc Max.                        |

| [PP[2]              | Vpp Current                | Read Mode  |      | 5       | mA   | V <sub>PP</sub> = V <sub>CC</sub> Max. |

|                     | ł                          | Prog. Mode |      | 30      | mA   | V <sub>PP</sub> = 21.5V                |

| I <sub>CC1</sub>  2 | V <sub>CC</sub> Standby Cu | rrent      |      | 30      | mA   | CE = VIH                               |

| Icc2 <sup>[2]</sup> | Vcc Active Curre           | ent        |      | 100     | mA   | CE = OE = V <sub>IL</sub>              |

| VIL                 | Input Low Voltag           | je         | -0.1 | 0.8     | ٧    |                                        |

| ViH                 | Input High Voltag          | ge         | 2    | Vcc + 1 | V    |                                        |

| VoL                 | Output Low Volta           | age        |      | 0.45    | ٧    | I <sub>OL</sub> = 2.1 mA               |

| Voн                 | Output High Volt           | tage       | 2.4  |         | ٧    | I <sub>OH</sub> = -400 μA              |

- 1. The 5133 and 5143 have the same dash numbers and operate with the same operating conditions as the 2764 and 27128 respectively. The specifications are exactly the same.

- 2. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

## 2764 (5133) 27128 (5143)

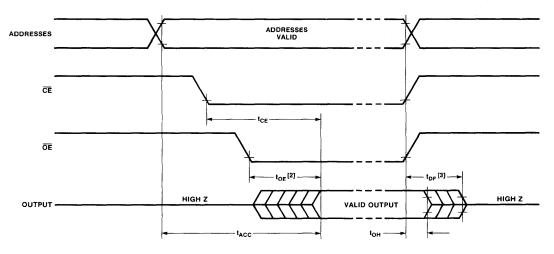

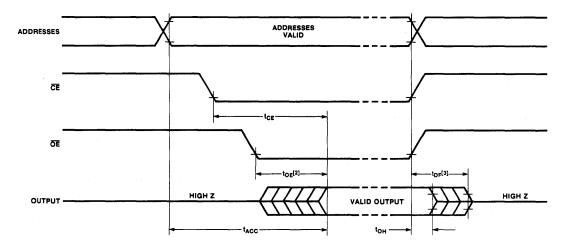

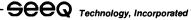

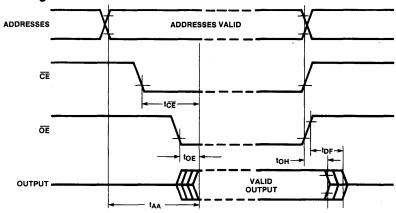

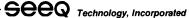

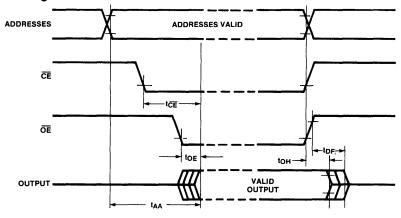

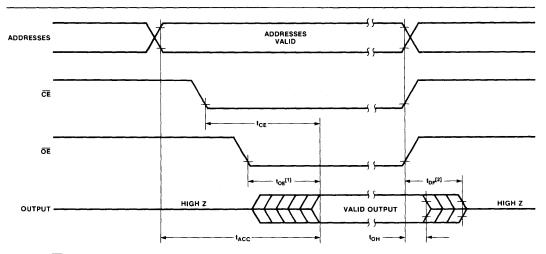

#### AC Operating Characteristics During Read

|                  |                                                                                             | Limits (nsec) |              |      |            |      |             |      |              |                      |

|------------------|---------------------------------------------------------------------------------------------|---------------|--------------|------|------------|------|-------------|------|--------------|----------------------|

|                  |                                                                                             |               | (X-2<br>X-20 |      | XX<br>X-25 |      | X-3<br>X-30 |      | (X-4<br>X-45 | Test                 |

| Symbol           | Parameter                                                                                   | Min.          | Max.         | Min. | Max.       | Min. | Max.        | Min. | Max.         | Conditions           |

| t <sub>ACC</sub> | Address to Data Valid                                                                       |               | 200          |      | 250        |      | 300         |      | 450          | CE = OE = VIL        |

| t <sub>CE</sub>  | Chip Enable to Data Valid                                                                   |               | 200          |      | 250        |      | 300         |      | 450          | OE = VIL             |

| toe              | Output Enable to Data<br>Valid                                                              |               | 75           |      | 100        |      | 120         |      | 150          | CE = VIL             |

| t <sub>DF</sub>  | Output Enable to Output Float                                                               | 0             | 60           | 0    | 60         | 0    | 105         | 0    | 130          | CE = V <sub>IL</sub> |

| t <sub>ОН</sub>  | Output Hold from Chip<br>Enable, Addresses, or<br>Output Enable whichever<br>occurred first | 0             |              | 0    |            | 0    |             | 0    |              | CE = OE = VIL        |

### Capacitance [1]

| Symbol | Parameter          | Тур. | Мах. | Unit | Conditions            |

|--------|--------------------|------|------|------|-----------------------|

| CIN    | Input Capacitance  | 4    | 6    | рF   | $V_{IN} = 0V$         |

| Соит   | Output Capacitance | 8    | 12   | pF   | V <sub>OUT</sub> = 0V |

#### A.C. Test Conditions

Output Load: 1 TTL gate and  $C_L = 100 pF$ Input Rise and Fall Times: ≤ 20ns Input Pulse Levels: 0.45V to 2.4V Timing Measurement Reference Level: Inputs 1V and 2V Outputs 0.8V and 2V

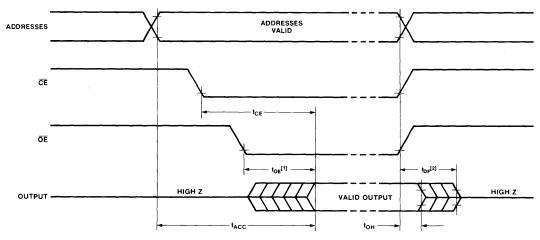

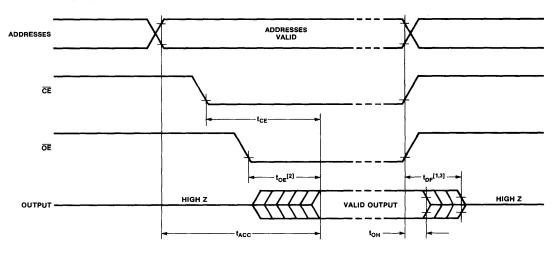

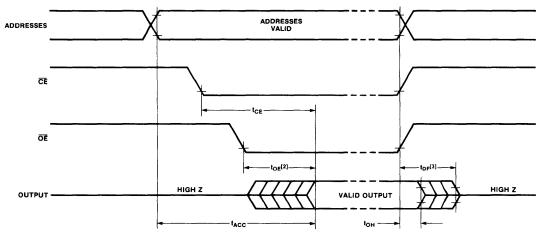

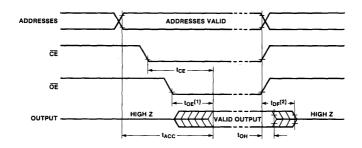

#### A.C. Waveforms

- NOTES:

1. THIS PARAMETER IS SAMPLED AND IS NOT 100% TESTED.

2. OE MAY BE DELAYED UP TO IACC toe AFTER THE FALLING EDGE OF CE WITHOUT IMPACT ON IACC.

3. top IS SPECIFIED FROM OE OR CE, WHICHEVER OCCURS FIRST.

#### Erasure Characteristics

The 64K and 128K EPROMs are erased using ultraviolet light which has a wavelength of 2537 Angstroms. The integrated dose, i.e., intensity x exposure time, for erasure is a minimum of 15 wattsecond/cm2. The EPROM should be placed within one inch of the lamp tube during erasure. Table 1 shows the typical EPROM erasure time for various light intensities.

Table 1. Typical EPROM Erasure Time

| Light Intensity<br>(Micro-Watts/cm²) | Erasure Time<br>(Minutes) |

|--------------------------------------|---------------------------|

| 15,000                               | 20                        |

| 10,000                               | 30                        |

| 5,000                                | 55                        |

#### Silicon Signature™

Incorporated in SEEQ's EPROMs is a row of mask programmed read only memory (ROM) cells which is outside of the normal-memory cell array. The ROM contains the EPROM's Silicon Signature. Silicon Signature contains data which identifies SEEQ as the manufacturer and gives the product code. This data allows programmers to match the programming specification against the product which is to be programmed. If there is verification, then the programmer can proceed programming.

Silicon Signature is activated by raising address A9 to 12V ± 0.5V, bringing chip enable and output enable to a TTL low, having V<sub>CC</sub> at 5V, and having all addresses except Ao at a TTL low. The Silicon Signature data is then accessed by toggling (using TTL) the column addresses A<sub>0</sub>. There are 2 bytes of data available (see Table 2). The data appears on outputs O<sub>0</sub> to O<sub>6</sub>, with O<sub>7</sub> used as an odd parity bit. This mode is functional at  $25 \pm 5^{\circ}$  C ambient temperature.

**Table 2. Silicon Signature Bytes**

|                       | A <sub>0</sub> | Hex Data |

|-----------------------|----------------|----------|

| SEEQ Code (Byte 0)    | VIL            | 94       |

| Product Code (Byte 1) |                |          |

| 2764                  | ViH            | 40       |

| 27128                 | ViH            | C1       |

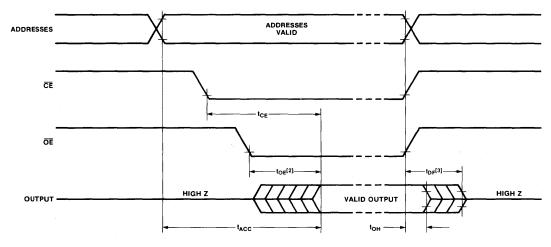

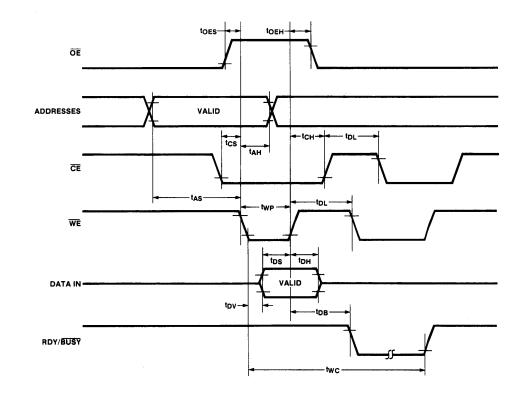

#### Programming

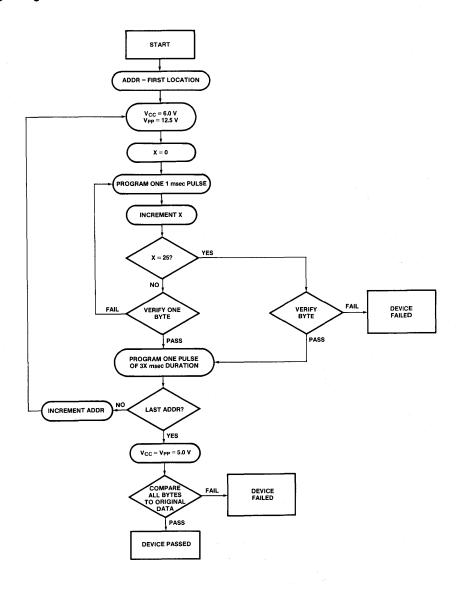

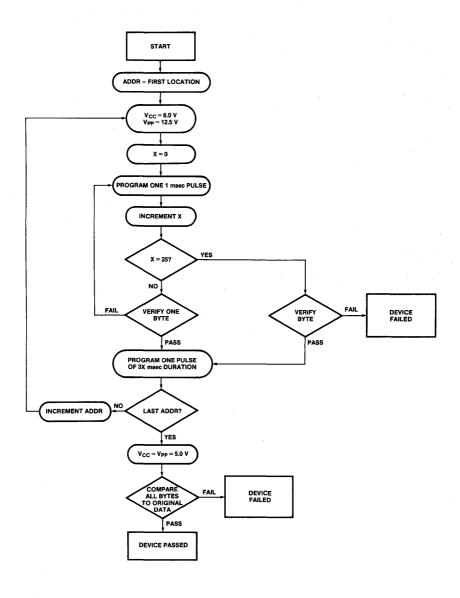

Both EPROMs may be programmed using an intelligent algorithm or with a conventional 50 msec programming pulse. The intelligent algorithm improves the total programming time by approximately 10 times over the conventional 50 msec algorithm. It typically requires only 1 and 2 minute programming time for all 64K and 128K bits respectively.

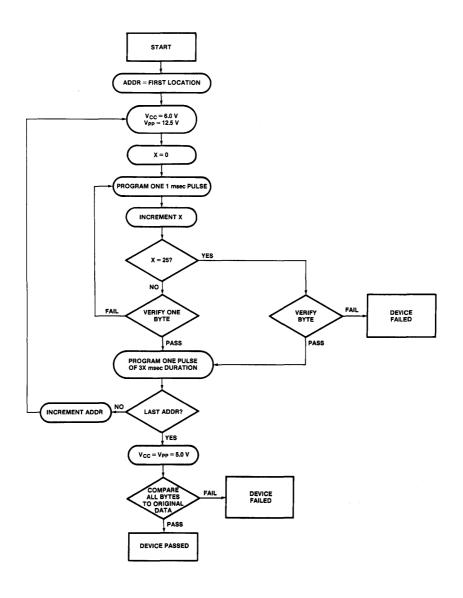

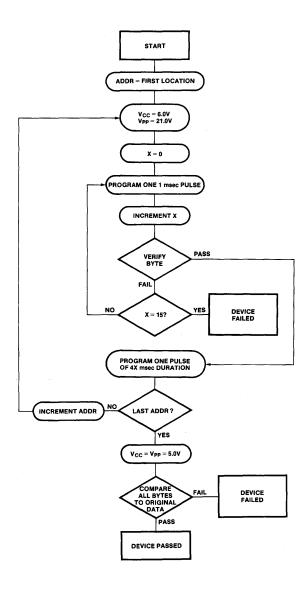

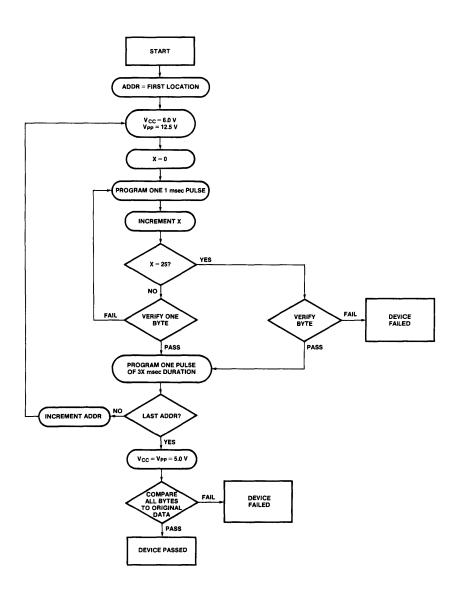

The intelligent algorithm requires  $V_{CC} = 6V$  and  $V_{PP}$ = 21V during byte programming. The initial program pulse width is one millisecond, followed by a sequence of one millisecond pulses. A byte is verified after each pulse. A single program pulse, with a time duration equal to 4 times the number of one millisecond pulses applied, is additional given to the address after it is verified as being correctly programmed. A maximum of 15 one millisecond pulses per byte should be applied to each address. When the intelligent algorithm cycle has been completed, all bytes must be read at  $V_{CC} = V_{PP} = 5V$ .

#### Intelligent Algorithm Flowchart

# 2764 (5133) 27128 (5143)

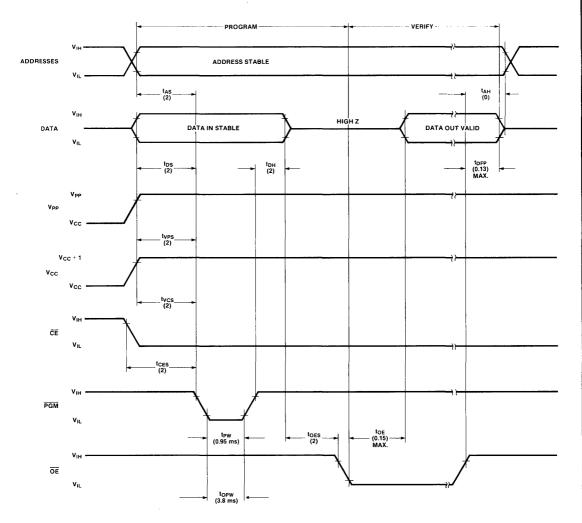

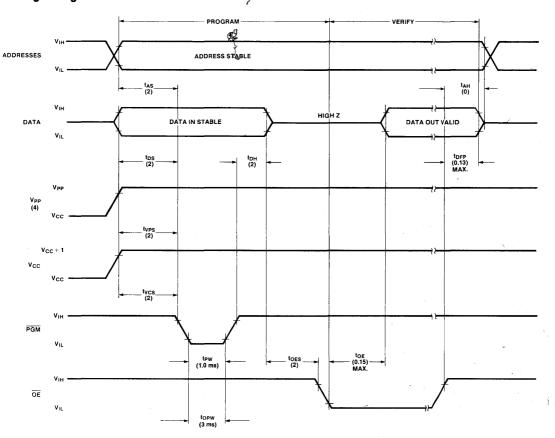

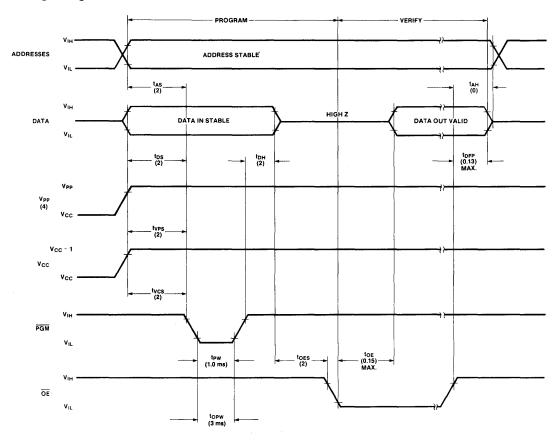

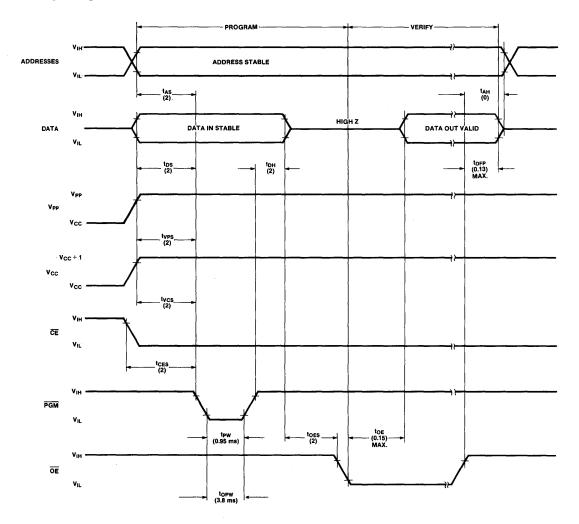

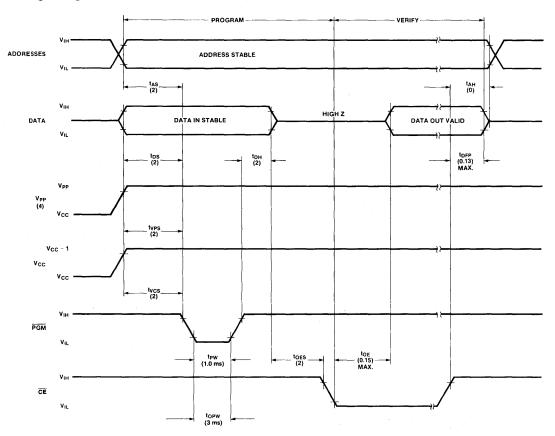

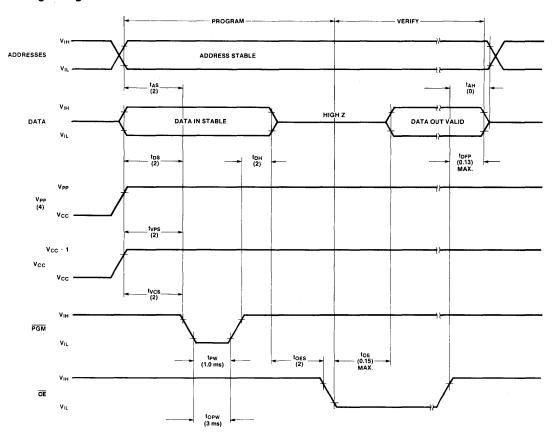

#### Intelligent Algorithm

- NO 165:

1. ALL TIMES SHOWN IN ( ) ARE MINIMUM AND IN "SEC UNLESS OTHERWISE SPECIFIED.

2. THE INPUT TIMING REFERENCE LEVEL IS .8V FOR A V<sub>II</sub>. AND 2V FOR A V<sub>II</sub>.

3. t<sub>OE</sub> AND t<sub>DFP</sub> ARE CHARACTERISTICS OF THE DEVICE BUT MUST BE ACCOMMODATED BY THE PROGRAMMER.

## 2764 (5133) 27128 (5143)

#### Intelligent Algorithm

AC Programming Characteristics [4]  $T_A = 25 \pm 5^{\circ}$  C,  $V_{CC}$ [1] = 6.0 V  $\pm$  0.25 V,  $V_{PP}$  = 21 V  $\pm$  0.5 V

|                     | Parameter                           |      | Limits |      | Unit |

|---------------------|-------------------------------------|------|--------|------|------|

| Symbol              |                                     | Min. | Тур.   | Max. |      |

| tas                 | Address Setup Time                  | 2    |        |      | μs   |

| toes                | OE Setup Time                       | 2    |        |      | μS   |

| tps                 | Data Setup Time                     | 2    |        |      | μS   |

| tah                 | Address Hold Time                   | 0    |        |      | μS   |

| tDH                 | Data Hold Time                      | 2    |        |      | μs   |

| tDFP                | Output Enable to Output Float Delay | 0    |        | 130  | ns   |

| tvps                | V <sub>PP</sub> Setup Time          | 2    |        |      | μS   |

| tvcs                | Vcc Setup Time                      | 2    |        |      | μs   |

| t <sub>PW</sub> [2] | PGM Initial Program Pulse Width     | 0.95 | 1.0    | 1.05 | ms   |

| topw[3]             | PGM Overprogram Pulse Width         | 3.8  |        | 63   | ms   |

| tces                | CE Setup Time                       | 2    |        |      | μs   |

| toE                 | Data Valid from OE                  |      |        | 150  | ns   |

#### NOTES:

- 1. Vcc must be applied simultaneously or before Vpp and removed simultaneously or after VPP.

- 2. Initial Program Pulse width tolerance is 1 msec ± 5%.

- 3. The length of the overprogram pulse will vary from 3.8 msec to 63 msec as a function of the iteration counter value X.

- 4. For 50 ms programming,  $V_{CC}$  = 5 V  $\pm$  5%,  $T_{PW}$  = 50 ms ± 10%, and Topw is not applicable.

#### \*AC Test Conditions

| Input Rise and Fall Times (10% to 90%) | 20 ns         |

|----------------------------------------|---------------|

| Input Pulse Levels                     | 0.45V to 2.4V |

| Input Timing Reference Level           | 0.8V and 2.0V |

| Output Timing Reference Level          | 0.8V and 2.0V |

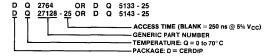

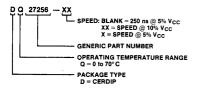

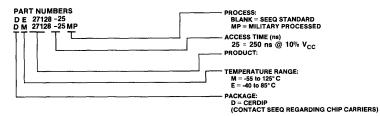

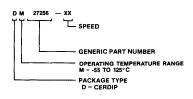

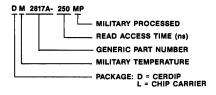

#### Ordering Information

SEEQ's 64K EPROM may be ordered using either the generic product number 2764 or 5133. The package is dual marked with both product numbers. The die, masks, processing, testing, and data sheet specifications are the same. The 5133 is SEEQ's original part number for the 2764 64K EPROM. The same is also true for the 5143 (i.e. 27128) 128K EPROM.

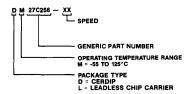

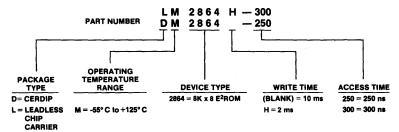

#### PART NUMBER

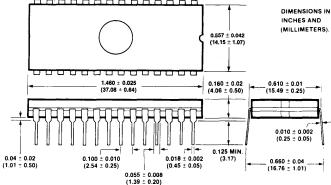

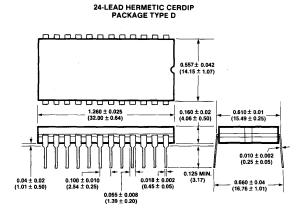

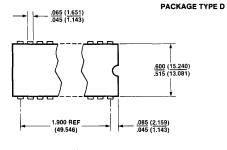

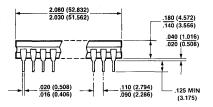

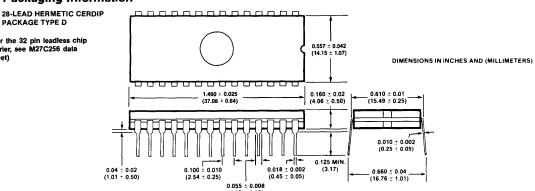

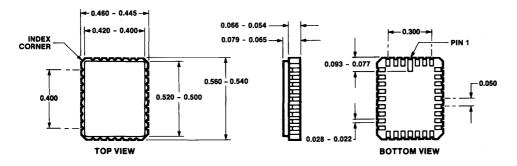

#### Package Diagram

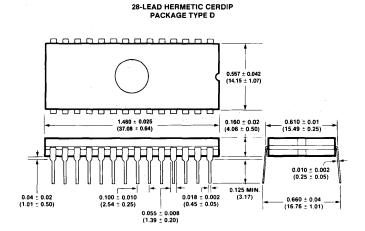

## 28-LEAD HERMETIC CERDIP PACKAGE TYPE D

SEEQ Technology, Incorporated

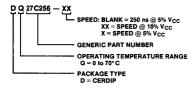

## 27C256 256K CMOS EPROM

August 1985

#### **Features**

- **256K (32K x 8) CMOS EPROM**

- Ultra Low Power

- 100 μA Max. V<sub>CC</sub> Standby Current

- 40 mA Max. Active Current

- Programmed Using Intelligent Algorithm - 12.5 Vpp

- 250 ns Access Times

- 5 V ±10% V<sub>CC</sub>

- 0 to 70° C Temperature Range

- JEDEC Approved Bytewide Pin Configuration

- Silicon Signature™

#### Description

SEEQ's 27C256 is the industry's first 256K CMOS EPROM. It has a 32K x 8 organization and has very low power dissipation. Its 40 mA active current is less than one half the active power of n-channel EPROMs. In addition the 100 μA V<sub>CC</sub> standby current is orders of magnitude lower than those same EPROMs. Consequently, system memory sizes can be substantially increased at a very small increase in power. Low active and standby power is important in applications which require portability, low cooling cost, high memory bit density, and long term reliability.

The 27C256 is specified over the 0 to 70°C temperature range and at 5 V  $\pm$  10% V<sub>CC</sub>. The access time is specified at 250 ns, making the 27C256 compatible with most of today's microcomputers. Its inputs and outputs are completely TTL compatible.

#### **Block Diagram**

#### **Mode Selection**

| PINS<br>MODE        | CE<br>(20) | OE<br>(22) | V <sub>PP</sub> (1) | V <sub>CC</sub> (28) | Outputs<br>(11-13, 15-19) |

|---------------------|------------|------------|---------------------|----------------------|---------------------------|

| Read                | VIL        | VIL        | Vcc                 | Vcc                  | Dout                      |

| Output Disable      | Х          | ViH        | Vcc                 | Vcc                  | High Z                    |

| Standby             | ViH        | Х          | Vcc                 | Vcc                  | High Z                    |

| Program             | VIL        | ViH        | VPP                 | Vcc                  | Din                       |

| Program Verify      | ViH .      | VIL        | VPP                 | Vcc                  | Dout                      |

| Program Inhibit     | ViH        | ViH        | VPP                 | Vcc                  | High Z                    |

| Silicon Signature™* | VIL        | VIL        | Vcc                 | Vcc                  | Encoded<br>Data           |

X can be either VIL or VIH.

#### Pin Configuration

|                | 27C256 |      |                 |

|----------------|--------|------|-----------------|

| VPP            | 1      | 28   | Vcc             |

| A12            | 2      | 27 5 | A <sub>14</sub> |

| A7 🗍           | 3      | 26   | A <sub>13</sub> |

| A6 🗖           | 4      | 25 🗖 | A <sub>8</sub>  |

| A <sub>5</sub> | 5      | 24   | A <sub>9</sub>  |

| A₄₫            | 6      | 23   | A <sub>11</sub> |

| A <sub>3</sub> | 7      | 22 🗖 | DE              |

| A2 🗖           | 8      | 21   | A <sub>10</sub> |

| A1             | 9      | 20 🗖 | CE              |

| A0 🗖           | 10     | 19 🗖 | ٥,              |

| ٥٠◘            | 11     | 18 🗖 | <b>D</b> 6      |

| 01             | 12     | 17   | <b>5</b>        |

| 02             | 13     | 16   | ٥4              |

| GND            | 14     | 15   | <b>o</b> 3      |

| _              |        |      |                 |

#### Pin Names

| A <sub>0</sub> - A <sub>5</sub>  | ADDRESSES — COLUMN (LSB) |

|----------------------------------|--------------------------|

| A <sub>6</sub> - A <sub>14</sub> | ADDRESSES ROW            |

| ĈĒ                               | CHIP ENABLE              |

| ŌE                               | OUTPUT ENABLE            |

| O <sub>0</sub> - O <sub>7</sub>  | OUTPUTS                  |

<sup>\*</sup>For Silicon Signature™: A₀ is toggled, A₂ = 12 V, and all other addresses are at a TTL low. Silicon Signature™ is a registered trademark of SEEQ Technology.

Initially, and after erasure, all bits are in the "1" state. An intelligent algorithm is used to program the 27C256 typically in four minutes. Data is programmed using a 12.5 V VPP and an initial chip enable pulse of 1.0 ms.

Incorporated on the 27C256 is Silicon Signature™. Silicon Signature contains encoded data which identifies SEEQ as the EPROM manufacturer and gives the product code. This data is encoded in ROM to prevent erasure by ultraviolet light.

#### **Absolute Maximum Ratings**

| Temperature                            |                   |

|----------------------------------------|-------------------|

| Storage                                | -65° C to +150° C |

| Under Bias                             | −10° C to +80° C  |

| All Inputs or Outputs with             |                   |

| Respect to Ground                      | +7 V to -0.6 V    |

| V <sub>PP</sub> with Respect to Ground | +14.0 V to -0.6 V |

| Voltage on A <sub>9</sub> with         |                   |

| Respect to Ground                      | +14.0 V to -0.6 V |

|                                        |                   |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

|                                | 27C256-25, 27C256-30, 27C256-45 | 27C256, 27C256-3, 27C256-4 |

|--------------------------------|---------------------------------|----------------------------|

| Vcc Supply Voltage[1]          | 5 V ± 10%                       | 5 V ± 5%                   |

| Temperature Range (Read Mode)  | 0 to 70° C                      | 0 to 70° C                 |

| VPP During Read <sup>[2]</sup> | Vcc                             | Vcc                        |

| VPP During Programming[3]      | 12.5 ± 0.3 V                    | 12.5 ± 0.3 V               |

#### DC Operating Characteristics During Read or Programming

|                  |                           |            | Li   | mits    |      |                                                              |

|------------------|---------------------------|------------|------|---------|------|--------------------------------------------------------------|

| Symbol Parameter | Symbol                    |            | Min. | Max.    | Unit | Test Conditions                                              |

| lin              | Input Leakage             | Current    |      | 10      | μΑ   | VIN = VCC Max.                                               |

| lo               | Output Leakag             | e Current  |      | 10      | μΑ   | Vout = Vcc Max.                                              |

| Ірр              | Vpp Current               | Read Mode  |      | 100     | μΑ   | V <sub>PP</sub> = V <sub>CC</sub> Max.                       |

|                  |                           | Prog. Mode |      | 30      | mA   | V <sub>PP</sub> = 12.5 V                                     |

| Icc1             | V <sub>CC</sub> Standby C | Current    | •    | 100     | μΑ   | CE ≥ V <sub>CC</sub> -1 V                                    |

| ICC2             | V <sub>CC</sub> Standby C | Current    |      | 1       | mA   | CE ≥ ViH                                                     |

| Іссз             | Vcc Active Cui            | rrent      |      | 40      | mA   | CE = OE = V <sub>IL</sub> ,<br>f = 5 MHz, I <sub>O</sub> = 0 |

| V <sub>IL</sub>  | Input Low Volt            | age        | -0.1 | 0.8     | ٧    |                                                              |

| ViH              | Input High Voll           | tage       | 2    | Vcc + 1 | ٧    |                                                              |

| VoL              | Output Low Vo             | oltage     |      | 0.45    | V    | I <sub>OL</sub> = 2.1 mA                                     |

| Voн              | Output High Vo            | oltage     | 2.4  |         | V    | I <sub>OH</sub> = -400 μA                                    |

#### NOTES:

- 1. Vcc must be applied simultaneously or before VPP and removed simultaneously or after VPP.

- 2. VPP cannot be left floating and should be connected to Vcc during read.

- 3. 0.1 µF ceramic capacitor on Vpp is required during programming only to suppress voltage transients.

#### AC Operating Characteristics During Read

|                  | Limits (nsec)                                                                            |                     |      |      |      |                       |            |                           |  |      |

|------------------|------------------------------------------------------------------------------------------|---------------------|------|------|------|-----------------------|------------|---------------------------|--|------|

|                  |                                                                                          | 27C256<br>27C256-25 |      |      |      | 27C256-3<br>27C256-30 |            | 27C256-4<br>27C256-45     |  | Test |

| Symbol Parameter | Min.                                                                                     | Max.                | Min. | Max. | Min. | Max.                  | Conditions |                           |  |      |

| TACC             | Address to Data Valid                                                                    |                     | 250  |      | 300  |                       | 450        | CE = OE = VIL             |  |      |

| T <sub>CE</sub>  | Chip Enable to Data Valid                                                                |                     | 250  |      | 300  |                       | 450        | ŌĒ = VIL                  |  |      |

| TOE              | Output Enable to Data Valid                                                              |                     | 100  |      | 120  |                       | 150        | CE = V <sub>IL</sub>      |  |      |

| T <sub>DF</sub>  | Output Enable or Chip Enable to Output Float <sup>[3]</sup>                              | 0                   | 60   | 0    | 105  | 0                     | 130        | CE = V <sub>IL</sub>      |  |      |

| Тон              | Output Hold from Chip Enable,<br>Addresses, or Output Enable<br>whichever occurred first | 0                   |      | 0    |      | 0                     |            | CE = OE = V <sub>IL</sub> |  |      |

### Capacitance |1|

| Symbol | Parameter          | Тур. | Max. | Unit | Conditions           |

|--------|--------------------|------|------|------|----------------------|

| Cin    | Input Capacitance  | 4    | 6    | pF   | V <sub>IN</sub> = 0V |

| Соит   | Output Capacitance | 8    | 12   | pF   | Vout = 0V            |

#### A.C. Test Conditions

Output Load: 1 TTL gate and  $C_L = 100 pF$ Input Rise and Fall Times: ≤ 20ns Input Pulse Levels: 0.45V to 2.4V Timing Measurement Reference Level: Inputs 1V and 2V Outputs 0.8V and 2V

#### A.C. Waveforms

NOTES: 1. THIS PARAMETER IS SAMPLED AND IS NOT 100% TESTED. 2.  $\overline{\text{CE}}$  MAY BE DELAYED TO  $1_{\text{ACC}} \rightarrow 1_{\text{DE}}$  AFTER THE FALLING EDGE OF  $\overline{\text{CE}}$  WITHOUT IMPACT ON  $1_{\text{ACC}}$ . 3.  $1_{\text{DF}}$  IS SPECIFIED FROM  $\overline{\text{OE}}$  OR  $\overline{\text{CE}}$ , WHICHEVER OCCURS FIRST.

#### Erasure Characteristics

The 27C256 is erased using ultraviolet light which has a wavelength of 2537 Angstroms. The integrated dose, i.e., intensity x exposure time, for erasure is a minimum of 15 watt-second/cm2. The EPROM should be placed within one inch of the lamp tube during erasure. Table 1 shows the typical EPROM erasure time for various light intensities.

Table 1, Typical EPROM Erasure Time

| Light Intensity<br>(Micro-Watts/cm²) | Erasure Time<br>(Minutes) |

|--------------------------------------|---------------------------|

| 15,000                               | 20                        |

| 10,000                               | 30                        |

| 5,000                                | 55                        |

#### Silicon Signature™

Incorporated in SEEQ's EPROMs is a row of mask programmed read only memory (ROM) cells which is outside of the normal memory cell array. The ROM contains the EPROM's Silicon Signature. Silicon Signature contains data which identifies SEEQ as the manufacturer and gives the product code. This data allows programmers to match the programming specification against the product which is to be programmed. If there is verification, then the programmer proceeds to program.

Silicon Signature is activated by raising address Ag to

$12V \pm 0.5V$ , bringing chip enable and output enable to a TTL low, having V<sub>CC</sub> at 5V, and having all addresses except Ao at a TTL low. The Silicon Signature data is then accessed by toggling A<sub>0</sub>. The data appears on outputs Oo to O6, with O7 used as an odd parity bit (see Table 2).

**Table 2. Silicon Signature Bytes**

|                       | A <sub>0</sub> | Data (Hex) |

|-----------------------|----------------|------------|

| SEEQ Code (Byte 0)    | VIL            | 94         |

| Product Code (Byte 1) | ViH            | C2         |

#### Programming

The 27C256 is programmed using the industry standard intelligent algorithm.

The intelligent algorithm requires  $V_{CC} = 6 V$  and  $V_{PP} =$ 12.5 V during byte programming. The initial program pulse width is 1.0 millisecond, followed by a sequence of 1.0 millisecond pulses. A byte is verified after each pulse. A single program pulse, with a time duration equal to 3 times the number of 1.0 millisecond pulses applied, is additionally given to the address after it is verified as being correctly programmed. A minimum of one to a maximum of 25 1-ms pulses, plus one 3X overpulse, may be applied to each byte. When the intelligent algorithm cycle has been completed, all bytes must be read at  $V_{CC} = V_{PP} = 5 V$ .

#### Intelligent Algorithm Flowchart

#### Intelligent Algorithm

- 1. ALL TIMES SHOWN IN ( ) ARE MINIMUM AND IN #SEC UNLESS OTHERWISE SPECIFIED.

2. THE INPUT TIMING REFERENCE LEVEL IS 0.8 V FOR A VIL AND 2 V FOR A VIH.

3. TOE AND TO JOPP ARE CHARACTERISTICS OF THE DEVICE BUT MUST BE ACCOMMODATED BY THE PROGRAMMER.

4. 0.1 #F CERAMIC CAPACITOR ON VPP IS REQUIRED DURING PROGRAMMING ONLY TO SUPPRESS VOLTAGE TRANSIENTS.

#### Intelligent Algorithm

#### AC Programming Characteristics $T_A = 25 \pm 5^{\circ}C$ , $V_{CC}[1] = 6.0V \pm 0.25V$ , $V_{PP} = 12.5V$

| Symbol              | Parameter                           | Min. | Тур. | Max.  | Unit |

|---------------------|-------------------------------------|------|------|-------|------|

| tas                 | Address Setup Time                  | 2    |      |       | μS   |

| toes                | OE Setup Time                       | 2    |      |       | μS   |

| tos                 | Data Setup Time                     | 2    |      |       | μs   |

| tah                 | Address Hold Time                   | 0    |      |       | μs   |

| t <sub>DH</sub>     | Data Hold Time                      | 2    |      |       | μS   |

| tDFP                | Output Enable to Output Float Delay | 0    |      | 130   | ns   |

| tvps                | Vpp Setup Time                      | 2    |      |       | μS   |

| tvcs                | Vcc Setup Time                      | 2    |      |       | μS   |

| tpw                 | CE Initial Program Pulse Width      | 0.95 | 1.0  | 1.05  | ms   |

| topw <sup>[2]</sup> | CE Overprogram Pulse Width          | 2.85 |      | 78.75 | ms   |

| toe                 | Data Valid from OE                  |      |      | 150   | ns   |

#### \*AC Conditions of Test

| Input Rise and Fall Times (10% to 90%) 2 | 20 ns |

|------------------------------------------|-------|

| Input Pulse Levels 0.45 V to             | 2.4 V |

| Input Timing Reference Level 0.8 V and   | 2.0 V |

| Output Timing Reference Level 0.8 V and  | 2.0 V |

#### NOTES:

- 1. VCC must be applied simultaneously or before Vpp and removed simultaneously or after Vpp.

- 2. The length of the overprogram pulse will vary from 2.85 msec to 78.75 msec as a function of the iteration counter value X.

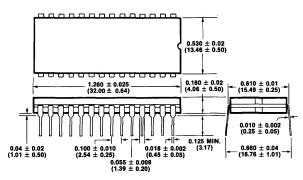

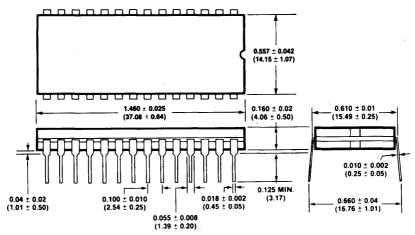

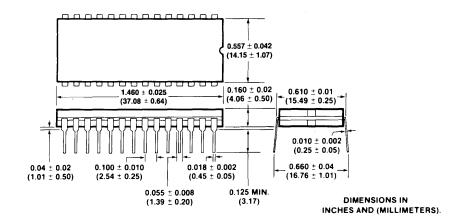

#### Ordering and Package Information

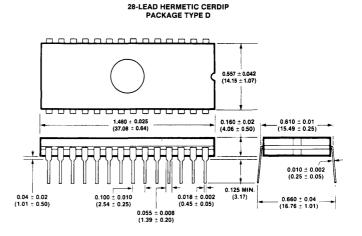

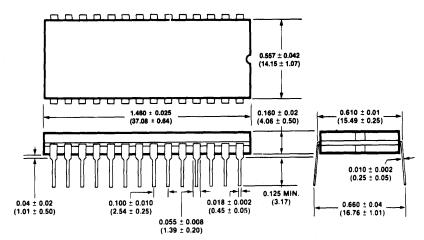

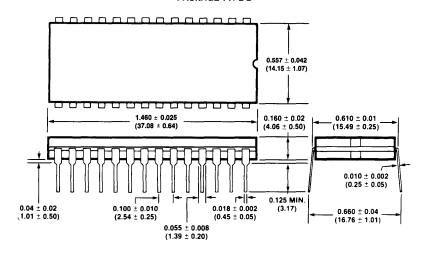

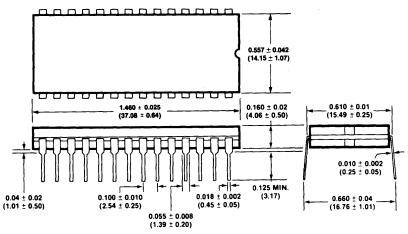

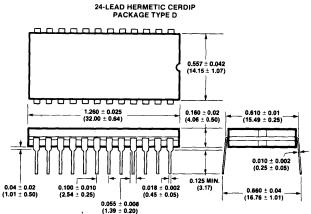

## PACKAGE TYPE D 0.557 ± 0.042 (14.15 ± 1.07) 0.160 ± 0.02 (4.06 ± 0.50) 0.610 ± 0.01 (15.49 ± 0.25) 0.010 ± 0.002 (0.25 ± 0.05) 0.125 MIN (3.17) 0.100 ± 0.010 (2.54 ± 0.25) 0.018 ± 0.002 0.04 ± 0.02 (1.01 ± 0.50) 0.660 ± 0.04 (16.76 ± 1.01) $(0.45 \pm 0.05)$ 0.055 ± 0.008 (1.39 ± 0.20)

28-LEAD HERMETIC CERDIP

DIMENSIONS IN INCHES AND (MILLIMETERS).

## 27256 256K EPROM

August 1985

#### Features

- 256K (32K x 8) EPROM

- 250 ns Access Times

- 5 V ±10% VCC

- 0 to 70° C Temperature Range

- Low Power

- 40 mA Max. V<sub>CC</sub> Standby Current

70 mA Max. Active Current

- Programmed Using Intelligent Algorithm - 12.5 Vpp

- JEDEC Approved Bytewide Pin Configuration

- Silicon Signature™

#### Description

SEEQ's 27256 is a 256K ultraviolet light erasable EPROM. It is organized as 32K x 8, operates from a single 5V supply, and programs using a 12.5V intelligent algorithm. The 27256's operating conditions are specified over the 0 to 70 mA temperature range and at 5V±10% V<sub>CC</sub>. The active power is only 70 mA, approximately 30% lower than NMOS 256K EPROMs. Consequently, memory system sizes can be increased with a substantial savings in power, resulting in lower power supply cost and inherently greater system reliability. For systems requiring even lower power, a 40 mA active and 100 µA standby power CMOS 27C256 is available from SEEO. The 27256's low active power is achieved without sacrificing performance. The access time is 200 nsec. making it compatible with most of today's microcomputers. Wait states can be eliminated with the 200 nsec access times.

### **Block Diagram**

#### **Mode Selection**

| PINS<br>MODE        | CE<br>(20) | OE<br>(22)      | V <sub>PP</sub> (1) | V <sub>CC</sub><br>(28) | Outputs<br>(11-13, 15-19) |

|---------------------|------------|-----------------|---------------------|-------------------------|---------------------------|

| Read                | VIL        | VIL             | Vcc                 | Vcc                     | Dout                      |

| Output Disable      | Х          | ViH             | Vcc                 | Vcc                     | High Z                    |

| Standby             | ViH        | Х               | Vcc                 | Vcc                     | High Z                    |

| Program             | VIL        | ViH             | Vpp                 | Vcc                     | Din                       |

| Program Verify      | ViH        | VIL             | VPP                 | Vcc                     | Dout                      |

| Program Inhibit     | ViH        | V <sub>IH</sub> | VPP                 | Vcc                     | High Z                    |

| Silicon Signature™* | VIL        | VIL             | Vcc                 | Vcc                     | Encoded<br>Data           |

X can be either VIL or VIH.

#### Pin Configuration

| V <sub>PP</sub> | 1  | 28 V <sub>CC</sub>    |

|-----------------|----|-----------------------|

| A12             | 2  | 27 A14                |

| A7 🗍            | 3  | 26 A <sub>13</sub>    |

| A6 [            | 4  | 25 🗖 A <sub>8</sub>   |

| A <sub>5</sub>  | 5  | 24 🗖 A <sub>9</sub>   |

| A4[             | 6  | 23 🗖 A <sub>1</sub> , |

| A <sub>3</sub>  | 7  | 22 OE                 |

| A <sub>2</sub>  | 8  | 21 A 10               |

| A1 🗍            | 9  | 20 🗖 CE               |

| A <sub>0</sub>  | 10 | 19 07                 |

| 0₀□             | 11 | 18 06                 |

| 01              | 12 | 17 O <sub>5</sub>     |

| 0₂ 🗖            | 13 | 16 🗖 0₄               |

| GND             | 14 | 15 O <sub>3</sub>     |

|                 |    |                       |

#### Pin Names

| A <sub>0</sub> - A <sub>5</sub>  | ADDRESSES — COLUMN (LSB) |

|----------------------------------|--------------------------|

| A <sub>6</sub> - A <sub>14</sub> | ADDRESSES — ROW          |

| CE                               | CHIP ENABLE              |

| ŌĒ                               | OUTPUT ENABLE            |

| O <sub>0</sub> - O <sub>7</sub>  | OUTPUTS                  |

<sup>\*</sup>For Silicon Signature™: A₀ is toggled, A₀ = 12 V, and all other addresses are at a TTL low. Silicon Signature™ is a registered trademark of SEEQ Technology.

An intelligent algorithm is used to program the 27256. Data is programmed using a 12.5V VPP and an initial chip enable pulse of 1 msec. Initially, and after erasure, all bits are in the "1" state. The typically programming time is under five minutes. Programming is available from commercial programmers and is compatible with other 256K EPROM intelligent algorithms.

Incorporated on the 27256 is Silicon Signature™. Silicon Signature contains encoded data which identifies SEEQ as the EPROM manufacturer and gives the product code. The product code is used by a programmer to identify the programming algorithm for the 27256.

#### Absolute Maximum Ratings

| Temperature                                              |

|----------------------------------------------------------|

| Storage65° C to +150° C                                  |

| Under Bias10° C to +80° C                                |

| All Inputs or Outputs with                               |

| Respect to Ground +7 V to -0.6 V                         |

| V <sub>PP</sub> with Respect to Ground +14.0 V to −0.6 V |

| Voltage on A <sub>9</sub> with                           |

| Respect to Ground +14.0 V to -0.6 V                      |

|                                                          |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

|                                                   | 27256-20, 27256-25, 27256-30 | 27256, 27256-2, 27256-3 |

|---------------------------------------------------|------------------------------|-------------------------|

| V <sub>CC</sub> Supply Voltage <sup>[1]</sup>     | 5 V ± 10%                    | 5 V ± 5%                |

| Temperature Range (Read Mode)                     | 0 to 70° C                   | 0 to 70° C              |

| V <sub>PP</sub> During Read <sup>[2]</sup>        | Vcc                          | Vcc                     |

| V <sub>PP</sub> During Programming <sup>[3]</sup> | 12.5 ± 0.3 V                 | 12.5 ± 0.3 V            |

#### DC Operating Characteristics During Read or Programming

| Symbol           |                         |            | Li   | mits    |      |                                        |  |

|------------------|-------------------------|------------|------|---------|------|----------------------------------------|--|

|                  | Parameter               |            | Min. | Max.    | Unit | Test Conditions                        |  |

| lin              | Input Leakage           | Current    |      | 10      | μА   | V <sub>IN</sub> = V <sub>CC</sub> Max. |  |

| lo               | Output Leaka            | ge Current |      | 10      | μΑ   | Vout = Vcc Max                         |  |

| Ірр              | Vpp Current             | Read Mode  |      | 100     | μА   | VPP = VCC Max.                         |  |

|                  |                         | Prog. Mode |      | 30      | mA   | V <sub>PP</sub> = 12.5 V               |  |

| I <sub>CO1</sub> | V <sub>CC</sub> Standby | Current    |      | 40      | mA   | CE ≥ VIH                               |  |

| I <sub>CC2</sub> | Vcc Active Cu           | irrent     |      | 70      | mA   | CE = OE = VIL,                         |  |

| VIL              | Input Low Vol           | tage       | -0.1 | 0.8     | V    |                                        |  |

| ViH              | Input High Vo           | Itage      | 2    | Vcc + 1 | ٧    |                                        |  |

| VoL              | Output Low V            | oltage     |      | 0.45    | ٧    | I <sub>OL</sub> = 2.1 mA               |  |

| Vон              | Output High V           | /oltage    | 2.4  |         | V    | I <sub>OH</sub> = -400 μA              |  |

#### NOTES:

- 1. Vcc must be applied simultaneously or before VPP and removed simultaneously or after VPP.

- 2. Vpp cannot be left floating and should be connected to Vcc during read.

- 3. 0.1 µF ceramic capacitor on Vpp is required during programming only to suppress voltage transients.

#### **AC Operating Characteristics During Read**

|                  |                                                                                          | Limits (nsec) |      |      |      |      |      |                           |

|------------------|------------------------------------------------------------------------------------------|---------------|------|------|------|------|------|---------------------------|

|                  | 27C256 27256<br>27256-20 27256-2                                                         |               |      |      |      | Test |      |                           |

| Symbol           | Parameter                                                                                | Min.          | Max. | Min. | Max. | Min. | Max. | Conditions                |

| T <sub>ACC</sub> | Address to Data Valid                                                                    |               | 250  |      | 300  |      | 450  | CE = OE = V <sub>IL</sub> |

| T <sub>CE</sub>  | Chip Enable to Data Valid                                                                |               | 250  |      | 300  |      | 450  | ŌĒ = VIL                  |

| T <sub>OE</sub>  | Output Enable to Data Valid                                                              |               | 100  |      | 120  |      | 150  | CE = VIL                  |

| T <sub>DF</sub>  | Output Enable or Chip Enable to Output Float <sup>[3]</sup>                              | 0             | 60   | 0    | 105  | 0    | 130  | CE = VIL                  |

| Тон              | Output Hold from Chip Enable,<br>Addresses, or Output Enable<br>whichever occurred first | 0             |      | 0    |      | 0    |      | CE = OE = VIL             |

#### Capacitance [1]

| Symbol | Parameter          | Тур. | Max. | Unit | Conditions            |

|--------|--------------------|------|------|------|-----------------------|

| CIN    | Input Capacitance  | 4    | 6    | pF   | $V_{IN} = 0V$         |

| Соит   | Output Capacitance | 8    | 12   | pF   | V <sub>OUT</sub> = 0V |

#### A.C. Test Conditions

Output Load: 1 TTL gate and  $C_L = 100 pF$ Input Rise and Fall Times: ≤ 20ns Input Pulse Levels: 0.45V to 2.4V Timing Measurement Reference Level: Inputs 1V and 2V Outputs 0.8V and 2V

#### A.C. Waveforms

NOTES: 1. THIS PARAMETER IS SAMPLED AND IS NOT 100% TESTED. 2.  $C\bar{C}E$  WITHOUT IMPACT ON  $t_{ACC}$ . 2.  $C\bar{C}E$  MAY BE DELAYED TO  $t_{ACC} - t_{OE}$  AFTER THE FALLING EDGE OF  $C\bar{C}E$  WITHOUT IMPACT ON  $t_{ACC}$ . 3.  $t_{OF}$  IS SPECIFIED FROM  $O\bar{C}E$  OR  $C\bar{C}E$ , WHICHEVER OCCURS FIRST.

#### Erasure Characteristics

The 27256 is erased using ultraviolet light which has a wavelength of 2537 Angstroms. The integrated dose, i.e., intensity x exposure time, for erasure is a minimum of 15 watt-second/cm2. The EPROM should be placed within one inch of the lamp tube during erasure. Table 1 shows the typical EPROM erasure time for various light intensities.

Table 1. Typical EPROM Erasure Time

| Light Intensity<br>(Micro-Watts/cm <sup>2</sup> ) | Erasure Time<br>(Minutes) |

|---------------------------------------------------|---------------------------|

| 15,000                                            | 20                        |

| 10,000                                            | 30                        |

| 5,000                                             | 55                        |

#### Silicon Signature™

Incorporated in SEEQ's EPROMs is a row of mask programmed read only memory (ROM) cells which is outside of the normal memory cell array. The ROM contains the EPROM's Silicon Signature. Silicon Signature contains data which identifies SEEQ as the manufacturer and gives the product code. This data allows programmers to match the programming specification against the product which is to be programmed. If there is verification, then the programmer proceeds to program.

Silicon Signature is activated by raising address A<sub>9</sub> to

$12V \pm 0.5V$ , bringing chip enable and output enable to a TTL low, having V<sub>CC</sub> at 5V, and having all addresses except Ao at a TTL low. The Silicon Signature data is then accessed by toggling A<sub>0</sub>. The data appears on outputs Oo to O6, with O7 used as an odd parity bit (see Table 2).

**Table 2. Silicon Signature Bytes**

|                       | A <sub>0</sub> | Data (Hex) |

|-----------------------|----------------|------------|

| SEEQ Code (Byte 0)    | VIL            | 94         |

| Product Code (Byte 1) | ViH            | C2         |

#### **Programming**

The 27256 is programmed using the industry standard intelligent algorithm.

The intelligent algorithm requires  $V_{CC} = 6 \text{ V}$  and  $V_{PP} =$ 12.5 V during byte programming. The initial program pulse width is 1.0 millisecond, followed by a sequence of 1.0 millisecond pulses. A byte is verified after each pulse. A single program pulse, with a time duration equal to 3 times the number of 1.0 millisecond pulses applied, is additionally given to the address after it is verified as being correctly programmed. A minimum of one to a maximum of 25 1-ms pulses, plus one 3X overpulse, may be applied to each byte. When the intelligent algorithm cycle has been completed, all bytes must be read at  $V_{CC} = V_{PP} = 5 V$ .

#### Intelligent Algorithm Flowchart

#### Intelligent Algorithm

NOTES:

1. ALL TIMES SHOWN IN ( ) ARE MINIMUM AND IN  $\mu$ SEC UNLESS OTHERWISE SPECIFIED.

2. THE INPUT TIMING REFERENCE LEVEL IS 0.8 V FOR A  $V_{IL}$  AND 2 V FOR A  $V_{IH}$ .

3. 10E AND 10FP ARE CHARACTERISTICS OF THE DEVICE BUT MUST BE ACCOMMODATED BY THE PROGRAMMER.

4.  $0.1~\mu F$  CERAMIC CAPACITOR ON  $V_{PP}$  IS REQUIRED DURING PROGRAMMING ONLY TO SUPPRESS VOLTAGE TRANSIENTS.

#### Intelligent Algorithm

#### AC Programming Characteristics $T_A = 25 \pm 5^{\circ} C$ , $V_{CC}[1] = 6.0 V \pm 0.25 V$ , $V_{PP} = 12.5 V$

|                 |                                     |      | Limits |       |      |

|-----------------|-------------------------------------|------|--------|-------|------|

| Symbol          | Parameter                           | Min. | Тур.   | Max.  | Unit |

| tas             | Address Setup Time                  | 2    |        |       | μS   |

| toes            | OE Setup Time                       | 2    |        |       | μS   |

| tps             | Data Setup Time                     | 2    |        |       | μS   |

| t <sub>AH</sub> | Address Hold Time                   | 0    |        |       | μS   |

| toH             | Data Hold Time                      | 2    |        |       | μs   |

| tDFP            | Output Enable to Output Float Delay | 0    |        | 130   | ns   |

| tvps            | Vpp Setup Time                      | 2    |        |       | μS   |

| tvcs            | V <sub>CC</sub> Setup Time          | 2    |        |       | μS   |

| tpw             | CE Initial Program Pulse Width      | 0.95 | 1.0    | 1.05  | ms   |

| topw[2]         | CE Overprogram Pulse Width          | 2.85 |        | 78.75 | ms   |

| toE             | Data Valid from OE                  |      |        | 150   | ns   |

#### \*AC Conditions of Test

| Input Rise and Fall Times (10% to 90%)  | 20 ns |

|-----------------------------------------|-------|

| Input Pulse Levels 0.45 V to            | 2.4 V |

| Input Timing Reference Level 0.8 V and  | 2.0 V |

| Output Timing Reference Level 0.8 V and | 2.0 V |

#### NOTES:

- 1. VCC must be applied simultaneously or before Vpp and removed simultaneously or after Vpp.

- 2. The length of the overprogram pulse will vary from 2.85 msec to 78.75 msec as a function of the iteration counter value X.

#### Ordering and Package Information

DIMENSIONS IN INCHES AND (MILLIMETERS).

SEEQ Technology, Incorporated

## **SECTION 2**

# E<sup>2</sup>ROMS

(Electrically Erasable Programmable Read Only Memories)

#### E<sup>2</sup>ROM CROSS REFERENCE GUIDE

|                |                      |                     |                 | Features                 |                                            |                                          |                                                 | ,                            |

|----------------|----------------------|---------------------|-----------------|--------------------------|--------------------------------------------|------------------------------------------|-------------------------------------------------|------------------------------|

| Device Type    | 21 Volt<br>Operation | 5 Volt<br>Operation | Latches<br>Only | Latches<br>and<br>Timers | Access<br>Time<br>Faster<br>Than<br>350 ns | Write<br>Time<br>Faster<br>Than<br>10 ms | Endurance<br>Higher<br>Than<br>10,000<br>Cycles | Nearest<br>SEEQ<br>Equivalen |

| Intel 2816     | х                    |                     |                 |                          |                                            |                                          |                                                 | DQ52B13                      |

| Intel 2816A    |                      | х                   |                 |                          |                                            |                                          |                                                 | DQ52B13                      |

| Intel 2817[1]  | х                    |                     |                 | x                        |                                            |                                          |                                                 | DQ2817                       |

| Intel 2817A[1] |                      | Х                   |                 | Х                        | ×                                          |                                          |                                                 | DQ2817                       |

| National 2816  | Х                    |                     |                 |                          |                                            |                                          |                                                 | DQ2816A                      |

| National 2816A |                      | Х                   |                 | x                        |                                            |                                          |                                                 | DQ2816/                      |

| Xicor 2816A    | x                    | Х                   |                 | X                        |                                            |                                          |                                                 | DQ2816A                      |

| Xicor 2864     |                      | Х                   |                 | Х                        |                                            |                                          |                                                 | DQ2864                       |

| AMD 9864       |                      | Х                   |                 | Х                        | Х                                          |                                          |                                                 | DQ2864                       |

| SEEQ 52B13     | ×                    | Х                   | ×               |                          | х                                          |                                          |                                                 |                              |

| SEEQ 2816A     | Х                    | Х                   |                 | X                        | х                                          | ×                                        |                                                 |                              |

| SEEQ 2817A     |                      | Х                   |                 | X                        | ×                                          | ×                                        |                                                 |                              |

| SEEQ 5516A     | X                    | Х                   |                 | ×                        | X                                          | ×                                        | X                                               |                              |

| SEEQ 5517A     |                      | Х                   |                 | ×                        | x                                          | ×                                        | X                                               |                              |

| SEEQ 52B33     |                      | Х                   | x               |                          | X                                          | ×                                        |                                                 |                              |

| SEEQ 2864      |                      | Х                   |                 | X                        | X                                          | X                                        |                                                 |                              |

Note: 1. The 2817 and 2817A are supplied in a 28-pin package. All other 16K  $E^2ROMs$  are in a 24-pin package.

SeeQ

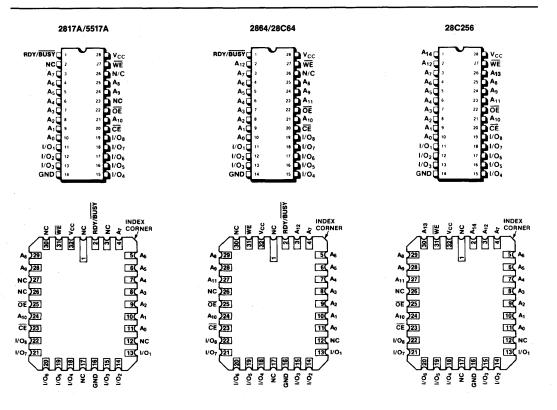

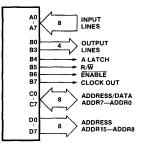

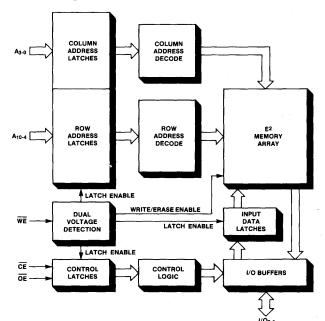

# SEEQ's E<sup>2</sup>ROM Family Configuration

SEEQ's 28XXX family

# SEEQ's E<sup>2</sup>ROM Family Configuration

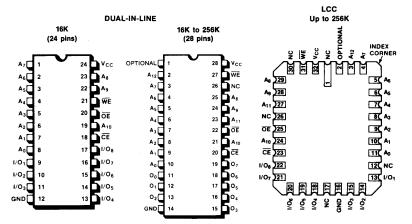

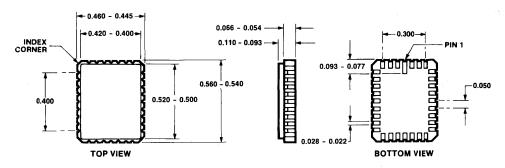

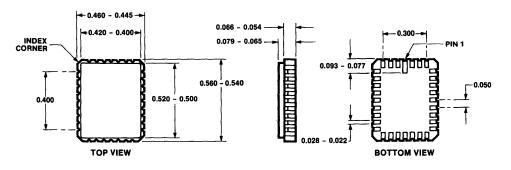

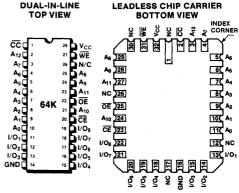

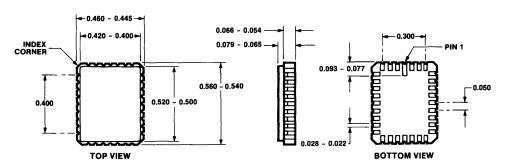

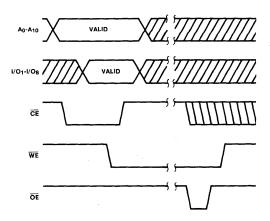

SEEQ's E<sup>2</sup>ROM family conforms to JEDEC's byte-width pin configuration in both dual-in-line and LCC packages. This allows upgrades from 16K to 256K densities. It should be noted that pin 1 is an optional pin (up to the 256K) used for various E<sup>2</sup>ROM features such as ready/busy and chip clear.

#### JEDEC Pin Configuration

DUAL-IN-LINE

Pins

1

26

64K

Optional

NC

256K

A14

A13

| Pins<br>Density | 2        | 30  |

|-----------------|----------|-----|

| 64K             | Optional | NC  |

| 256K            | A14      | A13 |

LCC

#### SEEQ's 52BXX family

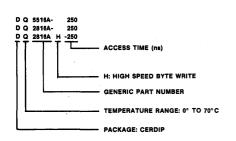

# **2816A/5516A**Timer E<sup>2</sup> 16K Electrical Erasable ROMs

February 1984

#### Features

- High Endurance Write Cycles

- 5516A: 1,000,000 Cycles/Byte

- 2816A: 10,000 Cycles/Byte

- On-Chip Timer

- Automatic Erase and Write Time Out

- 2 ms Byte Write Time (2816AH)

- All Inputs Latched by Write or Chip Enable

- Direct Replacement to 2K x 8 E2ROMs

- 21 V 2816

- 5 V Timer 2816A

- 5 V ± 10% Power Supply

- Power Up/Down Protection Circuitry

- 250 ns max. Access Time

- **■** Low Power Operation

- 110 mA max. Active Current

- 40 mA max. Standby Current

- JEDEC Approved Byte-Wide Pinout

#### Description

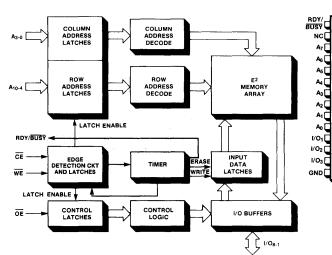

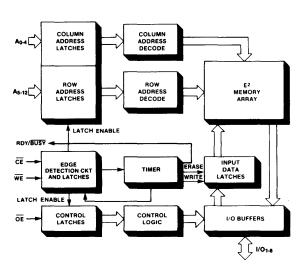

SEEQ's 5516A and 2816A are 5 V only, 2K x 8 electrically erasable read only memories (E²ROMs). E²ROMs are ideal for applications which require non-volatility and in-system data modification. The endurance, the number of times that a byte may be written, is 1 million for the 5516A and 10 thousand for the 2816A. The 5516A's extraordinary high endurance was accomplished using SEEQ's proprietary oxynitride E²ROM process and its innovative "Q cell™" design. The 5516A is ideal for systems that require frequent updates.

Both E<sup>2</sup>ROMs have an internal timer that automatically times out the write time. A separate erase cycle is not required and the minimum write enable (WE) pulse width needs to be only 150 ns. The on-chip timer, along with the inputs being latched by a write or chip enable signal edge, frees the microcomputer system for other tasks during the write time. The standard 2816A and 5516A's write time is 10 ms. while the (continued on next page)

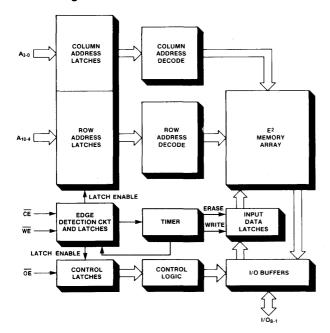

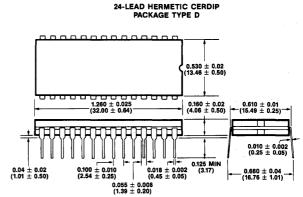

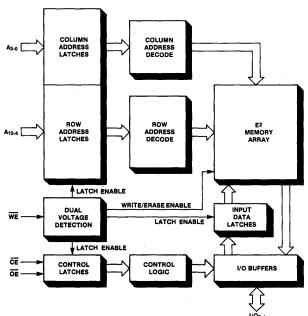

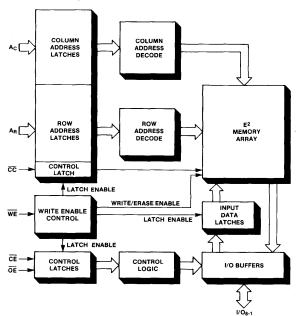

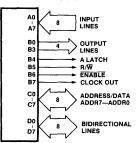

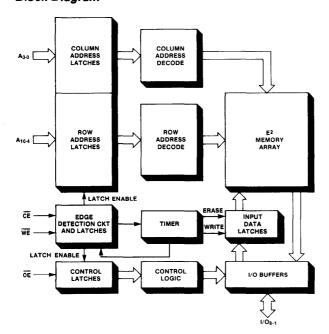

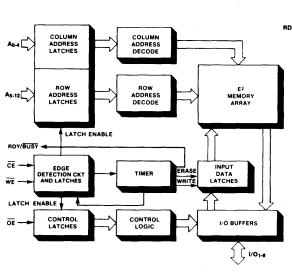

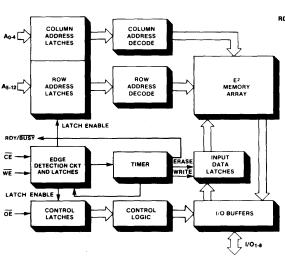

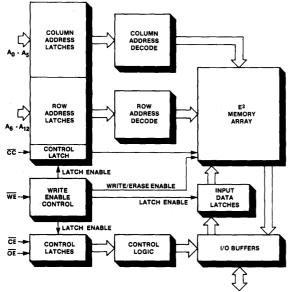

#### **Block Diagram**

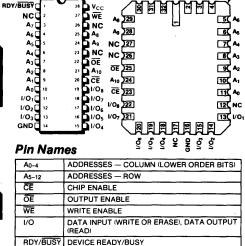

#### Pin Configuration

#### Pin Names

| 5 | A <sub>0</sub> -A <sub>10</sub> | ADDRESSES                                            |

|---|---------------------------------|------------------------------------------------------|

|   | CE                              | CHIP ENABLE                                          |

|   | ŌĒ                              | OUTPUT ENABLE                                        |

|   | WE                              | WRITE ENABLE                                         |

|   | I/O                             | DATA INPUT (WRITE OR<br>ERASE)<br>DATA OUTPUT (READ) |

## 2816A/5516A

2816AH's write time is a fast 2 ms. Once a byte is written, it can be read in 250 ns. The inputs are TTL for both the byte write and read mode.

These two timer E<sup>2</sup>ROMs are ideal for systems with limited board area. For systems where cost is important or higher density is required, SEEQ has a latch only "52B" family at 16K, 32K, and 64K bit densities. The "52B" family has the same JEDEC approved pin configuration but without the on-chip timer. All "52B" family inputs are latched by the falling edge of the write enable signal.

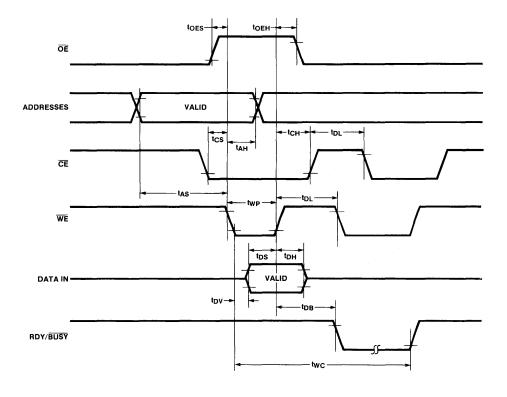

#### **Device Operation**

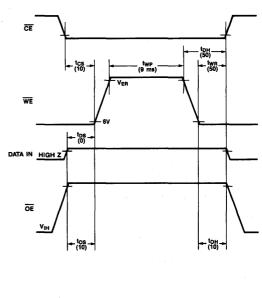

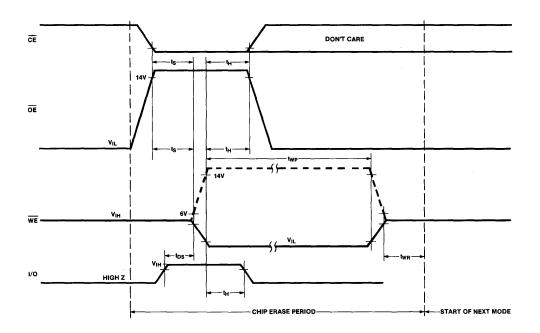

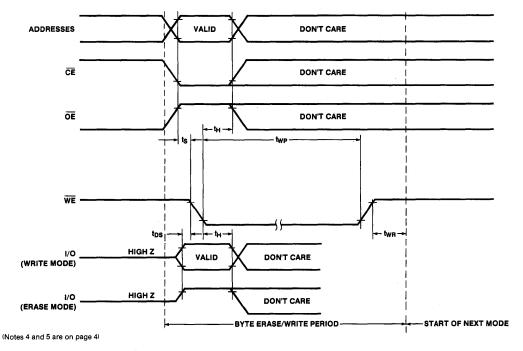

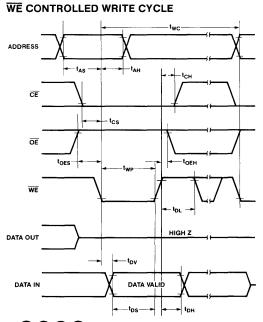

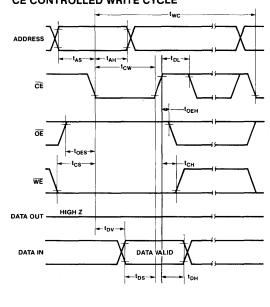

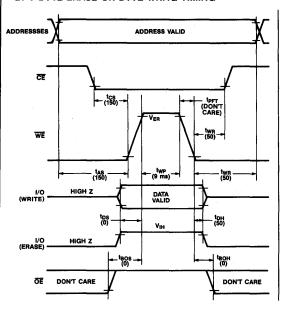

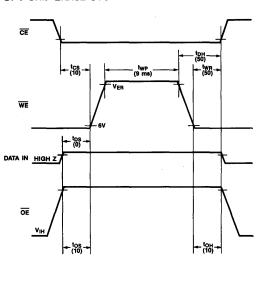

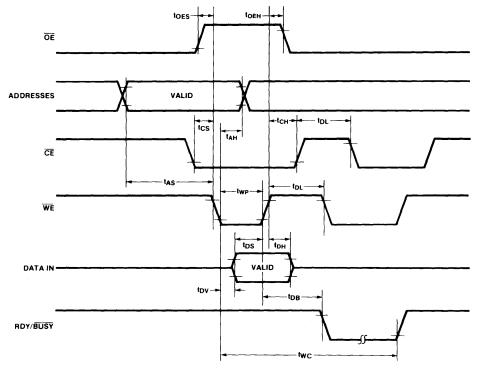

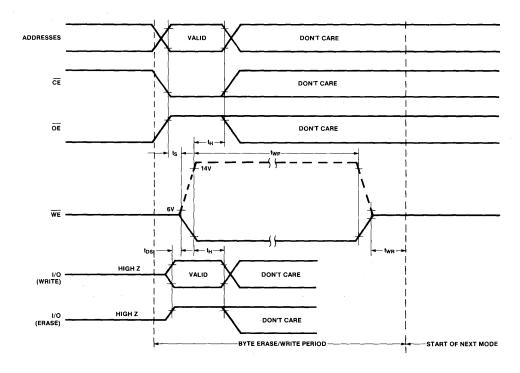

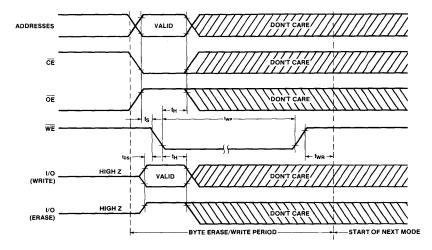

There are five operational modes (see Table 1) and, except for the chip erase mode, only TTL inputs are required. To write into a particular location, a TTL low is applied to the write enable ( $\overline{WE}$ ) pin of a selected ( $\overline{CE}$  low) device. This, combined with output enable ( $\overline{OE}$ ) being high, initiates a write cycle. During a byte write cycle, addresses are latched on the last falling edge of  $\overline{CE}$  or  $\overline{WE}$  and data is latched on the first rising edge of  $\overline{CE}$  or  $\overline{WE}$ . An internal timer times out the required byte write time. An automatic byte erase is performed internally in the byte write mode.

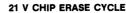

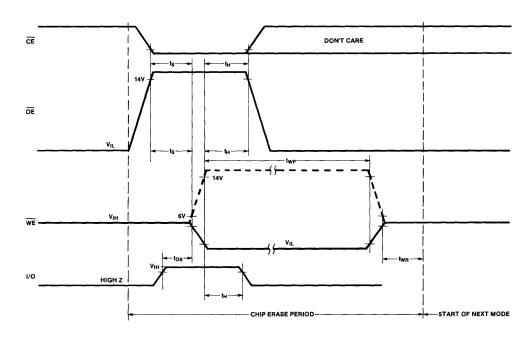

The chip erase mode clears all data to a TTL high in one 9 ms cycle. This is accomplished by raising both  $\overline{WE}$  and  $\overline{OE}$  to a high voltage (e.g. 21 V) and having all

the data inputs at a TTL high. In addition an optional 21 V byte write (preceded by a byte erase) mode is available.

#### Mode Selection (Table 1)

| Mode                     | CE  | ŌĒ  | WE              | 1/0    |

|--------------------------|-----|-----|-----------------|--------|

| Read                     | VIL | VIL | V <sub>IH</sub> | Dout   |

| Standby                  | ViH | Х   | Х               | High Z |

| Byte Write               | VIL | ViH | VIL*            | DIN    |

| Write or Read<br>Inhibit | VIL | ViH | ViH             | High Z |

| Chip Erase               | VIL | VER | VER             | ViH    |

<sup>\*</sup>A 21 V input on WE is an optional mode.

#### Power Up/Down Considerations

The 2816A/5516A has internal circuitry to minimize a false write during system  $V_{\rm CC}$  power up or down. This circuitry prevents writing under any one of the following conditions.

- 1. V<sub>CC</sub> is less than 3 V.

- A negative Write Enable (WE) transition has not occurred when V<sub>CC</sub> is between 3 V and 5 V.

Writing will also be prevented if  $\overline{CE}$  or  $\overline{OE}$  are in a logical state other than that specified for a byte write in the Mode Selection table.

#### Absolute Maximum Stress Ratings\*

| Temperature         -65° C to +150° C           Under Bias         −10° C to +80° C |

|-------------------------------------------------------------------------------------|

| All Inputs or Outputs with Respect to Ground+6V to -0.3V                            |

| WE During Writing/Erasing with Respect to Ground +22.5V to −0.3V                    |

| Duration of WE Supply at 22V During W/E Inhibit                                     |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Operating Characteristics** $T_A = 0$ to $70^{\circ}$ C, $V_{CC} = 5$ V $\pm 10\%$ , unless otherwise noted.

|        |                                      | Limits |      |       |                                                                                       |

|--------|--------------------------------------|--------|------|-------|---------------------------------------------------------------------------------------|

| Symbol | Parameter                            | Min.   | Max. | Units | Test Condition                                                                        |

| lcc    | Active Vcc Current                   |        | 110  | mA    | CE = OE = V <sub>IL</sub> ; All I/O Open;<br>Other Inputs = 5.5 V                     |

| ISB    | Standby V <sub>CC</sub> Current      |        | 40   | mA    | CE = V <sub>IH</sub> , OE = V <sub>IL</sub> ; All I/O's<br>Open; Other Inputs = 5.5 V |

| ILI    | Input Leakage Current                |        | 10   | μΑ    | V <sub>IN</sub> = 5.5 V                                                               |

| ILO    | Output Leakage Current               |        | 10   | μΑ    | V <sub>OUT</sub> = 5.5 V                                                              |

| VIL    | Input Low Voltage                    | -0.1   | 0.8  | V     |                                                                                       |

| ViH    | Input High Voltage                   | 2.0    | 6    | V     |                                                                                       |

| VoL    | Output Low Voltage                   |        | 0.4  | V     | I <sub>OL</sub> = 2.1 mA                                                              |

| Vон    | Output High Voltage                  | 2.4    |      | V     | I <sub>OH</sub> = -400 μA                                                             |

| VER    | OE and WE Voltage in Chip Erase Mode | 12     | 22   | V     | I <sub>ER</sub> = 10 μA                                                               |

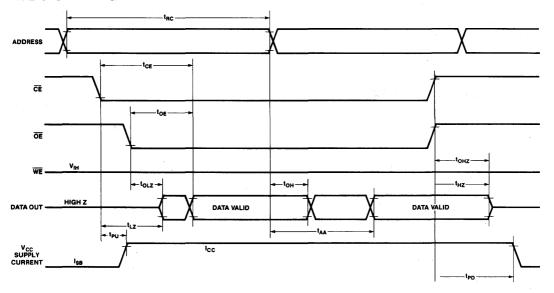

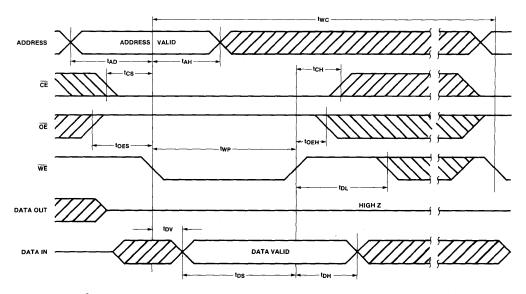

#### **AC Characteristics**

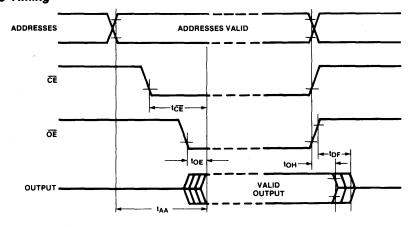

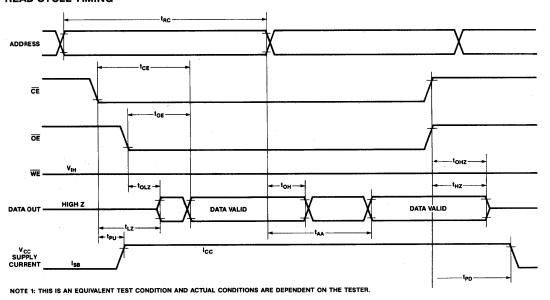

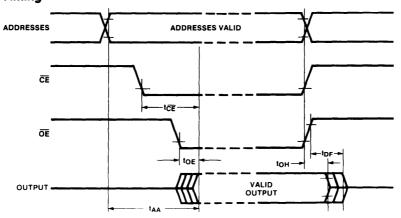

**Read Operation**  $T_A = 0$  to  $70^{\circ}$  C,  $V_{CC} = 5$  V  $\pm$  10%, unless otherwise noted

|        |                                 | Limits (ns)                   |      |                               |      |           |      |       |

|--------|---------------------------------|-------------------------------|------|-------------------------------|------|-----------|------|-------|

|        | e e                             | 5516A-250<br>2816A/2816AH-250 |      | 5516A-300<br>2816A/2816AH-300 |      | 2816A-350 |      |       |

| Symbol | Parameter                       | Min.                          | Max. | Min.                          | Max. | Min.      | Max. | Units |

| tRC    | Read Cycle Time                 | 250                           |      | 300                           |      | 350       |      | ns    |

| tce    | Chip Enable Access Time         |                               | 250  |                               | 300  |           | 350  | ns    |

| taa    | Address Access Time             |                               | 250  |                               | 300  |           | 350  | ns    |

| toE    | Output Enable Access Time       |                               | 90   |                               | 100  |           | 100  | ns    |

| tLZ    | CE to Output in Low Z           | 10                            |      | 10                            |      | 10        |      | ns    |

| tHZ    | CE to Output in High Z          | 10                            | 100  | 10                            | 100  | 10        | 100  | ns    |

| tolz   | OE to Output in Low Z           | 50                            |      | 50                            | 1.   | 50        |      | ns    |

| tонz   | OE to Output in High Z          | 10                            | 100  | 10                            | 100  | 10        | 100  | ns    |

| tон    | Output Hold from Address Change | 50                            |      | 50                            |      | 50        |      | ns    |

| tpu    | CE to Power-up Time             | 0                             |      | 0                             |      | 0         |      | ns    |

| tpp    | CE to Power Down Time           |                               | 50   |                               | 50   |           | 50   | ns    |

#### Capacitance TA = 25° C, f = 1 MHz

| Symbol | Parameter         | Max.  | Conditions             |

|--------|-------------------|-------|------------------------|

| CIN    | Input Capacitance | 6 pF  | V <sub>IN</sub> = 0 V  |

| Соит   | Data (I/O) Cap,   | 10 pF | V <sub>I/O</sub> = 0 V |

#### A.C. Test Conditions

Output Load: 1 TTL gate and  $C_L = 100 pF$ Input Rise and Fall Times: <20 ns Input Pulse Levels: 0.45 V to 2.4 V Timing Measurement Reference Level: Inputs 1 V and 2 V Outputs 0.8 V and 2 V

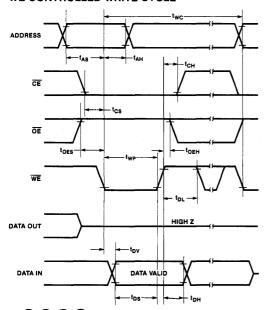

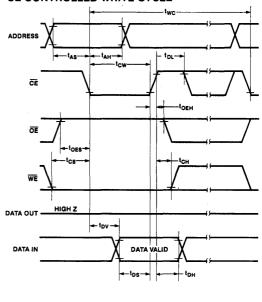

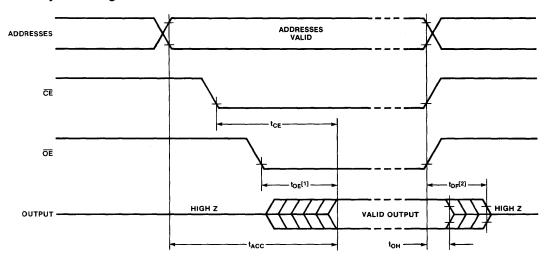

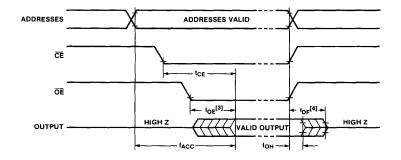

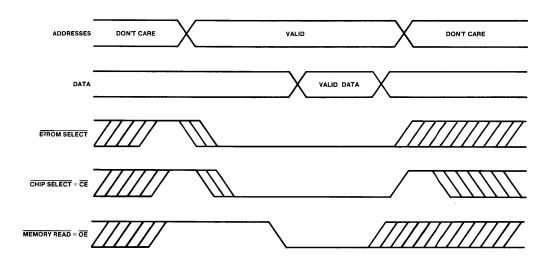

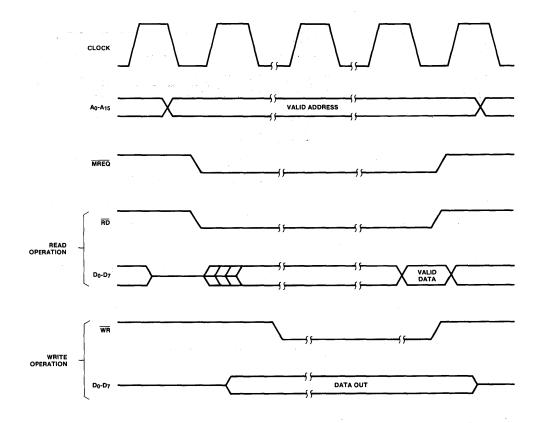

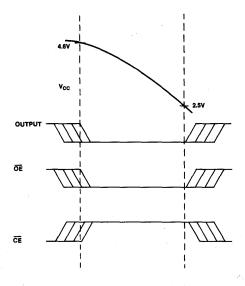

#### **READ CYCLE TIMING**

## 2816A/5516A