# MOS MEMORY PRODUCTS

2<sup>nd</sup> EDITION

## MOS MEMORY PRODUCTS

2<sup>nd</sup> EDITION FEBRUARY 1986

The M2716-16K EPROM memory designed and produced by SGS.

The 256K EPROM designed and produced by SGS.

Highly automated wafer processing increases yields and throughput to give SGS high production capability.

## SGS OFFICES

#### INTERNATIONAL HEADQUARTERS

SGS Microelettronica SpA Via C. Olivetti 2, - 20041 Agrate Brianza-Italy Tel.: 039 - 65551

Telex: 330131 - 330141 - SGSAGR

SGS Microelettronica SpA Sales Office: Bruxelles 1040 Bld. Reverslaan, 207 209

Tel.: 02 - 7366060 Telex: 24149

#### BRAZIL

SGS Semicondutores LTDA Sales Office:

05413 Sao Paulo

Av. Henrique Schaumann 286 - CJ33 Tel.: 011 - 853-5062

Telex: 37988 UMBR BR

#### DENMARK

SGS Semiconductor A.B. Sales Office: 2730 Herley Herlev Torv, 4 Tel.: 02 - 948533 Telex: 35411

#### FRANCE

Société Générale de Semiconducteurs 92120 Montrouge 21-23 Rue de la Vanne

Tel.: 01 - 47460800 Telex: 250938F

#### HONG KONG

SGS Semiconductor Asia Limited Hunghom, Kowloon 9th Floor, Block N, Kaiser Estate, Phase III, 11 Hok Yuen St., Tel.: 03-644251/5 Telex: 63906 ESGIE HX

#### ITALY

SGS Microelettronica SpA Direzione Italia e Sud Europa 20090 Assago (MI) V.le Milanofiori - Strada 4 - Palazzo A/4/A

Tel.: 02 - 8244131 (10 linee) Telex: 330131 - 330141 SGSAGR

Sales Offices: 40128 Bologna Via Corticella, 231 Tel.: 051-324486 00161 Roma Via A. Torlonia, 15 Tel.: 06-8444474

SGS Semiconductor Asia Ltd. Korea Liason Office Mapo, Seoul 121 Rm 1306 KMIC Bldg 168-9 Yumlidong Tel.: 712-7071/2/3 Telex: K 26493

#### SINGAPORE

SGS Semiconductor (Pte) Ltd. Singapore 2056 28 Ang Mo Kio Industrial Park 2 Tel.: 482-1411 Telex: RS 55201 ESGIES

#### SPAIN

SGS Microelettronica SpA 28036 Madrid Representative Office Calle Agustin De Foxà, 25 Tel.: 01 - 7337043 Telex: 41414

#### SWEDEN

SGS Semiconductor A.B. 19500 Märsta Bristagatan, 16

Tel.: 0760 - 40120 Telex: 054 - 10932

#### SWITZERLAND SGS Semiconductor S.A.

Sales Offices: 1218 Grand-Saconnex (Geneve) Chemin François-Lehmann, 18/A Tel.: 022 - 986462/3 Telex: 28895

#### TAIWAN-REPUBLIC OF CHINA

SGS Semiconductor Asia Ltd Taipei Sec 4

6th floor, Pacific Commercial Bldg 285 Chung Hsiao E Road Tel.: 2-7728203 Telex: 10310 ESGIETWN

#### UNITED KINGDOM

SGS Semiconductor Limited Aylesbury, Bucks Planar House, Walton Street Tel.: 0296 - 5977 Telex: 051 - 83245

#### WEST GERMANY

SGS Halbleiter Bauelemente GmbH 8018 Grafing bei München Haidling, 17 Tel.: 08092-690 Telex: 05 27378

#### Sales Offices:

3012 Langenhagen Hans Boeckler Str., 2

Tel.: 0511 - 789881 Telex: 923195

#### 8500 Nürnberg 40

Allersberger Str., 95 eingang Wilhelminenstr. 1 Tel.: 0911 - 464071

#### Telex: 626243 8023 Pullach bei München

Seitnerstrasse, 42 Tel.: 089 - 793 0662 Telex: 5215784 7000 Stuttgart 31

Loewenmarkt, 5 Tel.: 0711 - 881101

Telex: 723625

#### U.S.A.

SGS-Semiconductor Corporation

Phoenix, AZ 85022 1000 Fast Bell Boad Tel.: (602) 867-6100 Telex: 249976 SGSPH UR

Sales Offices:

#### Bloomington, MN 55420

One Appletree Square Suite 201 K Tel.: (612) 854-0525

Ft. Lauderdale FL 33309 1001 NW 62nd Street

Suite 314 Tel.: (305) 4938881

#### Telex: 291588 Hauppauge, NY 11788 330 Motor Parkway

Suite 100 Tel.: (516) 435-1050 Telex: 221275 SGSHA UR Indianapolis, IN 46268

8777 Purdue Road

Suite 113 Tel.: (317) 872-4404

Telex: 209144 SGSIN UR Irvine, CA 92714 18271 W. McDurmott Drive

Suite J. Tel. (714) 863-1222 Telex: 277793 SGSOR UR

Norcross, GA 30071

6045 Atlantic Blvd Road

Suite G Tel.: (404) 446-8686

Telex: 261395 SGSAT UR Plano, TX 75074

850 East Central Parkway

Suite 180 Tel.: (214) 881-0848

Telex: 203997 SGSDA UR Poughkeepsie, NY 12601

201 South Avenue

Suite 206 Tel.: (914) 473-2255

Santa Clara, CA 95051

2700 Augustine Drive Suite 209

Tel.: (408) 727-3404 Telex: 278833 SGSSA UR

Schaumburg, IL 60196 600 North Meacham Road Tel.: (312) 490-1890

Telex: 210159 SGSCH UR

Southfield, MI 48076 21411 Civic Center Dr. 309

Mark Plaza Bidg.

Tel.: (313) 358-4250

Telex: 810-224-4684 "MGA DET SOFD"

Waltham, MA 02154

240 Bear Hill Road Tel.: (617) 890-6688 Telex: 200297 SGSWH UR

## **TABLE OF CONTENTS**

| SGS: AN INTRODUCTION   | Page 4 |

|------------------------|--------|

| ALPHANUMERICAL INDEX   | 8      |

| PRODUCT GUIDE          | 9      |

| TECHNICAL INFORMATIONS | 13     |

| DATASHEETS             | 35     |

| PACKAGES               | 153    |

| RELIABILITY REPORTS    | 159    |

|                        |        |

## IDENTITY

Late in 1957, SGS was founded around a team of researchers who were already carrying out pioneer work in the field of semiconductors. From that small nucleus, the company has evolved into a Group of Companies, operating on a worldwide basis as a broad range semiconductor producer, with billings well over a quarter billion dollars and employing over 10000 people.

The SGS Group of Companies has now reached a total of 12 subsidiaries, located in Brazil, France, Germany, Italy, Malta, Malaysia, Singapore, Spain, Sweden, Switzerland, United Kingdom and the USA.

To go with its logo, the company takes the motto "Technology and Service", underlining the accent given to the development of state-of-the-art technologies and the corporate commitment to offer customers the best quality and service in the industry.

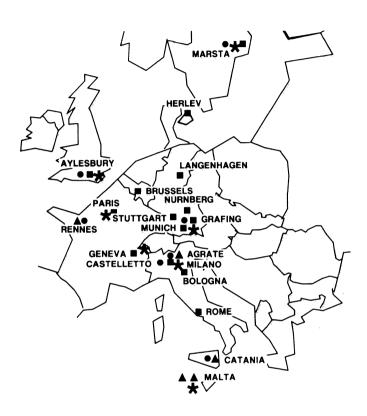

## **SGS LOCATIONS - EUROPE**

- \* HEADQUARTERS

- **A FACTORIES**

- SALES OFFICES

- DESIGN CENTERS

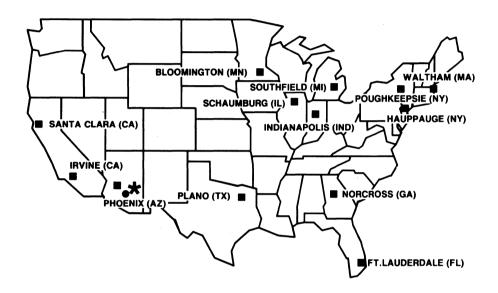

## **SGS LOCATIONS - NORTH AMERICA**

- \* HEADQUARTERS

- SALES OFFICES

- DESIGN CENTERS

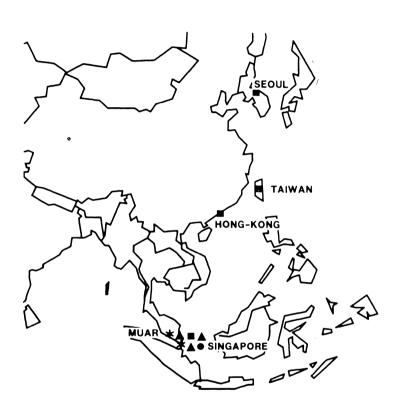

## SGS LOCATIONS - ASIA/PACIFIC

- \* HEADQUARTERS

- **A FACTORIES**

- SALES OFFICES

- DESIGN CENTERS

## **ALPHANUMERICAL INDEX**

| Type<br>Number | Function                          | Page<br>Number |

|----------------|-----------------------------------|----------------|

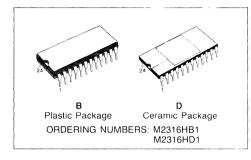

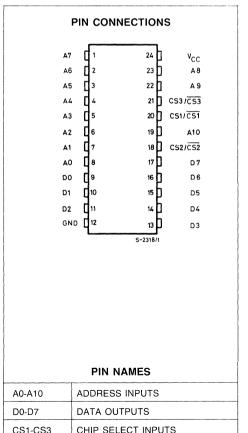

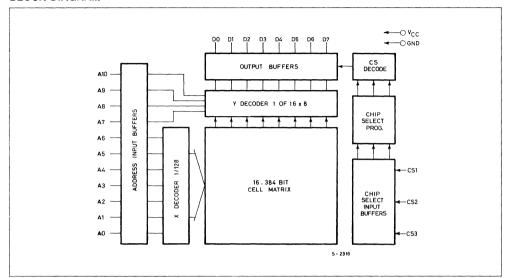

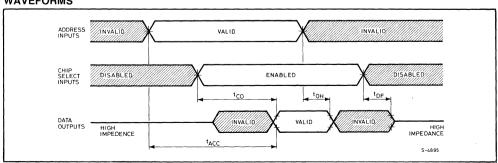

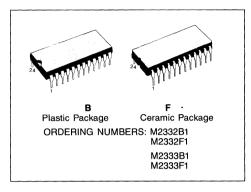

| M2316H         | 16K-bit (2K × 8) Read Only Memory | 111            |

| M2332          | 32K-bit (4K×8) Read Only Memory   | 115            |

| M2333          | 32K-bit (4K×8) Read Only Memory   | 115            |

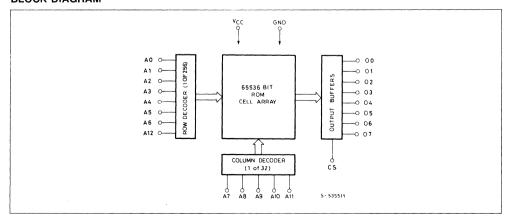

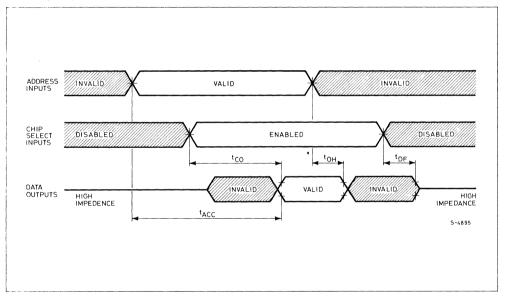

| M2364          | 64K-bit (8K×8) Read Only Memory   | 119            |

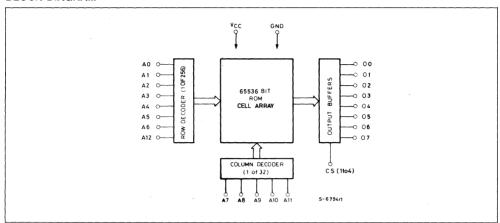

| M2365          | 64K-bit (8K×8) Read Only Memory   | 123            |

| M2716          | 16K (2K×8) UV Erasable PROM       | 37             |

| M2716P         | 16K (2K×8) OTP EPROM              | 103            |

| M2732A         | 32K (4K×8) UV Erasable PROM       | 45             |

| M2764          | 64K (8K×8) UV Erasable PROM       | 53             |

| M2764A         | 64K (8K×8) UV Erasable PROM       | 61             |

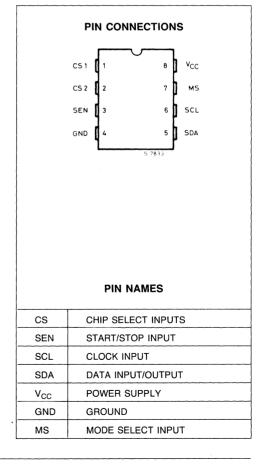

| M8571          | 1024 bit Serial EEPROM            | 133            |

| M9306          | 256 bit (16×16) Serial EEPROM     | 143            |

| M9346          | 1024 bit (64 × 16) Serial EEPROM  | 147            |

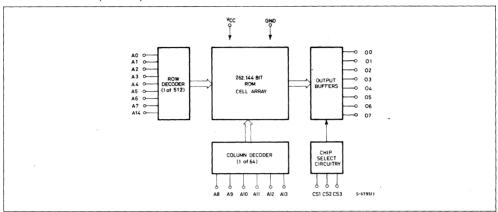

| M23256         | 256K bit (32K×8) Read Only Memory | 127            |

| M23256A        | 256K bit (32K×8) Read Only Memory | 127            |

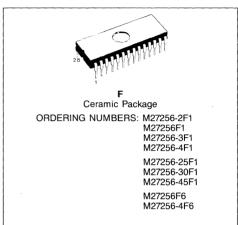

| M27128A        | 128K (16K×8) UV Erasable PROM     | 71             |

| M27256         | 256K (32K×8) UV Erasable PROM     | 81             |

| M27512         | 512K (64K×8) UV Erasable PROM     | 91             |

|                |                                   | <del></del>    |

PEODUCT CUIDE

## **SALES TYPE IDENTIFICATION**

| Memoi                   | ry Pref                                     | ix                    | ·                                              |                                       |                                              |      |  |

|-------------------------|---------------------------------------------|-----------------------|------------------------------------------------|---------------------------------------|----------------------------------------------|------|--|

| ldentif                 | ication                                     | Numb                  | oer                                            | · · · · · · · · · · · · · · · · · · · |                                              |      |  |

|                         |                                             |                       |                                                |                                       |                                              |      |  |

| Speed                   | Range                                       | <b>.</b>              | EPROMs                                         | T                                     | ROMs                                         |      |  |

| V <sub>CC</sub> 5V ± 5% | V <sub>CC</sub><br>5V ± 10%                 | M2716<br>M2716P       | M2732A-M2764<br>M2764A-27128A<br>M27256-M27512 | M2316H                                | M2332-M2333<br>M2364-M2365<br>M23256-M23256A |      |  |

| Notina                  | 05                                          | (ns)                  | (ns)                                           | (ns)                                  | (ns)                                         |      |  |

| Notyng<br>1             | 25                                          | 450<br>350            | 250                                            | 300                                   | 250                                          |      |  |

| 2                       | 20                                          | 330                   | 200                                            |                                       |                                              |      |  |

| 3                       | 30                                          |                       | 300                                            |                                       |                                              |      |  |

| 4                       | 45                                          |                       | 450                                            |                                       |                                              |      |  |

|                         |                                             |                       |                                                |                                       | <u></u>                                      |      |  |

| B Pla<br>D Cei<br>F Cer | ge<br>stic<br>ramic M<br>ramic F<br>-8 Plas | Multi La<br>Frit-Sea  |                                                |                                       |                                              |      |  |

| 4                       | A 1                                         | Range<br>70°C<br>85°C | e                                              | ·                                     |                                              | <br> |  |

## PROCESSES DESCRIPTION

#### **ERASABLE PROGRAMMABLE READ ONLY MEMORY**

| Capacity | Device  | Organization | Process | Access Time (Max.) | Page |

|----------|---------|--------------|---------|--------------------|------|

| 16K      | M2716   | 2K×8 bit     | NMOS E  | 350/450 ns         | 37   |

| 32K      | M2732A  | 4K×8 bit     | NMOS E1 | 200/250/300/450 ns | 45   |

| 64K      | M2764   | 8K×8 bit     | NMOS E2 | 200/250/300/450 ns | 53   |

| 64K      | M2764A  | 8K×8 bit     | NMOS E3 | 200/250/300/450 ns | 61   |

| 128K     | M27128A | 16K×8 bit    | NMOS E3 | 200/250/300/450 ns | 71   |

| 256K     | M27256  | 32K×8 bit    | NMOS E3 | 200/250/300/450 ns | 81   |

| 512K     | M27512  | 64K×8 bit    | NMOS E3 | 250/300 ns         | 91   |

#### MASK READ ONLY MEMORY

| Capacity | Device  | Organization | Process | Access Time (Max.) | Page |

|----------|---------|--------------|---------|--------------------|------|

| 16K      | M2316H  | 2K×8 bit     | NMOS H1 | 300 ns             | 111  |

| 32K      | M2332   | 4K×8 bit     | NMOS H1 | 250 ns             | 115  |

| 32K      | M2333   | 4K×8 bit     | NMOS H1 | 250 ns             | 115  |

| 64K      | M2364   | 8K×8 bit     | NMOS H2 | 250 ns             | 119  |

| 64K      | M2365   | 8K×8 bit     | NMOS H2 | 250 ns             | 123  |

| 256K     | M23256  | 32K × 8 bit  | NMOS H2 | 250 ns             | 127  |

| 256K     | M23256A | 32K × 8 bit  | NMOS H2 | 250 ns             | 127  |

#### **ELECTRICALLY ERASABLE PROGRAMMBLE READ ONLY MEMORY**

| Capacity | Device | Organization   | Process | Max. Clock Frequency | Page |

|----------|--------|----------------|---------|----------------------|------|

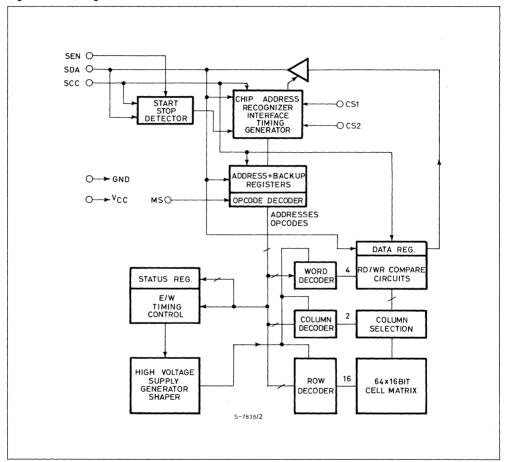

| 1K       | M8571  | see data sheet | NMOS F1 | 125 KHz              | 133  |

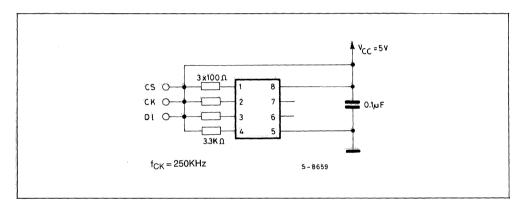

| 256      | M9306  | 16 × 16 bit    | NMOS F1 | 250 KHz              | 143  |

| 1024     | M9346  | 64 × 16 bit    | NMOS F1 | 250 KHz              | 147  |

| PROCESS | CHARACTERISTICS                                                                   | PRODUCTS                                                |  |  |  |

|---------|-----------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| NMOS E  | PH DOPING<br>CHANNEL LENGTH 4 μm<br>GATE OXIDE THICKNESS 1100 Å<br>VCC=5V VPP=25V | EPROM<br>(M2716)<br>(M2716P)                            |  |  |  |

| NMOS E1 | AS DOPING<br>CHANNEL LENGTH 3 μm<br>GATE OXIDE THICKNESS 700 Å<br>VCC=5V VPP=21V  | EPROM<br>(M2732A)<br>(M2732AP)                          |  |  |  |

| NMOS E2 | AS DOPING<br>CHANNEL LENGTH 2 μm<br>GATE OXIDE THICKNESS 700 Å<br>VCC=5V VPP=21V  | EPROM<br>(M2764)<br>(M2764P)                            |  |  |  |

| NMOS E3 | AS DOPING CHANNEL LENGTH 1.5 μm GATE OXIDE THICKNESS 350 Å VCC=5V VPP=12.5V       | EPROM<br>(M2764A)<br>(M2764AP)<br>(M27128A)<br>(M27256) |  |  |  |

| NMOS F1 | AS DOPING<br>CHANNEL LENGTH 3.5 μm<br>GATE OXIDE THICKNESS 800 Å<br>VCC = 5V      | EEPROM<br>(M8571)<br>(M9306)<br>(M9346)                 |  |  |  |

| NMOS H1 | AS DOPING RC CHANNEL LENGTH 3/4 μm GATE OXIDE THICKNESS 500 Å VCC=5V              |                                                         |  |  |  |

| NMOS H2 | AS DOPING<br>CHANNEL LENGTH 2.5 μm<br>GATE OXIDE THICKNESS 350 Å<br>VCC = 5V      | ROM                                                     |  |  |  |

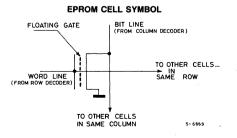

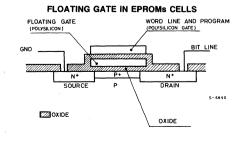

## **HOW DOES AN EPROM WORK**

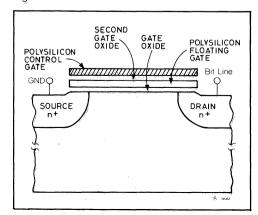

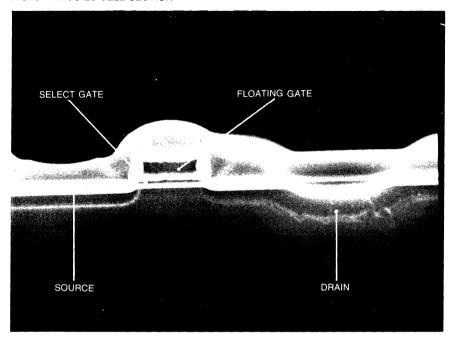

The EPROM cell transistor is just like a standard MOS transistor with the exception that a floating gate is added as shown in figure 1. The vertical stacking allows the functions of storage and reading, which normally require separate devices, to be within the space a single field effect transistor occupies. The EPROM cell is programmed by charging the floating gate with the injection of "hot electrons" from the drain's pinch off region. Erasing is obtained by internal photoemission from the floating gate to the top gate and substrate. The ultraviolet light give to the electrons enough energy to pass the energy barrier between the floating gate and the oxide surrounding it.

When the EPROM cell is programmed, the negative charge on the floating gate causes the floating gate to source voltage to be negative. This turns the cell off, even with a positive reading voltage applied to the select gate. Since the floating gate is not tied to a power supply, its voltage is determined by its charge and by capacitive coupling to the voltages of the select gate, the drain, the channel, and the source. The difference between the floating gate voltage and the voltages of these other areas can be used to determine the electric fields in the various oxide regions of the device. Although the voltage applied to the chip during programming is high 25; 21 or 12.5V) the fields across the gate oxide directly above the channel are relatively small, about 1.5MV/cm. During all other operations, even when the floating gate is fully charged, this field is less than 0.7MV/cm.

Fig. 1

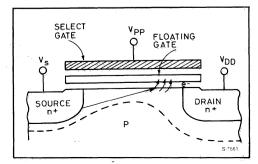

During programming (see fig. 2) the hot electrons get their energy from the voltage applied to the drain of the EPROM cell. They are accelerated along the channel into the even higher fields surrounding the drain depletion region. While traversing the channel, the electrons enter a region where the electric field in the substrate is about 10<sup>5</sup>V/cm or greater. At this point the rate of energy gained from the electric field can no longer be described by the temperature of the silicon; hence the term "hot". Once these electrons gain sufficient energy they can surmount the energy barrier of about 3.2 eV between the silicon substrate and the silicon dioxide insulator.

Because energy loss due to phonon emission increase at higher lattice temperature, it is actually easier to obtain hot electrons at lower operating temperatures. In addition to phonon emission, hot electrons with energies above about 1.8 eV may give up some of this energy in another way: through electron hole pair creation resulting from impact ionization. This phenomenon is observed in ordinary MOS transistors as the cause of the onset of the substrate current at high drain voltages. However, in the case of the EPROM, significant current multiplication produces substantial substrate current even before a large enough drain voltage is reached to produce hot electron injection into the oxide.

With positive drain and channel voltages, electrons injected into the oxide of an n-channel EPROM return to the substrate unless a high positive select gate voltage is applied to pull the electrons toward the floating gate. Not only does the floating gate have to be positively biased with respect to the source, it must also be positive with respect to the point along the channel where hot electron injection occurs.

Fig. 2

Near the beginning of the injection process the inversion layer extends almost all the way to the drain, and the field in the oxide is attractive except for a small portion very near the drain. Current begins to flow through the oxide at the point where the electrons are their hottest and where the oxide field is most favorable. As the floating gate charges up, the floating gate to source voltage drops and the drain's pinch off region moves towards the source. The surface field near the drain intensifies and more hot electrons are produced in the substrate. However in the region where the electron are their hottest, the oxide field is least favorable for injection and so the injected electron. injection process is self limiting. The charging of the floating gate reduces the number of electrons that can be accelerated in the high field region. As the floating gate becomes fully charged, to oxide current is reduced almost to zero because the oxide field is now repulsive to the electrons injected into the high field is now repulsive to the electrons injected into the high field region.

Since the reducing electric field between the floating gate and the channel is responsible for shutting off the oxide current, the saturated threshold voltage shift off the floating gate tracks the selected gate voltage during programming on a volt per volt basis. The floating gate charges to the same value relative as the source and channel. An increase in the selected gate voltage during programming merely increases the charge of the floating date necessary to abort the injection of hot electrons. The drain voltage boes not in general have a major effect on the final programmed voltage of the floating gate. However it does effect the speed at which the device is programmed. since injection exhibits an exponential dependence on the electric field in the channel.

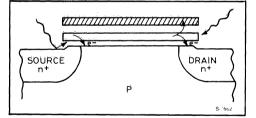

EPROMs needs to be completely erased before they are reprogrammed. Erasure is accomplished by exposing the devices to UV light. Typical erasure sources are quartz jacketed mercury arc lamps and mercury vapor lamps, which emit strong radiation at a wavelength of 2537 Å. The photons emitted by the lamps are absorbed by electrons in the conduction and valence bands of the floating gate; at this wavelength, most of them are absorbed within 50 Å of the oxide interface (see fig. 3).

The excited electrons leave the floating gate, enter the oxide, and are swept away to the select gate or substrate by local field. During erasure, the select gate, source, drain, and substrate are all near ground potential. With an N-type floating gate, electrons can be excited from either the conduction band or the valence band into the oxide. Ultraviolet rays are so strongly absorbed that they don't get past the top select gate and the photons

can only make their way to the floating gate from the side. In self aligned structure, the edge of the floating gate is directly exposed to the radiation. But in earlier N-channel structures in which the floating gate is completely covered by the select gate, erasure is accomplished as the photons travel through the field oxide, under the select gate, and to the floating gate where they are absorbed. This wave-guiding effect is efficent beacuse the reflectivity of silicon to 2500 Å light is roughly 65%.

During reading, the EPROM cell operates like an ordinary transistor except that the normal date capacitance is replaced by the series capacitance of the floating gate structure. The most important characteristic of a non volatile memory is how well they retain their data. For EPROMs the answer hinges on how well the charge on the floating gate stays put over the lifetime of the part. The advantage of floating gate memories is that the gates are surrounded by high integrity silicon dioxide. This oxide is a nearly ideal insulator because it has a wide bandgap, a very high barrier with reference to silicon and aluminium, a relatively low surface state density on silicon, low bulk trapping levels, and no structural polarization. For ordinary electric fields from the floating gate to the select gate and substrate encountered during reading and storage, electron emission is negligible.

Fig. 3

## **EPROMS TECHNOLOGY EVOLUTION**

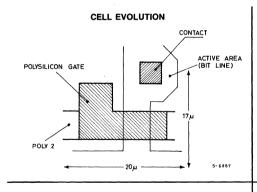

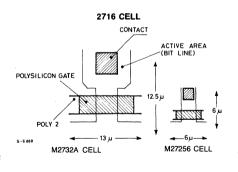

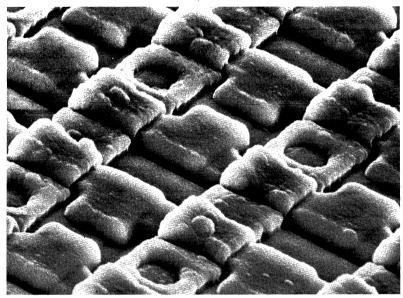

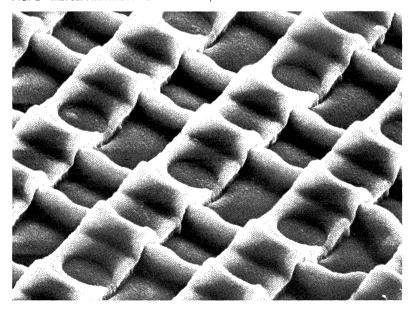

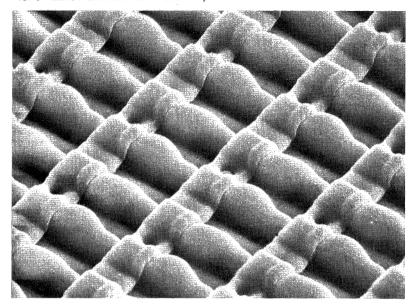

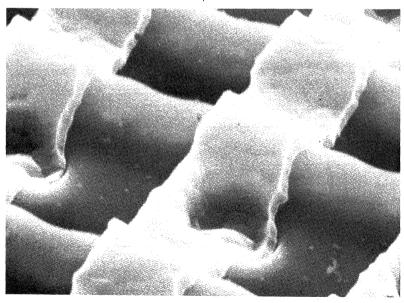

From the introduction of the M2716, SGS has been developing and evolving EPROM technologies in order to increase storage capacity and quality characteristics.

Starting from 1978 with the M2716, manufactured using the NMOS E0 process, four distinct advances have been made reducing cell area from 340µm² down to the present 36µm² with the NMOS E3

process. The evolution can be clearly seen in figs. 1 to 4.

Figure 1 shows the matrix area of a M2716. Figures 2, 3 and 4 then show respectively the M2732A, M2764 and M27256, respectively manufactured using NMOS E1, E2 and E3 processes. The table shown below gives some characteristics of the four processes.

| PROCESS NMOS          |       | E0   | E1    | E2   | E3   |

|-----------------------|-------|------|-------|------|------|

| CELL AREA             | (μm²) | 340  | 162.5 | 100  | 36   |

| GATE OXIDE1 THICKNESS | (Å)   | 1100 | 700   | 700  | 350  |

| GATE OXIDE2 THICKNESS | (Å)   | 1200 | 800   | 800  | 400  |

| PROGRAMMING VOLTAGE   | (V)   | 25   | 21    | 21   | 12.5 |

| CELL TRANS. LENGTH    | (μm)  | 4.00 | 3.00  | 2.25 | 1.50 |

#### **CELL EVOLUTION**

FIG. 1 - M2716 MATRIX AREA 1 cm = 4  $\mu$ m

FIG. 2 - M2732A MATRIX AREA 1 cm = 4  $\mu$ m

FIG. 3 - M2764 MATRIX AREA 1 cm = 4  $\mu$ m

FIG. 4 - M27256 MATRIX AREA 1 cm = 1  $\mu$ m

FIG. 5 - NMOS E3 CELL SECTION

## **EPROMS PROGRAMMING**

This document concerns programming characteristics of the M2764A and M27256, concentrating on those factors which will be new to the EPROM memory designer.

Figure 1 shows the evolution of SGS's EPROM family. The new generation M27256 brings with it improved performance and state-of-the-art reliability.

The lower programming voltage (12.5V) and the replacement of PGM by A14 highlight the additions accompanying the M27256. Advanced technology from the M27256 will soon bring enhanced performance to lower density EPROMs, specifically the M2764A and M27128A.

Fig. 1 - SGS EPROMs EVOLUTION

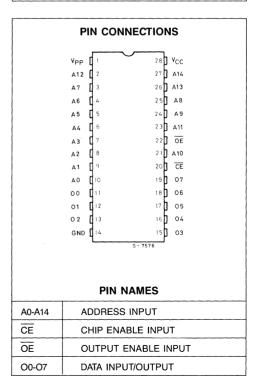

| 27256                  | 27128A                 | 2764A                  | 2732A | 2716 |              | 28           | 2716 | 2732A  | 2764A                  | 27128A                 | 27256                  |

|------------------------|------------------------|------------------------|-------|------|--------------|--------------|------|--------|------------------------|------------------------|------------------------|

| V <sub>PP</sub><br>A12 | V <sub>PP</sub><br>A12 | V <sub>PP</sub><br>A12 |       |      | [ 2<br>[ 3   | 27 ]<br>26 ] |      |        | V <sub>CC</sub><br>PGM | V <sub>CC</sub><br>PGM | V <sub>CC</sub><br>A14 |

| A7                     | A7                     | A7                     | A7    | A7   | ď 4          | 25           | Vcc  | Vcc    | N.C.                   | A13                    | A13                    |

| A6                     | A6                     | A6                     | A6    | A6   | <b>i</b> 5   | 24           | A8   | A8     | A8                     | A8                     | A8                     |

| A5                     | A5                     | A5                     | A5    | A5   | <b>r</b> é   | 23           | A9   | A9     | A9                     | Ä9                     | A9                     |

| A4                     | A4                     | A4                     | A4    | A4   | 7            | 22           | VPP  | A11    | A11                    | A11                    | A11                    |

| A3                     | A3                     | A3                     | A3    | A3   | d a          | 21           | ŌĒ   | OE/VPP | ŌĒ                     | ŌĒ                     | ŌĒ                     |

| A2                     | A2                     | A2                     | A2    | A2   | n 9          | 20           | A10  | A10    | A10                    | A10                    | A10                    |

| A1                     | A1                     | A1                     | A1    | A1   | <b>1</b> 10  | 1.           | CE   | CE     | CE                     | CE                     | CE                     |

| Ά0                     | A0                     | A0                     | A0    | A0   | 3            | 19]]         | 07   | 07     | 07                     | 07                     | 07                     |

| 00                     | 00                     | 00                     | 00    | 00   | 911          | 10]          | O6   | 06     | 06                     | 06                     | 06                     |

| 01                     | 01                     | 01                     | 01    | 01   | 12           | 17 🛭         | O5   | O5     | O5                     | O5                     | 05                     |

| 02                     | 02                     | O2                     | 02    | 02   | <b>[</b> ]13 | 16           | 04   | 04     | 04                     | 04                     | 04                     |

| GND                    | GND                    | GND                    | GND   | GND  | <b>(</b>  14 | 15           | 03   | 03     | О3                     | 03                     | 03                     |

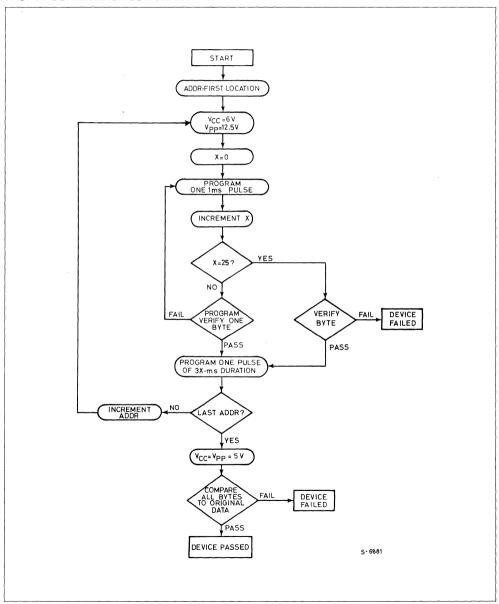

#### THE FAST PROGRAMMING ALGORITHM

The Fast Programming Algorithm was developed as an improved alternative to the 50 msec per byte programming techniques for SGS's M2764 EPROM. By taking advantage of the variable programming times required by the cells in an EPROM array, programming speed increase of 5 or 6 times have been achieved (see table 1). The success of

this algorithm, coupled with the long programming times which would be inherent in programming the M27256 with a 50 msec per byte algorithm, has prompted SGS to develop a new M27256 Fast Programming Algorithm specifically tailored to user requirements.

TABLE 1 - EPROM PROGRAMMING-TIME EVOLUTION

| DEVICE   | BYTES | PROGRAMMING<br>. TIME (MIN) |

|----------|-------|-----------------------------|

| 2716     | 2048  | 1.75                        |

| 2732A    | 4096  | 3.5                         |

| 2764     | 8192  | 7.0                         |

| 2764 *   | 8192  | 1.25                        |

| 2764A *  | 8192  | 1.25                        |

| 27128A * | 16384 | 2.5                         |

| 27256*   | 32768 | 5                           |

<sup>\*</sup> Using Fast Programming Algorithm

The programming speed improvement (Fast Programming Algorithm) is an interactive closed loop technique of margin checking.

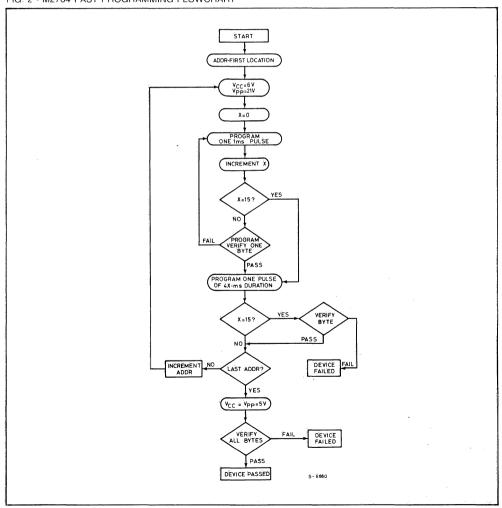

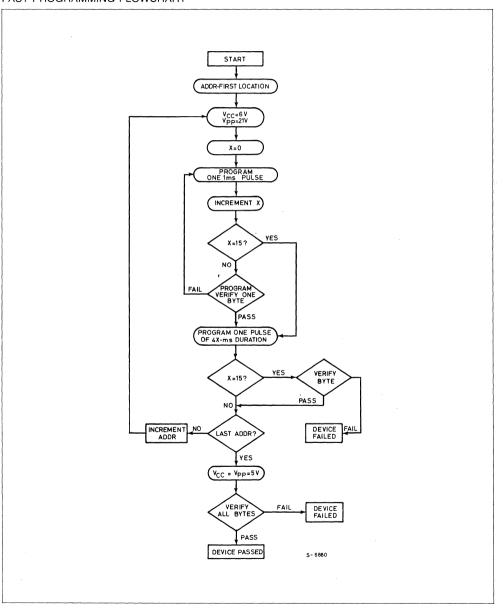

It ensure that the programmed bit won't change status once  $V_{CC}$  is in the normal operating range. For the M2764 the algorithm begins by setting  $V_{CC}$  to 6V (higher than required for normal operation but necessary to provide programming margin), setting the programming voltage  $V_{PP}$  to 21V and then iteratively supplying 1-msec LOW-going programming pulses to the EPROM's programm-disable pin PGM. After each pulse, the algorithm checks the EPROM's output for the desired programmed value. If the output is incorrect, the algorithm repeats the pulse-and-check operation; incorrect output after 15 pulses causes rejection

of the EPROM device.

If the EPROM is fully functional, however, one of the pulses results in proper EPROM output. At that point, the algorithm supplies still another programming pulse—this one four times longer than the combined length of the previously applied 1-msec pulses. This longer pulse helps ensure that the EPROM cell has adeguate programming margin for reliable operation.

Although the pulse can be as long as 60 msec, very few EPROM bytes require this much programming time. In fact, most EPROM bytes program with only one or two 1-msec pulses, so a typical total programming time per byte is 5 to 10 msec.

For reference see fig. 2

FIG. 2 - M2764 FAST PROGRAMMING FLOWCHART

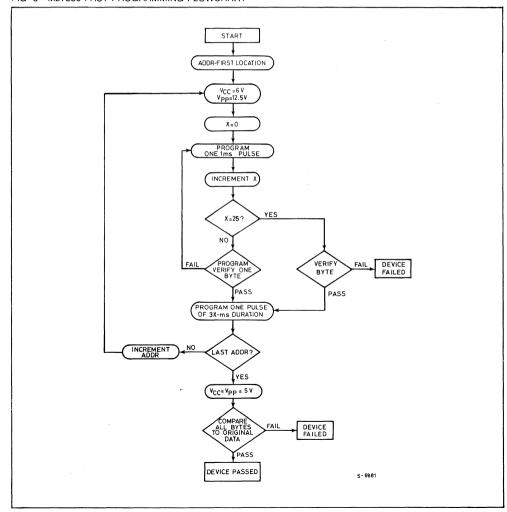

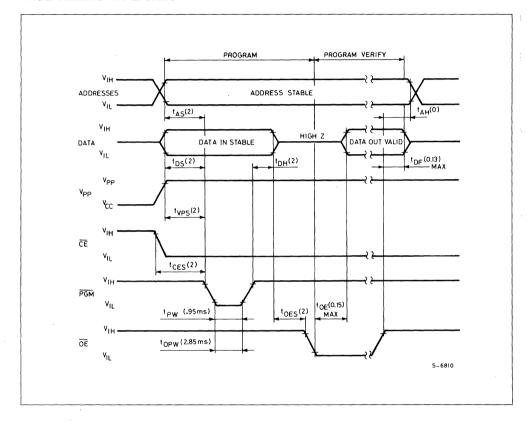

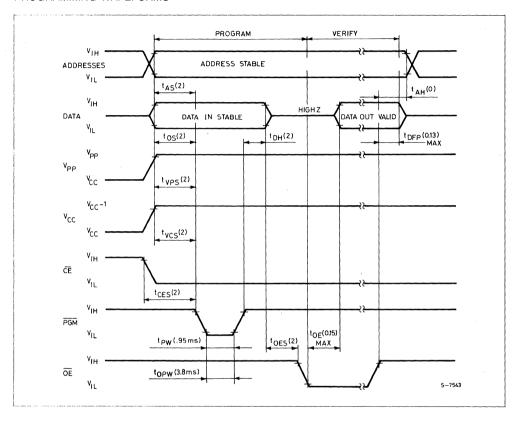

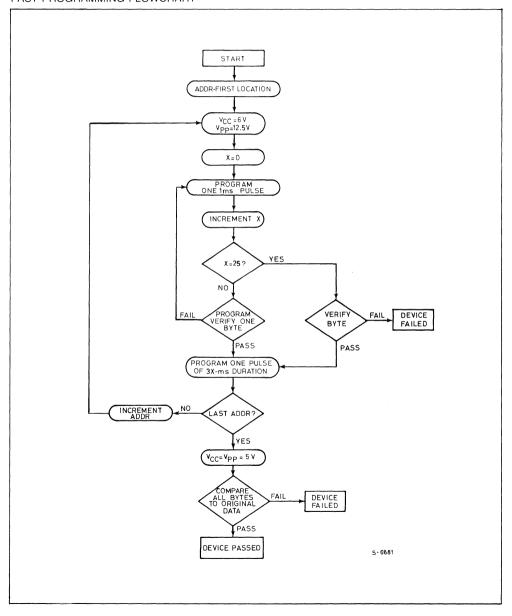

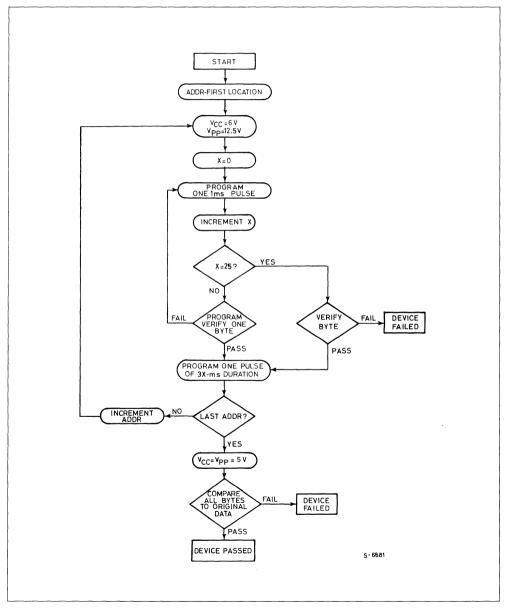

The M27256 programming algorithm is similar to the Fast Programming Algorithms used for SGS's M2764 and M27128 EPROMs. It is now available as a standard feature in many PROM programmers. This new programming algorithm guarantees that each cell has been programmed reliably. The M27256 Fast Programming Algorithm shown in figure 3 is a feedback control loop. In examining this flowchart three distinct characteristics can be seen. First, the programming voltage has been reduced form  $21 \pm 0.5$  volts, as was required on earlier generation M2764 EPROM, to  $12.5 \pm 0.5$  volts. In all cases the Vpp voltage should never exceed 14 volts, and a 0.1  $\mu$ F capacitor should be placed between VPP and ground to insure proper decoupling. The technology advances implemented in the M27256 allow the programming voltage to be reduced while taking advantage of the performance of the programmed cell. The second characteristic that should be noted is the maximum number of 1ms pulses which are applied throughout the closed loop programming algorithm. As shown, 25 iterations of the loop is the maximum number allowed. The last characteristic which should be mentioned is the insertion of a byte verify after the iteration count has been maximized. This will save time by failing any device which may not verify correctly after 25 one msec pulses.

This Programming Algorithm shoud be used as well for M2764A and M27128A manufactured with the same NMOS-E3 Process (see page 16)

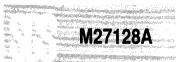

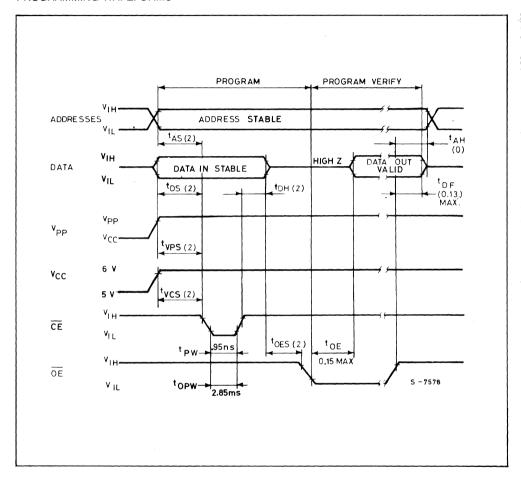

FIG. 3 - M27256 FAST PROGRAMMING FLOWCHART

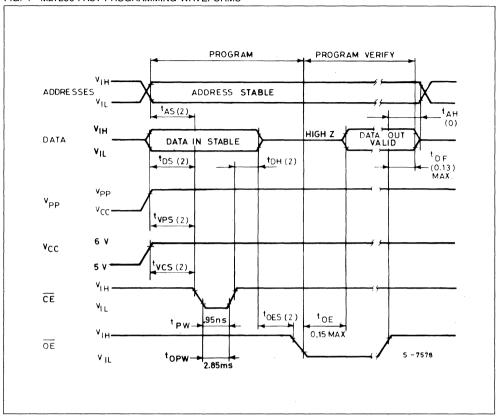

FIG. 4 - M27256 FAST PROGRAMMING WAVEFORMS

#### Notes:

- 1. All times shown in ( ) are minimum and in usec unless otherwise specified.

- 2. The input timing reference level is 0.8V for a  $V_{IL}$  and 2V for a  $V_{IH}$ .

- 3. t<sub>OF</sub> and t<sub>DFP</sub> are characteristics of the device but must be accommodated by the programmer.

- When the programming the M27256 a 0.1 μF capacitor is required across V<sub>PP</sub> and GROUND to suppress spurious voltage transients which can damage the device.

#### **ELECTRONIC SIGNATURE**

The Electronic Signature mode allow the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for uses by programming equipment for the purpose of automatically matching the device to be programmed with its correspongind programming algorithm. This mode is functional in the  $25^{\circ}\text{C} \pm 5^{\circ}\text{C}$  ambient temperature range that is requiered when programming the EPROM. For M27256 to activate this mode, the programming equipment must force 11.5V to 12.5V on address line A9 (pin 24) of the EPROM. Two identifier bytes may than be sequenced form the device outputs

by toggling address line A0 (pin 10) from  $V_{IL}$  to  $V_{IH}$ . All other address lines must be held at  $V_{IL}$  during Electronic Signature mode. Byte 0 (A0 =  $V_{IL}$ ) represents the manufacturer code and byte 1 (A0 =  $V_{IH}$ ) the device identifier code. For the SGS M27256, these two identifier bytes are given below. All identifiers for manufacturer and device codes will possess odd parity, with the MSB (07) defined as the parity bit.

This feature has been implemented also an M2764A, M27128A and M27512.

In Fig. 5 you can see the Electronic Signature Mode for the complete EPROM family.

FIG. 5 - ELECTRONIC SIGNATURE MODE

|          | PINS<br>IDENTIFIER | A0<br>(10)      | O7<br>(19) | O6<br>(18) | O5<br>(17) | O4<br>(16) | O3<br>(15) | O2<br>(13) | O1<br>(12) | O0<br>(11) | Hex<br>Data |

|----------|--------------------|-----------------|------------|------------|------------|------------|------------|------------|------------|------------|-------------|

| M2764A   | Manufacturer code  | V <sub>IL</sub> | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 20          |

| WZ/OTA   | Device code        | V <sub>IH</sub> | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 08          |

| M27128A  | Manufacturer code  | V <sub>IL</sub> | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 20          |

| WIZTIZOA | Device code        | V <sub>IH</sub> | 1          | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 89          |

| M27256   | Manufacturer code  | V <sub>IL</sub> | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 20          |

| 10127230 | Device code        | V <sub>IH</sub> | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 04          |

| M27512   | Manufacturer code  | V <sub>IL</sub> | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 20          |

| IVIZ/JIZ | Device code        | V <sub>IH</sub> | 0          | 0          | 0          | 0          | 1          | 1          | 0          | 1          | 0D          |

Note: For M27512 only A9 = 12V  $\pm$  0.5V; A1-A8, A10-A13,  $\overline{CE}$ ,  $\overline{OE}/V_{PP} = V_{JL}$ ; A14, A15 =  $V_{IH}$

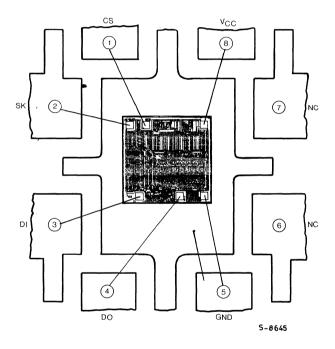

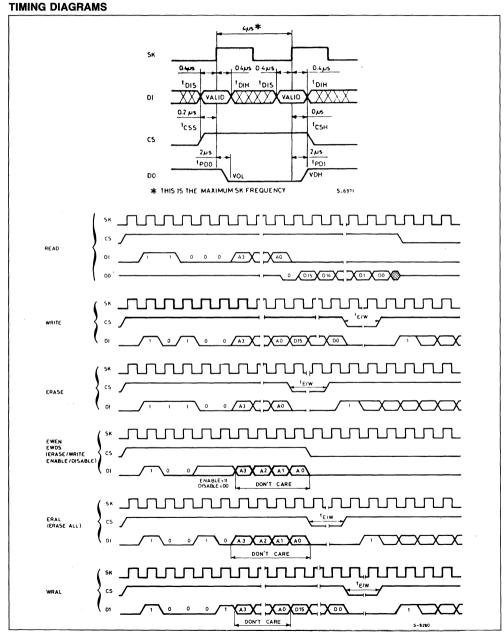

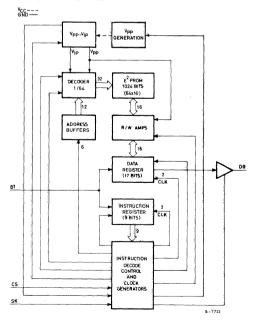

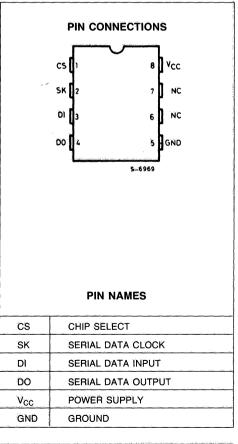

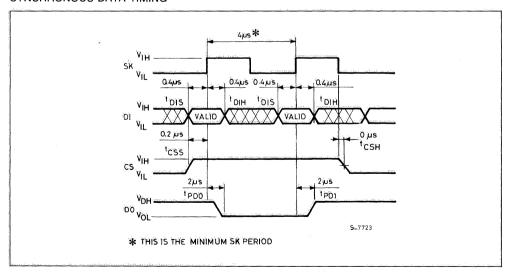

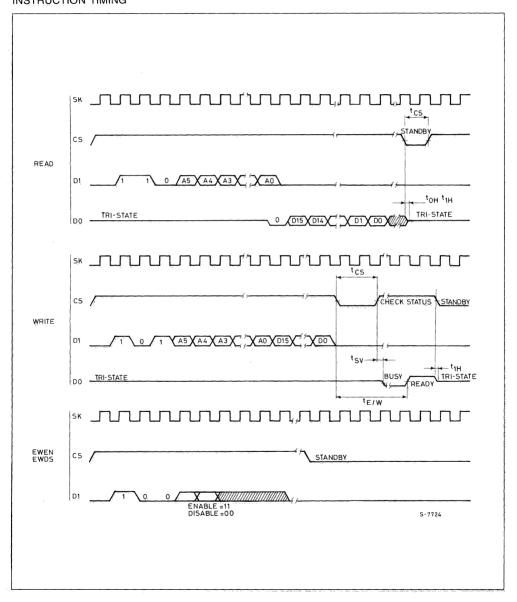

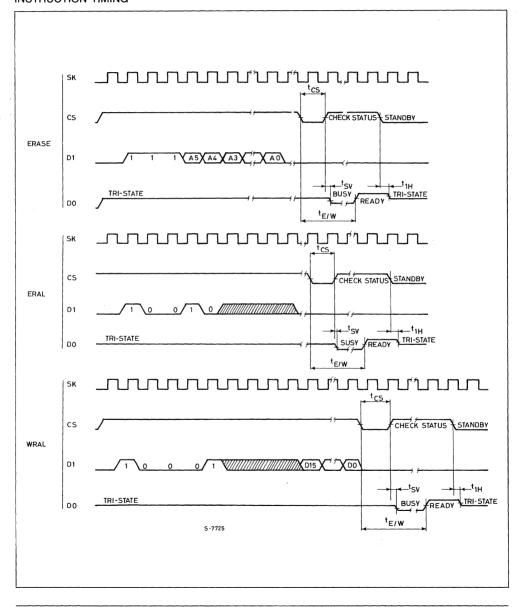

## **EEPROM M9306 PRODUCT DESCRIPTION**

New components being used in computer systems are necessary for computer evolution. One of these is the Electrically Erasable Programmable Read Only Memory (EEPROM), that can be elettrically erased and written one byte at a time.

EEPROM is particularly attractive in applications requiring field update of program store memory or

non volatile data captime, and has the data retention requirements of eaulier generations of PROMs, but also must maintain its field programmable characteristics over its device life. In this paper we will present the SGS M9306 serial EEPROM in all his characteristics.

#### PRODUCT DESIGN

#### **DESIGN CHARACTERISTICS**

| Device Name Device Desctiption Stepping (Revision) Process Name                         | 9306<br>256 bit serial EEPROM<br>1<br>NMOS-F1 |

|-----------------------------------------------------------------------------------------|-----------------------------------------------|

| Array Organization: Number of Rows Number of Columns/Output Number of Sense Amps/Output | 16 × 16<br>8<br>32<br>1                       |

| Memory Cell Area<br>Active<br>Total                                                     | 3.5 × 4μ<br>21 × 30μ                          |

| Min Row Pitch<br>Column Pitch                                                           | 12μ<br>21μ                                    |

| Die Size                                                                                | 64 × 65 mils                                  |

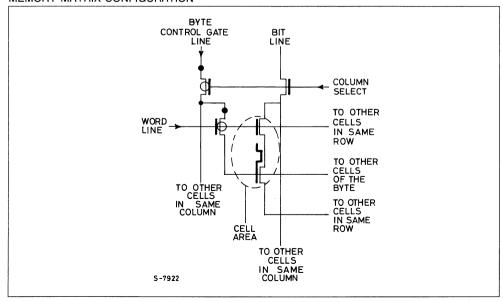

#### MEMORY MATRIX CONFIGURATION

#### PRODUCT TECHNOLOGY

#### PROCESS DEFINITION

- The NMOS-F1 is a n-channel MOS process with a minimum transitstor length of 4μm.

- The process has been optimized for a 21 Volt programming voltage.

- Active elements are obtained by means at ion implantation.

- NMOS-F1 is a two polysilicon level process; Source and Drain doping is As from As-doped polysilicon.

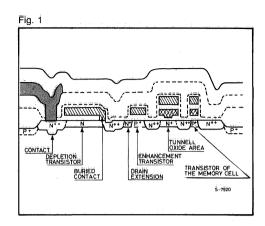

- A pictorial view of process is shown in Fig. 1.

#### MASK SEQUENCE

| PLANOX               | 100 |

|----------------------|-----|

| N + IMPLANT (FLOTOX) | 150 |

| DEPLETION            | 360 |

| THINNER OXIDE        | 150 |

| 1st POLY             | 600 |

| ENH. IMPLANT (LVS)   | 300 |

| BURIED CONTACTS      | 380 |

| 2nd POLY (Logic)     | 401 |

| DRAIN EXT.           | 451 |

| CONTACTS             | 741 |

| METAL                | 800 |

| GLASS PASSIVATION    | 900 |

| NITRIDE PASSIVATION  | 950 |

In the standard layout of the memory cell the mask 150 is used twice during the process:

first time to define the area to be implanted N + and a second time to define the area where the thin oxide will be grown.

#### MEMORY CELL

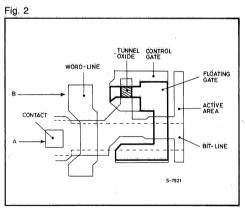

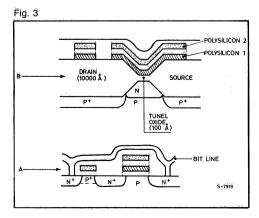

The memory cell is a transistor with a floating gate in first polysilicon level and a control gate in second polysilicon level.

The voltage of the floating gate is determined by capacitive coupling to the control gate and to the tunneling oxide, drain and field oxide areas.

The electric field during programming and the current in the channel of the transistor during reading depend on the voltage V<sub>F</sub>, so it is clear that for good operation of the memory cell it is very important that the values of the capacitive couplings are not changed.

The layout of the memory cell is shown in Fig. 2. A section view of the cell structure is shown in Fig. 3.

### PROCESS CHARACTERISTICS

| Device Name                     | 9306                                   |  |  |  |  |

|---------------------------------|----------------------------------------|--|--|--|--|

| Device Description              | 256 bits serial EEPROM                 |  |  |  |  |

| Process Name                    | NMOS-F1                                |  |  |  |  |

| Wafer Size                      | 4"<br>3.5μ<br>2<br>13                  |  |  |  |  |

| Min. Channel Length (left)      |                                        |  |  |  |  |

| Number Poly Layer               |                                        |  |  |  |  |

| Min. Number of Mask             |                                        |  |  |  |  |

| Min. Number of Implants         | 5*                                     |  |  |  |  |

| Lateral Diffusion               | $0.4\mu$                               |  |  |  |  |

| Oxide Thickness                 |                                        |  |  |  |  |

| Poly 1 Gate                     | 700 Å                                  |  |  |  |  |

| Poly 2 Gate                     | 800 Å                                  |  |  |  |  |

| Thinner Oxide                   | 100 Å                                  |  |  |  |  |

| Poly 1 Thickness                | 1800 Å                                 |  |  |  |  |

| Poly 2 Thickness                | 4500 Å                                 |  |  |  |  |

| Metal Thickness                 | $1.1\mu$                               |  |  |  |  |

| Min. Diffusion Width            | $4\mu$                                 |  |  |  |  |

| Min. Poly 2 Width               | $3\mu$                                 |  |  |  |  |

| Min. Poly 2 Spacing             | $4\mu$                                 |  |  |  |  |

| Min. Metal Width                | $\dot{6\mu}$                           |  |  |  |  |

| Min. Metal Spacing              | $\dot{6\mu}$                           |  |  |  |  |

| Source-Drain Length             | $4\mu$                                 |  |  |  |  |

| Contact to Poly 2 Spacing       | $4\mu$                                 |  |  |  |  |

| Min. Contact Size               | $4\times4\mu$                          |  |  |  |  |

| Thinner Oxide Area              | $\sim 5\mu^2$                          |  |  |  |  |

| Stanting Resistivity            | 30 ÷ 50 Ohm/cm                         |  |  |  |  |

| Type of Dopomt                  | Arsenicum                              |  |  |  |  |

| Gate Material                   | Polysilicon                            |  |  |  |  |

| Word Line Material              | Polysilicon                            |  |  |  |  |

| Bit Line Material               | Metal                                  |  |  |  |  |

| Metallization                   | Alluminum                              |  |  |  |  |

| Poly-Metal Isolation Material   | P-VAPOX                                |  |  |  |  |

| Poly-Metal Isolation Thickness  | $1.1\mu$                               |  |  |  |  |

| Passivation Material            | VAPOX + Si <sub>3</sub> N <sub>4</sub> |  |  |  |  |

| Passivation Thickness (Vapox)   | 7000 Å                                 |  |  |  |  |

| Passivation Thickness (Nitride) | 6000 Å                                 |  |  |  |  |

#### **ELECTRICAL CHARACTERIZATION**

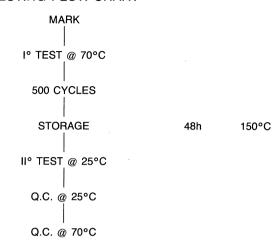

#### TESTING FLOW-CHART

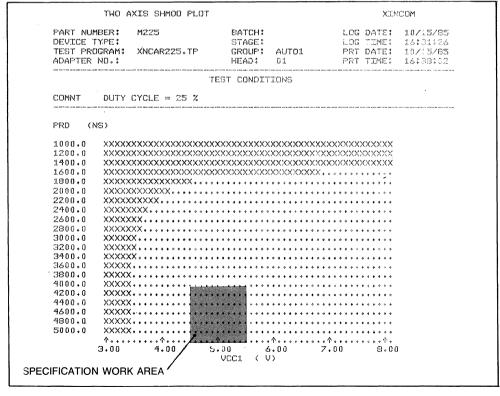

#### TWO AXIS SHMOO PLOT XINCOM PART NUMBER: M225 BATCH: LOG DATE: 10/15/85 DEVICE TYPE: LOG TIME: STAGE: 16:37:43 TEST PROGRAM: XNCAR225.TP GROUP: AUTO1 PRT DATE: 10/15/85 ADAFTER NO.: HEAD: 0.1 PRT TIME: 16:38:32 TEST CONDITTONS WRITE TIME COMNT TW (MS) 0.250.50 0.75 1.00 1.25 1.50 XXXXX.......... xxxxxx....... 1.75 2.00 XXXXXX...... 2.25 2.50 2.75 XXXXX....... 3.00 3.25 XXXXX........ 3.50 XXXXX...... 3.75 XXXXX............ XXXXX........ 4.00 <u> </u> 3.00 4.00 5.00 6.00 7.00 8.00 VCC1 ( V)

|                                              | TWO AXIS SHMOO PLOT                      |                                         |            |                                       |            | XINCOM      |                                     |  |

|----------------------------------------------|------------------------------------------|-----------------------------------------|------------|---------------------------------------|------------|-------------|-------------------------------------|--|

| PART NUI                                     | 1BER: M                                  | 1225                                    | BATC       | H:                                    | LOG        | DATE:       | 10/15/85                            |  |

| DEAXCE .                                     |                                          |                                         | STAG       | E::                                   | LOG        | TIME:       | 16:34:44                            |  |

| TEST PRO                                     |                                          | NCAR225.TP                              | GROU       | P: AUTO1                              | PRT        | DATE:       | 10/15/85                            |  |

| ADAPTER                                      | NO.:                                     |                                         | HEAD       | : 01                                  | PRT        | TIME:       | 16:38:18                            |  |

|                                              |                                          |                                         | TEST CON   | DITIONS                               |            |             |                                     |  |

| COMNT                                        | ERASE T                                  | IME                                     |            |                                       |            |             | · · · · · · · · · · · · · · · · · · |  |

| TE (1                                        | 1S)                                      |                                         |            |                                       |            |             |                                     |  |

| 0.25                                         | XXXXXXX                                  | xxxxxxxxx                               | (XXXXXXXXX | xxxxxxxxxx                            | (XXXXXXXXX | «xxxxx      |                                     |  |

| 0.50                                         | XXXXXXX                                  | XXXXXXXXXXX                             | XXXXXXXXX  | XXXXXXXXXX                            | (XXXXXXXX  | XXXXX       |                                     |  |

| 0.75                                         | XXXXXXX                                  | XXXXXXXXXX                              | XXXXXXXX   | XXXXXXXXXX                            | (XXXXXXXXX | XXXXX       |                                     |  |

| 1.00                                         | XXXXXXX                                  | XXXXXXXXXX                              | XXXXXXXXX  | XXXXXXXXXX                            | (XXXXXXXXX | XXXXXX      |                                     |  |

| 1.25                                         | XXXXXXX                                  | XXXXXXXXXX                              | XXXXXXXXX  | XXXXXXXXXX                            | (XXXXXXXXX | XXXXX       |                                     |  |

| 1.50                                         | XXXXXXX                                  | XXXXXXXXXX                              | XXXX       |                                       |            |             |                                     |  |

| 175                                          | XXXXXX.                                  |                                         |            | • • • • • • • • • •                   |            |             |                                     |  |

| 2.00                                         | XXXXXX.                                  |                                         |            | • • • • • • • • • •                   |            |             |                                     |  |

| 2.25                                         |                                          | * * * * * * * * * * * *                 |            |                                       |            |             |                                     |  |

|                                              |                                          | • • • • • • • • • •                     |            |                                       |            |             |                                     |  |

| 2.50                                         | XXXXXX.                                  | * * * * * * * * * * *                   |            |                                       |            |             |                                     |  |

| 2.50<br>2.75                                 |                                          |                                         |            |                                       |            |             |                                     |  |

| 2.50<br>2.75<br>3.00                         | XXXXXX.                                  |                                         |            |                                       |            |             |                                     |  |

| 2.50<br>2.75<br>3.00<br>3.25                 | XXXXXX.                                  |                                         |            |                                       |            |             | ,                                   |  |

| 2.50<br>2.75<br>3.00<br>3.25<br>3.50         | XXXXXX.<br>XXXXXX.                       | * * * * * * * * * * * * * * * * * * * * |            | • • • • • • • • • • •                 |            |             | ,                                   |  |

| 2.50<br>2.75<br>3.00<br>3.25<br>3.50<br>3.75 | XXXXXX .<br>XXXXXX .<br>XXXXXX .         | · · · · · · · · · · · · · · · · · · ·   |            | · · · · · · · · · · · · · · · · · · · |            |             | ,                                   |  |

| 2.50<br>2.75<br>3.00<br>3.25<br>3.50         | XXXXXX XXXXX XXXXXX XXXXXX XXXXXX XXXXXX |                                         |            | • • • • • • • • • • • • • • • • • • • |            | • • • • • • | •                                   |  |

| 2.50<br>2.75<br>3.00<br>3.25<br>3.50<br>3.75 | XXXXXX XXXXX XXXXXX XXXXXX XXXXXX XXXXXX | · · · · · · · · · · · · · · · · · · ·   |            | • • • • • • • • • • • • • • • • • • • |            | • • • • • • | ,                                   |  |

### CHARACTERIZZATION RESULTS

| Parameter           | Value |       | Measurement | - Limit | Unit      |      |

|---------------------|-------|-------|-------------|---------|-----------|------|

|                     | value | 0°C   | 25°C        | 70°C    | Littill   | Unit |

| I <sub>CC1</sub>    | min   | 1.1   | 1.2         | 1.1     |           |      |

|                     | typ.  | 1.53  | 1.53        | 1.47    | <5 mA     | mA   |

|                     | max   | 2.0   | 2.0         | 1.9     |           |      |

| ICC2                | min   | 1.1   | 1.1         | 1.1     |           |      |

|                     | typ.  | 1.48  | 1.45        | 1.39    | <3 mA     | mA   |

|                     | max   | 2.0   | 2.0         | 1.8     |           |      |

| Іссз                | min   | 2.0   | 2.0         | 1.9     |           |      |

|                     | typ.  | 2.76  | 2.58        | 2.38    | <6 mA     | mA   |

|                     | max   | 3.5   | 3.4         | 3.0     |           |      |

| VoH                 | min   | 2.83  | 2.84        | 2.84    |           |      |

|                     | typ.  | 2.89  | 2.90        | 2.91    | >2.4 V    | V    |

|                     | max   | 3.00  | 3.03        | 3.03    |           |      |

| VoL                 | min   | 0.063 | 0.065       | 0.069   |           |      |

|                     | typ.  | 0.066 | 0.071       | 0.077   | <0.4 V    | V    |

|                     | max   | 0.070 | 0.077       | 0.082   |           |      |

| VCC MIN             | min   |       | 3.50        | 3.40    |           |      |

|                     | typ.  |       | 3.65        | 3.63    | >4.5 V    | V.   |

|                     | max   |       | 3.90        | 3.90    |           |      |

| PW CK MIN.          | min   |       | 450         | 500     |           |      |

|                     | typ.  |       | 657         | 682     | >1.000 ns | ns   |

|                     | max   |       | 850         | 850     |           |      |

| T-ERA MIN.          | min   |       | 1.75        | 2.00    |           |      |

|                     | typ.  |       | 2.01        | 2.28    | 5 ÷ 30 ms | ms   |

|                     | max   |       | 2.50        | 2.75    |           |      |

| T-WRI MIN.          | min   |       | 1.50        | 1.75    | 777       |      |

|                     | typ.  |       | 1.80        | 2.03    | 5 ÷ 30 ms | ms   |

|                     | max   |       | 2.25        | 2.50    |           |      |

| V <sub>CC MAX</sub> |       |       | >8 V        | >8 V    | < 5.5 V   | V    |

## **BUILD ASSEMBLY INFORMATION**

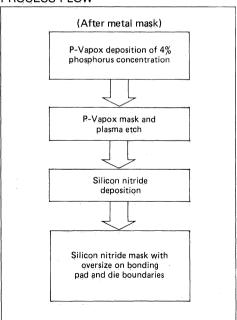

## DOUBLE LAYER P-VAPOX AND Si<sub>3</sub>N<sub>4</sub> GLASS PASSIVATION

A. Panchieri Q.A. MOS DIVISION

Newly developed passivation process for NMOS/HS-CMOS devices gives improved protection to die encapsulated in plastic packages.

#### PROCESS DESCRIPTION

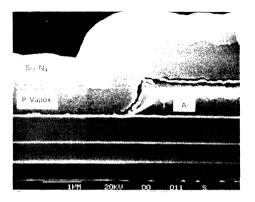

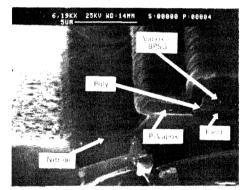

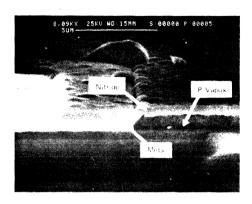

The process consists of a two layer film of P-Vapox (phosphorus doped silicon oxide) and  $Si_3\ N_4$  (silicon nitride), obtained by two different masking and etching steps to avoid defects caused by lack of dieletric integrity.

The process gives good metal step coverage together with PECVD (Plasma Enhanced Chemical Vapox Deposition) to avoid cracking near metal edge and possible hillocks defects.

The double layer enables us, by means of an appropriate oversize either at the boundaries of the die side or at the bonding pad side, to ensure full sealing of the underlying P-Vapox layer.

This prevents the layer from being exposed to moisture coming from the package. Thus the probability of metal corrosion on the bonding pad due to phosphoric acid is drastically reduced.

As a result the die is provided with a very good humidity immunity.

#### PROCESS FLOW

FIG. 1 - TYPICAL MICROSECTION OF DEVICE WITH NITRIDE PASSIVATION

FIG. 2 - SECTION ALONG THE SCRIBING LINE.

FIG. 3 - SECTION ALONG THE PAD

#### RELIABILITY RESULTS

The reliability performance in moist ambient was evalued using both 85°C/85% RH/BIAS and 121°C Pressure Pot test

Different products in different plastic packages were tested.

To give an idea of reliability performances obtained on products with the new passivation process, we have set out the process qualification test results in the following table:

|                                | HS-CMOS LOGICS |        |          | μPROCESSORS |          | MEMORIES |      |

|--------------------------------|----------------|--------|----------|-------------|----------|----------|------|

|                                | HOURS          | SAMPLE | FAIL     | SAMPLE      | FAIL     | SAMPLE   | FAIL |

| STATIC/DYNAMIC                 | 1000           | 1355   | 0        | 385         | 0        | 270      | 0    |

| LIFE TEST                      | 2000           | 915    | 0        | 385         | 0        | 270      | 0    |

| T <sub>amb</sub> = 125°C       | 3000           | 600    | 0        | _           | <u> </u> |          | _    |

| V <sub>CC</sub> = STD          | 4000           | 600    | Q        | _           | _        | _        | _    |

| TEMP HUMIDITY                  | 1000           | 740    | 0        | 240         | 0        | 360      | 0    |

| BIAS (85°C/85% RH)             | 2000           | 510    | 0        | 240         | 0        | 360      | 0    |

| V <sub>CC</sub> = STD          | 3000           | 260    | 1 funct. | _           | _        | _        | _    |

|                                | 4000           | 259    | 0        | `-          | _        | _        | _    |

| PRESSURE POT                   | 96             | 965    | 0        | 540         | 0        | 250      | 0    |

| T <sub>amb</sub> = 121°C-2 atm | 144            | 775    | 1 funct. | 540         | 0        | 250      | 0    |

|                                | 192            | 320    | 0        | 300         | 0        | 120      | 0    |

|                                | 288            | 320    | 0        | 300         | 1 funct. | 120      | 0    |

ERASABLE PROVESANIVA ELEGADIONES NUEVO EN CONTROLLA DE CO

# 16K (2K×8) UV ERASABLE PROM

- FAST ACCESS TIME: 350ns MAX M2716-1 450ns MAX M2716

- SİNGLE +5V POWER SUPPLY

- LOW POWER DISSIPATION:

525 mW MAX. ACTIVE POWER

132 mW MAX. STANDBY POWER

- SIMPLE PROGRAMMING REQUIREMENTS

SINGLE LOCATION PROGRAMMING

PROGRAMS WITH ONE 50 ms PULSE

- INPUTS AND OUTPUTS TTL COMPATIBLE DURING READ PROGRAM

- COMPLETELY STATIC

- EXTENDED TEMPERATURE RANGE

### DESCRIPTION

The M2716 is a 16.384-bit ultraviolet erasable and electrically programmable read-only memory (EPROM). The M2716 operates from a single - 5V power supply, has a static standby mode, and features fast single address location programming. It makes designing with EPROMs faster, easier and more economical. The M2716, with its single 5-volt supply and with an access time up to 350ns, is ideal for use with the newer high performance +5V microprocessor such as the Z8® . Z80® Z8000TM. The M2716P is also the first EPROM with a static standby mode which reduces the power dissipation without increasing access time. The maximum active power dissipation is 525 mW while the maximum standby power dissipation is only 132 mW, a 75% savings.

The M2716 has the simplest and fastest method yet devised for programming EPROMs — single pulse TTL level programming. No need for high voltage pulsing because all programming controls are handled by TTL signals. Program any location at any time-either individually, sequentially or at random, with the M2716's single address location programming. Total programming time for all 16.384 bits is only 100 seconds:

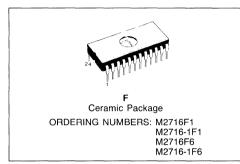

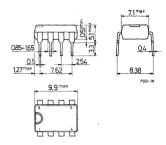

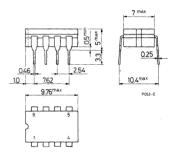

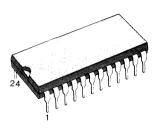

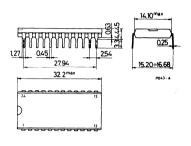

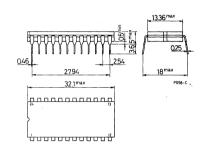

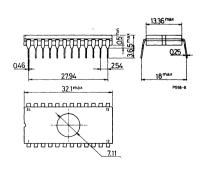

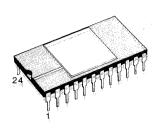

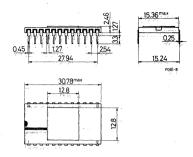

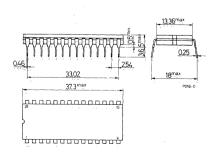

The M2716 is available in 24-lead dual in-line ceramic package glass lens (frit-seal)

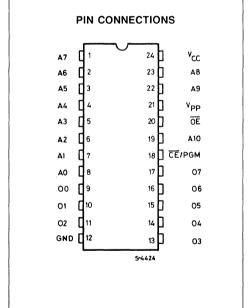

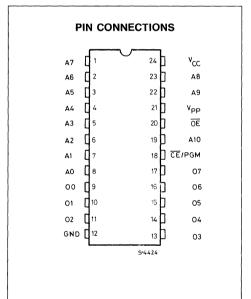

### **PIN NAMES**

| A0-A10 | ADDRESSES           |

|--------|---------------------|

| CE/PGM | CHIP ENABLE/PROGRAM |

| ŌĒ     | OUTPUT ENABLE       |

| 00-07  | OUTPUTS             |

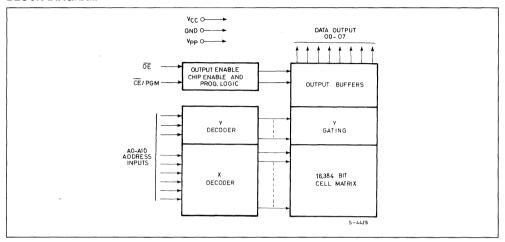

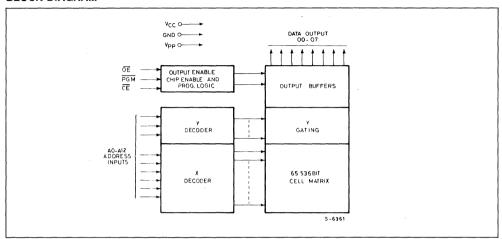

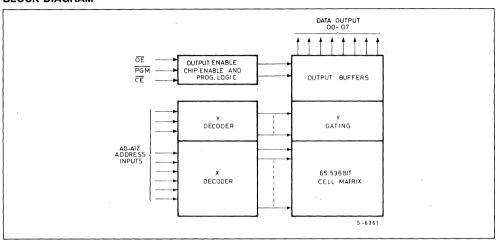

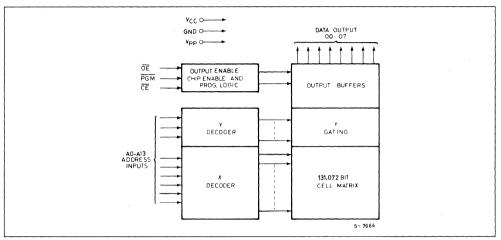

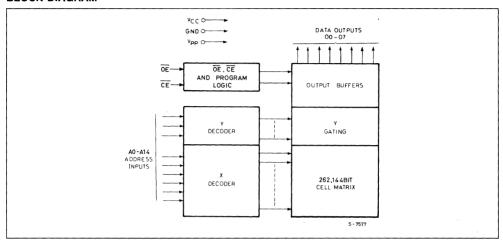

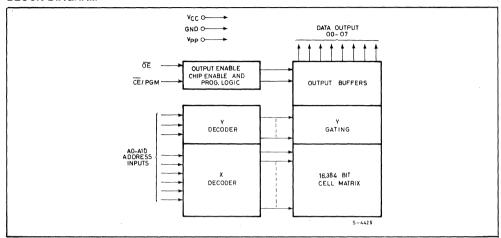

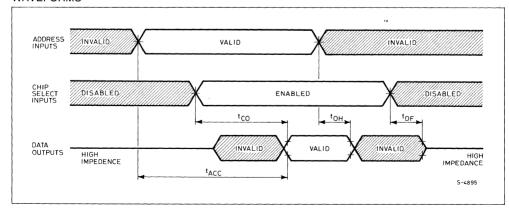

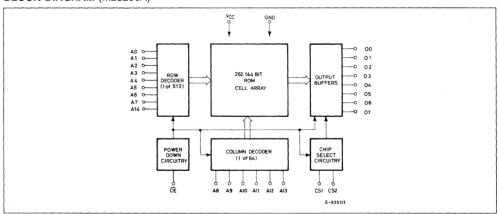

### **BLOCK DIAGRAM**

### ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                            | Value                    | Unit |

|------------------|------------------------------------------------------|--------------------------|------|

| VI               | All Input or Output voltages with respect to ground  | + 6 to - 0.3             | V    |

| V <sub>PP</sub>  | Supply voltage with respect to ground during program | +26.5 to - 0.3           | V    |

| T <sub>amb</sub> | Ambient temperature under bias: standard extended    | 0 to + 70<br>-40 to + 85 | °C   |

| T <sub>stg</sub> | Storage temperature range                            | -65 to +125              | °C   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **OPERATING MODES**

| PINS            | CE/PGM<br>(18)                           | OE<br>(20)      | V <sub>PP</sub> (21) | V <sub>CC</sub><br>(24) | OUTPUTS<br>(9-11, 13-17) |

|-----------------|------------------------------------------|-----------------|----------------------|-------------------------|--------------------------|

| READ            | V <sub>IL</sub>                          | V <sub>IL</sub> | + 5                  | +5                      | D <sub>OUT</sub>         |

| STANDBY         | $V_{IH}$                                 | Don't Care      | + 5                  | +5                      | HIGH Z                   |

| PROGRAM         | Pulse V <sub>IL</sub> to V <sub>IH</sub> | V <sub>IH</sub> | + 25                 | +5                      | D <sub>IN</sub>          |

| PROGRAM VERIFY  | $V_{IL}$                                 | V <sub>IL</sub> | + 25                 | +5                      | D <sub>OUT</sub>         |

| PROGRAM INHIBIT | V <sub>IL</sub>                          | V <sub>IH</sub> | + 25                 | +5                      | HIGH Z                   |

**Note:** The five modes of operation of the M2716P are listed in this table. It should be noted that all inputs for the five modes are at TTL levels. The power supplies required are a +5V V<sub>CC</sub> and a V<sub>PP</sub> power supply must be at 25V during the three programming modes, and must be at 5V in the other two modes.

### **READ OPERATION**

### DC AND AC OPERATING CONDITIONS

|                                    | M2716F1          | M2716-1F1            | M2716F6               | M2716-1F6        |

|------------------------------------|------------------|----------------------|-----------------------|------------------|

| Operating Temperature Range        | 0 to 70°C        | 0 to 70°C            | -40 to 85°C           | - 40 to 85°C     |

| V <sub>CC</sub> Power Supply (1,2) | 5V ±5%           | 5V ±10%              | 5V ±5%                | 5V ±10%          |

| V <sub>PP</sub> Power Supply (2)   | $V_{CC} \pm 0.6$ | V <sub>CC</sub> ±0.6 | V <sub>CC</sub> ± 0.6 | $V_{CC} \pm 0.6$ |

### DC AND OPERATING CHARACTERISTICS

| Symbol              | Parameter                                | Test Conditions                           | Min. | Тур. (3) | Max.                | Unit |

|---------------------|------------------------------------------|-------------------------------------------|------|----------|---------------------|------|

| ILI                 | Input Load Current                       | V <sub>I</sub> = 5.25V                    |      |          | 10                  | μА   |

| ILO                 | Output Leakage Current                   | V <sub>O</sub> = 5.25V                    |      |          | 10                  | μА   |

| I <sub>PP1(2)</sub> | V <sub>PP</sub> = 5.25V                  |                                           |      |          | 5                   | mA   |

| I <sub>CC1(2)</sub> | V <sub>CC</sub> Supply Current (Standby) | CE = V <sub>IH</sub> OE = V <sub>IL</sub> |      | 10       | 25                  | mA   |

| I <sub>CC2(2)</sub> | V <sub>CC</sub> Supply Current (Active)  | $\overline{OE} = \overline{CE} = V_{IL}$  |      | 57       | 100                 | mA   |

| VIL                 | Input Low Voltage                        |                                           | -0.1 |          | 0.8                 | ٧.   |

| V <sub>IH</sub>     | Input High Voltage                       |                                           | 2.0  |          | V <sub>CC</sub> + 1 | ٧    |

| V <sub>OL</sub>     | Output Low Voltage                       | I <sub>OL</sub> = 2.1 mA                  |      |          | 0.45                | V    |

| V <sub>OH</sub>     | Output High Voltage                      | $I_{OH} = -400 \ \mu A$                   | 2.4  |          |                     | ٧    |

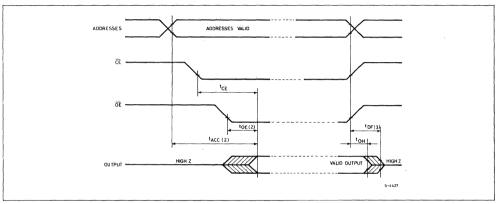

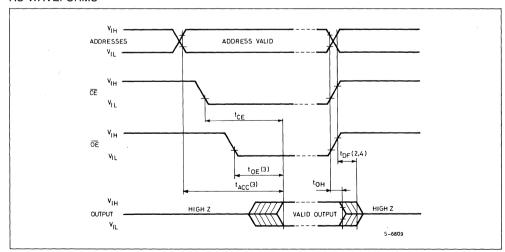

### **AC CHARACTERISTICS**

|                    |                                                            | Test                                     | M2716 |     | M2716-1 |     |      |

|--------------------|------------------------------------------------------------|------------------------------------------|-------|-----|---------|-----|------|

| Symbol             | Parameter                                                  | Conditions                               | Min   | Max | Min     | Max | Unit |

| t <sub>ACC</sub>   | Address to Output Delay                                    | $\overline{CE} = \overline{OE} = V_{IL}$ |       | 450 |         | 350 | ns   |

| t <sub>CE</sub>    | CE to Output Delay                                         | $\overline{OE} = V_{IL}$                 |       | 450 |         | 350 | ns   |

| toE                | OE to Output Delay                                         | CE = V <sub>IL</sub>                     |       | 120 |         | 120 | ns   |

| t <sub>DF(4)</sub> | OE High to Output Float                                    | CE = V <sub>IL</sub>                     | 0     | 100 | 0       | 100 | ns   |

| t <sub>OH</sub>    | Output Hold from Address CE or OE Whichever Occurred First | CE = OE = V <sub>IL</sub>                | 0     |     | 0       |     | ns   |

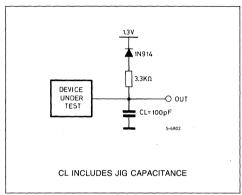

# CAPACITANCE<sup>(4)</sup> (T<sub>amb</sub> = 25°C, f = 1 MHz)

| Symbol           | Parameter          | Test Conditions     | Min. | Тур. | Max. | Unit |

|------------------|--------------------|---------------------|------|------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>1</sub> = 0V |      | 4    | 6    | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>O</sub> = 0V |      | 8    | 12   | pF   |

V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

V<sub>PP</sub> may be connected directly to V<sub>CC</sub> except during programming.

The supply current would then be the sum of I<sub>CC</sub> and I<sub>PP1</sub>.

Typical values are for T<sub>amb</sub> = 25°C and nominal supply voltages.

This parameter is only sampled and not 100% tested. Notes:

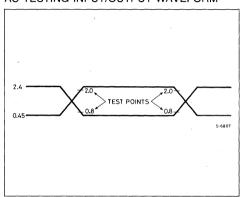

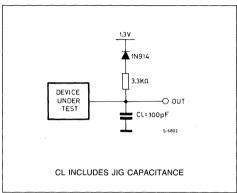

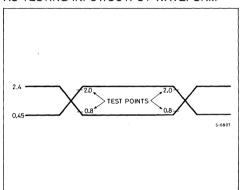

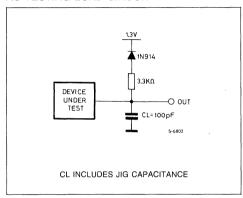

### AC TEST CONDITIONS

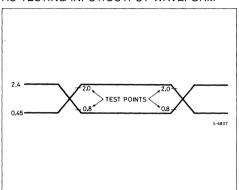

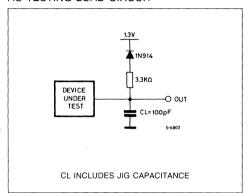

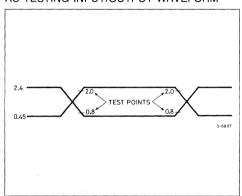

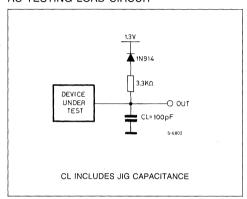

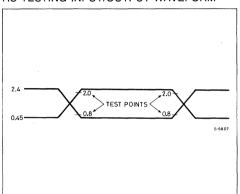

Output Load: 100pF + 1TTL Gate Input Rise and Fall Times: ≤ = 20ns Input Pulse Levels: 0.8 to 2.2V

Timing Measurement Reference Levels: Inputs 1 and 2V Outputs 0.8 and 2V

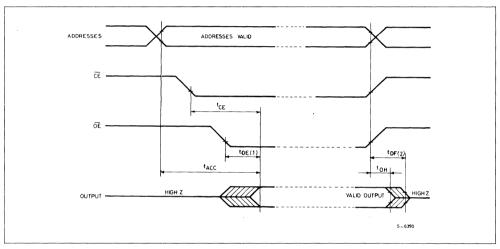

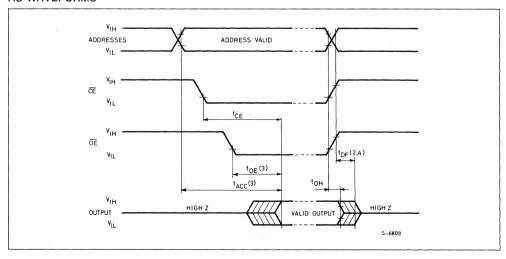

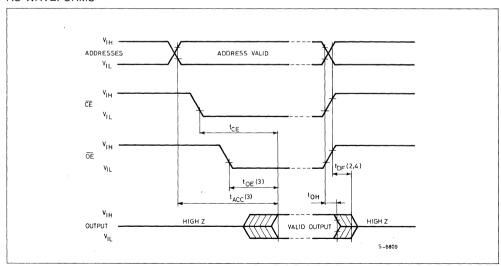

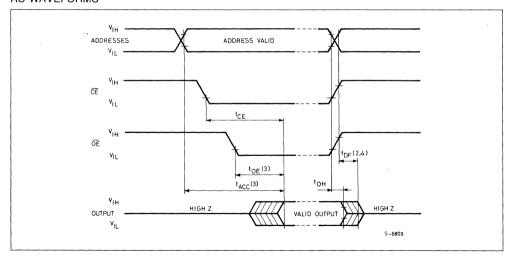

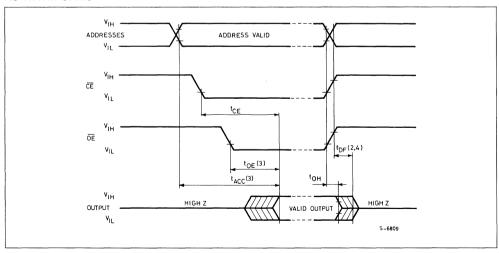

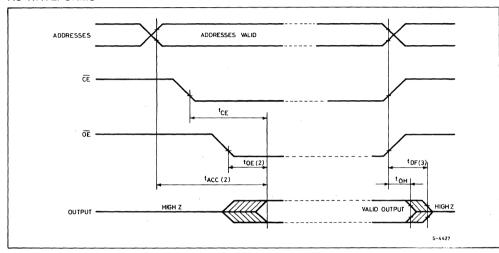

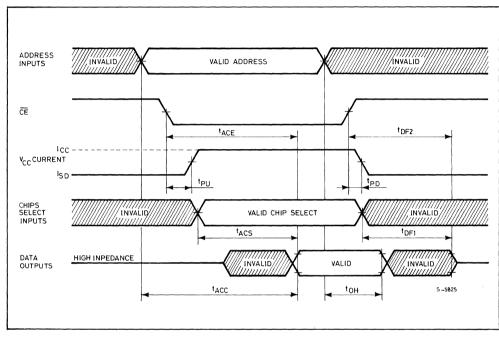

### AC WAVEFORMS

### Notes:

- 1. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

- OE may be delayed up to t<sub>ACC</sub> t<sub>OE</sub> after the falling edge CE without impact on t<sub>ACC</sub>.

t<sub>DE</sub> is specified from OE or CE whichever occurs first.

### READ MODE

The M2716 has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable (CE) is the power control and should be used for device selection. Output Enable (OE) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time (tACC) is equal to the delay from CE to output (tce). Data is available at the outputs 120 ns (top) after the falling edge of OE, assuming that CE has been low and addresses have been stable for at least tACC-tOF.

### STANDBY MODE

The M2716 has a standby mode which reduces the active power dissipation by 75%, from 525mW to 132mW. The M2716 is placed in the standby mode by applying a TTL high signal to CE input. When in standby mode, the output are in a high impedance state, independent of the OE input.

### **OUTPUT OR-TIEING**

Because M2716's are usually used in larger memory arrays, the product has 2 line control function that accommodates this use of multiple memory connection. The two line control function allows for:

- a) the lowest possible memory power dissipation

- b) complete assurance that output bus contention will not ouccur.

To most efficiently use these two control lines, it is recommended that CE be decoded and used as the primary device selecting function, while OE (pin 20) be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low power standby mode and the output pins are only active when data is desired from a particular memory device.

### **PROGRAMMING OPERATION** (1) $(T_{amb} = 25 ^{\circ}C \pm 5\%, V_{CC}^{(2)} = 5V \pm 5\%, V_{PP}^{(2,3)} = 25V \pm 1V)$

### DC AND OPERATING CHARACTERISTIC:

| Cumbal           | Parameter                                                  | Test Conditions             | Values |      |                     | l    |

|------------------|------------------------------------------------------------|-----------------------------|--------|------|---------------------|------|

| Symbol           |                                                            | rest Conditions             | Min.   | Тур. | Max.                | Unit |

| I <sub>LI</sub>  | Input Current (for Any Input)                              | V <sub>I</sub> = 5.25V/0.45 |        |      | 10                  | μΑ   |

| $V_{IL}$         | Input Low Level                                            |                             | - 0.1  |      | 0.8                 | V    |

| V <sub>IH</sub>  | Input High Level                                           |                             | 2.0    |      | V <sub>CC</sub> + 1 | V    |

| I <sub>CC</sub>  | V <sub>CC</sub> Supply Current                             |                             |        |      | 100                 | mA   |

| I <sub>PP1</sub> | V <sub>PP</sub> Supply Current                             | CE/PGM = V <sub>IL</sub>    |        |      | 5                   | mA   |

| I <sub>PP2</sub> | V <sub>PP</sub> Supply Current During<br>Programming Pulse | CE/PGM =V <sub>IH</sub>     |        |      | 30                  | mA   |

### AC CHARACTERISTICS

| Cumbal           | Barrandari                          | Test Conditions          | Values |      |      |      |

|------------------|-------------------------------------|--------------------------|--------|------|------|------|

| Symbol           | Parameter                           | rest Conditions          | Min.   | Тур. | Max. | Unit |

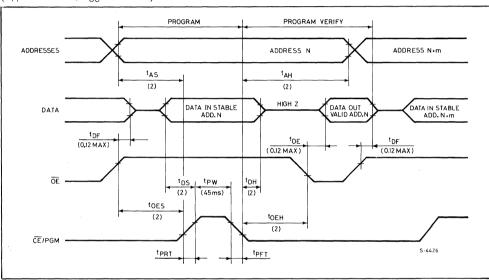

| t <sub>AS</sub>  | Address Setup Time                  |                          | 2      |      |      | μS   |

| toes             | OE Setup Time                       |                          | 2      |      |      | μS   |

| t <sub>DS</sub>  | Data Setup Time                     |                          | 2      |      |      | μS   |

| t <sub>AH</sub>  | Address Hold Time                   |                          | 2      |      |      | μS   |

| tOEH             | OE Hold Time                        |                          | 2      |      |      | μS   |

| t <sub>DH</sub>  | Data Hold Time                      |                          | 2      |      |      | μS   |

| t <sub>DF</sub>  | Output Enable to Output Float Delay | OE/PGM = V <sub>IL</sub> | 0      |      | 120  | ns   |

| t <sub>OE</sub>  | Output Enable to Output Delay       | CE/PGM = V <sub>IL</sub> |        |      | 120  | νS   |

| t <sub>PW</sub>  | Program Pulse Width                 |                          | 45     | 50   | 55   | ms   |

| t <sub>PRT</sub> | Program Pulse Rise Time             |                          | 5      |      |      | ns   |

| t <sub>PFT</sub> | Program Pulse Fall Time             |                          | 5      |      |      | νS   |

**CAUTION:** The  $V_{CC}$  and  $V_{PP}$  supplied must be sequenced on and off such that  $V_{CC}$  is applied simultaneosly or before  $V_{PP}$  and removed simultaneosly or after  $V_{PP}$  to prevent damage to the M2716. The maximum allowable voltage during programming which may be applied to the  $V_{PP}$  with respect to ground is + 26V. Care must be taken when switching the  $V_{PP}$  supply to prevent overshoot exceeding the 26-volt maximum specification. For convenience in programming, the M2716 may be verified with the  $V_{PP}$  supply at 25V  $\pm$  1V. During normal read operation, however,  $V_{PP}$  must be at  $V_{CC}$ .

### Notes:

<sup>1.</sup> SGS guarantees the product only if it is programmed to specifications described herein.

V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>. The M2716 must not be inserted into

or removed from a board with V<sub>PP</sub> at 25±1V to prevent damage to the device.

The maximum allowable voltage which may be applied to the V<sub>PP</sub> pin during programming is + 26V. Care must be taken when switching the V<sub>PP</sub> supply to prevent overshoot exceeding this 26V maximum specification.

### AC TEST CONDITIONS

$V_{CC}$  = 5V  $\pm$ 5%  $V_{PP}$  = 25V  $\pm$ 1V Input Rise and Fall Times (10% to 90%) = 20 ns Input Pulse Levels = 0.8V to 2.2V

Input Timing Reference Level = 1V and 2V

Output Timing Reference Level = 0.8V and 2V

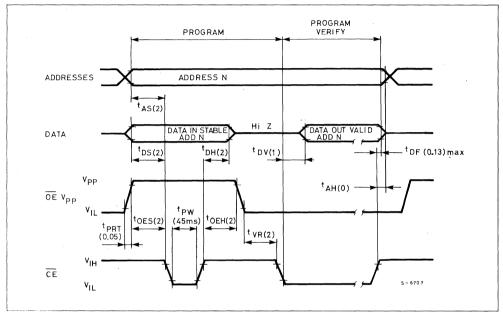

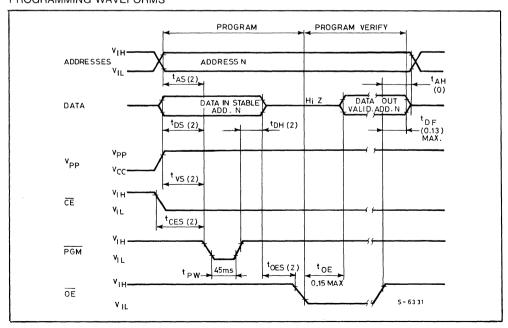

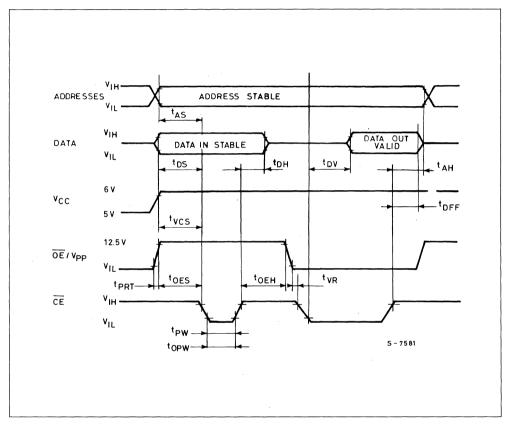

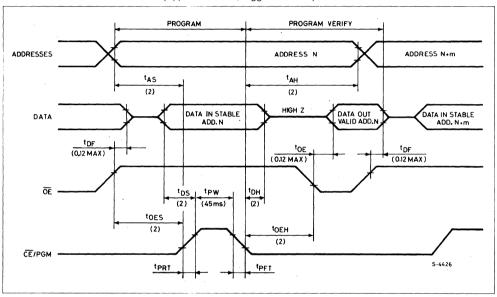

### PROGRAMMING WAVEFORMS

$(V_{PP} = 25V \pm 1V, V_{CC} = 5V \pm 5\%)$

Note: All times shown in parentheses are minimum times and are used unless otherwise noted.

### PROGRAMMING

Initially, and after each erasure, all bits of the M2716 are in the "1" state. Data is introduced by selectively programming "0's" into the desired bit locations. Although only "0's" will be programmed, both "1's" and "0's" can be presented in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure. The M2716 is in the programming mode when the V<sub>PP</sub> power supply is at 25V and OE is at VIH. The data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL. When the address and data are stable, a 50 msec, active high, TTL program pulse is applied to the CE/PGM input. A program pulse must be applied at each address location to be programmed. You can program any location at any time - either individually, sequentially, or at random. The program pulse has a maximum width of 55 msec. The M2716 must not be programmed with a DC signal applied to the CE/PGM input. Programming of multiple M2716s in parallel with the same data can be easily accomplished due to the simplicity of the programming requirements. Like inputs of the paralleled M2716s may be connected together when they are programmed with the same data. A high level TTL pulse applied to the CE/PGM input-programs the parallel M2716s.

### PROGRAM INHIBIT

Programming of multiple M2716s in parallel with different data is also easily accomplished. Except for  $\overline{\text{CE}}/\text{PGM}$ , all like inputs (including  $\overline{\text{OE}}$ ) of the parallel M2716s may be common. A  $\overline{\text{TTL}}$  level program pulse applied to a M2716's  $\overline{\text{CE}}/\text{PGM}$  input with  $\overline{\text{V}}_{\text{PP}}$  at 25V will program that M2716. A low level  $\overline{\text{CE}}/\text{PGM}$  input inhibits the other M2716 from beign programmed.

### PROGRAM VERIFY

A verify should be performed on the programmed bits to determine that they were correctly programmed. The verify may be performed with  $V_{PP}$  at 25V. Except during programming and program verify,  $V_{PP}$  must be at 5V.

### **ERASURE OPERATION**

The erasure characteristics of the M2716 are such that erasure begins to occur when exposed to light with wavelengths shorter than approximately 4000 Angstroms (A). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000-4000 A range. Data show that constant exposure to room level fluorescent lighting could erase the typical M2716 in approximately 3 years, while it would take approximately

1 week to cause erasure when exposed to direct sunlight. If the M2716 is to be exposed to these types of lighting conditions for extended periods of time, it is suggested to put opaque labels over the M2716 window to prevent unintentional erasure.

The recommended erasure procedure for the M2716 is exposure to shortware ultraviolet light which has a wavelength of 2537 Angstroms (A). The integrated dose (i.e. UV intensity X exposure time for erasure should be a minimum of 15 W-sec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 12000  $\mu$  W/cm² power rating. The M2716 should be placed within 2.5 cm of the lamp tubes during erasure. Some lamps have a filter on their tubes which should be removed before erasure.

# 32K (4K×8) UV ERASABLE PROM

- FAST ACCESS TIME:

200ns MAX M2732A-2F1

250ns MAX M2732AF1/M2732AF6

300ns MAX M2732A-3F1

450ns MAX M2732A-4F1/M2732A-4F6

- SINGLE +5V POWER SUPPLY

- LOW STANDBY CURRENT 35mA MAX

- INPUTS AND OUTPUTS TTL COMPATIBLE DURING READ AND PROGRAM

- COMPLETELY STATIC

### DESCRIPTION

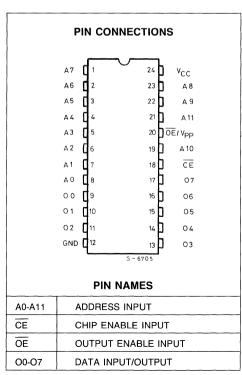

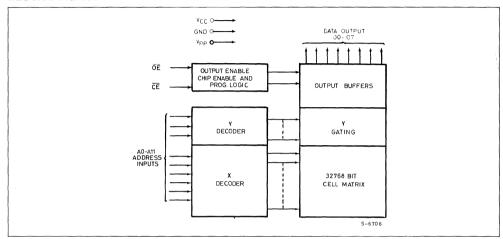

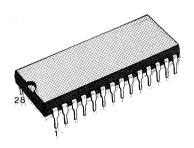

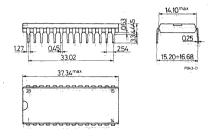

The M2732A is a 32,768-bits ultraviolet erasable and electrically programmable read-only memory (EPROM). It is organized as 4,096 words by 8 bits and manufactured using SGS' N-channel Si-Gate MOS process. The M2732A with its single +5V power supply and with an access time of 200ns, is ideal for use with the high performance +5V microprocessors such as the Z8® , Z80® and Z8000™. The M2732A has an important feature which is the separate output control, Output Enable (OE) from the Chip Enable control (CE). The OE control elimitates bus contention in multiple bus microprocessor systems.

The M2732A also features a standby mode which reduces the power dissipation without increasing access time. The active current is 125 mA while the maximum standby current is only 35 mA a 70% saving. The standby mode is achieved by applying a TTL-high signal to the CE input.

The M2732A is available in a 24-lead dual in-line ceramic package glass lens (frit-seal).

45

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                               | Value                        | Unit |

|------------------|---------------------------------------------------------|------------------------------|------|

| VI               | All Input or Output voltages with respect to ground     | + 6 to -0.6                  | V    |

| V <sub>PP</sub>  | Supply voltage with respect to ground during program    | +22 to -0.6                  | ۸ 3  |

| T <sub>amb</sub> | Ambient temperature under bias F1/-2F1/-3F1/-4F1 F6/4F6 | - 10 to + 80<br>- 50 to + 95 | °C   |

| T <sub>stg</sub> | Storage temperature range                               | -65 to + 125                 | °C   |