# Signetics

## 8X3O5 Users Manual

## 8X305 Users Manual

June 1982

Signetics reserves the right to make changes in the products contained in this book in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and Signetics makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of Signetics is prohibited.

**BIPOLAR LSI DIVISION**

USERS MANUAL 8X305

## **TABLE OF CONTENTS**

| 1 | INT | RODUCTION                                                                     |    |

|---|-----|-------------------------------------------------------------------------------|----|

|   | 1.1 | DEVICE DESCRIPTION                                                            |    |

|   | 1.2 | DEVICE ARCHITECTURE                                                           |    |

|   | 1.3 | PIN DESCRIPTION                                                               |    |

|   |     | THE INTERFACE VECTOR BUS                                                      |    |

|   |     | SYSTEM ENVIRONMENT                                                            |    |

|   | 1.5 | STOTEM ENVIRONMENT                                                            | •  |

| 2 | FUI | NCTIONAL OPERATION                                                            | •  |

|   | 2.1 | HARDWARE COMPONENT BLOCKS                                                     |    |

|   |     | 2.1.1 Oscillator and Timing Generator                                         |    |

|   |     | 2.1.2 Program Address Logic         2.1.3 Decode and Control Logic            |    |

|   |     | 2.1.4 Arithmetic Logic Unit                                                   | 8  |

|   |     | 2.1.5 Bit Manipulation Logic       2.1.6 Registers (Internal Working Storage) | 4. |

|   |     | 2.1.7 IV Bus Control                                                          |    |

|   | 22  | BASIC INSTRUCTION CYCLE                                                       |    |

|   |     | THE INSTRUCTION FORMAT                                                        |    |

|   | 2.0 | 2.3.1 General Formats                                                         |    |

|   |     | 2.3.2 Instruction Fields                                                      |    |

|   |     | 2.3.3 Source and Destination Fields         2.3.4 Rotate and Length Field     | 14 |

|   |     | 2.3.5 Instruction Sequence Control                                            | 14 |

|   | 2.4 | DATA FLOW DURING INSTRUCTION EXECUTION                                        |    |

|   |     | 2.4.1 Operations That Use Format RR                                           | 16 |

|   |     | 2.4.2 Operations That Use Format RB                                           |    |

|   |     | 2.4.4 Operations That Use Format XR                                           |    |

|   |     | 2.4.5 Operations That Use Format JB                                           | 28 |

|   |     | 2.4.6 Operations That Use Format XB2.4.7 Operations That Use Format JA        | 30 |

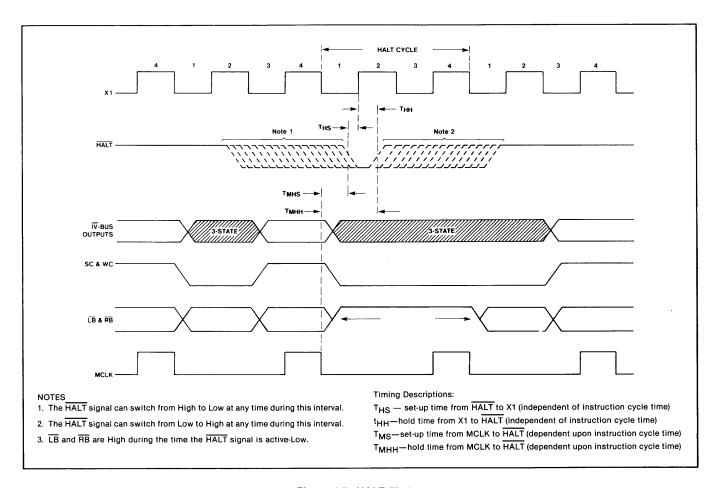

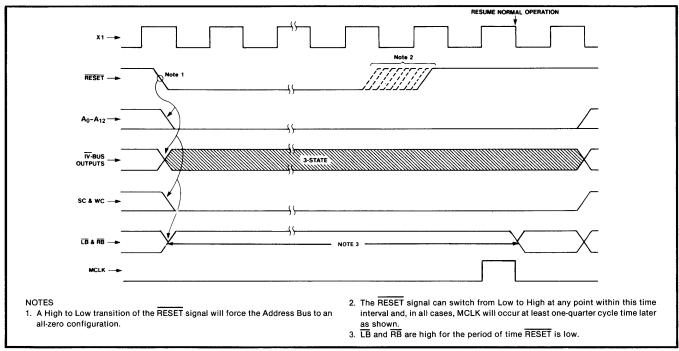

|   | 2.5 | HALT AND RESET OPERATIONS                                                     |    |

|   | 2.5 | TALL AND RESEL OPERATIONS                                                     | 32 |

| 3 | INS | TRUCTION SET                                                                  | 33 |

|   | 3.1 | MOVE INSTRUCTIONS                                                             |    |

|   |     | 3.1.1 MOVE-Register, Register                                                 |    |

|   |     | 3.1.2 MOVE-Register, IV Bus Address                                           |    |

|   |     | 3.1.4 MOVE-IV Bus, Register                                                   | 37 |

|   |     | 3.1.5 MOVE-IV Bus, IV Bus                                                     |    |

|   |     |                                                                               |    |

|   |     | ADD INSTRUCTIONS 3.2.1 ADD-Register, Register                                 |    |

|   |     | 3.2.2 ADD-Register, IV Bus Address                                            |    |

|   |     | 3.2.3 ADD-Register, IV Bus                                                    | 41 |

|   |     | 3.2.4 ADD-IV Bus, Register                                                    |    |

|   |     | 3.2.6 ADD-IV Bus, IV Bus Address                                              |    |

|     | AND INSTRUCTIONS  3.3.1 AND-Register, Register  3.3.2 AND-Register, IV Bus Address  3.3.3 AND-Register, IV Bus  3.3.4 AND-IV Bus, Register  3.3.5 AND-IV Bus, IV Bus  3.3.6 AND-IV Bus, IV Bus Address | . 44<br>. 45<br>. 45<br>. 46<br>. 46 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|     | XOR INSTRUCTIONS  3.4.1 XOR-Register, Register  3.4.2 XOR-Register, IV Bus Address  3.4.3 XOR-Register, IV Bus  3.4.4 XOR-IV Bus, Register  3.4.5 XOR-IV Bus, IV Bus  3.4.6 XOR-IV Bus, IV Bus Address | . 48<br>. 49<br>. 49<br>. 50         |

| 3.5 | XEC INSTRUCTIONS. 3.5.1 XEC-Register. 3.5.2 XEC-IV Bus                                                                                                                                                 | . 52                                 |

|     | NZT INSTRUCTIONS                                                                                                                                                                                       | . 54<br>. 54                         |

| 3.7 | XMIT INSTRUCTIONS  3.7.1 XMIT-Register  3.7.2 XMIT-Register, IV Bus  3.7.3 XMIT-IV Bus  3.7.4 XMIT-IV Bus Address                                                                                      | . 56<br>. 56<br>. 57                 |

| 3.8 | JMP INSTRUCTION                                                                                                                                                                                        | . 58                                 |

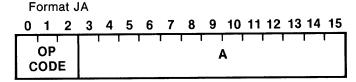

| 4 T | IMING                                                                                                                                                                                                  | . 61                                 |

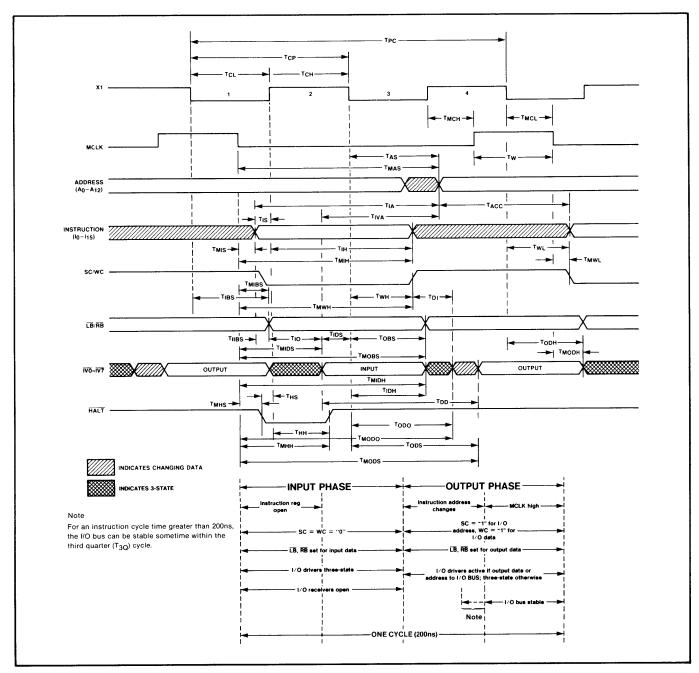

| 4.1 | CLOCK GENERATION                                                                                                                                                                                       | . 62<br>. 62<br>. 62                 |

| 4.2 | BASIC CYCLE TIMING                                                                                                                                                                                     | . 63                                 |

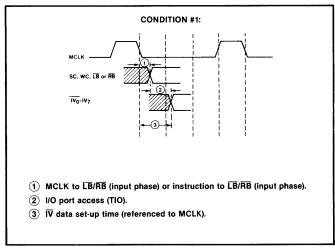

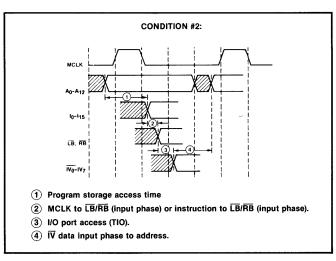

| 4.3 | TIMING RELATIONSHIPS.  4.3.1 Master Clock (MCLK)  4.3.2 Address Latches  4.3.3 Instruction Latches  4.3.4 I/O and I/O Control  4.3.5 HALT Timing  4.3.6 RESET Timing                                   | . 64<br>. 64<br>. 64<br>. 64         |

| 4.4 | CRITICAL TIMING CALCULATIONS  4.4.1 I/O Port Access Time  4.4.2 Program Storage Access Time  4.4.3 Instruction Cycle Time                                                                              | . 67<br>. 67                         |

| SYS | STEM DESIGN                                                                                                                                                                                            | . 69                                 |

|     | PROGRAM MEMORY                                                                                                                                                                                         |                                      |

5

|   | 5.2 EXTENDED MICROCODE  5.2.1 Fast I/O Select  5.2.2 Other Uses of Extended Microcode  5.2.3 Cycle Delay                                        | 71<br>72       |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 5.3 THE IV BUS INTERFACE  5.3.1 8X300 Family Bus-Compatible Devices  5.3.2 Non-8X300 Family Devices  5.3.3 IV Bus Operations  5.3.4 Bus Loading | 73<br>73<br>73 |

|   | 5.4 WORKING STORAGE 5.4.1 Data Storage with the 8X350 5.4.2 Alternate Data Storage 5.4.3 Implementation of the 8X360                            | 74<br>74       |

|   | 5.5 INTERRUPT HANDLING 5.5.1 Interrupts Using the 8X310 5.5.2 Interrupts Not Using the 8X310                                                    | .76            |

|   | 5.6 VOLTAGE REGULATION                                                                                                                          | . 78           |

| 3 | SOFTWARE DESIGN                                                                                                                                 | .79            |

|   | 6.1 ARITHMETIC AND LOGICAL OPERATIONS                                                                                                           |                |

|   | 6.1.1 Subtraction                                                                                                                               | .79            |

|   | 6.2 PROGRAM CONTROL 6.2.1 Conditional Branching 6.2.2 Multi-Way Branching                                                                       | . 79<br>. 80   |

|   | 6.2.3 Subroutines6.2.4 Looping                                                                                                                  |                |

|   | 6.3 CODE CONVERSION                                                                                                                             |                |

|   | 6.4 PERIPHERAL DEVICE OPERATION                                                                                                                 |                |

|   | 6.4.1 Device Polling                                                                                                                            |                |

|   | 6.4.3 Other 8X300 Family Devices                                                                                                                |                |

## **LIST OF FIGURES**

| 1-1          | Architectural Overview of 8X305 MicroController    |             |

|--------------|----------------------------------------------------|-------------|

| 1-2          | 8X305 Pin Designations and Functions               | . 3         |

| 1-3          | General System Example                             |             |

| 2-1          | Functional Block Diagram                           | . 6         |

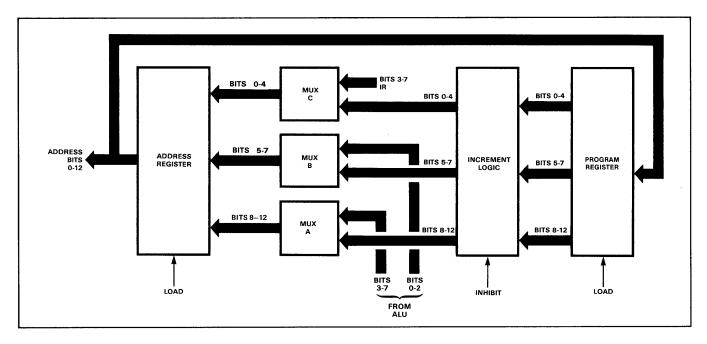

| 2-2          | Program Address Data Flow                          | . 7         |

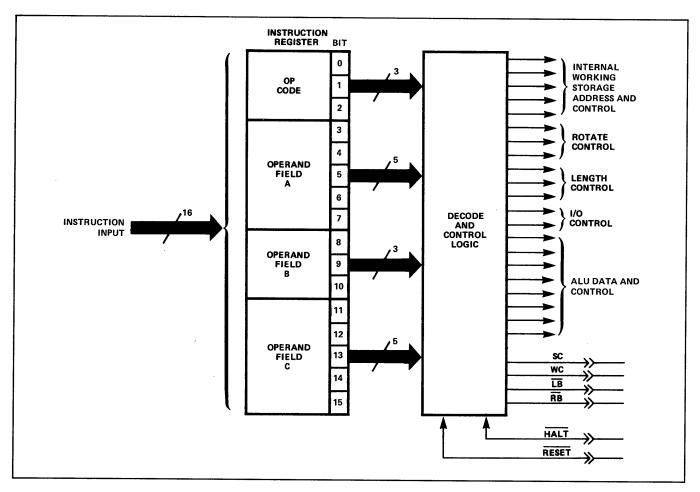

| 2-3          | Instruction Decode                                 | . 9         |

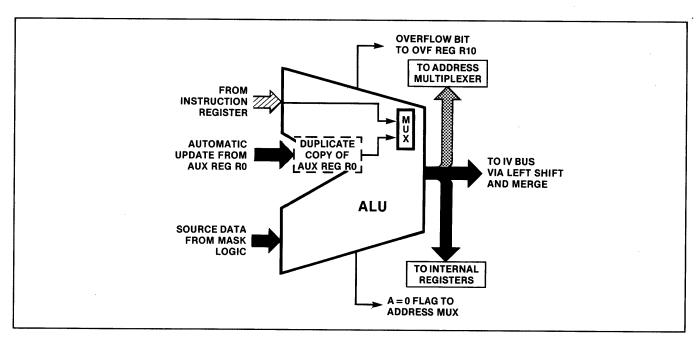

| 2-4          | ALU Data Flow                                      | . 9         |

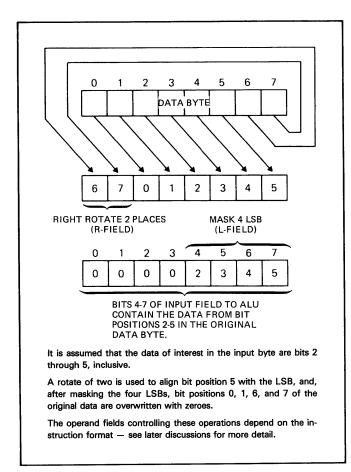

| 2-5          | Rotate and Mask Operations                         |             |

| 2-6          | Shift and Merge Operations                         |             |

| 2-7          | Instruction Cycle Subdivisions                     |             |

| 2-8          | General Formats of the Eight Instruction Classes   |             |

| 2-9          | S-Field Formats                                    |             |

|              | Data Flow for RR Format                            |             |

|              | Data Flow for RB Format                            |             |

|              | Data Flow for JR Format                            |             |

|              | Data Flow for XR Format                            |             |

|              | Data Flow for JB Format                            |             |

|              | Data Flow for XB Format                            |             |

|              | Data Flow for JA Format                            |             |

|              |                                                    |             |

| 3-1          | Example of MOVE Instruction                        |             |

| 3-2          | Example of ADD Instruction                         |             |

| 3-3          | Example of AND Instruction                         |             |

| 3-4          | Example of XOR Instruction                         |             |

| 3-5          | Example of XEC Instruction                         |             |

| 3-6          | Example of NZT Instruction                         |             |

| 3-7          | Examplt of XMIT Instruction                        |             |

| 3-8          | Example of JMP Instruction                         |             |

| 4-1          | Timing Diagram of 8X305 MicroController            |             |

| 4-2          | Clocking with a Pulse Generator                    |             |

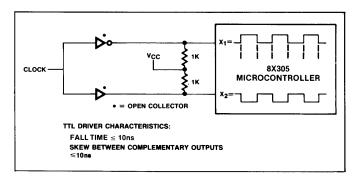

| 4-3          | Clocking with TTL Signals                          |             |

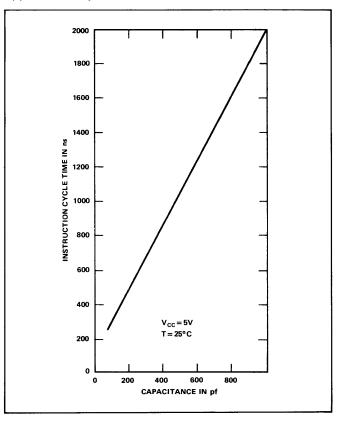

| 4-4          | Typical Cycle Time versus Capacitance              |             |

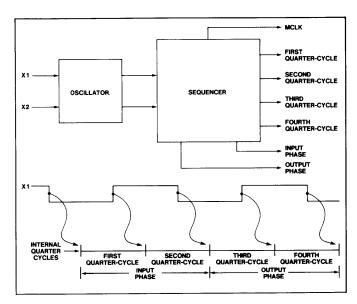

| 4-5          | Timing and Timing Control Signals                  | . 63        |

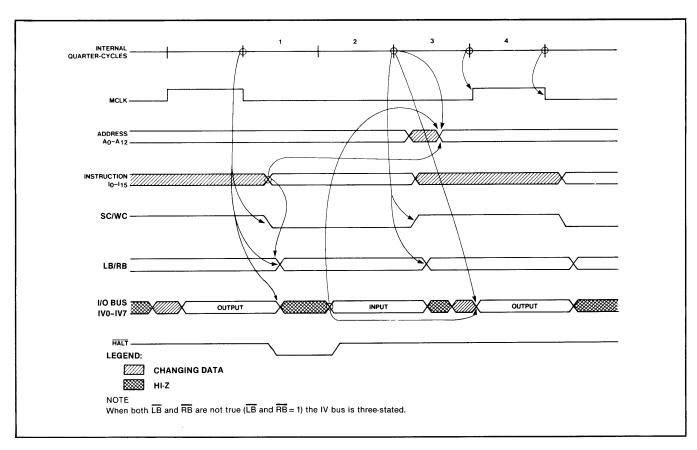

| 4-6          | Typical Instruction Timing Relationships           | . 63        |

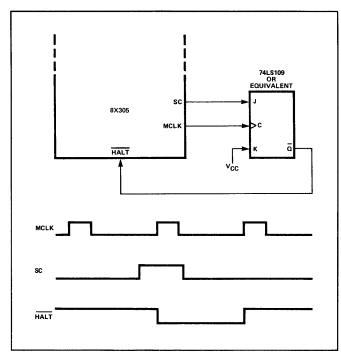

| 4-7          | HALT Timing                                        | . 65        |

| 4-8          | RESET Timing                                       | . 66        |

| 4-9          | Calculating Access Time of I/O Port                | . 66        |

| 4-10         | Calculating Access Time of Program Storage         | . 66        |

| 4-11         | Verification of Program Storage Access Time        |             |

| 5-1          | Representative Control System                      |             |

| 5-2          | Elongated Positive Clock Cycle                     |             |

| 5-3          | Extended Microcode Scheme                          |             |

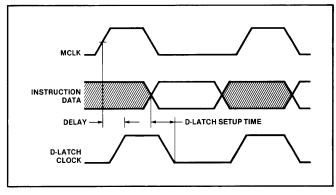

| 5-4          | Port Enable Latching Scheme                        |             |

| 5-5          | Latching Timing Diagram                            |             |

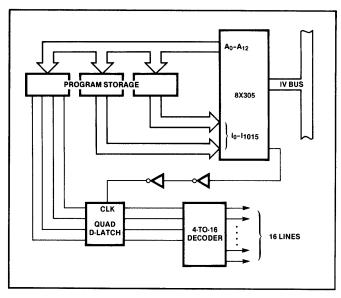

| 5-6          | Extended Microcode Decoding                        | 72          |

| 5-7          | Working Storage Access Delay Generation            |             |

| 5-8          | Delay Generation with Program Storage Partitioning |             |

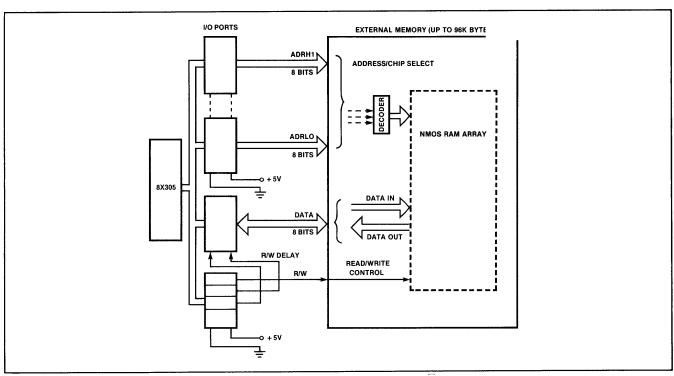

| 5-0<br>5-9   | General Memory Scheme                              |             |

|              | Small Data Storage Scheme                          |             |

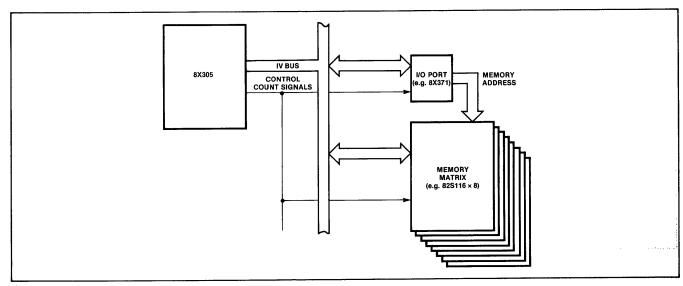

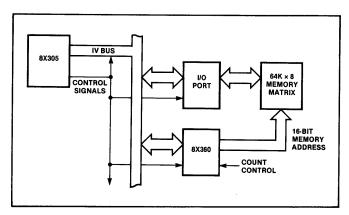

|              | System Using the 8X360                             |             |

| ט-וו<br>5.10 | System with 8X310 Interrupt Control                | . 10<br>77  |

|              | Voltage Regulation                                 | . / /<br>79 |

|              |                                                    |             |

JUNE 1982

## USERS MANUAL 8X305

## **LIST OF TABLES**

|     | Instruction Classes                    |      |

|-----|----------------------------------------|------|

|     | Internal Register Assignments of 8X305 |      |

| 2-3 | Description of Instruction Classes     | .13  |

| 3-1 | Instruction Set Summary                | . 33 |

| 4-1 | Definitions of Timing Parameters       | . 60 |

| 4-2 | Crystal Specifications                 | .62  |

|     | Comparison of Fast I/O Select          |      |

USERS MANUAL 8X305

#### Chapter 1

#### INTRODUCTION

This manual provides the system designer with a complete technical discussion of the Signetics 8X305 Bipolar MicroController. The first two chapters address the functional operation of the 8X305, Chapter 3 is a reference for the device instruction set, Chapter 4 discusses timing considerations, and the final two chapters deal with application of the device.

The 8X305 Data Sheet provides complementary data to this manual, including detailed timing and electrical characteristics. The 8X300 Family Product Capabilities Manual discusses the 8X305 in the context of the many compatible support devices available from Signetics. Together, the three documents provide the information necessary to design and implement a system that takes full advantage of the powerful features of the 8X305.

The Signetics 8X305 Bipolar MicroController provides a real alternative to the complexity of bit-slice designs and the relatively slow speed of MOS microprocessors in high performance, cost effective control systems.

#### 1.1 DEVICE DESCRIPTION

The 8X305 MicroController (Figure 1-1) is a monolithic Central Processing Unit implemented in bipolar Schottky technology. It is designed to operate at a speed of 200 nsec for each 16-bit instruction, fetched on a dedicated bus for higher throughput. It controls a series of peripheral devices which are attached to it by means of a standard 8-bit bus known as the Interface Vector bus and its associated control signals. The 8X305 can be easily integrated into most support systems using 8X300 Family support devices.

The 8X305 is upward-compatible with its predecessor, the 8X300, allowing enhancement of existing MicroController systems. Software written for the 8X300 will function correctly on an 8X305, but the expansion of the instruction set and internal working storage allows more flexible manipulation of data, higher throughput, and simplification of code. Care should be taken, however, in analyzing signal and timing requirements for each application where the MicroController is to be updated.

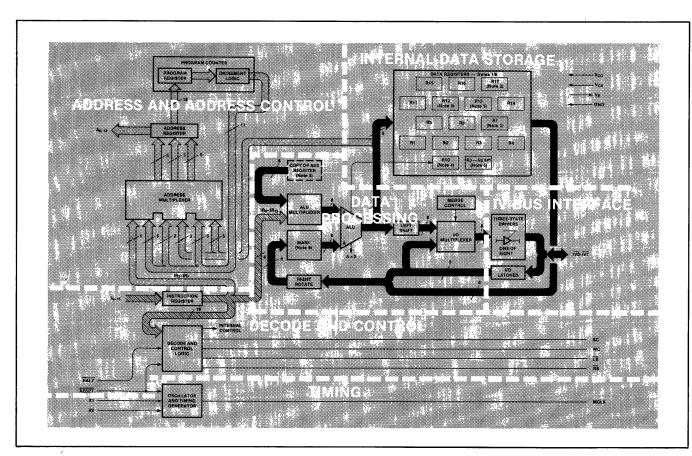

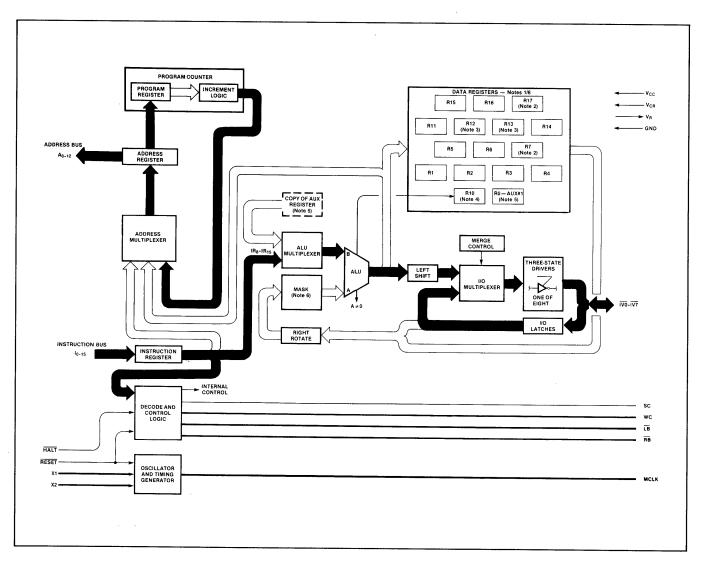

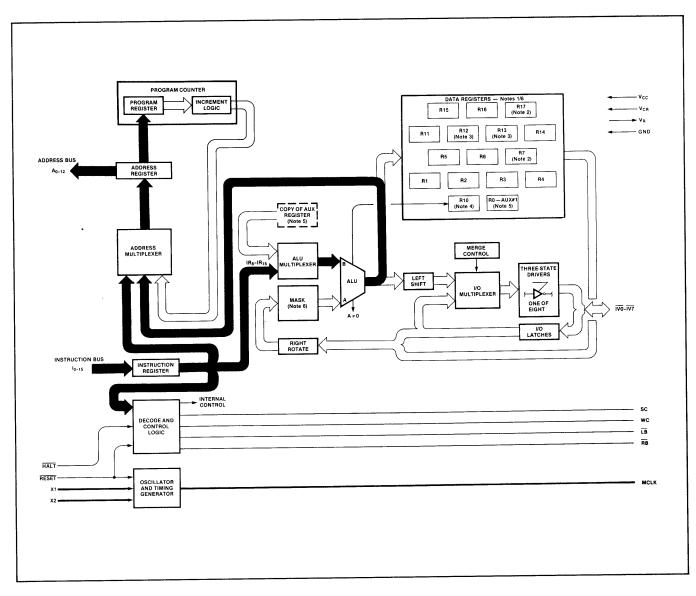

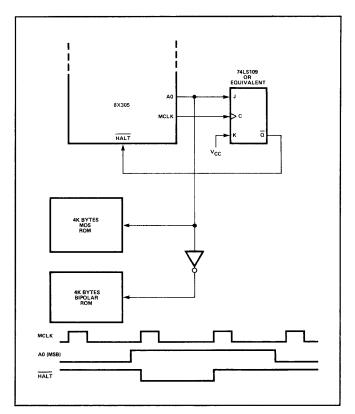

Figure 1-1. Architectural Overview of 8X305 MicroController

USERS MANUAL 8X305

The 8X305 is designed to provide the optimum combination of features for controller design:

- · Powerful, simple instruction set

- · Eight instruction classes

- · Single chip package

- Bipolar speed

- Family of compatible peripheral devices

- Flexible bit manipulation in a single instruction

- Single +5 volt supply

- TTL three-state bus operation

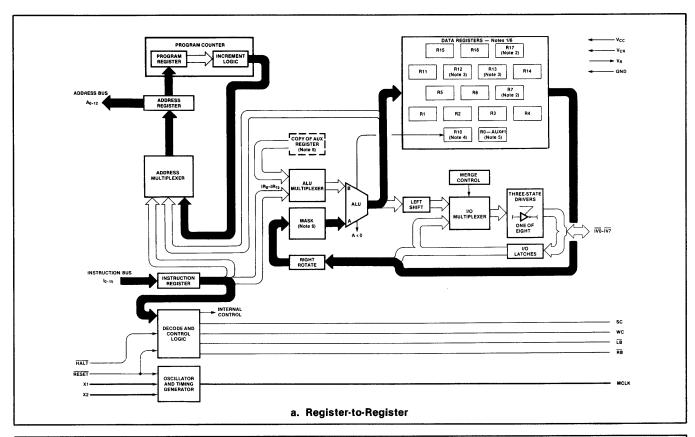

#### 1.2 DEVICE ARCHITECTURE

An understanding of the internal architecture of the 8X305 is required to maximize the efficiency of a design. Figure 1-1 illustrates the logical structure, but does not necessarily represent exact physical connections within the device.

The instruction arrives at the Instruction Register from the Instruction Bus ( $I_0$ – $I_{15}$ ). It is interpreted on the basis of the Op Code which defines the significance of the other bits in the instruction. Data paths within the chip are set up by the Decode and Control logic. External control signals are also generated by this logic. At a later point in the cycle, the Program Counter, Increment Logic, and Address Multiplexer generate the address of the next instruction to be executed and place it in the Address Register. The address is then placed on the Instruction Address Bus ( $A_0$ – $A_{12}$ ) to fetch the next instruction.

All timing is generated by an on-chip oscillator running at twice the actual instruction cycle speed.

Source data can be accessed from three locations:

- 16 internal registers

- · The IV bus

- Absolute or modified constant specifications from the current instruction word

Data from external sources can be manipulated by means of the Rotate and Mask Logic before becoming the first operand for an ALU operation. The implied second operand is the Auxiliary Register (AUX or R0). The result of the operation is stored in an Internal Register or transmitted to the IV bus.

The sixteen 8-bit registers contained in the 8X305 are used as temporary storage of data and pointers. Three of these registers have special applications for IV bus address transmission and flag storage, leaving thirteen available as general-purpose storage.

#### 1.3 PIN DESCRIPTION

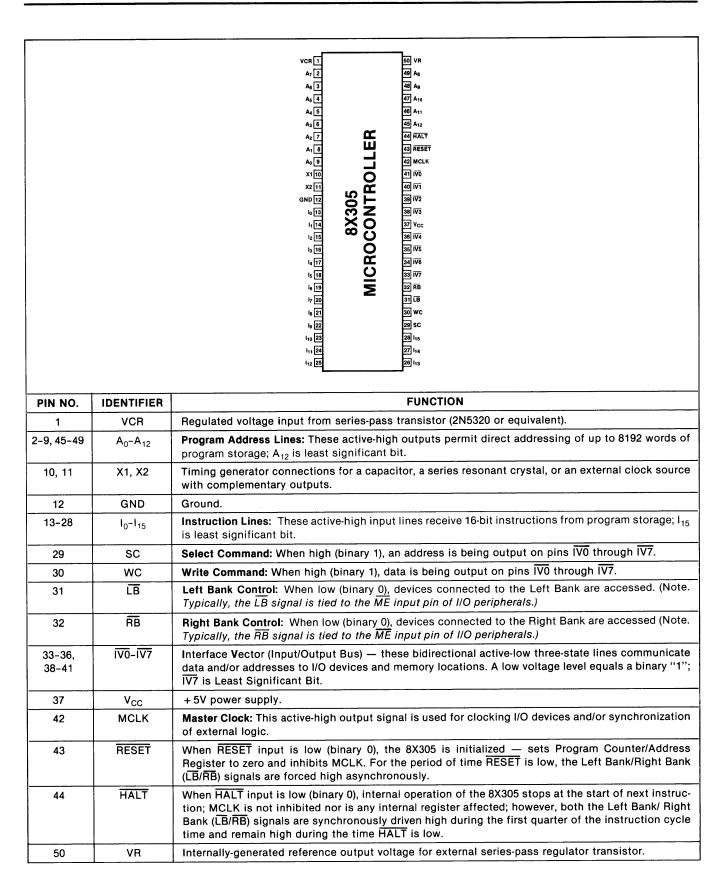

The 8X305 MicroController is housed in a 0.9-inch wide, 50-pin Dual In-Line (DIP) package, with pin assignments and designated functions as indicated in Figure 1-2.

#### 1.4 THE INTERFACE VECTOR BUS

The 8X305 communicates with peripheral devices by means of a bidirectional, 8-bit TTL bus known as the Interface Vector, or IV bus. Five control signals generated by the 8X305 indicate the direction in which the bus is being driven and the configuration of the data or address on the bus

Devices connected to the IV bus are commonly referred to as I/O Ports. Any one of up to 256 such devices can be selected in a single cycle when the 8X305 places the I/O Port's unique address on the bus and asserts the Select Command (SC) signal. Once selected, an I/O Port normally remains selected until the SC signal is again asserted with a different address on the bus.

The direction of data flow is indicated by the Write Command (WC) signal. This signal is asserted when data is being placed on the bus by the 8X305, and is not asserted when data is being read from the bus. The data will normally be read from or written into whatever I/O Port was last selected.

To optimize the 8X305's capabilities in data manipulation and device selection, two control signals known as Left Bank ( $\overline{\text{LB}}$ ) and Right Bank ( $\overline{\text{RB}}$ ) are provided. These signals are asserted concurrently with other control signals based on the contents of the instruction word. They can be used in conjunction with the other signals to determine which I/O Port will be enabled at any given time. They can be used in a variety of ways, but the two most significant are as follows:

- The optimum performance of the MicroController can be achieved by connecting the input I/O Port to one bank and the output port to the other. The two ports can then be selected concurrently and data can pass between them in a single cycle, resulting in a transfer rate of five megabytes per second.

- 2. Since the bank select signal ( $\overline{LB}$  or  $\overline{RB}$ ) must be asserted for a port to be enabled, two ports may share the same address provided that they are connected to opposite banks. This expands the number of I/O Ports that can be addressed in a single cycle to 512.

Timing on the bus is synchronized with the Master Clock (MCLK) signal. Together with the other control signals, it enables the I/O Ports to access the IV bus at the correct points in the MicroController's instruction cycle.

USERS MANUAL 8X305

Figure 1-2. 8X305 Pin Designations and Functions

The I/O Ports must be capable of performing the address select operation, determining the direction of the bus, analyzing the bank control signals, and presenting or receiving data. Signetics offers numerous circuits that perform these functions for specific applications. Refer to the 8X300 Family Product Capabilities Manual for information on these devices.

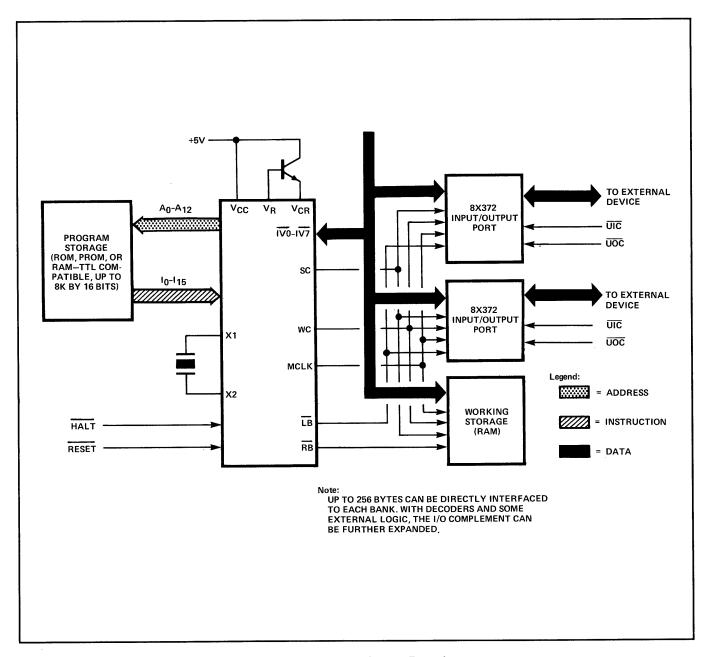

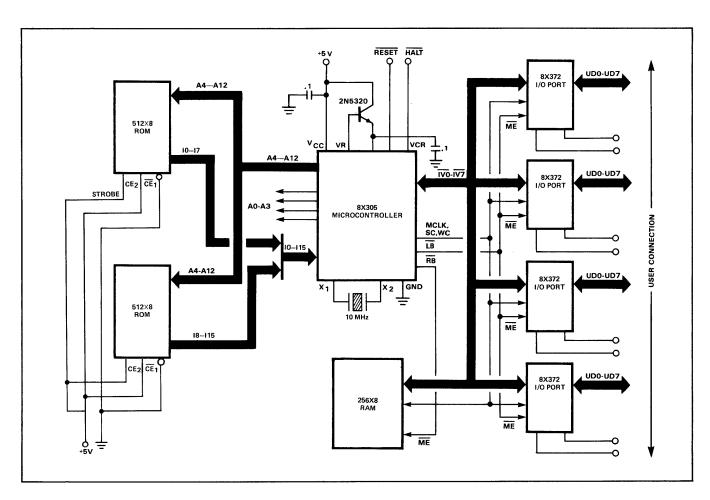

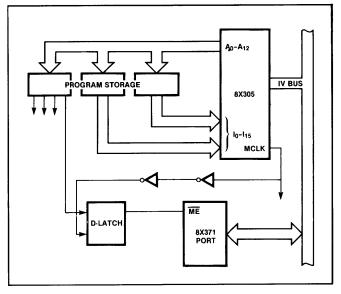

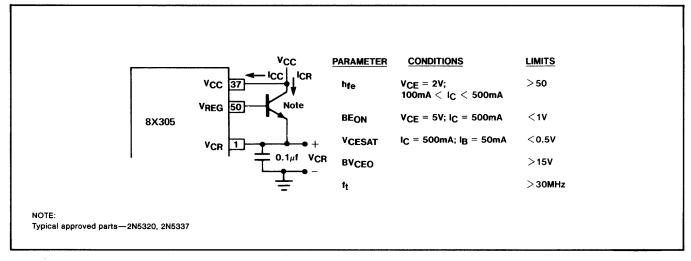

#### 1.5 SYSTEM ENVIRONMENT

A generalized system configuration consisting of program storage (ROM/PROM), working storage (RAM), I/O devices, and the IV bus interface (IVO-IV7) is shown in Figure 1-3. Except for the off-chip timing crystal, the regulator transistor, and any user-generated logic associated with the HALT and RESET lines, no external parts are required for implementation. The TTL-compatible bus, simple interface logic, and bitmanipulation features optimize the 8X305 MicroController for almost any system where high-speed operation, flexibility, and minimum board space are required.

The program storage can consist of any ROM or PROM with sufficient access speed. It can be configured to the

size of program required by the application, up to a maximum of 8,192 instruction words.

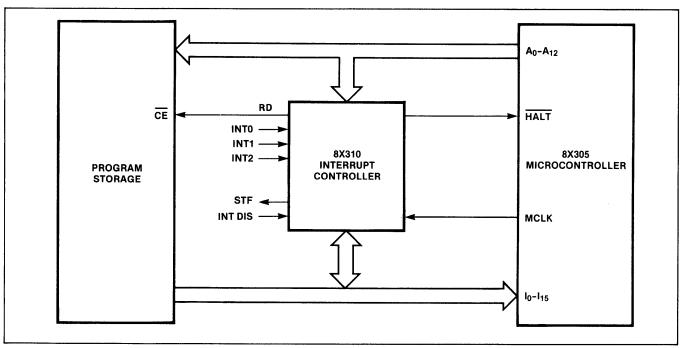

An Interrupt Control Coprocessor, the 8X310, is available. This device connects to the Instruction Bus and Instruction Address Bus, providing a single-chip interrupt handler and an enhanced ability for subroutine processing.

Ports on the IV bus must be tailored to the application. Some additional high-speed working storage may also be required. This is implemented by assigning contiguous memory locations in a small byte-wide RAM to a series of contiguous port addresses. It is good practice to pair peripherals which transfer a good deal of data between each other on opposite banks, which enables single-instruction processing and transfer of data.

Since they have been designed specifically for the IV bus, the 8X300 Family of parts provide the simplest solution to most requirements encountered in an 8X305 system. The family includes an array of I/O Ports, working storage RAM, and single-chip solutions to problems such as floppy disk control and computer bus interfacing.

**JUNE 1982 BIPOLAR LSI DIVISION**

#### 8X305 **USERS MANUAL**

Figure 1-3. General System Example

**USERS MANUAL**

6

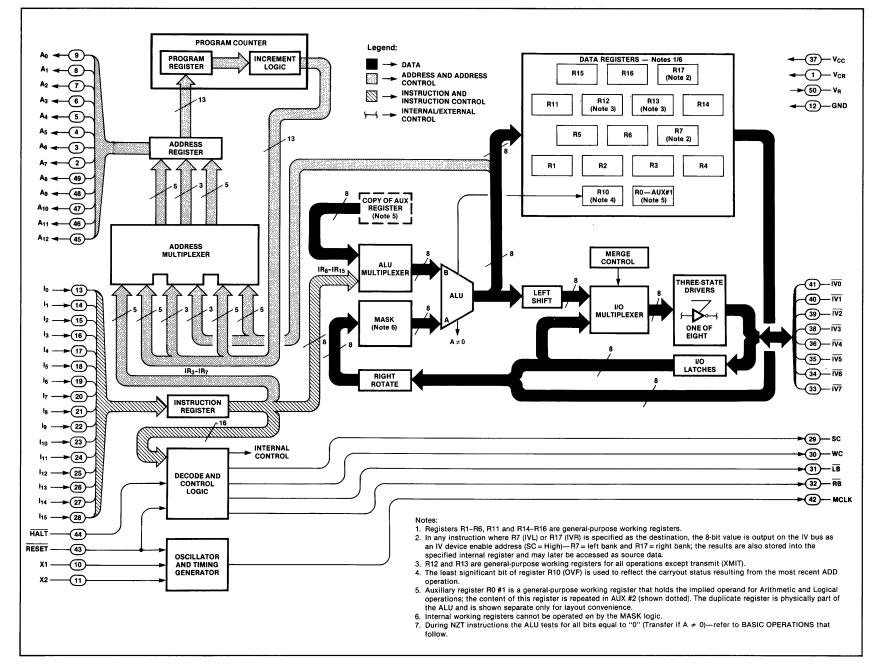

Figure 2-1. Functional Block Diagram

USERS MANUAL 8X305

#### Chapter 2

#### **FUNCTIONAL OPERATION**

The purpose of this chapter is to provide the user of the 8X305 MicroController with a detailed description of the functional blocks used to process data under program control. Understanding of these mechanisms will assist the user in making full use of the power and flexibility of the MicroController within the context of a particular application.

The 8X305 will be discussed in several stages; from the hardware components of which it is composed, through the basic steps of each instruction cycle and a discussion of the instruction format, to the flow of data in the device during instruction execution. Figure 2-1 shows a detailed functional block diagram of the 8X305, which will be used as the basis of discussion for this chapter.

#### 2.1 HARDWARE COMPONENT BLOCKS

The functional blocks of the 8X305 may be categorized as:

- · Oscillator and Timing

- Program Addressing

- Decode and Control

- · Arithmetic and Logic Unit

- Bit Manipulation

- Internal Registers

- IV Bus Control

#### 2.1.1 Oscillator and Timing Generator

Using an external frequency-determining element, such as a crystal (or capacitor), the on-chip oscillator provides reference pulses to the Timing Generator which, in turn, produces the Master CLock (MCLK) and four quartercycle pulses. MCLK is used for external control and system synchronization whereas the 1st, 2nd, 3rd, and 4th quarter-cycle pulses are used for internal gate control during the instruction cycle.

#### 2.1.2 Program Address Logic

Functional detail of the program address logic is shown in Figure 2-2. The program address logic revolves around two basic registers-the Address Register (AR) and the Program Register (PR). The Address Register holds the address of the current instruction for program memory and the Program Register holds the address of the current (or next) instruction. Normally, these two registers contain the same address; however, for branch operations, the content of the two registers may differ. Except for XEC (Execute), NET (non-zero transfer), and JMP (Jump) instructions, the output of the Program Counter is incremented during the third quarter cycle. The incremented data is passed through the lower ports of multiplexers A (bits 8-12), B (bits 5-7), and C (bits 0-4) and the composite is loaded into the Address Register. During the fourth quarter cycle, the incremented address is looped back to update the Program Counter.

Figure 2-2. Program Address Data Flow

For branch operations, the generation of the next address is modified by internal logic to achieve ease of programming and operating flexibility. Multiplexers A, B, and C allow the Address Register to be loaded from two sources—8 bits from the ALU via multiplexers A and B and 5 bits from the instruction register via multiplexer C. For XEC and NZT instructions, these loading options provide the programmer with 256-byte pages for register operations and 32-byte pages for IV-bus operations. If the source for an execute operation is an internal register, the eight least significant bits of the Address Register is updated via the ALU; if the source is the IV bus, the five least significant bits are changed. In either case, incrementing of the Program Register is inhibited, that is, the contents of this register do not change. For non-zero transfer operations, the source data (register or bus) is tested for a "zero" or "not-zero" condition. If the result is zero, the Program Register is incremented in normal fashion; if the result is not zero, the 8 LSB (source = internal register) or the 5 LSB (source = IV bus) of both the Address Register and Program Register are updated via the ALU. In the case of the JMP instruction, all thirteen bits of the Address Register and the Program Register are changed to identify the new address.

#### 2.1.3 Decode and Control Logic

An instruction from program memory is latched into the Instruction Register at the beginning of each cycle, and is interpreted by the Decode and Control Logic on the basis of the high-order three bits, which specify the Operation, or Op Code. There are eight (8) instruction classes and they can be separated into two control areas—data control and program control; general functions within these areas are:

Program Control —

XEC |

NZT | Branch or Test

JMP |

The operation and function of each instruction class are defined in Table 2-1.

Table 2-1. Instruction Classes

| Mnemonic Code Operation |            | Function          |                             |

|-------------------------|------------|-------------------|-----------------------------|

| Data Contro             | <b>]</b> : |                   |                             |

| MOVE                    | 0          | Move              | Data Transfer               |

| ADD                     | 1 1        | Add A and B       | Arithmetic                  |

| AND                     | 2          | Logic AND         | Logic                       |

| XOR                     | 3          | Exclusive OR      | Logic                       |

| XMIT                    | 6          | Transmit          | Data Transfer               |

| Program Cor             | ntrol:     |                   |                             |

| XEC                     | 4          | Execute           | Indexed Temporary<br>Branch |

| NZT                     | 5          | Non-Zero Transfer | r Conditional<br>Branch     |

| JMP                     | 7          | Jump              | Non-Conditional<br>Branch   |

As shown in Figure 2-3, the rest of the instruction word is divided into three Operand Fields whose significance is a function of the Op Code. The Decode and Control Logic generates the internal enable signals for data flow and manipulation and also provides the external bus control signals, using timing provided by the timing generator.

#### 2.1.4 Arithmetic Logic Unit

Referring to Figure 2-4, the Arithmetic Logic Unit (ALU) receives the "A" inputs from either internal registers or I/O (through Rotate/Mask logic) and the "B" inputs from either the Instruction Register (IR8-IR15) or from a register containing an exact duplicate of the information contained in the Auxiliary Register R0 via a multiplexer. The ALU performs one of four functions on the data. It may ADD, AND or XOR the A and B input data, or it may pass it straight through with no modification (MOVE,XMIT,JMP). The ALU output data is then transferred to either the internal registers, the I/O Bus through Shift and Merge logic, or the Program Address logic. The ALU also indicates overflow condition during ADD functions by means of a discrete output to the LSB of the Overflow Register, R10. This bit is set if the 8th bit overflows. During NZT instructions, the ALU tests for all bits "0".

#### 2.1.5 Bit Manipulation Logic

As shown by the block diagram in Figure 2-1, the "A" data path to and from the ALU contains three operating functions—Right Rotate, Mask, and Left Shift. Coupled with the Merge control logic, these three functions provide extensive bit manipulation capability and lend themselves to programming techniques that are efficient and powerful.

Figure 2-3. Instruction Decode

Figure 2-4. ALU Data Flow

The combination of the *Right Rotate* and *Mask* functions allows selection of one or more bits from a source data field. For instructions where both the source and destination are internal registers, only the *Right Rotate* function can be used—the data being a fixed length of 8 bits. The right rotate function provides an end-around-shift of one to seven places of the 8-bit source field. In this manner, the least significant bit of the required bit string can be positioned in the least significant position of the data byte and readied for further processing. Refer to Figure 2-5.

Figure 2-5. Rotate and Mask Operations

The number of places that the data is to be rotated is specified by the R-field operand (when present) and by the  $S_0$ -field when the source is the IV bus. The R-field specifies the number of places the data is to be rotated; the  $S_0$ -field specifies the bit of the source data field which will be rotated to bit position seven before masking.

The Mask function allows selection of the least significant "L" bits of the rotated IV bus source data for subsequent processing. The L-field operand is specified by the "L" field of the instruction. After masking, the least significant bits specified by "L" are output to the ALU. All remaining bits of the byte are set to zero.

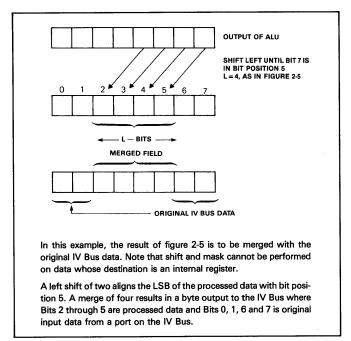

The Left Shift and Merge control logic provide the wherewithal to alter a bit string within an IV bus data byte. The preceding Right Rotate and Mask functions ensure that the required processed data is in the least significant bits of the ALU output; the Left Shift operation then aligns the data with the proper bit positions prior to merging. Refer to Figure 2-6. Because the process is not an end-around-shift, data shifted from the MSB (position 0) is lost. The number of positions to be shifted is specified by the value of  $D_0$  and the data is left shifted until the LSB reaches this value.

Figure 2-6. Shift and Merge Operations

The user can update 1-to-7 bits of existing IV bus data without affecting other bits via the *Merge* control logic. The length of the bit string to be merged with existing data is specified by the L-field operand; the LSB of the bit string is specified by  $D_0$  (after shifting).

Regardless of what bit-manipulation functions are invoked, the ALU performs all arithmetic and logic operations. For this purpose, the ALU has a direct input from the AUXiliary register for the implied operand in AND, ADD, and XOR instructions. The output of the ALU may go directly to the address or data registers or, via the shift and merge circuits, to the IV bus.

#### 2.1.6 Registers (Internal Working Storage)

The 8X305 contains sixteen 8-bit registers, thirteen of which are used as general-purpose storage of data during program execution. Any of the internal registers can be specified as a *source* of data and, if so specified, the data passes through the Rotate and Mask operators on the way to the ALU. In any operation which requires a second operand, such as an ADD instruction, the implied second operand is always the AUXiliary Register ( $R_0$ ).

Operational parameters of the preceding registers are given in Table 2-2. Note that the Overflow (OVF) Register  $R_{10}$  is loaded automatically during each ADD operation, and consists effectively of only one bit.

Table 2-2. Internal Register Assignments of 8X305

| Reg —<br>Octal Desig | Function                                                | Note |

|----------------------|---------------------------------------------------------|------|

| R0                   | AUXiliary Register                                      | 1    |

| R1                   | General Purpose Operation                               |      |

| R2                   | General Purpose Operation                               |      |

| R3                   | General Purpose Operation                               |      |

| R4                   | General Purpose Operation                               |      |

| R5                   | General Purpose Operation                               |      |

| R6                   | General Purpose Operation                               |      |

| R7                   | Left Bank Register                                      | 2    |

| R10                  | Overflow (OVF) Register                                 | 3    |

| R11                  | General Purpose Operation                               |      |

| R12                  | Special Purpose Register used for<br>Transmit Operation | 4    |

| R13                  | Special Purpose Register used for<br>Transmit Operation | 4    |

| R14                  | General Purpose Operation                               |      |

| R15                  | General Purpose Operation                               |      |

| R16                  | General Purpose Operation                               |      |

| R17                  | Right Bank Register                                     | 2    |

#### Notes:

- Contains the second or implied operand. Physically consists of two registers with identical data—the second register (Accumulator) is located in the ALU.

- When R7 is specified as the destination, the 8-bit value is also output to the selected port on Left Bank of IV bus; the operation is exactly the same for R17, except the Right Bank is affected. Either register can also be used as a source of data.

- Least Significant Bit used as OVF flag storage for the most recent ADD operation.Only the LSB is used and this register can only be specified as a source.

- 4. For all instructions except transmit (XMIT), R12 and R13 operate as general-purpose registers; when either register is specified as a destination during a transmit instruction, data is transmitted to the Left Bank of IV bus (R12 specified) or to the Right Bank (R13 specified). Whichever the case, the contents of the register is unchanged.

#### 2.1.7 IV Bus Control

Timing of the IV bus is synchronous with the Master Clock (MCLK) signal—an output of the Timing Generator. MCLK is high during the last quarter of each instruction cycle.

IV bus control is provided by four signals generated by the Decode and Control Logic. These control signals and their functions are as follows: Select Command (SC)—a high (binary 1) on this line indicates that an address is being output on the IV bus to enable an I/O port or device.

Write Command (WC)—a high (binary 1) on this line indicates that data is being output on the IV bus, to be stored in a previously-enabled register/port. When both SC and WC are low (binary 0) the MicroController expects data from the selected device. Both SC and WC high (binary 1) is a condition not generated by the 8X305.

Left Bank Enable  $(\overline{LB})$ —a low (binary 0) on this line enables one of two groups of I/O devices (or memory locations). In all following text, this group of devices is referred to as the Left Bank.

Right Bank Enable (RB)—a low (binary 0) on this line enables the second of the previously mentioned two groups of I/O devices (or memory locations). In all following text, this group of devices is referred to as the Right Bank.

Note: When neither bank-select signal is true (both high) this signifies that the 8X305 has released the bus by putting  $\overline{1V0}$ - $\overline{1V7}$  in a three-state condition; the bus may then be used for other activities.

#### 2.2 BASIC INSTRUCTION CYCLE

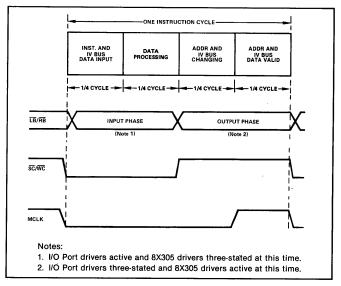

The instruction cycle of the 8X305 equals one-half of the external clock cycle. The instruction cycle is subdivided into four quarter-cycles, which are used to gate data flow and processing in the correct sequence. The cycle is outlined here for the purpose of understanding its effect on data processing. Refer to Figure 2-7 during the following timing discussion of the four quarter-cycles. Note that the quarter-cycles are internal to the device and cannot be seen as external signals.

Figure 2-7. Instruction Cycle Subdivisions

### USERS MANUAL 8X305

The exact operations performed depend on the instruction to be executed. An instruction which performs an IV bus-to-IV bus transfer is described in the rest of this subsection.

During the first quarter-cycle, a new instruction is input to the 8X305 from program storage, via the  $I_0\text{-}I_{15}$  lines. This instruction is interpreted by the Decode and Control Logic. Data from the user system is accessed via the  $\overline{\text{IV0}}$ - $\overline{\text{IV7}}$  lines under control of the bus control signals. At the end of this quarter-cycle, the instruction is latched. The input phase, when data is input to the 8X305 from a point in the IV bus consists of this and the following quarter-cycle.

During the second quarter-cycle, instruction processing is initiated. The bus data is latched into the IV bus and ALU latches at the end of the quarter-cycle. Since there are a number of gate delays between the IV bus and ALU latches, the bus data must be stable early in this quarter-cycle to allow time for correct ALU latching of data.

In the third quarter-cycle, while the address for the next instruction fetch is output to the  $A_0$ - $A_{12}$  lines, control signals for execution of the output phase of the present instruction are generated, and output data for the bus is stabilized. During this time, the address latch is open.

During the fourth quarter-cycle, a master clock signal (MCLK) generated by the 8X305 is used to latch valid address or data into peripheral devices connected to the IV bus; MCLK is also used to synchronize any external logic with timing circuits of the 8X305. This concludes the output phase and the instruction cycle.

To summarize the action, the first half of the instruction cycle deals primarily with input functions, and the second half is mostly concerned with output functions. Some instructions, such as register-to-register, make no use of the IV bus, and others, such as a branch, manipulate address information before it is output to program memory. All instructions, however, conform with this basic sequence.

#### 2.3 INSTRUCTION FORMATS

The 16-bit instruction word is fetched from program storage and input to the Decode and Control Logic.

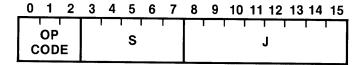

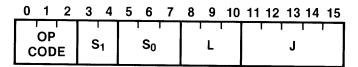

The twenty-four variations of 8X305 instructions are grouped in eight classes, each distinguished by a unique Op Code. These are classified by seven formats of the instruction, as follows:

- Manipulation of register data (Format RR)

- Manipulation of register and IV bus data (Format RB)

- · Branch or Test on register data (Format JR)

- Transmission of data to a register (Format XR)

- Branch or Test on IV bus data (Format JB)

- Transmission of data to the IV bus (Format XB)

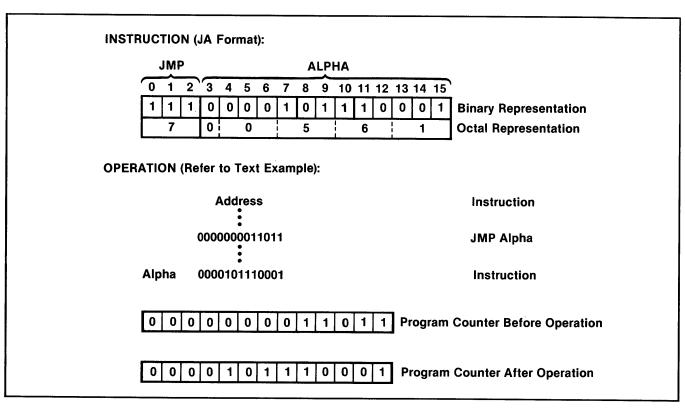

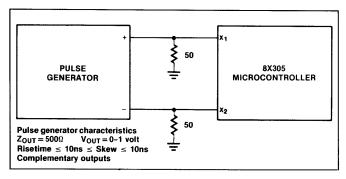

- Unconditional branch (Format JA)

Within each class, operands of the instruction word provide powerful variations for the manipulation of data down to the bit level. This section is a detailed machine-level discussion of the operation of the various instruction fields and helps the reader understand internal workings of the 8X305 which are masked by the simplicity of the MCCAP CrossAssembler. For further information on MCCAP, refer to the MCCAP Manual.

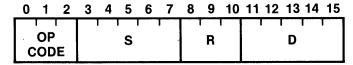

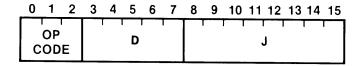

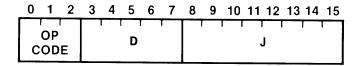

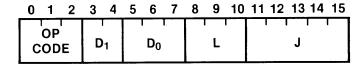

#### 2.3.1 General Formats

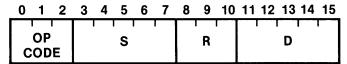

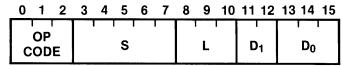

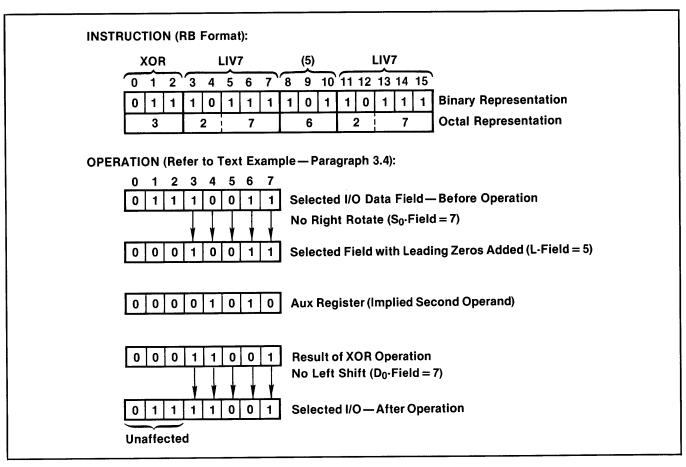

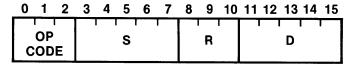

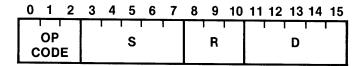

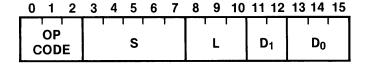

Each instruction class has its individual members defined by the six Operand Fields that comprise bits  $I_3$  through  $I_{15}$ . Refer to Figure 2-8 for the various configurations of these fields which result in the seven general formats.

| F                                               | 0 1 2                   |                                   | 8 9 10<br>PERANDS     | 11 12 13 14 15      |

|-------------------------------------------------|-------------------------|-----------------------------------|-----------------------|---------------------|

| Format RR<br>Register-Register                  | MOVE                    | Α                                 | В                     | С                   |

| Register-IV Bus Address                         | ADD<br>AND<br>XOR       | s                                 | R                     | D                   |

| Format RB<br>Register–IV Bus<br>IV Bus–Register | 0 1 2<br>OPCODE<br>MOVE | 3 4 5 6 7<br>C                    | 8 9 10<br>PERANDS     | 11 12 13 14 15<br>6 |

| IV Bus-IV Bus<br>IV Bus-IV Bus Address          | ADD<br>AND<br>XOR       | S S <sub>0</sub> ; S <sub>1</sub> | L                     | D D 1               |

|                                                 | 0 1 2<br>OPCODE         | 3 4 5 6 7                         | 8 9 10<br>OPERAND     | 11 12 13 14 15<br>S |

| Format JR<br>Register                           | XEC<br>NZT              | A<br>S                            |                       | B-C<br>J            |

|                                                 | INZ!                    |                                   | <u> </u>              |                     |

| Format XR<br>Register                           | 0 1 2<br>OPCODE         | 3 4 5 6 7                         | 8   9   10<br>DPERAND | 11 12 13 14 15<br>S |

| IV Bus Address                                  |                         | Α                                 |                       | B-C                 |

| IV Bus-8 Bits Immediate                         | XMIT                    | D                                 |                       | J                   |

|                                                 | 0 1 2                   | 3 4 5 6 7                         | 8 9 10<br>OPERAND     | 11 12 13 14 15      |

| Format JB<br>IV Bus                             | OPCODE                  | A                                 | R                     | C                   |

|                                                 | XEC<br>NZT              | S S <sub>0</sub> ; S <sub>1</sub> | ī                     | J                   |

|                                                 | 0 1 2                   | 3 4 5 6 7                         |                       | 11 12 13 14 15      |

| Format XB                                       | OPCODE                  |                                   | OPERAND               |                     |

| IV Bus Variable<br>Field Immediate              |                         | Α                                 | . В                   | С                   |

| Field minediate                                 | XMIT                    | D D 1 D1                          | <u> </u>              | J                   |

|                                                 | 0 1 2<br>OPCODE         |                                   | 8 9 10                | 11 12 13 14 15      |

| Format JA                                       | OFCODE                  |                                   | A-B-C                 |                     |

|                                                 | JMP                     |                                   | Α                     |                     |

|                                                 |                         |                                   |                       |                     |

Figure 2-8. General Formats of the Eight Instruction Classes

### USERS MANUAL 8X305

All instructions in the 8X305 can be characterized by one of these formats, and reference will be made to Figure 2-8 while explaining specific instruction operations discussed in the rest of this section.

Each of these fields specifies a functional component, the net effect of which is to identify a particular instruction. Since the *Source, Destination, Rotate* and *Length* fields are somewhat complex in their definition, they are explained in separate subsections.

#### 2.3.2 Instruction Fields

The exact contents of each instruction field is a function of the specific instruction, but the following fields may be distinguished:

- Op Code, which defines the class of instruction

- Source (S), which defines the origin of the data

- Destination (D), which defines the final location of the data

- Rotate (R), which defines the amount of source data rotation

- Length (L), which defines the number of bits of the source or destination data

- Immediate (J), which defines a Literal Constant

- Address (A), which points to the next instruction to be executed

The Op Code identifies the class of instruction, which includes a definition of the ALU operation to be performed on the data, if any. Table 2-3 gives a brief overview of the 8X305 instruction classes.

The J-field specifies a literal as a source for the instruction, which may be modified in accordance with the particular instruction type. This is most often used to introduce a constant into the program flow, such as presetting a register to a particular value, or providing an offset address for conditional branches.

The A-field is only used in a JMP (Jump) instruction, and is a special case of a Literal, which is used to branch to a specific address, or location in program memory for the next instruction.

Table 2-3. Description of Instruction Classes

| Op Code | Mnemonic                                                                                                                    | Operation                                                                                                                                                                  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0       | MOVE                                                                                                                        | Move data in location specified by S-field to location specified by D-field.                                                                                               |  |  |

| 1       | ADD                                                                                                                         | Add data in location specified by S-field to contents of accumulator (AUX Register R0) and store result in location specified by D-field.                                  |  |  |

| 2       | 2 AND Logically AND data in location specified by S-field with contents of accumulator and store result in D-field location |                                                                                                                                                                            |  |  |

| 3       | XOR                                                                                                                         | Exclusively-OR data in location specified by S-field with contents of accumulator and move result to location specified by D-field.                                        |  |  |

| 4       | XEC                                                                                                                         | Execute out of sequence, the instruction within the current address page pointed to by a combination of the S-field location data and the J-field data within current page |  |  |

| 5       | NZT                                                                                                                         | If the data specified by the S-field is non-zero, a branch is performed. If the data is zero, increment the program counter by one.                                        |  |  |

| 6       | XMIT                                                                                                                        | Transfer the data of the J-field to the D-field location                                                                                                                   |  |  |

| 7       | JMP                                                                                                                         | Branch to the instruction pointed to by the A-field                                                                                                                        |  |  |

**JUNE 1982**

USERS MANUAL 8X305

#### 2.3.3 Source and Destination Fields

The S and D fields define where the data of the first operand of the instruction is to come from, and where the result of the operation is to be stored. In the case of Arithmetic/Logic operations, a third field is implied, although not specifically defined in the instruction. This is the second operand of the ALU function. Since this is effectively an automatic source in that AUX register  $R_0$  is always used, this need not be explicitly stated in instruction coding. Note that the desired value of the second operand must have been stored in  $R_0$  during a previous instruction.

The source of data in the 8X305 can be any one of the internal registers or it can be the IV bus. The S-field has two distinct formats, depending on which of these is being used as the source.

When an internal register is the data source, the 4 loworder bits of the S-field are used to address the register, and the high-order bit is always zero.

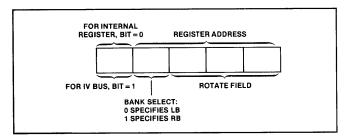

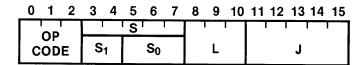

When the IV bus is the data source, this is flagged by the high-order bit being one, and the next-to-high-order bit selecting either the Left Bank (bit is zero) or Right Bank (bit is one). These two bits form the  $S_1$ -field. The remaining three low-order bits form the  $S_0$ -field, and define the amount of rotation that will be performed on the incoming data. Refer to Figure 2-9.

Figure 2-9. S-Field Formats

Note that it is not possible to rotate data from an internal register source under control of the S-field, although internal register rotate is possible using the R-field.

The destination of the result of an instruction is defined similarly to the above, but a few additional effects should be noted.

Any instruction specifying register  $R_7$  or  $R_{17}$  as the destination will, in addition to placing the result in that register, also output it to the IV bus as an I/O device address when SC is high.

A XMIT instruction that specifies  $R_{12}$  or  $R_{13}$  as a destination will output the result on the IV bus as data, and the register contents remain unchanged.

Any internal register except  $R_{10}$  can be selected as a destination by having the high-order bit of the D-field set to zero, and placing the register address in the remaining four bits, similar to register source selection above.

To select the IV bus as the destination, the high-order bit of the D-field is set to one, and the next-to-high-order field is used for bank select, as in IV bus sources. This is designated the  $D_1$ -field, with the other three bits being the  $D_0$ -field and specifying the amount of left shift to be applied to the result from ALU.

Note that is it not possible to shift data destined for an internal register under D-field control.

#### 2.3.4 Rotate and Length Field

Rotation of IV bus data is achieved by the proper coding of the  $S_0$ -Field. In the case of a register-to-register (Format RR) operation, where both the S-field and D-field specify Internal Registers, then the R/L-field is interpreted as a rotation to be performed on the source data before it is presented to the ALU. In this case, no masking of data is possible.

In the case of a Format RB, JB, or XB instruction, the R/L-field is used as a Length field to control the number of bits of the I/O data field (data source or destination on the IV bus). Refer to Figures 2-5 and 2-6 for the details of the bits allowed to pass the Mask or Merge logic.

For an IV Bus-to-Register instruction, the L-field specifies the length of source data allowed to pass the Mask logic and enter the ALU with the high order bits being set to zero. Note that the source data could have been right-rotated after input from the IV bus in accordance with the S-field.

For a Register-to-IV Bus instruction, the L-field specifies the length of the destination field whose least significant bit is specified by  $\mathsf{D}_0$ .

For an IV Bus-to-IV Bus instruction, the L-field specifies the length of both the source data passing the Mask logic, and the destination data to be replaced by the Merge logic.

#### 2.3.5 Instruction Sequence

Sequential execution of instructions in the program memory can be deviated from by use of the XEC, NZT and JMP instructions.

The Address Register and Program Counter are used to generate addresses for accessing an instruction from program storage. The instruction address is formed in any one of four ways:

USERS MANUAL 8X305

For all except the JMP, XEC, and a "satisfied" NZT instruction, the Program Counter is incremented by one and placed in the Address Register and the Program Counter.

- For the JMP instruction, the 13-bit A-field contained in the JMP instruction word replaces the contents of the Address Register and the Program Counter.

- For the XEC instruction, the Address Register is loaded with the high-order bits of the Program Counter and the low-order bits modified as follows:

XEC using IV Bus Data: low order 5-bits of ALU output replaces counterpart bits in Address Register. The Program Counter is not modified.

XEC using Data from Internal Register: low order 8-bits of ALU output replaces counterpart bits in Address Register. The Program Counter is not modified.

For a "satisfied" NZT instruction, the high order bits of the Address Register and the Program Counter are loaded from the Program Counter and the low order 5-bits (NZT source is IV Bus Data) or low order 8-bits (NZT source is an Internal Register) are loaded with the literal value specified by the J-field of the instruction word. Refer to Chapter 3 for a more complete discussion of individual instructions.

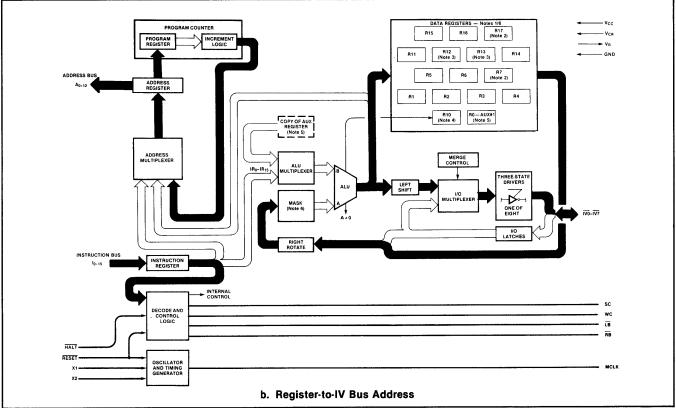

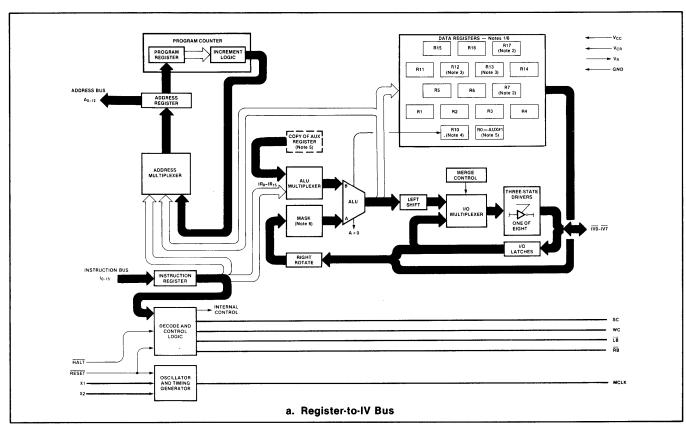

## 2.4 DATA FLOW DURING INSTRUCTION EXECUTION

This section illustrates the major paths of data flow within the device during execution of instructions from each of the general formats. This is illustrated diagrammatically in each case by using a block diagram on which the path has been outlined. This is not an exhaustive collection of all possible data paths. Refer to Figure 2-8 for the format being used in each case.

The details illustrated serve as aids in understanding internal functions of the 8X305. They are not required for understanding normal programming of the 8X305.

Throughout this section, the numeric examples are given in terms of octal values within each operand field, and not in pure octal.

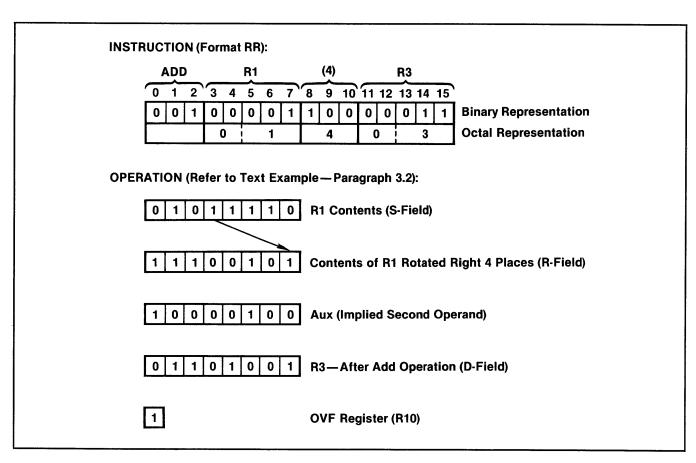

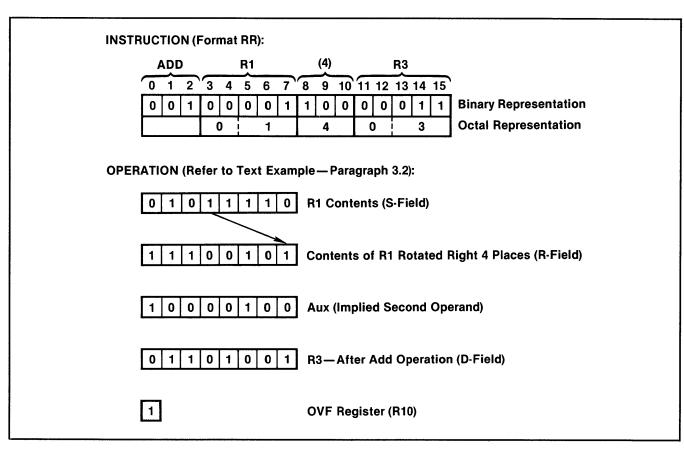

#### 2.4.1 Operations That Use Format RR

Operations that use Format RR are Register-to-Register and Register-to-IV Bus Address; either operation can be invoked by a MOVE, AND, ADD, or XOR instruction. Paths for the address, the instruction, the data flow, and the required control lines for a Register-to-Register operation are shown in Figure 2-10a. A summary of operational parameters pertaining to Figure 2-10a are given below.

Format: See Format RR, Figure 2-8.

Description: Contents of the register specified by S are right-rotated as specified by R and placed in the destination register specified by D. The contents of the source register remain unchanged; original contents of the destination register are lost. Overflow (OVF) Register R10 is updated if Op Code specifies an ADD operation; this register cannot be used as a destination. Also, the Copy of AUX Register is used only for AND, ADD, and XOR instructions—not for MOVE. (Note: As defined by the RR format, registers

R7 and R17 can only be used as a *Source* for a Register-to-Register operation; this is not, however, a hardware limitation—see Figure 2-10b and discussion below.)

Permitted Operand Values:

S = R0-R17

R = 0.7

D = R0-R6, R11-R16, R7/R17 (refer to Note in Description)

Paths for the address, the instruction, the data flow, and the required control lines for a Register-to-IV Bus Address operation are shown in Figure 2-10b. Operational parameters for this operation are identical to those for a Register-to-Register operation, except that one or the other of Registers R7 (Left Bank) or R17 (Right Bank) must always be the destination. In any case, the final result is output on the IV bus as an enabling address and stored in the destination register as well. The last step in the operating sequence puts the contents of the Address Register into the Program Counter.

**JUNE 1982**

BIPOLAR LSI DIVISION

8X305 **USERS MANUAL**

Figure 2-10. Data Flow for RR Format—See Figure 2-8 For Instruction Format

USERS MANUAL 8X305

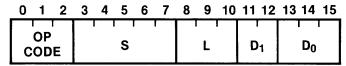

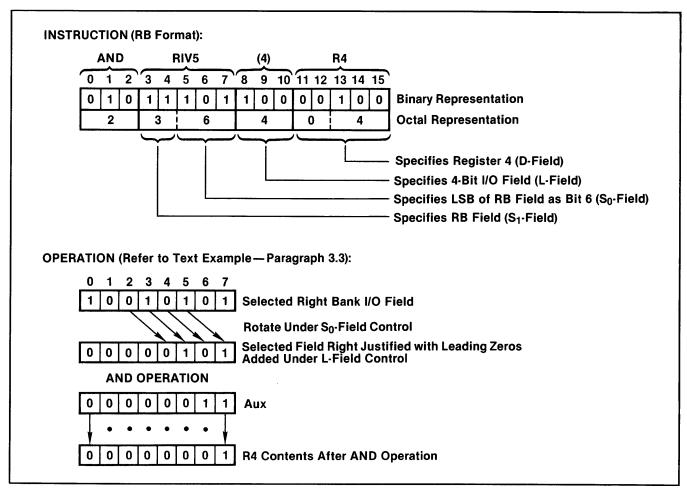

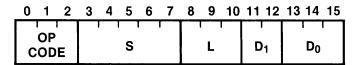

#### 2.4.2 Operations That Use Format RB

Operations that use Format RB are Register-to-IV Bus, IV Bus-to-Register, IV Bus-to-IV Bus, and IV Bus-to-IV Bus Address; any one of these operations can be invoked by a MOVE, AND, ADD, or XOR instruction.

#### Register-to-IV Bus

Paths for the address, the instruction, the data flow, and the required control lines for a Register-to-IV Bus operation are shown in Figure 2-11a. A summary of operational parameters pertaining to Figure 2-11a is given below.

Format: See Format RB, Figure 2-8

Description: Move the least significant L bits of the register specified by S to a variable length field of the IV bus as specified by D<sub>0</sub> and D<sub>1</sub>, where,

S = the source register

L = number of bits in masked data field to be merged with existing byte of IV data.

$D_0$  = bit position of IV data with which LSB of processed data field is to be aligned; this implies that the data field is left-shifted until bit 7 is aligned with bit  $D_0$  of the IV bus.

D<sub>1</sub> = specifies bank of IV bus; 2 specifies Left Bank and 3 specifies Right Bank.

The order of operation is:

- Copy contents of selected IV data into I/O latches.

- · Read contents of source register.

- Left shift source data field as specified by D<sub>0</sub>.

- Merge least significant L bits with data in I/O latches

- Output modified 8-bit data field to selected IV device as specified by D<sub>1</sub>.

Observe that the original IV data outside the merged L-bit field remains unaltered; also, the contents of the source register remain unchanged. Overflow (OVF) Register R10 is updated if Op Code specifies an ADD operation; the Copy of AUX Register is used only for AND, ADD, and XOR instructions—not for MOVE.

Permitted Operand Values:

S = R0-R17

L = 0.7 (L = 0 selects an 8-bit field)

$D_0 = 0.7$

$D_1 = 2 \text{ or } 3$

#### IV Bus-to-Register

Paths for the address, the instruction, the data flow, and the required control lines for an IV Bus-to-Register operation are shown in Figure 2-11b; a summary of operational parameters pertaining to this figure is given below.

Format: See Format RB, Figure 2-8

Description: Move the least significant L bits of the IV data specified by  $S_0$  and  $S_1$  to the least significant L bits of the destination register specified by D, where.

S<sub>0</sub> = least significant bit of IV data field after rotation

S<sub>1</sub> = specifies bank of IV bus; 2 specifies Left Bank and 3 specifies Right Bank.

L = number of bits in masked data field.

D = the destination register.

The order of operation is:

- Read contents of selected IV data as specified by S<sub>1</sub> into I/O latches.

- Right rotate the input data field as specified by So.

- Mask the least significant L bits of the rotated data.

- Move masked field to the least significant L bits of destination register with zeroes in the unmasked positions.

Overflow (OVF) Register R10 is updated if Op Code specifies an ADD operation; this register cannot be used as a destination. Also, the Copy of AUX Register is used only for AND, ADD, and XOR instructions—not for MOVE.

Permitted Operand Values:

$S_0 = 0.7$

$S_1 = 2 \text{ or } 3$

L = 0.7 (L = 0 selects an 8-bit field)

D = R0-R6, R11-R16

USERS MANUAL 8X305

Figure 2-11. Data Flow for RB Format—See Figure 2-8 For Instruction Format

USERS MANUAL 8X305

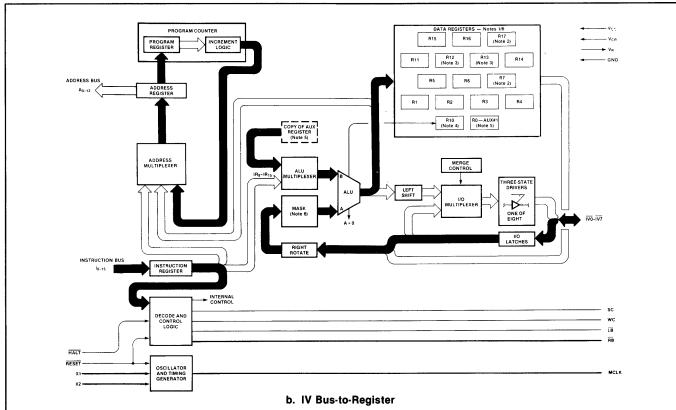

#### IV Bus-to-IV Bus

Paths for the address, the instruction, the data flow, and the required control lines for an IV Bus-to-IV Bus operation are shown in Figure 2-11c; a summary of operational parameters pertaining to this figure is given below.

Format: See Format RB, Figure 2-8

Description: Move the variable length field specified by  $S_0$ ,  $S_1$ , and L to the field and bank specified by  $D_0$ ,  $D_1$ , where,

$S_0$  = the LSB of the rotated IV input data field.

S<sub>1</sub> = specifies input bank of IV bus; 2 specifies Left Bank and 3 specifies Right Bank.

L = number of bits in masked data field to be merged with existing byte of IV data.

$D_0$  = bit position of IV output data with which LSB of processed data field is to be aligned; this implies that the data field is left-shifted until bit 7 is aligned with bit  $D_0$  of the IV bus.

D<sub>1</sub> = specifies output bank of IV bus; 2 specifies Left Bank and 3 specifies Right Bank.

The order of operation is:

- Read contents of selected IV data as specified by S<sub>1</sub> into I/O latches.

- Right rotate the input data field as specified by So.

- Mask the least significant L bits of the rotated data.

- Left shift source data field as specified by D<sub>0</sub>.

- Merge least significant L bits with data in I/O latches.

- Output modified 8-bit data field to selected IV device as specified by D<sub>1</sub>.

Overflow (OVF) Register R10 is updated if Op Code specifies an ADD operation; the Copy of AUX register is used only for AND, ADD, and XOR instructions—not for MOVE.

Permitted Operand Values:

$S_0 = 0.7$   $S_1 = 2$  or 3 L = 0.7 (L = 0 selects an 8-bit field)  $D_0 = 0.7$  $D_1 = 2$  or 3

#### IV Bus-to-IV Bus Address

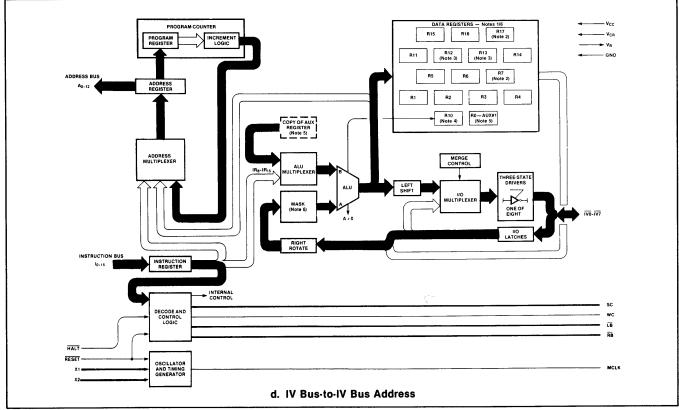

Paths for the address, the instruction, the data flow, and the required control lines for an IV Bus-to-IV Bus Address operation are shown in Figure 2-11d. A summary of operational parameters pertaining to Figure 2-11d is given below.

Format: See Format RB, Figure 2-8.

Description: Copy data from IV Bus as specified by  $S_0$  and  $S_1$

L = number of bits in masked field.

D =destination bank for processed data; R7 specifies Left Bank and R17 specifies Right Bank

Note: The output address is also stored in the selected register, R7 or R17.

The order of operation is:

- · Read input data from the IV bus.

- Right rotate input data as specified by S<sub>0</sub>.

- Mask the least significant L bits. (Note: Bits outside the mask in the output field are set to zero.)

- Output result to designated bank of the IV bus as an enabling address.

Observe that the output address data is written into Register R7 (Left Bank) or R17 (Right Bank) and can subsequently be accessed as a source. Overflow (OVF) Register R10 is updated if Op Code specifies an ADD operation; the Copy of AUX Register is used only for AND, ADD, and XOR instructions—not for MOVE.

Permitted Operand Values:

$S_0 = 0.7$   $S_1 = 2$  or 3 L = 0.7 (L = 0 selects an 8-bit field) D = 0.7

## USERS MANUAL 8X305

Figure 2-11 (Continued)

#### 2.4.3 Operations That Use Format JR

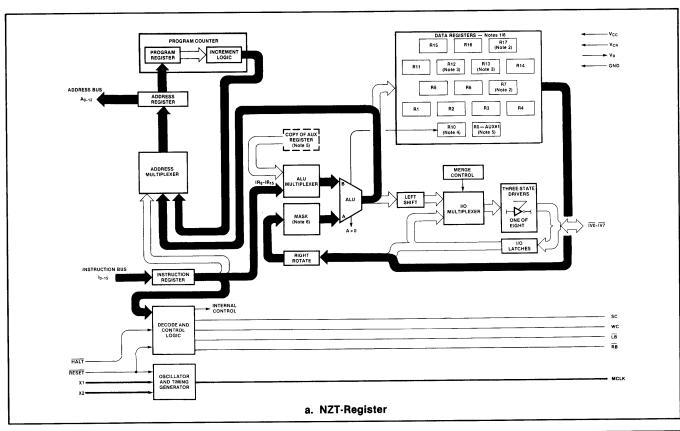

Operations that use Format JR are NZT-Register and XEC-Register.

#### **NZT-Register Operation**

Paths for the address, the instruction, the data flow, and the required control lines for the NZT-Register operation are shown in Figure 2-12a. A summary of operational parameters pertaining to the NZT-Register instruction is given below.

Format: See Format JR, Figure 2-8.

Description: If  $S \neq 0$ , jump to address formed by replacing 8 LSBs of Address and Program Registers with value of J field; if S=0, increment Program counter by one, where,

- S = register which is subject of test (A input to ALU)

- J =8-bit integer that modifies address

The order of operation is:

- · Read contents of source register.

- Test contents of source register for all zeroes.

- If contents are not zero, replace 8-LSBs of Address Register and Program Counter with 8-bit integer in J-field.

- If contents are zero, increment Program Counter by one.

Permitted Operand Values:

- S = R0-R17

- $J = 0.377_8$

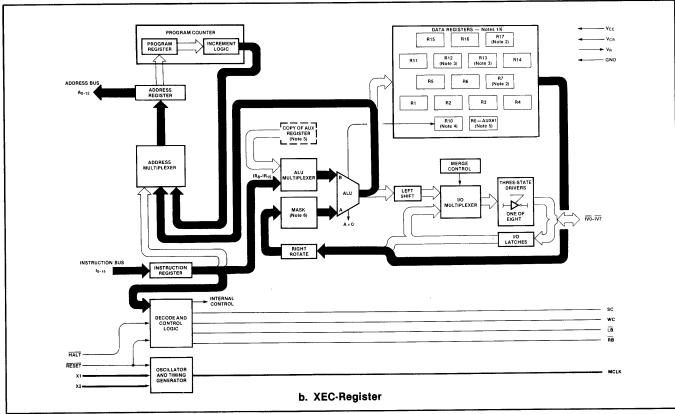

#### **XEC-Register Operation**

Paths for the address, the instruction, the data flow, and the required control lines for the XEC-Register operation are shown in Figure 2-12b. A summary of operational parameters pertaining to the XEC-Register is given below.

Format: See Format JR, Figure 2-8

Description: Execute instruction at the address formed by replacing 8 LSBs of Address Register with the 8-bit sum of J and the contents of register specified by S, where,

- S = source register

- J =8-bit integer used in address modification

The order of operation is:

- · Read contents of source register

- Form 8-bit sum by adding value of J-field to contents of source register

- · Modify Address Register with the 8-bit sum

The Program Counter is not altered by the XEC instruction, that is, the original address within the 256 instruction page (0  $\leq$  J  $\leq$  3778) is retained. During the instruction to be executed, the Program Counter is incremented by one in the normal manner to point to the instruction following the XEC instruction. However, if the executed instruction is a JMP or NZT, the Program Counter can be changed to the jump address and instruction execution does not return to the address following the XEC instruction.

Permitted Operand Values:

- S = R0-R17

- J = 0-377<sub>8</sub> (When sum of S + J is greater than 255<sub>10</sub> (377<sub>8</sub>), only the 8-LSBs are used; Overflow (OVF) Register R10 is not changed.)

## USERS MANUAL 8X305

Figure 2-12. Data Flow for JR Format—See Figure 2-8 for Instruction Flow

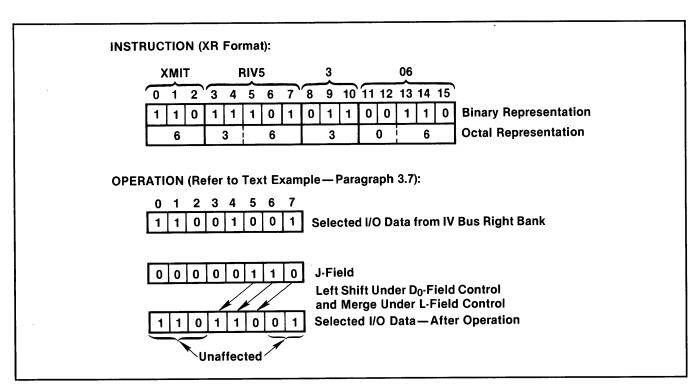

#### 2.4.4 Operations That Use Format XR

Operations that use Format XR are XMIT-Register, XMIT-IV Address, and XMIT-8 Bits Immediate IV Bus.

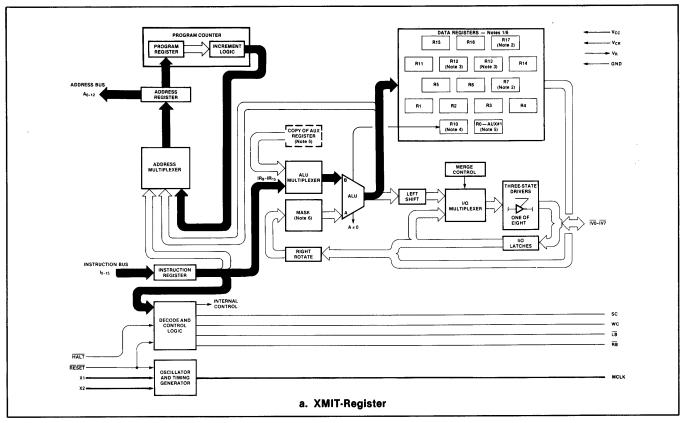

#### **XMIT-Register**

Paths for the address, the instruction, the data flow, and the required control lines for the XMIT-Register instruction are shown in Figure 2-13a. Operational parameters for these instructions are shown below.

Format: See Format XR, Figure 2-8

Description: Store value of 8-bit integer specified by J in register specified by D.

Permitted Operand Values:

D = R0-R6, R11, R14-F16

$J = 0-377_8$

#### **XMIT-IV Address**

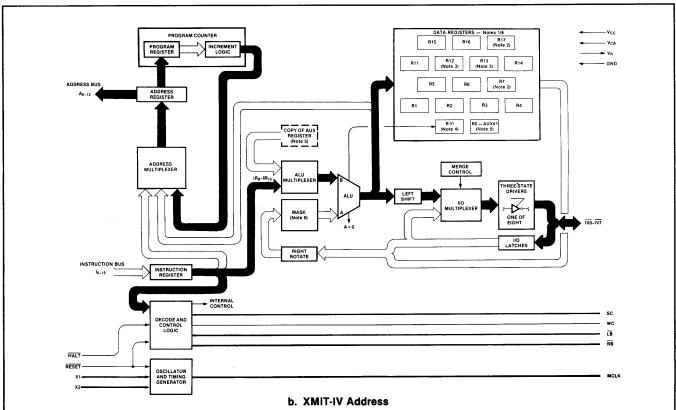

Paths for the address, the instruction, the data flow, and the required control lines for the XMIT-IV Address instruction are shown in Figure 2-13b. Operational parameters for this instruction are described below.

Format: See Format XR, Figure 2-8

Description: Enable I/O device on the IV bus bank specified by D, whose address is the 8-bit integer specified by J, where,

D = destination bank of IV bus for address data

J =8-bit address of port to be enabled

Permitted Operand Values:

D = 07 (Left Bank) or 17 (Right Bank)

$J = 0.377_8$

Note: The address is also stored in the selected register, R7 or R17.

**JUNE 1982**

**BIPOLAR LSI DIVISION**

#### 8X305 **USERS MANUAL**

Figure 2-13. Data Flow for XR Format — See Figure 2.8 for Instruction Format

USERS MANUAL 8X305

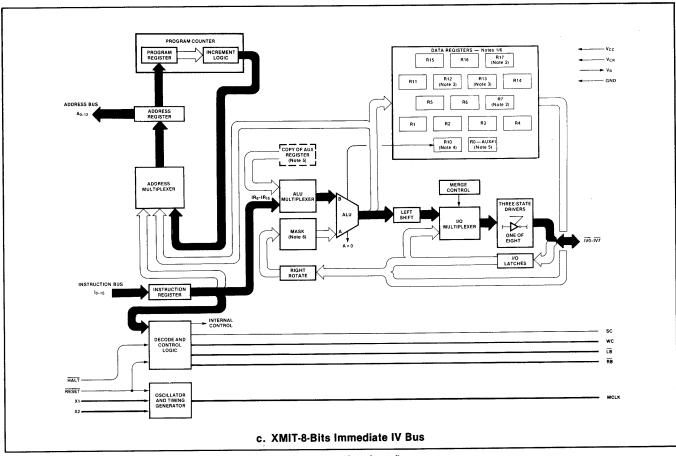

#### XMIT-8 Bits Immediate IV Bus

Paths for the address, the instruction, the data flow, and the required control lines for the XMIT-8 Bits Immediate IV Bus are shown in Figure 2-13c. Operational parameters for this instruction are described below.

Format: See Format XR, Figure 2-8

Description: Transmit value of 8-bit integer specified by J to Left Bank (R12) or to Right Bank (R13) as data. The contents of R12 and R13 remain unchanged.

Permitted Operand Values:

D = 12 (Left Bank) or 13 (Right Bank)

$J = 0.377_8$

8X305

JUNE 1982 **BIPOLAR LSI DIVISION**

## **USERS MANUAL**

Figure 2-13 (Continued)

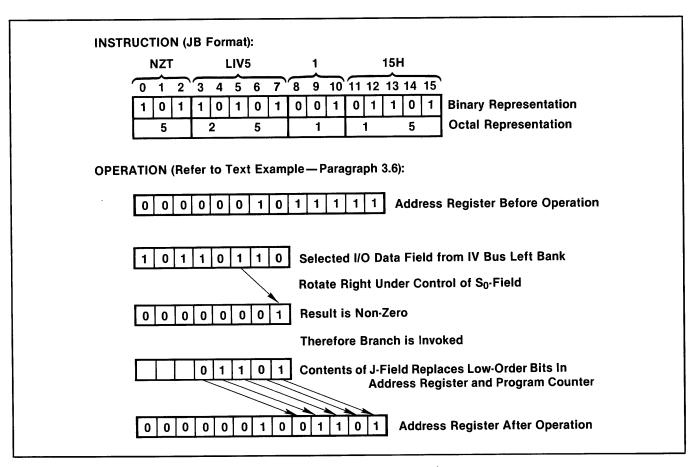

#### 2.4.5 Operations That Use Format JB

Operations that use Format JB are NZT-IV Bus and XEC-IV Bus.

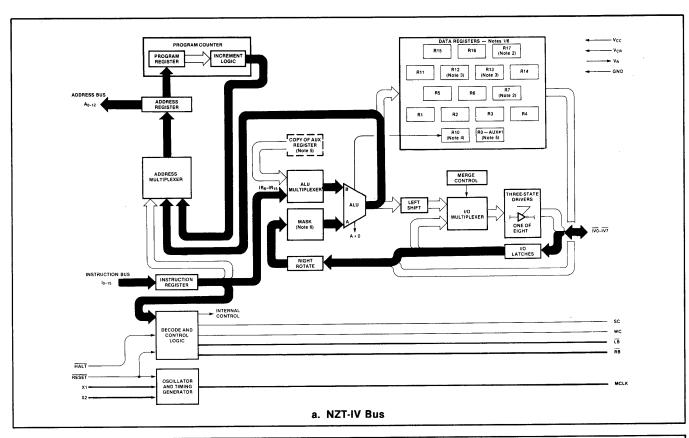

#### NZT-IV Bus

Paths for the address, the instruction, the data flow, and the required control lines for the NZT-IV Bus instruction are shown in Figure 2-14a. A summary of operational parameters pertaining to this instruction is shown below.

Format: See Format JB, Figure 2-8

Description: If contents of IV bus source data field as specified by S and L is non-zero, replace 5 LSBs of both Address Register and Program Counter with the 5-bit integer specified by J; if the contents of the source field is zero, increment the Program Counter by one, where,

S<sub>0</sub> = least significant bit of IV input data field after rotation.

S<sub>1</sub> = specifies bank of IV bus; 2 specifies Left Bank and 3 specifies Right Bank.

L = number of bits in masked field.

J =5-bit integer used in address modification.

The order of operation is:

- Read contents of selected IV data, as specified by S<sub>1</sub>, into I/O latches.

- Right rotate the input data field as specified by S<sub>n</sub>.

- Mask the least significant L bits of the rotated data.

- · Test contents of masked field.

- If contents of masked field are not zero, replace 5-LSBs of Address Register and Program Counter with 5-bit integer in J-field.

Permitted Operand Values:

$S_0 = 0.7$

$S_1 = 2 \text{ or } 3$

L = 0.7

$J = 0.37_8$

#### **XEC-IV Bus**

Paths for the address, the instruction, the data flow, and the required control lines for the XEC-IV Bus instruction are shown in Figure 2-14b. A summary of operational parameters pertaining to this instruction is shown below.

Format: See Format JB, Figure 2-8

Description: Execute instruction at the address formed by replacing 5-LSBs of Address Register with the 5-bit sum of J and the contents of the IV Bus field, as specified by S and L, where,

S<sub>0</sub> = least signicant bit of IV input data field after rotation.

S<sub>1</sub> = specifies bank of IV bus; 2 specifies Left Bank and 3 specifies Right Bank.

L = number of bits in masked field.

J =5-bit integer used in address modification.

The order of operation is:

- Read contents of selected IV data as specified by S<sub>1</sub> into I/O latches.

- Right rotate the input data field as specified by S<sub>0</sub>.

- Mask the least significant L bits of the rotated data.

- Add masked field to 5-bit integer specified by J.

- Replace 5-LSBs of Address Register with 5-bit result of the ADD operation.

The Program Counter is not altered by the XEC instruction, that is, the original address within the page (0  $\leq$  J  $\leq$  378) is retained. During the instruction to be executed, the Program Counter is incremented by one in the normal manner to point to the instruction following the XEC instruction. However, if the executed instruction is a JMP or NZT, the Program Counter can be changed to the jump address and instruction execution does not return to the address following the XEC instruction.

Permitted Operand Values:

$S_0 = 0.7$

$S_1 = 2 \text{ or } 3$

L = 1.5

J = 0-37<sub>8</sub> [When sum of S + J is greater than 37<sub>8</sub> only the 5-LSBs are used; overflow (OVF) Register R10 is not changed.]

JUNE 1982 **BIPOLAR LSI DIVISION**

## 8X305 **USERS MANUAL**

Figure 2-14. Data Flow for JB Format—See Figure 2.8 for Instruction Formats

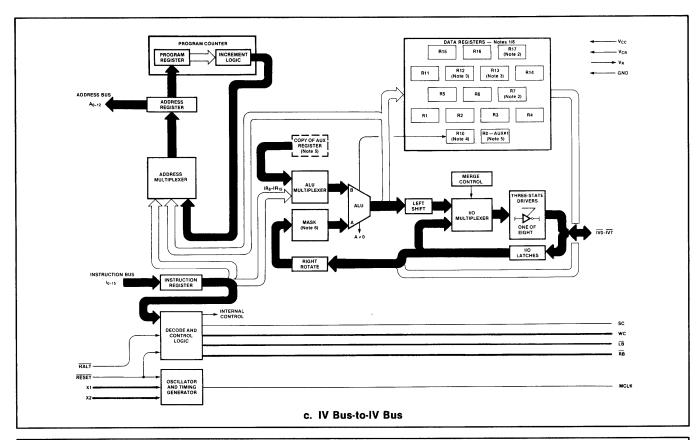

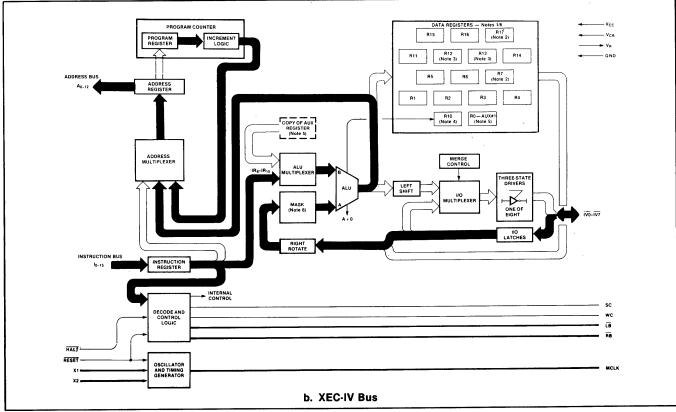

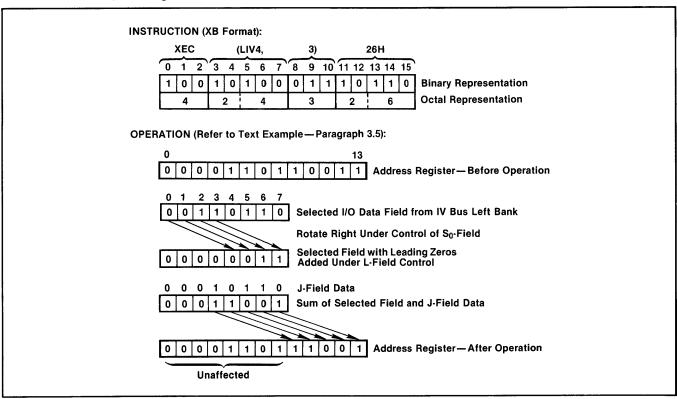

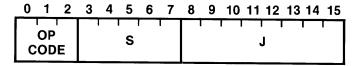

### 2.4.6 Operation That Uses Format XB

The XB format is used to implement a XMIT Variable-Bit Field Immediate IV Bus instruction. Paths for the address, the instruction, the data flow, and the required control lines for this operation are shown in Figure 2-15; operational parameters are described below.

Format: See Format XB, Figure 2-8

Description: Transmit the least significant L bits of the field to the L-bit field of the IV bus specified by D; if L is greater than 5-bits, the most significant bits of the destination field are filled with zeroes. Operand designations are,

$D_0$  = bit position of IV data with which LSB of J-field data is to be aligned; this implies that the input data field is left-shifted until bit 7 is aligned with bit  $D_0$ .

D<sub>1</sub> = specifies bank of IV bus; 2 specifies Left Bank and 3 specifies Right Bank.

L = number of bits in destination field.

J =5-bit integer.

The order of operation is:

- Read contents of destination IV port into I/O latches.

- · Read 5-LSBs of instruction word.

- Left shift data field as specified by D<sub>0</sub>.

- Merge shifted field of data, as specified by L, with contents of I/O latches and output result to IV bus. (Note: Data in the I/O latches outside the field specified by D<sub>0</sub> and L is not altered.)

Permitted Operand Values:

$D_0 = 0.7$

$D_1 = 2 \text{ or } 3$

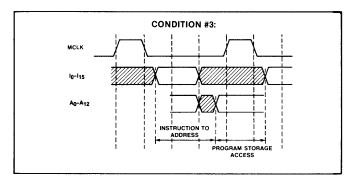

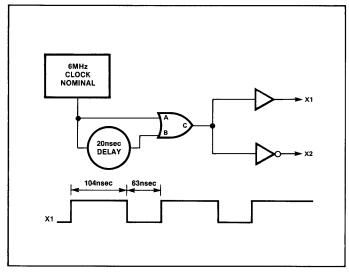

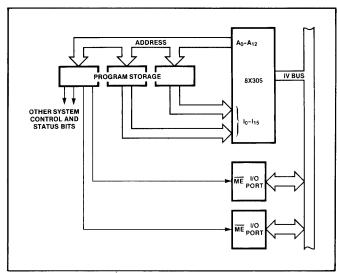

L = (L = 0 selects an 8-bit field)