# SIGNETICS FIELD PROGRAMMABLE LOGIC ARRAYS

#### Gentlemen:

Thank you for your interest in Signetics' family of field programmable logic arrays. The enclosed FPLA brochure contains device related information which should facilitate your understanding of the structure and applications of these new generation LSI devices.

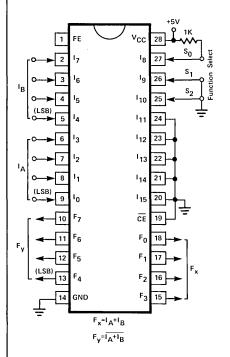

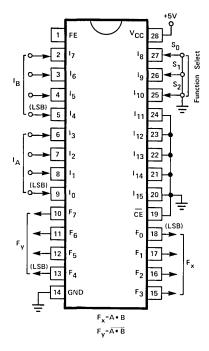

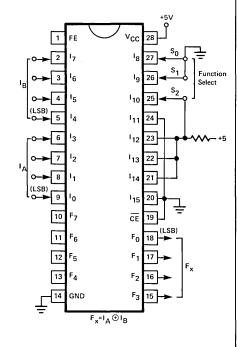

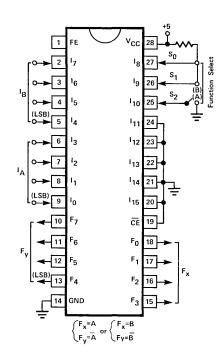

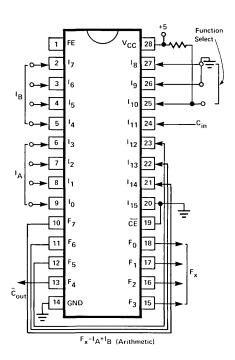

As a preview of FPLA versatility, page 59 of the brochure contains the program table stored in a sample device for demonstrating that an FPLA is a general purpose logic tool, which could be called upon to emulate the function of an ALU... almost! A device thus programmed performs the OR, AND, Exclusive-OR, Mux and Add (with serial carry) of two 4-bit words. These functions are selected by connecting the FPLA as shown on page 60.

Both Signetics FPLAs are available now in either ceramic (I) or power plastic (N) packages, with unit price related to quantity as follows (commercial temperature range):

| QUANTITY     | 1-24    | 25-99   | 100-999 |

|--------------|---------|---------|---------|

| N82S100/101N | \$17.50 | \$14.50 | \$11.50 |

| N82S100/101I | 30.00   | 24.60   | 19.45   |

We have in-house programming capability to supply custom programmed parts within 7 days after receipt of your program table. Each custom pattern carries a one time charge of \$25.00.

Field programming equipment is currently available to satisfy your programming needs as your usage develops.

| PROGRAMMING ENVIRONMENT            | MODEL    | MANUFACTURER                          | PRICE     |

|------------------------------------|----------|---------------------------------------|-----------|

| Prototyping and Qualification      | LTC-F100 | Signetics (408) 739-7700              | \$ 345.00 |

| Pilot Production and Field Support | PR-100   | Curtis Electro-Devices (415) 964-3136 | 1299.00   |

| Volume Production                  | X        | Data I/O<br>(206) 455-3990            | 8000.00   |

In some applications, marginal design tradeoffs can be resolved in favor of FPLAs by compressing the logic truth table to a minimum number of product terms. Signetics has a computer program for executing a practical minimization algorithm, which it offers as a free service to its customers.

Both Signetics FPLAs have been designed for operation over the full Mil-Temp range, and military parts are available in standard S-grade and S/883B.

Please, do not hesitate to contact me if you need further information.

Napoleone Cavlan

Applications Manager

Bipolar Memories

hapoleone Cavlan

# SIGNETICS FIELD PROGRAMMABLE LOGIC ARRAYS

Since the practical introduction of microprogramming in the last decade or so, microcode has progressively displaced random logic in step with the growing availability of user Programmable Read-Only Memories (PROMs). However, even with PROMs, designers soon realized that their rigid addressing structure made them unsuitable in a wide variety of applications which could greatly benefit from a structured logic approach.

Recently, microprocessors have provided a quantum jump in design flexibility in applications requiring about 30 IC packages, and beyond. When fewer packages are required, the inherent speed limitation, software requirements, and support circuitry of microprocessors place them out of range of a broad spectrum of applications.

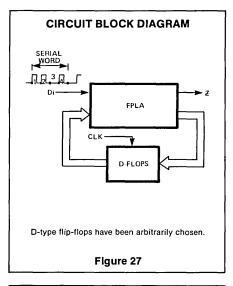

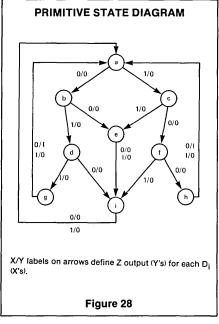

These in general involve algorithms which require a high speed logic decision based on a large number of controlling variables. It is here that we step into the basic domain of Field Programmable Logic Arrays, encompassing applications in microprogramming, code conversion, random logic, look-up and decision tables, high speed character generators, etc. Moreover, when combined with a few storage elements (flip-flops), FPLAs can implement powerful logic machines of the Mealy/Moore form for the realization of finite state sequential controllers for traffic, process, peripheral devices, and other similar applications.

# TABLE OF CONTENTS

| Chapter 1 INTRODUCTION                    | 7  |

|-------------------------------------------|----|

| Ni-Cr Technology Matures                  | 9  |

| What is an FPLA?                          |    |

| FPLA: Logic or Memory?                    |    |

| FPLA Resources                            | 13 |

| Chapter 2 DATA SPECIFICATIONS             | 15 |

| 82S100/82S101 Data Specifications         | 17 |

| Chapter 3 PROGRAM/VERIFY PROCEDURE        | 27 |

| Programming Signetics' FPLA               |    |

| Editing Signetics' FPLA                   | 29 |

| Generating the FPLA Program Table         |    |

| Disposition of Unused Inputs              |    |

| Verifying the Stored Program              |    |

| Array Verify                              |    |

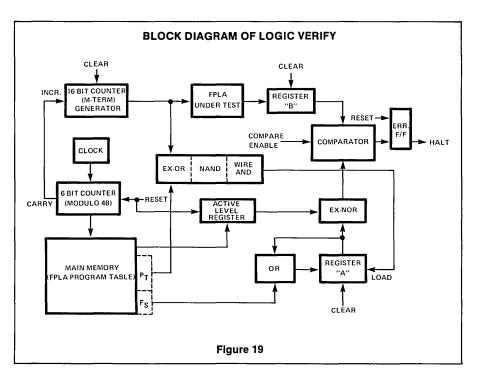

| Logic Verify                              | 34 |

| Chapter 4 USAGE AND LIMITATIONS           | 37 |

| Logic Compression                         | 39 |

| Asynchronous Sequential Logic             |    |

| Synchronous Sequential Logic              |    |

| Dealing with Device Limitations           |    |

| Product Term Expansion                    |    |

| Input Variable Expansion                  |    |

| Output Expansion                          | 46 |

| Chapter 5 APPLICATIONS                    |    |

| Fault Monitor Networks                    |    |

| Fast Multibit Shifter                     |    |

| Priority Resolver and Latch               |    |

| Memory Overlays                           |    |

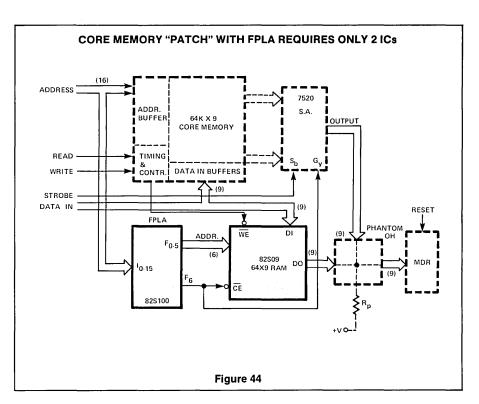

| Core Memory Patch                         |    |

| Subroutine Address Map and Branch Logic   |    |

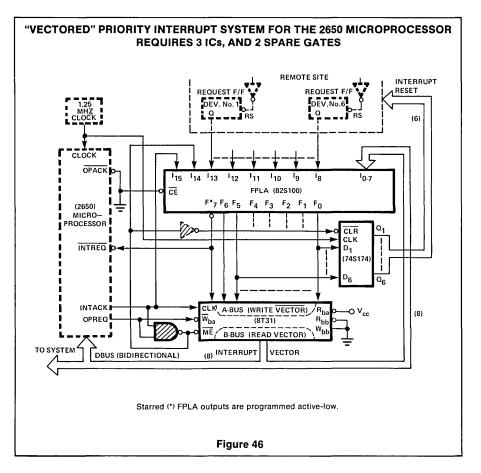

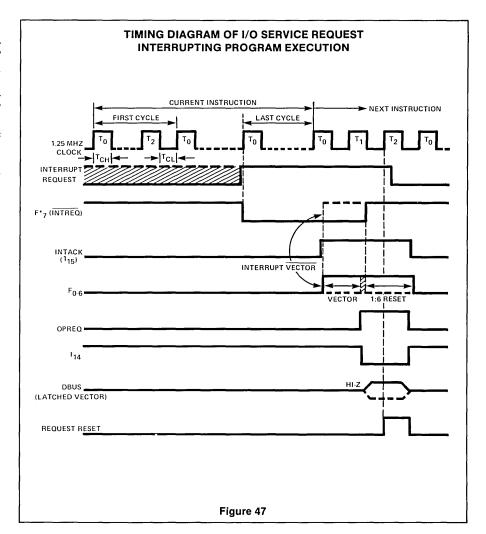

| "Vectored" Priority Interrupt System      | 53 |

| Chapter 6 APPENDICES                      |    |

| Appendix A Program Table of Sample Device | 59 |

| Appendix B Connections for Sample Device  |    |

| SALES OFFICES                             |    |

# CHAPTER I INTRODUCTION

signetics

#### **NI-CR TECHNOLOGY MATURES**

Nichrome was the first material to give rise to stable, low current fuses with excellent fusing characteristics, easily reproducible. However, as with all new developments. Nichrome technology had to undergo a learning curve, with each advance signaling the advent of more complex and higher performance devices, without a compromise in reliability. It soon became apparent that each incremental step in complexity implied a fuller understanding of the fusing phenomenon. Accordingly, fusible link technology has been intensively investigated by Signetics over the last 6 years (see Signetics' Prom Reliability page 39), giving rise to the broadest line of PROMs in the industry, and presently, the addition of a family of Field Programmable Logic Arrays (FPLAs), designed for both commercial and military temperature ranges.

#### WHAT IS AN FPLA?

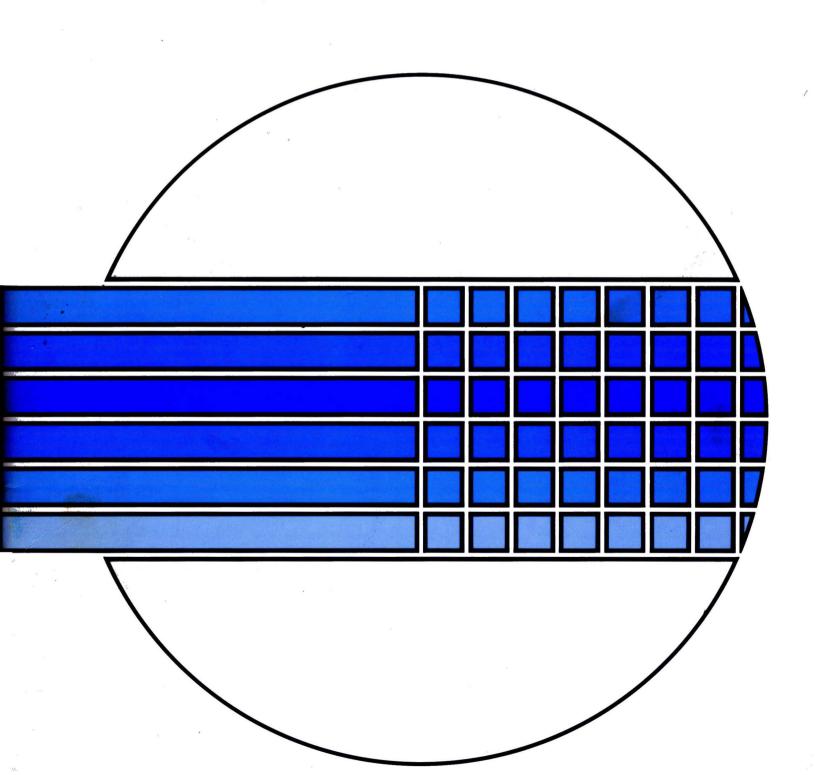

Signetics' FPLAs are fast, user programmable, TTL logic elements with memory, which can streamline logic system design by integrating the equivalent of 528 TTL gates in 196 packages into a *single* IC package.

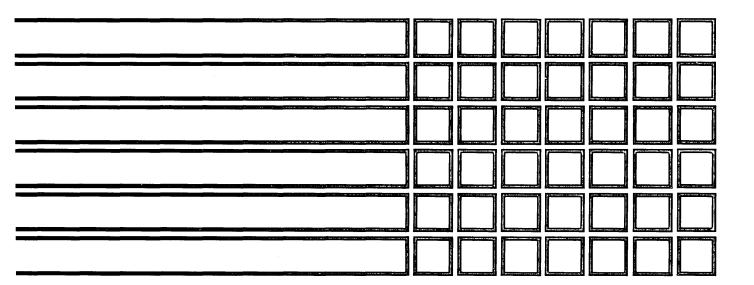

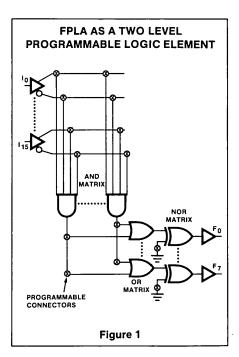

In terms of logic, the FPLA is a two level AND-OR, AND-NOR combinatorial logic element, consisting of a system of logic gates with programmable inputs and outputs as shown in Figure 1. These, by means of on-chip programmable connectors, enable the user to quickly implement 8 logic functions with a maximum of 48 product (AND) terms, involving up to 16 input variables.

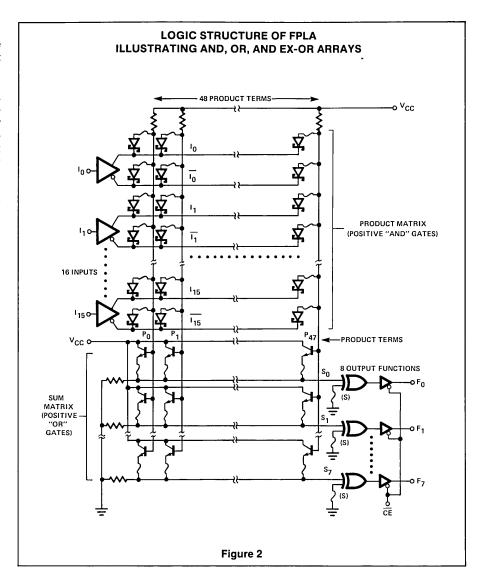

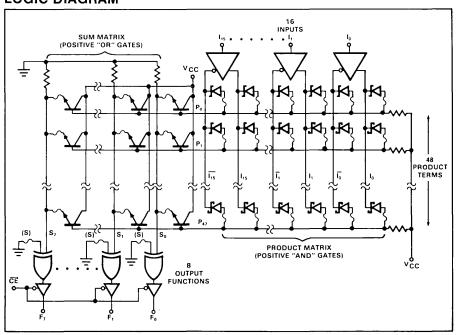

A more detailed organization of the FPLA is shown in Figure 2. The device consists of an upper resistor-diode AND matric containing 48 product term columns (P-terms), and a lower emitter-follower OR matrix containing 8 sum term rows (S-terms), one for each output function. Each P-term in the AND matrix is initially coupled to 16 true and complement input variables via 32 fusible Ni-Cr links for programming any desired input combination.

Each P-term is also coupled to each S-term in the OR matrix through an emitter fuse, for pulling the summing node to a high level when the P-term is activated. Each S-term in turn is coupled to its respective output via an Ex-OR gate, which has programmable transmission polarity by means of an input to ground through a fusible link. fusible link.

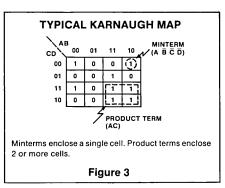

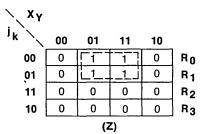

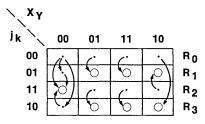

Selective programming of the internal links allows the user to create specific logic paths for producing any logic functions as a sum of products, defined in the typical Karnaugh Map of Figure 3.

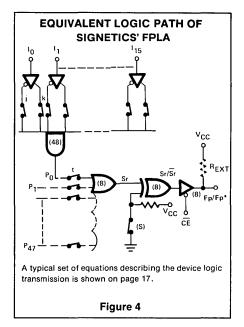

The transmission through the FPLA can be traced along the equivalent logic path shown in Figure 4. From this figure, it is apparent that Signetics' FPLA is basically a two level logic element. The first level produces 48 internal AND functions, Pothrough P47, of up to 16 logic input variables, or their complement. The second level produces 8 OR output functions, Fothrough F7, each involving up to 48 of the internally generated AND terms. Alternately, if desired, this second logic level can be programmed to provide 8 NOR output functions F0\* through F7\*. However, for

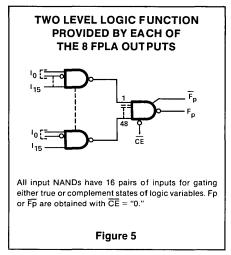

each of the 8 outputs, either the function  $F_p$  (active-high), or  $F_p^{\star}$  (active-low) is available, but not both. The required output polarity is programmed by the user via link (S). Th overall logic function provided by each FPLA output is summarized in Figure 5.

When viewed strictly as a logic element, the FPLA can be used to implement sets of logic equations of the type:

$$\begin{split} F_0 &= I_0 + I_1 \, \overline{I}_5 + I_2 \, \overline{I}_3 \, I_7 \, \dots \\ F_1 &= \overline{I}_0 + I_1 \, \overline{I}_5 + I_6 \, I_7 \, I_8 \, \dots \\ \overline{F}_2 &= \overline{I}_2 + I_7 \, I_5 + \dots \, \text{etc.} \end{split}$$

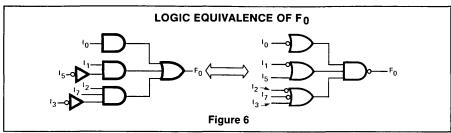

or, by use of De Morgan's theorem, their equivalent as for  $F_0$ :

$$F_0 = (\overline{I}_0) (\overline{I}_1 + I_5) (\overline{I}_2 + I_3 + \overline{I}_7) \dots$$

This is readily shown in the logic equivalence of Figure 6.

Generally FPLAs are effectively used in design situations involving many input variables and few active logic states; and, with a maximum access time of 50ns, the FPLA is a practical alternative to the long logic chains necessary when dealing with several input variables.

The following example is a brief, but concise, illustration of how to integrate random logic with discrete gates into a Signetics' FPLA. Given the set of logic equations F<sub>1-4</sub> below:

$$\begin{aligned} F_1 &= X_1 + \overline{X}_2 \overline{X}_3 \\ F_2 &= X_2 + \overline{X}_1 \overline{X}_3 \\ F_3 &= X_3 + \overline{X}_1 \overline{X}_2 \\ F_4 &= \overline{X}_1 X_3 + \overline{X}_1 \overline{X}_2 \end{aligned}$$

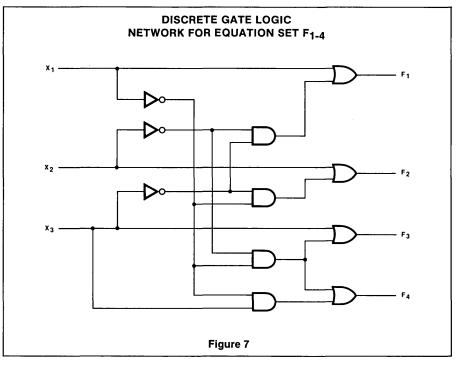

These can be implemented with discrete gates as in the AND-OR-NOT logic network of Figure 7.

This method is practical for simple systems; but in more complex applications, it soon produces a distributed logic network with many IC packages and types, difficult to design, troubleshoot and modify.

On the other hand, the same set of equations can be easily coded in an FPLA Program Table (see page 23) and programmed in a device using inexpensive field equipment.

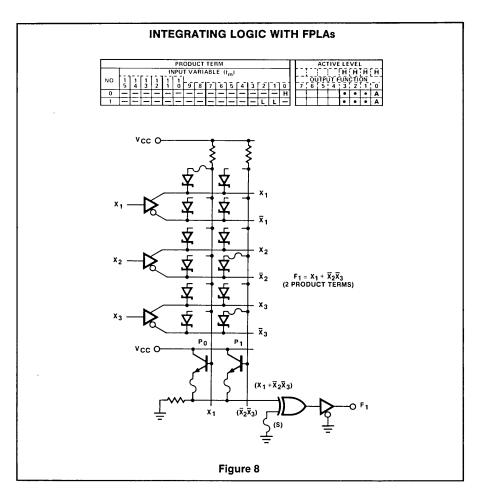

Typically, F<sub>1</sub> would require the FPLA to contain the fused link pattern shown in Figure 8, as specified in the accompanying Program Table slice. Overall, all four logic functions would use 3 inputs, 4 outputs and 7 product terms of the FPLA, leaving remaining resources spare for later modifications.

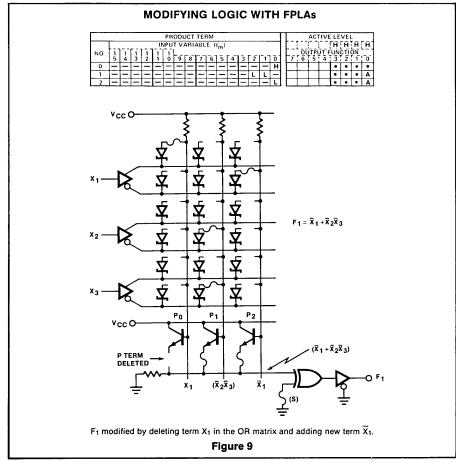

For example, if it becomes necessary to change the  $X_1$  product term in  $F_1$  to  $\overline{X}_1$ , deleting the wrong product term and adding the new one becomes a trivial task, as indicated in the modified pattern and revised Program Table of Figure 9.

These modifications can be made at any time in the field by the user, usually within the same device (as long as spare resources are available), by means of inexpensive programming equipment (as low as \$350).

#### **FPLA: LOGIC OR MEMORY?**

In all practical applications, the view of Signetics' FPLAs as two level AND-OR (or AND-NOR) logic elements is perfectly adequate to manage all necessary logic manipulations. However, the use of FPLAs in certain types of applications can be better grasped by focusing on an alternate aspect of their internal structure. A useful insight is gained by comparing FPLAs to Programmable Read Only Memories (PROMs), and realizing that FPLAs can also be viewed as Conditionally Addressable Memories.

In the industry we refer to PROMs as 1K, 4K, etc. These usually imply standard organizations such 'as 256X4, 512X8, respectively. The larger in each pair of numbers refers to the number of words in a PROM, and the second represents the number of bits in each word. The product of both numbers (approximately 1K, 4K) gives the total number of storage bits contained in the PROM.

This aspect of PROMs carries over to FPLAs, such that Signetics' FPLAs can be described as 48X8, for a total **working** storage density of 384 bits. Thus, the FPLA is a relatively small PROM, but a much more useful one, due to a fundamental difference in input structure.

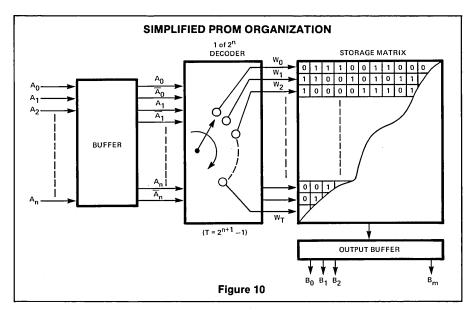

In a PROM (Figure 10), all internal words are reached by a **fixed** decoder internal to the device. The size of this decoder, as well as the storage matrix, doubles for each additional address input. In a 256X8 PROM, the internal decoder selects 1 of 256 words by examining 8 address inputs. For a 512X8 PROM, 1 of 512 words are selected by a decoder twice as large by examining 9 address inputs.

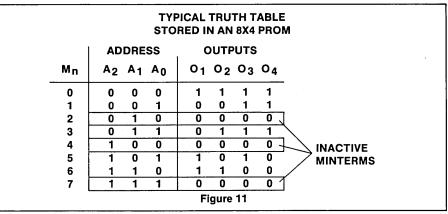

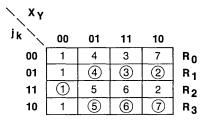

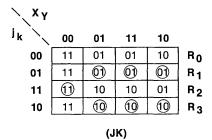

The presence of a fixed decoder renders PROM addressing exhaustive. This can never be avoided, and forces the utilization of PROMs in discrete chunks. This constraint is at the root of the inefficiency of PROMs in the type of application shown in Figure 11. Notice that if we define logic "1" as the active-true state of all output functions, it is not possible to compress the truth table by eliminating inactive minterms 2, 4, and 7. Moreover, with regard to minterms 0 and 1, it is necessary to allocate 2 distinct storage locations to activate output function 03 with a single change in input variable Ao. In this case, Ao represents a logical don't care (X) which cannot be directly programmed in a PROM. Instead, separate minterms  $\overline{A}_2\overline{A}_1\overline{A}_0$  and A2A1A0 must be programmed.

With an FPLA, both constraints are removed.

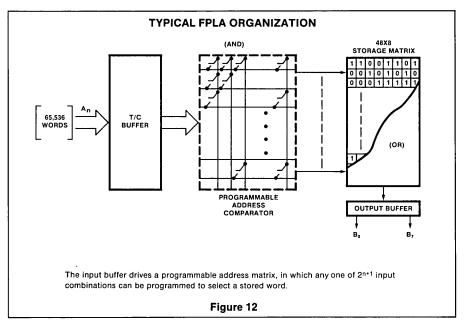

As shown in Figure 12, the FPLA does away with a fixed decoder in favor of a programmable address matrix, which offers, in place of forced exhaustive addressing, the

flexibility to choose by "linear-select" any finite subset from a large number of input states. This is possible because each column of the address matrix functions essentially as a logic comparator programmed to recognize the simultaneous presence of (n) inputs, each either true, false, or both (don't care).

As a result, storage for unused minterms is no longer required. The necessary logic output for the inactive minterms occurs by "default." And, don't care states of input variables can be directly programmed in the FPLA. This allows to program the FPLA with either minterms, or the more general product terms (P-terms) of the input variables (addresses) to minimize logic "waste."

When any programmed logic combination is present at the FPLA inputs, the corresponding address matrix column (P-term) will be pulled high (logically active), forcing all (B) outputs to their true logic state programmed in the storage matrix. Conversely, for all **unprogrammed** logic combinations present at the FPLA inputs, all columns will remain low (logically inactive) forcing all (B) outputs to their false logic state by **default** (the complementary logic state of their programmed active level polarity).

Because it is programmable, the FPLA address matrix is not bound in size by the number of inputs it examines. Signetics' FPLA has 16 inputs to the matrix. If it were a PROM, this address matrix would have to be large enough to decode the address of 65,536 words. For the FPLA, the matrix has to be only large enough to store the address of 48 words: the FPLA's P-terms. The advantage comes about because here we have a choice to select a minimum of any 48 input words (or more, as determined by don't care input variables) from a total available pool of 65,536.

Due to the unique capability of FPLAs to store directly don't care (X) input states, each internal word (W) in the device storage matrix can be addressed by several logic input combinations (minterms), given by:

Thus, if  $P_t = XXXI_0$ , m = 4 and r = 1, for which  $(M_n)T = 8$ .

#### **FPLA RESOURCES**

Signetics' family of bipolar Field Programmable Logic Arrays includes both tri-state (82S100), and open collector devices (82S101), featuring the following characteristics:

- Field programmable (Ni-Cr link)

- 16-input variables

- · 8 output functions

- 48 product terms

- 50ns max. access time (0-75° C)

- 600mW power dissipation (typical)

- TTL compatible

- 28-pin package

- CE input for expansion or inhibit

- Outputs individually programmable active "high" or "low"

- Single +5V power supply

These features and organization combine into an easy to use, high performance device, affording distinct user benefits:

#### A. 16-input variables

The 16X8 I/O configuration permits direct byte manipulations required by intelligent terminals, peripherals, microprocessor based emulators, minicomputers, and all the way up to the larger mainframes. Also, in address mapping applications, it provides the capability to scan an address field 65,536 words deep.

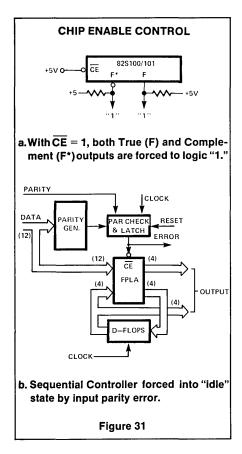

#### B. Chip Enable input

The Chip Enable input is a major improvement over alternate devices:

- Eases expansion of input variables and/or product terms.

- Permits application of tri-state device in bus organized systems.

- Provides logic inhibit or preconditional decoding functions.

- Provides a unique "default" logic state for all outputs, regardless of programmed output polarity.

#### C. Fastest access time

50ns maximum over the commercial temperature range renders the replacement of random logic feasible.

#### D. Fully buffered devices

All product terms can be utilized as many times as required, without affecting device speed and power dissipation.

#### E. 48 product terms (P-terms)

Allow the user to store in the FPLA 48 distinct words of 8 bits each. These 48 words can be addressed by a minimum of 48 input address combinations, chosen by the user among a total available pool of 216 (65,536).

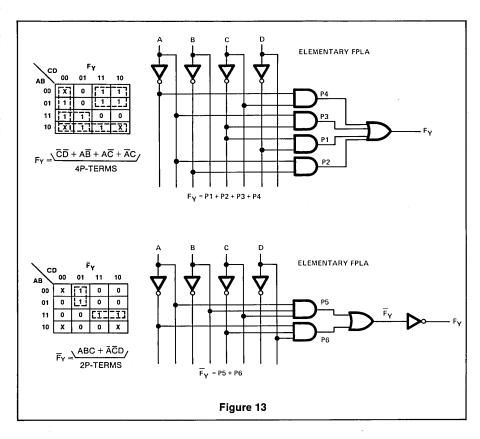

F. Polarity of all outputs individually programmable active-high or active-low This feature is particularly useful in achieving further product term minimization in cases where the complement of an output function can be implemented with fewer product terms.

#### Example:

As shown in Figure 13, a 50% reduction in P-terms is obtained when the output of the logical structure of  $\overline{F_y}$  is inverted by means of a gate **external** to the elementary FPLA. The desired function  $F_Y$  is then realized with penalties in hardware, and circuit delays (however small). These are eliminated when using an FPLA with output polarity programmed active-low to realize the function 0's, rather than 1's.

# CHAPTER 2 DATA SPECIFICATIONS

#### **DESCRIPTION**

The 82S100 (tri-state outputs) and the 82S101 (open collector outputs) are Bipolar Programmable Logic Arrays, containing 48 product terms (AND terms), and 8 sum terms (OR terms). Each OR term controls an output function which can be programmed either true active-high (Fp), or true active-low (Fp). The true state of each output function is activated by any logical combination of 16-input variables, or their complements, up to 48 terms. Both devices are cited programmable, which means that custom patterns are immediately available by following the fusing procedure outlined in this data sheet.

The 82S100 and 82S101 are fully TTL compatible, and include chip-enable control for expansion of input variables, and output inhibit. They feature either open collector or tri-state outputs for ease of expansion of product terms and application in busorganized systems.

Both devices are available in commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N82S100/101,I or N, and for the military temperature range (-55°C to +125°C) specify S82S100/101,I.

#### **FPLA EQUIVALENT LOGIC PATH**

#### **LOGIC FUNCTION**

Typical Product Term:  $P_0 = I_0 \cdot I_1 \cdot I_2 \cdot I_5 \cdot I_{13}$

Typical Output Functions:

$F_0 = (\overline{CE}) + (P_0 + P_1 + P_2)$  @ S = Closed  $F_0^* = (\overline{CE}) + (P_0 \cdot \overline{P_1} \cdot \overline{P_2})$  @ S = Open

NOTE

For each of the 8 outputs, either the function Fp (active-high) or  $\dot{F}_{P}$  (active low) is available, but not both. The required function polarity is programmed via link (S).

#### **FEATURES**

- Field programmable (Ni-Cr link)

- Input variables: 16

- Output functions: 8

- Product terms: 48

- Address access time: S82S100/101—80ns Max N82S100/101—50ns Max

- Power dissipation: 600mW typ

- Input loading:

S82S100/101: -50μA Max N82S100/101: -100μA Max

- · Chip enable input

- Output option:

82S100: Tri-state

82S101: Open collector

Output disable function: Tri-state—Hi-Z Open collector—Hi

#### **APPLICATIONS**

- . CRT display systems

- Random logic

- Code conversion

- · Peripheral controllers

- Function generators

- . Look-up and decision tables

- Microprogramming

- Address mapping

- Character generators

- Sequential controllers

- . Data security encoders

- Fault detectors

- Frequency synthesizers

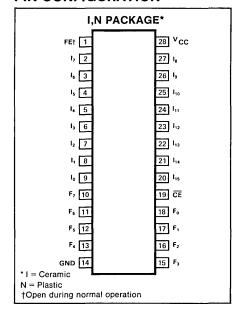

#### PIN CONFIGURATION

#### **TRUTH TABLE**

| MODE                 | Pn | CE | Sr 🖁 f(Pn) | Fp   | Fp   |

|----------------------|----|----|------------|------|------|

| Disabled<br>(82S101) | Х  | 1  | X          | 1    | 1    |

| Disabled<br>(82S100) | ^  | 1  |            | Hi-Z | Hi-Z |

| Read                 | 1  | 0  | Yes        | 1    | 0    |

| neau                 | Х  | 0  | No         | 0    | 1    |

#### LOGIC DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS**<sup>1</sup>

#### **RATING PARAMETER** UNIT Min Max Vcc Supply voltage +7 Vdc $V_{IN}$ Input voltage +5.5 Vdc Output voltage $V_{\text{OUT}}$ +5.5 Vdc Input currents liN -30 +30 $\mathsf{m}\mathsf{A}$ lout Output currents +100 mΑ Temperature range °C $\mathsf{T}_\mathsf{A}$ Operating N82S100/101 0 +75 S82S100/101 -55 +125 -65 TSTG Storage +150

#### THERMAL RATINGS

| TEMPERATURE                                | MILI-<br>TARY | COM-<br>MER-<br>CIAL |

|--------------------------------------------|---------------|----------------------|

| Maximum<br>junction                        | 175° C        | 150° C               |

| Maximum<br>ambient                         | 125° C        | 75° C                |

| Allowable thermal rise ambient to junction | 50° C         | 75° C                |

DC ELECTRICAL CHARACTERISTICS N82S100/101:  $0^{\circ} \le T_A \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

S82S100/101:  $-55^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  +125 $^{\circ}$ C, 4.5V  $\leq$  V<sub>CC</sub>  $\leq$  5.5V

|          | -                                           |                                | N8  | 2S100/           | 101  | S82 |                  |      |      |  |

|----------|---------------------------------------------|--------------------------------|-----|------------------|------|-----|------------------|------|------|--|

|          | PARAMETER                                   | TEST CONDITIONS                | Min | Typ <sup>2</sup> | Max  | Min | Typ <sup>2</sup> | Max  | דומט |  |

|          | Input voltage <sup>3</sup>                  |                                |     |                  | ļ    |     |                  |      | l v  |  |

| $V_{IH}$ | High                                        | V <sub>CC</sub> = Max          | 2   |                  |      | 2   |                  |      |      |  |

| $V_{IL}$ | Low                                         | V <sub>CC</sub> = Min          |     |                  | 0.85 |     | ·                | 0.8  | 1    |  |

| $V_{IC}$ | Clamp <sup>3,4</sup>                        | $V_{CC} = Min, I_{IN} = -18mA$ |     | -0.8             | -1.2 |     | -0.8             | -1.2 |      |  |

|          | Output voltage                              | V <sub>CC</sub> = Min          |     |                  |      |     |                  |      | V    |  |

| Vон      | High (82S100)3,5                            | $I_{OH} = -2mA$                | 2.4 |                  | i    | 2.4 |                  |      |      |  |

| Vol      | Low <sup>3,6</sup>                          | $I_{OL} = 9.6 \text{mA}$       |     | 0.35             | 0.45 |     | 0.35             | 0.50 |      |  |

|          | Input current                               |                                |     |                  |      |     |                  |      | μ    |  |

| lıн      | High                                        | $V_{IN} = 5.5V$                |     | <1               | 25   |     | <1               | 50   | '    |  |

| ابر      | Low                                         | $V_{IN} = 0.45V$               |     | -10              | -100 | 1   | -10              | -150 |      |  |

|          | Output current                              | V <sub>CC</sub> = Max          |     |                  |      |     |                  |      |      |  |

| IOLK     | Leakage <sup>7</sup>                        | $V_{OUT} = 5.5V$               |     | 1                | 40   |     | 1                | 60   | μ,   |  |

| IO(OFF)  | Hi-Z state (82S100)7                        | $V_{OUT} = 5.5V$               |     | 1                | 40   |     | 1                | 60   | μ    |  |

|          |                                             | $V_{OUT} = 0.45V$              |     | -1               | -40  |     | -1               | -60  | Ì    |  |

| los      | Short circuit (82S100)4.8                   | V <sub>OUT</sub> = 0V          | -20 |                  | -70  | -15 |                  | -85  | m.   |  |

| Icc      | V <sub>CC</sub> supply current <sup>9</sup> | V <sub>CC</sub> = Max          |     | 120              | 170  |     | 120              | 180  | m.   |  |

|          | Capacitance <sup>7</sup>                    | V <sub>CC</sub> = 5.0V         |     |                  |      |     |                  |      | рГ   |  |

| CIN      | Input                                       | V <sub>IN</sub> = 2.0V         |     | 8                |      |     | 8                |      | 1    |  |

| Cout     | Output                                      | $V_{OUT} = 2.0V$               |     | 17               |      |     | 17               | 1    |      |  |

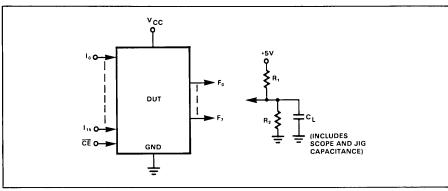

AC ELECTRICAL CHARACTERISTICS  $\,$  R $_1$  =  $470\Omega,\,$  R $_2$  =  $1k\Omega,\,$  C $_L$  = 30pF

N82S100/101:  $0^{\circ}C \le T_{A} \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$ S82S100/101:  $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ ,  $4.5V \le V_{CC} \le 5.5V$

|                                    |                                     |                  |                      | N8  | 32S100/1         | 01       | S8  |                  |          |      |  |

|------------------------------------|-------------------------------------|------------------|----------------------|-----|------------------|----------|-----|------------------|----------|------|--|

| PA                                 | PARAMETER TO                        |                  | FROM                 | Min | Typ <sup>2</sup> | Max      | Min | Typ <sup>2</sup> | Max      | UNIT |  |

| T <sub>IA</sub><br>T <sub>CE</sub> | Access time<br>Input<br>Chip enable | Output<br>Output | Input<br>Chip enable |     | 35<br>15         | 50<br>30 |     | 35<br>15         | 80<br>50 | ns   |  |

| T <sub>CD</sub>                    | Disable time<br>Chip disable        | Output           | Chip enable          |     | 15               | 30       |     | 15               | 50       | ns   |  |

NOTES on following page.

#### BIPOLAR FIELD PROGRAMMABLE LOGIC ARRAY (16X48X8)

82S100-I,N • 82S101-I,N

#### NOTES

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the

device. This is a stress rating only, and functional operation of the device of these or any other

condition above those indicated in the operation of the device specifications is not implied.

- 2. All typical values are at Vcc = 5V, TA = 25°C.

- 3. All voltage values are with respect to network ground terminal

- 4. Test one at the time.

- 5. Measured with ViL applied to  $\overline{CE}$  and a logic high stored.

- Measured with a programmed logic condition for which the output test is at a low logic level. Output sink current is applied thru a resistor to V<sub>CC</sub>.

- 7. Measured with: VIH applied to CE.

- 8. Duration of short circuit should not exceed 1 second.

- 9. Icc is measured with the chip enable input grounded, all other inputs at 4.5V and the outputs open.

#### **TEST LOAD CIRCUIT**

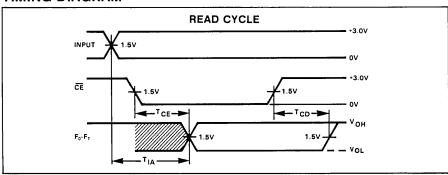

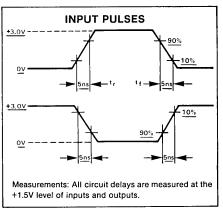

#### TIMING DIAGRAM

#### **TIMING DEFINITIONS**

Tce Delay between beginning of Chip Enable low (with Address valid) and when Data Output becomes valid.

TcD Delay between when Chip Enable becomes high and Data Output is in off state (Hi-Z or high).

T<sub>IA</sub> Delay between beginning of valid Input (with Chip Enable low) and when Data Output becomes valid.

#### **VIRGIN DEVICE**

The 82S100/101 are shipped in an unprogrammed state, characterized by:

- 1. All internal Ni-Cr links are intact.

- Each product term (P-term) contains both true and complement values of every input variable I<sub>m</sub> (P-terms always logically " alse").

- 3. The "OR" Matrix contains all 48-P-terms.

- 4. The polarity of each output is set to active high (Fp function).

- 5. All outputs are at a low logic level.

# RECOMMENDED PROGRAMMING PROCEDURE

To program each of 8 Boolean logic functions of 16 true or complement variables, including up to 48 P-terms, follow the Program/Verify procedures for the "AND" matrix, "OR" matrix, and output polarity outlined below. To maximize recovery from programming errors, leave all links in unused device areas intact.

#### **SET-UP**

Terminate all device outputs with a 10K resistor to +5V. Set GND (pin 14) to 0V.

#### **VOLTAGE WAVEFORM**

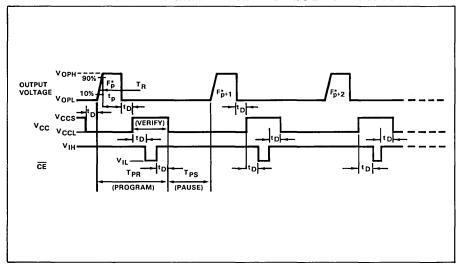

#### **Output Polarity**

### PROGRAM ACTIVE LOW (Fp FUNCTION)

Program output polarity before programing "AND" matrix and "OR" matrix. Program 1 output at the time. (S) links of unused outputs are not required to be fused.

- 1. Set FE (pin 1) to VFEL.

- 2. Set Vcc (pin 28) to VccL.

- 3. Set  $\overline{\text{CE}}$  (pin 19), and I<sub>0</sub> through I<sub>15</sub> to V<sub>IH</sub>.

- 4. Apply V<sub>OPH</sub> to the appropriate output, and remove after a period t<sub>D</sub>.

- 5. Repeat step 4 to program other outputs.

#### **VERIFY OUTPUT POLARITY**

- Set FE (pin 1) to V<sub>FEL</sub>; set V<sub>CC</sub> (pin 28) to V<sub>CCS</sub>.

- 2. Enable the chip by setting  $\overline{CE}$  (pin 19) to  $V_{IL}$ .

- 3. Address a non-existent P-term by applying V<sub>IH</sub> to all inputs I<sub>0</sub> through I<sub>15</sub>.

- 4. Verify output polarity by sensing the logic state of outputs F<sub>0</sub> through F<sub>7</sub>. All outputs at a high logic level are programmed active low (F<sub>p</sub> function), while all outputs at a low logic level are programmed active high (F<sub>p</sub> function).

- 5. Return Vcc to Vccp or Vccl.

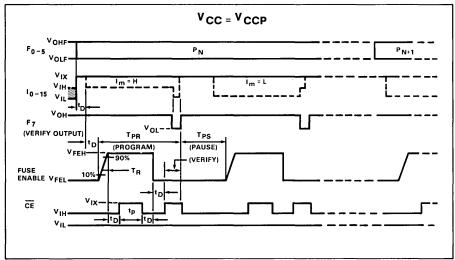

## "AND" Matrix PROGRAM INPUT VARIABLE

Program one input at the time and one Pterm at the time. All input variable links of unused P-terms are not required to be fused. However, unused input variables must be programmed as Don't Care for all programmed P-terms.

- Set FE (pin 1) to V<sub>FEL</sub>, and V<sub>CC</sub> (pin 28) to V<sub>CCP</sub>.

- 2. Disable all device outputs by setting CE (pin 19) to V<sub>IH</sub>.

- Disable all input variables by applying V<sub>IX</sub> to inputs I<sub>0</sub> through I<sub>15</sub>.

- 4. Address the P-term to be programmed (No. 0 through 47) by forcing the corresponding binary code on outputs Fo through F<sub>5</sub> with F<sub>0</sub> as LSB. Use standard TTL logic levels V<sub>OHF</sub> and V<sub>OLF</sub>.

- 5a. If the P-term contains neither I<sub>0</sub> nor I<sub>0</sub> (input is a Don't Care), fuse both I<sub>0</sub> and I<sub>0</sub> links by executing both steps 5b and 5c, before continuing with step 7.

- 5 b. If the P-term contains I<sub>0</sub>, set to fuse the I<sub>0</sub> link by lowering the input voltage at I<sub>0</sub> from V<sub>IX</sub> to V<sub>IH</sub>. Execute step 6.

- 5 c. If the P-term contains  $\overline{l_0}$ , set to fuse the  $l_0$  link by lowering the input voltage at  $l_0$  from  $V_{IX}$  to  $V_{IL}$ . Execute step 6.

- 6 a . After to delay, raise FE (pin 1) from V<sub>FEL</sub> to V<sub>FEH</sub>.

- 6b. After t<sub>D</sub> delay, pulse the  $\overline{CE}$  input from  $V_{IH}$  to  $V_{IX}$  for a period t<sub>D</sub>.

- $6\,c_{\,\cdot}$  After  $t_D$  delay, return FE input to  $V_{FEL}.$

- 7. Disable programmed input by returning I<sub>0</sub> to V<sub>IX</sub>.

- Repeat steps 5 through 7 for all other input variables.

- 9. Repeat steps 4 through 8 for all other Pterms.

- 10. Remove VIX from all input variables.

#### **VERIFY INPUT VARIABLE**

- Set FE (pin 1) to V<sub>FEL</sub>; set V<sub>CC</sub> (pin 28) to V<sub>CCP</sub>.

- 2. Enable F7 output by setting CE to VIX.

- 3. Disable all input variables by applying  $V_{IX}$  to inputs  $I_0$  through  $I_{15}$ .

- Address the P-term to be verified (No. 0 through 47) by forcing the corresponding binary code on outputs F<sub>0</sub> through F<sub>5</sub>.

- 5. Interrogate input variable I<sub>0</sub> as follows:

- A. Lower the input voltage at  $I_0$  from  $V_{IX}$  to  $V_{IH}$ , and sense the logic state of output  $F_7$ .

- B. Lower the input voltage at I<sub>0</sub> from V<sub>IH</sub> to V<sub>IL</sub>, and sense the logic state output F<sub>7</sub>.

The state of  $I_0$  contained in the P-term is determined in accordance with the following truth table:

| l <sub>o</sub> | F <sub>7</sub> | INPUT VARIABLE STATE CONTAINED IN P-TERM |

|----------------|----------------|------------------------------------------|

| 0              | 1<br>0         | ī <sub>0</sub>                           |

| 0              | 0              | I <sub>0</sub>                           |

| 0              | 1              | Don't Care                               |

| 0              | 0<br>0         | (I <sub>0</sub> ), ( <del>I</del> 0)     |

Note that 2 tests are required to uniquely determine the state of the input variable contained in the P-term.

- 6. Disable verified input by returning  $l_0$  to  $V_{IX}$ .

- 7. Repeat steps 5 and 6 for all other input variables.

- 8. Repeat steps 4 through 7 for all other P-terms.

- 9. Remove  $V_{IX}$  from all input variables.

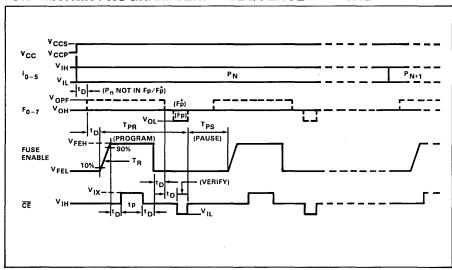

#### "OR" MATRIX

#### PROGRAM PRODUCT TERM

Program one output at the time for one Pterm at the time. All P<sub>n</sub> links in the "OR" matrix corresponding to unused outputs and unused P-terms are not required to be fused.

- 1. Set FE (pin 1) to V<sub>FEL</sub>.

- Disable the chip by setting CE (pin 19) to V<sub>IH</sub>.

- After t<sub>D</sub> delay, set V<sub>CC</sub> (pin 28) to V<sub>CCS</sub>, and inputs I<sub>6</sub> through I<sub>15</sub> to V<sub>IH</sub>, V<sub>IL</sub>, or V<sub>IX</sub>.

- Address the P-term to be programmed (No. 0 through 47) by applying the corresponding binary code to input

- variables I<sub>0</sub> through I<sub>5</sub>, with I<sub>0</sub> as LSB.

- 5a. If the P-term is contained in output function  $F_0$  ( $F_0 = 1$  or  $F_0^* = 0$ ), got to step 6, (fusing cycle not required).

- 5b. If the P-term is not contained in output function F<sub>0</sub> (F<sub>0</sub> = 0 or F<sub>0</sub>\* = 1), set to fuse the P<sub>n</sub> link by forcing output F<sub>0</sub> to V<sub>OPF</sub>.

- 6a. After t<sub>D</sub> delay, raise FE (pin 1) from V<sub>FEL</sub> to V<sub>FEH</sub>.

- 6b. After t<sub>D</sub> delay, pulse the  $\overline{\text{CE}}$  input from  $V_{\text{IH}}$  to  $V_{\text{IX}}$  for a period t<sub>D</sub>.

- ic. After to delay, return FE input to VFEL.

- 6d. After  $t_D$  delay, remove  $V_{OPF}$  from output  $F_0$ .

- Repeat steps 5 and 6 for all other output functions.

- Repeat steps 4 through 7 for all other P-terms.

- 9. Remove Vccs from Vcc.

#### **VERIFY PRODUCT TERM**

- 1. Set FE (pin 1) to V<sub>FEL</sub>.

- 2. Disable the chip by setting  $\overline{CE}$  (pin 19) to V<sub>IH</sub>.

- After t<sub>D</sub> delay, set V<sub>CC</sub> (pin 28) to V<sub>CCS</sub>, and inputs I<sub>0</sub> through I<sub>15</sub> to V<sub>IH</sub>, V<sub>IL</sub>, or V<sub>IX</sub>.

- Address the P-term to be verified (No. 0 through 47) by applying the corresponding binary code to input variables I<sub>0</sub> through I<sub>5</sub>.

- 5. After to delay, enable the chip by setting CE (pin 19) to V<sub>IL</sub>.

- 6. To determine the status of the P<sub>n</sub> link in the "OR" matrix for each output function F<sub>p</sub> or F<sub>p</sub>\*, sense the state of outputs F<sub>0</sub> through F<sub>7</sub>. The status of the link is given by the following truth table:

|                  | ОИТРИТ             |                     |  |  |  |  |  |  |  |

|------------------|--------------------|---------------------|--|--|--|--|--|--|--|

| ow P-TERM LINK   | Active Low<br>(Fp) | Active High<br>(Fp) |  |  |  |  |  |  |  |

| Fused<br>Present | 1<br>0             | 0<br>1              |  |  |  |  |  |  |  |

- Repeat steps 4 through 6 for all other Pterms.

- 8. Remove Vccs from Vcc.

#### **OUTPUT POLARITY PROGRAM-VERIFY SEQUENCE (TYPICAL)**

#### "AND" MATRIX PROGRAM-VERIFY SEQUENCE (TYPICAL)

#### "OR" MATRIX PROGRAM-VERIFY SEQUENCE (TYPICAL)

#### PROGRAMMING SYSTEM SPECIFICATIONS 1 (TA = +25°C)

|                                      | PARAMETER                                                                         | TEST CONDITIONS                                             |          |      | רואט         |          |

|--------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|----------|------|--------------|----------|

|                                      | PARAMETER                                                                         | TEST CONDITIONS                                             | Min      | Тур  | Max          | UNII     |

| Vccs                                 | V <sub>CC</sub> supply (program/verify "OR", verify output polarity) <sup>2</sup> | I <sub>CCS</sub> = 550mA, min,<br>Transient or steady state | 8.25     | 8.5  | 8.75         | ٧        |

| V <sub>CCL</sub><br>I <sub>CCS</sub> | Vcc supply (program output polarity) lcc limit (program "OR")                     | $V_{CCS} = +8.75 \pm .25V$                                  | 0<br>550 | 0.4  | 0.8<br>1,000 | V<br>mA  |

|                                      |                                                                                   |                                                             |          |      |              |          |

| Voph                                 | Output voltage Program output polarity <sup>3</sup>                               | $I_{OPH} = 300 \pm 25 \text{mA}$                            | 16.0     | 17.0 | 18.0         | V        |

| VOPL                                 | Idle                                                                              |                                                             | 0        | 0.4  | 0.8          |          |

| Іорн                                 | Output current limit (Program output polarity)                                    | V <sub>OPH</sub> = +17 ± 1V                                 | 275      | 300  | 325          | mA       |

|                                      | Input voltage                                                                     |                                                             |          |      |              | V        |

| VIH                                  | High                                                                              |                                                             | 2.4      |      | 5.5          |          |

| VIL                                  | Low                                                                               |                                                             | 0        | 0.4  | 0.8          |          |

|                                      | Input current                                                                     |                                                             |          |      |              | μΑ       |

| liH                                  | High                                                                              | $V_{IH} = +5.5V$ $V_{IL} = 0V$                              |          |      | 50<br>-500   |          |

| iir                                  | Low                                                                               | VIL = UV                                                    |          |      | -500         |          |

|                                      | Forced output voltage                                                             |                                                             |          |      |              | V        |

| VOHF                                 | High<br>Low                                                                       |                                                             | 2.4<br>0 | 0.4  | 5.5<br>0.8   |          |

| Volf                                 |                                                                                   |                                                             | U        | 0.4  | 0.8          |          |

|                                      | Output current                                                                    |                                                             |          |      | 100          | ١.       |

| IOHF<br>IOLF                         | High<br>Low                                                                       | $V_{OHF} = +5.5V$ $V_{OLF} = 0V$                            |          |      | 100          | μA<br>mA |

| V <sub>IX</sub>                      | CE program enable level                                                           | VOLI CV                                                     | 9.5      | 10   | 10.5         | V        |

| I <sub>IX1</sub>                     | Input variables current                                                           | $V_{IX} = +10V$                                             | 0.0      | '    | 2.5          | m.A      |

| l <sub>IX2</sub>                     | CE input current                                                                  | $V_{IX} = +10V$                                             |          |      | 5.0          | m/       |

| VFEH                                 | FE supply (program) <sup>3</sup>                                                  | $I_{\text{FEH}} = 300 \pm 25 \text{mA},$                    | 16.0     | 17.0 | 18.0         | "v       |

| * F E F1                             | 1 L Supply (program)                                                              | Transient or steady state                                   | 10.0     |      | 1            |          |

| VFEL                                 | FE supply (idle)                                                                  | I <sub>FEL</sub> = -1mA, max                                | 1.25     | 1.5  | 1.75         | V        |

| I <sub>FEH</sub>                     | FE supply current limit                                                           | $V_{\text{FEH}} = +17 \pm 1V$                               | 275      | 300  | 325          | mA       |

| VCCP                                 | Vcc supply (program/verify "AND")                                                 | I <sub>CCP</sub> = 550mA, min,<br>Transient or steady state | 4.75     | 5.0  | 5.25         | V        |

| Ісср                                 | Icc limit (program "AND")                                                         | $V_{CCP} = +5.0 \pm .25V$                                   | 550      |      | 1,000        | m/       |

| VOPF                                 | Forced output (program)                                                           |                                                             | 9.5      | 10   | 10.5         | V        |

| IOPF                                 | Output current (program)                                                          |                                                             |          |      | 10           | m/       |

| TR                                   | Output pulse rise time                                                            |                                                             | 10       |      | 50           | μs       |

| tp                                   | CE programming pulse width                                                        |                                                             | 0.3      | 0.4  | 0.5          | ms       |

| $t_D$                                | Pulse sequence delay                                                              |                                                             | 10       |      |              | μs       |

| TPR                                  | Programming time                                                                  |                                                             |          | 0.6  |              | ms       |

| TPR                                  | — Programming duty cycle                                                          |                                                             |          |      | 50           | %        |

| T <sub>PR</sub> + T                  | PS                                                                                |                                                             |          |      | 2            | 000      |

| F <sub>L</sub>                       | Fusing attempts per link Verify threshold <sup>4</sup>                            |                                                             | 1        | 1.5  |              | cyc      |

| Vs                                   | verily uneshold                                                                   | L                                                           | 1.4      | 1.5  | 1.6          | V        |

#### NOTES

These are specifications which a Programming System must satisy in order to be qualified by Signetics.

<sup>2.</sup> Bypass  $V_{CC}$  to GND with a  $0.01\mu f$  capacitor to reduce voltage spikes.

Care should be taken to ensure that the voltage is maintained during the entire fusing cycle. The recommended supply is a constant current source clamped at the specified voltage limit.

V<sub>S</sub> is the sensing threshold of the FPLA output voltage for a programmed link. It normally constitutes

the reference voltage applied to a comparator circuit to verify a successful fusing attempt.

These are new limits resulting from device improvements, and which supersede, but do not obsolete

the performance requirements of previously manufactured programming equipment.

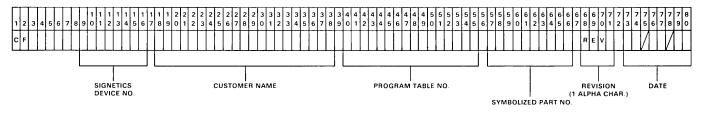

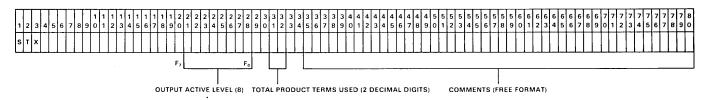

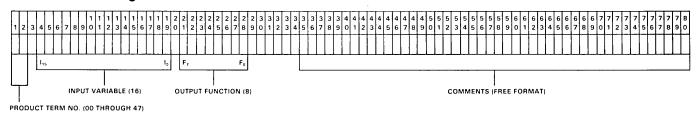

#### 16X48X8 FPLA PROGRAM TABLE

|                                           |                |                                          |                           | 7            | PROGRAM TABLE ENTRIES |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  | _        |          |          |              |                   |              |                 |         |      |          |

|-------------------------------------------|----------------|------------------------------------------|---------------------------|--------------|-----------------------|----------|--------|------|--------------------------------------------------|--------------|----------|----------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------|----------|----------|--------------|-------------------|--------------|-----------------|---------|------|----------|

|                                           | 1              |                                          |                           | <b> </b>     |                       | IPU1     | r VA   | RIA  | BLE                                              | :            |          |          |                                                  |                                                  | TPU                                              |                                                  |                                                  |                                                  |          | <u> </u> | 0        | LITE         | PUT               | ACI          | TIVE            | I.F.    | VFI  | -        |

|                                           |                |                                          |                           |              | Ť                     |          | $\Box$ |      |                                                  |              |          |          | Prod                                             |                                                  |                                                  | Ť                                                |                                                  |                                                  |          | Not      | -        | Activ        |                   | Ť            |                 | Acti    |      |          |

| S                                         |                |                                          |                           | Im           | ł                     | Ιm       | י      | Do   | on't                                             | Care         | 9        |          |                                                  |                                                  | ı F <sub>P</sub>                                 |                                                  |                                                  | eser                                             |          |          |          | Higi         |                   |              |                 | Lov     |      |          |

| 5                                         |                |                                          | }                         | Н            |                       | L        |        | _    | - (da                                            | sh)          |          |          |                                                  | Α                                                |                                                  |                                                  | •                                                | (pe                                              | riod     | )        |          | Н            |                   |              |                 | L       |      |          |

| Ä                                         |                |                                          |                           | NOT          | ΓE                    |          |        |      |                                                  |              |          | NOT      | ES                                               |                                                  |                                                  |                                                  |                                                  |                                                  |          |          | NO       | OTES         |                   |              |                 |         |      |          |

| THIS PORTION TO BE COMPLETED BY SIGNETICS |                |                                          |                           | Ente<br>P-te |                       | for u    | nused  | inpu | uts of                                           | used         |          |          |                                                  |                                                  | pende<br>r unus                                  |                                                  |                                                  |                                                  |          | -terms.  |          |              | arity p<br>er (H) |              |                 |         |      |          |

| œ<br>G                                    |                |                                          |                           |              |                       |          |        |      |                                                  | PRC          | DU       | CT       | TER                                              | М¹                                               |                                                  |                                                  |                                                  |                                                  |          |          |          |              | ACT               | IVE          | LE\             | /EL¹    |      |          |

| 單                                         |                |                                          |                           |              |                       | ,        |        | . —  |                                                  | NP           | ٦T ٧     | /AR      | ABL                                              | Ε¹                                               |                                                  |                                                  |                                                  |                                                  |          |          |          | Ţ            |                   |              | _  <br> _       | _ 7<br> |      | Ι_       |

| Ä                                         |                | ļ                                        |                           | NO.          | 1                     | 1        | 1      | 1    | 1                                                | 1            | L _      |          |                                                  |                                                  |                                                  |                                                  |                                                  | .— -                                             |          |          |          | . —          | JTPL              | JT F         | UN              |         | יַמכ |          |

| Ĭ.                                        |                |                                          |                           |              | 5                     | 4        | 3      | 2    | 1                                                | 0            | 9        | 8        | 7                                                | 6                                                | 5                                                | 4                                                | 3                                                | 2                                                | 1        | 0        | 7        | 6            | 5                 | 4            | 3               | 2       | 1    | 0        |

| ខ                                         |                |                                          |                           | 0            |                       |          |        |      | <u> </u>                                         | _            | _        |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  | _        |          | <u> </u> |              |                   |              |                 |         |      |          |

| <b>B</b> E                                | ł              | #                                        |                           | 1 2          | _                     |          |        |      | <del> </del>                                     | <del> </del> | -        | -        |                                                  |                                                  | <u> </u>                                         | -                                                | -                                                | <u> </u>                                         | -        |          |          | -            | -                 |              |                 | _       |      |          |

| 2                                         |                | PART                                     |                           | 3            |                       |          |        |      | <u> </u>                                         |              |          |          |                                                  |                                                  | <u> </u>                                         |                                                  |                                                  | <u> </u>                                         |          |          |          |              |                   |              |                 |         |      |          |

| Z                                         |                | /d (                                     |                           | 4            |                       |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

| Ĭ                                         |                | CUSTOMER SYMBOLIZED DATE RECEIVED        |                           | 5            | $\vdash$              | -        | ļ      |      | -                                                | ├            | -        | -        | <del>                                     </del> | <del>                                     </del> | -                                                | -                                                | <u> </u>                                         | <del> </del>                                     |          |          | -        | ļ            | -                 | <u> </u>     | $\vdash \vdash$ |         |      | -        |

| Ď                                         |                | )LIŽ                                     |                           | 7            |                       |          |        |      | <del>                                     </del> | <u> </u>     |          |          |                                                  |                                                  | <del>                                     </del> |                                                  |                                                  |                                                  |          |          |          |              |                   | <u> </u>     | $\Box$          |         |      |          |

| <u> </u>                                  |                | ABC /                                    |                           | 8            |                       |          |        |      |                                                  |              |          | <u> </u> |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

| 프                                         |                | SYN                                      |                           | 10           | _                     |          |        |      | <u> </u>                                         |              | _        |          | <u> </u>                                         |                                                  | -                                                | <del> </del>                                     |                                                  | -                                                |          |          |          |              |                   |              | $\square$       |         |      | <u> </u> |

|                                           | į              | CUSTOMER SYM<br>DATE RECEIVED            | TS.                       | 11           |                       |          |        |      | <del>                                     </del> | -            |          | -        |                                                  |                                                  | -                                                | -                                                | -                                                |                                                  | -        |          | -        | _            |                   |              | $\vdash$        | _       |      | -        |

|                                           | CF (XXXX)      | 3EC                                      | COMMENTS                  | 12           |                       |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

|                                           | ž              | STC                                      | Σ×                        | 13           |                       |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

|                                           | Ë              | SC FC                                    | Ö                         | 14           |                       |          |        |      |                                                  |              |          | _        | <u> </u>                                         | -                                                | <u> </u>                                         | <del> </del>                                     | _                                                | <u> </u>                                         | -        |          |          |              |                   |              | H               |         |      |          |

|                                           |                |                                          |                           | 16           |                       |          |        |      |                                                  | -            | -        | -        | ╁                                                |                                                  |                                                  |                                                  | $\vdash$                                         | ļ                                                |          |          |          | -            |                   |              | H               |         |      | $\vdash$ |

|                                           |                |                                          |                           | 17           |                       |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

| -                                         | -              |                                          |                           | 18           |                       |          |        |      |                                                  |              | ļ        | <u> </u> |                                                  |                                                  |                                                  |                                                  | _                                                |                                                  |          |          | <u> </u> |              |                   | _            | Ш               |         |      |          |

| l                                         | Į              |                                          |                           | 19<br>20     |                       |          |        |      |                                                  | 5 1          | -        | -        | -                                                |                                                  |                                                  | ļ                                                | $\vdash$                                         | ļ                                                | -        |          |          | <del> </del> | -                 |              | H               |         |      | -        |

|                                           |                | İ                                        |                           | 21           |                       |          |        |      |                                                  |              | -        |          | ļ                                                |                                                  |                                                  | <u> </u>                                         | <u> </u>                                         |                                                  | -        |          |          | -            |                   | _            |                 |         |      |          |

|                                           | İ              |                                          |                           | 22           |                       |          |        | -    |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

| ŀ                                         | ļ              |                                          |                           | 23           |                       |          |        | _    |                                                  |              | <u> </u> | _        | _                                                | <u> </u>                                         |                                                  | _                                                | _                                                |                                                  |          |          | -        |              |                   |              |                 |         |      |          |

|                                           |                |                                          |                           | 25           |                       |          |        |      |                                                  |              |          | -        |                                                  |                                                  |                                                  |                                                  | -                                                |                                                  | -        | $\dashv$ |          |              | $\vdash$          |              | Н               |         |      | -        |

|                                           |                |                                          |                           | 26           |                       |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

|                                           |                |                                          |                           | 27           |                       |          |        |      | <u> </u>                                         |              |          | _        |                                                  | ļ                                                |                                                  |                                                  |                                                  | ļ                                                |          |          |          | ļ            |                   |              |                 |         |      | L        |

| ľ                                         |                |                                          |                           | 28<br>29     |                       |          |        |      |                                                  |              |          |          |                                                  | <u> </u>                                         | -                                                | -                                                | -                                                | <del>                                     </del> | -        |          | -        |              |                   |              |                 |         |      | -        |

|                                           |                |                                          |                           | 30           |                       |          |        |      |                                                  | $\vdash$     |          |          |                                                  | <u> </u>                                         |                                                  | <u> </u>                                         |                                                  | <del>                                     </del> | $\vdash$ |          | -        |              |                   | <u> </u>     |                 |         |      |          |

|                                           |                |                                          |                           | 31           |                       |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      |          |

| İ                                         |                |                                          |                           | 32           |                       |          |        |      |                                                  |              |          | -        | _                                                |                                                  |                                                  |                                                  | <u> </u>                                         |                                                  |          |          |          | _            |                   |              |                 |         |      | <u> </u> |

| ţ                                         |                | ] [                                      |                           | 33           | -                     |          |        |      |                                                  |              |          |          | ┢                                                |                                                  |                                                  |                                                  |                                                  | -                                                | -        |          | -        | -            | ├                 |              | H               |         | _    | $\vdash$ |

| 1                                         | 1              |                                          |                           | 35           |                       |          | _      |      |                                                  |              |          |          | $I^-$                                            |                                                  | -                                                |                                                  |                                                  |                                                  |          |          |          |              |                   |              |                 |         |      | Г        |

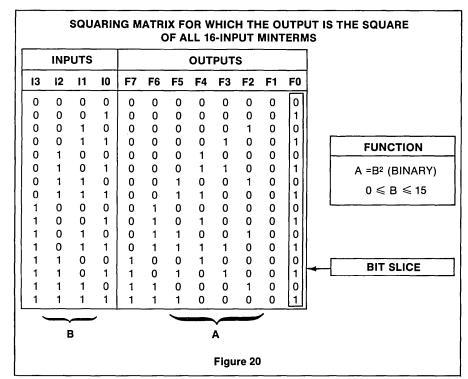

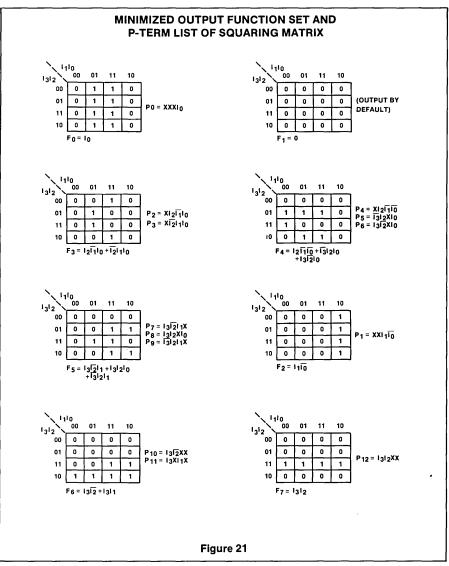

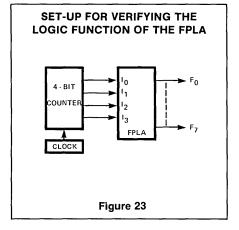

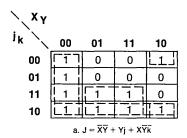

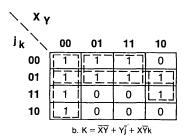

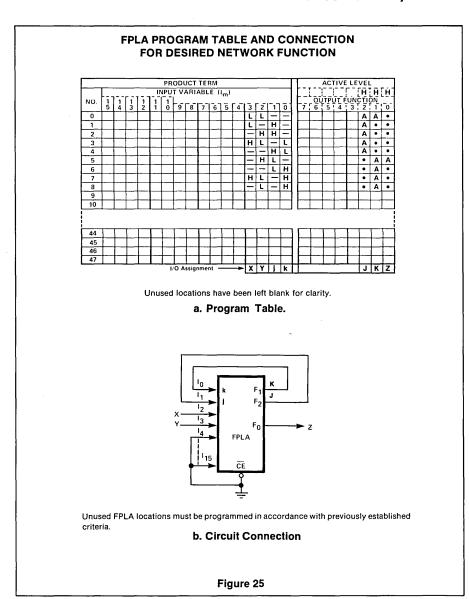

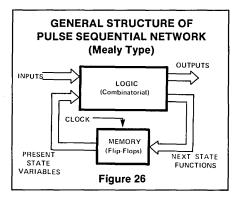

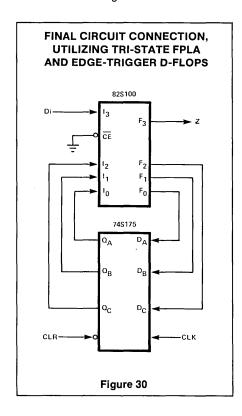

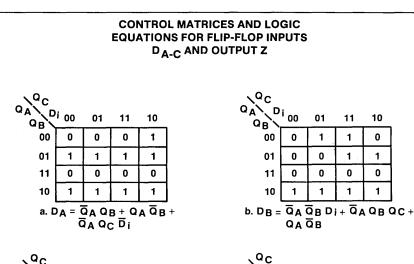

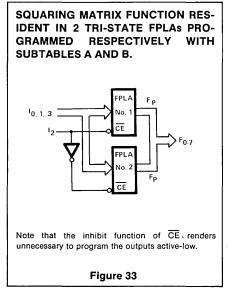

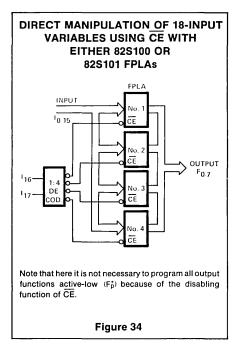

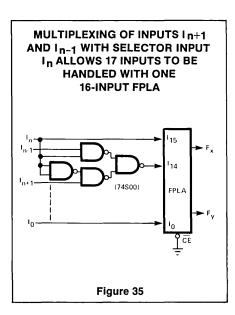

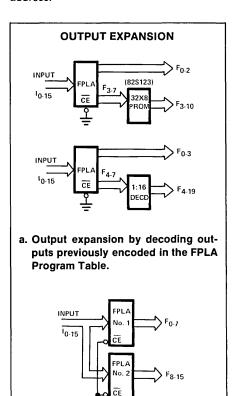

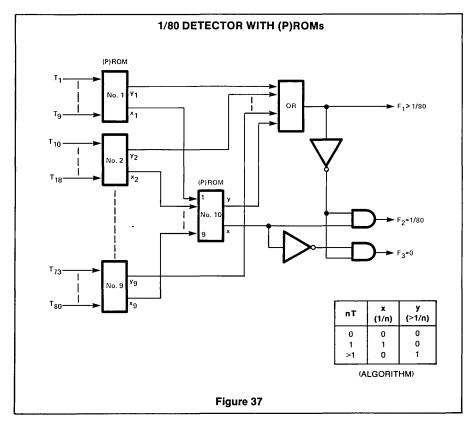

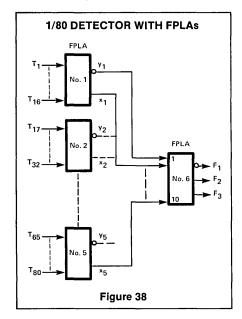

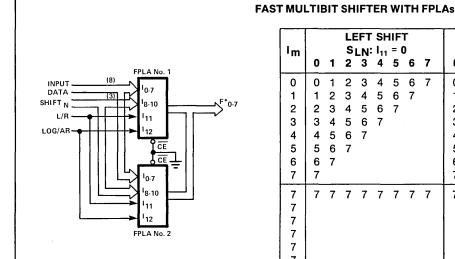

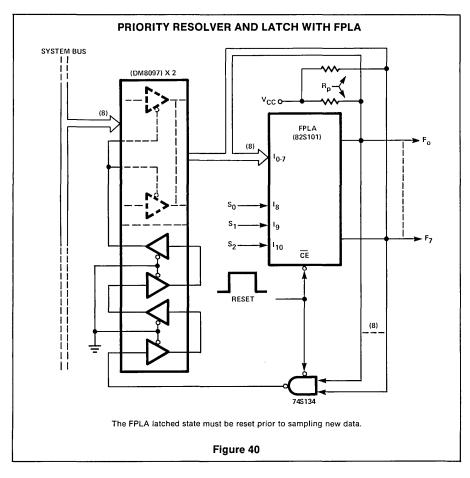

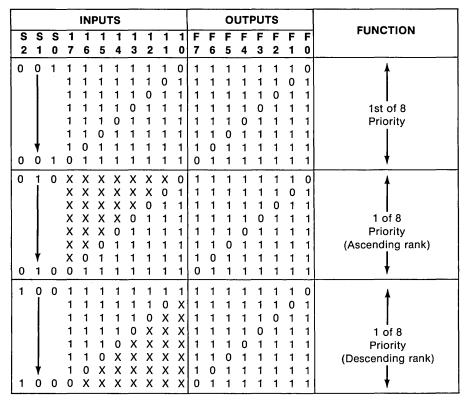

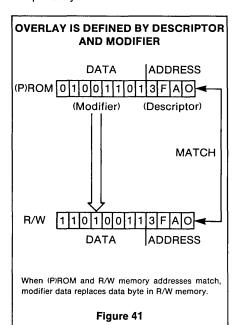

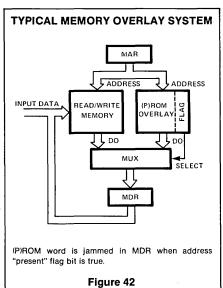

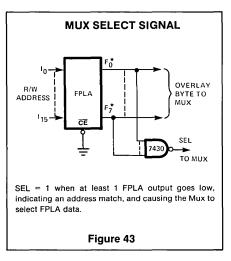

|                                           |                | ပ်                                       |                           | 36           |                       |          |        |      |                                                  |              |          |          |                                                  |                                                  |                                                  |                                                  | <u> </u>                                         |                                                  |          |          |          |              |                   |              |                 |         |      |          |