# Sil3132

PCI Express to Serial ATA Controller Data Sheet

Document # Sil-DS-0136-B

- Silicon Image, Inc.

Aug 2006

#### **Revision History**

| Revision | Comment                                                            | Date     |

|----------|--------------------------------------------------------------------|----------|

| Α        | Derived from preliminary datasheet rev 0.3                         | 04/08/05 |

| A1       | Corrected inconsistent sentences (minor fixes including mistyping) | 08/11/06 |

| В        | Updated Company Logo                                               | 08/14/06 |

# **Table of Contents**

| 1 | Ove                 | erview                                                          | 6  |

|---|---------------------|-----------------------------------------------------------------|----|

|   | 1.1                 | Features                                                        | 6  |

|   | 1.1.1               | 1 Overall Features                                              | 6  |

|   | 1.1.2               |                                                                 |    |

|   | 1.1.3               |                                                                 |    |

|   | 1.2                 | References                                                      | 6  |

| 2 | Ele                 | ctrical Characteristics                                         |    |

|   | 2.1                 | Device Electrical Characteristics                               | 7  |

|   | 2.2                 | SATA Interface Timing Specifications                            |    |

|   | 2.3                 | SATA Interface Transmitter Output Jitter Characteristics        | 9  |

|   | 2.4                 | PCI Express Interface Timing Specifications                     | 10 |

|   | 2.5                 | PCI Express Interface Transmitter Output Jitter Characteristics | 10 |

|   | 2.6                 | CLKI SATA Reference Clock Input Requirements                    | 10 |

|   | 2.7                 | Power Supply Noise Requirements                                 | 11 |

| 3 | Pin                 | Definition                                                      | 12 |

|   | 3.1                 | Sil3132 Pin Listing                                             | 12 |

|   | 3.2                 | Sil3132 Pin Diagram                                             |    |

|   | 3.3                 | Sil3132 Pin Descriptions                                        |    |

|   | 3.3.1               | ·                                                               |    |

|   | 3.3.2               |                                                                 |    |

|   | 3.3.3               |                                                                 |    |

|   | 3.3.4<br>3.3.5      |                                                                 |    |

| _ |                     |                                                                 |    |

| 4 | Pac                 | kage Drawing                                                    | 17 |

| 5 | Pro                 | gramming Model                                                  | 20 |

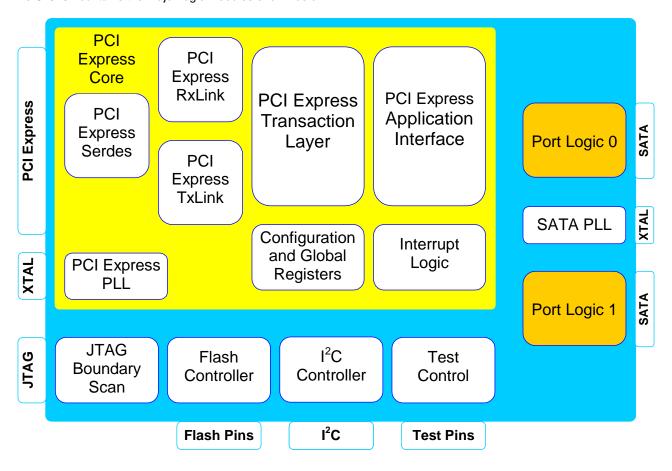

|   | 5.1                 | Sil3132 Block Diagram                                           | 20 |

| 6 | Aut                 | o-Initialization                                                | 21 |

| Ī | 6.1                 | Auto-Initialization from Flash                                  |    |

|   | 6.2                 | Auto-Initialization from EEPROM                                 |    |

| 7 | _                   | ver Management                                                  |    |

|   |                     |                                                                 |    |

| 8 |                     | sh, GPIO, EEPROM, and I <sup>2</sup> C Programming              |    |

|   | 8.1                 | Flash Memory Access                                             |    |

|   | 8.1.1               |                                                                 |    |

|   | 8.1.2<br><b>8.2</b> | 2 Register Access                                               |    |

|   | 0.4                 | I C UDEI AUUI                                                   | Zə |

# **Table of Tables**

| Table 2-1 Absolute Maximum Ratings                                           | 7  |

|------------------------------------------------------------------------------|----|

| Table 2-2 DC Specifications                                                  |    |

| Table 2-3 SATA Interface DC Specifications                                   |    |

| Table 2-4 PCI Express Interface DC Specifications                            | 8  |

| Table 2-5 SATA Interface Timing Specifications                               | 9  |

| Table 2-6 SATA Interface Transmitter Output Jitter Characteristics, 1.5 Gb/s |    |

| Table 2-7 SATA Interface Transmitter Output Jitter Characteristics, 3 Gb/s   |    |

| Table 2-8 PCI Express Interface Timing Specifications                        | 10 |

| Table 2-9 PCI Express Interface Transmitter Output Jitter Characteristics    | 10 |

| Table 2-10 CLKI SerDes Reference Clock Input Requirements                    | 10 |

| Table 2-11 Power Supply Noise Requirements                                   |    |

| Table 3-1 Sil3132 Pin Listing                                                |    |

| Table 3-2 Pin Types                                                          | 13 |

| Table 4-1 Package Dimensions                                                 | 17 |

| Table 6-1 Auto-Initialization from Flash Timing                              |    |

| Table 6-2 Flash Data Description                                             | 21 |

| Table 6-3 Auto-Initialization from EEPROM Timing                             |    |

| Table 6-4 Auto-Initialization from EEPROM Timing Symbols                     | 22 |

| Table 6-5 EEPROM Data Description                                            |    |

| Table 7-1 Power Management Register Bits                                     |    |

## Silicon Image, Inc. —

# **Table of Figures**

| Figure 3-1 Pin Diagram                            | 14 |

|---------------------------------------------------|----|

| Figure 4-1 Package Drawing 88 QFN                 |    |

| Figure 4-2 Marking Specification                  |    |

| Figure 5-1 Sil3132 Block Diagram                  |    |

| Figure 6-1 Auto-Initialization from Flash Timing  |    |

| Figure 6-2 Auto-Initialization from EEPROM Timing | 22 |

## 1 Overview

The Silicon Image Sil3132 is a two-port PCI Express to Serial ATA controller. The Sil3132 is designed to provide multiple port serial ATA connectivity with minimal host overhead and host to device latency. The Sil3132 supports a 1-lane 2.5 Gb/s PCI Express bus and the Serial ATA Generation 2 transfer rate of 3.0 Gb/s (300 MB/s).

#### 1.1 Features

#### 1.1.1 Overall Features

- Host Protocol

- Optimized for transaction oriented designs minimal Host overhead

- Supports two command issuance mechanisms

- Efficient in both embedded and PC implementations

- Reduces dependency on bridge behavior

- Supports up to 4Mbit external Flash for BIOS expansion

- Supports a master/slave I<sup>2</sup>C interface

- Supports external Flash or serial EEPROM for programmable subsystem vendor ID / subsystem product ID

- Fabricated in a 0.18μ CMOS process with a 1.8 volt core and 3.3 volt I/Os

- Available in an 88-pin QFN package (10x10 mm, 0.4 mm lead pitch). An EPAD must be soldered to PCB GND

- · JTAG boundary scan

#### 1.1.2 PCI Express Features

- Supports 1-lane 2.5 Gb/s PCI Express

- Internal application interface multiplexed to 2 ports

- All registers appear in unified memory space

- All registers accessible through I/O space

- Full-chip command completion status accessible with single PCI Express access

#### 1.1.3 Serial ATA Features

- Integrated Serial ATA Link and PHY logic

- Compliant with Serial ATA 1.0 specifications

- Supports Serial ATA Generation 2 transfer rate of 3.0 Gb/s

- Plesiochronous, Single PLL architecture, 1 PLL for 2 ports

- Output Swing Control

- Supports two independent Serial ATA channels

- Independent Link, Transport, and data FIFO

- Independent command fetch, scatter/gather, and command execution

- Hard coded state machines no code space or download

- Supports Legacy Command Queuing (LCQ)

- Supports Native Command Queuing (NCQ)

- o Supports Non-zero offsets NCQ

- o Supports Out of order data delivery NCQ

- o Supports FIS-based switching with Port Multipliers

- 31 Commands and Scatter/Gather Tables per Port on-chip

- Protocol Override per Command

- Staggered Spin-up Control

### 1.2 References

- Serial ATA / High Speed Serialized AT Attachment specification, Revision 1.0

- PCI Express Base Specification Revision 1.0a

## 2 Electrical Characteristics

## 2.1 Device Electrical Characteristics

Specifications are for Commercial Temperature range, 0°C to +70°C, unless otherwise specified.

| Symbol                                                                    | Parameter                                                                                  | Ratings           | Unit |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------|------|

| VDDO                                                                      | I/O Supply Voltage                                                                         | 4.0               | V    |

| VDDD                                                                      | Core Supply Voltage                                                                        | 2.15              | V    |

| VDDSRX, VDDSTX<br>VDDSPLL, VDDPRX<br>VDDPTX, VDDPTXPLL<br>VDDPRXPLL, VDDX | Supply Voltage for S-ATA and PCI<br>Exp Receivers, Transmitters, and<br>PLLs, respectively | 2.15              | ٧    |

| $V_{IN}$                                                                  | Input Voltage                                                                              | -0.3 ~ VDD+0.3    | V    |

| I <sub>OUT</sub>                                                          | DC Output Current                                                                          | 16                | mA   |

| $\theta_{\sf JA}$                                                         | Thermal Resistance, Junction to Ambient, Still Air                                         | 22.2 <sup>1</sup> | °C/W |

| T <sub>STG</sub>                                                          | Storage Temperature                                                                        | -65 ~ 150         | °C   |

Notes: 1 An EPAD must be soldered to PCB GND

**Table 2-1 Absolute Maximum Ratings**

| Symbol                 | Parameter                              | Condition            | Type    | Min  | Тур | Max        | Unit |

|------------------------|----------------------------------------|----------------------|---------|------|-----|------------|------|

| VDDD                   | Core Supply Voltage                    | -                    | -       |      |     |            |      |

| VDDSRX                 | S-ATA Receiver<br>Supply Voltage       | -                    | -       |      |     |            |      |

| VDDSTX                 | S-ATA Transmitter<br>Supply Voltage    | •                    | -       |      |     |            |      |

| VDDSPLL                | S-ATA SerDes PLL<br>Supply Voltage     | -                    | -       |      |     |            |      |

| VDDPRX                 | PCI Exp Receiver Supply Voltage        | -                    | -       | 1.71 | 1.8 | 1.89       | V    |

| VDDPTX                 | PCI Exp Transmitter Supply Voltage     | •                    | -       |      |     |            |      |

| VDDPTX<br>PLL          | PCI Exp Transmitter PLL Supply Voltage | •                    | -       |      |     |            |      |

| VDDPRX<br>PLL          | PCI Exp Receiver PLL Supply Voltage    | •                    | -       |      |     |            |      |

| VDDX                   | Oscillator Supply Voltage              | -                    | -       |      |     |            |      |

| VDDO                   | Supply Voltage(I/O)                    | -                    | -       | 3.0  | 3.3 | 3.6        | V    |

| IDD <sub>1.8V-3G</sub> | Supply Current (1.8V Supply)           | 3GHz<br>Operating    | -       | -    | 450 | 570        | mA   |

| IDD <sub>1.8V-</sub>   | Supply Current (1.8V                   | 1.5GHz               | _       | -    | 380 | 500        | mA   |

| 1.5G                   | Supply)                                | Operating            |         | 0.0  |     |            |      |

| V <sub>IH</sub>        | Input High Voltage                     | 3.3V I/O             |         | 2.0  | -   | -          | V    |

| V <sub>IL</sub>        | Input Low Voltage                      | 3.3V I/O<br>3.3V I/O | Schmitt | -    | 1.8 | 0.8<br>2.3 | V    |

| V-                     | Input High Voltage Input Low Voltage   | 3.3V I/O             | Schmitt | 0.5  | 0.9 | -          | V    |

| V <sub>H</sub>         | Hysteresis Voltage                     | 3.3V I/O             | Schmitt | 0.3  | -   | -          | V    |

| I <sub>IH</sub>        | Input High Current                     | $V_{IN} = VDD$       | -       | -10  | _   | 10         | μА   |

| I <sub>IL</sub>        | Input Low Current                      | $V_{IN} = VSS$       | _       | -10  | -   | 10         | μΑ   |

| V <sub>OH</sub>        | Output High Voltage                    | -                    | -       | 2.4  | -   | -          | V    |

| V <sub>OL</sub>        | Output Low Voltage                     | -                    | -       | -    | -   | 0.4        | V    |

| I <sub>OZ</sub>        | 3-State Leakage<br>Current             | -                    | -       | -10  | -   | 10         | μΑ   |

<sup>3.3</sup>V power consumption depends on LED, JTAG, Enclosure management status. If all are disabled, 3.3V power consumption will be uA.

**Table 2-2 DC Specifications**

© 2006 Silicon Image, Inc.

Sil-DS-0136-B

7

|                        |                                                         |                                                                | Limits |     |     |      |

|------------------------|---------------------------------------------------------|----------------------------------------------------------------|--------|-----|-----|------|

| Symbol                 | Parameter                                               | Condition                                                      | Min    | Тур | Max | Unit |

| V <sub>SATA_DOUT</sub> | TX+/TX- differential peak-to-<br>peak voltage swing.    | Terminated by 50 Ohms.<br>BAR1 1050h [4:0] = 0x0C <sup>1</sup> | 400    | 550 | 700 | mV   |

| V <sub>SATA_DIN</sub>  | RX+/RX- differential peak-to-<br>peak input sensitivity |                                                                | 240    |     |     | mV   |

| V <sub>SATA_SQ</sub>   | RX+/RX- OOB Signal Detection Threshold                  |                                                                | 50     | 125 | 240 | mV   |

| V <sub>SATA ACCM</sub> | Tx AC common-mode voltage                               |                                                                |        |     | 50  | mV   |

| Z <sub>SATA DIN</sub>  | Tx Pair Differential impedance                          |                                                                | 85     | 100 | 115 | ohms |

| Z <sub>SATA DOUT</sub> | Rx Pair Differential impedance                          |                                                                | 85     | 100 | 115 | ohms |

| Z <sub>SATA SIN</sub>  | Tx Single-Ended impedance                               |                                                                | 40     |     |     | ohms |

| Z <sub>SATA</sub> SOUT | Rx Single-Ended impedance                               |                                                                | 40     |     |     | ohms |

Notes: 1 0x0C is a reset value.

**Table 2-3 SATA Interface DC Specifications**

|                                          |                                                         |                         | Limits |      |      |      |

|------------------------------------------|---------------------------------------------------------|-------------------------|--------|------|------|------|

| Symbol                                   | Parameter                                               | Condition               | Min    | Тур  | Max  | Unit |

| V <sub>PCI_DOUT</sub>                    | TX+/TX- differential peak-to-peak voltage swing.        | Terminated by 50 Ohms.  | 800    | 1000 | 1200 | mV   |

| V <sub>PCI_DE-RATIO</sub>                | Tx De-Emphasized Differential Output Voltage            | Ratio                   | - 3.0  | -3.5 | -4.0 | dB   |

| V <sub>PCI_DIN</sub>                     | RX+/RX- differential peak-to-<br>peak input sensitivity |                         | 175    |      | 1200 | mV   |

| Z <sub>PCI DIN</sub>                     | Tx Pair Differential impedance                          | DC impedance            | 80     | 100  | 120  | ohms |

| Z <sub>PCI DOUT</sub>                    | Rx Pair Differential impedance                          | DC impedance            | 80     | 100  | 120  | ohms |

| Z <sub>PCI SIN</sub>                     | Tx Single-Ended impedance                               | DC impedance            | 40     | 50   | 60   | ohms |

| Z <sub>PCI_SOUT</sub>                    | Rx Single-Ended impedance                               | DC impedance            | 40     | 50   | 60   | ohms |

| Z <sub>PCI_RX-HIGH-</sub>                | Rx Powered Down Impedance                               | DC impedance            | 200k   |      |      | ohms |

| Z <sub>PCI_RX-IDLE-</sub><br>DET-DIFFp-p | Electtical Idle Detect Threshold                        | Measured at the Rx pins | 65     |      | 175  | mV   |

**Table 2-4 PCI Express Interface DC Specifications**

## 2.2 SATA Interface Timing Specifications

|                           |                                             |                                                                                                                                                          |           | Limits |            |      |

|---------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|------------|------|

| Symbol                    | Parameter                                   | Condition                                                                                                                                                | Min       | Тур    | Max        | Unit |

| T <sub>TX_RISE_FALL</sub> | Rise and Fall time at transmitter           | 20%-80% at Gen 1<br>20%-80% at Gen 2                                                                                                                     | 100<br>67 |        | 273<br>136 | ps   |

| T <sub>TX_TOL_FREQ</sub>  | Tx Frequecny Long Term Stability            |                                                                                                                                                          | -350      |        | +350       | ppm  |

| T <sub>TX_AC_FREQ</sub>   | Tx Spread-Sprectrum<br>Modulation Deviation | CLKI = SSC AC<br>modulation, subject to the<br>"Downspread SSC"<br>triangular modulation (30-<br>33KHz) profile per 6.6.4.5<br>in SATA 1.0 specification | -5000     |        | +0         | ppm  |

| T <sub>TX SKEW</sub>      | Tx Differential Skew                        |                                                                                                                                                          |           |        | 15         | ps   |

**Table 2-5 SATA Interface Timing Specifications**

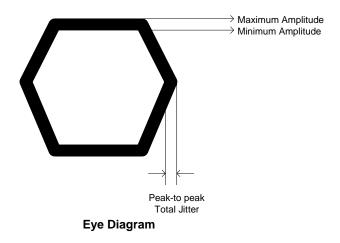

## 2.3 SATA Interface Transmitter Output Jitter Characteristics

|                         |                                         |                              | Limits |     |     |      |

|-------------------------|-----------------------------------------|------------------------------|--------|-----|-----|------|

| Symbol                  | Parameter                               | Condition                    | Min    | Тур | Max | Unit |

|                         |                                         | Measured at Tx output pins   |        |     |     |      |

| TJ <sub>5UI 15G</sub>   | Total Jitter, Data-Data 5UI             | peak to peak phase variation |        | 80  |     | ps   |

|                         |                                         | Random data pattern          |        |     |     |      |

|                         | Deterministic Jitter, Data-<br>Data 5UI | Measured at Tx output pins   |        |     |     |      |

| DJ <sub>5UI_15G</sub>   |                                         | peak to peak phase variation |        | 40  |     | ps   |

|                         |                                         | Random data pattern          |        |     |     |      |

|                         | Total littor Data Data                  | Measured at Tx output pins   |        |     |     |      |

| TJ <sub>250UI_15G</sub> | Total Jitter, Data-Data<br>250UI        | peak to peak phase variation |        | 100 |     | ps   |

|                         | 25001                                   | Random data pattern          |        |     |     |      |

|                         | Deterministic litter Dete               | Measured at Tx output pins   |        |     |     |      |

| DJ <sub>250UI_15G</sub> | Deterministic Jitter, Data-             | peak to peak phase variation |        | 60  |     | ps   |

|                         | Data 250UI                              | Random data pattern          |        |     |     | -    |

Table 2-6 SATA Interface Transmitter Output Jitter Characteristics, 1.5 Gb/s

|                            |                                                                    |                                                                                 | Limits |     |     |      |

|----------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------|--------|-----|-----|------|

| Symbol                     | Parameter                                                          | Condition                                                                       | Min    | Тур | Max | Unit |

| TJ <sub>fBAND/10_3G</sub>  | Total Jitter, f <sub>C3dB</sub> =f <sub>BAUD</sub> /10             | Measured at SATA Compliance Point Random data pattern Load = LL Laboratory Load |        | 60  |     | ps   |

| DJ <sub>fBAND/10_3G</sub>  | Deterministic Jitter,<br>f <sub>C3dB</sub> =f <sub>BAUD</sub> /10  | Measured at SATA Compliance Point Random data pattern Load = LL Laboratory Load |        | 15  |     | ps   |

| TJ <sub>fBAND/500_3G</sub> | Total Jitter, f <sub>C3dB</sub> =f <sub>BAUD</sub> /500            | Measured at SATA Compliance Point Random data pattern Load = LL Laboratory Load |        | 70  |     | ps   |

| DJ <sub>fBAND/500_3G</sub> | Deterministic Jitter,<br>f <sub>C3dB</sub> =f <sub>BAUD</sub> /500 | Measured at SATA Compliance Point Random data pattern Load = LL Laboratory Load |        | 20  |     | ps   |

Table 2-7 SATA Interface Transmitter Output Jitter Characteristics, 3 Gb/s

## 2.4 PCI Express Interface Timing Specifications

|                                       |                                                                                                             |              | Limits |     |        |      |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------|--------|-----|--------|------|

| Symbol                                | Parameter                                                                                                   | Condition    | Min    | Тур | Max    | Unit |

| T <sub>PCI UI</sub>                   | Tx / Rx Unit Interval                                                                                       | SSC disabled | 399.88 | 400 | 400.12 | ps   |

| T <sub>PCI_TX_RISE_FALL</sub>         | Rise and Fall time at transmitter                                                                           | 20%-80%      | 0.125  |     |        | UI   |

| T <sub>PCI_TX-IDLE-MIN</sub>          | Minimum time spent in<br>Electrical Idle                                                                    |              | 50     |     |        | UI   |

| T <sub>PCI_TX-IDLE-SET-TO-</sub> IDLE | Maximum time to transition to<br>a valid Electrical Idle after<br>sending an Electrical Idle<br>ordered set |              |        |     | 20     | UI   |

| T <sub>PCI_TX-IDLE-TO-TO-</sub>       | Maximum time to transition to valid TX specifications after leaving an Elctrical Idle condition             |              |        |     | 20     | UI   |

| T <sub>PVPERL</sub>                   | Power stable to PERST# inactive                                                                             |              | 100    |     |        | ms   |

| T <sub>PERST-CLK</sub>                | REFCLK stable before PERST# inactive                                                                        |              | 100    |     |        | us   |

| $T_{PERST}$                           | PERST# active time                                                                                          |              | 100    |     |        | us   |

**Table 2-8 PCI Express Interface Timing Specifications**

## 2.5 PCI Express Interface Transmitter Output Jitter Characteristics

|                    |              |                                                   | Limits |     |     |      |

|--------------------|--------------|---------------------------------------------------|--------|-----|-----|------|

| Symbol             | Parameter    | Condition                                         | Min    | Тур | Max | Unit |

| TJ <sub>PCle</sub> | Total Jitter | Defined by PCI Express Base Specification Rev 1.1 |        | 65  |     | ps   |

**Table 2-9 PCI Express Interface Transmitter Output Jitter Characteristics**

## 2.6 CLKI SATA Reference Clock Input Requirements

|                             |                            |                                                                                       | Limits   |     |          |       |

|-----------------------------|----------------------------|---------------------------------------------------------------------------------------|----------|-----|----------|-------|

| Symbol                      | Parameter                  | Condition                                                                             | Min      | Тур | Max      | Unit  |

| T <sub>CLKI_FREQ</sub>      | Nominal Frequency          |                                                                                       |          | 25  |          | MHz   |

| V <sub>CLKI_IH</sub>        | Input High Voltage         | -                                                                                     | 0.7xVDDX |     |          | V     |

| V <sub>CLKI_IL</sub>        | Input Low Voltage          | -                                                                                     |          |     | 0.3xVDDX | V     |

| T <sub>CLKI_J</sub>         | CLKI frequency tolerance   | -                                                                                     | -50      |     | +50      | ppm   |

| T <sub>CLKI_RISE_FALL</sub> | Rise and Fall time at CLKI | 25MHz reference                                                                       |          |     | 4        | ns    |

| T <sub>CLKI_RJ</sub>        | Random Jitter              | Measured at CLKI pin<br>10 <sup>-12</sup> Bit Error Ratio<br>1 sigma deviation        |          |     | 50       | psrms |

| T <sub>CLKI_TJ</sub>        | Total Jitter               | Measured at CLKI pin<br>10 <sup>-12</sup> Bit Error Ratio<br>peak-to-peak phase noise |          |     | 1        | ns    |

| T <sub>CLKI_RC_DUTY</sub>   | CLKI duty cycle            | 20%-80%                                                                               | 40       | •   | 60       | %     |

Table 2-10 CLKI SerDes Reference Clock Input Requirements

2.7 Power Supply Noise Requirements

|                         |                          |                                                          | Limits |     |     |      |

|-------------------------|--------------------------|----------------------------------------------------------|--------|-----|-----|------|

| Symbol                  | Parameter                | Condition                                                | Min    | Тур | Max | Unit |

| V <sub>NOISE_VDDA</sub> |                          | peak-to-peak sinewave across<br>500KHz to 3GHz frequency |        |     | 50  | mV   |

| $V_{NOISE\_VDDD}$       | 1.8V Digital Power Noise | range.                                                   |        |     | 100 | mV   |

| $V_{NOISE\_VDDO}$       | 3.3V IO Power Noise      | Measured with differential probe trigger by nois source  |        |     | 200 | mV   |

**Table 2-11 Power Supply Noise Requirements**

## 3 Pin Definition

## 3.1 Sil3132 Pin Listing

This section describes the pin-out of the Sil3132 PCI Express to Serial ATA host controller. The table below gives the pin numbers, pin names, pin types, drive types where applicable, internal resistors where applicable, and descriptions. Power pins (VDD and VSS) are excluded from this listing.

Table 3-1 Sil3132 Pin Listing

| Pin# | Pin Name    | Туре      | Drive | Internal<br>Resistor | Description                                                                                      |

|------|-------------|-----------|-------|----------------------|--------------------------------------------------------------------------------------------------|

| 4    | RX1+        | Diff In   |       | Kesistoi             | Serial port 1 differential receiver + input                                                      |

| 5    | RX1+        | Diff In   |       |                      | Serial port 1 differential receiver – input                                                      |

| 8    | TX1-        | Diff Out  |       |                      | Serial port 1 differential receiver – input  Serial port 1 differential transmitter – output     |

| 9    | TX1+        | Diff Out  |       |                      | Serial port 1 differential transmitter + output  Serial port 1 differential transmitter + output |

| 13   | TX0+        | Diff Out  |       |                      | Serial port 1 differential transmitter + output  Serial port 0 differential transmitter + output |

|      |             |           |       |                      | Serial port 0 differential transmitter – output                                                  |

| 14   | TX0-        | Diff Out  |       |                      |                                                                                                  |

| 17   | RX0-        | Diff In   |       |                      | Serial port 0 differential receiver – input                                                      |

| 18   | RX0+        | Diff In   |       |                      | Serial port 0 differential receiver + input                                                      |

| 20   | REFCLK+     | Diff In   |       |                      | PCI Express differential reference clock + input                                                 |

| 21   | REFCLK-     | Diff In   |       |                      | PCI Express differential reference clock - input                                                 |

| 25   | PRX+        | Diff In   |       |                      | PCI Express differential receiver + input                                                        |

| 26   | PRX-        | Diff In   |       |                      | PCI Express differential receiver – input                                                        |

| 29   | PTX-        | Diff Out  |       |                      | PCI Express differential transmitter – output                                                    |

| 30   | PTX+        | Diff Out  |       |                      | PCI Express differential transmitter + output                                                    |

| 34   | PERST_N     | I-Schmitt |       |                      | PCI Express Reset                                                                                |

| 36   | LED1        | OD        | 12 mA |                      | Channel 1 activity LED indicator                                                                 |

| 37   | LED0        | OD        | 12 mA |                      | Channel 0 activity LED indicator                                                                 |

| 39   | FL_DATA0    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 0                                                                              |

| 40   | FL_DATA1    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 1                                                                              |

| 41   | FL_DATA2    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 2                                                                              |

| 42   | FL_DATA3    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 3                                                                              |

| 43   | FL_DATA4    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 4                                                                              |

| 45   | FL_DATA5    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 5                                                                              |

| 46   | FL_DATA6    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 6                                                                              |

| 47   | FL_DATA7    | I/O       | 8 mA  | PU-70K               | Flash Memory Data 7                                                                              |

| 49   | FL_ADDR00   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 0                                                                           |

| 50   | FL_ADDR01   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 1                                                                           |

| 51   | FL_ADDR02   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 2                                                                           |

| 52   | FL_ADDR03   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 3                                                                           |

| 53   | FL_ADDR04   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 4                                                                           |

| 55   | FL_ADDR05   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 5                                                                           |

| 56   | FL_ADDR06   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 6                                                                           |

| 57   | FL_ADDR07   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 7                                                                           |

| 58   | FL_ADDR08   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 8                                                                           |

| 59   | FL ADDR09   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 9                                                                           |

| 61   | FL_ADDR10   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 10                                                                          |

| 62   | FL_ADDR11   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 11                                                                          |

| 63   | FL_ADDR12   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 12                                                                          |

| 64   | FL_ADDR13   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 13                                                                          |

| 65   | FL_ADDR14   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 14                                                                          |

| 68   | FL_ADDR15   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 15                                                                          |

| 69   | FL_ADDR16   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 16                                                                          |

| 70   | FL_ADDR17   | I/O       | 8 mA  | PU-70K               | Flash Memory Address 17                                                                          |

| 70   | 1 F_VDDU 11 | 1/0       | UIIIA | 1 0-701              | i lasti McIlloty Address II                                                                      |

Table 3-1 Sil3132 Pin Listing

| Pin # | Pin Name   | Туре        | Drive | Internal<br>Resistor | Description                   |

|-------|------------|-------------|-------|----------------------|-------------------------------|

| 71    | FL_ADDR18  | I/O         | 8 mA  | PU-70K               | Flash Memory Address 18       |

| 72    | FL_RD_N    | I/O         | 8 mA  | PU-70K               | Flash Memory Read Strobe      |

| 73    | FL_WR_N    | I/O         | 8 mA  | PU-70K               | Flash Memory Write Strobe     |

| 74    | FL_CS_N    | I/O         | 8 mA  | PU-70K               | Flash Memory Chip Select      |

| 76    | TMS        | I           |       | PU-70K               | JTAG Test Mode Select         |

| 77    | TCK        | I-Schmitt   |       |                      | JTAG Test Clock               |

| 78    | TDI        | 1           |       | PU-70K               | JTAG Test Data In             |

| 79    | TDO        | 0           | 4 mA  |                      | JTAG Test Data Out            |

| 80    | TRSTN      | 1           |       | PU-70K               | JTAG Test Reset               |

| 81    | SCAN_MODE  | I           |       | PD-60K               | Internal Scan Mode Control    |

| 82    | I2C_SDAT   | I/O-Schmitt | 4 mA  | PU-70K               | I <sup>2</sup> C Serial Data  |

| 83    | I2C_SCLK   | I/O-Schmitt | 4 mA  | PU-70K               | I <sup>2</sup> C Serial Clock |

| 86    | XTALO      | Analog      |       |                      | Crystal Output                |

| 87    | XTALI/CLKI | Analog      |       |                      | Crystal or Clock Input        |

| Table 3-2 Pin Types |                                         |  |  |  |

|---------------------|-----------------------------------------|--|--|--|

| Pin Type            | Pin Description                         |  |  |  |

| 1                   | Input Pin with LVTTL Thresholds         |  |  |  |

| I-Schmitt           | Input Pin with Schmitt Trigger          |  |  |  |

| 0                   | Output Pin                              |  |  |  |

| I/O                 | Bi-directional Pin                      |  |  |  |

| I/O-Schmitt         | Bi-directional Pin with Schmitt Trigger |  |  |  |

| OD                  | Open Drain Output Pin                   |  |  |  |

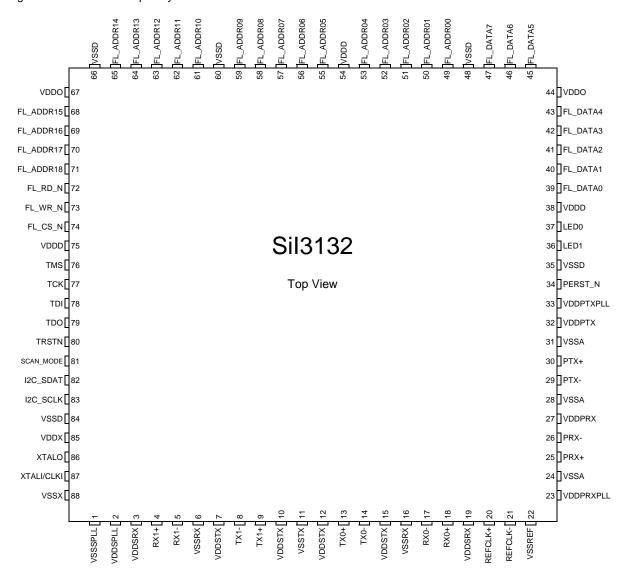

## 3.2 Sil3132 Pin Diagram

The diagram below shows the pin layout for the Sil3132.

Figure 3-1 Pin Diagram

# 3.3 Sil3132 Pin Descriptions 3.3.1 PCI Express Pins

| Signal Name | Pin Number(s) | Description                                                                                                                                                                                        |

|-------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRx+        | 25            | Receive +. Serial receiver differential signal, positive side. Must be AC coupled                                                                                                                  |

| PRx-        | 26            | Receive Serial receiver differential signal, negative side. Must be AC coupled                                                                                                                     |

| PTx+        | 30            | <b>Transmit +.</b> Serial transmitter differential signal, positive side. Must be AC coupled with a 100nF capacitor                                                                                |

| PTx-        | 29            | <b>Transmit</b> Serial transmitter differential signal, negative side. Must be AC coupled with a 100nF capacitor                                                                                   |

| REFCLK+     | 20            | Reference Clock +. PCI Express system supplied differential reference clock, positive side. This input signal must be compliant with PCI Express Card Electromechnical Specification Revision 1.0a |

| REFCLK-     | 21            | Reference Clock PCI Express system supplied differential reference clock, negative side. This input signal must be compliant with PCI Express Card Electromechnical Specification Revision 1.0a    |

| PERST_N     | 34            | Reset. PERST_N initializes the PCI Express interface and sets internal registers to their initial state.                                                                                           |

## 3.3.2 Flash / I<sup>2</sup>C / LED pins

| Signal Name    | Pin Number(s)                 | Description                                                                                                                          |

|----------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| FL_ADDR[18:00] | 49-53, 55-59, 61-65,<br>68-71 | <b>Flash Address.</b> FL_ADDR[18:00] is the Flash Memory address for up to 512K of Flash Memory.                                     |

| FL_DATA[07:00] | 39-43, 45-47                  | Flash Data. 8-bit Flash memory data bus                                                                                              |

| FL_RD_N        | 72                            | Flash Read Enable. Active low                                                                                                        |

| FL_WR_N        | 73                            | Flash Write Enable. Active low                                                                                                       |

| FL_CS_N        | 74                            | Flash Chip Select. Active low                                                                                                        |

| I2C_SDAT       | 82                            | I <sup>2</sup> C Serial Data. Serial Interface (I <sup>2</sup> C) data line (internally connected to PHY I <sup>2</sup> C data line) |

| I2C_SCLK       | 83                            | I <sup>2</sup> C Serial Clock. Serial Interface (I <sup>2</sup> C) clock (internally connected to PHY I <sup>2</sup> C clock)        |

| LED[1:0]       | 36, 37                        | Activity LED. Activity LED drivers for channels 1 and 0.                                                                             |

#### 3.3.3 Serial ATA Signals

| Signal Name | Pin Number(s) | Description                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rx[1:0]+    | 4, 18         | Receive +. Serial receiver differential signal, positive side. Must be AC coupled                                                                                                                                                                                                                                             |

| Rx[1:0]-    | 5, 17         | Receive Serial receiver differential signal, negative side. Must be AC coupled                                                                                                                                                                                                                                                |

| Tx[1:0]+    | 9, 13         | <b>Transmit +.</b> Serial transmitter differential signal, positive side. Must be AC coupled                                                                                                                                                                                                                                  |

| Tx[1:0]-    | 8, 14         | <b>Transmit</b> Serial transmitter differential signal, negative side. Must be AC coupled                                                                                                                                                                                                                                     |

| XTALI/CLKI  | 87            | Crystal In. Crystal oscillator pin for SerDes reference clock. When external clock source is selected, the 25MHz external clock will come in through this pin. The clock must be 1.8V swing and the precision recommendation is ±50ppm. Please refer Table 2-10 CLKI SerDes Reference Clock Input Requirements for the detail |

| XTALO       | 86            | <b>Crystal Out.</b> Crystal oscillator pin for SerDes reference clock. A 25MHz crystal must be used.                                                                                                                                                                                                                          |

Sil-DS-0136-B © 2006 Silicon Image, Inc.

#### 3.3.4 Test Pins

| Signal Name | Pin Number(s) | Description                                                                    |

|-------------|---------------|--------------------------------------------------------------------------------|

| TMS         | 76            | JTAG Test Mode Select                                                          |

| TCK         | 77            | JTAG Test Clock                                                                |

| TDI         | 78            | JTAG Test Data In                                                              |

| TDO         | 79            | JTAG Test Data Out                                                             |

| TRSTN       | 80            | JTAG Test Reset. This pin must be tied to ground if JTAG function is not used. |

| SCAN_MODE   | 81            | Scan Mode. Used for factory testing; do not connect.                           |

#### 3.3.5 Power/Ground Pins

All like-named power/ground pins, in the table below, are connected together within the package.

| Pin Name  | Pin Number(s)      | Description                                                                                                                  |

|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------|

| VDDSRX    | 3, 19              | Receiver Power. These pins provide 1.8V for the Serial ATA receivers.                                                        |

| VSSRX     | 6, 16              | <b>Receiver Ground.</b> These pins provide the Ground reference for the Serial ATA receivers.                                |

| VDDSTX    | 7, 10, 12, 15      | <b>Transmitter Power.</b> These pins provide 1.8V for the Serial ATA transmitters.                                           |

| VSSTX     | 11                 | <b>Transmitter Ground.</b> This pin provides the Ground reference for the Serial ATA transmitters.                           |

| VDDPRX    | 27                 | Receiver Power. This pin provides 1.8V for the PCI Express receivers.                                                        |

| VDDPTX    | 32                 | <b>Transmitter Power.</b> This pin provides 1.8V for the PCI Express transmitters.                                           |

| VDDPTXPLL | 33                 | PLL Power. This pin provides 1.8V for the PCI Express transmitter PLL.                                                       |

| VDDPRXPLL | 23                 | PLL Power. This pin provides 1.8V for the PCI Express receiver PLL.                                                          |

| VSSA      | 24, 28, 31         | <b>PCI-E Ground.</b> These pins provide the Ground reference for the PCI Express SerDes.                                     |

| VDDSPLL   | 2                  | <b>PLL Power.</b> This pin provides 1.8V for the Serial ATA PLL and crystal oscillator.                                      |

| VSSSPLL   | 1                  | PLL Ground. This pin provides the Ground reference for the Serial ATA PLL.                                                   |

| VSSREF    | 22                 | <b>Reference Clock Ground.</b> This pin provides the Ground reference for the PCI-Express reference clock receiver.          |

| VDDX      | 85                 | Oscillator Power. This pin provides 1.8V for the crystal oscillator (associated with XTALI and XTALO pins).                  |

| VSSX      | 88                 | Oscillator Ground. This pin provides the Ground reference for the crystal oscillator (associated with XTALI and XTALO pins). |

| VDDO      | 44, 67             | I/O Power. These pins provide 3.3V for the digital I/O.                                                                      |

| VDDD      | 38, 54, 75         | Digital Power. These pins provide 1.8V for the digital logic.                                                                |

| VSSD      | 35, 48, 60, 66, 84 | <b>Digital Ground.</b> These pins provide the Ground reference for the digital portion of the chip.                          |

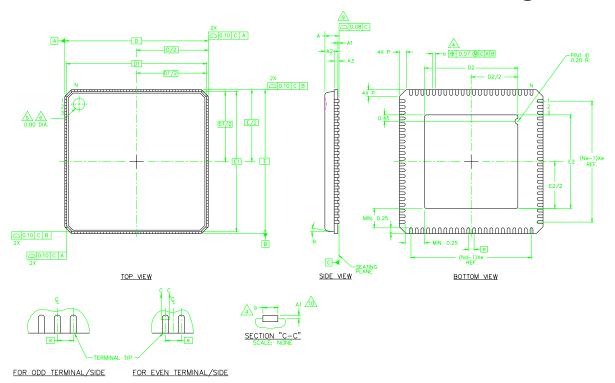

# 4 Package Drawing

Figure 4-1 Package Drawing 88 QFN

| Cymbol | D         | imensions (mn     | n)      |  |  |

|--------|-----------|-------------------|---------|--|--|

| Symbol | Minimum   | Nominal           | Maximum |  |  |

| е      |           | 0.40              |         |  |  |

| L      | 0.30      | 0.40              | 0.50    |  |  |

| b      | 0.15      | 0.20              | 0.25    |  |  |

| D2     | 5.85      | 6.00 <sup>1</sup> | 6.65    |  |  |

| E2     | 5.85      | 6.00 <sup>1</sup> | 6.65    |  |  |

| Α      | -         | 0.85              | 0.90    |  |  |

| A1     | 0.00      | 0.02              | 0.05    |  |  |

| A2     | -         | 0.65              | 0.70    |  |  |

| A3     |           | 0.20 REF          |         |  |  |

| D      |           | 10.00 BSC         |         |  |  |

| D1     | 9.75 BSC  |                   |         |  |  |

| E      | 10.00 BSC |                   |         |  |  |

| E1     | 9.75 BSC  |                   |         |  |  |

| θ      |           |                   | 12°     |  |  |

| Р      | 0.24      | 0.42              | 0.60    |  |  |

**Table 4-1 Package Dimensions**

Note: <sup>1</sup> It is required that an EPAD is soldered to PCB ground and the landing area be incorporated on the PCB within the footprint of the package corresponding to the EPAD. The size of this landing area can be larger than the exposed pad on the package, should be at least the same as the maximum size of exposed pad of the package (6.65 x 6.65mm). If the traces are within the maximum size of exposed pad, the trace may short to the exposed pad when the package has the exposed pad with the maximum dimension.

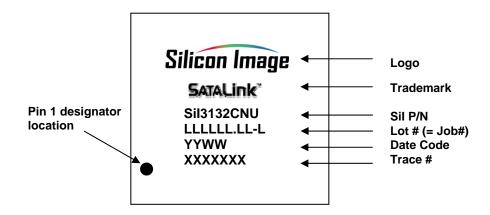

Part Ordering Number:

- Silicon Image, Inc.

Sil3132CNU (88 pin QFN lead free package with an exposed pad)

**Figure 4-2 Marking Specification**

# **5 Programming Model**

## 5.1 Sil3132 Block Diagram

The Sil3132 contains the major logic modules shown below.

Figure 5-1 Sil3132 Block Diagram

The PCI Express Core logic block provides PCI Express 1.0a compatibility. The Global Register File block corresponds to the registers addressed by Base Address Register 0.

The initialization function provided by the I<sup>2</sup>C Controller and Flash Controller is described in Section 6, Auto-Initialization, on page 21.

## 6 Auto-Initialization

The Sil3132 supports an external Flash and/or EEPROM device for BIOS extensions and user-defined PCI configuration header data.

#### 6.1 Auto-Initialization from Flash

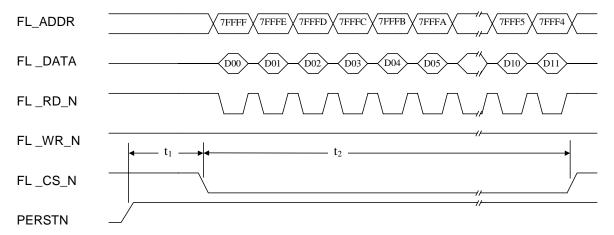

The Sil3132 initiates the Flash detection and configuration space loading sequence upon the release of PERST#. It begins by reading the highest two addresses ( $7FFFF_H$  and  $7FFFE_H$ ), checking for the correct data signature pattern –  $AA_H$  and  $55_H$ , respectively. If the data signature pattern is correct, the Sil3132 continues to sequence the address downward, reading a total of twelve bytes. If the Data Signature is correct ( $55_H$  at  $7FFFC_H$ ), the last eight bytes are loaded into the PCI Configuration Space registers.

If both Flash and EEPROM are installed, the PCI Configuration Space registers will be loaded with the EEPROM's data.

While the sequence is active, the Sil3132 responds to all PCI bus accesses with a Target Retry.

Figure 6-1 Auto-Initialization from Flash Timing

| Parameter      | Value   | Description                                        |

|----------------|---------|----------------------------------------------------|

| t <sub>1</sub> | 660 ns  | PCI reset to Flash Auto-Initialization cycle begin |

| t <sub>2</sub> | 4200 ns | Flash Auto-Initialization cycle time               |

Table 6-1 Auto-Initialization from Flash Timing

| Address            | Data Byte | Description                                          |

|--------------------|-----------|------------------------------------------------------|

| 7FFFF <sub>H</sub> | D00       | Data Signature = AA <sub>H</sub>                     |

| 7FFFE <sub>H</sub> | D01       | Data Signature = 55 <sub>H</sub>                     |

| 7FFFD <sub>H</sub> | D02       | AA = 120 ns Flash device / Else, 240 ns Flash device |

| 7FFFC <sub>H</sub> | D03       | Data Signature = 55 <sub>H</sub>                     |

| 7FFFB <sub>H</sub> | D04       | PCI Device ID [23:16]                                |

| 7FFFA <sub>H</sub> | D05       | PCI Device ID [31:24]                                |

| 7FFF9 <sub>H</sub> | D06       | PCI Class Code [15:08]                               |

| 7FFF8 <sub>H</sub> | D07       | PCI Class Code [23:16]                               |

| 7FFF7 <sub>H</sub> | D08       | PCI Sub-System Vendor ID [07:00]                     |

| 7FFF6 <sub>H</sub> | D09       | PCI Sub-System Vendor ID [15:08]                     |

| 7FFF5 <sub>H</sub> | D10       | PCI Sub-System ID [23:16]                            |

| 7FFF4 <sub>H</sub> | D11       | PCI Sub-System ID [31:24]                            |

**Table 6-2 Flash Data Description**

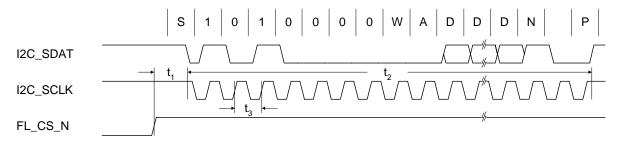

#### 6.2 Auto-Initialization from EEPROM

The Sil3132 initiates the EEPROM detection and configuration space loading sequence after the Flash read sequence. The Sil3132 supports EEPROMs with an  $I^2$ C serial interface. The sequence of operations consists of the following.

- 1) START condition defined as a high-to-low transition on I2C\_SDAT while I2C\_SCLK is high.

- 2) Control byte = 1010 (Control Code) + 000 (Chip Select) + 0 (Write Address)

- 3) Acknowledge

- 4) Starting address field = 00000000.

- 5) Acknowledge

- 6) Sequential data bytes separated by Acknowledges.

- 7) STOP condition.

While the sequence is active, the Sil3132 responds to all PCI bus accesses with a Target Retry.

Figure 6-2 Auto-Initialization from EEPROM Timing

| Parameter      | Value    | Description                                                                       |

|----------------|----------|-----------------------------------------------------------------------------------|

| t <sub>1</sub> | 26.00 μs | End of Auto-Initialization from Flash to start of Auto-Initialization from EEPROM |

| t <sub>2</sub> | 1.4 ms   | Auto-Initialization from EEPROM cycle time                                        |

| t <sub>3</sub> | 10 μs    | EEPROM serial clock period                                                        |

Table 6-3 Auto-Initialization from EEPROM Timing

| Parameter | Description                             |

|-----------|-----------------------------------------|

| S         | START condition                         |

| W         | R/W 0 = Write Command, 1 = Read Command |

| Α         | Acknowledge                             |

| D         | Serial data                             |

| N         | No-Acknowledge                          |

| Р         | STOP condition                          |

**Table 6-4 Auto-Initialization from EEPROM Timing Symbols**

| Address         | Data Byte | Description                              |

|-----------------|-----------|------------------------------------------|

| 00 <sub>H</sub> | D00       | Memory Present Pattern = AA <sub>H</sub> |

| 01 <sub>H</sub> | D01       | Memory Present Pattern = 55 <sub>H</sub> |

| 02 <sub>H</sub> | D02       | Data Signature = AA <sub>H</sub>         |

| 03 <sub>H</sub> | D03       | Data Signature = 55 <sub>H</sub>         |

| 04 <sub>H</sub> | D04       | PCI Device ID [23:16]                    |

| 05 <sub>H</sub> | D05       | PCI Device ID [31:24]                    |

| 06 <sub>H</sub> | D06       | PCI Class Code [15:08]                   |

| 07 <sub>H</sub> | D07       | PCI Class Code [23:16]                   |

| 08 <sub>H</sub> | D08       | PCI Sub-System Vendor ID [07:00]         |

| 09 <sub>H</sub> | D09       | PCI Sub-System Vendor ID [15:08]         |

| 0A <sub>H</sub> | D10       | PCI Sub-System ID [23:16]                |

| 0B <sub>H</sub> | D11       | PCI Sub-System ID [31:24]                |

**Table 6-5 EEPROM Data Description**

## 7 Power Management

The following register bits control Power Management in a Sil3132 Port.

| Register         | Bits       | Description                                                                        |

|------------------|------------|------------------------------------------------------------------------------------|

| Interrupt Status | PM Change  | This bit reports a change in the Power Management mode. It corresponds to the      |

|                  | Bit 3      | interrupt enabled by bit 3 of the Port Interrupt Enable register.                  |

| SError           | W          |                                                                                    |

|                  | Bit 18     | This bit reports a ComWake received from the Serial ATA bus. It corresponds to     |

| Interrupt Status | ComWake    | the interrupt enabled by bit 5 of the Port Interrupt Enable register.              |

| ·                | Bit 5      |                                                                                    |

| SControl         | SPM        | This bit field initiates transitions to/from Partial or Slumber power management   |

|                  | Bits 15-12 | states; bit 14 corresponds to ComWake (exit power management); bit 13              |

|                  |            | corresponds to Slumber mode; bit 12 corresponds to Partial mode.                   |

| SControl         | IPM        | This bit field disables transitions to Partial or Slumber power management states; |

|                  | Bits 11-8  | bit 9 corresponds to Slumber mode; bit 8 corresponds to Partial mode.              |

| SStatus          | IPM        | This bit field reports the power management state; '0110' corresponds to Slumber   |

|                  | Bits 11-8  | mode; '0010' corresponds to Partial mode.                                          |

**Table 7-1 Power Management Register Bits**

There are two power management modes: Partial and Slumber. These power management modes may be software initiated through the SControl register or device initiated from the Serial ATA device.

Transitions to and from either power management mode generate an interrupt, the Power Management Mode Change Interrupt, which may be masked in the Port Interrupt Enable register (bit 3).

Partial/Slumber mode may be initiated by software through the SControl register. By setting the SPM field to either '0001' (Partial) or '0010' (Slumber), software causes a PMREQ to the Serial ATA device, which will respond with either a PMACK or PMNAK. If a PMACK is received the Partial/Slumber mode is entered. A PMNAK is ignored; the request remains asserted.

The Serial ATA device may initiate Partial/Slumber mode. Software enables the acknowledgement of this request by setting the IPM field in the SControl register to '0001' (Partial), '0010' (Slumber), or '0011' (Partial or Slumber). If enabled, a PMACK will be sent to the device; if not enabled, a PMNAK will be sent. When the request is received and its acknowledgement is enabled, Partial/Slumber mode is entered.

Partial/Slumber mode status is reported in the SStatus register ('0010'/'0110' in the IPM field).

Partial/Slumber mode is cleared by ComWake (asserted when the SPM field is set to '0100').

# 8 Flash, GPIO, EEPROM, and I<sup>2</sup>C Programming

## 8.1 Flash Memory Access

The Sil3132 supports an external Flash memory device of up to 4 Mbits (512 KBytes) in capacity. Access to the Flash memory is available using either PCI Direct Access or Register Access.

#### 8.1.1 PCI Direct Access

Access to the Expansion Rom is enabled by setting bit 0 in the Expansion Rom Base Address register at Offset 30h of the PCI Configuration Space. When this bit is set, bits [31:19] of the same register are programmable by the system to set the base address for all Flash memory accesses. Read and write operations with the Flash memory are initiated by Memory Read and Memory Write commands on the PCI bus. Accesses may be as Bytes, Words, or DWords.

#### 8.1.2 Register Access

This type of Flash memory access is carried out through a sequence of internal register read and write operations. The proper programming sequences are detailed below.

#### 8.1.2.1 Flash Write Operation

Verify that Flash Address register bit 25 (Mem Access Start) is zero. The bit is one when a memory access is in progress. It is zero when the memory access is complete and ready for another operation.

Program the write address for the Flash memory access. The address field is bits [18:0] in the Flash Address register.

Program the write data for the Flash memory access. The data field is bits [7:0] in the Flash Memory Data register.

Program Flash Address register bit 24 (Mem Access Type) to zero for a memory write.

Initiate the Flash memory access by setting bit 25 in the Flash Address register.

#### 8.1.2.2 Flash Read Operation

Verify that Flash Address register bit 25 (Mem Access Start) is zero. The bit is one when a memory access is in progress. It is zero when the memory access is complete and ready for another operation.

Program the read address for the Flash memory access. The address field is bits [18:0] in the Flash Address register.

Program Flash Address register bit 24 (Mem Access Type) to one for a memory read.

Initiate the Flash memory access by setting bit 25 in the Flash Address register.

Verify that Flash Address register bit 25 (Mem Access Start) is clear. The bit is one when a memory access is in progress. It is zero when the memory access is complete.

Read the data from bits [7:0] in the Flash Memory Data register.

## 8.2 I<sup>2</sup>C Operation

The Sil3132 provides a Multimaster I<sup>2</sup>C interface. For Auto-initialization of some PCI Configuration registers an external 256-byte EEPROM memory device may be connected to this I<sup>2</sup>C interface (see section 6). Two registers are provided for programmed read/write access to the I<sup>2</sup>C interface: the I<sup>2</sup>C Address register and the I<sup>2</sup>C Data/Control register.

#### 8.2.1.1 I<sup>2</sup>C Write Operation

Verify that I<sup>2</sup>C Data/Control register bit 31 (I<sup>2</sup>C Access Start) is zero. The bit is one when an access is in progress. It is zero when the access is complete and another operation may be started.

Write '1' to clear bit 28 in the I<sup>2</sup>C Data/Control register. This bit is set if an error occurred during a previous access.

Program the write address for the access in the I<sup>2</sup>C Address register.

Program the write data for the access in the I<sup>2</sup>C Data/Control register (bits 7:0).

Write zero to bit 24 (I<sup>2</sup>C Access Type) in the I<sup>2</sup>C Address register.

Initiate the I<sup>2</sup>C write by setting bit 31 (I<sup>2</sup>C Access Start) in the I<sup>2</sup>C Data/Control register.

Poll bit 31 in the I<sup>2</sup>C Data/Control register. The bit is one while an access is in progress. It becomes zero when the access completes. (Alternatively, the I<sup>2</sup>C Interrupt may be enabled by the Global Control register and Global Interrupt Status register)

Check bit 28 in the I<sup>2</sup>C Data/Control register. The bit is set if an error occurred during the access.

#### 8.2.1.2 I<sup>2</sup>C Read Operation

Verify that I<sup>2</sup>C Data/Control register bit 31 (I<sup>2</sup>C Access Start) is zero. The bit is one when an access is in progress. It is zero when the access is complete and another operation may be started.

Write '1' to clear bit 28 in the I<sup>2</sup>C Data/Control register. The bit is set if an error occurred during a previous access.

Program the read address for the access in the I<sup>2</sup>C Address register.

Write one to bit 24 (I<sup>2</sup>C Access Type) in the I<sup>2</sup>C Address register.

Initiate the I<sup>2</sup>C read by setting bit 31 (I<sup>2</sup>C Access Start) in the I<sup>2</sup>C Data/Control register.

Poll bit 31 in the I<sup>2</sup>C Data/Control register. The bit is one while an access is in progress. It becomes zero when the access completes. (Alternatively, the I<sup>2</sup>C Interrupt may be enabled by the Global Control register and Global Interrupt Status register.)

Check bit 28 in the I<sup>2</sup>C Data/Control register. The bit is set if an error occurred during the access.

Read the data from bits 7:0 in the I<sup>2</sup>C Data/Control register.

#### **Legal Statement**

#### **Copyright Notice**

Copyright © 2006 Silicon Image, Inc. All rights reserved. These materials contain proprietary and/or confidential information (including trade secrets, copyright and/or other interests) of Silicon Image, Inc. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/services from Silicon Image or its affiliates, and/or only in connection with your purchase of products and/or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions herein. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of or distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

#### **Trademark Acknowledgment**

Silicon Image<sup>TM</sup>, VastLane<sup>TM</sup>, SteelVine<sup>TM</sup>, PinnaClear<sup>TM</sup>, Simplay<sup>TM</sup>, Simplay HD<sup>TM</sup>, Satalink<sup>TM</sup>, and TMDS<sup>TM</sup> are trademarks or registered trademarks of Silicon Image, Inc. in the United States and other countries. HDMI<sup>TM</sup>, the HDMI logo and High-Definition Multimedia Interface<sup>TM</sup> are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC.

#### **Disclaimers**

These materials are provided on an "AS IS" basis. SILICON IMAGE, INC. AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), INCLUDING BUT NOT LIMITED TO: (I) ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS; (II) ALL WARRANTIES ARISING OUT OF COURSE-OF-DEALING, USAGE, AND/OR TRADE; AND (III) ALL WARRANTIES THAT THE INFORMATION OR RESULTS PROVIDED IN, OR THAT MAY BE OBTAINED FROM USE OF, THE MATERIALS ARE ACCURATE, RELIABLE, COMPLETE, UP-TO-DATE, OR PRODUCE SPECIFIC OUTCOMES. SILICON IMAGE, INC. AND ITS AFFILIATES ASSUME NO LIABILITY OR RESPONSIBILITY FOR ANY ERRORS OR OMISSIONS IN THESE MATERIALS, MAKES NO COMMITMENT OR WARRANTY TO CORRECT ANY SUCH ERRORS OR OMISSIONS OR UPDATE OR KEEP CURRENT THE INFORMATION CONTAINED IN THESE MATERIALS, AND EXPRESSLY DISCLAIMS ALL DIRECT, INDIRECT, SPECIAL, INCIDENTAL, CONSEQUENTIAL, RELIANCE AND PUNITIVE DAMAGES, INCLUDING WITHOUT LIMITATION ANY LOSS OF PROFITS ARISING OUT OF YOUR ACCESS TO, USE OR INTERPRETATION OF, OR ACTIONS TAKEN OR NOT TAKEN BASED ON THE CONTENT OF THESE MATERIALS.

Silicon Image, Inc. and its affiliates reserve the right, without notice, to periodically modify the information in these materials, and to add to, delete, and/or change any of this information.

Notwithstanding the foregoing, these materials shall not, in the absence of authorization under U.S. and local law and regulations, as required, be used by or exported or re-exported to (i) any U.S. sanctioned or embargoed country, or to nationals or residents of such countries; or (ii) any person, entity, organization or other party identified on the U.S. Department of Commerce's Denied Persons or Entity List, the U.S. Department of Treasury's Specially Designated Nationals or Blocked Persons List, or the Department of State's Debarred Parties List, as published and revised from time to time; (iii) any party engaged in nuclear, chemical/biological weapons or missile proliferation activities; or (iv) any party for use in the design, development, or production of rocket systems or unmanned air vehicles.

#### **Products and Services**

The products and services described in these materials, and any other information, services, designs, know-how and/or products provided by Silicon Image, Inc. and/or its affiliates are provided on as "AS IS" basis, except to the extent that Silicon Image, Inc. and/or its affiliates provides an applicable written limited warranty in its standard form license agreements, standard Terms and Conditions of Sale and Service or its other applicable standard form agreements, in which case such limited warranty shall apply and shall govern in lieu of all other warranties (express, statutory, or implied). EXCEPT FOR SUCH LIMITED WARRANTY, SILICON IMAGE, INC. AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), REGARDING THE INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS PROVIDED BY SILICON IMAGE, INC. AND/OR ITS AFFILIATES, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. YOU ACKNOWLEDGE AND AGREE THAT SUCH INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS HAVE NOT BEEN DESIGNED, TESTED, OR MANUFACTURED FOR USE OR RESALE IN SYSTEMS WHERE THE FAILURE, MALFUNCTION, OR ANY INACCURACY OF THESE ITEMS CARRIES A RISK OF DEATH OR SERIOUS BODILY INJURY, INCLUDING, BUT NOT LIMITED TO, USE IN NUCLEAR FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION, EMERGENCY SYSTEMS, OR OTHER SYSTEMS WITH A SIMILAR DEGREE OF POTENTIAL HAZARD. NO PERSON IS AUTHORIZED TO MAKE ANY OTHER WARRANTY OR REPRESENTATION CONCERNING THE PERFORMANCE OF THE INFORMATION, PRODUCTS, KNOW-HOW, DESIGNS OR SERVICES OTHER THAN AS PROVIDED IN THESE TERMS AND CONDITIONS.

## Silicon Image, Inc. -

#### **Further Information**

To request other materials, documentation, and information, contact your local Silicon Image, Inc. sales office or visit the Silicon Image, Inc. web site at <a href="https://www.siliconimage.com">www.siliconimage.com</a>.