# **DUAL LINEAR-ANTILOG VOLTAGE CONTROLLED AMPLIFIER**

#### DESCRIPTION

The SSM 2022 is a low cost, high performance, dual voltage-controlled amplifier designed for easy use in programable electronic music systems, and as a general purpose gain control element. On-chip control amplifiers have been provided for each channel for independent linear or antilog gain control. The signal and linear control inputs are current summing nodes and current outputs allow for summing by simple connection. The signal channels offer low noise, low distortion, wide bandwidth, and low control feedthrough. The device requires few external components to implement its basic function.

#### **FEATURES**

- Low Cost

- Wide Supply Range

- Low 3rd Harmonic Distortion

- 82db Signal Noise

- Low Control Voltage Feedthrough

- Adjustable Gain Scale

- Temperature Compensated Gain Cells Process Controllers

- Wide Bandwidth

- Summing Node Signal Inputs

- Current Outputs

- Linear and Exponential Gain Control

- Minimum External Part Count

#### **APPLICATIONS**

- 2 and 4 Quandrant **Multipliers**

- Limiters

- Voltage-Controlled, Low Distortion Sine Wave Oscillators

- Compandors

- Voltage-Controlled Filters

- AGC Circuits

- Data Aguisition

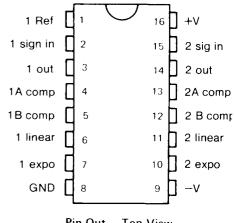

Pin Out - Top View

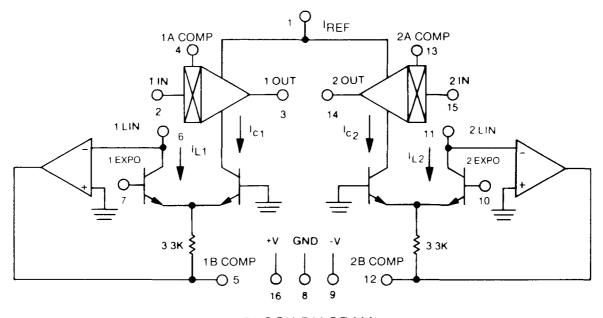

**BLOCK DIAGRAM**

### SPECIFICATIONS\*

@ V5 =  $\pm 15$ V. IREF = 0.8 mA, TA =  $25^{\circ}$  C

| PARAMETER                                                                 | MIN | ТҮР  | MAX  | UNITS          | CONDITIONS                                              |

|---------------------------------------------------------------------------|-----|------|------|----------------|---------------------------------------------------------|

| Supply Voltage                                                            | ±4  | ±15  | ±18  | V              |                                                         |

| Supply Current Positive                                                   | 2.3 | 2.6  | 3.0  | mA             | I <sub>C1</sub> = I <sub>C2</sub> = 0                   |

| Negative                                                                  | 2.3 | 2.4  | 2.5  | mA             | ICI = IC2 = 0                                           |

| Reference Current (PIN 1)                                                 |     | -0.8 |      | mA             |                                                         |

| Peak Input Signal<br>Current                                              |     | ±100 | ±200 | μΑ             | (±200 μA at Clipping)                                   |

| Current Gain Io/IIN                                                       | 0.9 | 1.0  | 1.1  | _              | I <sub>C1</sub> = I <sub>C2</sub> = 200 μA              |

| Gain Tempco                                                               |     | +200 |      | ppm/C°         |                                                         |

| Current Bandwidth                                                         |     | 1    |      | MHz            | $I_{C1} = I_{C2} = 200 \mu A$                           |

| Channel Separation                                                        |     | 100  |      | db             | @ 1 KHz                                                 |

| Output Offset<br>(Untrimmed)                                              |     | -2   | ±5   | μΑ             | I <sub>Cl</sub> = I <sub>C2</sub> = 200 μA              |

| Signal to Noise                                                           |     | 82   |      | db             | 20 Hz to 20 KHz, I <sub>SIG</sub> = ±100μ.              |

| Distortion                                                                |     | 1.2  |      | % 2nd<br>% 3rd | $I_{C1} = I_{C2} = 200 \mu A$ $I_{S G} = \pm 100 \mu A$ |

| Max Control Current I <sub>C</sub> (For Best Performance)                 |     | _    | 400  | μА             |                                                         |

| Control OP AMP Input<br>Bias Current                                      | _   | 50   | 150  | nA             |                                                         |

| Expo Control Input<br>Current                                             | 0.8 | 1.6  | 2.6  | μΑ             | I <sub>L1</sub> = I <sub>L2</sub> = 200 μA              |

| Control Feedtrough<br>(Untrimmed)<br>20 Log <sub>10</sub> (Lout)          | _   | -40  | 32   | db             | 0 ≤ I <sub>C1</sub> , I <sub>C2</sub> ≤200 μA           |

| Control Feedtrough<br>(Trimmed)<br>20 Log <sub>10</sub> (1 out<br>IC MAX) |     | -56  |      | db             | 0 ≤ I <sub>C1</sub> , I <sub>C2</sub> ≤200 μA           |

| Linear Control Input<br>Offset Voltage                                    | -5  | 0    | +5   | m∨             |                                                         |

| Exponential Control<br>Sensitivity                                        |     | -18  |      | mV/Octave      | (At PINS 7 AND 10)                                      |

<sup>\*</sup>Final Specification may be subject to change

## **Design Equations**

10 = 4 IC lin/IREF

IC = IL e -Vexpo q/KT

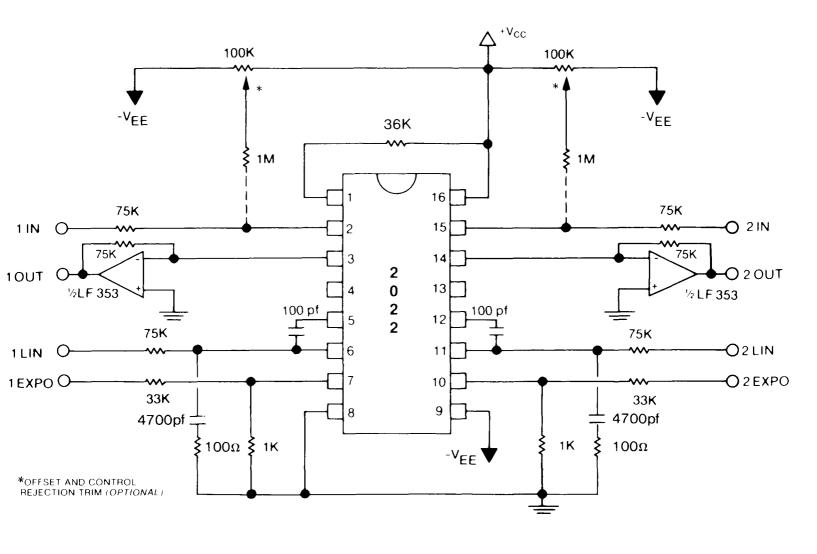

#### **BASIC CONNECTION**

The figure above shows the typical connection of the 2022 as a dual VCA. The signal input(s), pins 2 nd 15, are virtual ground summing nodes. The reference current established at pin 1 determines the level at which the input signal will clip. With reference current of 0.8mA this will be 200uA. The input resistor(s) should be chosen to give a  $\pm$  100uA signal current at the input voltage peaks. The 75K resistor shown will satisfy this condition for a  $\pm$  7.5 signal with clipping taking place at twice this level: the maximum voltages available from  $\pm$  15V supplies. The offset/control feedthrough adjustment is required only for precision applications or to null offsets generated in previous stages.

The output current(s) at pins 3 and 4 is converted to a voltage with the op amp, resistor-network shown. 75K will give unity gain for a control current of 200uA. Ic, the output of the on-chip control circuit, is proportional to the product of the linear control current(s), pins 6 and 11, and the negative exponent of the voltage at the exponential control pins: 7 and 10. For best distortion and control current feedthrough performance, the maximum control current should be in the 200 to 400uA range.

The linear control inputs are virtual ground summing nodes. The sense of the control(s) is from ground up, with the output(s) going to zero with ground at the corresponding control input. The linear control resistor(s) above will give 200uA for a +15V control voltage. The exponential control input attenuator can be designed for a wide range of control sensitivities and input voltage ranges. In all cases the minimum voltage will give maximum gain and the maximum voltage will give maximum attenuation. The input attenuator(s) shown will control the gain of the channel(s) over a 100db range for an input voltage of 0 to +10 volts. Other sensitivities and input voltage ranges can be easily accommodated by changing the attenuation factor and the current at the linear input pin(s).

The 100pf, 100Ω, 4700pf networks provide feedforward compensation of the on-chip control op amps. With these values one can achieve a 1 MHz bandwidth for the signal channel. The actual bandwidth one will realize will be determined by the slew rate and small signal bandwidth of the op amp in the output current of voltage conventors.