The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group

**AUGUST 1977**

TEXAS INSTRUMENTS

#### **IMPORTANT NOTICES**

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

Copyright©1977

Texas Instruments Incorporated

## **TABLE OF CONTENTS**

| 1.         | INTRO  | DDUCTION                                               |

|------------|--------|--------------------------------------------------------|

|            | 1.1    | General                                                |

|            | 1.2    | Manual Organization                                    |

|            | 1.3    | Specifications                                         |

|            | 1.4    | Board Characteristics                                  |

|            | 1.5    | Glossary                                               |

|            | 1.6    | Applicable Documents                                   |

|            |        |                                                        |

| 2.         | INSTA  | LLATION AND OPERATION                                  |

|            | 2.1    | General                                                |

|            | 2.2    | Required Equipment                                     |

|            | 2.3    | Unpacking                                              |

|            | 2.4    | Power and Terminal Hookup                              |

|            | 2.4.1  | Power Supply Hookup                                    |

|            | 2.4.2  | Terminal Hookup                                        |

|            | 2.5    | Operation                                              |

|            | 2.6    | Sample Programs                                        |

|            |        |                                                        |

| 3.         | TIBUG  | INTERACTIVE DEBUG MONITOR                              |

|            | 3.1    | General                                                |

|            | 3.2    | <i>TIBUG</i> Commands                                  |

|            | 3.2.1  | Execute Under Breakpoint (B)                           |

|            | 3.2.2  | CRU Inspect/Change (C)                                 |

|            | 3.2.3  | Dump Memory to Cassette/Paper Tape (D)                 |

|            | 3.2.4  | Execute Command (E)                                    |

|            | 3.2.5  | Find Command (F)                                       |

|            | 3.2.6  | Hexadecimal Arithmetic (H)                             |

|            | 3.2.7  | Load Memory From Cassette or Paper Tape (L)            |

|            | 3.2.8  | Memory Inspect/Change, Memory Dump (M)                 |

|            | 3.2.9  | Inspect/Change User WP, PC, and ST Registers (R)       |

|            | 3.2.10 | Execute in Step Mode (S)                               |

|            | 3.2.11 | TI 733 ASR Baud Rate (T)                               |

|            | 3.2.12 | Inspect/Change User Workspace (W)                      |

|            | 3.3    | User Accessible Utilities                              |

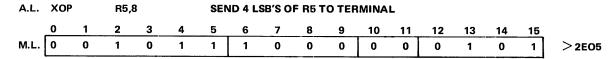

|            | 3.3.1  | Write One Hexadecimal Character to Terminal (XOP 8)    |

|            | 3.3.2  | Read Hexadecimal Word FromTerminal (XOP 9)             |

|            | 3.3.3  | Write Four Hexadecimal Characters to Terminal (XOP 10) |

|            | 3.3.4  | Echo Character (XOP 11)                                |

|            | 3.3.5  | Write One Character to Terminal (XOP 12)               |

|            | 3.3.6  | Read One Character from Terminal (XOP 12)              |

|            | 3.3.6  |                                                        |

|            |        | Write Message to Terminal (XOP 14)                     |

|            | 3.4    | TIBUG Error Messages                                   |

| 4.         | BBAAR  | AMMING THE TM 990/100M                                 |

| <b>+</b> . | 4.1    | General                                                |

|            |        | ·                                                      |

|            | 4.2    | User Memory                                            |

|            | 4.3    | · · · · · · · · · · · · · · · · · · ·                  |

|            | 4.3.1  | Program Counter                                        |

|            | 4.3.2  | Workspace Pointer                                      |

## **TABLE OF CONTENTS (Continued)**

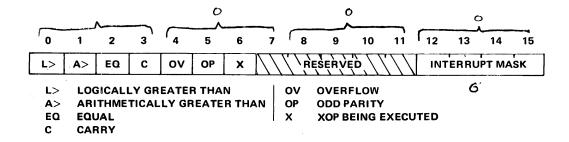

|                        | 4.3.3                                                                                                        | Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | 4.4                                                                                                          | Software Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        | 4.5                                                                                                          | Instruction Formats and Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

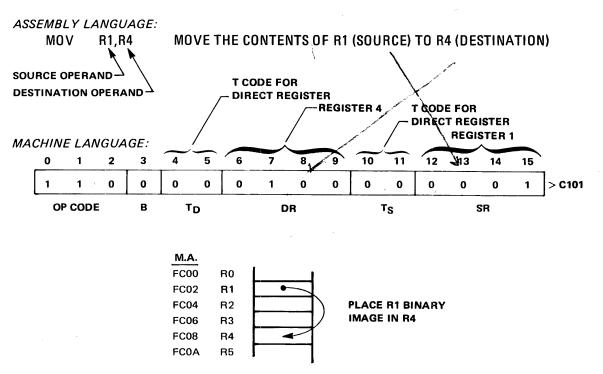

|                        | 4.5.1                                                                                                        | Direct Register Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        | 4.5.2                                                                                                        | Indirect Register Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | 4.5.3                                                                                                        | Indirect Register Autoincrement Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        | 4.5.4                                                                                                        | Symbolic Memory Addressing, Not Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 4.5.5                                                                                                        | Symbolic Memory Addressing, Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 4.6                                                                                                          | Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | 4.6.1                                                                                                        | Format 1 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.2                                                                                                        | Format 2 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.3                                                                                                        | Format 3 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.4                                                                                                        | Format 4 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.5                                                                                                        | Format 5 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.6                                                                                                        | Format 6 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.7                                                                                                        | Format 7 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.8                                                                                                        | Format 8 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.6.9                                                                                                        | Format 9 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 4.7                                                                                                          | CRU Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                        | 4.8                                                                                                          | Comparison of Jumps, Branches, XOP's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | 4.9                                                                                                          | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        | 4.9.1                                                                                                        | Interrupt Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 4.9.2                                                                                                        | Programmable Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 4.10                                                                                                         | Programming the Interval Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                        | 4.10.1                                                                                                       | TMS 9901 Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        |                                                                                                              | TMS 9902 Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 4.10.2                                                                                                       | 1 MS 9902 Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                        | 4.10.2<br>4.11                                                                                               | Context Switch to Another Program such as Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                        |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.                     | 4.11                                                                                                         | Context Switch to Another Program such as Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.                     | 4.11                                                                                                         | Context Switch to Another Program such as Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.                     | 4.11 THEOR                                                                                                   | Y OF OPERATION         5-1           System Clock         5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

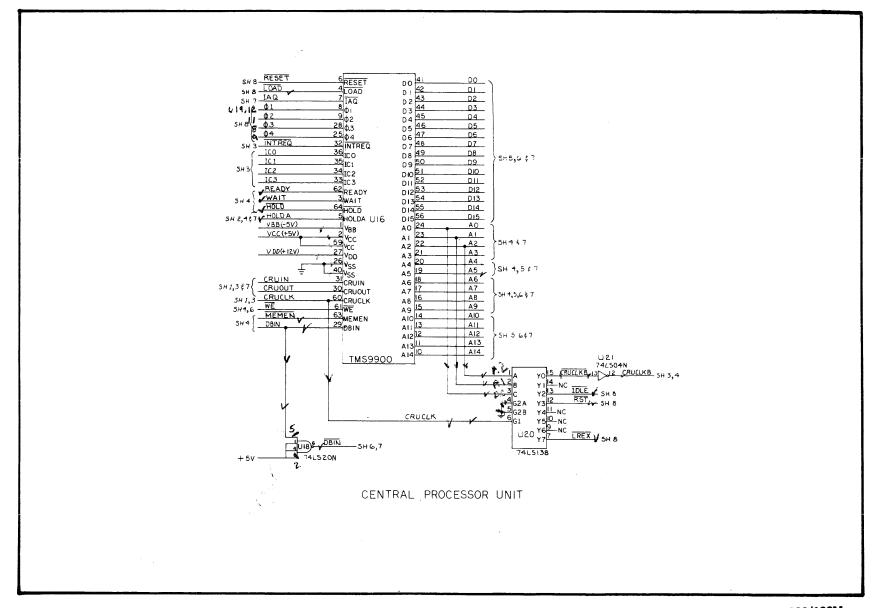

| 5.                     | 4.11<br>THEOR<br>5.1                                                                                         | Y OF OPERATION       5-1         System Clock       5-1         Central Processing Unit       5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2                                                                                  | Y OF OPERATION         5-1           System Clock         5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3                                                                           | Y OF OPERATION       5-1         System Clock       5-1         Central Processing Unit       5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

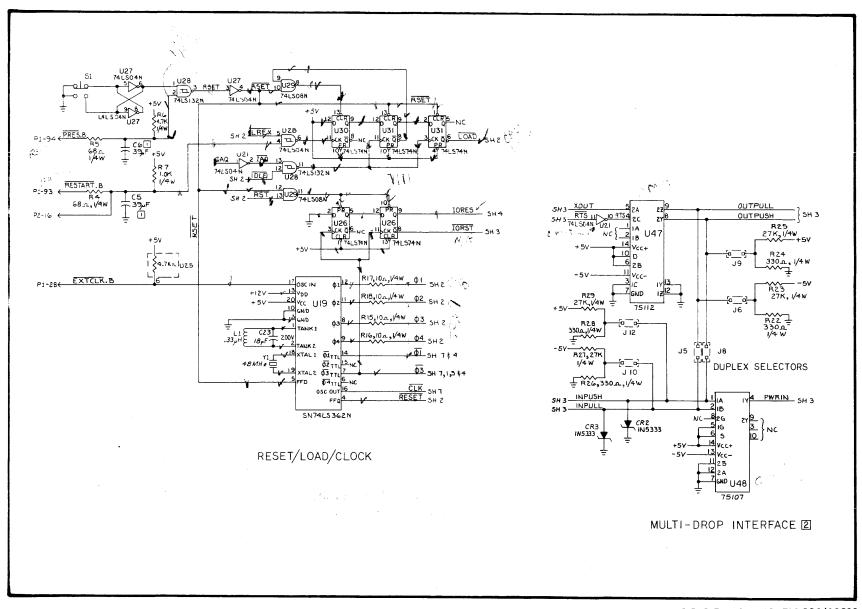

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4                                                                    | Y OF OPERATION       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

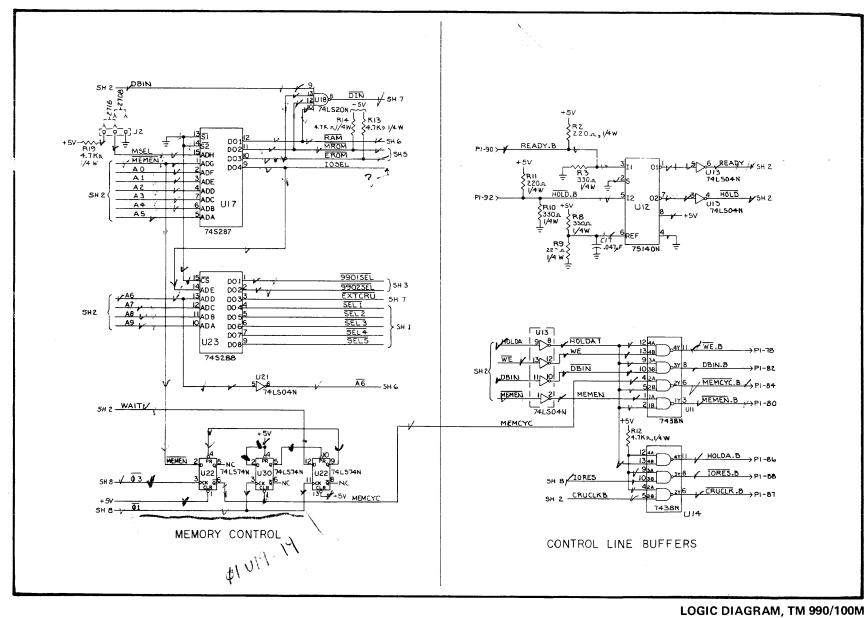

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                             | Y OF OPERATION       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

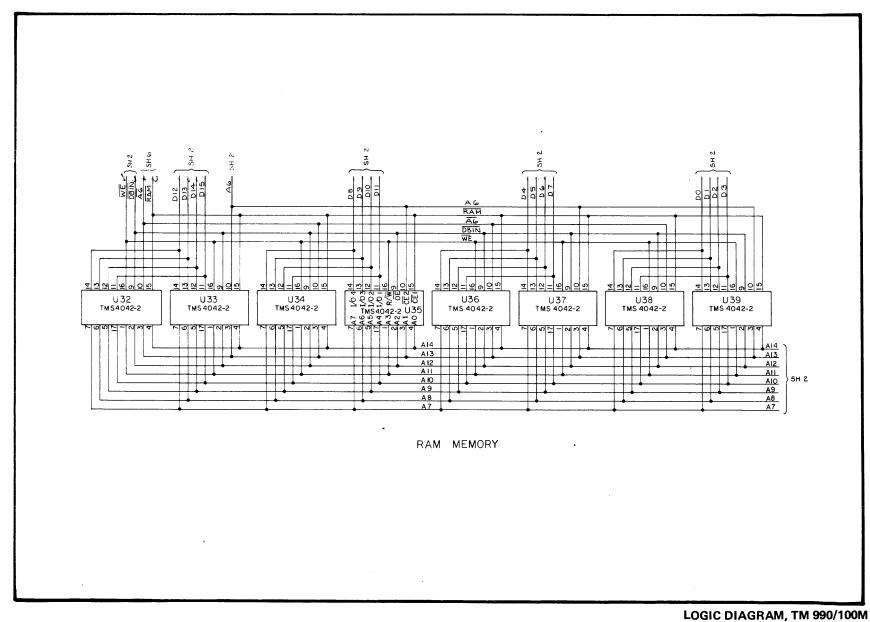

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                      | Y OF OPERATION       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

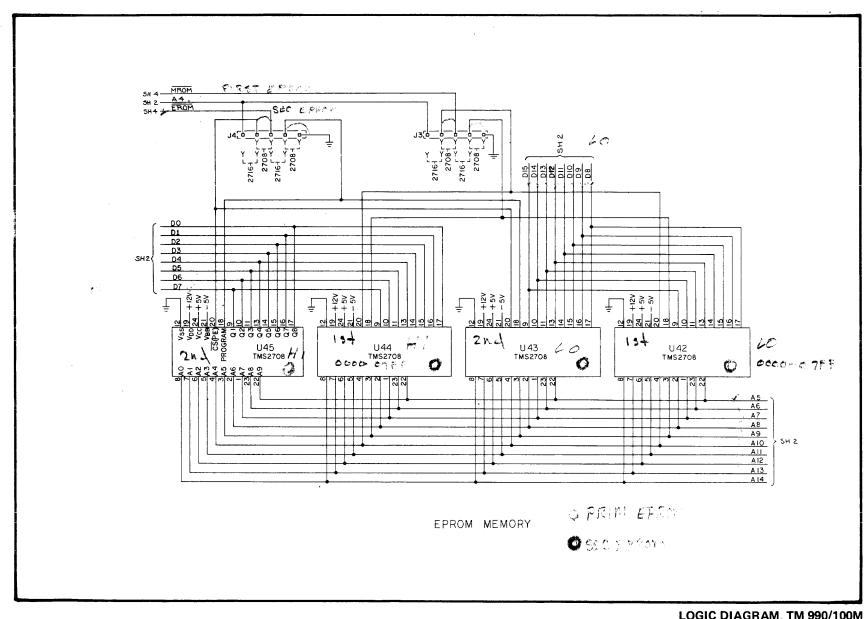

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                               | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7                                                                                                                                                                                                                                                                                                                                                                                                                    |

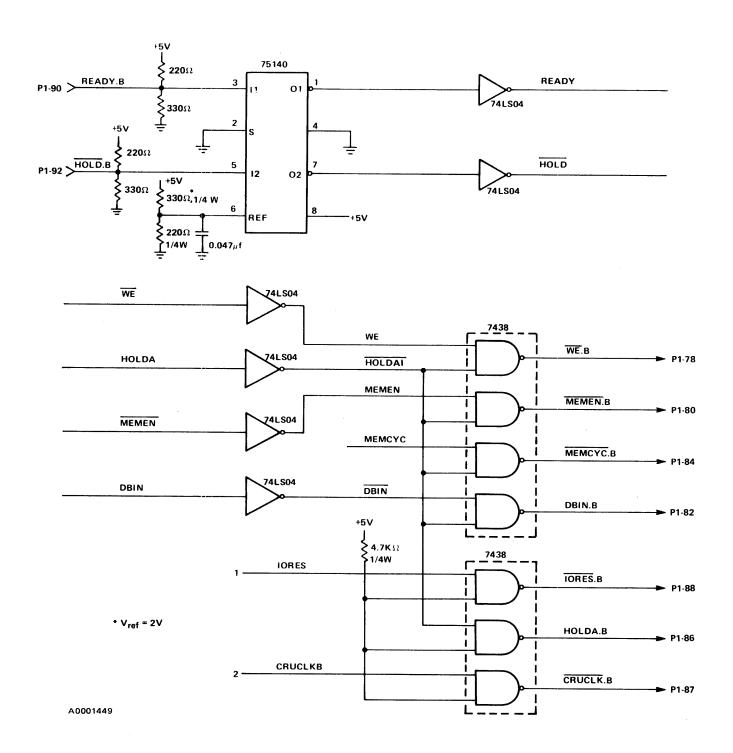

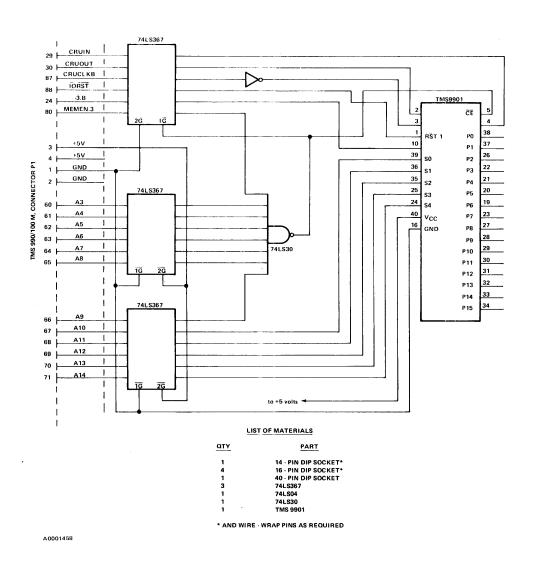

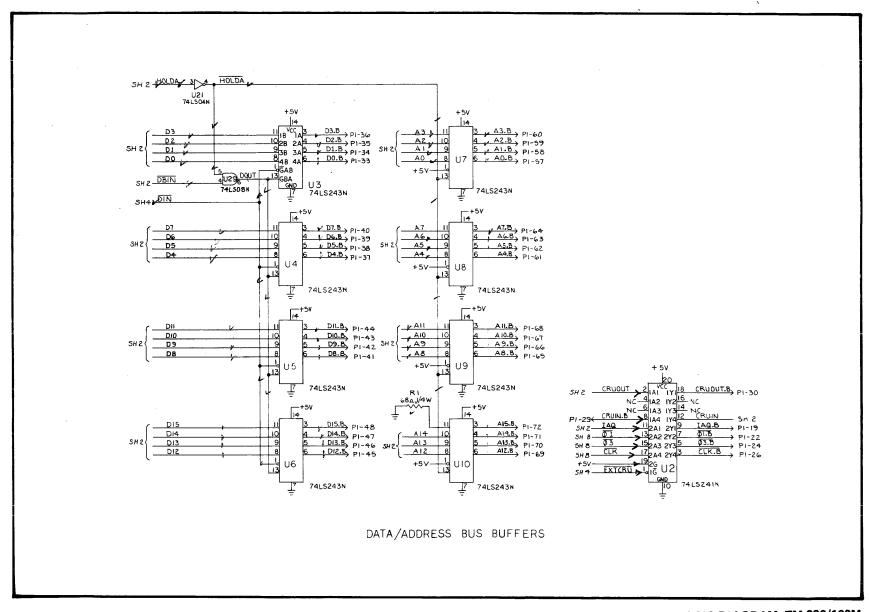

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                        | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8                                                                                                                                                                                                                                                                                                                   |

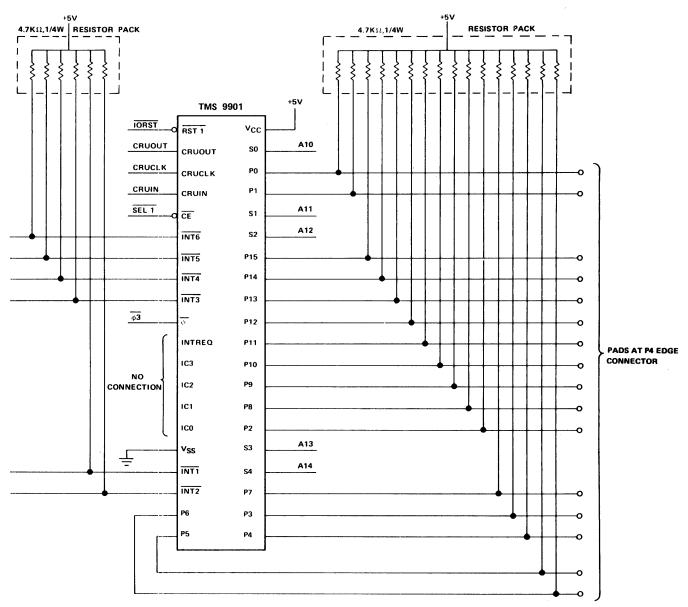

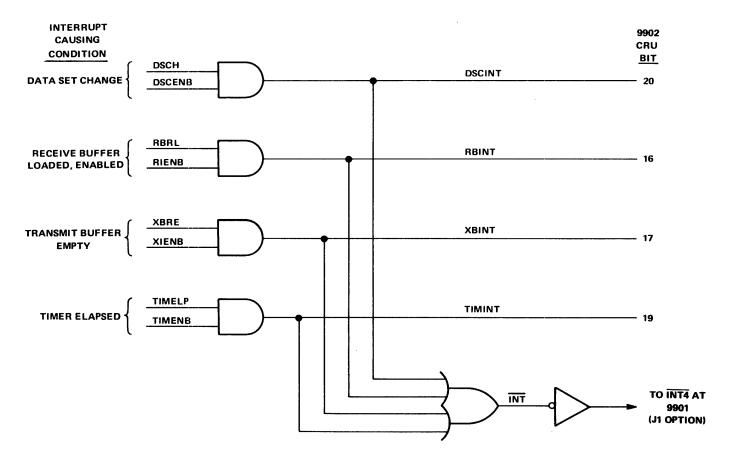

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                 | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8                                                                                                                                                                                                                                                                                                                                                                       |

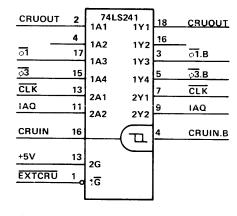

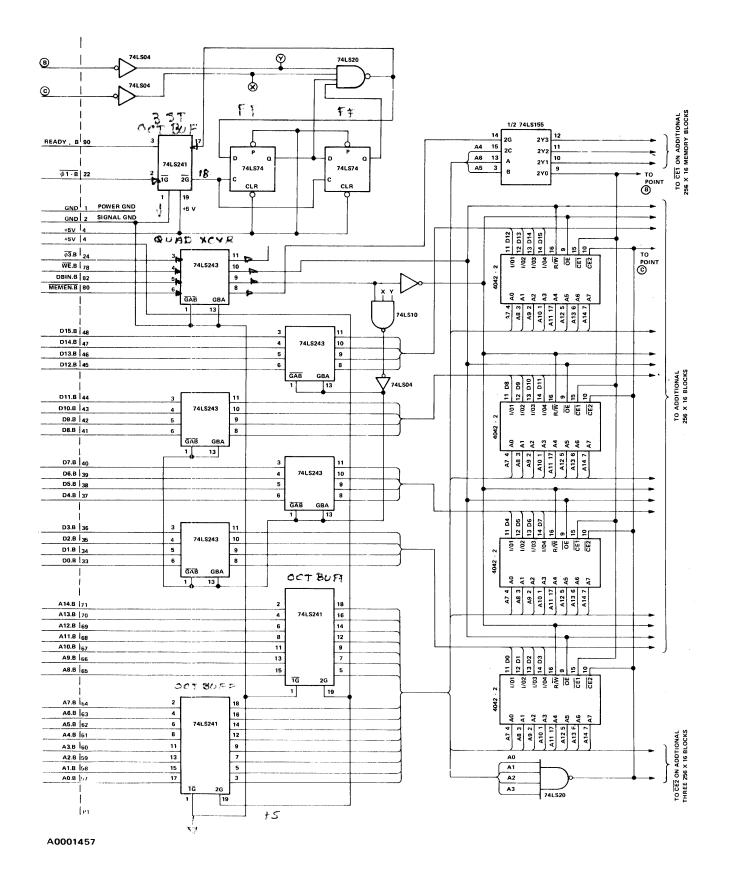

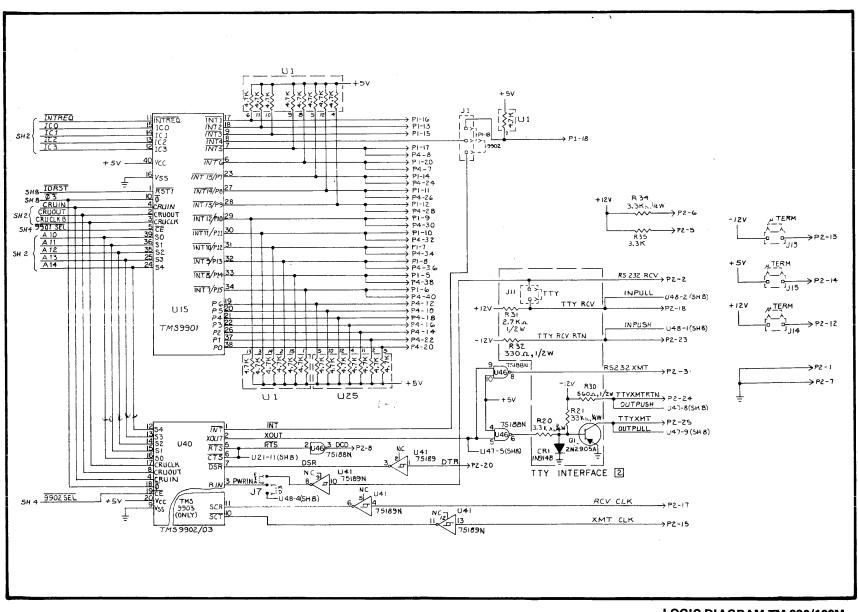

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                         | Y OF OPERATION       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15                                                                                                                                                                                                                                                                                                                                                                 |

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                 | Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15                                                                                                                                                                                                                                                                                               |

| 5.                     | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12         | Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15         Wire-Wrap Area       5-15                                                                                                                                                                                                                                                             |

| <ol> <li>6.</li> </ol> | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13 | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15         Wire-Wrap Area       5-15         Multidrop Interface       5-15                                                                                                                                                 |

|                        | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13 | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15         Wire-Wrap Area       5-15         Multidrop Interface       5-15         ATIONS         General       6-1                                                                                                        |

|                        | 4.11<br>THEOR<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13 | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15         Wire-Wrap Area       5-15         Multidrop Interface       5-15         ATIONS       6-1         General       6-1         Wire-Wrap Additional On-Card TMS 9901       6-1                                      |

|                        | 4.11 THEOR 5.1 5.2 5.3 5.4 5.5 5.6 5.7 5.8 5.9 5.10 5.11 5.12 5.13 APPLIC                                    | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15         Wire-Wrap Area       5-15         Multidrop Interface       5-15         ATIONS         General       6-1         Wire-Wrap Additional On-Card TMS 9901       6-1         Parallel I/O Port Circuitry       6-1  |

|                        | 4.11 THEOR 5.1 5.2 5.3 5.4 5.5 5.6 5.7 5.8 5.9 5.10 5.11 5.12 5.13 APPLIC 6.1 6.2                            | Y OF OPERATION       4-43         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15         Wire-Wrap Area       5-15         Multidrop Interface       5-15         ATIONS       6-1         General       6-1         Wire-Wrap Additional On-Card TMS 9901       6-1         Parallel I/O Port Circuitry       6-1         Off-Card Additional Random Access Memory       6-1 |

|                        | 4.11 THEOR 5.1 5.2 5.3 5.4 5.5 5.6 5.7 5.8 5.9 5.10 5.11 5.12 5.13 APPLIC 6.1 6.2 6.3                        | Context Switch to Another Program such as Monitor       4-43         Y OF OPERATION       5-1         General       5-1         System Clock       5-1         Central Processing Unit       5-1         RESET and LOAD       5-3         Memory I/O Decoder       5-7         Random Access Memory       5-7         Read Only Memory       5-7         Offboard Expansion Buffers       5-8         TMS 9901 Parallel I/O, Interrupts       5-8         TMS 9902 Serial I/O Interface       5-15         Serial I/O Interface       5-15         Wire-Wrap Area       5-15         Multidrop Interface       5-15         ATIONS         General       6-1         Wire-Wrap Additional On-Card TMS 9901       6-1         Parallel I/O Port Circuitry       6-1  |

# **TABLE OF CONTENTS (Concluded)**

7. **OPTIONS** 7.1 G

| 7.2<br>7.2.1<br>7.2.2    | On-Board Memory Expansion                          |

|--------------------------|----------------------------------------------------|

| 7.2.2                    | RAM Expansion                                      |

| 7.3<br>7.4               | Asynchronous Serial Communication                  |

| 7.5                      | External System Reset                              |

| 7.6                      | Memory Map Change                                  |

| 7.0<br>7.7               | Line-By-Line Assembler                             |

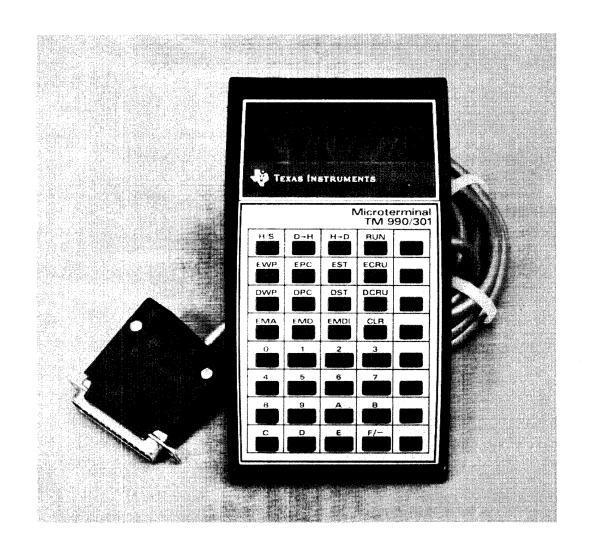

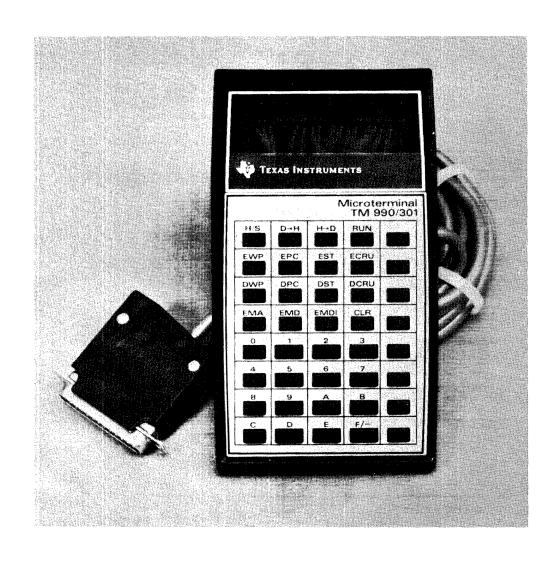

| 7.7                      | TM 990/301 Microterminal                           |

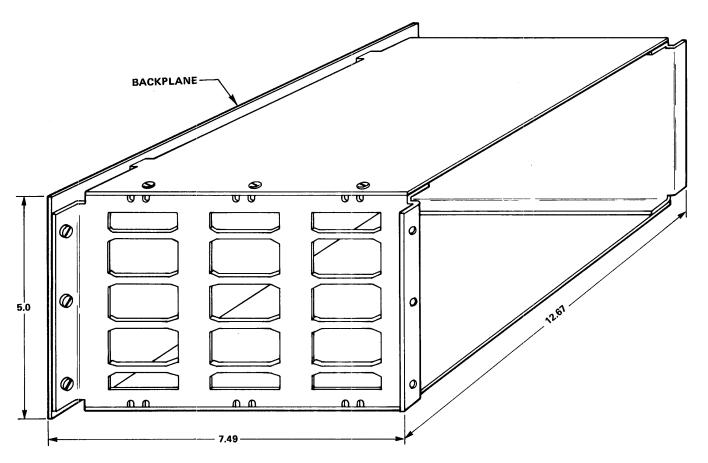

| 7.0<br>7.9               | OEM Chassis                                        |

| 7.10                     | Interrupt from TMS 9902                            |

| ,                        |                                                    |

|                          | APPENDICES                                         |

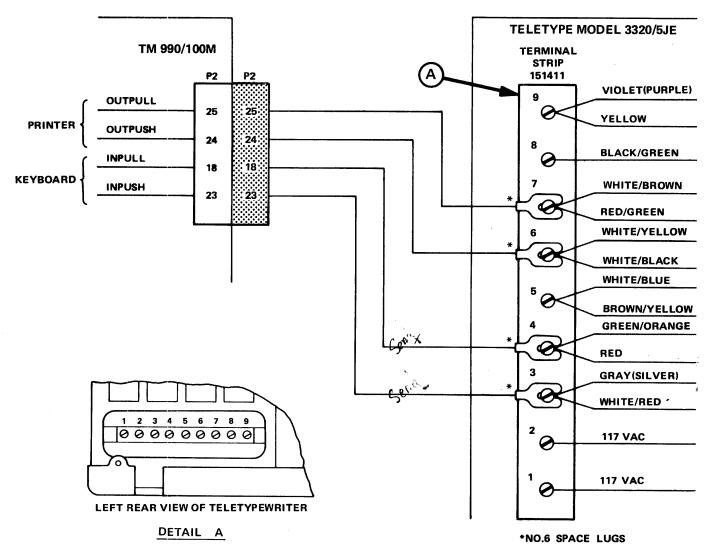

| A                        | WIRING TELETYPE MODEL 3320/SJE FOR TM 990/100M     |

| B<br>C                   | EIA RS-232-C CABLING                               |

|                          | ASCII CODE                                         |

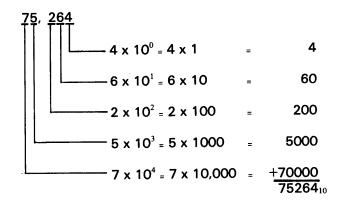

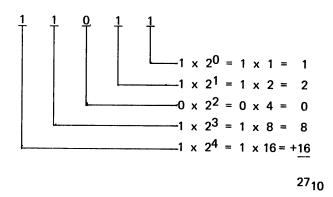

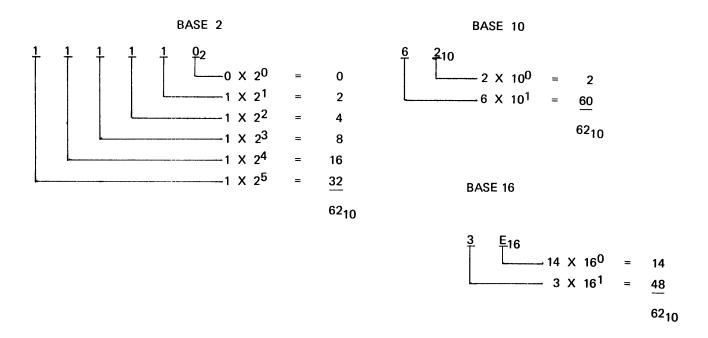

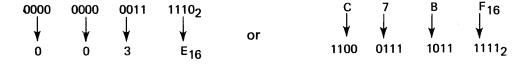

| D<br>E                   | BINARY, DECIMAL, AND HEXADECIMAL NUMBERING         |

| F                        | PARTS LIST SCHEMATICS                              |

| G                        | 990 OBJECT CODE FORMAT                             |

| Н                        | P1, P2, AND P4 PIN ASSIGNMENTS                     |

| 1                        | TM 990/301 MICROTERMINAL                           |

|                          |                                                    |

|                          | LIST OF ILLUSTRATIONS                              |

| Figure 1-1               | TM 990/100M Microcomputer PC Board                 |

| Figure 1-2               | Principal TM 990/100M Components                   |

| Figure 1-3               | TM 990/100M Board Dimensions                       |

| F. 0.4                   |                                                    |

| Figure 2-1               | Power Supply Hookup                                |

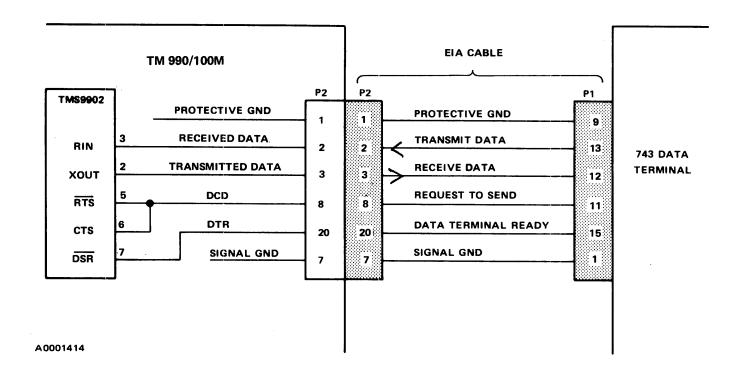

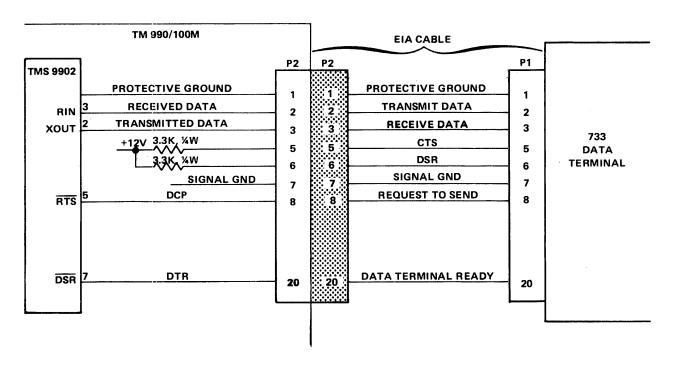

| Figure 2-2               | 743 KSR Terminal Hookup                            |

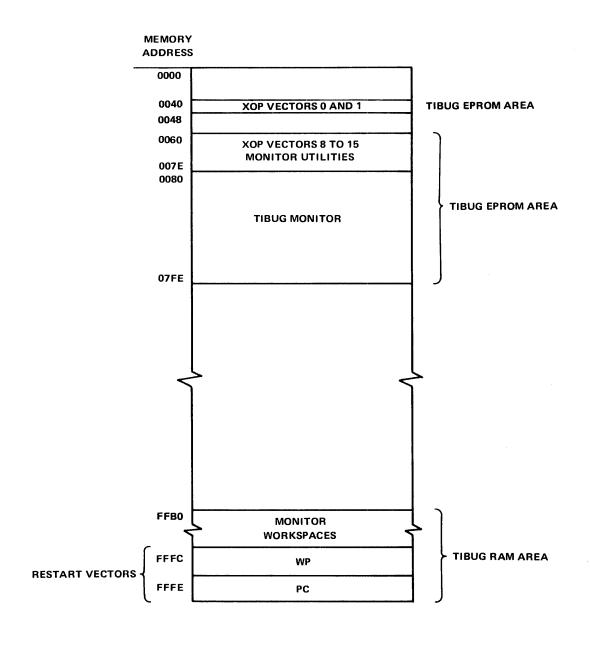

| Figure 3-1               | Memory Requirements for TIBUG                      |

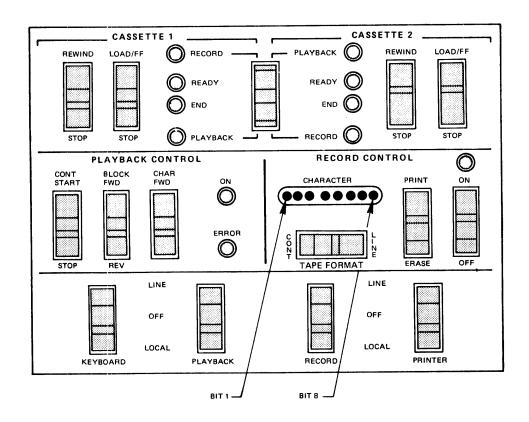

| Figure 3-2               | 733 ASR Upper Switch Panel                         |

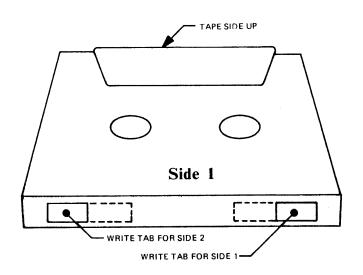

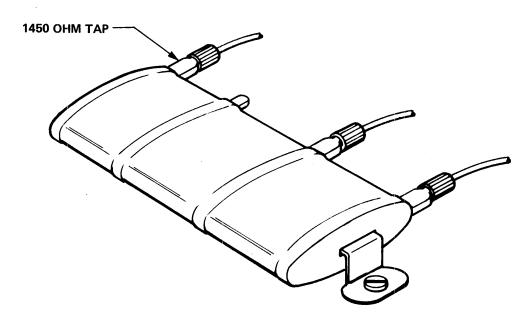

| Figure 3-3               | Tap Tabs                                           |

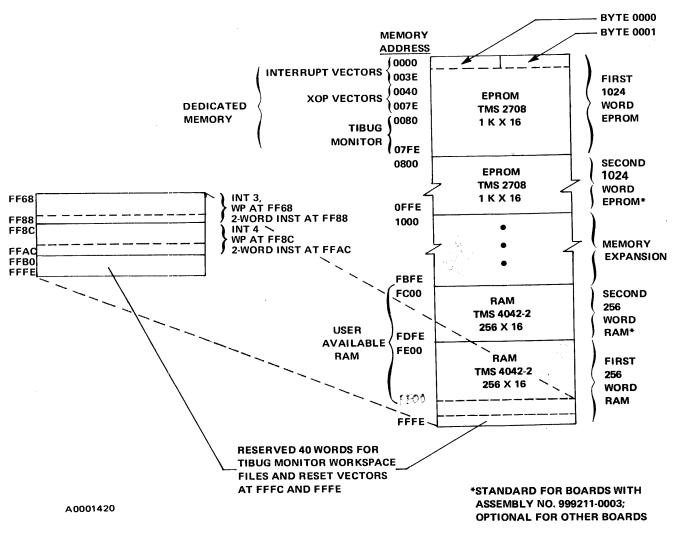

| Figure 4-1               | Memory Map                                         |

| Figure 4-7               | Status Register                                    |

| Figure 4-2               | Workspace Example                                  |

| Figure 4-3               | TM 990/100M Instruction Formats                    |

| Figure 4-4<br>Figure 4-5 | Direct Register Addressing Example                 |

| Figure 4-5               | Indirect Register Addressing Example               |

| Figure 4-7               | Indirect Register Autoincrement Addressing Example |

| Figure 4-7               | Direct Memory Addressing Example                   |

| i igaio T U              | Direct Memory Additionally Example                 |

# LIST OF ILLUSTRATIONS (Continued)

| Figure 4-9  | Direct Memory Addressing, Indexed, Example                       | . 4-13 |

|-------------|------------------------------------------------------------------|--------|

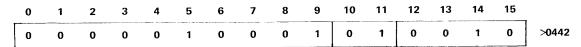

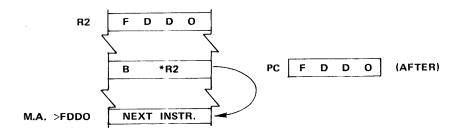

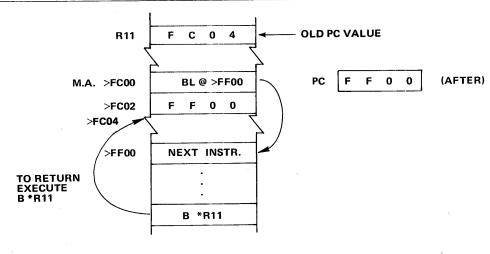

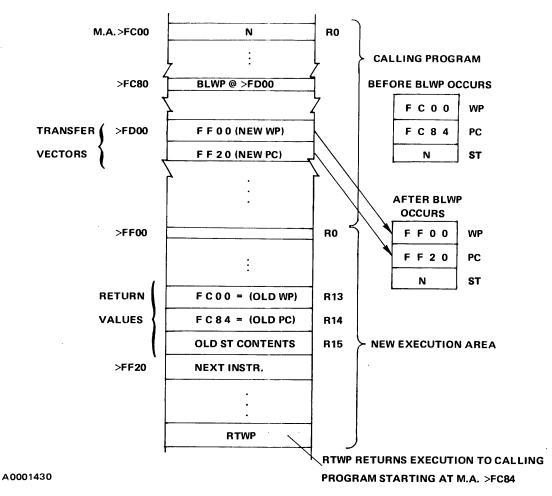

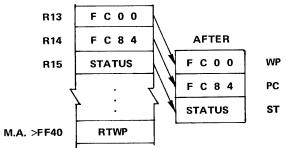

| Figure 4-10 | BLWP Example                                                     | . 4-29 |

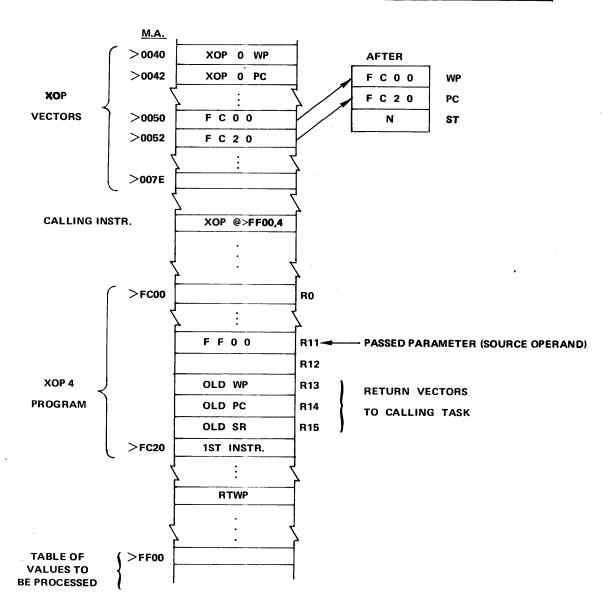

| Figure 4-11 | XOP Example                                                      |        |

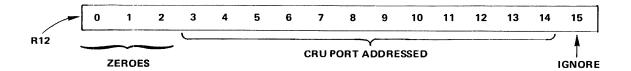

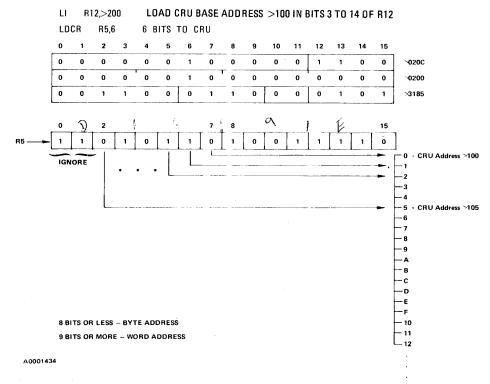

| Figure 4-12 | LDCR Byte Instruction                                            |        |

| Figure 4-13 | STCR Word Instruction                                            |        |

| Figure 4-14 | Interrupt Trap Locations                                         |        |

| Figure 4-15 | Dedicated Instruction and Workspace Areas for Interrupts 3 and 4 |        |

| Figure 4-16 | Enabling and Triggering TMS 9901 Interval Timer                  |        |

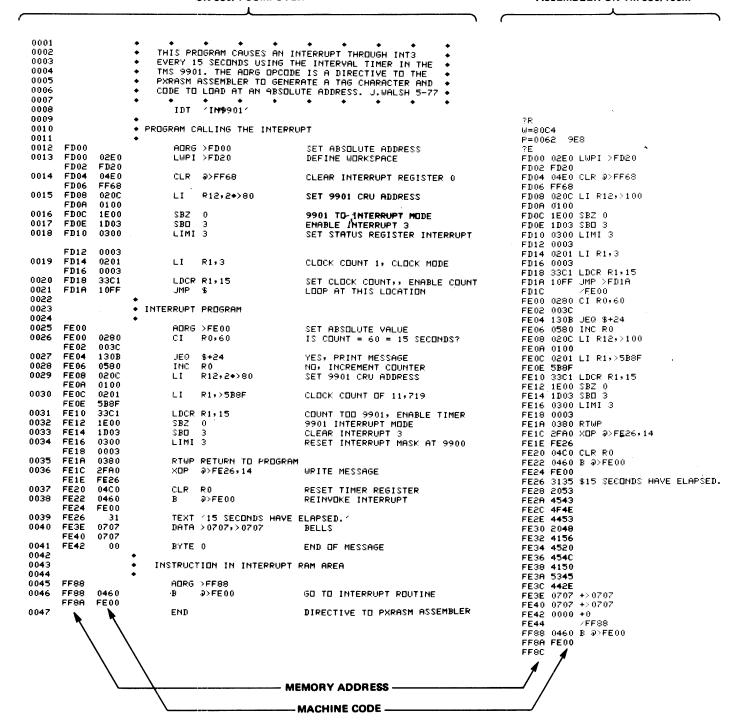

| Figure 4-17 | Example of Code to Run TMS 9901 Interval Timer                   |        |

|             |                                                                  |        |

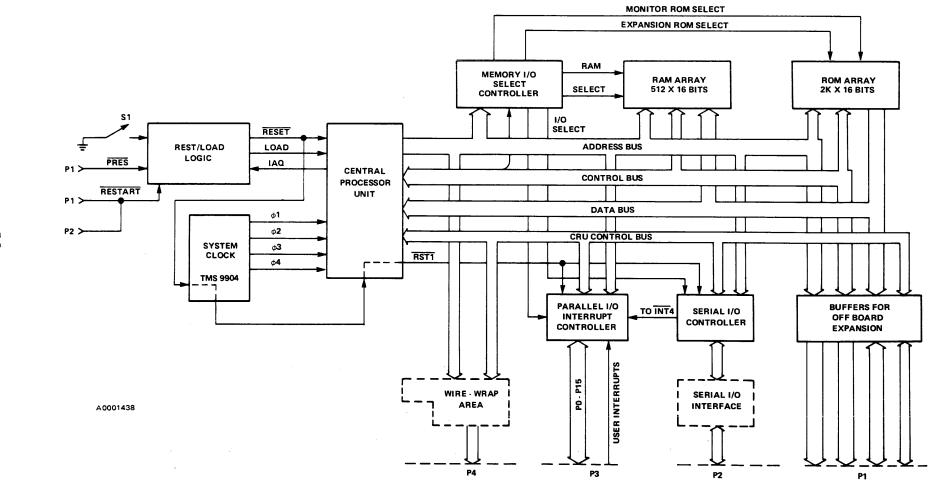

| Figure 5-1  | TM 990/100M Block Diagram                                        | 5-2    |

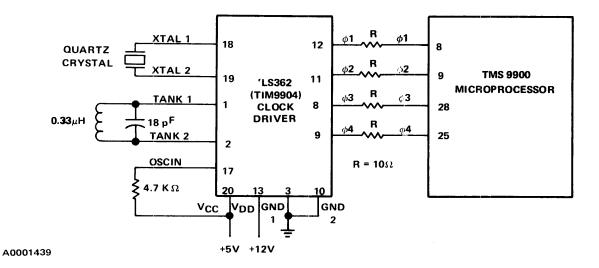

| Figure 5-2  | Crystal-Controlled Operation                                     |        |

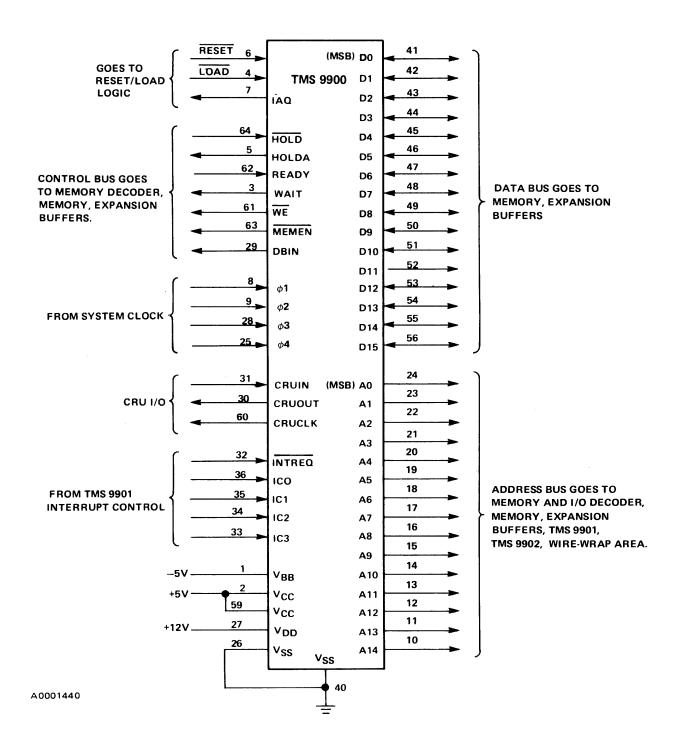

| Figure 5-3  | TMS 9900 Signals                                                 |        |

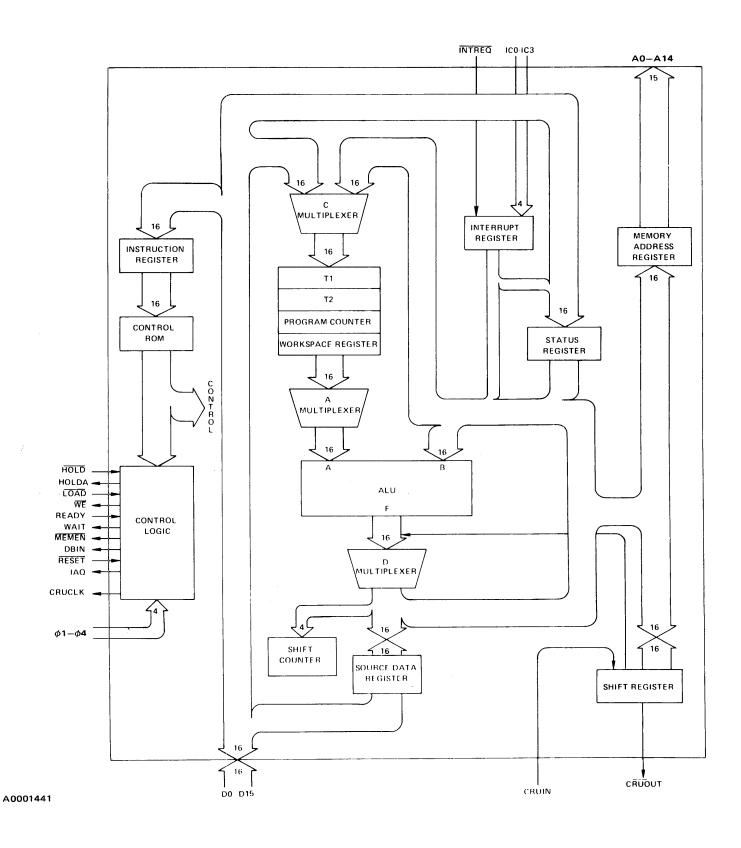

| Figure 5-4  | TMS 9900 Data and Address Flow                                   |        |

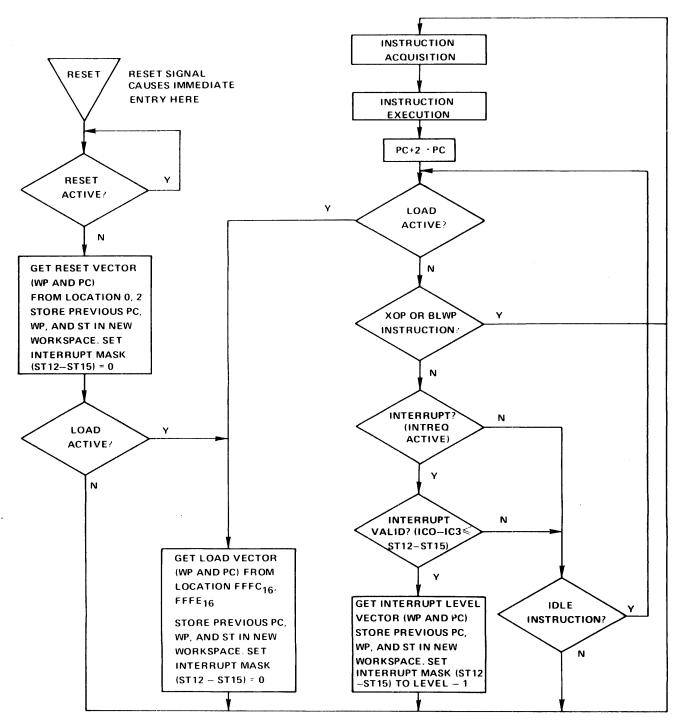

| Figure 5-4  | TMS 9900 CPU Flow Chart                                          |        |

| -           |                                                                  |        |

| Figure 5-6  | External Instruction Decode Logic on TMS 9902                    |        |

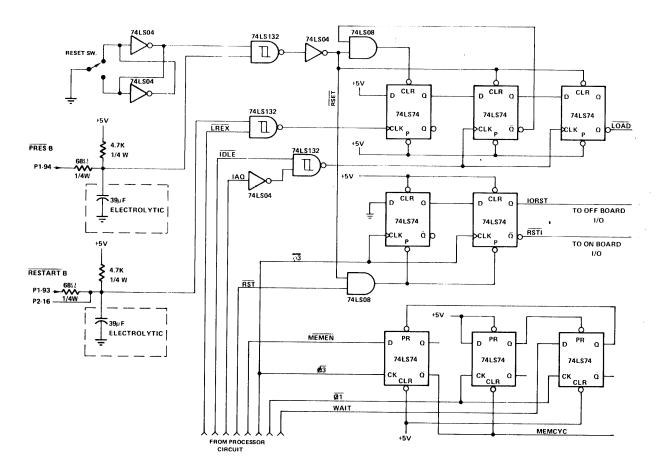

| Figure 5-7  | RESET and LOAD Logic                                             |        |

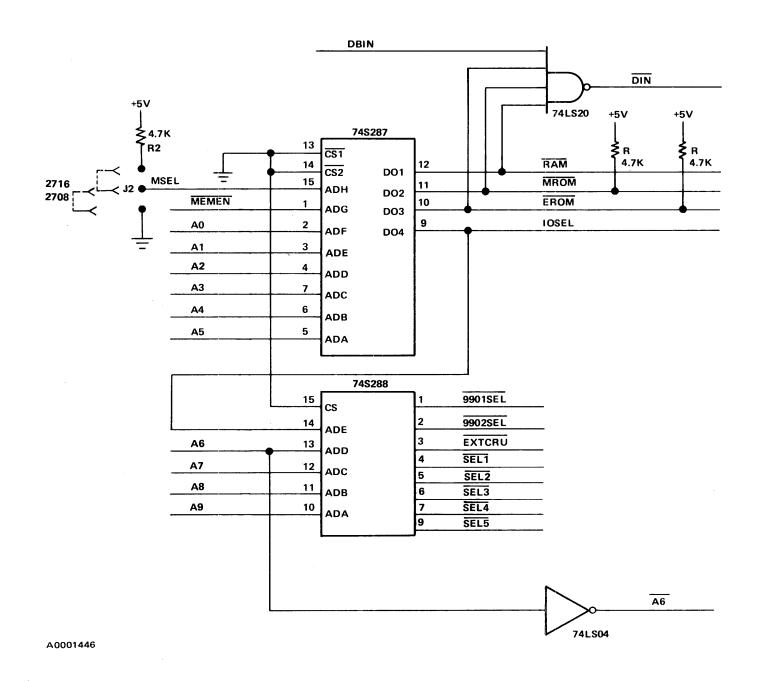

| Figure 5-8  | Memory I/O Decoder                                               |        |

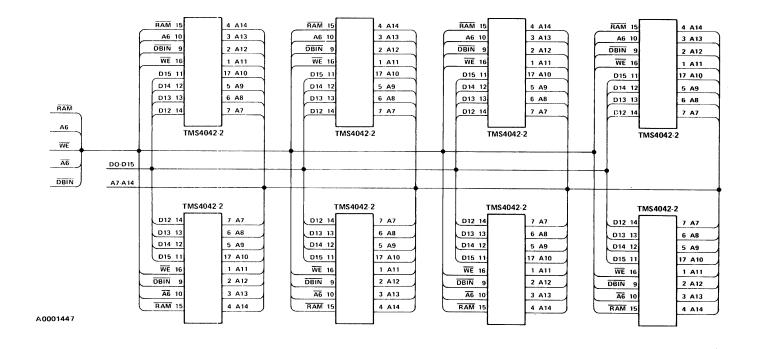

| Figure 5-9  | Random Access Memory                                             |        |

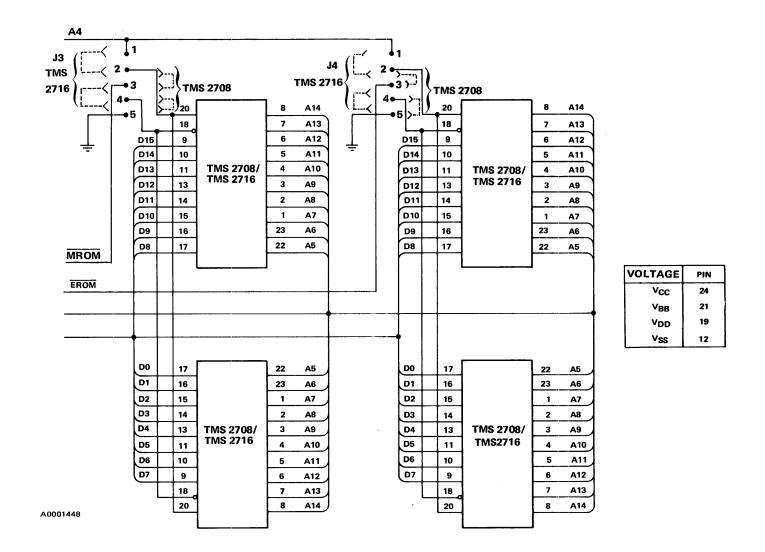

| Figure 5-10 | Read Only Memory                                                 |        |

| Figure 5-11 | Buffering of Control Signals to Connector P1                     |        |

| Figure 5-12 | Buffering of Address and Data Signals to Connector P1            | . 5-13 |

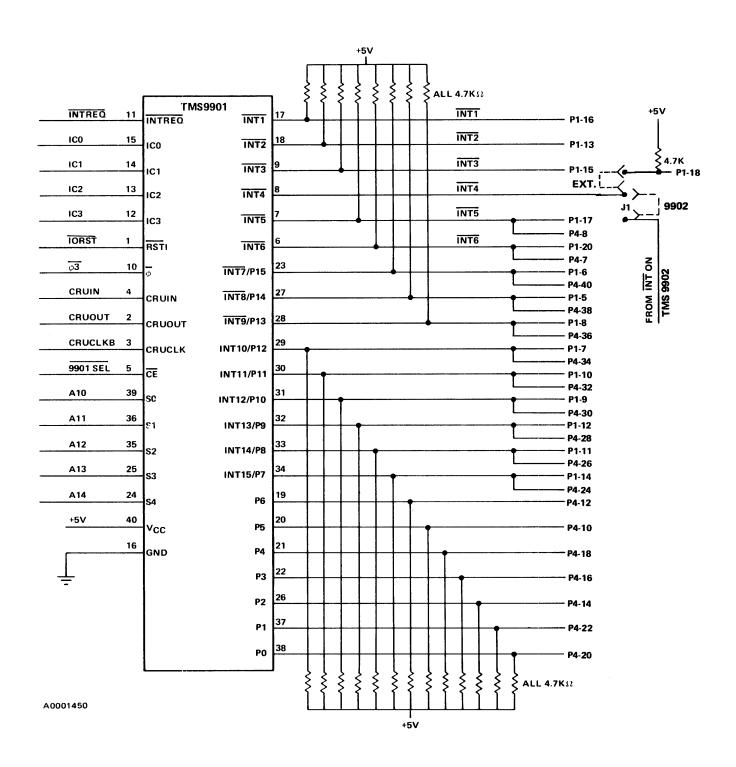

| Figure 5-13 | TMS 9901 External Logic                                          | . 5-14 |

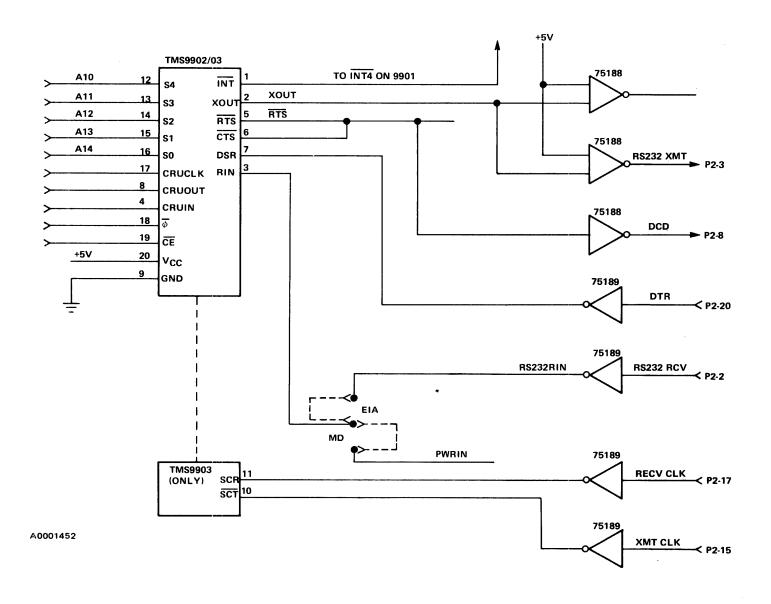

| Figure 5-14 | TMS 9902 External Logic                                          | . 5-16 |

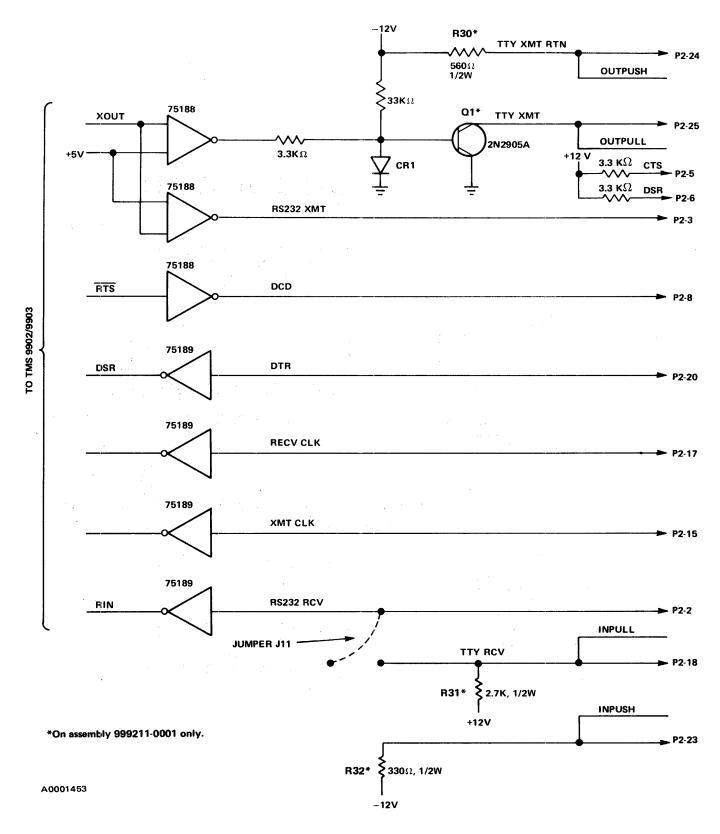

| Figure 5-15 | Serial I/O Interface                                             | . 5-17 |

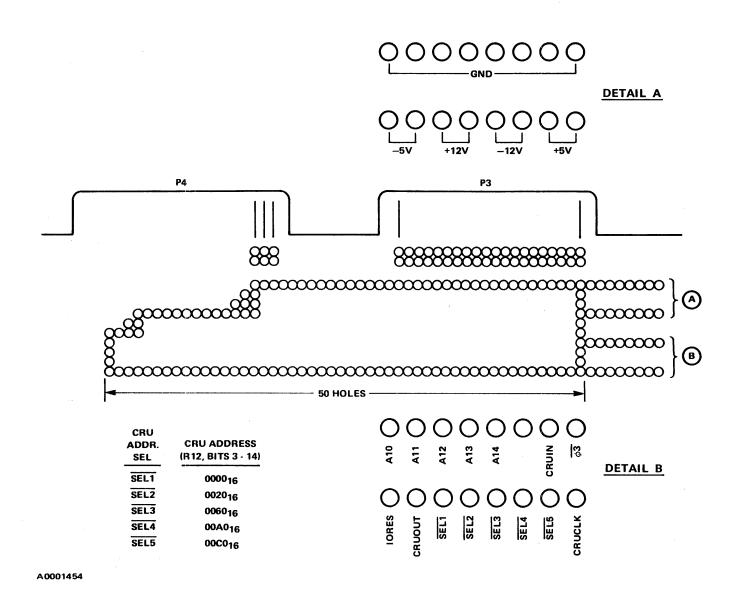

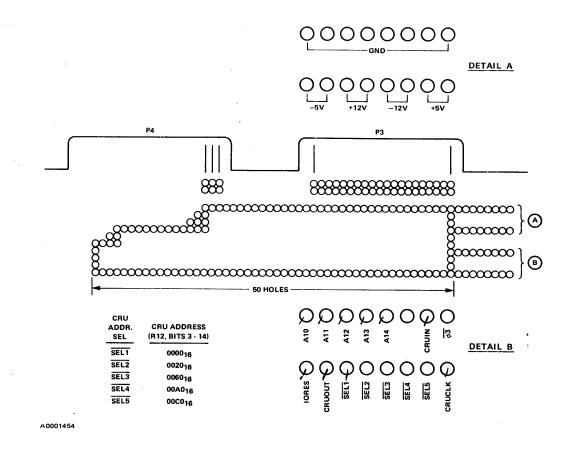

| Figure 5-16 | Signals at Wire-Wrap Area                                        | . 5-18 |

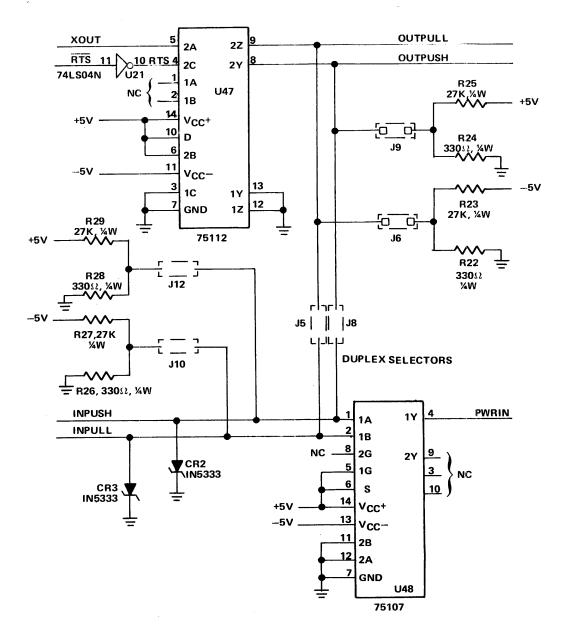

| Figure 5-17 | Multi-Drop Interface                                             |        |

| J           |                                                                  |        |

| Figure 6-1  | Devices Used in Various Applications                             | 6-2    |

| Figure 6-2  | Signals at Wire-Wrap Area                                        |        |

| Figure 6-3  | On-Board TMS 9901 Wiring                                         |        |

| Figure 6-4  | Parallel I/O Port                                                |        |

| Figure 6-5  | Off-Board Expansion of RAM                                       |        |

| Figure 6-6  | Circuitry to Add TMS 9901 Off-Board                              |        |

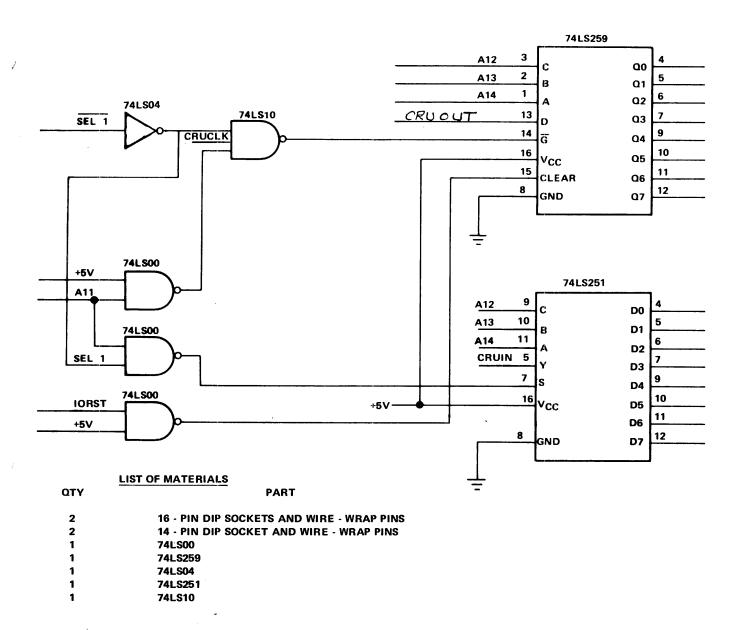

| Figure 6-7  | Four Interrupt-Causing Conditions at TMS 9902                    |        |

| rigure 0-7  | Tour interrupt-causing conditions at 1860 5502                   |        |

| Figure 7-1  | Memory Placement On Board                                        | 7-2    |

| Figure 7-1  | Jumpers and Capacitors Used for Option Selection                 |        |

| -           | Memory Expansion Maps                                            |        |

| Figure 7-3  |                                                                  |        |

| Figure 7-4  | Line-By-Line Assembler Output                                    |        |

| Figure 7-5  | TM 990/301 Microterminal                                         |        |

| Figure 7-6  | OEM Chassis                                                      |        |

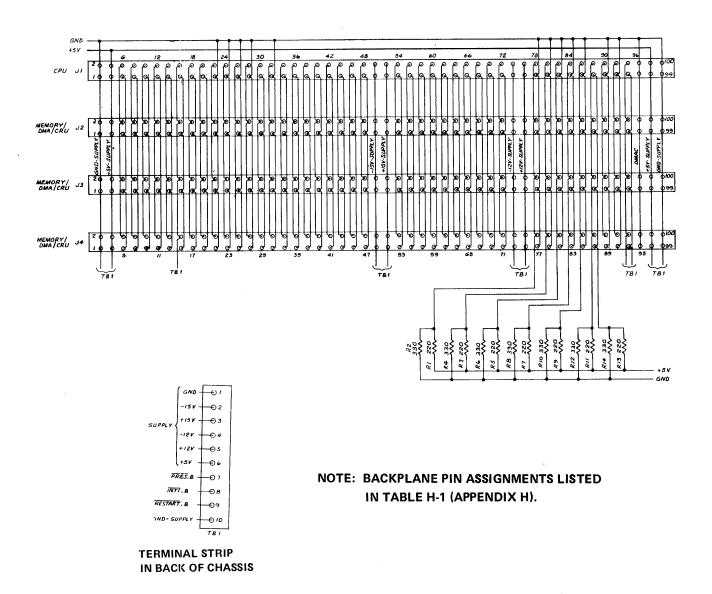

| Figure 7-7  | OEM Chassis Backplane Schematic                                  | . 7-10 |

|             |                                                                  |        |

| Figure A-1  | Teletypewriter Terminal Strip Connections                        |        |

| Figure A-2  | Teletypewriter Resistor Connection                               | . A-3  |

|             |                                                                  |        |

| Figure B-1  | EIA RS-232-C Cabling                                             | . B-1  |

# LIST OF ILLUSTRATIONS (Concluded)

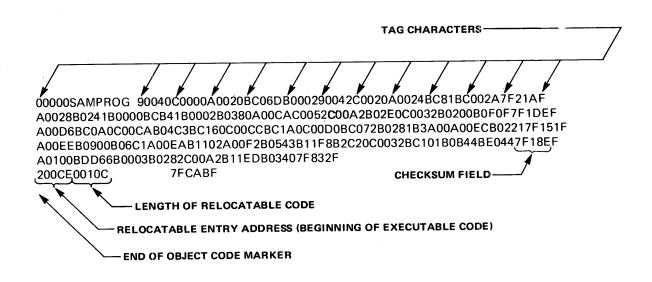

| Figure G-1<br>Figure G-2 | Object Code Example                                |

|--------------------------|----------------------------------------------------|

| Figure I-1               |                                                    |

| Figure 1-1               | TM 990/301 Microterminal                           |

|                          | LIST OF TABLES                                     |

|                          | LIST OF TABLES                                     |

| Table 3-1                | TIBUG Commands                                     |

| Table 3-2                | Command Syntax Conventions                         |

| Table 3-3                | User Accessible Utilities                          |

| Table 3-4                | TIBUG Error Messages                               |

| Table 4-1                | Status Bits Affected by Instructions               |

| Table 4-2                | Instruction Description Terms                      |

| Table 4-3                | Instruction Set, Alphabetical Index                |

| Table 4-4                | Instruction Set, Numerical Index                   |

| Table 4-5                | CRU Addressing Map                                 |

| Table 4-6                | Comparison of Jumps, Branches, XOP's               |

| Table 5-1                | I/O Device Select Lines                            |

| Table 6-1                | I/O Pins at Wire-Wrap Area                         |

| Table 6-2                | List of Materials for Adding RAM                   |

| Table 7-1                | Jumpers and Capacitors Used With Options           |

| Table C-1                | ASCII Control Codes                                |

| Table C-2                | ASCII Character Code                               |

| Table D-1                | Hexadecimal/Decimal Conversion Chart               |

| Table D-2                | Binary, Decimal, and Hexadecimal Equivalents       |

| Table G-1                | Object Output Tags Supplied by Assemblers          |

| Table H-1                | Chassis Interface Connector (P1) Signal Assignment |

| Table H-2                | Serial I/O Interface (P2) Pin Assignments          |

| Table H-3                | Parallel I/O Interface (P4) Signal Assignments     |

| Table I-1                | EIA Cable Signals                                  |

#### **SECTION 1**

#### INTRODUCTION

## 1.1 GENERAL

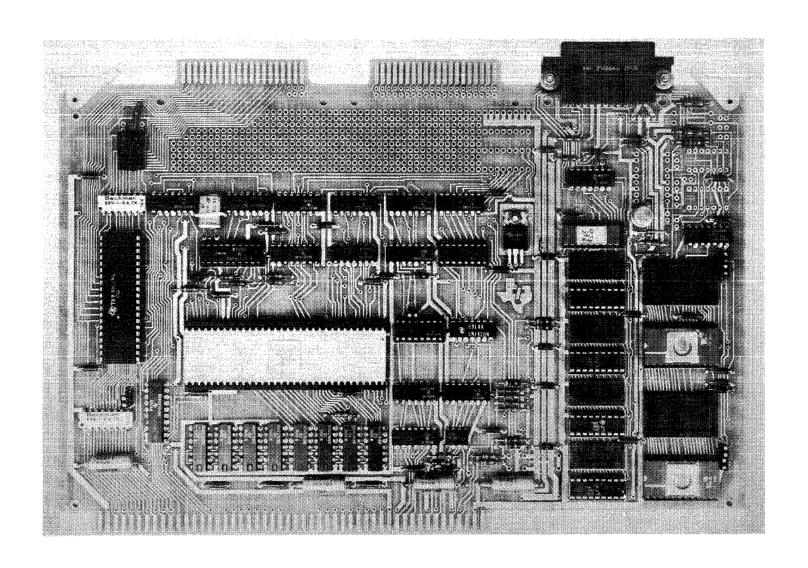

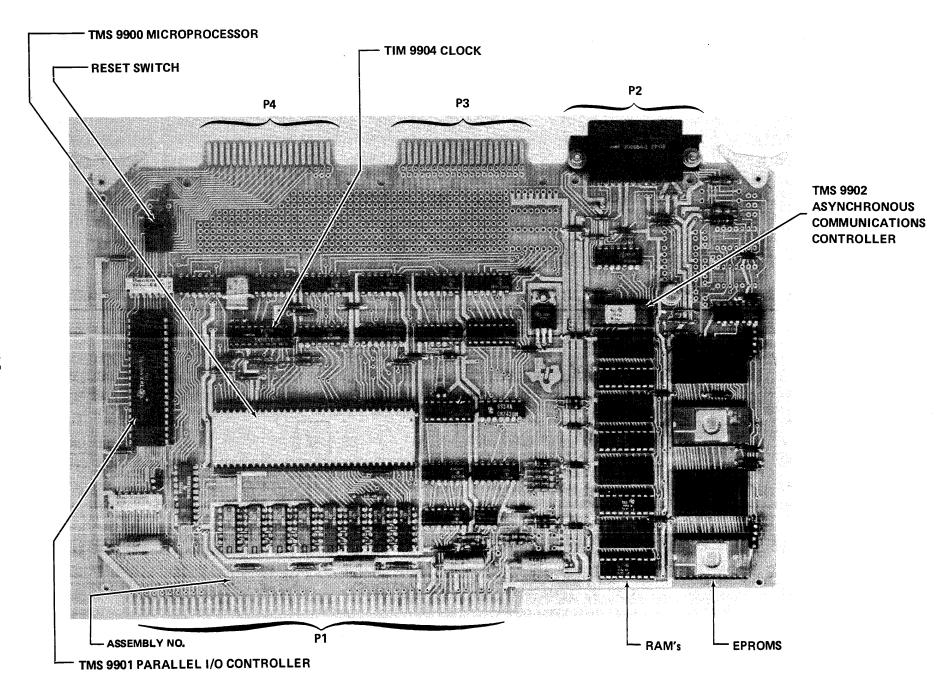

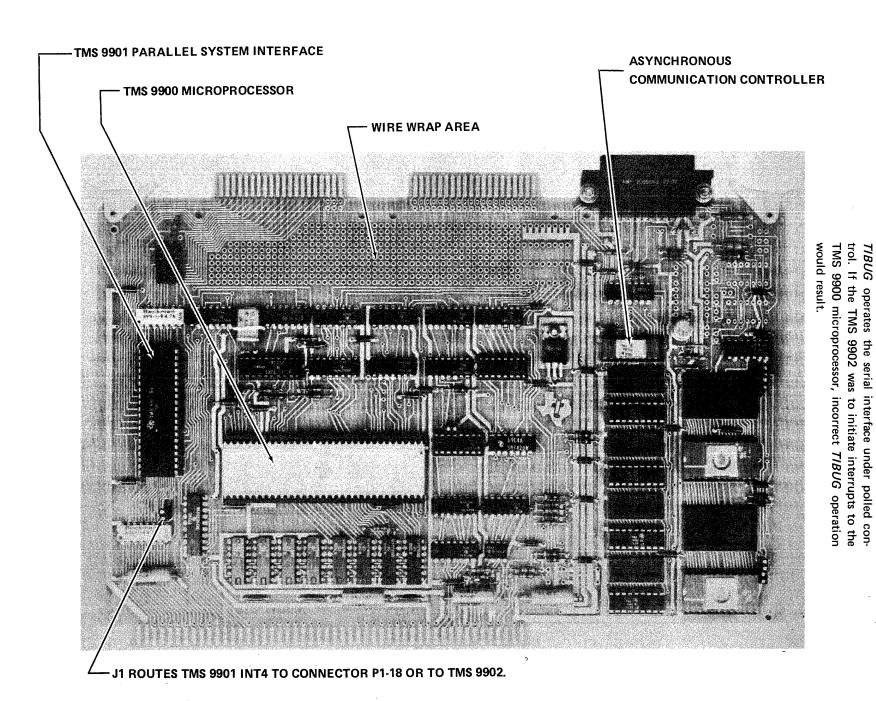

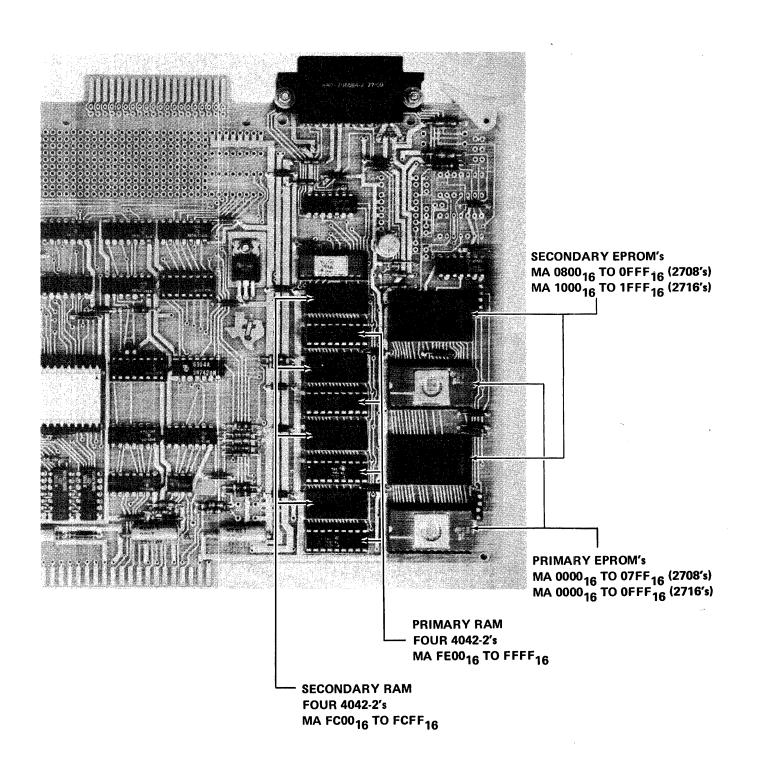

The Texas Instruments TM 990/100M is a self-contained microcomputer on a single printed-circuit board. The board's component side is shown in Figure 1-1. It contains features found on computer systems of much larger size including a Central Processing Unit (CPU) with hardware multiply and divide, programmable serial and parallel I/O lines, external interrupts, and a monitor to assist the programmer in program development and execution. Other features include (see Figure 1-2):

- TMS 9900 microprocessor based system: software is compatible with other members of the 990 family.

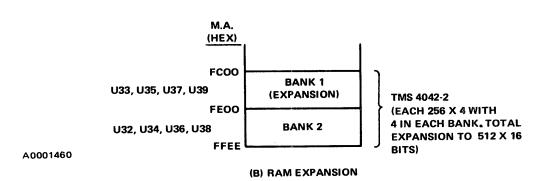

- 256 x 16 bits of TMS 4042-2 random-access memory (RAM) expandable on board to 512 x 16 bits.

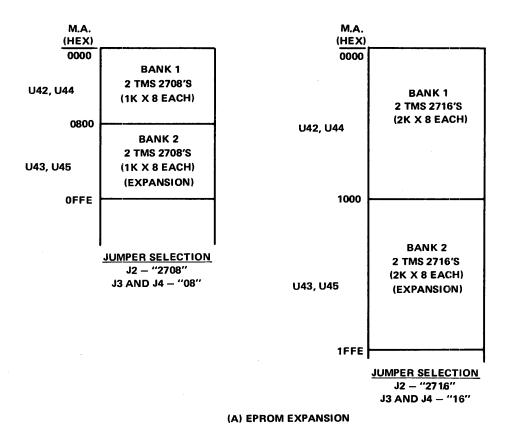

- 1K x 16 bits of TMS 2708 erasable programmable read-only memory (EPROM) expandable on board to 2K x 16 bits. Simple jumper modifications allow substitution of large TMS 2716 EPROM's (16K bits each) for the smaller TMS 2708's (8K bits). Four TMS 2716's allow EPROM expansion to 4K x 16 bits.

#### NOTE

Three board configurations are available. The characteristics of each are explained in paragraph 1.4.

- Buffered address, data, and control lines for off-board memory and I/O expansion.

- 3 MHz crystal-controlled clock.

- Interfaces to 20 mA current loop or RS-232-C terminals or to twisted-pair multidrop interface (see paragraph 1.4).

- Two programmable interval timers.

- User wire-wrap area surrounded by signal access pins; area adjacent to spare onboard 40-pin connector (P3).

- PROM memory decoders allow easy reassignment of memory map configuration.

## 1.2 MANUAL ORGANIZATION

Section 1 covers board specifications and characteristics. A glossary in paragraph 1.5 explains terms used throughout the manual.

Section 2 of this manual shows how to install, power up, and operate the TM 990/100 microcomputer with the addition of the following:

Power supply

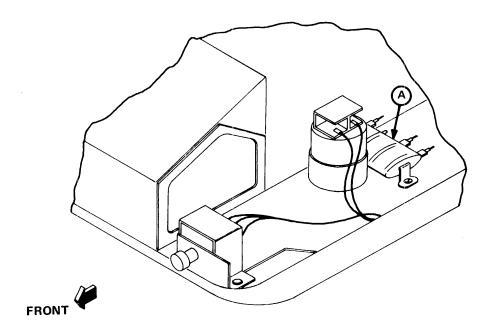

FIGURE 1-1. TM 990/100M MICROCOMPUTER

FIGURE 1-2. PRINCIPAL TM 990/100M COMPONENTS

- Data terminal (properly wired and connected)

- Connecting cables

Section 3 explains how you can communicate with the TM 990/100M using the *TIBUG* monitor (on board 999211-0001 only). This versatile monitor, complete with supervisor calls and operator communication commands facilitates the development and execution of software. Section 4 covers programming procedures including the instruction set, interrupts, extended operations (XOPs), context switching, and I/O programming.

Section 5 covers theory of operation with paragraphs keyed to schematics of specific areas of the TM 990/100M board. Section 6 contains application considerations, and Section 7 covers options including a microterminal and a line-by-line (no-label) assembler.

#### 1.3 GENERAL SPECIFICATIONS

Power Consumption:

|                               | +5 <b>V</b> | +12 V | −12 V |

|-------------------------------|-------------|-------|-------|

| 256 words RAM, 1K words EPROM | 1.2 A       | 0.2 A | 0.1 A |

| 256 words RAM, 2K words EPROM | 1.2 A       | 0.2 A | 0.1 A |

| 512 words RAM, 1K words EPROM | 1.4 A       | 0.2 A | 0.1 A |

Clock rate: 3 MHz

Baud Rates (set by TIBUG monitor):

110 baud, 300 baud, 1200 baud, 2400 baud

Memory Size:

RAM (TMS 4042-2's), 256 x 16 bits expandable on-board to 512 x 16 bits

EPROM (TMS 2708's), 1K x 16 bits expandable on-board to 2K x 16 bits

Optional EPROM (TMS 2716's), 2K x 16 bits expandable to 4K x 16 bits

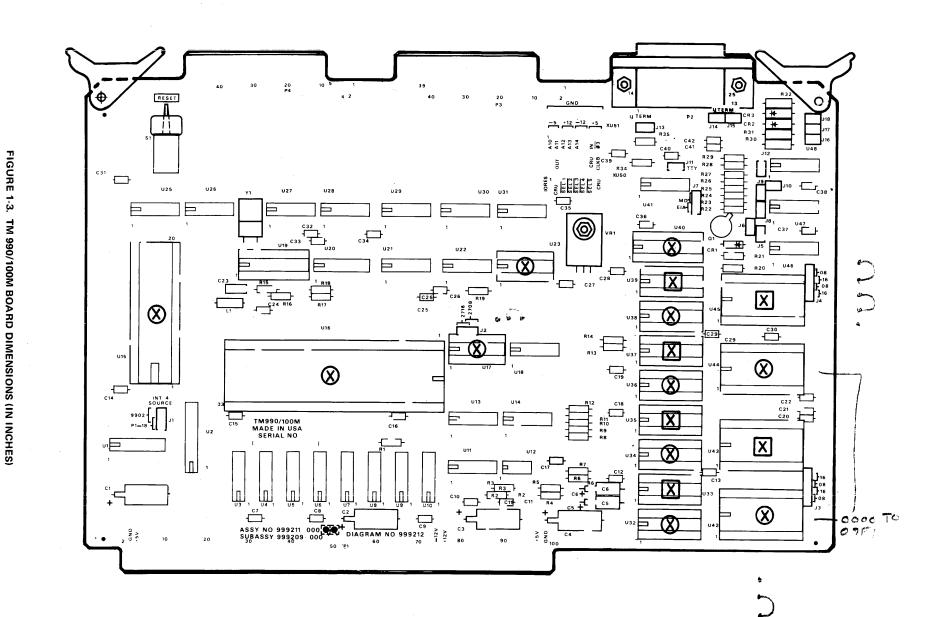

Board Dimensions: See Figure 1-3.

## 1.4 BOARD CHARACTERISTICS

Different models of the TMS 990/100M microcomputer and identified by different assembly numbers. This number is in the lower left as shown in Figure 1-2. The different aspects of these boards as shipped from the factory are listed in Table 1-1.

## 1.5 GLOSSARY

The following are definitions of terms used with the TM 990/100M. Applicable areas in this manual are in parentheses.

Absolute Address: The actual memory address in quantity of bytes. Memory addressing is usually represented in hexadecimal from 0000<sub>16</sub> to FFFF<sub>16</sub> for the TM 990/100M.

Alphanumeric Character: Letters, numbers, and associated symbols.

TABLE 1-1. BOARD ASSEMBLY CHARACTERISTICS

| ASSEMBLY NO. | I/O INTERFACE TYPES            | EPROM*          | RAM              |

|--------------|--------------------------------|-----------------|------------------|

| 999211-0001  | RS-232-C (EIA) or Current Loop | 1K x 16 bits**  | 256 × 16 bits**  |

| 999211-0002  | Multidrop or RS-232-C only     | 1K x 16 bits**  | 256 × 16 bits**  |

| 999211-0003  | Multidrop or RS-232-C only     | 2K x 16 bits*** | 512 × 16 bits*** |

<sup>\*</sup>Assembly 999211-0001 EPROM's contain TIBUG monitor; assemblies 999211-0002 and -0003 EPROM's are not programmed.

ASCII Code: A seven-bit code used to represent alphanumberic characters and control (Appendix C).

Assembler: Program that interprets assembly language source statements into object code.

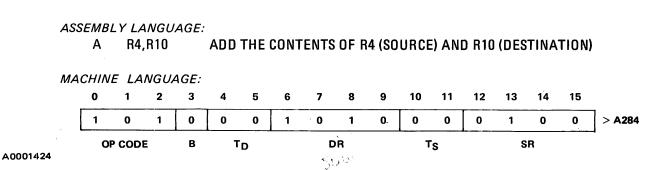

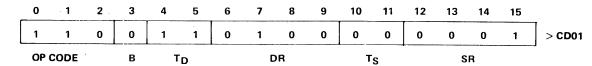

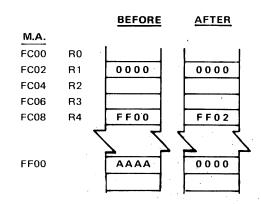

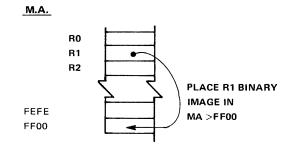

Assembly Language: Mnemonics which can be interpreted by an assembler and translated into an object program (paragraph 4.6).

Bit: The smallest part of a word; it has a value of either a 1 or 0.

Breakpoint: Memory address where a program is intentionally halted. This is a program debugging tool.

Byte: Eight bits or half a word.

Carry: A carry occurs when the most-significant bit is carried out in an arithmetic operation (i.e., resultant cannot be contained in only 16 bits), (paragraph 4.3.3.4).

Central Processing Unit (CPU): The "heart" of the computer: responsibilities include instruction access and interpretation, arithmetic functions, I/O memory access. The TMS 9900 is the CPU of the TM 990/100M.

Chad: Dot-like paper particles resulting from the punching of paper tape.

Command Scanner: A given set of instructions in the *TIBUG* monitor which takes the user's input from the terminal and searches a table for the proper code to execute.

Context Switch: Change in program execution environment, includes new program counter (PC) value and new register file.

CRU (Communications Register Unit): The TMS 9900's general purpose, command-driven input/output interface. The CRU provides up to 4096 directly addressable input and output bits (paragraph 4.8).

Effective Address: Memory address resulting from interpretation of an instruction, required for execution of that instruction.

EPROM: See Read Only Memory.

Hexadecimal: Numerical notation in the base 16 (Appendix D).

<sup>\*\*</sup>Two 2708 EPROM's and two 4042 RAM's.

<sup>\*\*\*</sup>Four 2708 EPROM's and four 4042 RAM's.

- Immediate Addressing: An immediate or absolute value (16-bits) is part of the instruction (second word of instruction).

- Indexed Addressing: The effective address is the sum of the contents of an index register and an absolute (or symbolic) address (paragraph 4.5.3.5).

- Indirect Addressing: The effective address is the contents of a register (paragraph 4.5.3.2).

- Interrupt: Context switch in which new program counter (PC) and workspace pointer (WP) values are obtained from one of 16 interrupt traps in memory addresses 0000<sub>16</sub> to 003E<sub>16</sub> (paragraph 4.9).

- I/O: The input/output lines are the signals which connect an external device to the data lines of the TMS 9990.

- Least Significant Bit (LSB): Bit having the smallest value (smallest power of base 2); represented by the right-most bit.

- Link: The process by which two or more object code modules are combined into one, with cross-referenced label address locations being resolved.

- Loader: Program that places one or more absolute or relocatable object programs into memory (Appendix G).

- Machine Language: Binary code that can be interpreted by the CPU (Table 4-4).

- Monitor: A program that assists in the real-time aspects of program execution such as operator command interpretation and supervisor call execution. Sometimes called supervisor (Section 3).

- Most Significant Bit (MSB): Bit having the most value; the left-most bit representing the highest power of base 2. This bit is used to show sign with a 1 indicating negative and a 0 indicating positive.

- Object Program: The hexadecimal interpretations of source code output by an assembler program. This is the code executed when loaded into memory.

- One's Complement: Binary representation of a number in which the negative of the number is the complement or inverse of the positive number (all ones become zeroes, vice versa). The MSB is one for negative numbers and zero for positive. Two representations exist for zero: all ones or all zeroes.

- Op Code: Binary operation code interpreted by the CPU to execute the instruction (paragraph 4.5.1).

- Overflow: An overflow occurs when the result of an arithmetic operation cannot be represented in two's complement (i.e., in 15 bits plus sign bit), (paragraph 4.3.3.5).

- Parity: Means for checking validity of a series of bits, usually a byte. Odd parity means an odd number of one bits; even parity means an even number of one bits. A parity bit is set to make all bytes conform to the selected parity. If the parity is not as anticipated, an error flag can be set by software. The parity jump instruction can be used to determine parity (paragraph 4.3.3.6).

- Program Counter (PC): Hardware register that points to the next instruction to be executed or next word to be interpreted (paragraph 4.3.1).

PROM: See Read Only Memory.

Random Access Memory (RAM): Memory that can be written to as well as read from (vs. ROM).

Read Only Memory (ROM): Memory that can only be read from (can't change contents). Some can be programmed (PROM) using a PROM burner. Some PROM's can be erased (EPROM's) by exposure to ultraviolet light.

Source Program: Programs written in menmonics that can be translated into machine language (by an assembler).

Status Register (ST): Hardware register that reflects the outcome of a previous instruction and the current interrupt mask (paragraph 4.3.3).

Supervisor: See Monitor

Utilities: A unique set of instructions used by different parts of the program to perform the same function. In the case of *TIBUG*, the utilities are the I/O XOP's (paragraph 3.3).

Word: Sixteen bits or two bytes.

Workspace Register File: Sixteen words, designated registers 0 to 15, located in RAM for use by the executing program (paragraph 4.4).

Workspace Pointer (WP): Hardware register that contains the memory address of the beginning (register 0) of the workspace register file (paragraph 4.3.2).

#### 1.6 APPLICABLE DOCUMENTS

The following is a list of documents that provide supplementary information for the TM 990/100M user.

- TMS 9900 Microprocessor Data Manual

- TMS 9901 Programmable Systems Interface Data Manual

- TMS 9902 Asynchronous Communication Controller (Data Manual)

- Model 990 Computer, TMS 9900 Microprocessor Assembly Language Programmer's Guide (P/N 943441-9701)

- TM 990/301 Microterminal

- TM 990/401 TIBUG Monitor Listing

- TM 990/402 Line-By-Line Assembler

- TM 990/402L Line-By-Line Assembler Listing

#### **SECTION 2**

#### **INSTALLATION AND OPERATION**

## 2.1 GENERAL

This section explains procedures for unpacking and setting up the TM 990/100M board for operation.

## 2.2 REQUIRED EQUIPMENT

- (1) Volt-ohmmeter

- (2) Soldering iron, electrical solder

- (3) 24 AWG insulated stranded wire

- (4) 18 AWG insulated stranded wire

- (5) Connectors

- 100-pin, 0.125 in. C-C, wire-wrap PCB edge connector such as:

- TI H321150

- Amphenol 225-804-50

- Viking 3VH50/9N05

- Elco 00-6064-100-061-001

- 40-pin, 0.1 in. C-C, wire-wrap PCB edge connector such as:

- TI H311120

- Viking 3VH20/IJND5

- 25-pin RS-232 style (plug)

- ITT DB25P

- TRW CINCH DB25P

- (6) Power Supplies

| Voltage | Reg. | Current |  |

|---------|------|---------|--|

| +5 V    | ±3%  | 1.3 A   |  |

| −12 V   | ±3%  | 0.2 A   |  |

| +12 V   | ±3%  | 0.1 A   |  |

- (7) Terminal such as:

- Texas Instruments 743 KSR or 733 KSR/ASR (see Appendix B)

- Teletype Model 3320/5JE (see Appendix A). This current-loop terminal is useable with board assembly 999211-0001 only

- RS-232-C compatible terminal (see Appendix B).

#### 2.3 UNPACKING

Take the TM 990/100M board from its carton and remove the protective wrapping.

Check the board for any abnormalities that could have occurred in shipping. Report any discrepancies to your supplier.

## 2.4 POWER AND TERMINAL HOOKUP

These procedures assume that user has the following configuration:

- TM 990/100M board with two TMS 2708 erasable, programmable read-only memories (EPROM's).

- Texas Instruments Model 743 KSR terminal.

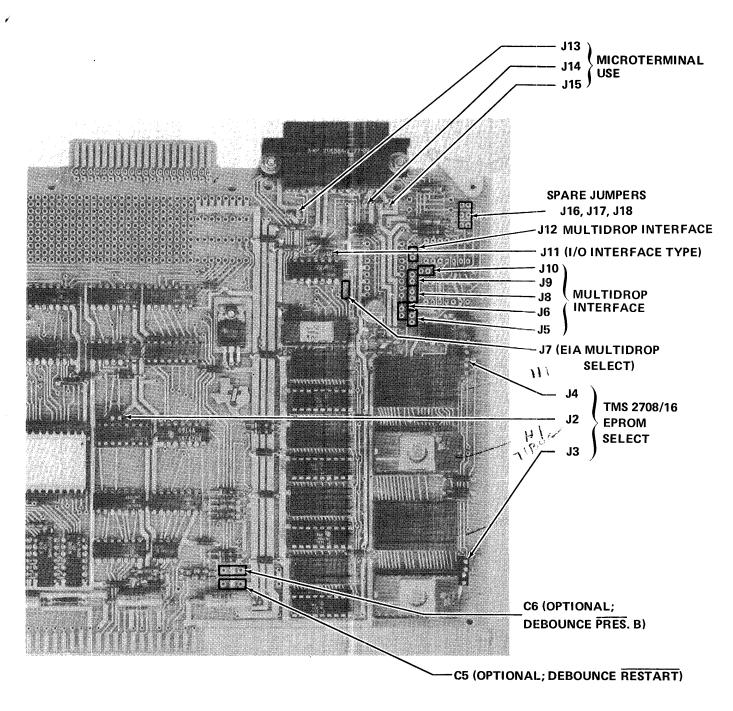

It is also assumed that jumper configuration is as shipped by the factory (J1, J2, J3, and J4 installed). See Figure 7-2.

For other memory configurations, see paragraph 7.2 for applicable jumper connections.

For other terminals, contact the manufacturer for correct wiring. Hookup to a Teletype model 3320/SJE is explained in Appendix A. Hookup for other RS-232-C compatible terminals is explained in Appendix B.

#### CAUTION

Be very cautious to avoid applying incorrect voltage levels to the TM 990/100M. Texas Instruments assumes no responsibility for damage caused by improper wiring or voltage application by the user.

## 2.4.1 POWER SUPPLY HOOKUP

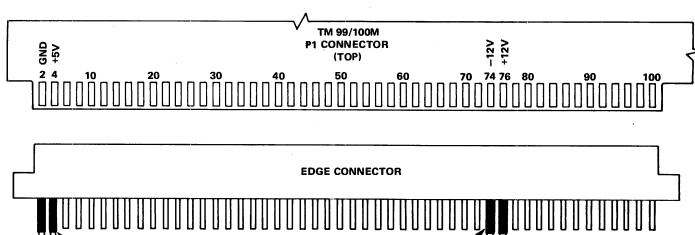

Figure 2-1 shows how to connect voltage to the TM 990/100M through connector P1. Be careful to use the correct pins as numbered on the board; these pin numbers may not correspond to the numbers on the particular edge connector used.

The table in Figure 2-1 shows suggested color coding for the power supply plugs. To prevent incorrect connection, label the top side of the edge connector "TOP" and the bottom "TURN OVER."

## 2.4.2 TERMINAL HOOKUP

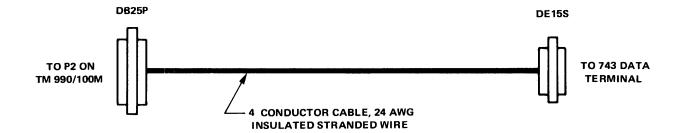

Figure 2-2 shows how to connect the TM 990/100M to the 743 KSR terminal through connector P2. A DEI5S connector attaches to the terminal; a DB25P connector attaches to P2 on the board. Point-to-point connections between the connectors are shown in the table.

Because this is an RS-232-C type terminal, make sure that jumper J11 is removed and that jumper J7 is in the EIA position (Figure 7-2).

## 2.5 OPERATION

(1) Verify that all wiring has been correctly connected.

| لــا     | EDGE CONNECTOR                                                   |

|----------|------------------------------------------------------------------|

|          |                                                                  |

|          | SHRINK SLEEVING —                                                |

| -        | 18 AWG INSULATED STRANDED WIRE                                   |

| لے       |                                                                  |

| ∏<br>∏GN | BANANA PLUGS  SUGGEST COLOR CODING THESE AS PER TABLE  -12V +12V |

|          |                                                                  |

| VOLTAGE | P1 PIN* | SUGGESTED PLUG COLORS |

|---------|---------|-----------------------|

| +5V     | 3, 4    | RED                   |

| +12V    | 75, 76  | BLUE                  |

| -12V    | 73, 74  | GREEN                 |

| GND     | 1, 2    | BLACK                 |

|         |         |                       |

<sup>\*</sup>ON BOARD, ODD-NUMBERED PADS ARE DIRECTLY BENEATH EVEN-NUMBERED PADS.

A0001417

FIGURE 2-1. POWER SUPPLY HOOKUP

#### **CAUTION**

Before connecting the power supply to P1, use a volt-ohmmeter to verify that correct voltages are present as shown in Figure 2-2.

- (2) Set the 743 KSR data terminal switches to the following:

- LOW SPEED switch to high speed (30 characters per second).

- HALF DUP switch to full duplex.

- ON LINE switch to ON LINE.

| CONNECTIONS                      |   |      |  |  |  |

|----------------------------------|---|------|--|--|--|

| PIN ON DE15S PIN ON DB25P SIGNAL |   |      |  |  |  |

| 13                               | 2 | XMIT |  |  |  |

| 12                               | 3 | RECV |  |  |  |

| 11                               | 8 | DCD  |  |  |  |

| 1                                | 7 | GND  |  |  |  |

A0001418

FIGURE 2-2. 743 KSR TERMINAL HOOKUP

- (3) Apply power to board and data terminal.

- (4) Press the RESET switch on the board (see Figure 1-2).

- (5) Press the "A" key on the terminal.

- (6) The *TIBUG* monitor (assembly 999211-0001 only) will be called up and print a message on the terminal. Following the message, a question mark will be printed on a new line. This is a request to input a command to the *TIBUG* command scanner. Commands are explained in detail in Section 3 and assembly language is presented in Section 4.

#### NOTE

If control is lost during operation, return control back to monitor by repeating steps (4) and (5).

## 2.6 SAMPLE PROGRAMS

## 2.6.1 SAMPLE PROGRAM 1

The following is a sample program you can input using the *TIBUG* commands M (paragraph 3.2.8), R (paragraph 3.2.9), and E (paragraph 3.2.4). (*TIBUG* is on assembly 999211-0001 only).

(1) Enter the M command with a hexadecimal address of FD00.

(2) Enter the following values into memory beginning at hexadecimal address FD00 by using the space bar with the M command as described in paragraph 3.2.8.

| LOCATION | ENTER<br>VALUE | ASSEMBLY<br>LANGUAGE<br>MNEMONICS |  |  |  |  |  |  |

|----------|----------------|-----------------------------------|--|--|--|--|--|--|

| FE00     | 2FA0           | XOP @ > FE08, 14                  |  |  |  |  |  |  |

| FE02     | FE08           |                                   |  |  |  |  |  |  |

| FE04     | 0420           | BLWP@>FFFC                        |  |  |  |  |  |  |

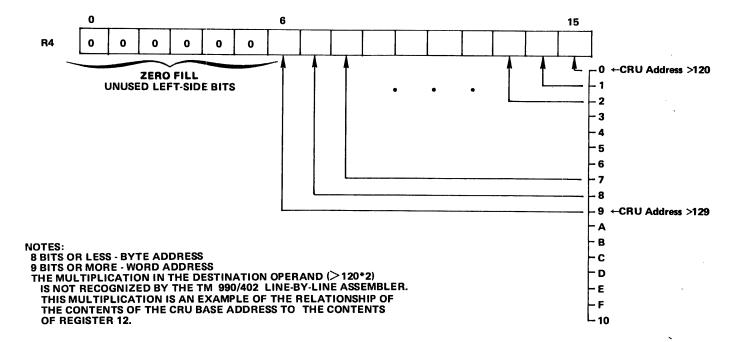

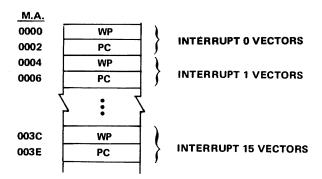

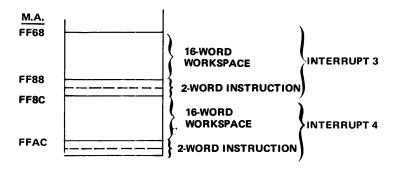

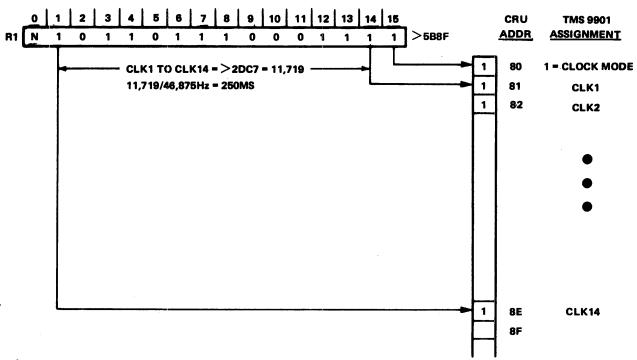

| FE06     | FFFC           |                                   |  |  |  |  |  |  |