## **TVP4010**

## **3D Graphics Processor**

# Data Manual

Preliminary Mixed-Signal Products

Data Manual

TVP4010

3D Graphics Processor

1996

# TVP4010 Data Manual

**3D Graphics Processor**

SLAS155 January 1997

## **TVP4010 Data Manual**

3Dlabs is the worldwide trading name of 3Dlabs Inc. Ltd. 3Dlabs and GLINT are registered trademarks of 3Dlabs.

OpenGL is a registered trademark of Silicon Graphics, Inc. Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation. DirectDraw, DirectX, and Direct3D are trademarks of Microsoft Corporation. AutoCAD is a registered trademark of Autodesk Inc. MicroStation is a registered trademark of Bentley Systems Inc., an affiliate of Intergraph Corporation.. RAMDAC is a trademark of Brooktree Corporation.

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

## Contents

| Se | ction                                                               | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                            |

|----|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|    |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                 |

| 1  | 1.1<br>1.2<br>1.3<br>1.4<br>1.5                                     | Features Functional Block Diagram Terminal Assignments Ordering Information Terminal Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1–2<br>1–4<br>1–5<br>1–6                                                                        |

| 2  | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | illed Description PCI Interface Graphics Core Memory Interface Video Timing Generation Auxiliary Device Support Reset Configuration Control ROM Support Address Mapping Test Mode PCI Configuration 2.10.1 PCI Configuration Region PCI Register Set 2.11.1 Vendor ID Register (CFGVendorld) 2.11.2 Device ID Register (CFGDeviceld) 2.11.3 Command Register (CFGCommand) 2.11.4 Status Register (CFGStatus) 2.11.5 Revision ID Register (CFGCacheLine) 2.11.6 Class Code Register (CFGCacheLine) 2.11.8 Latency Timer Register (CFGLatTimer) 2.11.9 Header Type Register (CFGBest) 2.11.10 BIST Register (CFGBist) 2.11.11 Base Address 0 Register (CFGBaseAddr0) 2.11.12 Base Address 1 Register (CFGBaseAddr1) 2.11.13 Base Address 2 Register (CFGBaseAddr2) 2.11.14 Base Address 3 Register (CFGBaseAddr3) 2.11.15 Base Address 4 Register (CFGBaseAddr4) 2.11.16 CardBus CIS Pointer Register (CFGCardBus) 2.11.17 Subsystem Vendor ID Register (CFGSubsystemVendorld) 2.11.18 Subsystem ID Register (CFGSubsystemId) | 2-1 2-1 2-1 2-1 2-1 2-1 2-1 2-1 2-2 2-3 2-3 2-4 2-4 2-5 2-6 2-7 2-8 2-9 2-9 2-10 2-11 2-11 2-12 |

|    |                                                                     | 2.11.19 Expansion ROM Base Address Register (CFGRomAddr)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-12                                                                                            |

|      | 2.11.20 Interrupt Line Register (CFGIntLine)                  |      |

|------|---------------------------------------------------------------|------|

|      | 2.11.21 Interrupt Pin Register (CFGIntPin)                    |      |

|      | 2.11.22 Minimum Grant Register (CFGMinGrant)                  | 2–13 |

|      | 2.11.23 Maximum Latency Register (CFGMaxLat)                  |      |

| 2.12 | Region 0 Registers                                            |      |

|      | 2.12.1 Region 0 Address Map                                   | 2–14 |

| 2.13 | Control Status Registers                                      | 2–15 |

|      | 2.13.1 Reset Status Register (ResetStatus)                    | 2–15 |

|      | 2.13.2 Interrupt Enable Register (IntEnable)                  |      |

|      | 2.13.3 Interrupt Flags Register (IntFlags)                    |      |

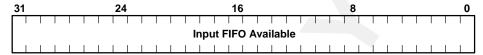

|      | 2.13.4 Input FIFO Space Register (InFIFOSpace)                |      |

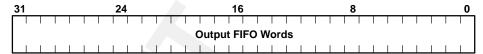

|      | 2.13.5 Output FIFO Words Register (OutFIFOWords)              | 2–18 |

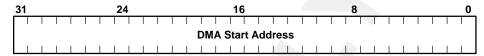

|      | 2.13.6 DMA Start Address Register (DMAAdress)                 |      |

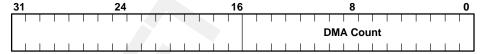

|      | 2.13.7 DMA Count Register (DMACount)                          |      |

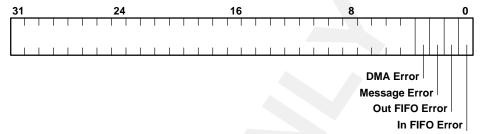

|      | 2.13.8 Error Flags Register (ErrorFlags)                      |      |

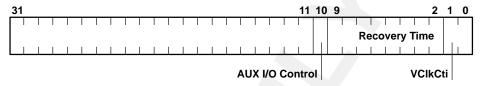

|      | 2.13.9 Video Clock Control Register (VClkCtl)                 |      |

|      | 2.13.10 Test Register (TestRegister)                          |      |

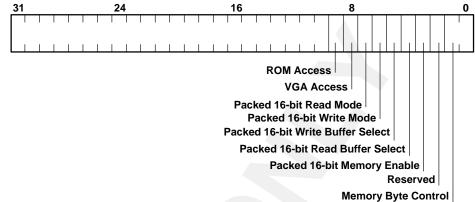

|      | 2.13.11 Aperture 1 Control Register (ApertureOne)             |      |

|      | 2.13.12 Aperture 2 Control Register (ApertureTwo)             |      |

|      | 2.13.13 DMA Control Register (DMAControl)                     |      |

|      | 2.13.14 FIFO Disconnect Register (FIFODiscon)                 |      |

|      | 2.13.15 Chip Configuration Register (ChipConfig)              |      |

| 2.14 | Memory Control Registers                                      | 2–26 |

|      | 2.14.1 Re-Boot Register (Reboot)                              |      |

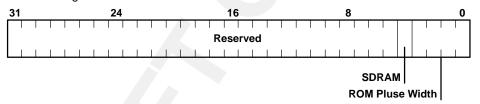

|      | 2.14.2 ROM Control Register (RomControl)                      |      |

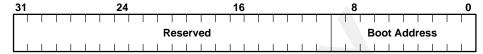

|      | 2.14.3 Boot Address Register (BootAddress)                    |      |

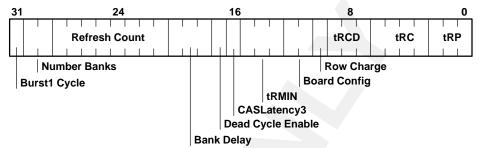

|      | 2.14.4 Memory Configuration Register (MemConfig)              |      |

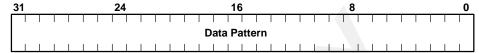

|      | 2.14.5 Bypass Write Mask Register (BypassWriteMask)           |      |

|      | 2.14.6 Framebuffer Write Mask Register (FramebufferWriteMask) |      |

| 0.45 | 2.14.7 Count Register (Count)                                 |      |

| 2.15 | Video Control Registers                                       |      |

|      | 2.15.1 Screen Base Register (ScreenBase)                      |      |

|      | 2.15.2 Screen Stride Register (ScreenStride)                  |      |

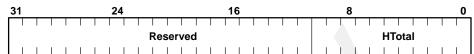

|      | 2.15.3 Horizontal Total Register (HTotal)                     |      |

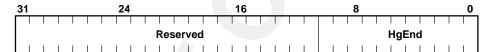

|      | 2.15.4 Horizontal Gate End Register (HgEnd)                   |      |

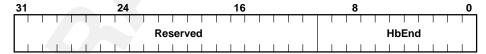

|      | 2.15.5 Horizontal Blank End Register (HbEnd)                  |      |

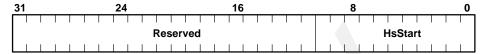

|      | 2.15.6 Horizontal Sync Start Register (HsStart)               |      |

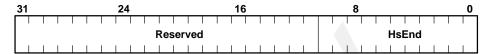

|      | 2.15.7 Horizontal Sync End Register (HsEnd)                   |      |

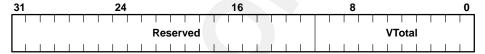

|      | 2.15.8 Vertical Total Register (VTotal)                       |      |

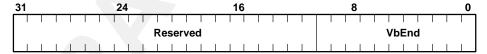

|      | 2.15.9 Vertical Blank End Register (VbEnd)                    |      |

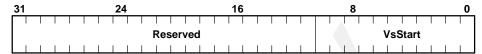

|      | 2.15.10 Vertical Sync Start Register (VsStart)                |      |

|      | 2.15.11 Vertical Sync End Register (VsEnd)                    |      |

|      | 2.15.12 Video Control Register (VideoControl)                 |      |

|      | 2.15.13 Interrupt Line Register (InterruptLine)               |      |

|      | 2.15.14 Display Data Channel Data Register (DDCData)          |      |

| 2 16 |                                                               |      |

| ∠.10 | VGA Interface                                                 | Z-31 |

|   |      | 2.16.1 VGA Memory                                                  | 2-37  |

|---|------|--------------------------------------------------------------------|-------|

|   |      | 2.16.2 VGA Registers                                               |       |

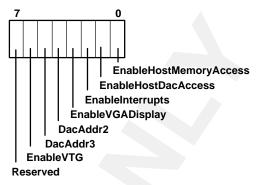

|   |      | 2.16.3 VGA Control Register (VGAControlReg)                        |       |

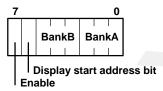

|   |      | 2.16.4 Mode 640 Register (Mode64Reg)                               |       |

|   | 2.17 | Memory System                                                      |       |

|   |      | 2.17.1 System Parameters                                           | 2-40  |

|   |      | 2.17.2 TimeRPW                                                     |       |

|   |      | 2.17.3 RowCharge                                                   |       |

|   |      | 2.17.4 TimeRCD                                                     |       |

|   |      | 2.17.5 TimeRC                                                      |       |

|   |      | 2.17.6 TimeRP                                                      |       |

|   |      | 2.17.7 CASLatency3                                                 |       |

|   |      | 2.17.8 BootAddress                                                 |       |

|   |      | 2.17.9 NumberBanks                                                 |       |

|   |      | 2.17.10 RefreshCount                                               |       |

|   |      | 2.17.11 TimeRASMin                                                 |       |

|   |      | 2.17.12 DeadCycleEnable                                            |       |

|   |      | 2.17.13 BankDelay                                                  |       |

|   |      | 2.17.14 Burst1Cycle                                                |       |

|   |      | 2.17.15 SDRAM                                                      |       |

|   | 2 18 | Recommended Parameter Values                                       |       |

|   |      | Using the Video Unit                                               |       |

|   |      | Example Timing Values                                              |       |

|   | 2.20 | 2.20.1 Timing Values for 640 x 480 16 BPP 75 Hz                    |       |

|   |      | 2.20.2 Timing Values for 800 x 600 32 BPP 75 Hz                    |       |

|   | 2 21 | Display Data Channel                                               |       |

|   |      | Auxiliary Bus                                                      |       |

|   |      | Reset Control                                                      |       |

|   |      |                                                                    |       |

| 3 | Elec | trical Characteristics                                             |       |

|   | 3.1  | Absolute Maximum Ratings Over Operating Free-Air Temperature Range | . 3–1 |

|   | 3.2  | Recommended Operating Conditions                                   |       |

|   | 3.3  | Electrical Characteristics                                         | . 3–1 |

|   |      | 3.3.1 PCI                                                          | . 3–2 |

|   |      | 3.3.2 Non-PCI                                                      | . 3–2 |

|   | 3.4  | Operating Characteristics                                          | . 3–2 |

|   | 3.5  | Timing Requirements                                                | . 3–3 |

|   |      | 3.5.1 PCI Clock Referenced Input Timing                            | . 3–4 |

|   |      | 3.5.2 PCI Clock Referenced Output Timing                           | . 3–4 |

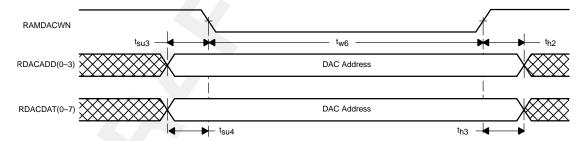

|   |      | 3.5.3 RAMDAC Timing, 33 MHz PCI Clock                              |       |

|   |      | 3.5.4 AUX Timings, 33 MHz PCI Clock                                |       |

|   |      | 3.5.5 MEMCKOUT Referenced Input Timing                             |       |

|   |      | 3.5.6 MEMCKOUT Referenced Output Timing                            |       |

|   | _    | ·                                                                  |       |

| L | Para | meter Measurement Information                                      | 4_1   |

| 5  | Application Information          | 5-1         |

|----|----------------------------------|-------------|

|    | 5.1 Video Unit                   | 5–1         |

| Ар | pendix A Thermal Characteristics | <b>A</b> –1 |

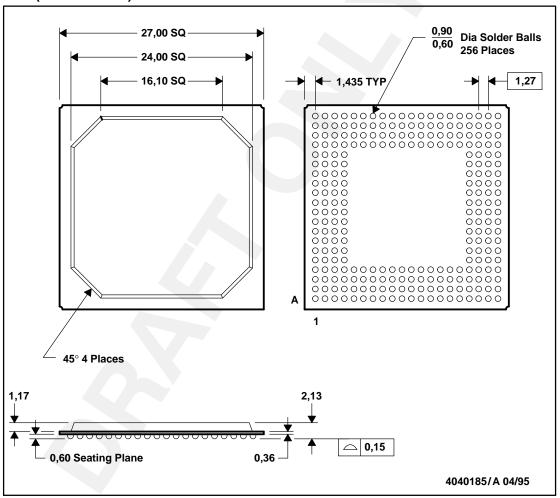

| Αn | pendix B Mechanical Data         | B-1         |

## **List of Illustrations**

| Figure                                   | Title | Page |

|------------------------------------------|-------|------|

| 1–1 Functional Block Diagram             |       | 1–4  |

| 1–2 Terminal Assignments                 |       |      |

| 2-1 PCI Configuration Region             |       | 2–3  |

| 2-2 Organization of Memory Devices       |       |      |

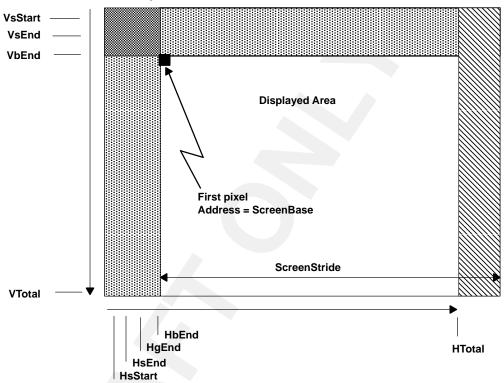

| 2–3 Video Timing Parameters              |       |      |

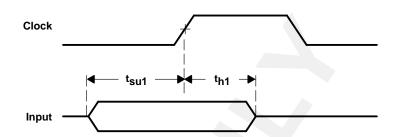

| 4–1 Input Timing Parameters              |       |      |

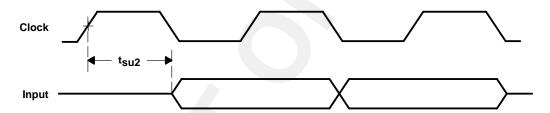

| 4–2 Output Timing Parameters             |       |      |

| 4–3 DAC Write Timing                     |       |      |

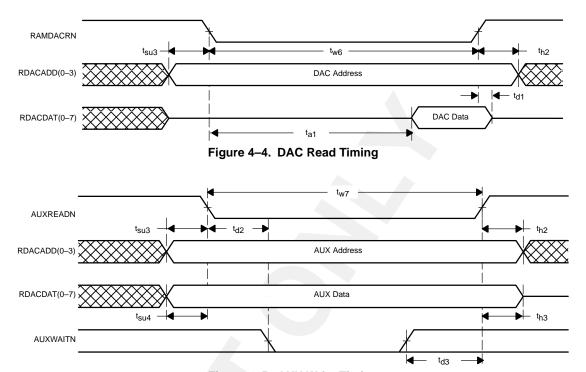

| 4–4 DAC Read Timing                      |       |      |

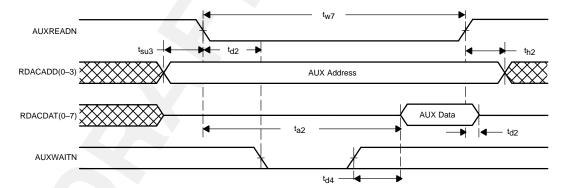

| 4–5 AUX Write Timing                     |       |      |

| 4–6 AUX Read Timing                      |       |      |

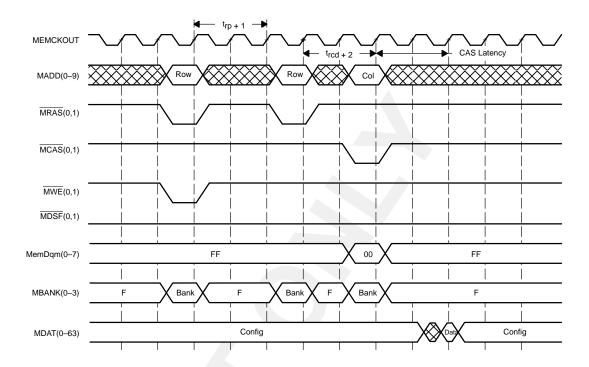

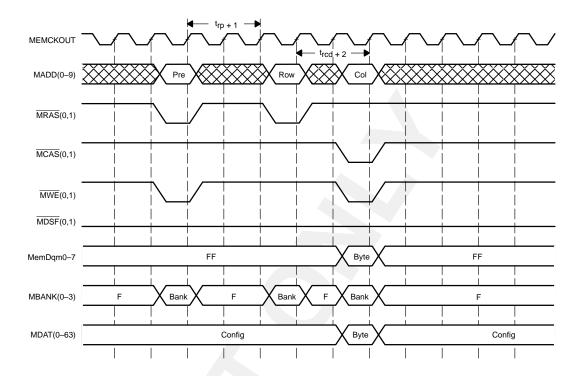

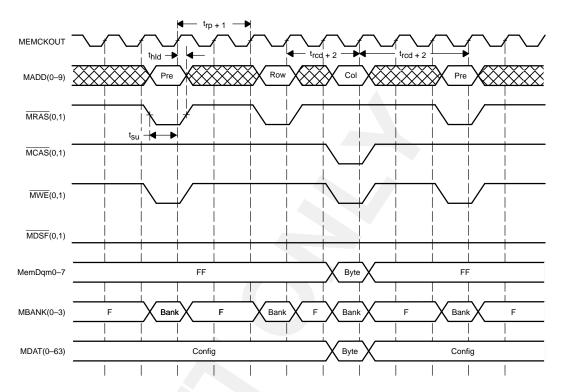

| 4–7 Single Read with Precharge Timing .  |       |      |

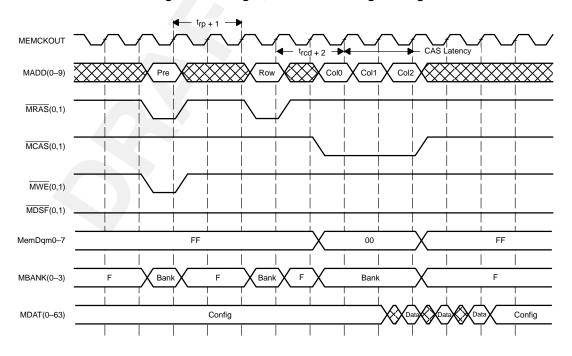

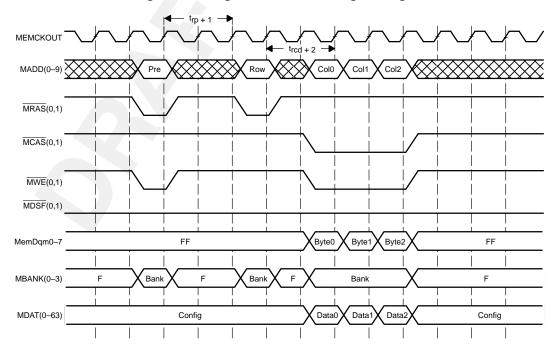

| 4–8 Multiple Reads to Same Bank Timing   |       |      |

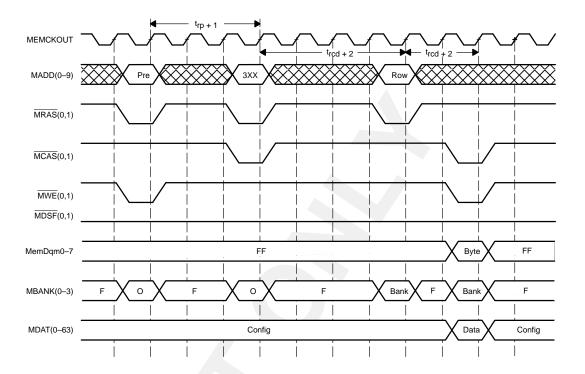

| 4–9 Single Write with Precharge Timing . |       |      |

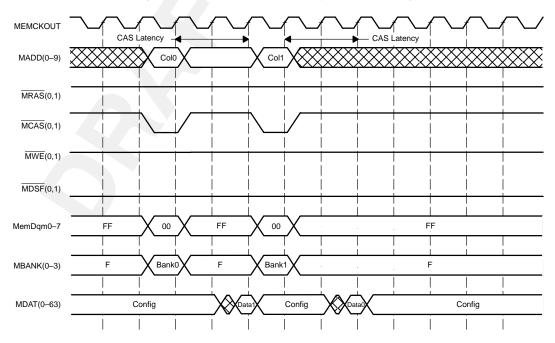

| 4–10 Multiple Writes to Same Bank Timing |       |      |

| 4–11 Refresh Followed by Access Timing   |       |      |

| 4–12 Multiple Reads From Different Banks |       |      |

| 4–13 RAS Minimum Access Timing           |       |      |

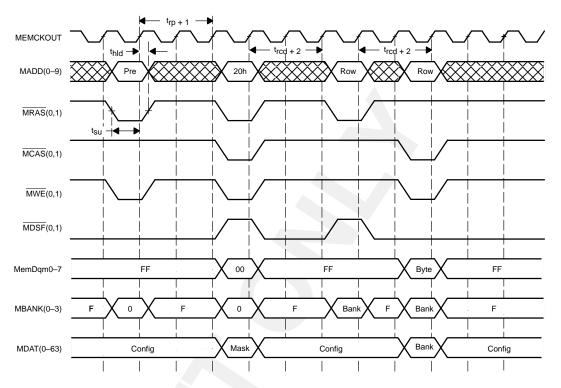

| 4–14 Mask Load Followed by Masked Wri    | •     |      |

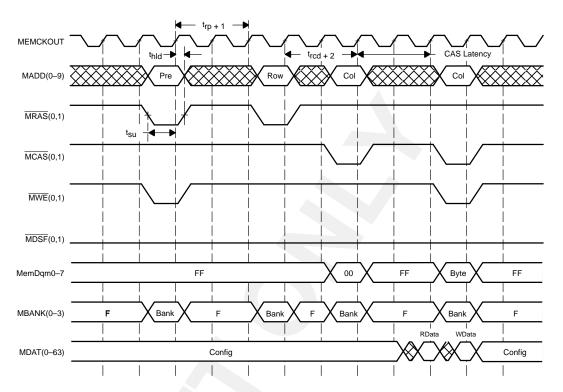

| 4–15 Read Followed by Write - No Dead (  |       |      |

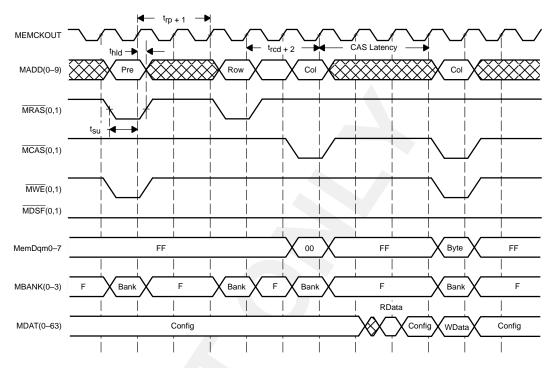

| 4–16 Read Followed by Write - With Dead  |       |      |

| 5–1 Typical RAMDAC Organization          |       |      |

| 5–2 Video Timing Parameters              |       | 5-2  |

## **List of Tables**

| Page      |

|-----------|

| <br>. 2–1 |

| <br>. 2–2 |

| <br>. 2–2 |

| <br>. 2–4 |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

|           |

| <br>2-21  |

|           |

|           |

|           |

|           |

|           |

| 2–42 | FIFO Disconnect Register                     | 2-24 |

|------|----------------------------------------------|------|

| 2–43 | Chip Configuration Register                  | 2-25 |

| 2–44 | Reboot Register                              | 2-26 |

| 2–45 | ROM Control Register                         | 2-26 |

| 2–46 | Boot Address Register                        | 2-27 |

| 2–47 | Memory Configuration Register                | 2-28 |

| 2–48 | Bypass Write Mask Register                   | 2-29 |

| 2–49 | Framebuffer Write Mask Register              | 2-30 |

| 2–50 | Count Register                               | 2-30 |

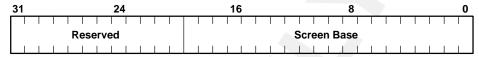

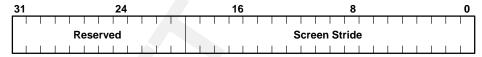

| 2–51 | Screen Base Register                         | 2-31 |

| 2–52 | Screen Stride Register                       | 2-31 |

|      | Horizontal Total Register                    |      |

| 2–54 | Horizontal Gate End Register                 | 2-32 |

| 2–55 | Horizontal Blank End Register                | 2-32 |

| 2–56 | Horizontal Sync Start Register               | 2-33 |

| 2–57 | Horizontal Sync End Register                 | 2-34 |

|      | Vertical Total Register                      |      |

| 2–59 | Vertical Blank End Register                  | 2–34 |

| 2–60 | Vertical Sync Start Register                 | 2–35 |

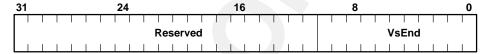

| 2–61 | Vertical Sync End Register                   | 2–35 |

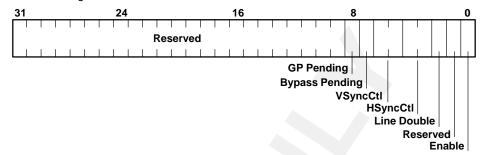

| 2–62 | Video Control Register                       | 2–36 |

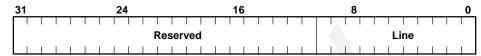

|      | Interrupt Line Register                      |      |

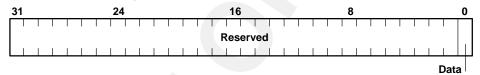

|      | Display Data Channel Data Register           |      |

|      | Line Count Register                          |      |

| 2–66 | VGA Control Register                         | 2–39 |

|      | Mode 640 Register                            |      |

|      | Parameter Values, MCLK = 50 MHz and 4 Mbytes |      |

|      | Parameter Values, MCLK = 66 MHz and 6 Mbytes |      |

| 2–70 | Parameter Values, MCLK = 66 MHz and 8 Mbytes | 2–44 |

|      | Timing Values for 640 x 480 16 BPP 75 Hz     |      |

|      | Timing Values for 800 x 600 32 BPP 75 Hz     |      |

| 2–73 | Reset Control                                | 2-47 |

| 2-73 | Reset Control                                | 2-47 |

## 1 Introduction

The TVP4010 high-performance 3D graphics processor combines workstation-class 3D graphics acceleration and state of the art 2D performance in a single chip. All 3D rendering operations are accelerated by the TVP4010 including Gouraud shading, depth buffering, texture mapping and alpha blending.

Implemented around a scaleable memory architecture, the TVP4010 reduces the cost and complexity of delivering high-performance 3D graphics within a windowing environment making it ideal for a wide range of graphics products from PC boards to workstation accelerators.

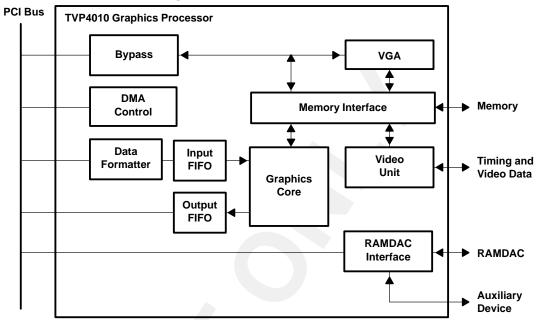

The major TVP4010 functional blocks are:

- PCI interface

- Graphics core

- Memory interface

- Video timing generation

- Auxiliary device support

- Reset configuration control

- ROM support

- Address maps

### 1.1 Features

#### **Texture Mapping**

- True per-pixel perspective correction

- High-quality bilinear filtering

- Palletized and RGB textures

- Local texture buffer

- Specular texture highlighting

- · Fast texture loading with DMA

- Real-time video textures

- Chroma-keying

- Configurable texture compression

#### 3D Rendering

- Points, lines, triangles and sprites

- Gouraud and flat shading

- Optional Z-buffering (16-bit)

- Fog and depth-cueing

- · Blending and stippling

- Volumetric collision detection

- Stencil buffer (1-bit)

- Real-time full scene anti-aliasing

- Scissor test and logic operations

- 3D transparent sprites with Z

### **Advanced Real-Time 2D Processing**

- Fast affine image transforms

- Flexible alpha-based compositing

- Alpha-blended sprites with full Z

- Stencil for cut-outs

#### **GUI Acceleration**

- Over 30 million Winmarks (WinBench 97)

- BitBlt with ROPS

- Fast linear addressed framebuffer

- Block fill and text acceleration

- 8-, 16-, and 24-bit color

- Fast on-chip SVGA

- Windows and QuickDraw<sup>TM</sup> drivers

- Bypass to linear framebuffer

#### **Accelerated Video Playback**

- YUV to RGB conversion

- MPEG compatible

- XY scaling and smoothing

- Dithering

- Chroma-keying (with color range)

## Performance (TVP4010 - 80)

- 42 M textured pixels/séc

- 800 K textured polygons/sec

- 2 Gbyte/sec block fill

- 120 Mbyte/sec texture download rate

- 30 fps scaled, filtered video playback

### **Display Features**

- Double and triple-buffering

- 32-bit RGBA for 2D

- 16-bit RGBA for 3D

- 8-and 16-bit dithering

- 320 x 200 to 1600 x 1200 resolution

- Hardware pan

#### **PCI** Interface

- 32-bit glueless PCI bus (Rev 2.1)

- DMA mastering

- 32-entry command FIFO

- Byte swapping for Mac platforms

- ACI interrupt support

- GLINT Delta interface

### **Memory Architecture**

- 64-bit SGRAM/SDRAM interface

- SDRAM for lower cost

- SGRAM for higher performance

- 600 Mbyte/sec bandwidth

- Single 2, 4, 6, or 8 Mbytes total memory

- Multi-function memory store:

- Display buffer and backbuffer(s)

- Texture maps

- Z-buffer and stencil data

- Flexible memory usage

- · Can use rendered images as texture

- Dynamic allocation of memory

- · Linear and patched addressing

- Block and masked writes

- · Mixed RGBA, CI and YUV data

## **System Integration**

- 3.3 V supply, 2.5 W

- 256-pin BGA package

- Internal video timing generator

- Fast 32-bit LUT-DAC port

- ROM interface

- VESA DPMS and DDC

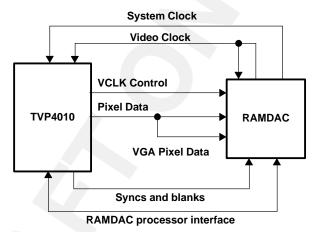

## 1.2 Functional Block Diagram

Figure 1-1. Functional Block Diagram

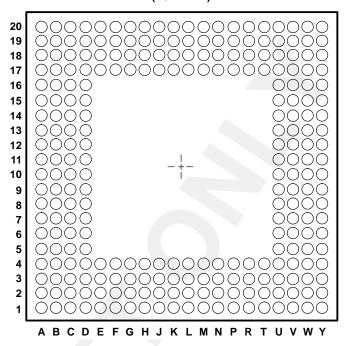

## 1.3 Terminal Assignments

## GFN PACKAGE (TOP VIEW)

Figure 1-2. Terminal Assignments

## 1.4 Ordering Information

Pixel Clock

MUST CONTAIN TWO CHARACTERS:

-60: 60-MHz pixel clock

-80: 80-MHz pixel clock

Package

MUST CONTAIN THREE LETTERS:

GFN: Plastic Ball Grid Array

## 1.5 Terminal Functions

| TERMINAL |     | 1/0 | DESCRIPTION        | DD11/57 |

|----------|-----|-----|--------------------|---------|

| NAME     | NO. | 1/0 | DESCRIPTION        | DRIVET  |

| AUXREAD  | E18 | 0   | Aux read           | 8       |

| AUXWAIT  | E17 | - 1 | Aux wait           | _       |

| AUXWRITE | D19 | 0   | Aux write          | 8       |

| DDC      | C19 | - 1 | DDC data port      | _       |

| MADD0    | Y13 | 0   | Memory address     | 12      |

| MADD1    | U12 | 0   | Memory address     | 12      |

| MADD2    | V12 | 0   | Memory address     | 12      |

| MADD3    | W12 | 0   | Memory address     | 12      |

| MADD4    | Y12 | 0   | Memory address     | 12      |

| MADD5    | U11 | 0   | Memory address     | 12      |

| MADD6    | V11 | 0   | Memory address     | 12      |

| MADD7    | W11 | 0   | Memory address     | 12      |

| MADD8    | Y11 | 0   | Memory address     | 12      |

| MADD9    | Y10 | 0   | Memory address     | 12      |

| MBANK0   | J18 | 0   | Memory bank select | 8       |

| MBANK1   | J19 | 0   | Memory bank select | 8       |

| MBANK2   | J20 | 0   | Memory bank select | 8       |

| MBANK3   | K17 | 0   | Memory bank select | 8       |

| MBYTE0   | J17 | 0   | Memory byte enable | 8       |

| MBYTE1   | H20 | 0   | Memory byte enable | 8       |

| MBYTE2   | H19 | 0   | Memory byte enable | 8       |

| MBYTE3   | H18 | 0   | Memory byte enable | 8       |

| MBYTE4   | G20 | 0   | Memory byte enable | 8       |

| MBYTE5   | G19 | 0   | Memory byte enable | 8       |

| MBYTE6   | F20 | 0   | Memory byte enable | 8       |

| MBYTE7   | E20 | 0   | Memory byte enable | 8       |

| MCAS0    | M20 | 0   | Memory byte enable | 8       |

| MCAS1    | L19 | 0   | Memory byte enable | 8       |

| MCLK     | B10 | I   | System clock       | -       |

| MDAT0    | W3  | I/O | Memory data        | 8       |

| MDAT1    | W4  | I/O | Memory data        | 8       |

| MDAT10   | W9  | I/O | Memory data        | 8       |

| MDAT11   | W10 | I/O | Memory data        | 8       |

| MDAT12   | W13 | I/O | Memory data        | 8       |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output.

| TERMINAL |     |     |             |        |

|----------|-----|-----|-------------|--------|

| NAME     | NO. | 1/0 | DESCRIPTION | DRIVET |

| MDAT13   | Y14 | I/O | Memory data | 8      |

| MDAT14   | Y15 | I/O | Memory data | 8      |

| MDAT15   | Y16 | I/O | Memory data | 8      |

| MDAT16   | V15 | I/O | Memory data | 8      |

| MDAT17   | Y17 | I/O | Memory data | 8      |

| MDAT18   | W17 | I/O | Memory data | 8      |

| MDAT19   | U16 | I/O | Memory data | 8      |

| MDAT2    | U5  | I/O | Memory data | 8      |

| MDAT20   | W18 | I/O | Memory data | 8      |

| MDAT21   | V18 | I/O | Memory data | 8      |

| MDAT22   | Y20 | I/O | Memory data | 8      |

| MDAT23   | V19 | I/O | Memory data | 8      |

| MDAT24   | U18 | I/O | Memory data | 8      |

| MDAT25   | V20 | I/O | Memory data | 8      |

| MDAT26   | T18 | I/O | Memory data | 8      |

| MDAT27   | T20 | I/O | Memory data | 8      |

| MDAT28   | P17 | I/O | Memory data | 8      |

| MDAT29   | P18 | I/O | Memory data | 8      |

| MDAT3    | Y4  | I/O | Memory data | 8      |

| MDAT30   | P20 | I/O | Memory data | 8      |

| MDAT31   | N19 | I/O | Memory data | 8      |

| MDAT32   | Y2  | I/O | Memory data | 8      |

| MDAT33   | V4  | I/O | Memory data | 8      |

| MDAT34   | Y3  | I/O | Memory data | 8      |

| MDAT35   | V5  | I/O | Memory data | 8      |

| MDAT36   | Y5  | I/O | Memory data | 8      |

| MDAT37   | U7  | I/O | Memory data | 8      |

| MDAT38   | V7  | I/O | Memory data | 8      |

| MDAT39   | Y7  | I/O | Memory data | 8      |

| MDAT4    | W5  | I/O | Memory data | 8      |

| MDAT40   | W8  | I/O | Memory data | 8      |

| MDAT41   | V9  | I/O | Memory data | 8      |

| MDAT42   | Y9  | I/O | Memory data | 8      |

| MDAT43   | V10 | I/O | Memory data | 8      |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output.

| TERMINAL  |     |     |                     |        |

|-----------|-----|-----|---------------------|--------|

| NAME      | NO. | 1/0 | DESCRIPTION         | DRIVET |

| MDAT44    | V13 | I/O | Memory data         | 8      |

| MDAT45    | W14 | I/O | Memory data         | 8      |

| MDAT46    | V14 | I/O | Memory data         | 8      |

| MDAT47    | U14 | I/O | Memory data         | 8      |

| MDAT48    | W16 | I/O | Memory data         | 8      |

| MDAT49    | V16 | I/O | Memory data         | 8      |

| MDAT5     | V6  | I/O | Memory data         | 8      |

| MDAT50    | Y18 | I/O | Memory data         | 8      |

| MDAT51    | V17 | I/O | Memory data         | 8      |

| MDAT52    | Y19 | I/O | Memory data         | 8      |

| MDAT53    | W19 | I/O | Memory data         | 8      |

| MDAT54    | W20 | I/O | Memory data         | 8      |

| MDAT55    | U19 | I/O | Memory data         | 8      |

| MDAT56    | T17 | I/O | Memory data         | 8      |

| MDAT57    | U20 | I/O | Memory data         | 8      |

| MDAT58    | T19 | I/O | Memory data         | 8      |

| MDAT59    | R18 | I/O | Memory data         | 8      |

| MDAT6     | W6  | I/O | Memory data         | 8      |

| MDAT60    | R19 | I/O | Memory data         | 8      |

| MDAT61    | P19 | I/O | Memory data         | 8      |

| MDAT62    | N18 | I/O | Memory data         | 8      |

| MDAT63    | N20 | I/O | Memory data         | 8      |

| MDAT7     | W7  | I/O | Memory data         | 8      |

| MDAT8     | V8  | I/O | Memory data         | 8      |

| MDAT9     | Y8  | I/O | Memory data         | 8      |

| MDSF0     | K18 | 0   | Memory DSF          | 8      |

| MDSF1     | K20 | 0   | Memory DSF          | 8      |

| MEMCKE    | G17 | 0   | Memory clock enable | 8      |

| MEMCKOUT0 | F18 | 0   | Memory clock        | 12     |

| MEMCKOUT1 | E19 | 0   | Memory clock        | 12     |

| MRAS0     | M18 | 0   | Memory RAS          | 8      |

| MRAS1     | M19 | 0   | Memory RAS          | 8      |

| MWE0      | L18 | 0   | Memory write enable | 8      |

| MWE1      | L20 | 0   | Memory write enable | 8      |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output.

| TERMIN  | TERMINAL |     | DECORPTION                 | DD1)/5† |

|---------|----------|-----|----------------------------|---------|

| NAME    | NO.      | 1/0 | DESCRIPTION                | DRIVET  |

| NC0     | A15      | ı   | No connection (see Note 1) | -       |

| NC2     | F19      | ı   | No connection (see Note 1) | _       |

| NC4     | R20      | ı   | No connection (see Note 1) | -       |

| NC5     | W15      | 1   | No connection (see Note 1) | _       |

| NC6     | Y6       | ı   | No connection (see Note 1) | 8       |

| PCIAD0  | Y1       | I/O | PCI address and data       | Р       |

| PCIAD1  | W1       | I/O | PCI address and data       | Р       |

| PCIAD10 | R1       | I/O | PCI address and data       | Р       |

| PCIAD11 | R3       | I/O | PCI address and data       | Р       |

| PCIAD12 | P1       | I/O | PCI address and data       | Р       |

| PCIAD13 | P2       | I/O | PCI address and data       | Р       |

| PCIAD14 | P3       | I/O | PCI address and data       | Р       |

| PCIAD15 | P4       | I/O | PCI address and data       | Р       |

| PCIAD16 | L1       | I/O | PCI address and data       | Р       |

| PCIAD17 | L2       | I/O | PCI address and data       | Р       |

| PCIAD18 | K1       | I/O | PCI address and data       | Р       |

| PCIAD19 | K3       | I/O | PCI address and data       | Р       |

| PCIAD2  | W2       | I/O | PCI address and data       | Р       |

| PCIAD20 | J1       | I/O | PCI address and data       | Р       |

| PCIAD21 | J2       | I/O | PCI address and data       | Р       |

| PCIAD22 | J3       | I/O | PCI address and data       | Р       |

| PCIAD23 | J4       | I/O | PCI address and data       | Р       |

| PCIAD24 | F2       | I/O | PCI address and data       | Р       |

| PCIAD25 | G2       | I/O | PCI address and data       | Р       |

| PCIAD26 | G3       | I/O | PCI address and data       | Р       |

| PCIAD27 | F3       | I/O | PCI address and data       | Р       |

| PCIAD28 | G4       | I/O | PCI address and data       | Р       |

| PCIAD29 | E1       | I/O | PCI address and data       | Р       |

| PCIAD3  | V1       | I/O | PCI address and data       | Р       |

| PCIAD30 | E2       | I/O | PCI address and data       | Р       |

| PCIAD31 | E3       | I/O | PCI address and data       | Р       |

| PCIAD4  | V2       | I/O | PCI address and data       | Р       |

| PCIAD5  | V3       | I/O | PCI address and data       | Р       |

| PCIAD6  | U2       | I/O | PCI address and data       | Р       |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output. NOTE 1: Unused pins should be left no connect.

| TERMINAL       |     | 1/0 |                      | DD11/57 |

|----------------|-----|-----|----------------------|---------|

| NAME           | NO. | I/O | DESCRIPTION          | DRIVET  |

| PCIAD7         | T1  | I/O | PCI address and data | Р       |

| PCIAD8         | T3  | I/O | PCI address and data | Р       |

| PCIAD9         | T4  | I/O | PCI address and data | Р       |

| PCICBEN0       | T2  | I/O | PCI byte enable      | Р       |

| PCICBEN1       | N2  | I/O | PCI byte enable      | Р       |

| PCICBEN2       | L3  | I/O | PCI byte enable      | Р       |

| PCICBEN3       | G1  | I/O | PCI byte enable      | Р       |

| PCICLK         | C4  | I   | PCI clock            | _       |

| PCIDEVSEI      | МЗ  | I/O | PCI device select    | Р       |

| PCIFIFOINDIS   | C2  | 0   | Delta control        | Р       |

| PCIFIFOOUTDILS | D2  | 0   | Delta control        | Р       |

| PCIFRAME       | L4  | I/O | PCI frame            | Р       |

| PCIGNT         | A2  | I   | PCI grant            | _       |

| PCIIDSEL       | H1  | I   | PCI id               | _       |

| PCIINTA        | B1  | OD‡ | PCI interrupt        | Р       |

| PCIIRDY        | M1  | I/O | PCI ready            | Р       |

| PCIPAR         | N1  | I/O | PCI parity           | Р       |

| PCIREQ         | C1  | 0   | PCI request          | Р       |

| PCIRST         | С3  | 1   | PCI reset            | -       |

| PCISTOP        | M4  | I/O | PCI stop             | Р       |

| PCITRDY        | M2  | I/O | PCI ready            | Р       |

| RAMDACR        | C20 | 0   | RAMDAC read          | 8       |

| RAMDACW        | D18 | 0   | RAMDAC write         | 8       |

| RDACADD0       | A20 | 0   | RAMDAC address       | 8       |

| RDACADD1       | B19 | 0   | RAMDAC address       | 8       |

| RDACADD2       | C18 | 0   | RAMDAC address       | 8       |

| RDACADD3       | B20 | 0   | RAMDAC address       | 8       |

| RDACDAT0       | B16 | I/O | RAMDAC data          | 8       |

| RDACDAT1       | C16 | I/O | RAMDAC data          | 8       |

| RDACDAT2       | A17 | I/O | RAMDAC data          | 8       |

| RDACDAT3       | A18 | I/O | RAMDAC data          | 8       |

| RDACDAT4       | D16 | I/O | RAMDAC data          | 8       |

| RDACDAT5       | C17 | I/O | RAMDAC data          | 8       |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output. ‡ OD is open drain.

| TERMINAL          |     | .,, | DECODINE                              | DD11/57 |

|-------------------|-----|-----|---------------------------------------|---------|

| NAME              | NO. | 1/0 | DESCRIPTION                           | DRIVET  |

| RDACDAT6          | B17 | I/O | I/O RAMDAC data                       |         |

| RDACDAT7          | B18 | I/O | RAMDAC data                           | 8       |

| RESERVED0         | E4  | ı   | No connection (see Note 1)            | _       |

| RESERVED1         | D5  | ı   | No connection (see Note 1)            | _       |

| RESERVED2         | B2  | ı   | No connection (see Note 1)            | _       |

| RESETOUT          | A19 | 0   | External reset                        | 8       |

| RI                | C5  | ı   | Pull high (see Note 2)                | _       |

| ROM               | D20 | 0   | ROM enable                            | 8       |

| ROMWE             | D3  | 0   | ROM write enable                      | 8       |

| TEST2             | K19 | 1   | No connection (see Note 1 and Note 2) | _       |

| TESTACLK          | G18 | ı   | No connection (see Note 1 and Note 2) | _       |

| TESTCCLK          | M17 | 1   | No connection (see Note 1 and Note 2) | _       |

| TESTGCLK          | H2  | 1   | No connection (see Note 1 and Note 2) | -       |

| TESTMODE          | U9  | ı   | I Pull low (see Note 2)               |         |

| VCC0              | F1  |     | Supply voltage                        |         |

| V <sub>CC1</sub>  | R2  |     | Supply voltage                        |         |

| VCLK              | А3  | ı   | Video clock                           |         |

| V <sub>DD0</sub>  | D11 |     | Supply voltage                        | -       |

| V <sub>DD1</sub>  | D15 |     | Supply voltage                        | -       |

| V <sub>DD10</sub> | U15 |     | Supply voltage                        | _       |

| V <sub>DD11</sub> | U6  |     | Supply voltage                        | -       |

| $V_{DD2}$         | D6  |     | Supply voltage                        | _       |

| V <sub>DD3</sub>  | F17 |     | Supply voltage                        | _       |

| $V_{\text{DD4}}$  | F4  |     | Supply voltage                        | -       |

| V <sub>DD5</sub>  | K4  |     | Supply voltage                        | _       |

| V <sub>DD6</sub>  | L17 |     | Supply voltage                        | _       |

| V <sub>DD7</sub>  | R17 |     | Supply voltage                        | _       |

| V <sub>DD8</sub>  | R4  |     | Supply voltage                        | -       |

| V <sub>DD9</sub>  | U10 |     | Supply voltage                        |         |

| VGAACTIVE         | B4  | 0   | Video is from VGA                     | 8       |

| VIDBLANK          | B5  | 0   | Video blank                           | 8       |

| VIDCTL0           | В3  | 0   | Control for clock synthesizer         |         |

| VIDCTL1           | A4  | 0   | Control for clock synthesizer         |         |

| VIDHSYNC          | D7  | 0   | Video horizontal sync                 | 8       |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output.

NOTES: 1. Unused pins should be left no connect.

<sup>2.</sup> Test pin RI should be pulled high in functional mode, test pin TESTMODE should be tied low, all other test pins (TESTACLK, TESTBCLK, TESTCCLK, TESTGCLK) should be left no connect.

| TERMINAL         |     | 1/0 | PEGGENETION         | DD11/57 |

|------------------|-----|-----|---------------------|---------|

| NAME             | NO. | 1/0 | DESCRIPTION         | DRIVET  |

| VIDPIX0          | A5  | 0   | Pixel data          | 8       |

| VIDPIX1          | B6  | 0   | Pixel data          | 8       |

| VIDPIX10         | C9  | 0   | Pixel data          | 8       |

| VIDPIX11         | B9  | 0   | Pixel data          | 8       |

| VIDPIX12         | A9  | 0   | Pixel data          | 8       |

| VIDPIX13         | D10 | 0   | Pixel data          | 8       |

| VIDPIX14         | A10 | 0   | Pixel data          | 8       |

| VIDPIX15         | A11 | 0   | Pixel data          | 8       |

| VIDPIX16         | C11 | 0   | Pixel data          | 8       |

| VIDPIX17         | B11 | 0   | Pixel data          | 8       |

| VIDPIX18         | A12 | 0   | Pixel data          | 8       |

| VIDPIX19         | B12 | 0   | Pixel data          | 8       |

| VIDPIX2          | C7  | 0   | Pixel data          | 8       |

| VIDPIX20         | C12 | 0   | Pixel data          | 8       |

| VIDPIX21         | D12 | 0   | Pixel data          | 8       |

| VIDPIX22         | A13 | 0   | Pixel data          | 8       |

| VIDPIX23         | B13 | 0   | Pixel data          | 8       |

| VIDPIX24         | C13 | 0   | Pixel data          | 8       |

| VIDPIX25         | A14 | 0   | Pixel data          | 8       |

| VIDPIX26         | B14 | 0   | Pixel data          | 8       |

| VIDPIX27         | C14 | 0   | Pixel data          | 8       |

| VIDPIX28         | B15 | 0   | Pixel data          | 8       |

| VIDPIX29         | D14 | 0   | Pixel data          | 8       |

| VIDPIX3          | A6  | 0   | Pixel data          | 8       |

| VIDPIX30         | C15 | 0   | Pixel data          | 8       |

| VIDPIX31         | A16 | 0   | Pixel data          | 8       |

| VIDPIX4          | B7  | 0   | Pixel data          | 8       |

| VIDPIX5          | A7  | 0   | Pixel data          | 8       |

| VIDPIX6          | C8  | 0   | Pixel data          | 8       |

| VIDPIX7          | B8  | 0   | Pixel data          | 8       |

| VIDPIX8          | A8  | 0   | Pixel data          | 8       |

| VIDPIX9          | D9  | 0   | Pixel data          | 8       |

| VIDVSYNC         | C6  | 0   | Video vertical sync |         |

| V <sub>SS0</sub> | A1  |     | Ground (see Note 3) |         |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output. NOTE 3: All V<sub>SS</sub> pins must be connected to ground, including the central pin grid H8–N13.

| TERMINAL          |     | 1/0 | DESCRIPTION         | DDWET  |

|-------------------|-----|-----|---------------------|--------|

| NAME              | NO. | 1/0 | DESCRIPTION         | DRIVET |

| V <sub>SS1</sub>  | C10 |     | Ground (see Note 3) | _      |

| VSS10             | K2  |     | Ground (see Note 3) | _      |

| VSS11             | N17 |     | Ground (see Note 3) | _      |

| VSS12             | N3  |     | Ground (see Note 3) | _      |

| VSS13             | N4  |     | Ground (see Note 3) | -      |

| V <sub>SS14</sub> | U1  |     | Ground (see Note 3) | -      |

| VSS15             | U13 |     | Ground (see Note 3) | _      |

| VSS16             | U17 |     | Ground (see Note 3) | _      |

| VSS17             | U3  |     | Ground (see Note 3) | _      |

| VSS18             | U4  |     | Ground (see Note 3) | -      |

| VSS19             | U8  |     | Ground (see Note 3) | -      |

| V <sub>SS2</sub>  | D1  |     | Ground (see Note 3) | -      |

| V <sub>SS3</sub>  | D13 |     | Ground (see Note 3) | _      |

| V <sub>SS4</sub>  | D17 |     | Ground (see Note 3) | _      |

| V <sub>SS5</sub>  | D4  |     | Ground (see Note 3) | _      |

| V <sub>SS6</sub>  | D8  |     | Ground (see Note 3) | _      |

| V <sub>SS7</sub>  | H17 |     | Ground (see Note 3) |        |

| V <sub>SS8</sub>  | H3  |     | Ground (see Note 3) | _      |

| $V_{SS9}$         | H4  |     | Ground (see Note 3) | _      |

<sup>†</sup> Output power ratings are marked as 8 or 12 for the mA current rating, or P indicating a PCI compatible output. NOTE 3: All V<sub>SS</sub> pins must be connected to ground, including the central pin grid H8–N13.

## 2 Detailed Description

#### 2.1 PCI Interface

The PCI interface conforms to the PCI local bus standard revision 2.1. The TVP4010 is a PCI local bus target and a PCI local bus read master.

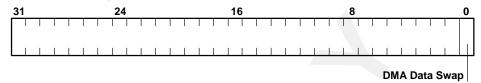

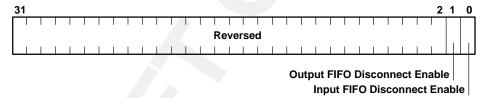

The PCI interface has an input FIFO for passing data to the graphics core, and an output FIFO for buffering up data to be read from the graphics core. The input FIFO is 32 words deep; the output FIFO is 8 words deep. A DMA controller is provided in the PCI interface to allow the TVP4010 to read data directly into the graphics core input FIFO.

#### 2.2 Graphics Core

The graphics core in the TVP4010 accelerates the key operations for 3D and 2D applications. For further information on the functionality of the graphics core refer to the TVP4010 Programmer's Reference Manual.

## 2.3 Memory Interface

The local memory is used to store color, depth, stencil, and texture data. For more information on the different data types and their usage refer to the TVP4010 Programmers Reference Manual.

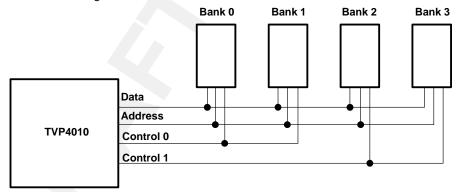

The memory is organized as 1 to 4 banks of synchronous graphics RAM (SGRAM). Each bank is 64 bits wide and made up of two devices, each 32 bits wide by 256K entries deep. This gives 2 Mbytes per bank, with a maximum memory array of 8 Mbytes.

Bank zero must always be fitted since the VGA uses this area for local storage. Any other combination of banks may be fitted, but for contiguous memory banks should be added from 1 to 3.

The TVP4010 makes use of special SGRAM features including block fill and write-per-bit masking. SDRAM may be used in place of SGRAM if it is identical to SGRAM except for missing block write and write per bit masks.

## 2.4 Video Timing Generation

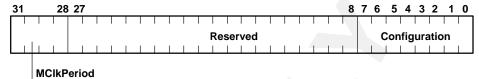

The TVP4010 has an internal timing generator. The maximum video clock (VCLK) is 50 MHz. Absolute maximum TVP4010 video clock rates are shown in Table 2–1.

| PIXEL WIDTH | MAXIMUM PIXEL FREQUENCY |

|-------------|-------------------------|

| 32 bit      | 50 MHz                  |

| 16 bit      | 100 MHz                 |

| 8 bit       | 200 MHz                 |

Table 2-1. Maximum Pixel Clock Frequencies

### 2.5 Auxiliary Device Support

The TVP4010 can act as a gateway to an additional device which shares address and data lines with the RAMDAC. This device can be mapped into IO space as well as memory space. The auxiliary bus protocol is asynchronous and supports a wait signal that the slave device may use to insert wait states into a transaction.

#### 2.6 Reset Configuration Control

A number of parameters for the TVP4010 are set at reset time, such as memory size and speed. The reset state is configured with resistors connected to the memory and video port data pins. The state of the data pins is sampled on the rising edge of the reset line. See Section 2.23, *Reset Control* for more details.

#### 2.7 ROM Support

The TVP4010 supports a flash ROM. This ROM may store code needed for device-specific initialization and the VGA BIOS.

### 2.8 Address Mapping

The TVP4010 has seven PCI base address regions as listed in Table 2-2.

Table 2-2. PCI Address Regions

|               | 9                        |

|---------------|--------------------------|

| REGION        | DESCRIPTION              |

| Configuration | PCI configuration region |

| 0             | GC control region        |

| 1             | Bypass access to memory  |

| 2             | Bypass access to memory  |

| 3             | Auxiliary bus            |

| 4             | Delta aperture           |

| ROM           | Expansion ROM            |

Two memory apertures are provided, each is a PCI region with a fixed size of 8 Mbytes. A variety of access modes are available, including byte swapped, half-word swapped, and packed 16-bit pixel modes to support per-window double buffering with a suitable RAMDAC. Each aperture can be programmed to address the memory controller directly, or to address the memory through the VGA subsystem. The two separately controlled apertures allow different views of the memory to co-exist without register reprogramming; for example, one aperture could be set for localbuffer data accesses and the other for framebuffer data accesses.

The two memory apertures can also be programmed to allow reading and writing of the ROM instead of memory. This ensures that the ROM is visible beyond system boot time, making it possible to program a flash ROM device in the system.

When displaying images in 16-bit per-window double buffered mode the framebuffer area of memory is divided into two interleaved buffers, A and B. Each pixel uses 32 bits: the bottom 16 bits (0–15) form buffer A, and the top 16 bits (16–31) form buffer B. The top bit in buffer B is used by the RAMDAC to select which buffer is displayed, on a per-pixel basis.

The control registers for each of memory apertures one and two can be set to allow reading and writing of buffers A and B as contiguous 16-bit packed buffers although they are pixel interleaved in the memory. Each 32-bit read or write access over the PCI bus thus transfers two pixels to/from the selected 16-bit packed buffer. The apertures can be programmed to access either buffer A or buffer B, to write to both buffer A and buffer B, or to read from the active buffer as specified by bit 31.

A further control bit is provided to route the memory address via the VGA controller, rather than directly to the main memory controller. This allows the memory address to be interpreted as a VGA address. This mechanism allows the VGA to be relocated away from the standard fixed addresses. The fixed addresses may be optionally disabled so that two VGA systems can co-exist on the same bus.

### 2.9 Test Mode

When the conditions listed in Table 2-3 are met, the TVP4010 will go to in-circuit test mode.

Table 2-3. Test Mode

| PIN | NAME     | STATE |

|-----|----------|-------|

| U9  | TESTMODE | High  |

| E17 | AUXWAITN | Low   |

| C19 | DDC      | Low   |

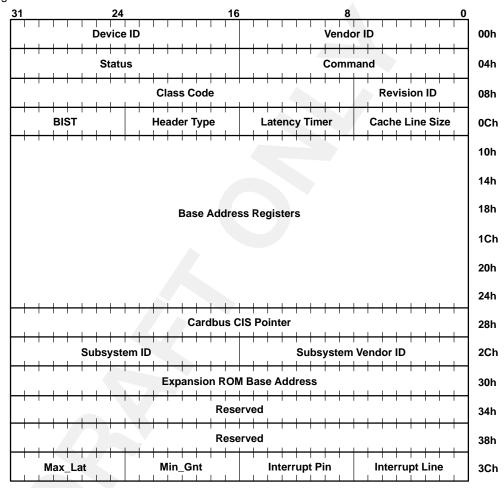

## 2.10 PCI Configuration

## 2.10.1 PCI Configuration Region

The PCI configuration region provides information that satisfies the needs of current and anticipated system configuration mechanisms.

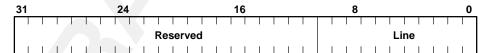

Figure 2-1. PCI Configuration Region

## 2.11 PCI Register Set

For more information about the use of the registers in this section refer to the PCI specification.

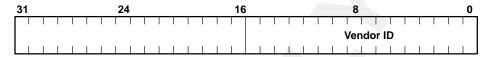

## 2.11.1 Vendor ID Register (CFGVendorld) (Region: Configuration, Index: 0x00, Access: R, Default: 0x104C)

The vendor identification register contains the vendor identification number or Texas Instruments company code.

Table 2-4. Vendor ID Register

| NAME      | DESCRIPTION |

|-----------|-------------|

| Bits 0-15 | 0x104C      |

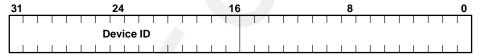

## 2.11.2 Device ID Register (CFGDeviceId) (Region: Configuration, Index: 0x02, Access: R, Default: 0x3D04)

The device identification register contains the device identification number or TVP4010 device number.

Table 2-5. Device ID Register

| NAME       | DESCRIPTION |

|------------|-------------|

| Bits 16-31 | 0x3D04      |

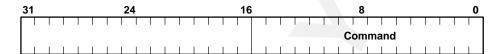

## 2.11.3 Command Register (CFGCommand) (Region: Configuration, Index: 0x04, Access: R/W, Default: 0x00)

The command register provides control over a device's ability to generate and respond to PCI cycles. Writing zero to this register disconnects the device from the PCI for all except configuration accesses. The TVP4010 supports all necessary bits within the command register for the functionality it contains.

Table 2-6. Command Register

| NAME       | I                                           | NAME DESCRIPTION                                                                                 |  |  |  |  |

|------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| INAME      |                                             |                                                                                                  |  |  |  |  |

|            |                                             | 0= Disable I/O space accesses.                                                                   |  |  |  |  |

| Bit 0      | I/O space enable                            | 1=Enable I/O space accesses. If fixed VGA addressing is disabled this bit will be 0 (read-only). |  |  |  |  |

| Bit 1      | Memory space enable                         | 0=Disable memory space accesses.                                                                 |  |  |  |  |

| DIL I      | Memory space enable                         | 1=Enable memory space accesses.                                                                  |  |  |  |  |

| Bit 2      | Bus master enable                           | 0=Disable master accesses.                                                                       |  |  |  |  |

| Dit 2      | Dus master enable                           | 1=Enable master accesses.                                                                        |  |  |  |  |

| Bit 3      | Special cycle enable (read                  | 0=TVP4010 never responds to special cycle accesses.                                              |  |  |  |  |

| DIL 3      | only)                                       | 1=?                                                                                              |  |  |  |  |

| Bit 4      | Memory write and invalidate<br>Enable       | 0= "Memory Write and Invalidate" is never generated.                                             |  |  |  |  |

| DIL 4      |                                             | 1=?                                                                                              |  |  |  |  |

| Bit 5      | VGA palette snoop enable                    | 0=Treat palette accesses like all other VGA accesses.                                            |  |  |  |  |

|            |                                             | 1= Enable VGA palette snooping. If fixed VGA addressing is disabled, this bit is 0.              |  |  |  |  |

| Bit 6      | Parity error response enable                | 0=TVP4010 does not support parity error reporting.                                               |  |  |  |  |

| סונס       | (read only)                                 | 1=?                                                                                              |  |  |  |  |

| Bit 7      | Address/data stepping enable                | 0=TVP4010 does not perform stepping.                                                             |  |  |  |  |

| DIL /      | (read only)                                 | 1=?                                                                                              |  |  |  |  |

| Bit 8      | 0500 11 11 ( 1 1)                           | 0=TVP4010 does not support parity error reporting.                                               |  |  |  |  |

| Bit 8      | SERR driver enable (read only)              | 1=?                                                                                              |  |  |  |  |

| Bit 9      | Master fast back-to-back enable (read only) | 0=The TVP4010 master does not do fast back-to-back access.                                       |  |  |  |  |

|            | enable (lead only)                          | 1=?                                                                                              |  |  |  |  |

| Bits 10-15 | Reserved (read only) default = 000000b.     |                                                                                                  |  |  |  |  |

|            |                                             |                                                                                                  |  |  |  |  |

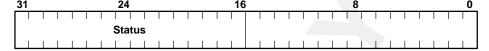

## 2.11.4 Status Register (CFGStatus) (Region: Configuration, Index: 0x06, Access: R, Default: 0x00)

The status register .....

Writes to this register cause bits to be reset, but not set. A bit is reset whenever the register is loaded with the corresponding bit position set to one.

Table 2-7. Status Register

| NAME      |                                                                               | DESCRIPTION                                               |  |

|-----------|-------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| Bits 0-4  | Reserved (read only). Default = 00000b.                                       |                                                           |  |

| D:4 F     | 00 MII                                                                        | 0=TVP4010 is 33 MHz capable only.                         |  |

| Bit 5     | 66 MHz capable (read only)                                                    | 1=?                                                       |  |

| Bit 6     | UDF supported (read only)                                                     | 0=TVP4010 does not support user-definable configurations. |  |

|           |                                                                               | 1=?                                                       |  |

|           | Fact hack to book conclus                                                     | 0=?                                                       |  |

| Bit 7     | Fast back-to-back capable (read only)                                         | 1=TVP4010 can accept fast back-to-back PCI transactions.  |  |

| Bit 8     | Data parity error detected (read                                              | 0=Parity checking not implemented on TVP4010.             |  |

| Bit 8     | only)                                                                         | 1= ?                                                      |  |

| Dito 0 40 | DEVSEL timing (read only)                                                     | 0 =?                                                      |  |

| Bits 9–10 |                                                                               | 01b=TVP4010 asserts DEVSEL# at medium speed.              |  |

| Bit 11    | Signalled target abort (read                                                  | 0=TVP4010 never signals target-abort.                     |  |

| DILTI     | only)                                                                         | 1=?                                                       |  |

| Bit 12    | Received target abort. This bit is set by the TVP4010 bus master whenever its | 0=?                                                       |  |

| DIL 12    | transaction is terminated with target-abort.                                  | 1=?                                                       |  |

| Bit 13    | Received master abort. This bit is set by the TVP4010 bus                     | 0=?                                                       |  |

| Bit 13    | master when ever its transaction is terminated with master-abort.             | 1=?                                                       |  |

| Bit 14    | Signalled system error (read                                                  | 0=TVP4010 never asserts a system error.                   |  |

| DIL 14    | only)                                                                         | 1=?                                                       |  |

| Bit 15    | Detected parity error (read                                                   | 0=Parity checking is not implemented by the TVP4010.      |  |

| DIL 15    | only)                                                                         | 1=?                                                       |  |

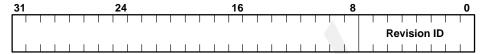

## 2.11.5 Revision ID Register (CFGRevisionId) (Region: Configuration, Index: 0x08, Access: R, Default: Rev Number)

The revision identification register identifies the revision identification number.

Table 2-8. Revision ID Register

| NAME     | DESCRIPTION                |

|----------|----------------------------|

| Bits 0-7 | Revision A, default = 0x01 |

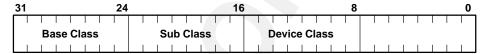

## 2.11.6 Class Code Register (CFGClassCode) (Region: Configuration, Index: 0x09, Access: R, Default: Config Data)

The class code register identifies the generic function of the TVP4010, which depends on the setting of configuration data detailed below.

Table 2-9. Class Code Register

| NAME       | DESCRIPTION                         |

|------------|-------------------------------------|

| Bits 8-15  | Device class, 00h (see table below) |

| Bits 16-23 | Sub class, 80h (see table below)    |

| Bits 24-31 | Base class, 03h (see table below)   |

Table 2-10. Class Code Register Configuration

| BASECLASSZERO<br>(CONFIG BIT) | FIXED VGA<br>ADDRESSING | BASE<br>CLASS | SUB<br>CLASS | DEVICE<br>CLASS | MEANING<br>(SEE PCI SPEC APPENDIX D) |

|-------------------------------|-------------------------|---------------|--------------|-----------------|--------------------------------------|

| 0                             | Disabled                | 03h           | 80h          | 00h             | Other display controller             |

| 0                             | Enabled                 | 03h           | 01h          | 00h             | VGA-compatible controller            |

| 1                             | Disabled                | 00h           | 00h          | 00h             | Non VGA-compatible device            |

| 1                             | Enabled                 | 00h           | 01h          | 00h             | VGA-compatible device                |

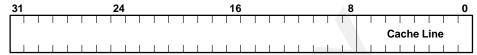

### Cache Line Size Register (CFGCacheLine) (Region: Configuration, Index: 0x0C, Access: R, Default: 0x00)

The cache line size register specifies the cache line size in units of 32-bit words. It is only implemented for masters which use the memory write and invalidate command. The TVP4010 does not use this command.

Table 2-11. Cache Line Size Register

| NAME     | DESCRIPTION                                                   |

|----------|---------------------------------------------------------------|

| Bits 0-7 | Cache line size. Cache line size unsupported. Default = 0x00. |

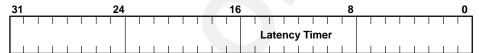

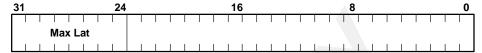

Latency Timer Register (CFGLatTimer) (Region: Configuration, Index: 0x0D, Access: R/W, Default: 0x00)

The latency timer register specifies, in PCI bus clocks, the value of the latency timer for this PCI bus master.

Table 2-12. Legacy Timer Register

| NAME | DESCRIPTION                                                                                 |  |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|      | Latency timer count. Sets the maximum number of PCI clock cycles for master burst accesses. |  |  |  |  |  |  |  |

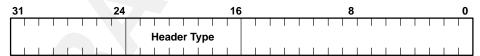

#### Header Type Register (CFGHeaderType) 2.11.9 (Region: Configuration, Index: 0x0E, Access: R, Default: 0x00)

The header type register identifies the header type. PCI definition: Single function device.

Table 2-13. Header Type Register

| NAME       | DESCRIPTION |

|------------|-------------|

| Bits 16-23 | 0x00        |

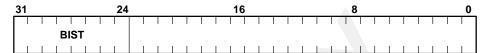

### 2.11.10 BIST Register (CFGBist)

(Region: Configuration, Index: 0x0F, Access: R, Default: 0x00)

The BIST register is optional and is used for control and status of BIST. BIST is unsupported by the TVP4010 over the PCI interface.

Table 2-14. BIST Register

| NAME       | DESCRIPTION |

|------------|-------------|

| Bits 24-31 | 0x00        |

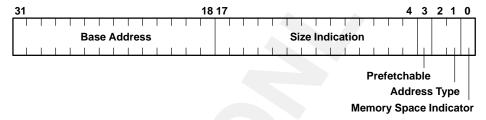

### 2.11.11 Base Address 0 Register (CFGBaseAddr0)

(Region: Configuration, Index: 0x10, Access: R/W, Default: 0x00000000)

The base address 0 register contains the TVP4010 control space offset. The control registers are in memory space. They are not prefetchable and can be located anywhere in 32-bit address space.

Table 2-15. Base Address 0 Register

| NAME       | DESCRIPTION                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------|

| Bits 0-3   | Address type (read only). Memory space, not prefetchable, in 32-bit address space. 0h.                  |

| Bits 4–16  | Size indication (read only). Indicates that the control registers must be mapped into 128 KBytes. 000h. |

| Bits 17-31 | Base offset loaded at boot time to set offset of the control register space.                            |

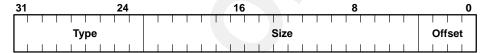

## 2.11.12 Base Address 1 Register (CFGBaseAdd1)

(Region: Configuration, Index: 0x14, Access: R/W, Default: 0x00000000)

The base address 1 register contains the TVP4010 aperture one memory offset. It is not prefetchable and can be located anywhere in 32-bit address space.

| 31 |      | 24 | 16 8 |  |  |  |  |  |  | 0  |    |  |  |  |  |  |   |     |     |  |

|----|------|----|------|--|--|--|--|--|--|----|----|--|--|--|--|--|---|-----|-----|--|

|    |      |    |      |  |  |  |  |  |  |    |    |  |  |  |  |  |   |     |     |  |

|    |      |    |      |  |  |  |  |  |  |    |    |  |  |  |  |  |   |     |     |  |

|    | Type |    |      |  |  |  |  |  |  | Si | ze |  |  |  |  |  | ( | Off | set |  |

Table 2-16. Base Address 1 Register

| NAME       | DESCRIPTION                                                                            |

|------------|----------------------------------------------------------------------------------------|

| Bit 0-3    | Address type (read only). Memory Space, not prefetchable, in 32-bit address space. 0h. |

| Bits 4-22  | Size indication (read only). Fixed at 8 Mbytes.                                        |

| Bits 23-31 | Base offset loaded at boot time to set offset of the memory space.                     |

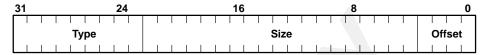

## 2.11.13 Base Address 2 Register (CFGBaseAddr2) (Region: Configuration, Index: 0x18, Access: R/W, Default: 0x00000000)

The base address 2 register contains the TVP4010 aperture two memory offset. It is not prefetchable and can be located anywhere in 32-bit address space.

Table 2-17. Base Address 2 Register

| NAME       | DESCRIPTION                                                                            |  |  |

|------------|----------------------------------------------------------------------------------------|--|--|

| Bits 0-3   | Address type (read only). Memory Space, not prefetchable, in 32-bit address space. 0h. |  |  |

| Bits 4-22  | Size indication (read only). Fixed at 8 Mbytes.                                        |  |  |

| Bits 23-31 | Base offset loaded at boot time to set offset of the memory space.                     |  |  |

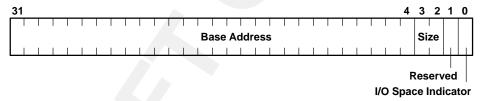

## 2.11.14 Base Address 3 Register (CFGBaseAddr3) (Region: Configuration, Index: 0x1C, Access: R/W, Default: Configured)

The base address 3 register contains the base address of the auxiliary bus. This register region is in PCI I/O space, and is enabled by the AuxEnable and AuxIOEnable configuration bits. When not enabled, the base address 3 register is zero and read-only.

Table 2-18. Base Address 3 Register

| NAME      | DESCRIPTION                                                                         |                               |  |

|-----------|-------------------------------------------------------------------------------------|-------------------------------|--|

| Bit 0     | I/O space indicator (read only)                                                     | 0=?                           |  |

| DIL U     | 1/O space indicator (read only)                                                     | 1=Region is in PCI I/O Space. |  |

| Bit 1     | Reserved (read only). 0=Reserved.                                                   |                               |  |

| Bits 2-3  | Size indication (read only). These bits are zero, giving a region size of 16 bytes. |                               |  |

| Bits 4-31 | Base address loaded at boot time to set base address of PCI region three.           |                               |  |

### 2.11.15 Base Address 4 Register (CFGBaseAddr4) (Region: Configuration, Index: 0x20, Access: R/W, Default: Configured)

The base address 4 register contains the base address of the dummy 256K address region which should be enabled when the TVP4010 is used with a GLINT delta device. This register is enabled by the DeltaEnable configuration bit. When not enabled, the base address 4 register is zero and read-only.

Although the BIOS will allocate a 256K memory region and initialize the base address 4 register, the TVP4010 will never respond to accesses in this allocated memory region. The sole purpose of this register is to obtain a 256K section of the system memory map, which can be used to reposition the GLINT delta base address registers.

Table 2-19. Base Address 4 Register

| NAME       | DESCRIPTION                                                                          |                                              |  |

|------------|--------------------------------------------------------------------------------------|----------------------------------------------|--|

| Bit 0      | Memory space indicator (read only)                                                   | 0=Region is in PCI memory space.             |  |

|            |                                                                                      | 1=?                                          |  |

| Bits 1–2   | Address type (read only)                                                             | 00b=Locate anywhere in 32-bit address space. |  |

| DIIS I-2   |                                                                                      | ,                                            |  |

| Bit 3      | Prefetchable (read only)                                                             | 0=Region is not prefetchable.                |  |

| Bit 3      |                                                                                      | 1=?                                          |  |

| Bits 4-17  | Size indication (read only). These bits are zero, giving a region size of 256 bytes. |                                              |  |

| Bits 18-31 | Base address loaded at boot time to set base address of PCI region four.             |                                              |  |

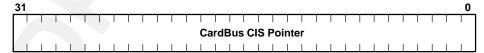

## 2.11.16 CardBus CIS Pointer Register (CFGCardBus) (Region: Configuration, Index: 0x28, Access: R, Default: 0x00)

Table 2-20. CardBus CIS Pointer Register

| NAME      | DESCRIPTION                                  |

|-----------|----------------------------------------------|

| Bits 0-31 | Cardbus pointer. 00000000h = Not implemented |

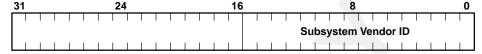

### 2.11.17 Subsystem Vendor ID Register (CFGSubsystemVendorId) (Region: Configuration, Index: 0x2C, Access: Write Once, Default: 0x0000)

The subsystem vendor ID register is used to identify the vendor of the add-in board on which the TVP4010 device resides. It has a reset value of zero and can only be written to once; all subsequent writes are discarded. All bytes of this register should be initialized by the TVP4010 BIOS after a reset.

Table 2-21. Subsystem Vendor ID Register

| NAME      | DESCRIPTION         |  |

|-----------|---------------------|--|

| Bits 0-15 | Subsystem vendor ID |  |

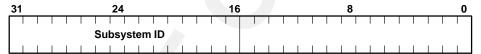

## 2.11.18 Subsystem ID Register (CFGSubsystemId) (Region: Configuration, Index: 0x2E, Access: Write Once, Default: 0x0000)

The subsystem ID register is used to identify the add-in board on which the TVP4010 device resides. It has a reset value of zero, and can only be written to once; all subsequent writes are discarded. Both bytes of this register should be initialized by the TVP4010 BIOS after a reset.

Table 2-22. Subsystem ID Register

| NAME       | DESCRIPTION  |  |

|------------|--------------|--|

| Bits 16-31 | Subsystem ID |  |

## 2.11.19 Expansion ROM Base Address Register (CFGRomAddr) (Region: Configuration, Index: 0x30, Access: R/W, Default: 0x00000000)

The expansion ROM base register is the offset address for the expansion ROM. The ROM is in memory space.

Table 2-23. Expansion ROM Base Address Register

| NAME       | DESCRIPTION                                                                                           |                                    |

|------------|-------------------------------------------------------------------------------------------------------|------------------------------------|

| Bit 0      | Access enable                                                                                         | 0=Expansion ROM accesses disabled. |

| DIL U      | Access enable                                                                                         | 1=Expansion ROM accesses enabled.  |

| Bit 1      | Reserved (read only). PCI reserved register bits.                                                     | 0x000                              |

| Bits 11–15 | Size indication (read only). Indicates that the control rgisters must be mapped into 64 KBytes.  0x00 |                                    |

| Bits 16-31 | Base offset loaded at boot time to set offset of the expansion ROM.                                   |                                    |

2.11.20 Interrupt Line Register (CFGIntLine) (Region: Configuration, Index: 0x3C, Access: R/W, Default: 0x00)

The interrupt line register is an 8-bit register used to communicate interrupt line routing information.

Table 2-24. Interrupt Line Register

| NAME     | DESCRIPTION    |  |

|----------|----------------|--|

| Bits 0-7 | Interrupt line |  |

2.11.21 Interrupt Pin Register (CFGIntPin) (Region: Configuration, Index: 0x3D, Access: R, Default: 0x01)

The interrupt pin register specifies which line the TVP4010 uses. The TVP4010 uses interrupt pin INTAN.