TEXAS INSTRUMENTS

F Logic (SN54/74F)

Data Book

# F Logic (SN54/74F)

1994 1994

Data Book

| General Information | 1 |

|---------------------|---|

| Data Sheets         | 2 |

| Application Report  | 3 |

| Mechanical Data     | 4 |

# F Logic Data Book (SN54/74F)

### IMPORTANT NOTICE

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of TI products in such applications is understood to be fully at the risk of the customer using TI devices or systems.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

Printed in the U.S.A.

### INTRODUCTION

In this volume, Texas Instruments presents technical information on the SN54/74F TTL logic family. The combination of the SN54/74F family with other Texas Instruments advanced families of TTL integrated circuits, Advanced Low-Power Schottky† (ALS) and Advances Schottky (AS), offers the industry the broadest spectrum of advanced bipolar logic products available from any supplier. In addition, the SN54/74F TTL logic family provides the system designer with a pin-for-pin compatible alternate source for SN54/74F devices in standard 300-mil plastic dual-in-line packages (DIPs) along with plastic small-outline (SO) packages, ceramic chip carriers, and ceramic DIPs. Texas Instruments offers all of the above packages with the service levels, quality, and reliability that users have come to expect in a logic family.

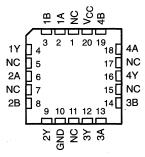

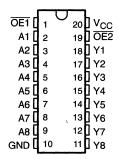

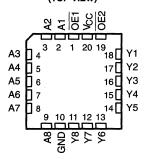

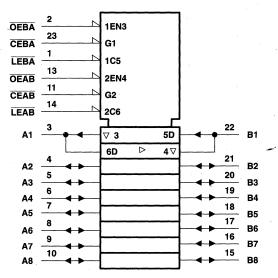

The SN54/74F TTL data sheets have been configured for ease of use. They stand alone and require a minimum of reference to other sections for supporting information. Each data sheet has complete absolute maximum ratings, recommended operating conditions, timing requirements (if applicable), and electrical characteristics. The input/output loading and fanout characteristics of each circuit are specified in terms of actual load-current value in amperes. Pinouts are specified using Texas Instruments TTL name conventions.

The following definitions are for the system design engineer who prefers to use unit loads. One unit load in the high state is defined to be 20  $\mu$ A. One unit load in the low state is defined to be 0.6 mA.

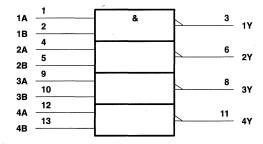

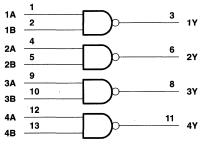

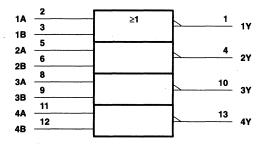

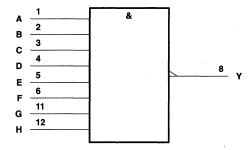

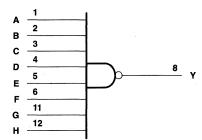

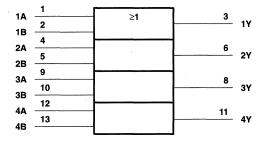

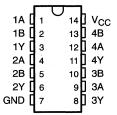

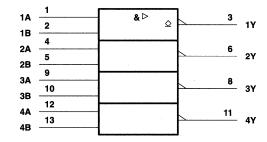

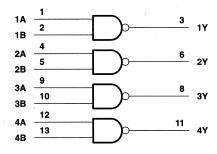

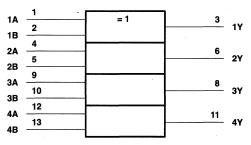

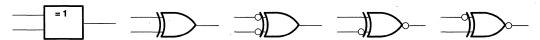

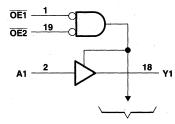

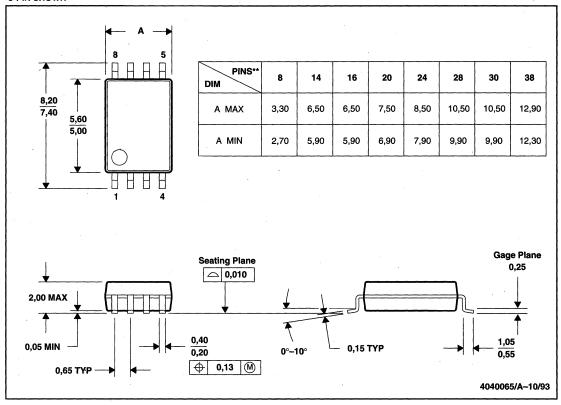

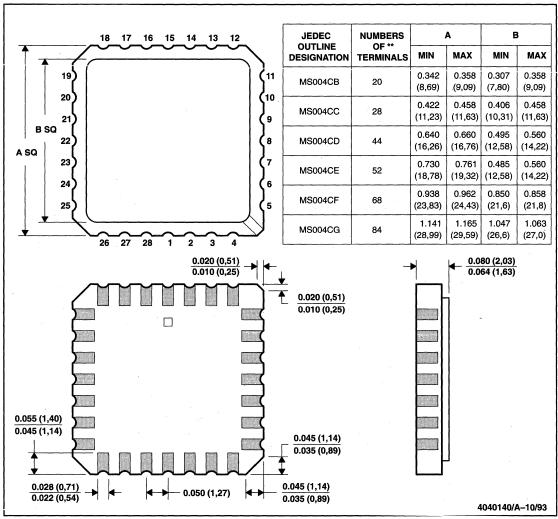

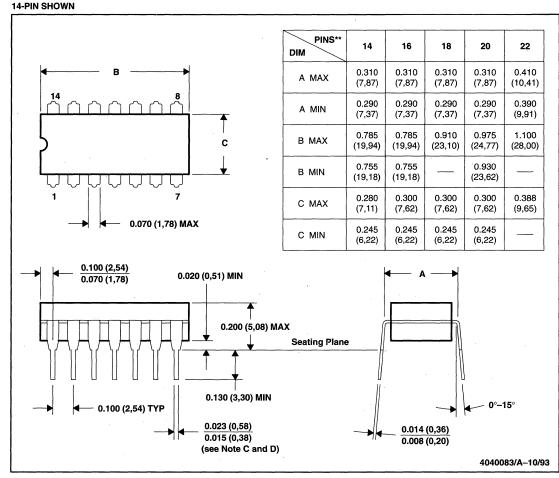

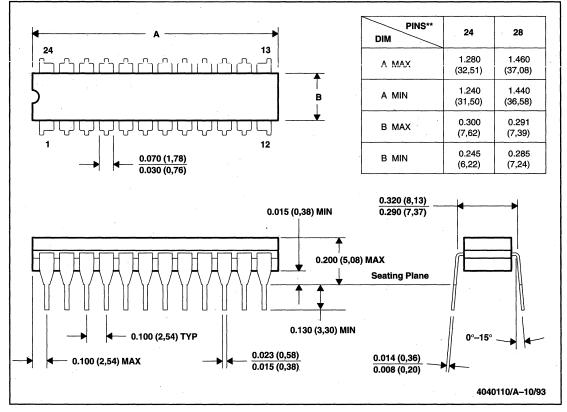

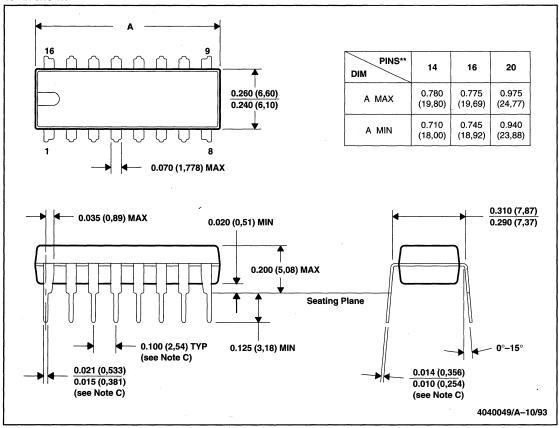

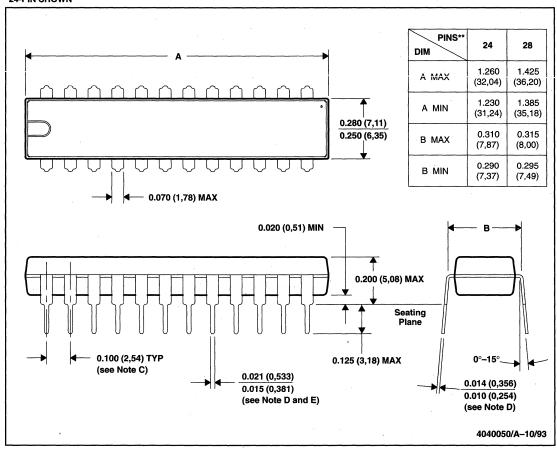

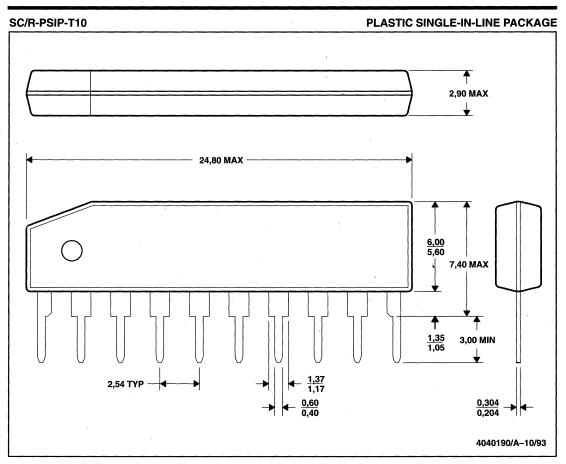

Logic symbols prepared in accordance with IEEE and IEC standards, logic diagrams, and pinout assignments are provided for all SN54/74F TTL devices. The logic diagrams are provided for the understanding of the logic operation of the device and should not be used to estimate propagation delays. Package dimensions given in the mechanical data section of this book are, with one exception, in inches with metric measurements in parentheses. This is to simplify board layout for designers involved in metric conversion and new designs.

In addition to providing pin-compatible alternate sources to common SN54/74F devices, Texas Instruments has also expanded the family to include new functions and packages. With these new solutions, the system designer has attractive options for new designs and/or upgrades to existing designs.

The SN54/74F240, '244, '245, '373, '374, and '543 functions are now available in standard packages and fine-pitch, EIAJ standard shrink small-outline packages (SSOP) with 0.65-mm pitch for board-area-conscious designs.

The Texas Instruments SN54/74F TTL logic family offers several new logic devices. Included among the new functions are:

| ′F520 | 8-bit identity comparator with input pullup resistors and open-collector outputs |

|-------|----------------------------------------------------------------------------------|

| ′F621 | Open-collector octal bus transceiver                                             |

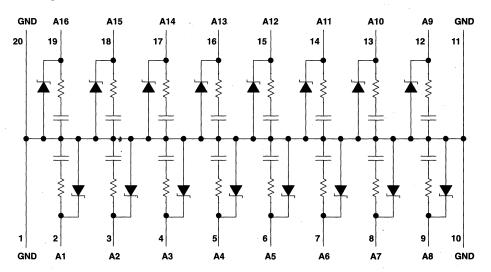

'F1056 8-bit enhanced single diode bus-termination array

All devices offered can be characterized into distinct logic functions that address several different applications areas. The following functional group table summarizes these groups and lists specific application areas that the functions address.

Complete technical data for any TI Advanced System Logic product is available from the nearest TI field sales office, local authorized TI distributor, or directly by calling the Advanced System Logic hotline at (214) 997-5202.

# **FUNCTIONAL GROUPS**

| FUNCTION                    | APPLICATIONS                                                                             |  |  |  |  |  |  |  |

|-----------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                             | Synchronous dividers and multipliers                                                     |  |  |  |  |  |  |  |

|                             | Timing circuits and state-machine sequencers                                             |  |  |  |  |  |  |  |

| Dinam/Dasada Carretara      | Pulse and sync generation                                                                |  |  |  |  |  |  |  |

| Binary/Decade Counters      | Code-conversion circuits                                                                 |  |  |  |  |  |  |  |

|                             | Analog-to-digital and digital-to-analog conversion circuits                              |  |  |  |  |  |  |  |

|                             | Modulo-n event counters and rate multipliers                                             |  |  |  |  |  |  |  |

|                             | Memory, board, processor, and component-enable generation                                |  |  |  |  |  |  |  |

| •                           | Minterm generation and data-flow control                                                 |  |  |  |  |  |  |  |

| Decoders                    | Clock-phase splitter and decoder trees                                                   |  |  |  |  |  |  |  |

|                             | Demultiplexing for clock distribution and scanning switch encoders                       |  |  |  |  |  |  |  |

|                             | Program counters and digital display systems                                             |  |  |  |  |  |  |  |

|                             | Extra register bits (e.g., guard bits and carry bits)                                    |  |  |  |  |  |  |  |

| Dual Elia Elana             | Synchronizing asynchronous inputs, interrupts, and control signals                       |  |  |  |  |  |  |  |

| ual Flip-Flops              | Finite or algorithmic state machine state bits                                           |  |  |  |  |  |  |  |

|                             | Customized modulo-n event counters                                                       |  |  |  |  |  |  |  |

| Gates                       | Combinational logic                                                                      |  |  |  |  |  |  |  |

|                             | Peripheral and board enables, address decodes, and cache-tag comparisons                 |  |  |  |  |  |  |  |

| Identity Comparators        | Page-memory boundary detection, page-fault detection, and error detection and correction |  |  |  |  |  |  |  |

|                             | Implementing combinational logic (function) tables                                       |  |  |  |  |  |  |  |

| Multiplexers/Demultiplexers | Data-flow-control and parallel-to-serial converters                                      |  |  |  |  |  |  |  |

| ,                           | Multiplexing trees, asynchronous shifting, and sorting                                   |  |  |  |  |  |  |  |

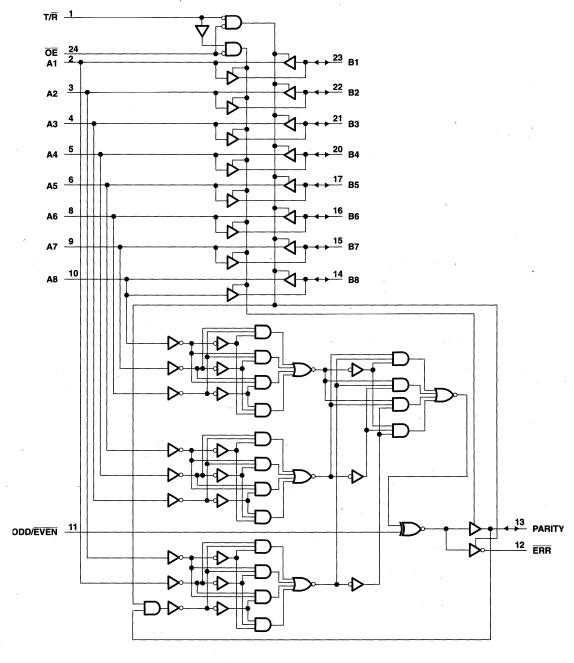

| Octal Buffers/Transceivers  | Error-detection and correction circuits                                                  |  |  |  |  |  |  |  |

| Octal Bullers/ Hariscelvers | Hamming code generation                                                                  |  |  |  |  |  |  |  |

|                             | Bus-interface, pipeline registers, and customized shift registers                        |  |  |  |  |  |  |  |

| Octal Flip-Flops            | Ring counters, Johnson counters, pattern generators, and custom modulo-n event counters  |  |  |  |  |  |  |  |

|                             | Synchronizing asynchronous inputs, interrupts, and control signals                       |  |  |  |  |  |  |  |

|                             | Serial-to-parallel conversion or parallel-to-serial conversion                           |  |  |  |  |  |  |  |

|                             | Clock-phase generation, custom counters, and random-number generators                    |  |  |  |  |  |  |  |

| Shifters/Shift Registers    | Pipeline registers, accumulators, and digital filters                                    |  |  |  |  |  |  |  |

|                             | On-board diagnostics and multiply and divide by 2 <sup>n</sup>                           |  |  |  |  |  |  |  |

|                             | CPU design and array processors                                                          |  |  |  |  |  |  |  |

### PRODUCT STAGE STATEMENTS

Product stage statements are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

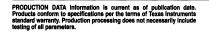

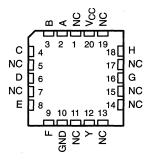

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

viii

| General Information | 1 |

|---------------------|---|

| Data Sheets         | 2 |

| Application Report  | 3 |

| Mechanical Data     | 4 |

# **ALPHANUMERIC INDEX**

| DEVICE    |           | PAGE    | DEVICE      | , PA         | ١GE  |

|-----------|-----------|---------|-------------|--------------|------|

| SN54F00   | SN74F00   | . 2–3   | SN54F240    | SN74F240 2–  | -15  |

| SN54F02   | SN74F02   | . 2-7   | SN54F241    | SN74F241 2-  | -16  |

| SN54F04   | SN74F04   | 2-11    | SN54F242    | SN74F242 2-  | -16  |

|           | SN74F08   | 2-15    | SN54F243    | SN74F243 2-  | -169 |

| SN54F10   | SN74F10   | 2-17    | SN54F244    | SN74F244 2-  | -173 |

| SN54F11   | SN74F11   | 2-21    | SN54F245    | SN74F245 2-  | -17  |

| SN54F20   | SN74F20   | 2-25    | SN54F251B   | SN74F251B 2- | -18  |

| SN54F21   | SN74F21   | 2-29    | SN54F253    | SN74F253 2-  | -18  |

| SN54F27   | SN74F27   | 2-33    | SN54F257    | SN74F257 2-  | -19  |

| SN54F30   | SN74F30   | 2-37    | SN54F258    | SN74F258 2-  | -19  |

| SN54F32   | SN74F32   | 2-41    |             | SN74F260 2-  | -20  |

| SN54F38   | SN74F38   | 2-45    | SN54F280B   | SN74F280B 2- | -20  |

| SN54F51   | SN74F51   | 2-49    | SN54F283    | SN74F283 2-  | -20  |

| SN54F74   | SN74F74   | 2-53    | SN54F299    | SN74F299 2-  | -21  |

| SN54F86   | SN74F86   | . 2–57  |             | SN74F323 2-  | -21  |

| SN54F109  | SN74F109  | 2-61    | SN54F373    | SN74F373 2-  | -22  |

|           | SN74F112  | 2-65    | SN54F374    | SN74F374 2-  | -22  |

|           | SN74F125  | 2-69    |             | SN74F377A 2- | -23  |

|           | SN74F126  | 2-73    |             | SN74F378     | -23  |

| SN54F138  | SN74F138  | . 2–77  |             | SN74F382 2-  | -23  |

| SN54F151B | SN74F151B | . 2–81  | SN54F520    | SN74F520 2-  | -24  |

| SN54F153  | SN74F153  | . 2–85  | SN54F521    | SN74F521     | -24  |

| SN54F157A | SN74F157A | . 2–91  | SN54F534A   | SN74F534A 2- | -25  |

| SN54F158A | SN74F158A | . 2–95  | SN54F541    | SN74F541 2-  | -25  |

|           | SN74F161A | . 2–99  |             | SN74F543 2-  | -26  |

|           | SN74F163A | 2-107   | SN54F573    | SN74F573 2-  | -26  |

| SN54F166A | SN74F166A | 2-115   |             | SN74F574     | -27  |

|           | SN74F168  | 2-121   | SN54F621    | SN74F621     | -27  |

|           | SN74F169  | 2-129   | SN54F623    | SN74F623 2-  | -27  |

|           | SN74F174A | . 2–137 |             | SN74F657 2–  | -28  |

| SN54F175  | SN74F175  |         |             | SN74F1016    |      |

|           | SN74F190A |         |             | SN74F1018    |      |

| •         | SN74F193A |         |             | SN74F1056    |      |

|           |           |         | SN54F2244 . | . SN74F2244  |      |

### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

### operating conditions and characteristics (in sequence by letter symbols)

C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device

Co Output capacitance

The internal capacitance at an output of the device

C<sub>pd</sub> Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):  $P_D = C_{pd} \ V_{CC}^2 \ f + I_{CC} \ V_{CC}$ .

f<sub>max</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

I<sub>CC</sub> Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit

∆I<sub>CC</sub> Supply current change

The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or  $V_{CC}$

I<sub>CEX</sub> Output high leakage current

The maximum leakage current into the collector of the pulldown output transistor when the output is high and the output forcing condition  $V_O = 5.5 \text{ V}$ .

I<sub>I(hold)</sub> Input hold current

Input current that holds the input at the previous state when the driving device goes to a high-impedance state

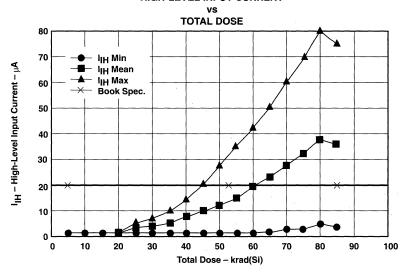

I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input

I<sub>IL</sub> Low-level input current

The current into\* an input when a low-level voltage is applied to that input

Input/output power-off leakage current

The maximum leakage current into/out of the input/output transistors when forcing the input/output to 4.5 V and  $V_{\rm CC}$  = 0 V

IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

I<sub>OL</sub> Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

<sup>\*</sup>Current out of a terminal is given as a negative value

## **GLOSSARY** SYMBOLS, TERMS, AND DEFINITIONS

### Off-state (high-impedance-state) output current (of a 3-state output) loz

The current flowing into\* an output having 3-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output

### Access time ta

tc

The time interval between the application of a specified input pulse and the availability of valid signals at an output

### Clock cycle time

Clock cycle time is 1/fmax.

### Disable time (of a 3-state or open-collector output) t<sub>dis</sub>

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from either of the defined active levels (high or low) to a high-impedance (off) state

NOTE: For 3-state outputs,  $t_{dis} = t_{PHZ}$  or  $t_{PLZ}$ . Open-collector outputs will change only if they are low at the time of disabling, so t<sub>dis</sub> = t<sub>PLH</sub>.

### Enable time (of a 3-state or open-collector output) t<sub>en</sub>

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from a high-impedance (off) state to either of the defined active levels (high or

NOTE: In the case of memories, this is the access time from an enable input (e.g.,  $\overline{OE}$ ). For 3-state outputs,  $t_{en} = t_{PZH}$  or  $t_{PZL}$ . Open-collector outputs will change only if they are responding to data that would cause the output to go low, so ten = tPHL.

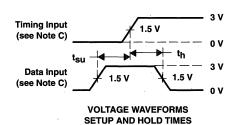

### t<sub>h</sub> **Hold time**

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal

NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected.

2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is to be expected.

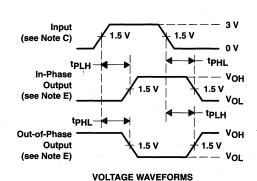

### Propagation delay time tpd

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level (tpd = tpHL or tpLH)

### Propagation delay time, high-to-low level output <sup>t</sup>PHL

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level

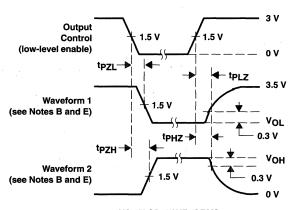

### Disable time (of a 3-state output) from high level t<sub>PHZ</sub>

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined high level to the high-impedance (off) state

### **t**PLH Propagation delay time, low-to-high level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level

\*Current out of a terminal is given as a negative value.

### t<sub>PLZ</sub> Disable time (of a 3-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined low level to the high-impedance (off) state

### tpzH Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined high level

### tpZL Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined low level

### t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal

- NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value, in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

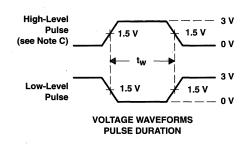

### tw Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform

### V<sub>IH</sub> High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is to be expected.

### V<sub>IL</sub> Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is to be expected.

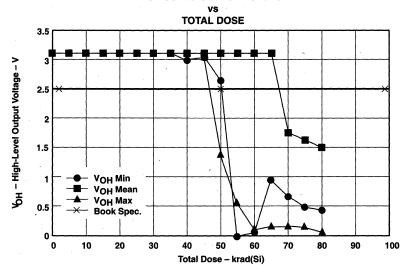

### V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output

### V<sub>OI</sub> Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output

### V<sub>IT+</sub> Positive-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{IT-}$

### V<sub>IT</sub>\_ Negative-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage, V<sub>IT+</sub>

### **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets:

H = high level (steady state)L = low level (steady state)

↑ = transition from low to high level ↓ = transition from high to low level

= value/level or resulting value/level is routed to indicated destination

= value/level is re-entered

X = irrelevant (any input, including transitions)

Z = off (high-impedance) state of a 3-state output

a . . . h = the level of steady-state inputs A through H respectively

Q<sub>0</sub> = level of Q before the indicated steady-state input conditions were established

$\overline{Q}_0$  = complement of  $Q_0$  or level of  $\overline{Q}$  before the indicated steady-state input

conditions were established

$Q_n$  = level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

\_\_\_ = one high-level pulse \_\_ = one low-level pulse

Toggle = each output changes to the complement of its previous level on each active

transition indicated by  $\downarrow$  or  $\uparrow$

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\neg \neg \neg \neg$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

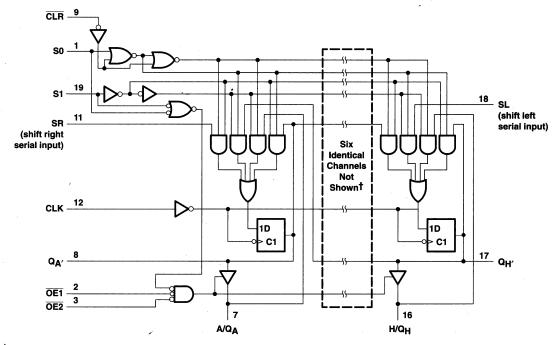

Among the most complex function tables are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

**FUNCTION TABLE**

|       |      |     |          | INPUTS |       |   |      |      |   |                 | OUT      | PUTS              |          |

|-------|------|-----|----------|--------|-------|---|------|------|---|-----------------|----------|-------------------|----------|

| CLEAR | MODE |     | СГОСК    | SEI    | RIAL  |   | PARA | LLEL |   |                 |          |                   | <b>~</b> |

| CLEAR | S1   | S0  | CLUCK    | LEFT   | RIGHT | Α | В    | С    | D | QA              | QB       | СС                | QD       |

| L     | Х    | Х   | Х        | Х      | Х     | Х | Х    | Х    | Х | L               | L        | L                 | г        |

| н     | Х    | Х   | L        | х      | X     | Х | Х    | Х    | Χ | Q <sub>A0</sub> | $Q_{B0}$ | $Q_{C0}$          | $Q_{D0}$ |

| н     | Н    | Н   | 1        | х      | X     | а | b    | С    | d | а               | b        | C                 | d        |

| н     | L    | Н   | 1        | х      | Н     | н | Н    | Н    | Н | Н               | $Q_{An}$ | $Q_{Bn}$          | $Q_{Cn}$ |

| н     | L    | н   | 1        | х      | L     | L | L    | L    | L | L               | $Q_{An}$ | $Q_{Bn}$          | $Q_{Cn}$ |

| н     | Н    | L   | <b>1</b> | Н      | Х     | Х | Х    | Х    | Χ | Q <sub>Bn</sub> | $Q_{Cn}$ | $Q_{Dn}$          | н        |

| н     | Н    | L   | 1        | L      | X     | Х | Χ    | Х    | Х | Q <sub>Bn</sub> | $Q_{Cn}$ | $\mathtt{Q}_{Dn}$ | L        |

| Н     | L    | . L | Х        | Х      | Х     | Х | Х    | Х    | Х | Q <sub>A0</sub> | $Q_{B0}$ | $Q_{C0}$          | $Q_{D0}$ |

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock.

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output  $Q_A$ , data entered at B will be at  $Q_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$ , respectively, and the data previously at  $Q_D$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is now at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  are now at  $Q_B$  and  $Q_C$ , respectively, and the data previously at  $Q_A$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

The function table functional tests do not reflect all possible combinations or sequential modes.

### **FUNCTIONAL TESTING**

Functional testing is performed on all logic devices by the execution of a set of functional patterns located in the test program. These patterns are used to guarantee conformance to the truth table and simulate operation in an actual system.

Problems are frequently discovered in functional testing when  $V_{IH(min)}$  and  $V_{IL(max)}$  are used as the input conditions to exercise the function table.  $V_{IH(min)}$  and  $V_{IL(max)}$  are input conditions that are used in parametric testing. These problems occur because of the noise that is present on the test heads of automated test equipment with long cables. Parametric tests such as  $V_{OH}$ ,  $V_{OL}$ ,  $I_{OZH}$ , or  $I_{OZL}$  are done at a relatively slow repetition rate, and any noise that is present on the test head will have settled out before the outputs are measured. However, during functional testing the outputs are sensed much sooner, before the noise on the inputs has settled out and the output has reached its final and correct state.

The functional patterns that are applied to the device under test are 0-V to 3-V transitions as defined in the parameter measurement information section. The use of  $V_{IH}=3$  V and  $V_{IL}=0$  V during functional testing does not imply that the devices are noise sensitive since the environment that the device sees on a system's printed circuit board is much less severe than a noisy production test environment. Therefore,  $V_{IH(min)}$  and  $V_{IL(max)}$  should not be used to test functionality of SN54/74F devices.

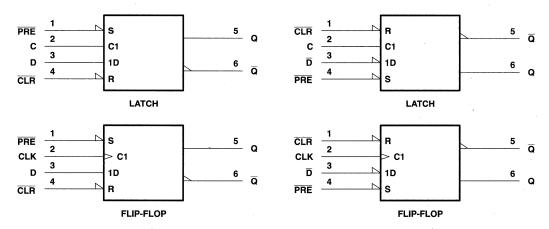

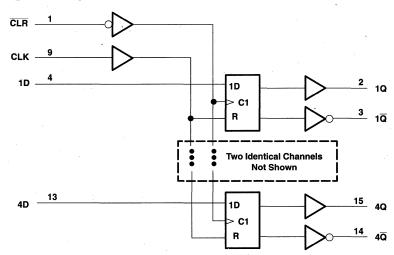

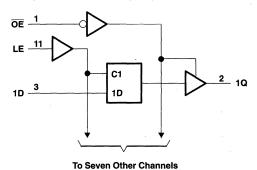

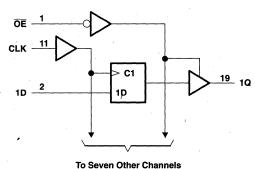

### D FLIP-FLOP AND LATCH SIGNAL CONVENTIONS

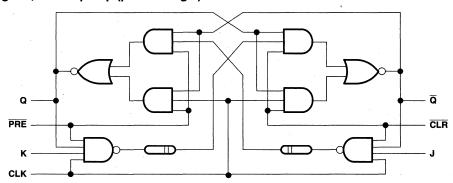

It is normal TI practice to name the outputs and other inputs of a D-type flip-flop or latch and to draw its logic symbol based on the assumption of true data (D) inputs. Outputs that produce data in phase with the data inputs are called Q and those producing complementary data are called  $\overline{Q}$ . An input that causes a Q output to go high or a  $\overline{Q}$  output to go low is called preset (PRE). An input that causes a  $\overline{Q}$  output to go high or a Q output to go low is called clear (CLR). Bars are used over these pin names (PRE and CLR) if they are active low.

The devices on several data sheets are second-source designs, and the pin name conventions used by the original manufacturers have been retained. That makes it necessary to designate the inputs and outputs of the inverting circuits  $\overline{D}$  and Q.

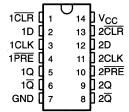

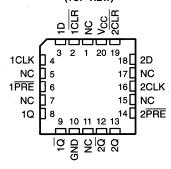

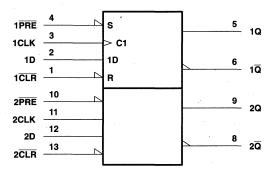

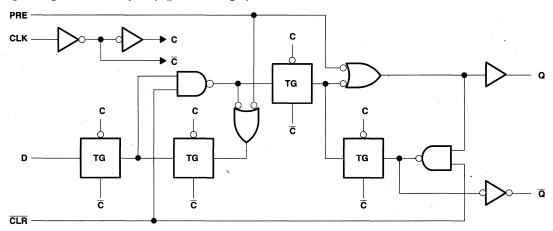

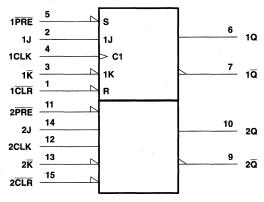

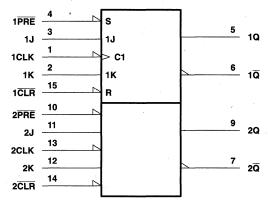

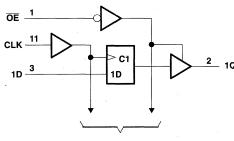

In some applications, it may be advantageous to redesignate the data input from D to  $\overline{D}$  or vice versa. In that case, all the other inputs and outputs should be renamed as shown below. Also shown are corresponding changes in the graphical symbols. Arbitrary pin numbers are shown.

The figures show that when Q and  $\overline{Q}$  exchange names, the preset and clear pins also exchange names. The polarity indicators ( $\searrow$ ) on  $\overline{PRE}$  and  $\overline{CLR}$  remain, as these inputs are still active low, but the presence or absence of the polarity indicator changes at D (or  $\overline{D}$ ), Q, and  $\overline{Q}$ . Pin 5 (Q or  $\overline{Q}$ ) is still in phase with the data input (D or  $\overline{D}$ ); their active levels change together.

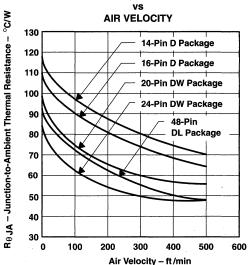

### THERMAL INFORMATION

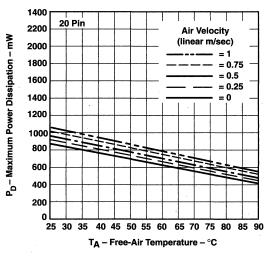

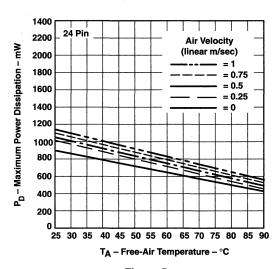

In digital system design, consideration must be given to thermal management of components. The small size of the small-outline package makes this even more critical. Figure 1 shows the thermal resistance of these packages for various rates of air flow.

The thermal resistances in Figure 1 can be used to approximate typical and maximum virtual junction temperatures for the SN54/74F family. In general, the junction temperature for any device can be calculated using equation 1.

$$T_{J} = R_{\theta JA}[(V_{CC} \times I_{CC}) + (N \times I_{OL} \times V_{OL})] + T_{A}$$

(1)

### where:

T<sub>J</sub> = virtual junction temperature

$R_{\theta JA}$  = thermal resistance, junction to free air  $V_{CC}$  = supply voltage (5 V for typical, 5.5 V for

maximum)

I<sub>CC</sub> = supply current (specified on device data sheet)

$egin{array}{lll} N & = & \text{number of outputs} \\ I_{OL} & = & \text{low-level output current} \\ V_{OL} & = & \text{low-level output voltage} \\ T_{\Delta} & = & \text{free-air temperature} \\ \end{array}$

### JUNCTION-TO-AMBIENT THERMAL RESISTANCE

Figure 1

Typical junction temperature can be calculated using equation 1 directly with typical values of  $I_{CC}$  taken from the data sheets and  $V_{CC} = 5$  V. To calculate maximum junction temperature, it is necessary to take into account the spread of  $I_{CC}$  values for a population. Due to the specification practices that have been followed, it is useful to use slightly different calculations for SN54F and SN74F devices.

Maximum junction temperature for SN54F parts can be calculated using equation 1 with  $I_{CC}$  being the maximum value specified on the data sheet and  $V_{CC}$  = 5.5 V. In fact,  $I_{CC}$  for series 54 devices at the temperature extremes of –55°C to 125°C will be higher than for series 74 devices at the temperature extremes of 0°C to 70°C.

The SN54/74F family data sheets give a single maximum value for  $I_{CC}$ . If that value is used to calculate maximum junction temperature for SN74F devices, an unrealistically high value will result. Instead, equation 2 can be used. This uses the factor 1.31 to scale the typical value of  $I_{CC}$  up to a practical maximum value for process variations and thermal effects.

Thus, for SN74F devices:

$$T_{J(max)} = R_{\theta JA}[(5.5 \times 1.31 \times I_{CC(tvp)}) + N \times I_{OL} \times V_{OL})] + T_{A}$$

(2)

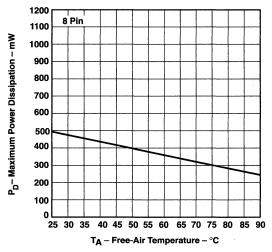

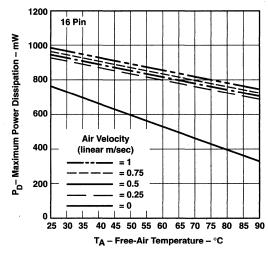

### DERATING CURVES FOR 210-MIL SHRINK SMALL-OUTLINE PACKAGE (DB)

Figure 2

Figure 4

Figure 5

The following tables outline the logic functions Texas Instruments offers in a variety of technologies. The tables are organized by function type and list all available or planned options of that function. The technology columns identify the appropriate family and a particular data book where more information can be found. The applicable literature number, composed of either seven or eight alphanumeric characters, can be found at the lower right-hand corner on the back cover of each publication.

List of additional Advanced System Logic data books:

| ABT Devices                     | Advanced BiCMOS Technology                 | SCBD002A |

|---------------------------------|--------------------------------------------|----------|

| AC and ACT Devices              | Advanced CMOS Logic Data Book              | SCAD001C |

| Advanced Logic Devices          | Advanced Logic and Bus-Interface Data Book | SCYD001  |

| ALS and AS Devices†             | ALS/AS Logic Data Book                     | SDAD001B |

| BCT Devices†                    | BiCMOS Bus-Interface Logic Data Book       | SCBD001A |

| FIFO Devices                    | High-Performance FIFO Memories Data Book   | SCAD003A |

| HC and HCT Devices              | High-Speed CMOS Logic Data Book            | SCLD001C |

| LV, LVC, LVT, and ALVC Devices† | Low-Voltage Logic Data Book                | SCBD003  |

| SCOPE™ Devices                  | SCOPE™ Product Information                 | SSYV001  |

| Std TTL, LS, and S Devices      | TTL Logic Data Book                        | SDLD001A |

<sup>†</sup> Updated data book planned for this technology

### Contents

| · ·                                                                 | Page          |

|---------------------------------------------------------------------|---------------|

| GATES 1                                                             | I–17          |

| Positive-NAND Gates 1                                               | 1–17          |

| Positive-AND Gates 1                                                | 1–17          |

| Positive-OR/NOR Gates 1                                             | 1–18          |

| OR/NOR Gates                                                        | 1–18          |

| AND-OR Gates 1                                                      | 1–18          |

| INVERTING/NONINVERTING BUFFERS 1                                    | 1–19          |

| Hex Inverters/Noninverters 1                                        | 1–19          |

| BUFFERS/DRIVERS AND BUS TRANSCEIVERS 1                              | I <b>–2</b> 0 |

| Buffers/Drivers1                                                    | 1–20          |

| Universal Bus Transceivers (UBT™)/Universal Bus Exchangers (UBE™) 1 | 1–21          |

| Bus Transceivers 1                                                  | 1–22          |

| MOS Memory Drivers/Transceivers 1                                   | 1–25          |

| TESTABILITY BUS-INTERFACE CIRCUITS                                  | 1–26          |

| JTAG/IEEE 1149.1 Testability Circuits                               | 1-26          |

# **FUNCTIONAL INDEX**

| Contents (continued)                                              |      |

|-------------------------------------------------------------------|------|

|                                                                   | Page |

| FLIP-FLOPS AND LATCHES                                            |      |

| Flip-Flops                                                        | 1–27 |

| Latches                                                           | 1–29 |

| REGISTERS                                                         | 1–31 |

| Shift Registers                                                   | 1–31 |

| Register Files                                                    | 1–31 |

| COUNTERS                                                          | 1–32 |

| Synchronous Counters – Positive Edge Triggered                    | 1–32 |

| Asynchronous Counters (Ripple Clock) - Negative Edge Triggered    | 1–32 |

| 8-Bit Binary Counters With Registers                              | 1–32 |

| DECODERS, ENCODERS, DATA SELECTORS/MULTIPLEXERS                   | 1–33 |

| Encoders/Data Selectors/Multiplexers                              | 1–33 |

| Decoders/Demultiplexers                                           | 1–34 |

| Shifters                                                          | 1–34 |

| COMPARATORS AND PARITY GENERATORS/CHECKERS                        | 1–35 |

| Comparators                                                       | 1–35 |

| Address Comparators                                               | 1–35 |

| Parity Generators/Checkers                                        | 1–35 |

| BUS SWITCHES AND 5-V/3-V VOLTAGE TRANSLATORS                      | 1–36 |

| Crossbar Technology (CBT)                                         | 1–36 |

| ARITHMETIC CIRCUITS                                               |      |

| Parallel Binary Adders                                            | 1–36 |

| Accumulators, Arithmetic Logic Units, Look-Ahead Carry Generators |      |

| FIFO MEMORIES                                                     |      |

| First-In, First-Out Memories (FIFOs)                              | 1–37 |

| CLOCK DISTRIBUTION CIRCUITS                                       |      |

| Clock Distribution Circuits (CDC)                                 |      |

| ECL TRANSLATORS                                                   |      |

| FOL to TTL on TTL to FOL Transplaters                             | 4 00 |

# **GATES**

# **Positive-NAND Gates**

| DESCRIPTION    | OUTDUT | TYPE   |     |    |   |    | TE  | CHNOL | OGY |     |     |    |     |

|----------------|--------|--------|-----|----|---|----|-----|-------|-----|-----|-----|----|-----|

| DESCRIPTION    | OUTPUT | ITPE   | ALS | AS | F | нс | нст | AC    | ACT | вст | ABT | LV | LVC |

| 0.1            |        | ′30    | ~   | ~  | ~ |    |     |       |     |     |     |    |     |

| 8-Input        |        | ′11030 |     |    |   |    |     | ~     | ~   |     |     |    |     |

| 13-Input       |        | ′133   | ~   |    |   | ~  |     |       | ·   |     |     |    |     |

| Dual 2-Input   |        | ′8003  | ~   |    |   |    |     |       |     |     |     |    |     |

|                |        | ′20    | V   | ~  | ~ | ~  |     |       |     |     |     |    |     |

| Dual 4-Input   |        | ′40    | ~   |    |   |    |     |       |     |     |     |    |     |

|                |        | ′11020 |     |    |   |    |     | ~     | ~   |     |     |    |     |

|                |        | ′10    | ~   | ~  | ~ | ~  |     |       |     |     |     |    | +   |

| Triple 3-Input |        | ′1010  | ~   |    |   |    |     |       |     |     |     |    |     |

|                |        | ′11010 |     |    |   |    |     | ~     | 1   |     |     |    |     |

|                |        | ′00    | ~   | ~  | ~ | ~  | ~   |       |     |     |     | ~  | +   |

|                |        | ′11000 |     |    |   |    |     | ~     | ~   |     |     |    |     |

|                |        | ′37    | ~   |    |   |    |     |       |     |     |     |    |     |

| Quad 2-Input   | ОС     | ′38    | ~   |    | ~ |    | ,   |       |     |     |     |    |     |

|                |        | ′132   |     |    |   | ~  |     |       |     |     |     |    |     |

|                |        | ′11132 |     |    |   |    |     | ~     | ~   |     |     |    |     |

|                |        | ′1000  |     | V  |   |    |     |       |     |     |     |    |     |

| Hex 2-Input    |        | ′804   | ~   | ~  |   |    |     |       |     |     |     |    |     |

| Ouad 2 Input   | ос     | ′01    | ~   |    |   | ~  |     |       |     |     |     |    |     |

| Quad 2-Input   |        | ′03    | ~   |    |   | V  |     |       |     |     |     |    |     |

### **Positive-AND Gates**

| DESCRIPTION    | CUITDUIT | TVDE   | TECHNOLOGY |    |   |    |     |    |     |     |     |    |     |  |

|----------------|----------|--------|------------|----|---|----|-----|----|-----|-----|-----|----|-----|--|

| DESCRIPTION    | OUTPUT   | TYPE   | ALS        | AS | F | нс | нст | AC | ACT | ВСТ | ABT | LV | LVC |  |

| Quad 2-Input   | ос       | ′09    | ~          |    |   | ~  |     |    |     |     |     |    |     |  |

|                |          | ′7001  |            |    |   | ~  |     |    |     |     |     |    |     |  |

| Dual 4-Input   |          | ′21    | ~          | ~  | ~ | ~  |     |    |     |     |     |    |     |  |

|                |          | ′11021 |            |    |   |    |     | 1  | ~   |     |     |    |     |  |

| T.:-!- 0 !     |          | ′11    | ~          | ~  | ~ | ~  |     |    |     |     |     |    |     |  |

| Triple 3-Input |          | ′11011 |            |    |   |    |     | ~  | ~   |     |     |    |     |  |

|                |          | ′08    | ~          | ~  | ~ | ~  | ~   |    |     |     |     | ~  | +   |  |

| Quad 2-Input   |          | ′1008  |            | ~  |   |    |     |    |     |     |     |    |     |  |

|                |          | ′11008 |            |    |   |    |     | V  | V   |     |     |    |     |  |

| Hex 2-Input    |          | ′808   |            | ~  |   |    |     |    |     |     |     |    |     |  |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

# **FUNCTIONAL INDEX**

### Positive-OR/NOR Gates

| DECODIBEION     | OUTDUT | TVDE   | TECHNOLOGY |    |   |    |     |    |     |     |     |    |     |  |

|-----------------|--------|--------|------------|----|---|----|-----|----|-----|-----|-----|----|-----|--|

| DESCRIPTION     | OUTPUT | TYPE   | ALS        | AS | F | НС | нст | AC | ACT | вст | ABT | LV | LVC |  |

| Triple 3-Input  |        | ′4075  |            |    |   | ~  |     |    |     |     |     |    |     |  |

| Quad 2-Input    |        | ′32    | ~          | ~  | ~ | ~  | ~   |    |     |     |     | ~  | +   |  |

|                 |        | ′1032  |            | ~  |   |    |     |    |     |     |     |    |     |  |

|                 |        | ′11032 |            |    |   |    |     | ~  | ~   |     |     |    |     |  |

|                 |        | ′7032  |            |    |   | ~  |     |    |     |     |     |    |     |  |

| Hex 2-Input     |        | ′832   | ~          | ~  |   | ~  |     |    |     |     |     |    |     |  |

| Dual 5-Input    |        | ′260   |            |    | ~ |    |     |    |     |     |     |    |     |  |

| Trials Olement  |        | ′27    | ~          | ~  | ~ | ~  |     |    |     |     |     |    |     |  |

| Triple 3-Input  |        | ′11027 |            |    |   |    |     | ~  | ~   |     |     |    |     |  |

|                 |        | ′02    | ~          | ~  | ~ | ~  | ~   |    |     |     |     | ~  | +   |  |

| Overal Ollerand | ОС     | ′33    | ~          |    |   |    |     |    |     |     |     | -  |     |  |

| Quad 2-Input    |        | ′7002  |            |    |   | ~  |     |    |     |     |     |    |     |  |

|                 |        | ′11002 |            |    |   |    |     | ~  | ~   |     |     |    |     |  |

| Hex 2-Input     |        | ′805   | ~          | ~  |   | ~  |     |    |     |     |     | -  |     |  |

### **OR/NOR Gates**

| DESCRIPTION                         | OUTPUT | TYPE   |     |    |   | ,  | TEC | CHNOLO | OGY |     |     |    |     |

|-------------------------------------|--------|--------|-----|----|---|----|-----|--------|-----|-----|-----|----|-----|

| DESCRIPTION                         | OUTPUT | ITPE   | ALS | AS | F | нс | нст | AC     | ACT | вст | ABT | LV | LVC |

| Quad 2-Input<br>Exclusive-OR Gates  |        | ′86    | ~   | ~  | ~ | ~  |     |        |     |     |     |    | +   |

| With Totem-Pole Outputs             |        | ′11086 |     |    |   |    |     | V      | ~   |     |     |    |     |

| Quad 2-Input<br>Exclusive-OR Gates  | ос     | ′136   | V   |    |   |    |     |        |     |     |     |    |     |

|                                     | OD     | ′266   |     |    |   | ~  |     |        |     |     |     |    |     |

| Quad 2-Input<br>Exclusive-NOR Gates |        | ′810   | ~   |    |   |    |     |        |     |     |     |    |     |

| Exolucivo (voi) datos               | ОС     | ′811   | ~   |    |   |    |     |        |     |     |     |    |     |

### **AND-OR Gates**

| DESCRIPTION                  | OUTPUT | TYPE |     |    |   | TE | CHNOLO | GY |     |     |     |

|------------------------------|--------|------|-----|----|---|----|--------|----|-----|-----|-----|

| DESCRIPTION                  | OUIPUI | ITPE | ALS | AS | F | нс | HCT    | AC | ACT | ВСТ | ABT |

| Dual 2-Wide 2-Input, 3-Input |        | ′51  |     |    | V |    |        |    |     |     |     |

<sup>✔</sup> Product available in technology indicated

<sup>+</sup> New product planned in technology indicated

### **INVERTING/NONINVERTING BUFFERS**

### **Hex Inverters/Noninverters**

| DESCRIPTION   | OUTPUT | TVDE   |     |    |              |    | TE  | CHNOL | GY  |     |     |       |     |

|---------------|--------|--------|-----|----|--------------|----|-----|-------|-----|-----|-----|-------|-----|

| DESCRIPTION   | OUIPUI | TYPE   | ALS | AS | F            | нс | нст | AC    | ACT | вст | ABT | LV    | LVC |

|               |        | ′04    | ~   | ~  | ~            | ~  | ~   |       |     |     |     | ~     | +   |

|               |        | ′U04   |     |    |              | ~  |     |       |     |     |     | ~     | +   |

|               |        | ′11004 |     |    |              |    |     | V     | ~   |     |     |       |     |

| Harrier dans  | ÓC     | ′05    | ~   |    | ************ | ~  |     |       |     |     |     |       |     |

| Hex Inverters |        | ′14    |     |    |              | ~  | 1   |       |     |     |     | ~     | +   |

|               |        | ′11014 |     |    |              |    |     | ~     | ~   |     |     |       |     |

|               |        | ′1004  | V   | ~  |              |    |     | -     |     |     |     | 10.10 |     |

|               |        | ′1005  | V   |    |              |    |     |       |     |     |     |       |     |

|               |        | ′11034 |     |    |              |    |     | ~     | ~   |     |     |       |     |

| Hex           | ОС     | ′35    | V   |    |              |    |     |       |     |     |     |       |     |

| Noninverters  |        | ′1034  | ~   | ~  |              |    |     |       |     |     |     |       |     |

|               | ОС     | ′1035  | ~   |    |              |    |     |       |     |     |     |       |     |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

### **Buffers/Drivers**

| DESCRIPTION                            | ОИТРИТ | TYPE    |                |          |         |              |          | TE | CHNOL    | OGY |          |          |     |          |          |

|----------------------------------------|--------|---------|----------------|----------|---------|--------------|----------|----|----------|-----|----------|----------|-----|----------|----------|

| DESCRIPTION                            | JUIPUI |         | ALS            | AS       | F       | нс           | нст      | AC | ACT      | вст | ABT      | LVT      | LV  | LVC      | ALVC     |

| Quad Buffers/Drivers                   | 38     | ′125    |                |          | ~       | ~            | ~        |    |          | ~   | ~        | ~        |     | +        |          |

|                                        |        | ′126    |                |          | 1       | ~            |          |    |          | ~   | ~        |          |     |          |          |

| Noninverting                           | 38     | ′365    |                |          |         | ~            |          |    |          |     |          |          |     |          |          |

| Hex Buffers/Drivers                    |        | ′367    |                |          |         | ~            |          |    |          |     |          |          |     |          |          |

| Inverting<br>Hex Buffers/Drivers       | 38     | ′368    |                |          |         | V.           |          |    |          |     |          |          | /   |          |          |

|                                        |        | ′241    | ~              | V .      | ~       | ~            | ~        |    |          | ~   | ~        |          |     |          |          |

|                                        |        | ′11241  |                |          |         |              |          | ~  | ~        |     |          |          |     |          |          |

|                                        |        | ′25241  |                |          |         |              |          |    |          |     | +        |          |     |          |          |

|                                        |        | ′244    | ~              | ~        | ~       | ~            | ~        |    |          | ~   | ~        |          | ~   | +        |          |

|                                        | 38     | ′244A   |                |          |         |              |          |    |          |     |          | ~        |     |          |          |

| Noninverting                           | -      | ′11244  |                |          |         |              |          | V  | ~        |     |          |          |     |          |          |

| Octal Buffers/Drivers                  |        | ′1244   | V              |          |         |              |          |    |          |     |          |          |     |          |          |

|                                        |        | ′25244  |                |          |         |              |          |    |          | ~   | +        |          |     |          |          |

|                                        |        | ′541    | V              |          | ~       | ~            | V        |    |          | V   | 1        |          |     | +        |          |

|                                        |        | ′757    |                | ~        |         |              |          |    |          | ~   |          |          |     |          |          |

|                                        | ос     | ′760    | V              | V        |         |              |          |    |          | ~   |          |          |     |          |          |

|                                        |        | ′25760  |                |          |         |              |          |    | <b> </b> | +   |          |          |     |          |          |

|                                        |        | ′240    | 1              | ~        | ~       | ~            | 1        |    | 1        | ~   | ~        | ~        | ~   | +        | 17       |

|                                        | · ·    | ′11240  |                |          | <b></b> | <b>†</b>     |          | 1  | 1        |     | <u> </u> |          |     |          | <u> </u> |

|                                        |        | ′1240   | ~              |          |         |              |          |    |          |     | İ        | <u> </u> |     | <b>†</b> |          |

| Inverting                              | 38     | ′25240  |                |          |         | <del> </del> | <b> </b> |    | ļ        | V   |          |          |     | 1        |          |

| Octal Buffers/Drivers                  |        | ′466    | V              |          |         | <b> </b>     |          |    | 1        |     |          |          |     | <u> </u> |          |

|                                        |        | ′540    | V              |          |         | 1            | ~        |    | <b></b>  | V   | V        |          |     | +        |          |

|                                        |        | ′756    | V              | ~        |         |              |          |    | 1        | ~   |          |          |     |          |          |

|                                        | ОС     | 763     | V              | ~        |         |              |          |    | 7        |     |          |          |     | <u> </u> |          |

| Inverting and                          | 38     | ′230    | <del>  `</del> | 1        |         | <del> </del> |          |    |          |     |          | <u> </u> |     | -        | <b>†</b> |

| Noninverting                           |        |         |                | <u> </u> |         | ļ            |          |    | ļ        |     |          |          |     | -        |          |

| Octal Buffers/Drivers                  | ос     | ′762    | ļ              | ~        |         |              |          |    | ļ        |     |          |          |     |          |          |

| Triple 4-Input<br>OR/NOR Drivers       |        | ′11802  |                |          |         |              |          |    | ~        | •   |          |          |     |          |          |

|                                        |        | ′827    |                |          | ` `     |              |          |    |          |     | ~        |          |     |          |          |

| Noninverting<br>10-Bit Buffers/Drivers | 38     | ′11827  |                |          |         |              |          | ~  | ~        |     |          |          |     |          |          |

| TO DR Dallers/Brivers                  |        | ′29827  | ~              |          |         |              |          |    |          | ~   |          |          |     |          |          |

|                                        |        | ′828    |                |          |         |              |          |    |          |     | +        |          |     |          |          |

| Inverting<br>10-Bit Buffers/Drivers    | 38     | ′11828  |                |          |         |              |          | ~  |          |     |          |          |     |          |          |

| 10 Dit Dulleta/DilVets                 |        | ′29828  | ~              |          |         |              |          |    |          | ~   |          |          |     |          |          |

|                                        |        | ′16241  |                |          |         |              |          |    | ~        |     | ~        |          | T . |          |          |

| Noninverting                           |        | ′16244  |                |          |         |              | · ·      | ~  | ~        |     | ~        |          |     | +        | +        |

| 16-Bit Buffers/Drivers                 | 3S     | ′16244A |                |          |         |              |          |    |          |     |          | ~        |     |          |          |

|                                        |        | ′16541  | 1              |          |         |              |          |    | ~        |     | ~        |          |     |          |          |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

# **Buffers/Drivers (continued)**

| DECODIDATION                                            | QUEDUT | TVDE   |     |    |   |    |     | TEC | CHNOL | OGY |     |     |    |     |      |

|---------------------------------------------------------|--------|--------|-----|----|---|----|-----|-----|-------|-----|-----|-----|----|-----|------|

| DESCRIPTION                                             | OUTPUT | TYPE   | ALS | AS | F | нс | нст | AC  | ACT   | вст | ABT | LVT | LV | LVC | ALVC |

| Inverting                                               | 38     | ′16240 |     |    |   |    |     | ~   | ~     |     | ~   |     |    | +   | +    |

| 16-Bit Buffers/Drivers                                  | 35     | ′16540 |     |    |   |    |     |     | ~     |     | ~   |     |    |     |      |

| Noninverting<br>18-Bit Buffers/Drivers                  | 38     | ′16825 |     |    |   |    |     |     | ~     |     | ~   |     |    |     |      |

| Inverting<br>18-Bit Buffers/Drivers                     | 38     | ′16826 |     |    |   |    |     |     |       |     | +   |     |    |     |      |

| Noninverting<br>20-Bit Buffers/Drivers                  | 38     | ′16827 |     |    |   |    |     | -   | V     |     | ~   |     |    |     | +    |

| Inverting<br>20-Bit Buffers/Drivers                     | 38     | ′16828 |     |    |   |    |     |     |       |     | +   |     |    |     | +    |

| Octal Buffers/Drivers<br>With Input Pullup<br>Resistors |        | ′746   | ~   |    |   |    |     |     |       |     |     |     |    |     |      |

### Universal Bus Transceivers (UBT™)/Universal Bus Exchangers (UBE™)

| DECORIDEION                                                     | ОИТРИТ | TYPE    |    |     |     | TECHNO | DLOGY |    |     |      |

|-----------------------------------------------------------------|--------|---------|----|-----|-----|--------|-------|----|-----|------|

| DESCRIPTION                                                     | OUIPUI | ITPE    | AC | ACT | вст | ABT    | LVT   | LV | LVC | ALVC |

| Noninverting 18-Bit                                             | 38     | ′16500  |    |     |     |        | +     |    |     | +    |

| Universal Bus Transceivers (UBT™)                               | 35     | ′16500B |    |     |     | ~      |       |    |     |      |

|                                                                 |        | ′16501  |    |     |     | ~      | +     |    | +   | +    |

| Noninverting 18-Bit<br>Universal Bus Transceivers (UBT™)        | 38     | ′16600  |    |     |     | 1      |       |    |     | +    |

| Oniversal Bus Transceivers (OBT )                               |        | ′16601  |    |     |     | ~      |       |    |     | +    |

| Noninverting 36-Bit<br>Universal Bus Transceivers (UBT™)        | 38     | ′32501  |    |     | -   | ~      |       |    |     |      |

| Noninverting 16-Bit Tri-Port<br>Universal Bus Exchangers (UBE™) | 38 .   | ′32316  |    |     |     | V      |       |    |     |      |

| Noninverting 18-Bit Tri-Port<br>Universal Bus Exchangers (UBE™) | 38     | ′32318  |    |     |     | ~      |       |    |     |      |

|                                                                 |        | ′162500 |    |     |     | +      |       | ,  |     |      |

| 18-Bit Universal Bus Transceivers                               |        | ′162501 |    |     |     | +      |       |    |     |      |

| (UBT™) With Series Resistors on B Port                          | 38     | ′162600 |    |     |     | +      |       | ,  |     |      |

|                                                                 |        | ′162601 |    |     |     | ~      |       | ,  |     |      |

| SCOPE™ 18-Bit<br>Universal Bus Transceivers (UBT™)              | 38     | ′18502  |    |     |     | ~      | +     |    |     |      |

| SCOPE™ 20-Bit<br>Universal Bus Transceivers (UBT™)              | 38     | ′18504  |    |     |     | ~      | `+    |    |     |      |

<sup>✔</sup> Product available in technology indicated

<sup>+</sup> New product planned in technology indicated

### **Bus Transceivers**

| DESCRIPTION                         | ОИТРИТ   | TYPE        |          |    |   |                                                  |          | TE | CHNOL    | OGY      |          |          |          |          |                                                  |

|-------------------------------------|----------|-------------|----------|----|---|--------------------------------------------------|----------|----|----------|----------|----------|----------|----------|----------|--------------------------------------------------|

| DESCRIPTION                         | OUIPUI   | ITPE        | ALS      | AS | F | нс                                               | нст      | AC | ACT      | вст      | ABT      | LVT      | LV       | LVC      | ALVC                                             |

| Noninverting<br>Quad Transceivers   | 38       | ′243        | ~        |    | ~ |                                                  |          |    |          |          |          |          |          |          |                                                  |

| Inverting                           | ос       | ′758        | ~        |    |   |                                                  |          |    |          |          |          |          |          |          |                                                  |

| Quad Transceivers                   | 38       | ′242        |          |    | ~ |                                                  |          |    |          |          |          |          |          |          | -                                                |

|                                     |          | ′245        | ~        | ~  | ~ | ~                                                | ~        |    |          | ~        | ~        | ~        | ~        | +        |                                                  |

|                                     | _        | ′1245       | ~        |    |   |                                                  |          |    |          |          |          |          |          |          |                                                  |

|                                     |          | ′11245      |          |    |   |                                                  |          | V  | ~        |          |          |          |          |          |                                                  |

|                                     | 38       | ′25245      |          |    |   |                                                  |          |    |          | ~        | V        |          |          |          |                                                  |

| Noninverting<br>Octal Transceivers  |          | ′645        | V        | V  |   | V                                                | V        |    |          |          |          |          |          |          |                                                  |

| Octai Transceivers                  |          | ′1645       | ~        |    |   |                                                  |          |    |          |          |          |          |          |          |                                                  |

|                                     |          | ′621        | V        |    | ~ |                                                  |          |    |          |          |          |          |          |          |                                                  |

|                                     | oc       | ′641        | ~        | ~  |   |                                                  |          |    |          |          |          |          |          |          |                                                  |

|                                     | OC/3S    | ′639        | ~        | ~  |   |                                                  |          |    |          |          |          |          |          |          |                                                  |

|                                     |          | ′620°       | V        |    |   |                                                  |          |    |          | ~        |          |          |          |          |                                                  |

|                                     |          | <b>′623</b> | 1        | ~  | ~ | 1                                                | V        |    |          | ~        | ~        | <b></b>  |          |          |                                                  |

|                                     |          | ′11623      |          |    |   |                                                  | <b> </b> |    | ~        |          |          |          |          | 1        |                                                  |

|                                     | 3S       | ′640        | ~        | V  |   | V                                                | <b> </b> |    | <u> </u> | ~        | ~        |          |          | 1        |                                                  |

| Inverting                           |          | ′1640       | V        |    |   |                                                  | <u> </u> |    | <b>†</b> |          |          | <b> </b> | ,        |          |                                                  |

| Octal Transceivers                  |          | ′11640      |          |    |   | Ī                                                |          |    | 1        |          |          |          |          |          |                                                  |

|                                     |          | ′642        | ~        |    |   |                                                  |          |    |          |          |          |          |          |          |                                                  |

|                                     | oc       | ′25642      |          |    |   | <del> </del>                                     |          |    | †        | ~        | 1        |          | <u> </u> | 1        |                                                  |

|                                     | OC/3S    | ′638        | V        | ~  |   | <u> </u>                                         |          |    |          |          | <u> </u> |          |          |          |                                                  |

| Noninverting                        |          | ′863        | <u> </u> |    |   |                                                  |          |    |          |          | 1        |          |          | +        |                                                  |

| 9-Bit Transceivers                  | 3S       | ′29863      | V        |    |   |                                                  |          |    |          | ~        |          |          |          |          |                                                  |

| Inverting<br>9-Bit Transceivers     | 38       | ′29864      |          |    |   |                                                  |          |    |          | V        |          |          |          |          |                                                  |

| Noninverting                        | <b> </b> | ′861        | 1.       |    |   |                                                  | <b>-</b> |    |          | <b> </b> | +        |          |          |          |                                                  |

| 10-Bit Transceivers                 | 38       | ′29861      |          | -  | ļ | t                                                |          | -  |          | 1        |          |          | ļ        | <b>†</b> |                                                  |

| Inverting<br>10-Bit Transceivers    | 38       | ′29862      |          |    |   |                                                  |          |    |          | ~        |          |          |          |          |                                                  |

| Noninverting                        |          | ′16245      |          |    |   |                                                  |          | 1  | ~        | 1        | 1        | ~        |          | +        | +                                                |

| 16-Bit Transceivers                 | 38       | ′16623      |          |    |   | 1                                                |          | 1  | 1        | <u> </u> | 1        |          |          |          |                                                  |

| Inverting                           |          | ′16640      |          |    |   |                                                  |          | V  | 1        |          | 1        |          | -        |          | <del>                                     </del> |

| 16-Bit Transceivers                 | 38       | ′16620      |          |    |   | <del>                                     </del> | t        | V  | V        | 1        | +        |          |          | <b>†</b> | <b>†</b>                                         |

| Noninverting<br>18-Bit Transceivers | , 3S     | ′16863      |          |    |   |                                                  |          |    | ~        |          | -        |          |          |          |                                                  |

| Inverting<br>18-Bit Transceivers    | 38       | ′16864      |          |    |   |                                                  |          |    |          |          | +        |          |          |          |                                                  |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

### **Bus Transceivers (continued)**

| DECODINE                            | OUTDUT | TVDE   |     |    |   |    |     | TE | CHNOL | OGY |     |     |    |     |      |

|-------------------------------------|--------|--------|-----|----|---|----|-----|----|-------|-----|-----|-----|----|-----|------|

| DESCRIPTION                         | ОИТРИТ | TYPE   | ALS | AS | F | нс | нст | AC | ACT   | вст | ABT | LVT | LV | LVC | ALVC |

| Noninverting<br>20-Bit Transceivers | 38     | ′16861 |     |    |   |    |     |    | ~     |     | +   |     |    |     |      |

| Inverting<br>20-Bit Transceivers    | 38     | ′16862 |     |    |   |    |     |    |       |     | +   |     |    |     |      |

|                                     |        | ′11470 |     |    |   |    |     |    | ~     |     |     |     |    |     |      |

|                                     |        | ′543   |     |    | ~ |    |     |    |       | ~   | ~   | ~   |    | +   |      |

|                                     | -      | ′11543 |     |    |   |    |     |    | ~     |     |     |     |    |     |      |

|                                     |        | ′646   | ~   | ~  |   | ~  | ~   |    |       | ~   | ~   | ~   |    | +   |      |

|                                     | 38     | ′646A  |     |    |   |    |     |    |       |     | ~   |     |    |     |      |

| Noninverting<br>Octal Registered    | 35     | ′11646 |     |    |   |    |     | ~  | ~     |     |     |     |    |     |      |

| Transceivers                        | İ      | ′652   | ~   | ~  |   | ~  | ~   |    |       | ~   | ~   | ~   |    | +   |      |

|                                     |        | ′11652 |     |    |   |    |     | ~  | ~     |     |     |     |    |     |      |

|                                     |        | ′2952  |     |    |   |    |     |    |       | ~   | +   | ~   |    | +   |      |

|                                     |        | ′2952A |     |    |   |    |     |    |       |     | ~   |     |    |     |      |

|                                     | OC/3S  | ′653   | ~   |    |   |    |     |    |       |     |     |     |    |     |      |

|                                     | 00/33  | ′654   | ~   |    |   |    |     |    |       |     |     |     |    |     |      |

|                                     |        | ′544   |     |    |   |    |     |    |       | ~   | +   |     |    |     |      |

|                                     |        | ′11544 |     |    |   |    |     |    | ~     |     |     |     |    |     |      |

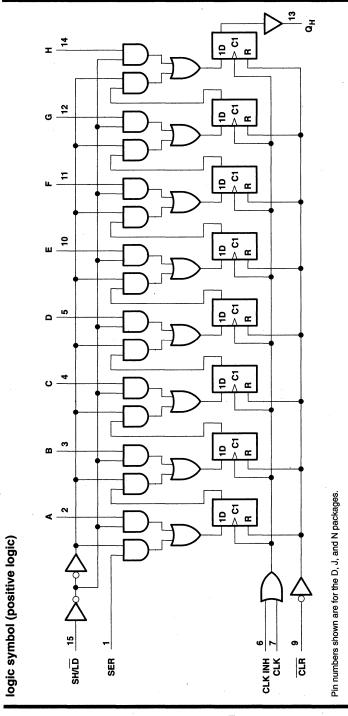

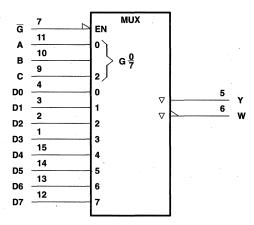

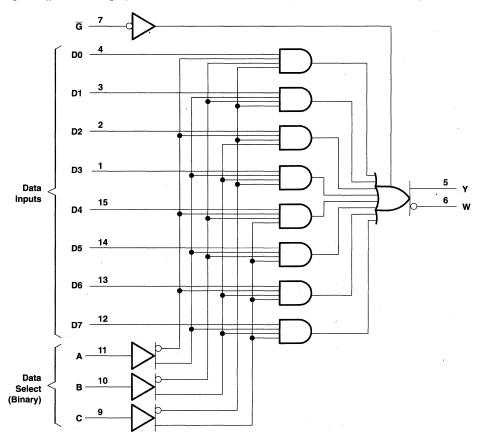

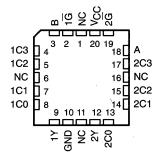

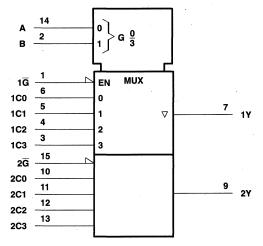

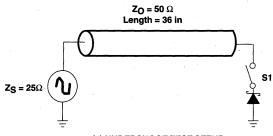

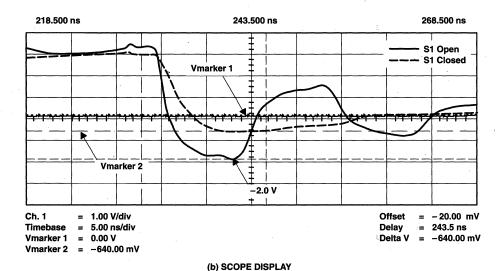

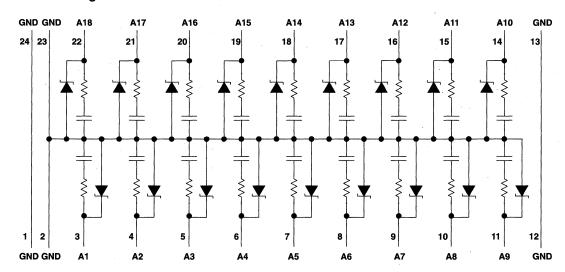

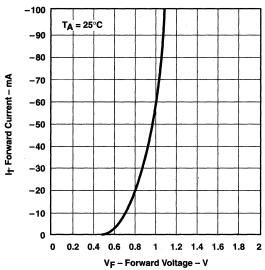

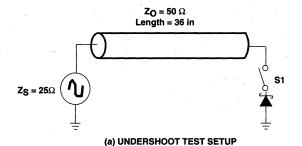

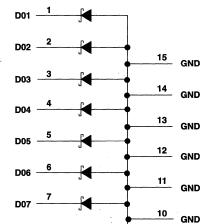

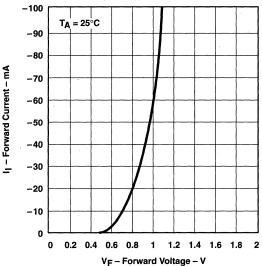

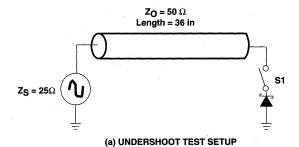

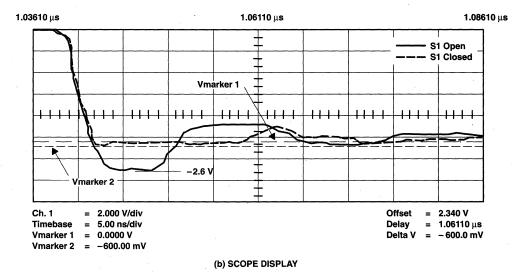

| Inverting<br>Octal Registered       | 38     | ′648   | ~   | ~  |   |    |     |    |       | ~   | +   |     |    |     |      |