Texas Instruments

# TMS 3556

3556 Video Display Processor

Document Scanner par humeur@orange.fr i search a TI99/4a and Exelvision Computer contact me

T M S 3 5 5 6

F A M I L Y

U S E R S

M A N U A L

M G O D D A R D

2 2 . 0 3 . 8 4

## IMPORTANT

## NOTICES

This product was developed by Texas Instruments under contract to the Centre Commun d'Etudes de Television et Telecommunications (CCETT).

Numero de marche : M4643W.

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No licence is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

## PREFACE

This document is a guide to the use of the TMS3556 family of Video Display Processors (VDP's).

It is intended to be autonomous by containing all pertinent details of specification, operation, application and characteristics of the VDP family of devices. With the possible exception certain documents relating to specific detailed applications it is intended that this users manual contain all necessary information for the system engineer designing around one of the VDP family devices. As such, it replaces all preceeding documention, and may in some cases render the latter obselete, erroneous or both.

## CONTENTS

| PIN ASSIGNEMENT 0 - 1                                     |

|-----------------------------------------------------------|

| INTRODUCTION 1 - 1                                        |

|                                                           |

| 1.1 Description                                           |

| 1 - 1                                                     |

|                                                           |

|                                                           |

| 1.2.3 Mixed mode                                          |

| 1 2                                                       |

| 1.3 Features                                              |

| 1.3 Features                                              |

| 2 1                                                       |

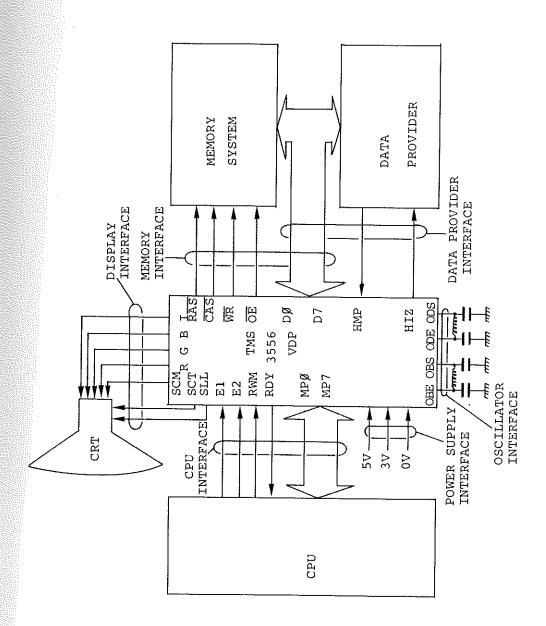

| 2 SYSTEM ARCHITECTURE 2 - 1                               |

|                                                           |

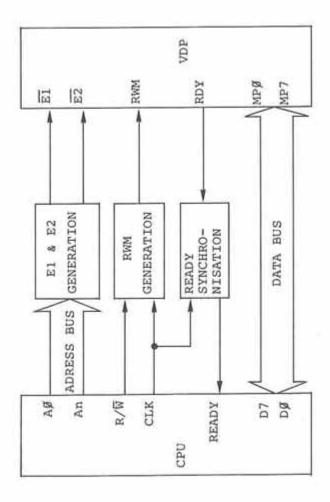

| 2.1 CPU Interface 2 - 1                                   |

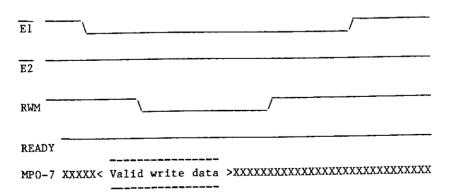

| 2.1.1 Control signals                                     |

| o i o U-ita to control registers """ -                    |

| 2 1 2 Upday to have address registers 2 - 4               |

| a . / n - J from chattle TPD18LCL **** 4                  |

| ~ · C *!! *~ VDD mamorv ***** *                           |

|                                                           |

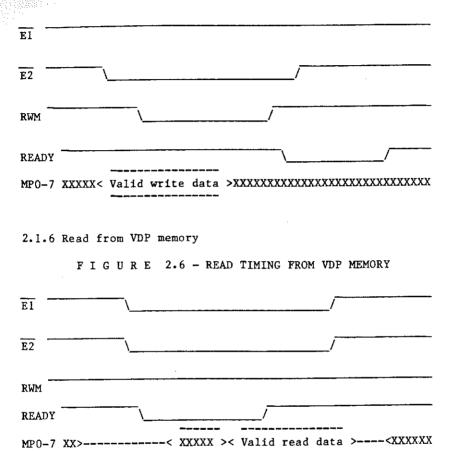

| 2.1.6 Read from vbr memory 2.1.7 VDP initialisation 2 - 5 |

| _ ,                                                       |

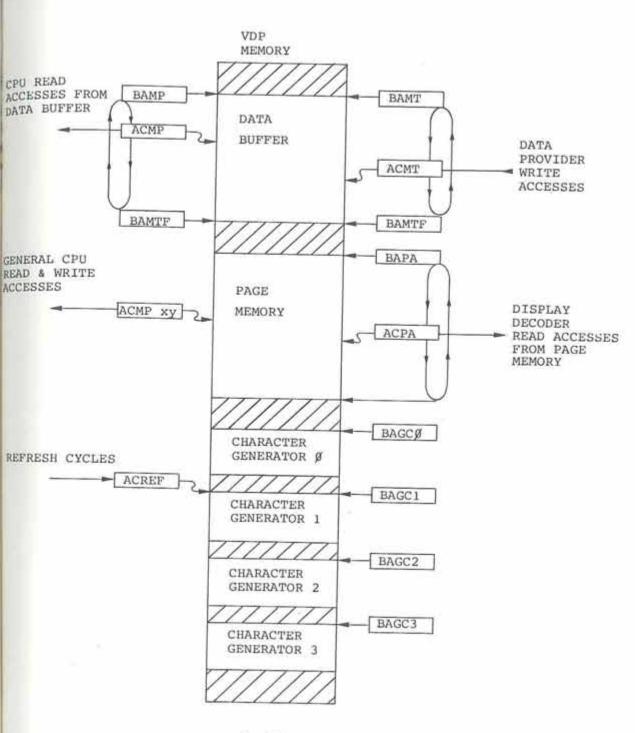

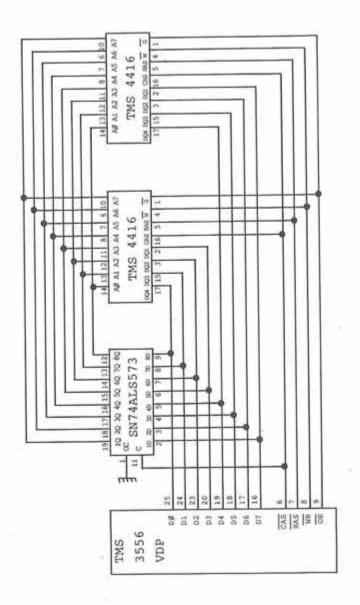

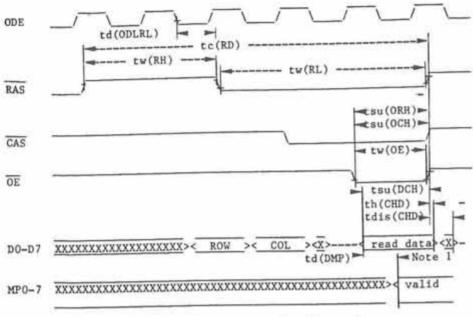

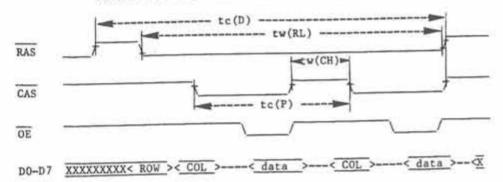

| 2.2 VDP/memory interface 2 - 6                            |

| 2 - 6                                                     |

| 2.2.1 Control signals                                     |

| 2.2.2 Memory Lypes                                        |

| 2 - 7                                                     |

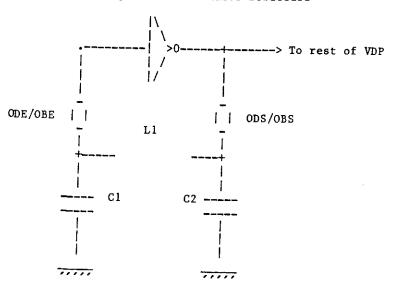

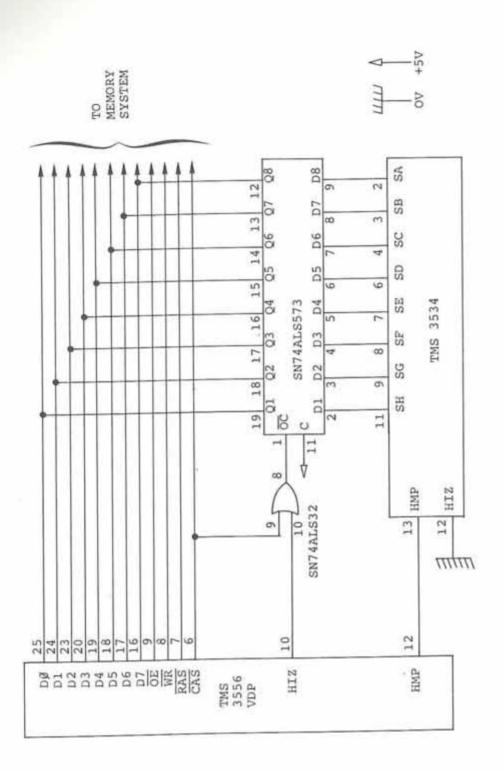

| 2.3 VDP/data provider interface 2 - 7                     |

| 2.3.1 General                                             |

| 2.3.2 Interface control signals 2 - 8                     |

| 2.3.1 General                                             |

| 2.4 VDP/TV interrace                                      |

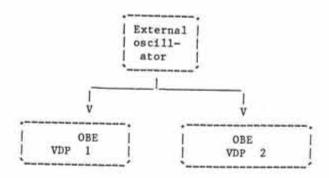

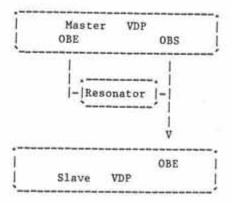

| 2.5 Oscillators 2 - 10                                    |

| 2 - 11                                                    |

| 2.6 Power supplies                                        |

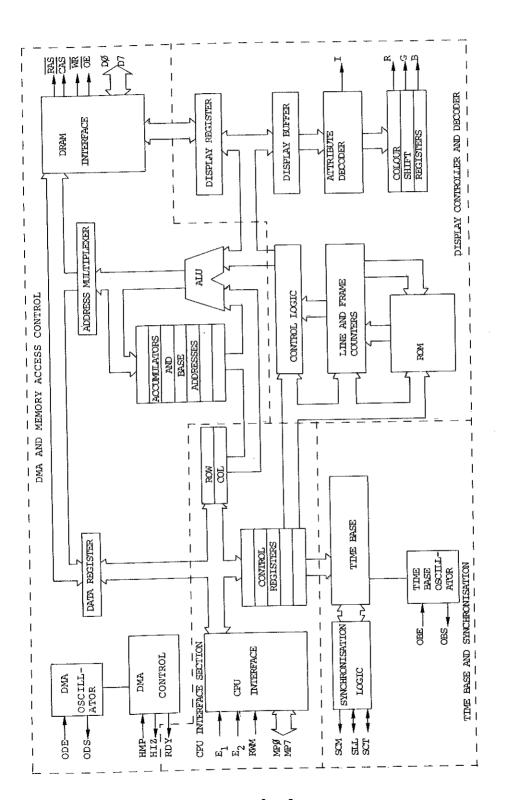

| 3 | VDP INTERNAL ARCHITECTURE                                     | 3   | _   | 1     |

|---|---------------------------------------------------------------|-----|-----|-------|

|   | 3.1 General                                                   |     |     |       |

|   |                                                               | J   | _   | 1     |

|   | 3.2 CPU interface section                                     | 3   | -   | 1     |

|   | 3.3 On-chip registers                                         | 3   | _   | 1     |

|   | 3.3.1 Programming registers 1 to 7 .                          | 2   |     | ı     |

|   | 3.3.2 Reading the Status register                             | 2   | _   | 4     |

|   | 3.3.3 Programming registers 8 to 15.                          | 3   | _   | ,     |

|   | 3.3.4 Status register                                         | 2   |     | 0     |

|   | 3.3.5 Command mandatum 7 and                                  | 3   | -   | 9     |

|   | 3.3.5 Command register I - CMl                                | .5  | _   | 1.    |

|   | J.J.U COMMAND PROISER 7 - CM7                                 | - 7 | _   | - 1 1 |

|   | 3.3.7 Command register 3 - CM3 3.3.8 Command register 4 - CM4 | 3   | -   | 15    |

|   | 3.3.8 Command register 4 - CM4                                | 3   | -   | 17    |

|   | 3.4 Memory organisation and base address registers            |     |     |       |

|   | registers                                                     | 3   | _   | 17    |

|   |                                                               | ,   | Ī   | .,    |

|   | 3.5 Auto-incrementing address pointers                        | 3   | -   | 19    |

|   | 3.5.1 Accumulators associated with                            | _   |     |       |

|   | the CPU                                                       | 3   | -   | 19    |

|   | the display decoder                                           | 3   | _   | 22    |

|   | 3.5.3 Accumulator associated with                             | ,   | _   | ~~    |

|   | the data buffer                                               | 2   |     | 22    |

|   | 3.5.4 Accumulator associated with                             | ,   | _   | 23    |

|   | refresh                                                       | 3   | _   | 24    |

|   |                                                               |     |     |       |

|   | 3.6 Buffer operation                                          | 3   | -   | 24    |

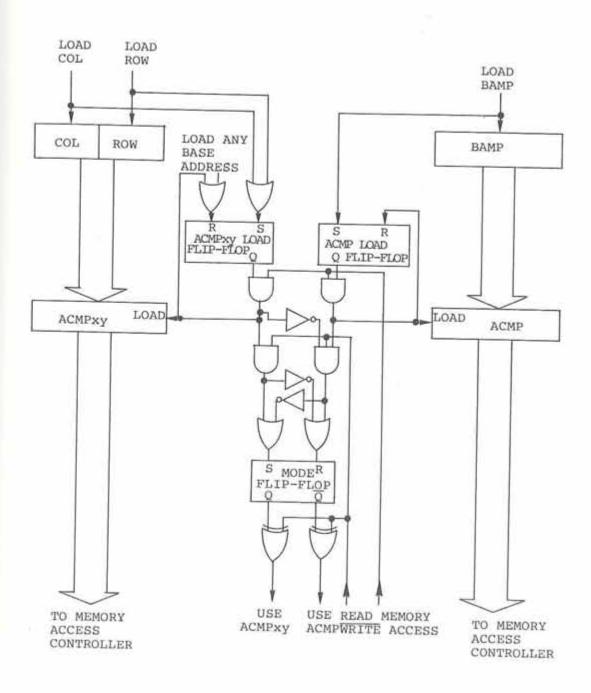

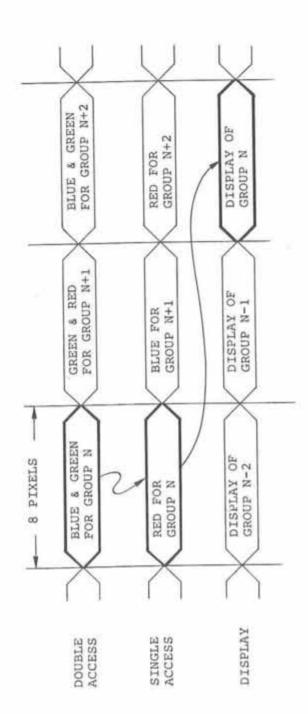

|   | 3.7 DMA controller                                            | 3   | _   | 24    |

|   |                                                               |     |     |       |

|   | 3.7.1 General                                                 | 3   | -   | 24    |

|   | 3.7.2 Priority control                                        | 3   | -   | 25    |

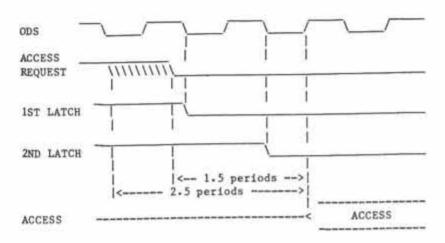

|   | 3.7.3 Request synchronisation                                 | 3.  | _   | 27    |

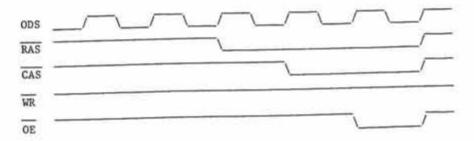

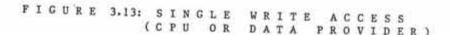

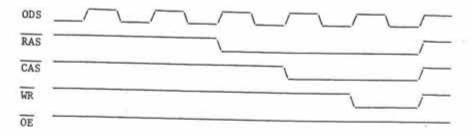

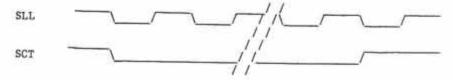

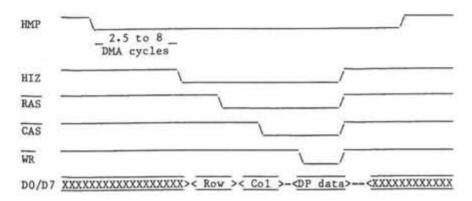

|   | 3.7.4 Memory access control                                   | 3 . | -   | 28    |

|   | 3.7.5 Memory access control                                   | 3 . | -   | 30    |

|   | 1./.b Retrech cycles                                          | ъ.  | _   | วา    |

|   | 3.7.7 Access response times                                   | з.  | - : | 32    |

|   | 3.7.7 Access response times                                   | 3 • | - : | 33    |

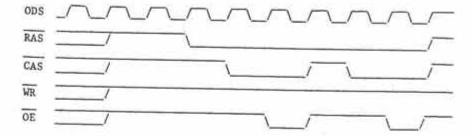

|   | 3.8 Time base                                                 | γ.  | -   | 33    |

|   |                                                               |     |     |       |

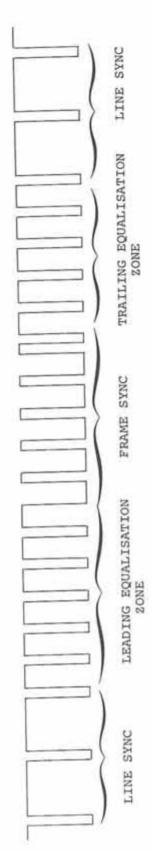

|   | 3.8.1 Display timing                                          | 3.  | - : | 33    |

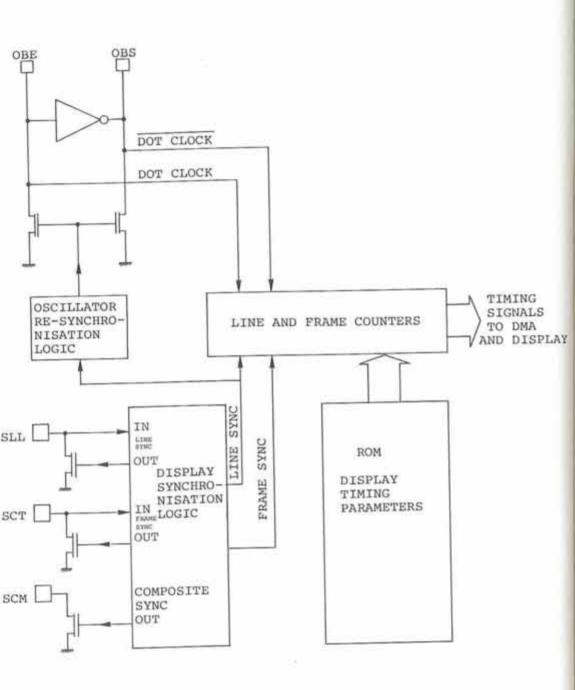

|   | 3.8.2 Display synchronisation                                 | 3.  | - : | 35    |

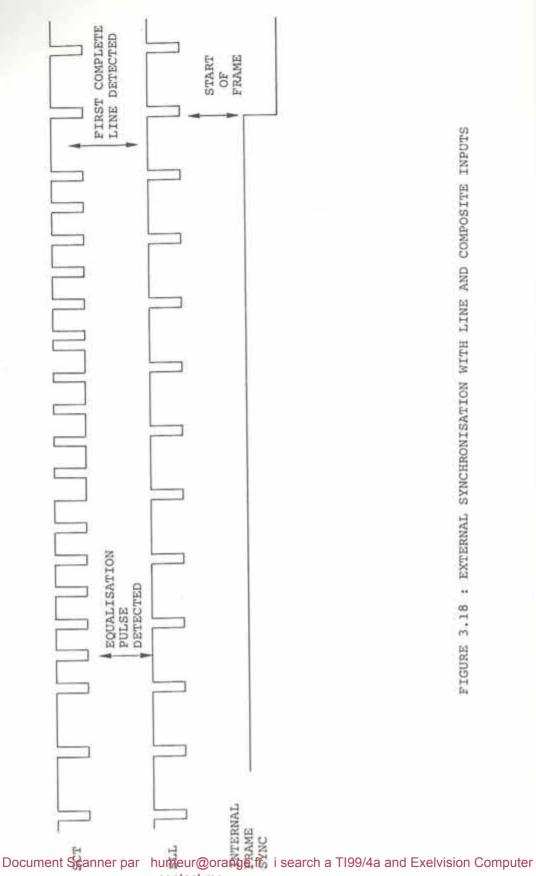

|   | 3.8.3 External synchronisation                                | 3.  | _ ; | 37    |

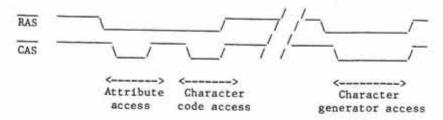

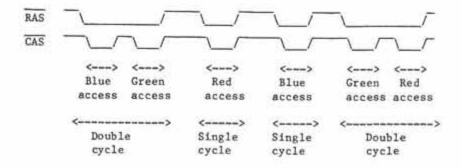

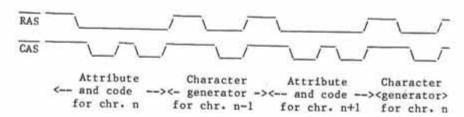

|   | 3.8.4 Display decoder timing                                  | 3.  | . : | 39    |

| OPERATION 4 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | L   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 Display standard options 4 - :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   |

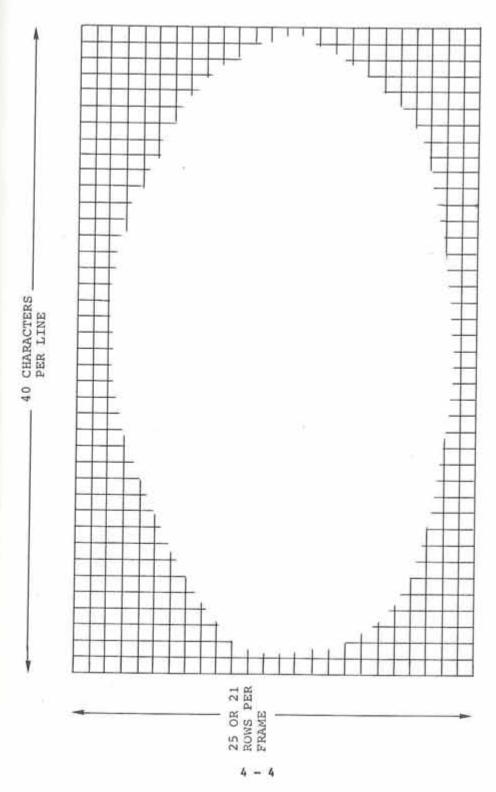

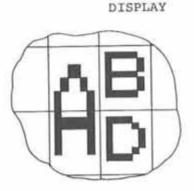

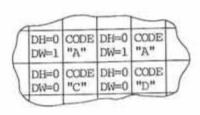

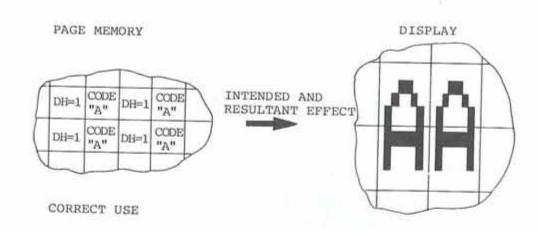

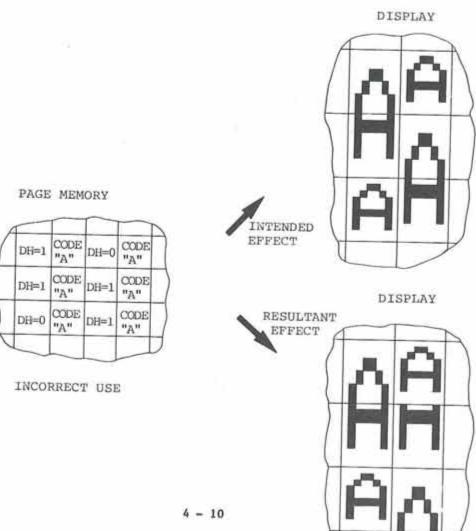

| 4.2 Text mode 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3   |

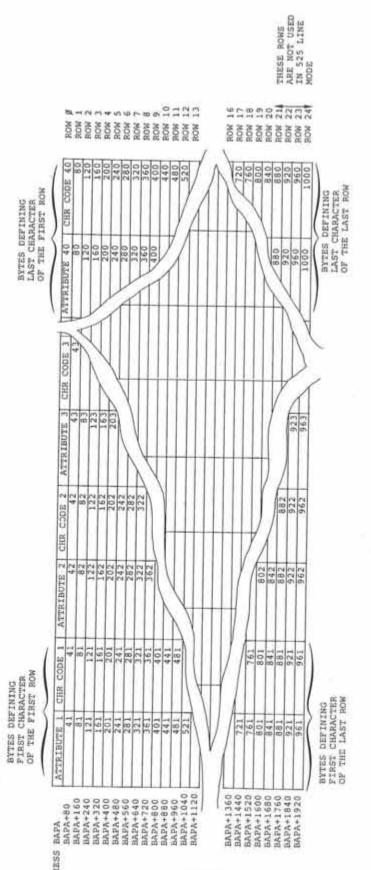

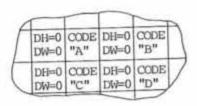

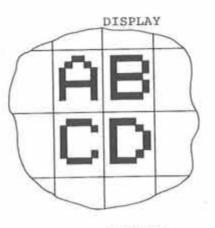

| 4.2.1 Page memory 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3   |

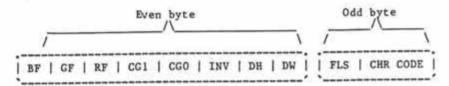

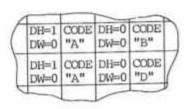

| 4.2.2 Attributes 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | /   |

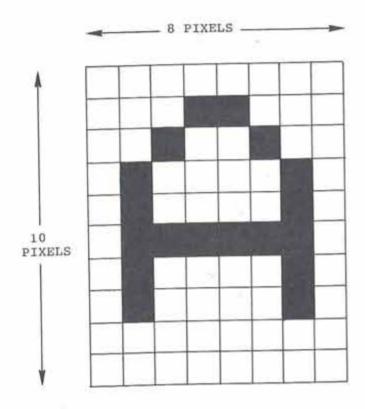

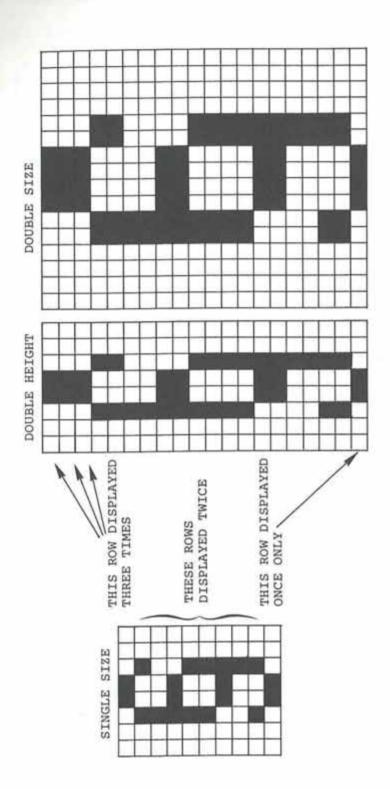

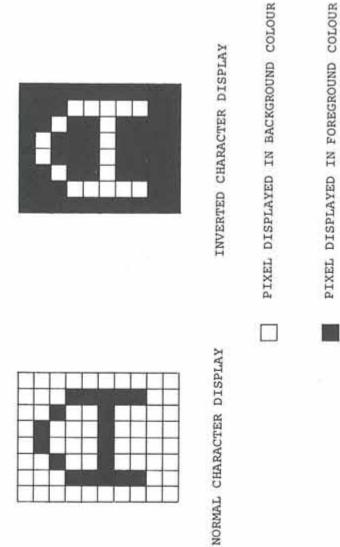

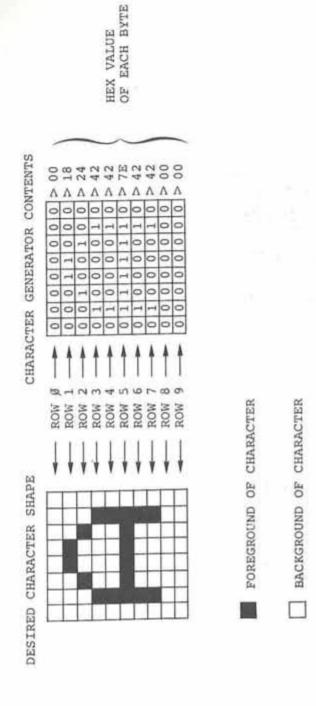

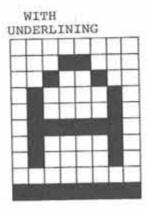

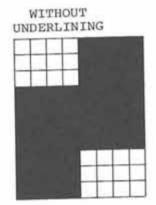

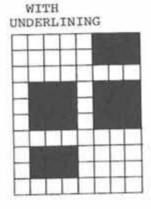

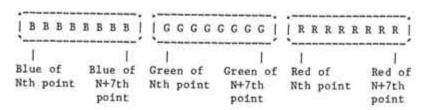

| 4.2.3 Character generators 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B   |

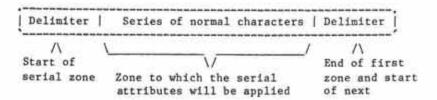

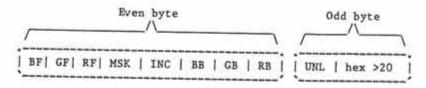

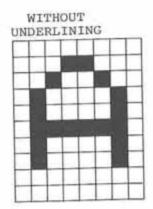

| 4.2.4 Serial attributes 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14  |

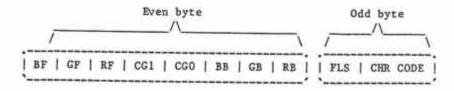

| 4.2.5 Alpha-mosaic attributes 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20  |

| 4 2.6 Command register CM4 and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| full page attributes 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12  |

| 4.3 Bit-mapped mode 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14  |

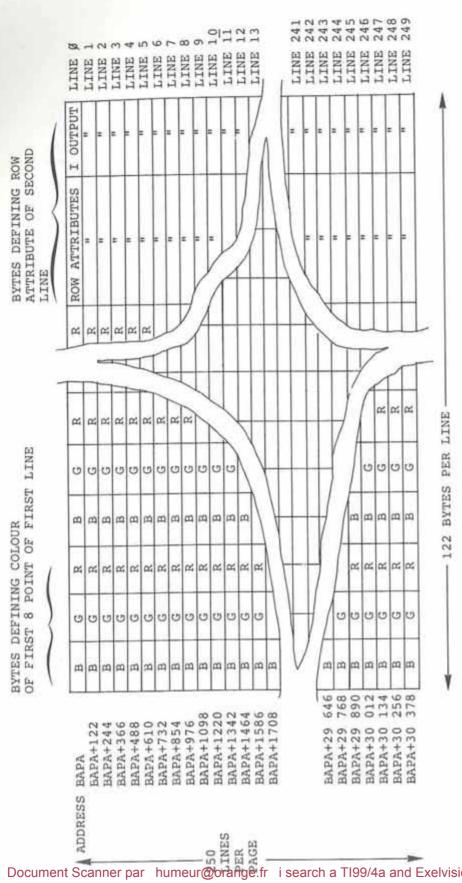

| 4.3.1 Page memory 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24  |

| 4.3.1 Page memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 4.3.2 Control of the I output and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24  |

| margin colour 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 4.4 Mixed mode 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 4.4.1 Page memory 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2   |

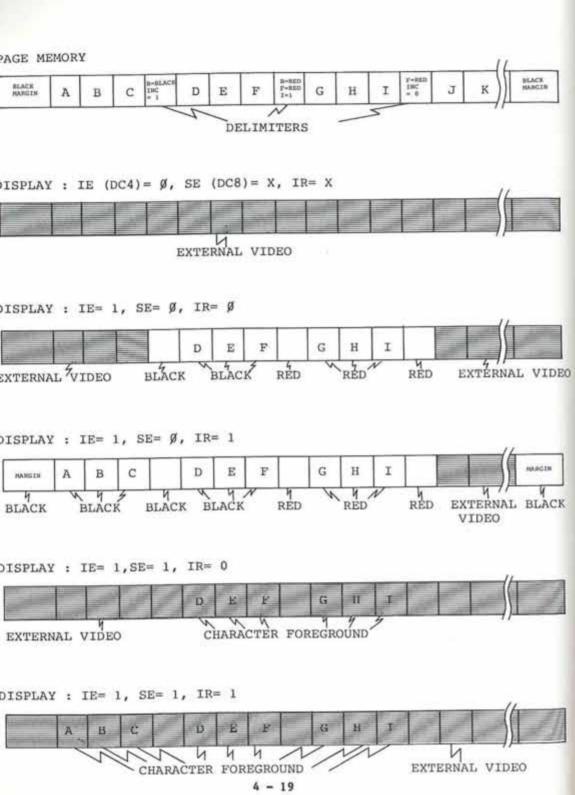

| 4.5 Subtitling mode 4 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29  |

| 5 OPERATIONAL SOFTWARE CONSIDERATIONS 5 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 5.1 Initialisation 5 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   |

| 5.1.1 Register pointer 5 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1   |

| 5.1.2 Control registers 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   |

| 5.1.3 Character generators 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 5.1.5 Data input buffer 5 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 3 |

| 5.1.5 Data Imput Dullet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 5.2 Memory address pointer manipulation . 5 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 4 |

| 5.2.1 Safe pointer manipulation 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 4 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| the data buffer ········                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| - ^ ^ N .11-4 maninularione                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| without a data buffer 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - ( |

| 5.3 Multipage and scrolling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| TO A MILITIDADE ALLA POLUMATANDE TOTO O CONTROLLO CONTRO |     |

| 5.4 Compliance with teletext and                        |            |            |

|---------------------------------------------------------|------------|------------|

| Videotex standards                                      | 5          | - 7        |

| 5.4.1 Antiope                                           | 5          | - 8        |

| 5.4.2 Ceefax                                            | 5          | _ 9        |

| 5.4.3 Prestel                                           | 5          | - 9        |

| 5.4.4 Teletel                                           | 5 .        | - 9        |

| 6 OPERATIONAL HARDWARE CONSIDERATIONS                   | 6 -        | - 1        |

| 6.1 DMA frequency and timing considerations             | 6 -        | - 1        |

| 6.1.1 Maximum DMA frequency 6.1.2 Minimum DMA frequency | 6 ·<br>6 · | - 1<br>- 2 |

| 6.2 Time base considerations                            | 6 -        | - 4        |

| 6.3 Clock generation                                    | 6 -        | - 5        |

| 6.4 External synchronisation                            | 6 -        | - 5        |

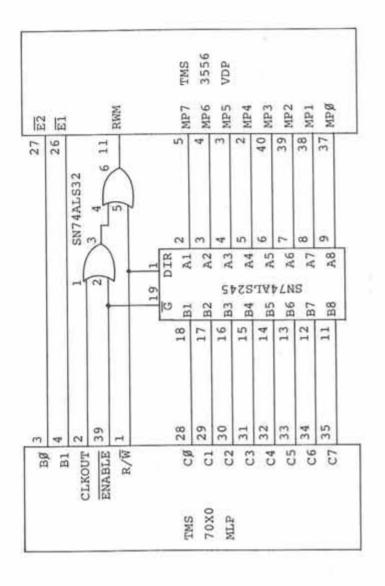

| 6.5 System interfaces                                   | 6 -        | - 6        |

| 6.5.1 Memory interface 6.5.2 Data provider interface    | 6 -<br>6 - | - 6<br>- 6 |

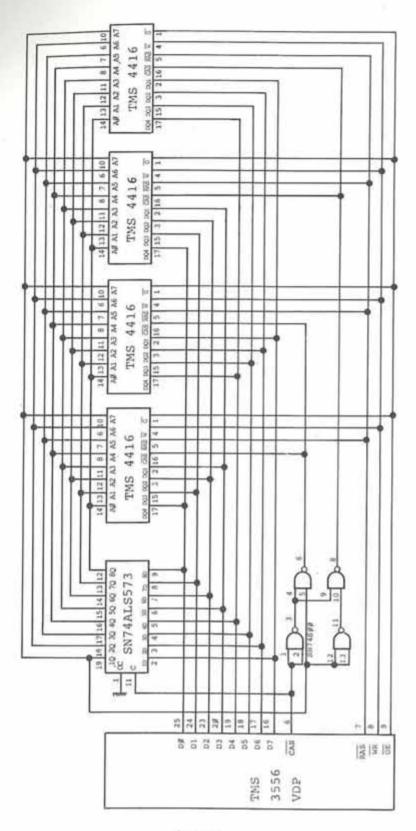

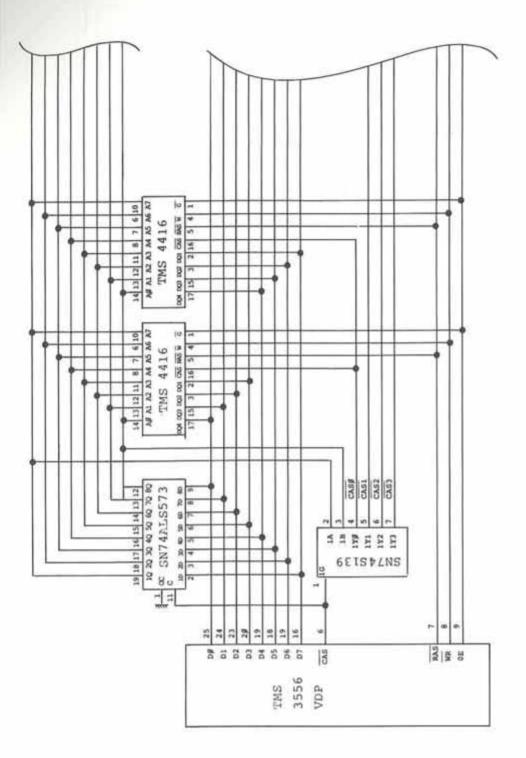

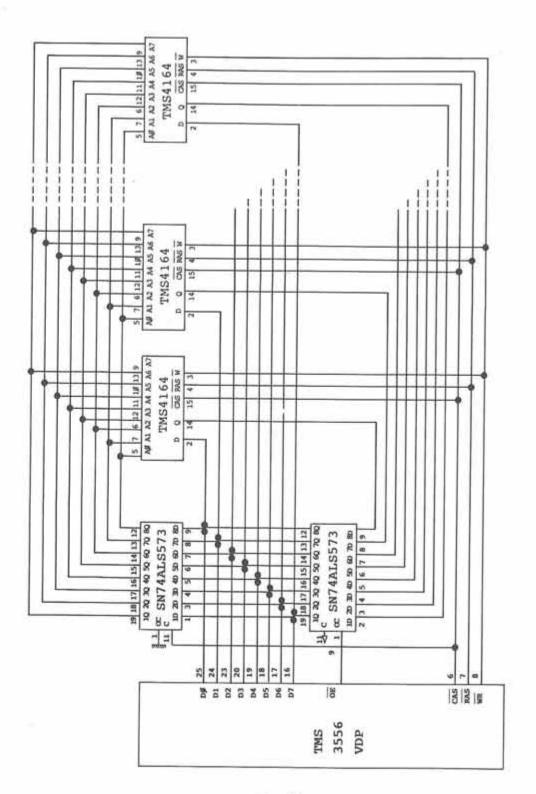

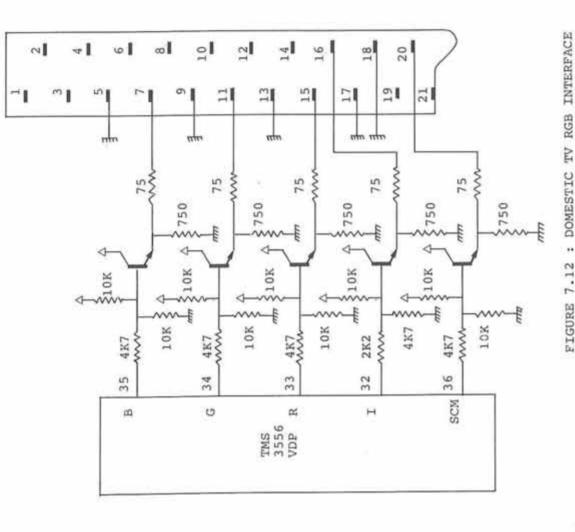

| 7 APPLICATIONS EXAMPLES                                 | 7 ~        | - 1        |

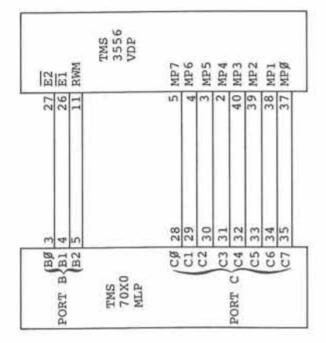

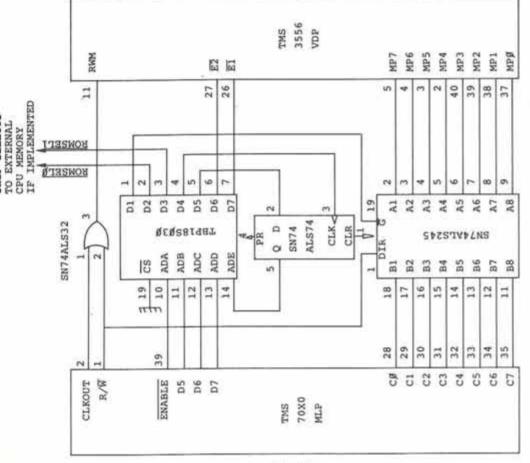

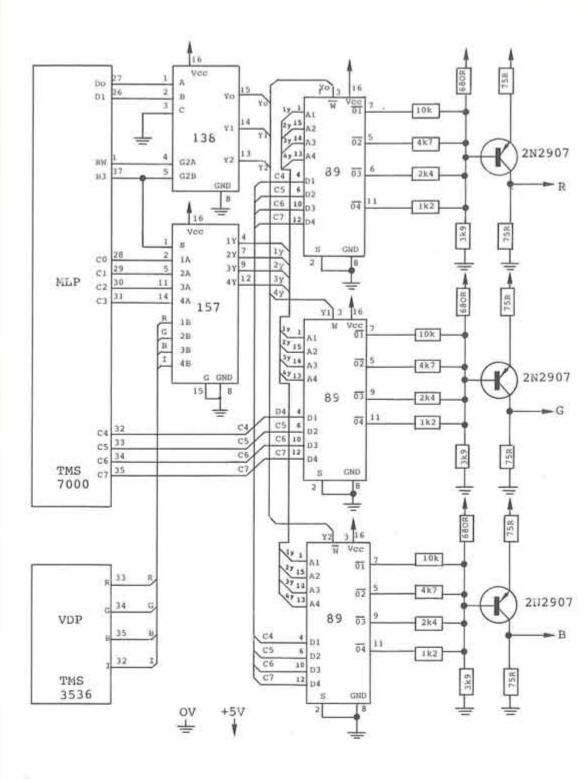

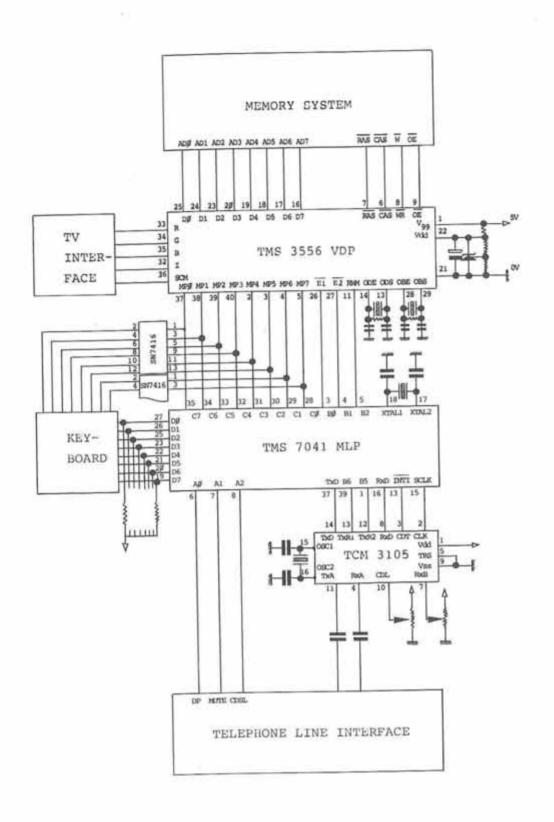

| 7.1 CPU - VDP interfaces                                | 7 -        | - 1        |

| 7.1.1 TMS7000 Single chip mode                          | 7 -        | - 1        |