WEITEK CORP 02 DE

9663826 0000442 /

T.49-12-05

WTL 3132/WTL 3332 XL-3132 32-BIT FLOATING POINT DATA PATH

## PRELIMINARY DATA

October 1987

The WEITEK WTL 3132, WTL 3332, and XL-3132 single-chip floating point data paths each offer a full instruction set, including multiply, multiply/accumulate, add, subtract, type conversion, and divide look-up operations. Efficient design and architecture, combined with CMOS technology, provide up to 25 MFLOPS of performance at very low power.

Related products: XL-8136 32-bit Sequencer, XL-8137 32-bit Integer Processor

| Contents                         |                             |

|----------------------------------|-----------------------------|

| Features                         | 1                           |

| Description                      | 1                           |

| Architecture                     | 2                           |

| Signal Description               | 4                           |

| Block Diagram                    | $\frac{2}{4}$ $\frac{5}{7}$ |

| Register File                    | 7                           |

| Multiplier/Accumulator           | 8                           |

| Temporary Registers              | 13                          |

| Internal Data Routing            | 16                          |

| Input/Output                     | 20                          |

| System Interfacing               | 25                          |

| Instruction Set                  | 30                          |

| Initialization                   | 35                          |

| Division                         | 38                          |

| Data Format                      | 39                          |

| IEEE Considerations              | 41                          |

| DC Specifications                | 42                          |

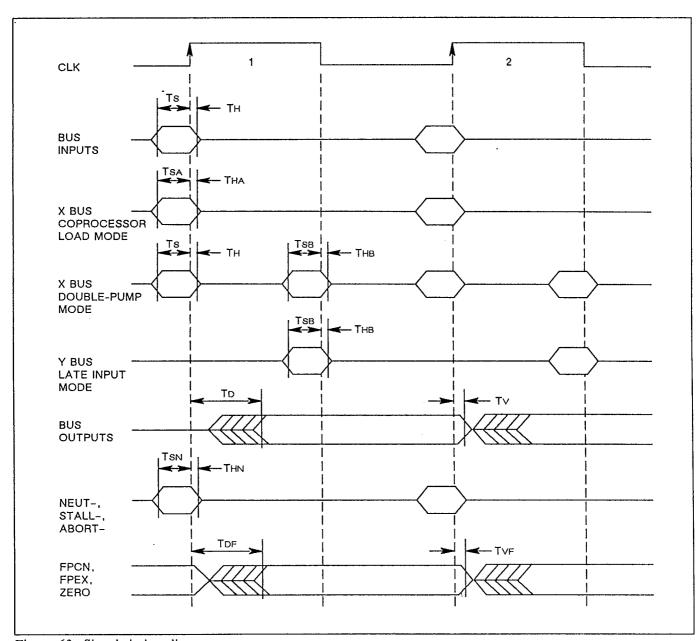

| Timing Diagrams                  | 43                          |

| AC Specifications                | 45                          |

| Pin Configuration                | 46                          |

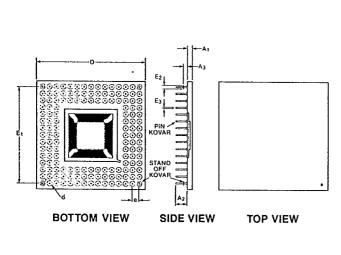

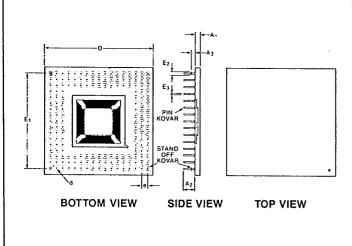

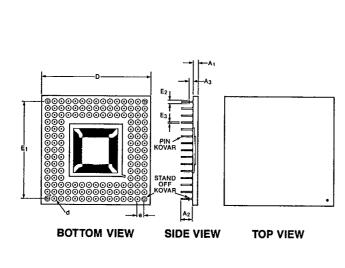

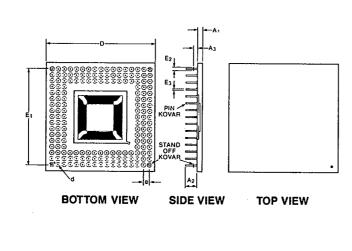

| Physical Dimensions              | 48                          |

| Appendix A: The XL-3132 in       |                             |

| the XL Environment               | 49                          |

| Appendix B: Programming Examples | 55                          |

| Ordering Information             | 58                          |

| Revision Summary                 | 59                          |

| Documentation Request Forr       | n 61                        |

| Sales Offices back               | cover                       |

## PRELIMINARY DATA

October 1987

### **Features**

32-BIT FLOATING POINT PROCESSOR

Single-precision floating point multiplier/ALU

Four-port 32×32 register file

IEEE floating point format

Low power, high integration CMOS

**FULL FUNCTION**

Add, subtract, multiply, multiply/accumulate

Divide look-up table

Type conversion to and from two's complement integer

Three-address (rc := ra + rb) architecture

Flexible I/O options

#### HIGH PERFORMANCE

80, 100 and 120 ns cycle times

Up to 25 MFLOPS throughput (1 MAC/cycle)

·Low latency (3-cycle register-to-register operation)

High I/O bandwidth (up to 200 Mbytes/sec)

#### MULTI-PURPOSE

For maximum throughput, use the three-port WTL 3332

For maximum design flexibility, use the WTL 3132 or WTL 3332 as microprogrammable building blocks

For high level language support, use the XL-3132 as the XL-8032 floating point coprocessor

## Description

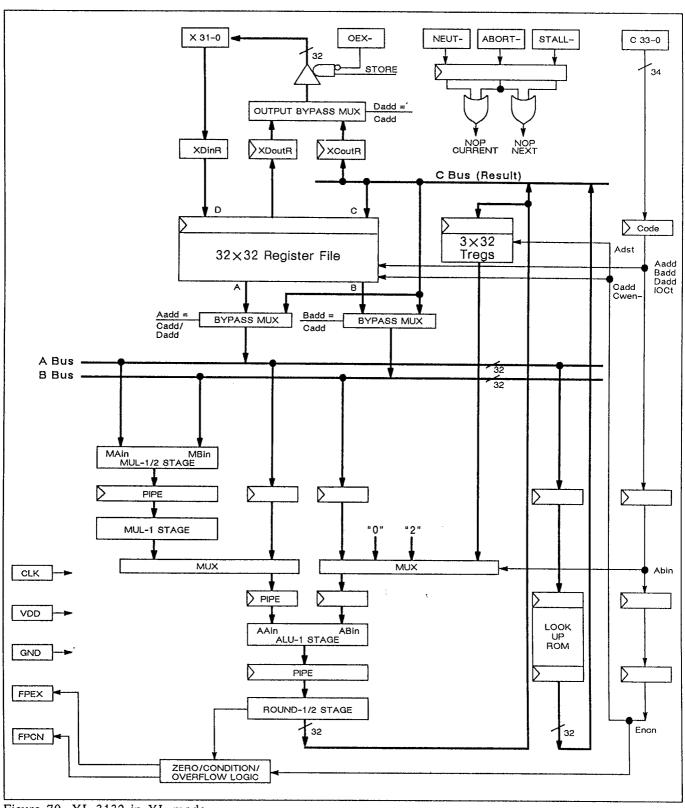

The WTL 3132 and WTL 3332 are single-precision floating point data paths. Each includes a pipelined multiplier/accumulator and a four-port register file with thirty-two 32-bit registers.

The WTL 3132/3332 are suited to a wide range of systems that need high numeric processing performance. They may be adopted as the floating point unit for a general-purpose processor, used as building blocks for application-specific data paths or even connected together to create vector or array processors.

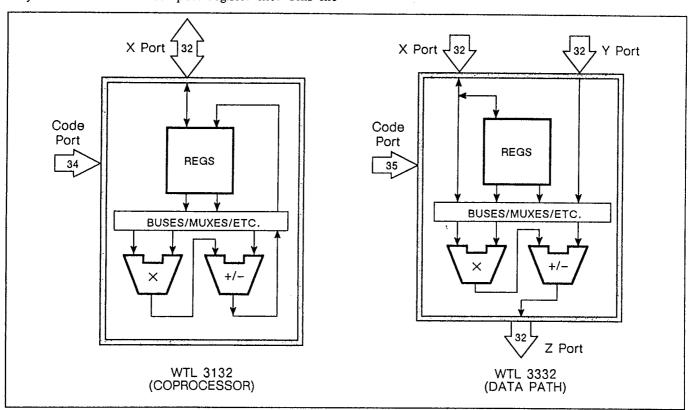

The WTL 3132 has a single bi-directional 32-bit input/output port. It is designed to be used as a floating point coprocessor or accelerator. The WTL 3332 has three 32-bit ports; one bi-directional input/output port, one input port and one output port. It should be used in applications which require multiple high-bandwidth buses.

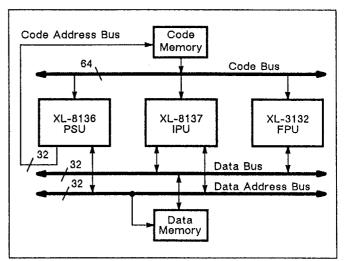

The XL-3132 may also be used with the WEITEK XL-8136 program sequencing unit (PSU) and XL-8137 integer processing unit (IPU) to create a fast, general-purpose numeric processor, the XL-8032. Full development system support, including FORTRAN and C compilers, is available for the XL-Series of processors. The XL-3132 is functionally identical to the WTL 3132.

Both devices are manufactured in low power CMOS and are available in standard pin grid array (PGA)

packages. The WTL 3132 is supplied in a 144-pin PGA and the WTL 3332 in a 168-pin PGA.

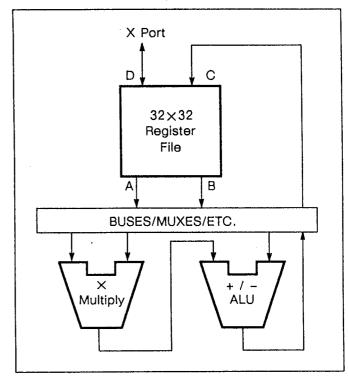

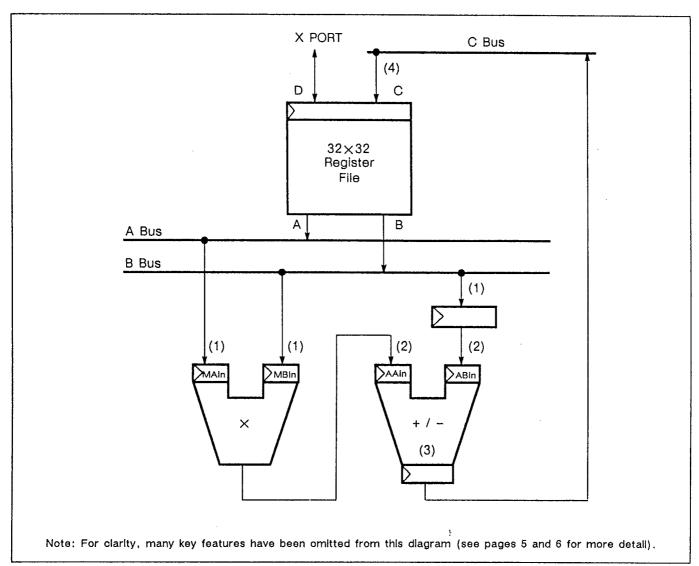

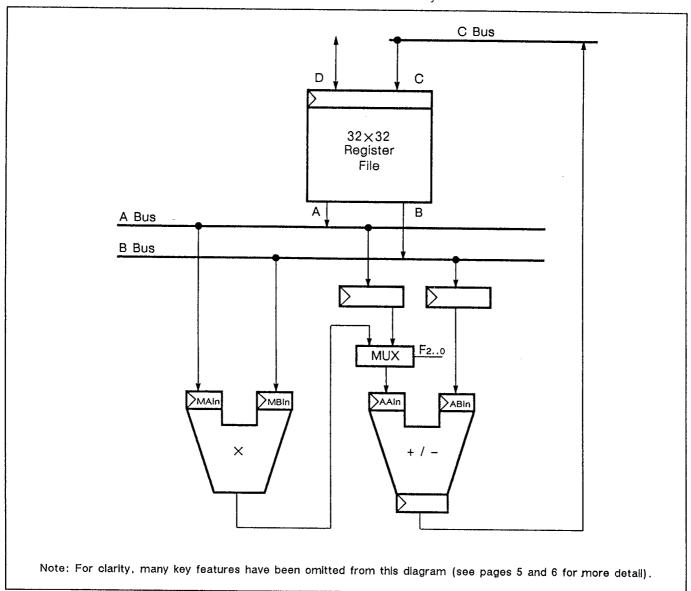

Figure 1. WTL 3132/3332 core functions

### Architecture

#### MULTIPLIER/ACCUMULATOR

The core of both the WTL 3132 and WTL 3332 is the multiplier/accumulator pipeline. Its first stage can multiply two operands together. The next stage can add or subtract another operand. Finally, the result is rounded and returned to a register and/or output port.

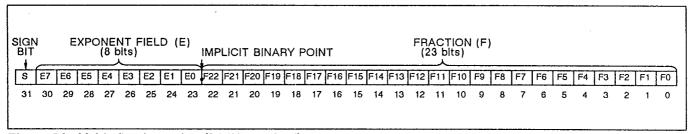

Multiply, add, subtract, and multiply/accumulate operations are performed in the multiplier/accumulator. They all operate on data that conforms to the IEEE single-precision floating point format.

Each operation takes three cycles, but, because the multiplier/accumulator is pipelined, a new operation can be started on every cycle. At any time, three independent operations may be at different stages in their execution.

Rounding, conversion between floating point and two's complement integer formats, and other miscellaneous functions are supported in the accumulator.

#### REGISTER FILE

Operands and results of the multiplier/accumulator may be stored in the four-port register file. This file contains thirty-two registers, each of which may store a 32-bit value.

The four ports allow the register file to supply two operands to the multiplier/accumulator, store its result back to a register, and perform an input/output transfer-all in the same cycle.

#### INPUT/OUTPUT PORTS

The external I/O ports are all 32 bits wide. They can each transfer a data value on every cycle.

The WTL 3132 has one bi-directional external port; the X port. It can load and store data to and from the register file, and it can transfer data directly to and from the multiplier/accumulator.

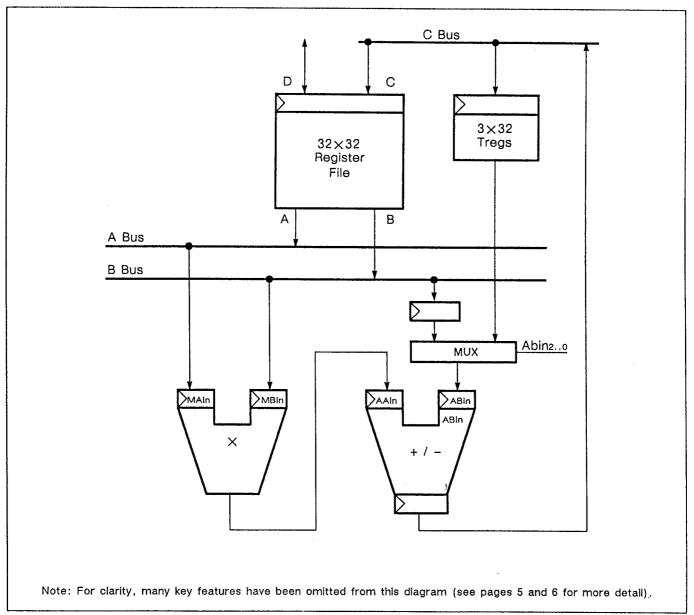

The WTL 3332 has three external ports; the X port, the Y port, and the Z port. The X port is the same as the WTL 3132's X port. The Y port feeds input operands directly to the multiplier/accumulator. The Z port outputs results directly from the multiplier/accumulator. These additional ports help to avoid the bottlenecks usually associated with I/O-intensive algorithms.

Figure 2. WTL 3132/3332 I/O options

### PRELIMINARY DATA

October 1987

DATA PATH

## Architecture, continued

#### TEMPORARY REGISTERS

Three 32-bit temporary registers are provided to store intermediate results. They make it possible to perform operations of the form

$x = x \pm (y \times z)$

in a single cycle.

### DIVIDE LOOK-UP TABLE

Support for divide operations is provided by an on-chip look-up table. It returns an approximation for the inverse of a value which may then be refined by iterative multiply/accumulate operations. Division is accomplished by multiplying the dividend by the inverse of the divisor. This complete divide operation takes eighteen cycles; other operations may be interleaved without a performance penalty.

### **INSTRUCTIONS**

An instruction is latched into the code port on every cycle. It specifies operand sources, a result destination and all of the steps that will create this result during the next three cycles. Condition codes and exceptions may be generated by each operation as the result is written back to the register file.

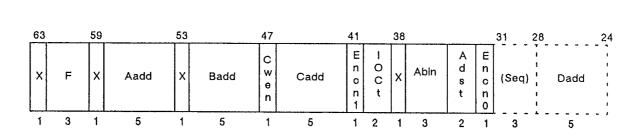

Four five-bit fields provide addresses for the register file. They each select a source or destination for one of the register ports. The three-bit function field specifies the type of multiplier/accumulator operation. The two-bit I/O control field directs data transfer at the external X port. Other fields select the route taken by the data during the the operation.

A Mode Register controls data routing options that rarely change, selecting between a number of I/O tim-

ing options, and supporting upward-compatibility with previous versions of the WTL 3132/3332.

#### XL-SERIES COMPATIBILITY

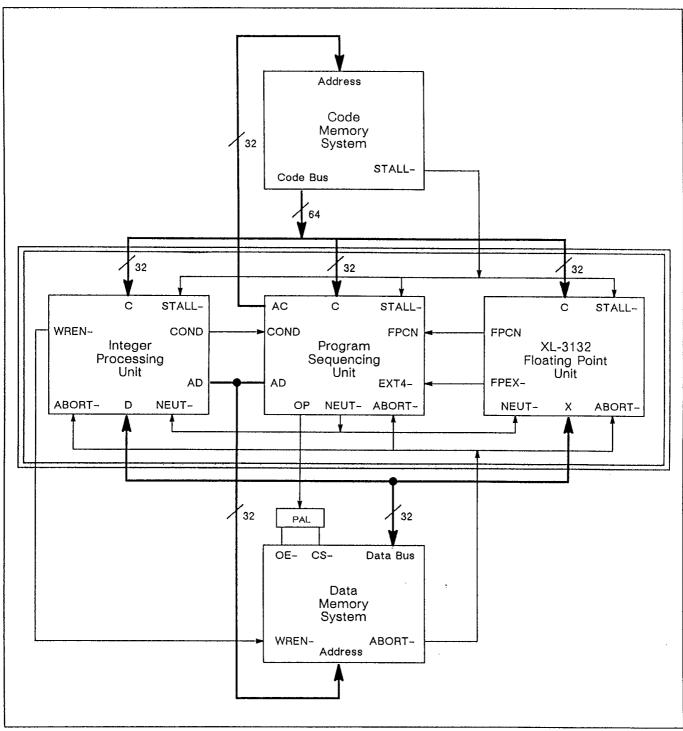

The XL-3132 may be used with the WEITEK XL-8136 program sequencing unit (PSU) and XL-8137 integer processing unit (IPU) to create the XL-8032 processor.

The XL-3132 floating point unit (FPU) shares a 64-bit instruction word with the IPU and PSU. The IPU and FPU also share the 32-bit-wide data bus.

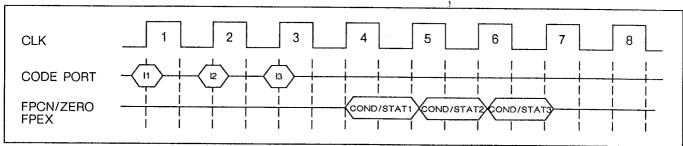

The XL-3132 responds to the NEUT-, STALL- and ABORT- signals used to control branching and "wait states" within the XL-8032. It communicates its status to the PSU with the floating point condition (FPCN) and exception (FPEX) lines. See Appendix A for more about the XL-Series.

Figure 3. XL-8032 block diagram

## Signal Description

### X PORT

The 32-bit X31..0 port is a bi-directional data bus. Input data is sampled on the rising edge of CLK (or, if Double-Pump Mode is enabled, both on the rising and falling edges of CLK). Data transfers are controlled by the IOCt1..0 field in the instruction word. The X port may be set to a high impedance state by the OEX- signal. Active high.

### Y PORT

The 32-bit Y<sub>31..0</sub> port is a data input bus. Input data is sampled on the rising edge of CLK (or, if the Y port Late Input Mode is enabled, on the falling edge of CLK). The Y port is only available on the WTL 3332. Active high.

#### Z PORT

The 32-bit Z<sub>31..0</sub> port is a data output bus. The output data is modified on every cycle. The Z port is only available on the WTL 3332. It may be set to a high impedance state by the OEZ- signal. Active high.

#### C PORT

The 35-bit C34..0 port is used as a code input bus. Instructions are latched the rising edge of CLK. Active high. C34 is only available on the WTL 3332 (see figure 40).

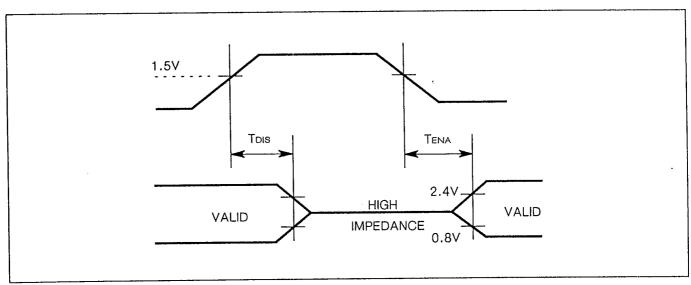

## OEX-

X port output enable input. OEX- asynchronously disables the X port when high. Active low.

#### OEZ-

Z port output enable input. OEZ- asynchronously disables the Z port when high. Active low.

### FPEX(-)

Floating point exception output. FPEX signals the occurrence of an enabled exception (overflow). Polarity is selectable by mode bit Ms.

### **FPCN**

Floating point condition output. FPCN signals the occurrence of a condition as specified in the Encn<sub>1..0</sub> field of an instruction. Active high.

#### **ZERO**

Zero condition output. Indicates that the result of an operation is exactly equal to zero. Controlled by the Enon...o field of an instruction. Active high.

#### NEUT-

Neutralize input. Cancels the effect of the current instruction. Typically used during delayed branches and interrupt response routines (see page 27). Latched on the cycle following the instruction to be cancelled. Active low.

#### STALL-

Stall input. Cancels the effect of the next instruction. Typically used as a "not ready" line from the code store (see page 28). Latched on the same cycle as the potentially invalid instruction. Active low.

### ABORT-

Abort input. Cancels the effect of both the current and next instructions. Typically used as a "not ready" line from the data store (see page 29). Latched on the same cycle as the next instruction. Active low.

#### CLK

Clock input. TTL compatible.

### **VDD**

All VDD pins must be connected to 5.0V.

### GND

All GND pins must be connected to system ground. Note: Signals denoted by "-" are active low.

## PRELIMINARY DATA

October 1987

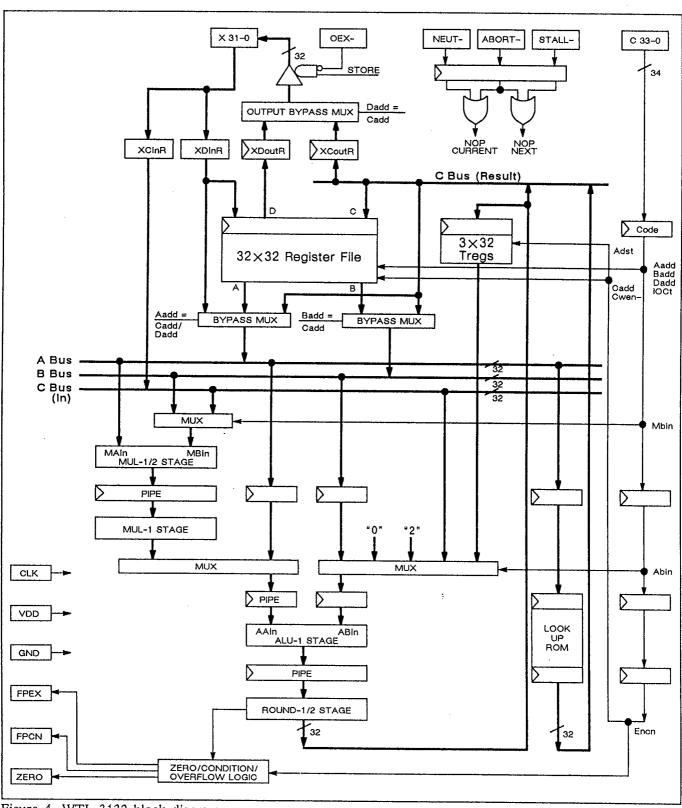

## Block Diagram

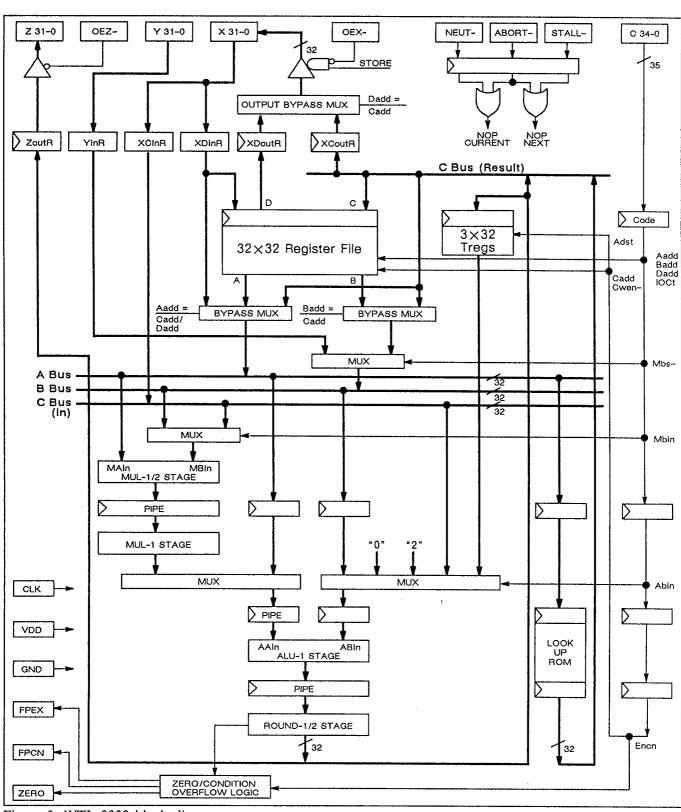

Figure 4. WTL 3132 block diagram

Figure 5. WTL 3332 block diagram

## PRELIMINARY DATA

October 1987

## Register File

The WTL 3132 and WTL 3332 each have thirty-two 32-bit general-purpose registers. Each register can store either a single-precision IEEE value or a two's complement integer value.

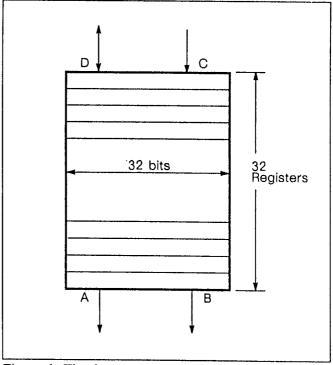

### **PORTS**

The register file has four ports, A, B, C and D. The A and B ports are read-only, the C port is write-only, and the D port is bi-directional. Each port can transfer a 32-bit data word on every clock cycle.

The A and B ports may be used to supply operands to the multiplier/accumulator and the divide look-up table. The C port receives the result of a previous operation. The D port communicates data between the register file and the external X port.

This organization allows I/O transfers to proceed in parallel with calculation, maximizing system performance.

#### REGISTER SELECTION

The registers that are to take part in each transfer are selected by the instruction word. The instruction format allows a register address to be supplied for each port. They are provided in the Aadd, Badd, Cadd and Dadd fields of the instruction. These fields are five bits in length, allowing each address to specify any of the thirty-two registers.

An instruction supplies the Aadd, Badd, and Dadd addresses to the register file during its first cycle and the Cadd address during its fourth cycle. This way a single instruction specifies all of the stages of an operation from initial source to ultimate destination.

It is possible for a register to be selected by more than one field in the same cycle, in which case the following rules apply:

- 1. If only read operations are to be performed on the register in question, then its value is copied to all of the necessary ports.

- 2. If two ports (C and D) attempt to write into the same register on the same cycle, the contents of the register will be left in an undefined state. Such contention should be avoided.

- 3. If a register is to be both read and written on the same cycle, its old value will be read before it is updated to the new value, unless one of the Bypass Modes is activated (see page 16).

Figure 6. The four-port register file

#### READ/WRITE CONTROL

Two other fields in the instruction word affect the operation of the register file.

The Cwen- bit controls writing of results into the C port. When it is active (low), the result data is written on the fourth cycle of the operation. When writes are disabled, the contents of the register specified by Cadd remain unchanged.

Register writes may be disabled either to direct a result to a Temporary Register or to allow arithmetic comparisons to modify the Status and Condition Registers without overwriting the contents of a general-purpose register.

2. The IOCt1..0 bits control the direction of D port transfers (see page 20 for details). If the C port and the D port attempt to write to the same register file location on the same cycle the register contents are left undefined.

# Multiplier/Accumulator

The WTL 3132 and WTL 3332 each have a pipelined multiplier/accumulator. These consist of a floating point multiplier whose output is fed into a floating point ALU (Arithmetic and Logic Unit). All multiplier/accu-

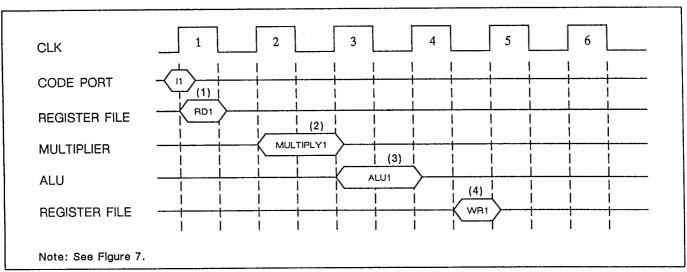

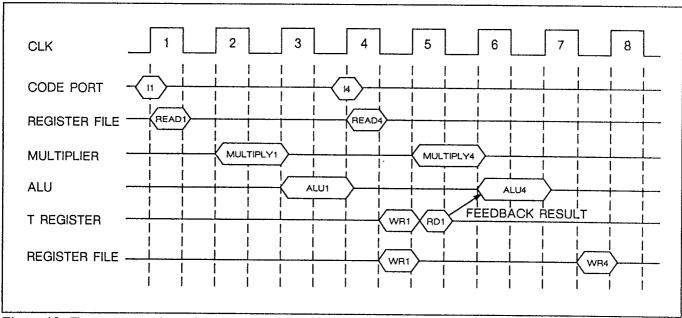

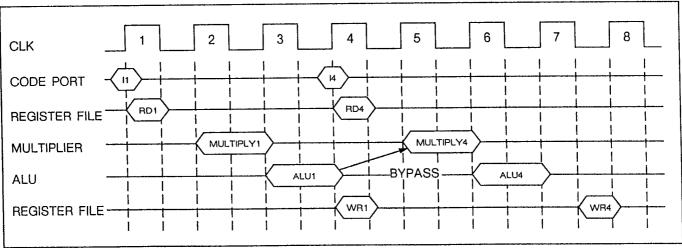

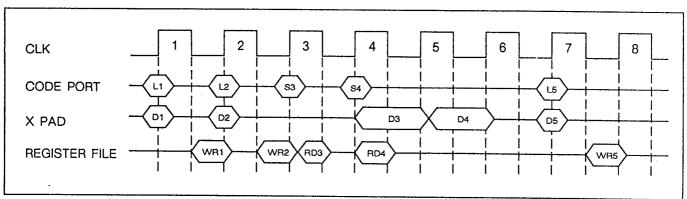

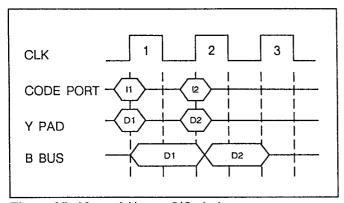

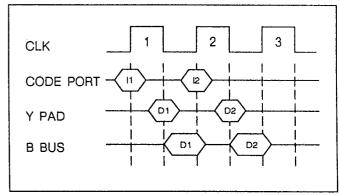

mulator input and output ports can transfer 32-bit data values. Figures 7 and 8 show how operations are pipelined through the multiplier/accumulator.

Figure 7. Simple example of multiplier/accumulator timing.

## PRELIMINARY DATA

October 1987

## Multiplier/Accumulator, continued

Figure 8. Timing of MAC operations

### **MULTIPLIER**

The multiplier has two input ports, MAin and MBin. It has one output which can only be connected to the AAin port of the ALU. In the first cycle of an operation, operands are transferred from the register file and fed into MAin and MBin. The multiplication is completed on the second cycle. The intermediate result may be negated before it is passed to the ALU.

#### ALU

The ALU has two input ports, AAin and ABin. It has one output which is normally connected to the C bus. AAin may be connected to the multiplier's output, so that its result is fed into the ALU. Another operand is fed into the ABin port simultaneously. The ALU completes the function specified by an instruction during its third cycle. The final result is rounded and output to the C bus to be returned to the register file on the fourth cycle.

### LATENCY

Because the multiplier/accumulator is pipelined, an operation can be initiated every cycle. The result of an operation is generated three cycles after it is initiated. On the fourth cycle, the result can be returned to the register file or fed straight back into the multiplier/accumulator using the temporary registers or a bypass mode (see pages 13 or 17).

# Multiplier/Accumulator, continued

### **FUNCTION SELECTION**

The multiplier/accumulator function is specified by the 3-bit field F2..0 in the instruction word as outlined in the function select table (figure 9). A single instruction

specifies all of the actions associated with one operation as it passes through the multiplier/accumulator.

| F2 F1 F0 | MNEMONIC | OPERATION .                   | DESCRIPTION           |

|----------|----------|-------------------------------|-----------------------|

| 0 0 0    | _        | Miscellaneous                 | See figure 10         |

| 0 0 1    | fsubr    | Negate and add                | -AAin + ABin          |

| 0 1 0    | fsub     | Subtract                      | AAin – ABin           |

| 0 1 1    | fadd     | Add                           | AAin + ABin           |

| 1 0 0    | -        | Reserved                      |                       |

| 1 0 1    | fmna     | Multiply, negate and add      | −(MAin × MBin) + ABin |

| 1 1 0    | fmns     | Multiply, negate and subtract | -(MAin × MBin) - ABin |

| 1 1 1    | fmac     | Multiply and accumulate       | (MAin × MBin) + ABin  |

Figure 9. Function select field encoding

When the F2..0 field is (0, 0, 0) the operation to be performed is specified by the Badd field according to figure 10.

| Badd4-0     | MNEMONIC | OPERATION             | DESCRIPTION    |

|-------------|----------|-----------------------|----------------|

| 00000       | fclsr    | Clear Status Register |                |

| 00001       | fstsr*   | Read Status Register  |                |

| 00010       | _        | Reserved              |                |

| 00011       | fmode    | Load Mode Register    |                |

| 00100       | fabs     | Absolute Value        | AAin           |

| 00101       | float    | Fixed-to-Float        | integer → IEEE |

| 00110       | fix      | Float-to-Fixed        | IEEE → integer |

| 00111       | flut     | Look-up Operation     |                |

| 01000-11111 | _        | Reserved              |                |

<sup>\*</sup> fstsr instructions must have their IOCt1..0 field set to select a store.

Figure 10. Miscellaneous function select encoding.

## PRELIMINARY DATA

October 1987

# Multiplier/Accumulator, continued

#### MULTIPLY/ACCUMULATE FUNCTIONS

The WTL 3132/3332 provide three multiply and accumulate functions. fmac multiplies MAin and MBin and then adds ABin. fmns multiplies MAin and MBin, negates the result and then subtracts ABin. fmna multiplies MAin and MBin, negates the result and then adds ABin.

These functions are triadic (they have three input operands). If an IEEE multiply operation is required, the constant 0.0 should be selected as the ABin input.

### **ALU FUNCTIONS**

The WTL 3132/3332 provide three diadic "ALU only" functions, fadd adds AAin to ABin, fsub subtracts ABin from AAin, fsubr subtracts AAin from ABin,

The F2..0 field determines whether the multiplier is bypassed and the ALU's input staged directly into the ALU (see figure 11).

These functions operate in the same number of cycles as the multiply and accumulate functions. This simplifies the programmer's model; every operation has the same latency.

Figure 11. "ALU only" operations

## Multiplier/Accumulator, continued

#### MISCELLANEOUS FUNCTIONS

If the function field is equal to zero, then a miscellaneous ALU function will be selected according to the contents of the instruction's Badd field (see figure 10).

- 1. flut is monadic (that is, it has a single input operand). It takes the value on the A bus as its operand and it returns an approximation to the inverse of this value onto the C bus on its fourth cycle. flut does not attempt to modify the Status, Condition or Zero Registers. It is recommended that the Abina...o field be set to select the constant 0.0. (See page 38.)

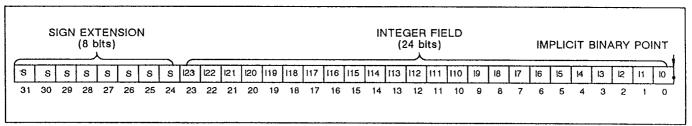

- 2. fix is a monadic "ALU only" function. It takes a single-precision IEEE format floating point value on the A bus as its operand and returns a 24-bit, sign extended, two's complement integer onto the C bus on its fourth cycle. fix does not attempt to modify the Status or Zero Registers. It is the only instruction that produces an integer result. It is recommended that the Abina..o field be set to select the constant 0.0. (See page 40.)

- 3. float is a monadic "ALU only" function. It takes a 24-bit, sign extended, two's complement value on the A bus as its operand and returns a single-precision IEEE format floating point number onto the C bus on its fourth cycle. float does not attempt to modify the Status or Zero Registers. It is the only instruction that requires an integer operand. It is recommended that the Abin2...o field be set to select the constant 0.0. (See page 40.)

- 4. fabs is a monadic "ALU only" function. It takes the value on the A bus as its operand and returns its absolute value onto the C bus on its fourth cycle. fabs does not attempt to modify the Status Register. The Zero and Condition Registers are modified according to the result unless Encn1..0 = (0,0). As with the diadic "ALU only" functions, it will clamp denormalized operands to zero and NaNs to infinity. The Abin2..0 field must be set to select the constant 0.0.

- 5. fmode loads the desired operating modes into the Mode Register (see page 35). Because this operation changes the timing of many operations, the results of the next three operations should be discarded.

- 6. fstsr copies the contents of the Status Register to the X port. It has the same timing as the other fstore operations. (See page 26.) It is recommended that the Cwen- bit be set to prevent register writes, the Encn1..0 field to disable updates of the FPCN pin, the IOCt1..0 field to an fstore and that the result sent to the register file on its fourth cycle be discarded. fstsr ignores the register address fields.

- 7. fclsr clears the contents of the Status Register to zero. (See page 26.) It is recommended that the Cwen- bit be set to prevent register writes, the Enon1..0 field to disable updates of the FPCN pin, the IOC11..0 to an I/O nop and that the result sent to the register file on its fourth cycle be discarded. fclsr ignores the register address fields.

#### MULTIPLIER/ACCUMULATOR NOP

The WTL 3132/3332 do not have a dedicated nop instruction. WEITEK software tools use fsub .f0, .f0, .f0 with the Cwen- bit set to disable register writes and the Encn...o field cleared to disable FPCN updates. This choice of nop causes no state changes.

## PRELIMINARY DATA

October 1987

## Temporary Registers

The WTL 3132 and WTL 3332 each include three 32-bit temporary registers (Tregs). They allow values to be recirculated to the ALU without passing through the general-purpose register file. The Tregs are often used as accumulators during successive multiply/accumulate operations. They make it possible to perform a calculation of the form  $x = x \pm (y \times z)$  every cycle.

Figures 12 and 13 show how the Tregs are used to feedback operands to the multiplier/accumulator: figure 15 gives an example of a code sequence that does this.

Figure 12. Use of temporary registers

# Temporary Registers, continued

Figure 13. Temporary register timing

### WRITING TEMPORARY REGISTERS

The instruction word contains a two-bit field, Adst1..0, that determines the destination of the ALU output (see figure 14).

The output of the ALU is always sent to the C bus. If no Treg is selected by the Adst1..0 field, then the result is returned only to the register selected by this instruction's Cadd field on its fourth cycle.

| Adst1-0 | RESULT DESTINATION |  |

|---------|--------------------|--|

| 00      | Treg3, C bus       |  |

| 01      | Treg2, C bus       |  |

| 10      | Treg1, C bus       |  |

| 11      | C bus              |  |

Figure 14. ALU destination select field encoding

If the Adst1..0 field selects a Treg in addition to the C bus, it is loaded with the result on the fourth cycle of an operation, just as the Cadd register write occurs. On the next cycle, the contents of the Treg may be input directly to the ABin port. This is illustrated by the example shown in figure 15.

The Cwen- bit of the instruction that writes to the Treg may be held high to prevent the write to the Cadd register. This increases the number of available generalpurpose registers.

## PRELIMINARY DATA

October 1987

## Temporary Registers, continued

#### READING TEMPORARY REGISTERS

The instruction word contains a three-bit field, Abin2..0, that determines the source of the MAC's ABin input.

Three encodings select one of the Tregs (see figure 17). If a Treg is selected, it is copied to the ABin port on the second cycle of the operation.

The Treg may be be read on the cycle after it was written. In figure 15, for example, .t1 gets read during the second cycle of op #4. This is the fifth cycle of op #1.

```

op #1

fmac

.f0.

.f1.

0,

.t1

.f3,

.f4,

op #2

fmac

.t1.

.f5

-old .t1

op #3

fmac

.f6,

.f7,

.t1,

.f8

-Illegal

op #4

fmac .f9,

.f10, .t1,

.f11 -new .t1

```

#### Notes:

A Treg cannot be both written and read in the same cycle. Op #3 must never attempt to read the Treg written by op

To make this code interruptable, op #2 and op #3 should not specify .t1 as an operand.

Full details of this syntax are given on page 32.

Figure 15. Use of temporary registers

# Internal Data Routing

### INTERNAL BUSES

The three main internal buses, A, B and C, move data between the major functional units of the WTL 3132 and WTL 3332. Each of these buses is 32 bits wide and can carry one word per cycle.

The A bus usually carries operands from the register file to the multiplier/accumulator or the divide look-up table. It may also be fed with operands directly from the X port if the Input Bypass Mode is enabled (see page 21).

The B bus usually carries operands from the register file to the multiplier/accumulator. It may also be fed directly with operands from the Y port on the WTL 3332 if selected by the Mbs- bit (see page 23).

The C bus usually carries multiplier/accumulator or flut results back to the general-purpose register file. If the Output Bypass Mode is enabled, then it may be used to feed the results directly to the X port.

If the C bus is not needed to carry the results back to the registers (eg., when they are output directly to the Z port), then its usual direction of transfer may be reversed. It is then used to carry inputs from the X port directly to the multiplier/accumulator. This is only possible by the use of the floadro operation or the Double-Pump Mode (see page 21).

| Mbin- | INPUT          |

|-------|----------------|

| 0     | B bus<br>C bus |

Figure 16. Multiplier input port select field encoding

| Abin2-0 | INPUT    |

|---------|----------|

| 000     | C bus    |

| 001     | B bus    |

| 010     | Treg2    |

| 011     | Treg1    |

| 100     | Treg3    |

| 101     | Reserved |

| 110     | 2.0      |

| 111     | 0.0      |

Figure 17. ALU input select field encoding

# MULTIPLIER/ACCUMULATOR INPUT PORTS

The multiplier/accumulator has four input ports, MAin, MBin, AAin and ABin. These ports can each receive a 32-bit word per cycle. They all have multiplexers which may be connected to various input sources. The possible selections for each port are described below:

- 1. MAin usually obtains input from the A bus. Results may be fed from the C bus to the A bus using the Internal Bypass Mode and then into MAin.

- 2. MBin usually obtains its input from the B bus. Results may be fed from the C bus to the B bus using the Internal Bypass Mode and then into MBin. Y port inputs may be enabled onto the B bus and then into the MBin.

Alternatively, the C bus can be reversed so that it is carrying inputs from the X port to the MBin port. This prevents the C bus from being used to return results to the register file and is done in conjunction with the floadro operation or Double-Pump Mode. MBin must select the C bus (see figure 16).

- 3. AAin usually obtains its input from the A bus. Results may be fed from the C bus to the A bus using the Internal Bypass Mode and then into AAin.

- 4. ABin usually obtains its input from the B bus. Results may be fed from the C bus to the B bus using the Internal Bypass Mode and then into ABin. Y port inputs may be enabled onto the B bus and then into the ABin.

The 3-bit Abinz..o field in the instruction word selects between input from the B bus (as above), input of the constants 0.0 or 2.0, input from one of the Tregs, or input from the C bus (as below) according to figure 17.

Alternatively, the C bus can be reversed so that it is carrying inputs from the X port to the MBin port. This prevents the C bus from being used to return results to the register file and is done in conjunction with either the floadro operation or Double-Pump Mode. ABin must select the C bus. When this pathway is used, the ABin data is not delayed: an external register may be needed to synchronize the X and Y inputs.

## PRELIMINARY DATA

October 1987

## Internal Data Routing, continued

If the function code specifies an operation that uses the multiplier, it directs data to the MAin or MBin ports. If the multiplier is not used, (that is, in "ALU only" operations), then the data is sent to the AAin or ABin

ports automatically. The WTL 3132/3332 are designed to maintain a consistent latency regardless of the type of operation.

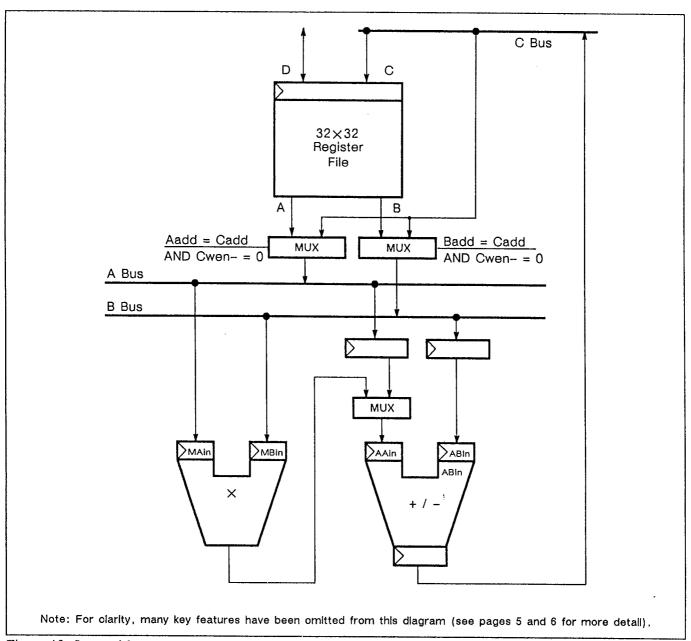

### INTERNAL BYPASS MODE

Figure 18. Internal bypass routes

## Internal Data Routing, continued

A code sequence may often specify the result of one operation to be the operand of a subsequent operation. The WTL 3132/3332 provide several methods of achieving this:

### 1. Internal Bypass Mode disabled

The default mode (M0 = 0 and M11 = 0) of operation is to send the result back to one of the generalpurpose registers and then read the new value of this register as the operand.

Figure 19 shows this code sequence: op #1 specifies .f3 as its destination and op #2-5 all specify .f3 as one of their operands. Because the result of op #1 gets written back to .f3 on its fourth cycle, op #5 is the first of the succeeding operations to read the new contents of .f3 as desired. This represents a registerto-register latency of four cycles.

```

.f1,

op #1 fadd

.f0,

.f2

op #2 fadd

.f2,

.f3,

.f4

-old .f2

.f6

op #3 fadd

.f2.

.f5,

—old .f2

op #4 fadd

.f2,

.f7,

.f8

—old .f2

op #5 fadd

.f2, .f9,

.f10

-new.f2

Notes:

To make this code interruptable, op #2, op #3 and op #4

should not specify .f2 as an operand.

```

Figure 19. No internal bypassing

Full details of this syntax are given on page 32.

#### 2. Internal Bypass Mode enabled

If the Internal Bypass Mode is enabled (M0 = 1) and M11 = 1) then the register-to-register latency is reduced to just three cycles. Figure 18 shows the two internal bypass multiplexers that allow results on the C bus to be copied over to the A or B buses without first being returned to the register file.

Figure 20 shows a code sequence that uses the bypass mode: op #1 specifies .f2 as its destination and op #2-4 all specify .f2 as one of their operands. In contrast to the previous example, op #4 is fed the result of op #1 on the same cycle that the result is written to the register file.

The multiplexers operate by comparing the Aadd and Badd address fields to the Cadd address field as they are presented to the register file on each cycle. If Aadd = Cadd, then the value on the C bus is copied to the A bus; and if Badd = Cadd, then the value on the C bus is copied to the B bus. Enough time remains for that value to be latched into a multiplier/ accumulator input port before the end of the cycle. In the example, the Cadd field of op #1 matches the Aadd field of op #4 as they are compared on the fourth cycle of op #1, the bypass from C to A buses is opened and op #4 can proceed immediately with the new data. During the same cycle, the result is copied into the Cadd register as usual so that the register file remains consistent with the data values in

Setting mode bit M0 = 1 enables the C-to-A bus bypass and setting mode bit M11 = 1 enables the Cto-B bus bypass. If the Cwen- bit of an instruction is set to prevent register writes, then the Internal Bypass Mode is temporarily suspended on the fourth cycle of that operation; this insures that the register file contents are kept in step with the operands used by each instruction. Similarly, the NEUT-, STALL-, and ABORT- signals cause the Internal Bypass Mode to be suspended as they cancel the register write of an instruction.

```

op #1 fadd

.f0,

.f2

.f1,

op #2 fadd

.f2.

.f3,

.f4

-old .f2

op #3 fadd

.f2.

.f5,

.f6

-old .f2

op #4 fadd

.f2,

.f7,

.f8

-new .f2

Notes:

To make this code interruptable, op #2 and op #3 should not

specify .f2 as an operand.

Full details of this syntax are given on page 32.

```

Figure 20. Use of internal bypassing

## PRELIMINARY DATA

October 1987

# Internal Data Routing, continued

Figure 21. The timing of Internal Bypass Mode (M0 = 1 and M11 = 1)

## 3. Temporary Registers

To complete the range of alternative routes available for feeding results back to the multiplier/accumulator, the Treg code example first given in figure 15 is repeated here.

The temporary register option has the same timing as the Internal Bypass Mode, but only feeds back to the ABin port. The Tregs bring an extra source of operands to the multiplier/accumulator, allowing operations of the form  $x = x \pm (y \times z)$  to be executed in a single cycle.

Many of the code examples given read a register after the instruction that modifies it has been initiated. While such code sequences are valid, they are uninterruptable. More detailed coverage of interruptable code may be found on page 33.

```

.t1

.f0,

.f1,

0,

op #1

fmac

.f3,

.t1,

.f4

-old .t1

.f2,

op #2

fmac

--Illegal

.f7

op #3

fmac

.f5,

.f6,

.t1,

.f9,

.f8.

.t1,

.f10 -new .t1

op #4

fmac

```

### Notes:

A Treg cannot be both written and read in the same cycle. Op #3 must never attempt to read the Treg written by op #1,

To make this code interruptable, op #2 and op #3 should not specify ,t1 as an operand.

Full details of this syntax are given on page 32.

Figure 22. Use of temporary registers

## Input/output

The WTL 3132 and WTL 3332 provide different input/output facilities. The WTL 3332 has additional Y and Z ports to increase the bandwidth between the multiplier/accumulator and external components. Sections specific to the WTL 3332 will state this in their headings.

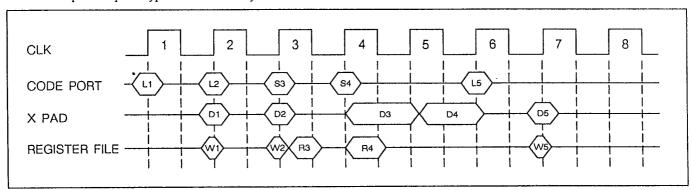

All data I/O ports are 32 bits wide. They can all transfer at least one word on each cycle. The memory-to-memory latency can be as low as five cycles (two more than the register-to-register latency). All output buses may be disabled by de-asserting their asynchronous output enable signals.

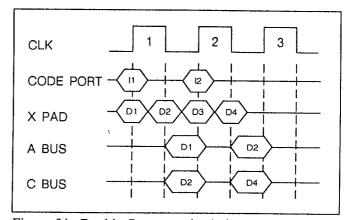

THE X PORT: NORMAL USAGE (WTL 3132 AND WTL 3332)

Figure 23. Normal X port I/O timing

The X port normally transfers data to and from the register file D port. The Dadd field selects the register in question and the IOCt1..0 field in the instruction word controls the transaction. These I/O transfers always begin during the first cycle of an operation. See figure 24 for the IOCt1..0 encoding scheme and figure 23 for normal I/O timing.

- 1. The fload operation loads the value at the X port pins into the register selected by Dadd. It is completed by the end of the first cycle. If the register is read on the same cycle, its previous contents will be output.

- 2. The fstore operation stores the contents of the register selected by Dadd to the X port output register (XDoutR) during the first cycle. This value is driven onto the X port pins on the second cycle. The fstore operation drives the X pads during most of its second cycle and at the start of its third cycle. Input data may not be applied to the pins until partway through its third cycle. The OEX- pin can asynchronously disable the output at any time.

- 3. The floadro operation is described on page 22.

4. The I/O nop operation simply disables the X port and ignores any input. It does not prevent the multiplier/accumulator from writing to registers or modifying the state of the condition and exception outputs.

Note: An fload should not follow a fstore immediately. At least two I/O nop cycles must be inserted between them if the Coprocessor Load Mode is disabled, and at least one I/O nop if it is enabled (see page 27).

| IOCt1-0 | OPERATION |  |

|---------|-----------|--|

| 00      | I/O nop   |  |

| 01 ·    | floadro   |  |

| 10      | fstore    |  |

| 11      | fload     |  |

Figure 24. X port I/O control field encoding

## PRELIMINARY DATA

October 1987

## Input/output, continued

Figure 25. Input/Output Bypass diagram (X port)

## INPUT BYPASS MODE (WTL 3132 AND WTL 3332)

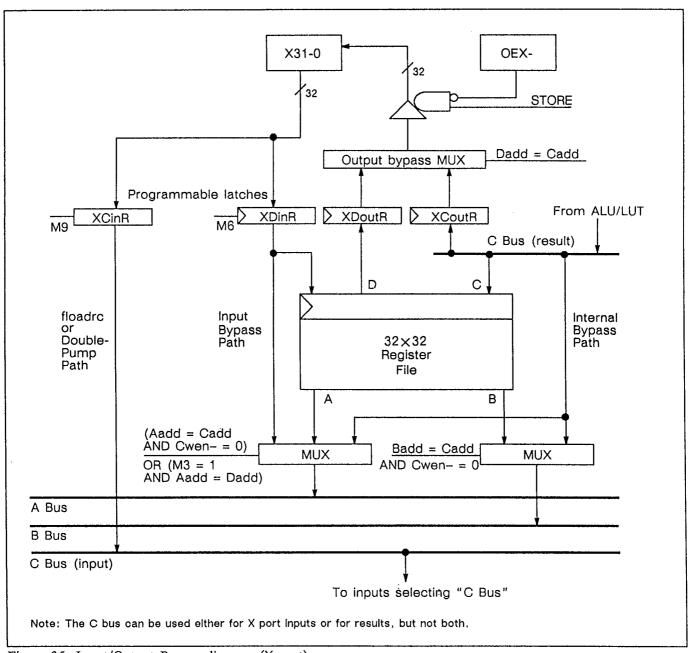

During a normal fload operation the X port data must be written to a register one cycle before it can be used as the operand of a subsequent operation. If, however, the Input Bypass Mode is enabled and Aadd = Dadd; the value at the X port is loaded into both the register selected by Dadd and onto the A bus during the first

The Input Bypass Mode is enabled when bit M3 of the Mode Register is set to 1 (see page 35).

## Input/output, continued

Figure 26. X Port I/O timing (Input and Output Bypass Modes enabled; M3 = 1 and M4 = 1)

The MAin port always receives the input data by the end of the first cycle. If the function is "ALU only", the data is staged into the AAin port during the second cycle.

The Input Bypass Mode should not be enabled when the Coprocessor Load Mode is enabled.

## FLOADRC OPERATION (WTL 3132 AND WTL 3332)

During a normal fload operation the X port data is copied to the D port, and, if the Input Bypass Mode is activated, the A bus. If the floadro operation is used instead, the value at the X port is loaded both into the register selected by Dadd and onto the C bus during the first cycle, where it can be selected by one of the multiplier/accumulator input ports, MBin or ABin.

floadre prevents the multiplier/accumulator from writing the result of a previous instruction to the Cadd register, and the resulting contents of this register are undefined. Results from the divide look-up table preempt the floadro operation and are written to the Cadd register as usual; floadrc still copies the X port value to the Dadd register. The Cwen- control can be set to prevent unwanted writes to the register specified by the Cadd field of an instruction.

If the MBin multiplexer selects the C bus it will receive the X port data by the end of the first cycle. If the ABin multiplexer selects the C bus it will receive the X port

data by the end of the first cycle. Note that the two ports are skewed by one cycle from the programmer's view because the ABin input is not delayed.

floadro should not be used in an interruptable environment.

## **OUTPUT BYPASS MODE** (WTL 3132 AND WTL 3332)

During a normal fstore operation the multiplier/accumulator result must be written to a register one cycle before it can be output to the X port. If, however, the Output Bypass Mode is enabled and Cadd = Dadd; the multiplier/accumulator result is sent to both the register selected by Cadd and the X port output register (XCoutR) on the same cycle.

The Output Bypass Mode is enabled when bit M4 of the Mode Register is set (see page 35).

The fstore instruction that specifies the Dadd must start execution on the fourth cycle of the arithmetic instruction that specified the Cadd. The output appears at the X port pins during the second cycle of the fstore instruction. (See figure 26.)

If the Cwen- bit of an instruction is set to prevent register writes, then the Output Bypass Mode is temporarily suspended on the fourth cycle of that operation. This insures that the register file contents are kept in step with the output data.

### PRELIMINARY DATA

October 1987

## Input/Output, continued

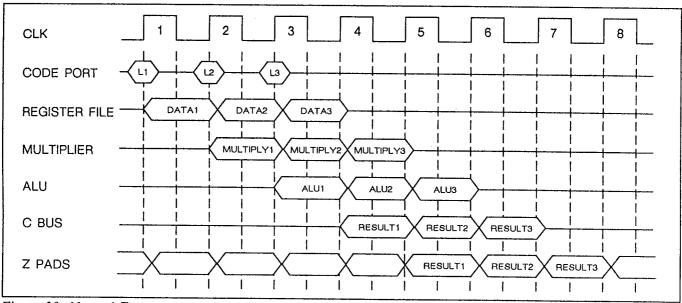

THE Y PORT: NORMAL USAGE (WTL 3332 ONLY)

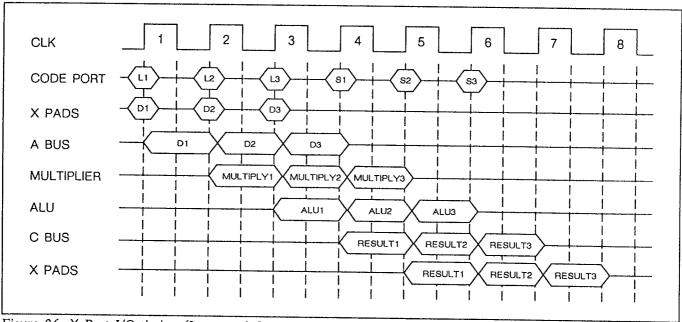

The Y port is an input-only port. The Mbs- bit in the instruction word controls whether the B register file port or the Y input port drives the B bus (see figure 28). If the B port is selected, then the data input at the Y port is discarded.

If the MBin port then selects the B bus as input, the multiplier will receive the Y port data by the end of the first cycle. If the ABin port selects the B bus as input, the ALU will receive the Y port data at the end of the next cycle.

Two external data streams may be fed into the multiplier/accumulator through the X and Y ports without being written to the register file. The Y port data can be fed into the MBin or ABin inputs via the B bus. Meanwhile, the X port data can be fed to the MAin or AAin inputs via the A bus using the Input Bypass Mode. Alternatively, the X port data may be fed into the C bus with the floadro operation.

Figure 27. Normal Y port I/O timing

| Mbs- | B BUS INPUT SOURCE                                |

|------|---------------------------------------------------|

| 0    | Register file (B Port)<br>External input (Y Port) |

Figure 28. Y port input select field encoding

## Y LATE INPUT MODE (WTL 3332 ONLY)

The Y port data may be sampled on the falling edge of CLK instead of its rising edge. This mode is selected by setting bit M12 of the Mode Register to 1 (see page 35). It reduces the delay through the YinR register so that the data still arrives at the multiplier/accumulator ports before the end of the first cycle.

The Y port Late Input Mode can be used to demultiplex a high-bandwidth input bus onto the X and Y ports.

Figure 29. Y port Late Input Mode timing

### THE Z PORT: NORMAL USAGE (WTL 3332 ONLY)

The Z port is an output-only port. It outputs the result of a multiply/accumulate operation directly (see figure 30). The result of a flut operation cannot be output to the Z port.

The Z port output register (ZoutR) is loaded on the fourth cycle of an operation; just when the Cadd register should be written. This transfer occurs without regard to any other activity on the C bus.

The Z port output register then drives this value onto the Z port pins. The output occurs during the fifth cycle of the instruction. The Z port output register is updated on every cycle, even if the multiplier/accumulator result is meaningless. The OEZ- pin can asynchronously float the output at any time.

# Input/Output, continued

Figure 30. Normal Z port output timing

### DOUBLE-PUMP MODE (WTL 3332 ONLY)

The WTL 3332 multiplier/accumulator has four ports. It can be fed an operand through each of the MAin, MBin and ABin inputs and returns a result via the ALU output on every cycle. Only three external ports are provided, X, Y and Z. Double-Pump Mode allows two inputs to be made via the X port on each cycle; all four multiplier/accumulator ports may then be serviced by the external ports.

Double-Pump Mode is enabled by setting bit M9 of the Mode Register to 1 (see page 35). If Double-Pump Mode is enabled, the IOCti..o field in the instruction word must constantly be set to fload.

The first input is latched into the X port on the rising edge of CLK at the beginning of the cycle, as usual. It is written into the Dadd register by the end of the cycle. If the Input Bypass Mode (see above) is enabled and Aadd = Dadd, then this value is also driven onto the A bus and can be latched by the MAin port by the end of the first cycle or the AAin port by the end of the second cycle.

The second input is latched into the X port on the next falling edge of CLK. It is driven onto the C bus and may be latched by the MBin port or the ABin port by the end of the first cycle.

The MBin or ABin port may also receive input data from the Y port via the B bus allowing all three multiplier/accumulator inputs to be fed simultaneously.

The multiplier/accumulator result should be directed to the Z port.

Figure 31. Double-Pump mode timing

## PRELIMINARY DATA

October 1987

## System Interfacing

Certain signals on the WTL 3132 and WTL 3332 are provided to communicate control information to and from the other parts of a system.

Two outputs, FPCN and ZERO, indicate the condition of an operation. They can be sent to a sequencer to control instruction branching.

One output, FPEX, signals the occurrence of arithmetic overflow. It can be used to interrupt a host processor to request corrective action.

Three inputs, NEUT-, STALL- and ABORT-, allow the effects of instructions fed into the C port to be canceled. They can be used to make the WTL 3132/3332 respond correctly to page faults, interrupts or other system requests.

### CONDITION AND ZERO

The WTL 3132/3332 have a Condition Register and a Zero Register. The multiplier/accumulator attempts to modify the contents of these registers on every cycle.

The instruction word includes a two-bit condition select field, Encni...o, which selectively allows the multiplier/ accumulator to succeed in updating the contents of these registers. If both bits are cleared, then the previous state of the registers remains unchanged.

Most functions update the Condition Register according to the sign and magnitude of their result. Miscellaneous functions may set the register for other reasons (see figure 32).

Encn1..0 determines the exact condition that will set the Condition Register for each instruction. This allows any of the common comparisons (>,  $\geq$ , =,  $\leq$ , <) to be made in one operation. Figure 33 gives the bit encod-

If the result of an operation is exactly equal to zero and the Encni..o field is not (0,0); the Zero Register is set to 1. If the result is not zero and Enchino is not (0,0); the Zero Register is cleared to 0. If Encni... is (0,0); the contents of the Zero Register remain the same.

The contents of the Zero and Condition Registers are copied to the ZERO and FPCN outputs respectively on the fourth cycle of the operation, just as the generalpurpose register file write occurs. Bypassing does not affect the timing of these signals. These outputs always drive a logic 0 or 1.

| FUNCTION | SET CONDITION REGISTER                       | SET ZERO REGISTER | SET STATUS REGISTER |

|----------|----------------------------------------------|-------------------|---------------------|

| fmac     | N ≤ 0, N < 0, N = 0                          | N = 0             | exp (N) ≥ 255       |

| fmns     | $N \le 0, N < 0, N = 0$                      | N = 0             | exp (N) ≥ 255       |

| fmna     | $N \le 0, N < 0, N = 0$                      | N = 0             | $exp(N) \ge 255$    |

| fadd     | $N \le 0, N < 0, N = 0$                      | N = 0             | $exp(N) \ge 255$    |

| fsub     | $N \le 0, N < 0, N = 0$                      | N = 0             | exp (N) ≥ 255       |

| fsubr    | $N \le 0, N < 0, N = 0$                      | N = 0             | exp (N) ≥ 255       |

| flut     | -                                            | _                 | -                   |

| fabs     | _                                            | !                 | <del>-</del>        |

| fix      | I M I >2 22                                  |                   | _                   |

| float    | $M < (-2^{23}) \text{ or } M > (2^{23} - 1)$ | _                 | -                   |

| fnop     | _                                            | _                 |                     |

N is the result of an operation; M is the operand.

Note: fix and float only test for operand range excess when M1 = 1.

Figure 32. Effect of functions on Condition, Zero, and Status Register

## System Interfacing, continued

| Encn1 | Encn0 | SET ZERO REGISTER | SET CONDITION REGISTER |

|-------|-------|-------------------|------------------------|

| 0     | 0     |                   | _                      |

| 0     | 1     | N=0               | $N \leq 0$             |

| 1     | 0     | N=0               | N<0                    |

| 1     | 1     | N=0               | N=0                    |

Note: Encn1 and Encn0 must be zero for fnop. Condition Register is set by fix or float when Enchi... o is (0,1) and the operand exceeds the permitted range.

Figure 33. Encn1..0 encoding

#### STATUS AND EXCEPTIONS

The WTL 3132/3332 have a Status Register. If an operation produces a result that is too large to be represented in the IEEE single-precision floating point format the multiplier/accumulator attempts to set the Status Register to 1.

The Mode Register includes an exception control bit, M5 (see page 35). If M5 is set to 1 and an overflow occurs, the Status Register is set to 1. If M5 is cleared to 0, the Status Register is cleared to 0. If M5 is subsequently set to re-enable overflows, the Status Register will contain 0.

The contents of the Status Register are copied to the FPEX output on the fourth cycle of the operation, just as the register file write occurs.

One bit in the Mode Register, M8, selects the polarity of FPEX. If it is set to 1, then FPEX is active high. If it is cleared to 0, then FPEX is active low. If M8 is cleared, the Status Register is "sticky"; once set it will remain so until an folsr operation is performed.

Two miscellaneous functions, fstsr and fclsr, allow the Status Register to be read at the X port or for it to be

cleared. They take effect during their first cycle. If the fstsr operation is performed, then the IOCti..o field must specify a 'store' and its timing is the same as a normal store operation (see figure 34). Only the leastsignificant bit of the Status Register is guaranteed; the other 31 bits should be masked off when it is read. If the fclsr operation is performed, it is complete by the end of its first cycle.

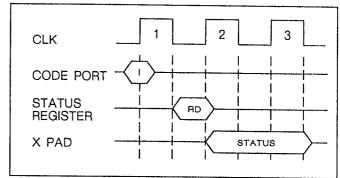

Figure 34, fstsr timing

Figure 34a. Condition/Status timing

## PRELIMINARY DATA

October 1987

## System Interfacing, continued

### COPROCESSOR LOAD MODE

The Coprocessor Load Mode is provided to support systems which generate a data address at the beginning of a cycle and need to latch the data word into the WTL 3132/3332 later in the same cycle.

If bit M6 of the Mode Register is set, then the data applied to the X port is not sampled until late in the first cycle. Time still remains to write the Dadd register before the end of this cycle. As usual, the next instruction can use this data value as one of its operands.

If this mode is used, neither the Double-pump Mode nor the X port Input Bypass Modes may be enabled.

The number of I/O nops that must be inserted between an fstore and a subsequent fload is reduced from two to one.

The STALL- signal timing is modified internally if the Coprocessor Load Mode is enabled so that it still cancels the fload and fstore operations.

This mode must be selected if the WTL 3132 is to be used in the XL environment (see Appendix A).

Figure 35. Coprocessor Load Mode timing

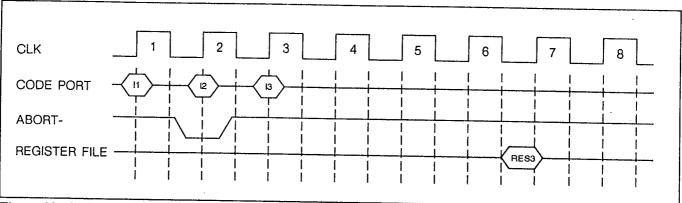

### NEUT-, STALL- AND ABORT-

These three inputs allow a system to modify the effect of certain instructions dynamically.

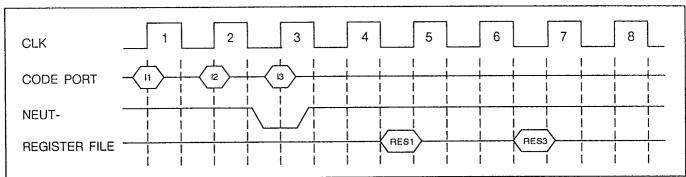

### 1. NEUT-

Neutralize is used to prevent the execution of instructions in the shadow of a delayed branch operation or during an interrupt service cycle.

In a system where the sequencer supports delayed branching, it will present the next instruction to the C port as it decides whether to take a branch. If the branch is taken, this instruction must be cancelled before it has any effect on the state of the system. Similarly, if an interrupt occurs, the instruction due to be executed can be cancelled in order to branch to an interrupt service routine. The cancelled instruction is resubmitted for execution on return from interrupt.

Figure 36. NEUT- timing

The neutralize signal cancels the effect of the current instruction. It prevents the result of this instruction from being written into the register file or temporary registers. It has no effect on fload or fstore operations. This signal is sampled on the rising edge of CLK after the current instruction was fed into the C port.

WEITEK CORP 02

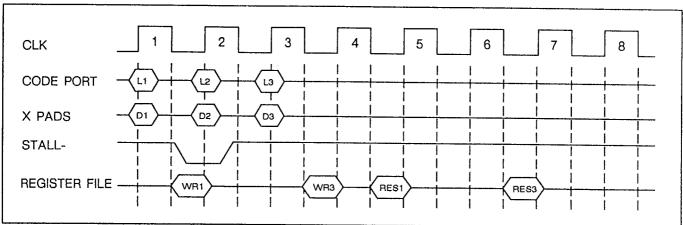

### 2. STALL-

STALL- is used to hold off execution until a valid code word is present when the code word is delayed (as in a code memory refresh cycle) or absent (as in a page fault). The next operation can be continually stalled until the correct instruction word is presented to the C port.

The STALL- signal cancels the effect of the next instruction. It prevents the result of this instruction from being written into the register file or temporary registers. It also cancels fload and fstore operations. This signal is sampled at the same time as the next instruction is fed into the C port.

If Coprocessor Load Mode is enabled, the timing of STALL- is modified internally to maintain its usual effect. The fmode and folsr instructions are also properly stalled.

Figure 37. STALL- timing (including fload)

Figure 38. STALL- timing (including fstore)

PRELIMINARY DATA

October 1987

## System Interfacing, continued

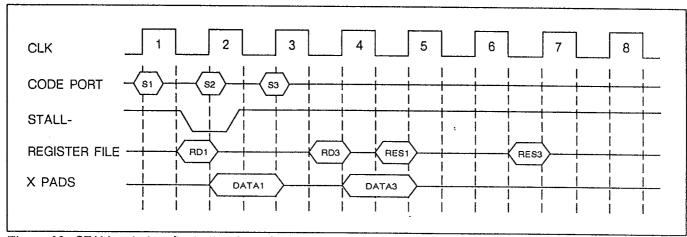

### 3. ABORT-

ABORT— is used to cancel the current and next instructions when the data word is delayed (as in a cache miss) or absent (as in a page fault). If the two cancelled instructions are subsequently resubmitted for execution the processor will behave as if no interrupt occurred.

The ABORT- signal cancels the effect of both the current and next instructions. It prevents the results of these instructions from being written into the register file or temporary registers. It also cancels the I/O operation specified in the next instruction, but not in the current instruction. This signal is sampled at the same time as the next instruction is fed into the C port.

All three of these signals are delayed internally when necessary: for example, the Cadd register write is only disabled on the instruction's fourth cycle. They prevent the cancelled instructions from modifying the Condition or Status Registers, thus preventing the state of the FPCN, FPEX and ZERO outputs from changing.

Figure 39. ABORT- timing

# **Instruction Set**

| C BIT | FIELD | OPERATION               |

|-------|-------|-------------------------|

| 0     | Encn0 | Condition Output Select |

| 1     | Encn1 | ·                       |

| 2     | Mbin- | MBin Input Select       |

| 3     | Adst0 | ALU Destination Select  |

| 4     | Adst1 |                         |

| 5     | Abin0 | ABin Input Select       |

| 6     | Abin1 |                         |

| 7     | Abin2 |                         |

| 8     | Dadd0 | D Port Register Address |

| 9     | Dadd1 |                         |

| 10    | Dadd2 |                         |

| 11    | Dadd3 |                         |

| 12    | Dadd4 |                         |

| 13    | IOCt0 | I/O Control             |

| 14    | IOCt1 |                         |

| 15    | Cwen- | C Port Write Enable     |

| 16    | Cadd0 | C Port Register Address |

| 17    | Cadd1 |                         |

| 18    | Cadd2 |                         |

| 19    | Cadd3 |                         |

| 20    | Cadd4 |                         |

| 21    | Badd0 | B Port Register Address |

| 22    | Badd1 |                         |

| 23    | Badd2 |                         |

| 24    | Badd3 |                         |

| 25    | Badd4 |                         |

| 26    | Aadd0 | A Port Register Address |

| 27    | Aadd1 |                         |

| 28    | Aadd2 |                         |

| 29    | Aadd3 |                         |

| 30    | Aadd4 |                         |

| 31    | F0    | Function Code           |

| 32    | F1    | <b>!</b>                |

| 33    | F2    |                         |

| 34    | Mbs-  | Y Port Input Select*    |

\*Only on WTL 3332

Figure 40. Instruction format

### PRELIMINARY DATA

October 1987

### Instruction Set, continued

#### **FORMAT**

The WTL 3132 has a 34-bit instruction word. The WTL 3332 has a 35-bit instruction word because it requires the extra Mbs- bit to control the Y port input. Refer to figure 40 for the location of each field in the instruction word.

### 1. Mbs-bit. (WTL 3332 only)

B bus input control bit. May be register file port B or external input port Y.

#### 2. F field.

Function control (F2..0) field. Selects function to be performed on this instruction's operands.

#### 3. Aadd field.

A register address (Aadd4..0) field. Selects location in general-purpose register file to be read out via the A port.

#### 4. Badd field.

B register address (Badd4..0) field. Selects location in general-purpose register file to be read out via the B port. Also encodes miscellaneous functions that require only one operand.

### 5. Cadd field.

C register address (Cadd4..0) field. Selects location in general-purpose register file to be written into via the C port.

## 6. Cwen- bit.

C port write enable bit. Active low.

#### 7. IOCt field.

I/O control (IOCt1..0) field. Selects type of I/O transfer performed via D port.

#### 8. Dadd field.

D register address (Dadd4..0) field. Selects location in general-purpose register file to be read out or written into via the D port.

### 9. Abin field.

ALU input multiplexer input control (Abin2..0) field. Selects the input source for ALU.

#### 10. Adst field.

ALU output destination control (Adst...o) field. Selects output destination for ALU. May be the C bus or the C bus and a Temporary Register.

#### 11. Mbin- bit.

MBin port input control bit. Selects multiplier input source. May be the B bus or C bus.

### 12. Encn field.

Condition select (Encn1..0) field. Enables a selectable combination of the condition and zero flags onto the FPCN output.

All of the actions specified by these fields are defined in the same instruction word. In this way, all of the stages of an operation, from supplying its operands to storing its results back into a register, are specified together.

## Instruction Set, continued

#### **MNEMONICS**

The mnemonics shown in figures 41 through 43 are those used to control the XL-3132 in the XL-Series programming environment. They are given here to simplify understanding of the programming model and to provide a syntax in which to present the programming examples.

These mnemonics represent a subset of the functions available on the WTL 3132/3332. In particular, the Input Bypass Mode is disabled and the Output Bypass, Internal Bypass, and Coprocessor Load Modes are enabled unless otherwise noted. The user is free to enhance or disregard this suggested programming model according to system requirements.

| I/O SELECTION | OPERAND · |             |

|---------------|-----------|-------------|

|               | Source    | Destination |

| fload         | X port    | .f0-31      |

| fstore        | .f0-31    | X port      |

Note: If no I/O operation is specified, an I/O nop will be selected in the IOCt1..0 instruction field.

Figure 41. Recommended mnemonics

| OPERAND NOTATION          | DESCRIPTION                                                                                          |  |

|---------------------------|------------------------------------------------------------------------------------------------------|--|

| .f0-31<br>0<br>2<br>.t1-3 | Thirty-two, 32-bit general purpose registers Constant "0.0" Constant "2.0" Three temporary registers |  |

Figure 42. Recommended mnemonics

| FUNCTION     | OPERAND SELECTIONS |                        |                                  |                                            |

|--------------|--------------------|------------------------|----------------------------------|--------------------------------------------|

| PONCTION     | SOURCE (Aadd)      | . SOURCE (Badd)        | SOURCE (Tregs)                   | DESTINATION (Cadd)                         |

| fmac<br>fmns | .f0-31             | .f0-31<br>.f0-31       | 0, 2, or .t1-3                   | .f0-31 and/or .t1-3                        |

| fmna         | .f0-31             | .f0-31                 | 0, 2, or .t1-3<br>0, 2, or .t1-3 | .f0-31 and/or .t1-3<br>.f0-31 and/or .t1-3 |

| fadd<br>fsub | .f0-31             | .f0-31, 0, 2, or .t1-3 |                                  | .f0-31 and/or .t1-3                        |

| fsubr        | .f0-31             | .f0-31, 0, 2, or .t1-3 |                                  | .f0-31 and/or .t1-3                        |

| flut<br>fabs | .f0-31<br>.f0-31   |                        | ,                                | .f0-31<br>.f0-31 and/or .t1-3              |

| fix<br>float | .f0-31<br>.f0-31   |                        |                                  | .f0-31 and/or .t1-3                        |

| fnop         | -                  |                        |                                  | TO OT ANOTOLITY                            |

Figure 43. Recommended mnemonics

## PRELIMINARY DATA

October 1987

## Instruction Set, continued

### CODE CONSTRAINTS

The following set of rules prevents illegal code sequences:

1. All instructions must avoid writing to the Cadd register and Dadd register simultaneously. Thus no fload operation with Dadd = .fx may start on the fourth cycle of an operation with Cadd = .fx.

```

op #1 fadd .f?, .f?, .fx

op #2 fadd .f?, .f?, .f?;

fload.fx

op #3 fadd .f?, .f?, .f?;

fload.fx

op #4 fadd .f?, .f?, .f?;

fload.fx

--Illegal

op #5 fadd .f?, .f?, .f?;

fload.fx

```

Figure 44.

2. Because the X port output is driven on the cycle after an fstore operation is specified, an fload cannot follow an fstore immediately. At least one I/O nop must intervene if the Coprocessor Load Mode is enabled (M6 = 1), or two I/O nops if it is disabled (M6 = 0) (see page 27).

```

op #1 fadd .f?, .f?,

.f?; .fstore.f?

op #2 fadd .f?, .f?,

.f?; .fload.f? -Illegal

op #3 fadd .f?, .f?, .f?; .fload.f?

```

Figure 45. Coprocessor Load Mode enabled, M6=1

```

op #1 fadd .f?, .f?, .f?;

fstore.f?

op #2 fadd .f?, .f?,

.f?;

fload.f? --Illegal

op #3 fadd .f?, .f?,

.f?;

fload.f? -Illegal

op #4 fadd .f?, .f?,

.f?:

fload.f?

```

Figure 46. Coprocessor Load Mode disabled, M6=0

3. No temporary register can be written and read on the same cycle. Thus no operation that selects .tx as an operand register may start on the third cycle of an operation with Cadd = .tx.

```

op #1 fmac .f?, .f?,

.tx

op #2 fmac .f?, .f?,

.f?

.tx.

op #3 fmac .f?, .f?,

.tx.

.f?

-Illegal

op #4 fmac .f?, .f?,

٠tx,

.f?

```

Figure 47. Coprocessor Load Mode disabled, M6=0

## Instruction Set, continued

If code is to be interruptable and respond correctly to the NEUT-, STALL- and ABORT- signals, then these additional rules must also be followed. They all prevent delayed register writes from modifying operand values in a time-dependent fashion.

4. No operation with Aadd or Badd = .fx may start after the first cycle and before the fourth cycle of an operation with Cadd = .fx. (If the Internal Bypass Mode is disabled (M0 = 0 and M11 = 0), this becomes the fifth cycle).

```

op #1 fadd .f?, .f?,

.f? --Illegal

op #2 fadd .fx, .f?,

op #3 fadd

.fx, .f?,

.f? —Illegal

op #4 fadd .fx, .f?, .f?

```

Figure 48. Internal Bypass Mode enabled, M0 = 1 and M11 = 1

```

op #1 fadd .f?, .f?, .fx

op #2 fadd .fx, .f?, .f? -Illegal

op #3 fadd .fx, .f?,

.f? --Illegal

op #4 fadd .fx, .f?,

.f? -Illegal

op #5 fadd .fx, .f?,

```

Figure 49. Internal Bypass Mode disabled, M0 = 0 and M11 = 0

5. No operation that selects .tx as an operand register may start after the first cycle and before the fourth cycle of an operation with Cadd = .tx.

```

op #1 fmac .f?, .f?, 0, .tx

op #2 fmac .f?, .f?, .tx, .f? --Illegal

op #3 fmac .f?, .f?, .tx, .f? —Illegal

op #4 fmac .f?, .f?, .tx, .f?

```

Figure 50.

6. No operation with Aadd or Badd = .fx may start on the same cycle as an fload where Dadd = .fx.

```

op #1 fadd .fx, .f?, .f?; fload.fx --Illegal

op #2 fadd .f?, .f?, .f?

```

Figure 51.

7. The NEUT- line does not cancel fload and fstore, so when it is used to cancel the effect of an instruction in the shadow of a delayed branch operation (as in the XL-Series), this instruction should not perform I/O transfers. (This is not necessary when NEUT- is asserted during an interrupt response cycle because the cancelled instruction is resubmitted for execution.)

In the examples, the notation .f? is used to indicate any register except .fx.

PRELIMINARY DATA

October 1987

### Initialization

#### MODE REGISTER

The Mode Register controls which of the special modes are enabled. Normally, it is initialized to the desired state and is not subsequently altered. Some mode bits are provided to maintain backward compatibility with previous versions of the WTL 3132/3332. Other bits are reserved and should be set to the value specified in figure 52.

| MODE BIT | LOGIC VALUE | DESCRIPTION                                 |

|----------|-------------|---------------------------------------------|

| МО       | 0           | Internal Bypass Mode (Aadd = Cadd) disabled |

|          | 1           | Internal Bypass Mode (Aadd = Cadd) enabled  |

| M1       | 0           | fix rounds to negative infinity             |

|          | 1           | fix rounds to nearest (enable range test)   |

| M2       | _           | Reserved: should be cleared to 0            |

| M3       | 0           | Input Bypass Mode disabled                  |

|          | 1           | Input Bypass Mode enabled                   |

| M4       | 0           | Output Bypass Mode disabled                 |

|          | 1           | Output Bypass Mode enabled                  |

| M5       | 0           | FPEX Output disabled                        |

|          | 1           | FPEX Output enabled                         |

| M6       | 0           | Co-processor Load Mode disabled             |

|          | 1           | Co-processor Load Mode enabled              |

| M7       | · _         | Reserved: should be set to 1                |

| М8       | 0           | FPEX active low and "sticky"                |

|          | 1           | FPEX active high                            |

| M9       | 0           | Double-pump Mode disabled                   |

|          | 1           | Double-pump Mode enabled                    |

| M10      | -           | Reserved: should be set to 1                |

| M11      | 0           | Internal Bypass Mode (Badd = Cadd) disabled |

|          | 1           | Internal Bypass Mode (Badd = Cadd) enabled  |

| M12      | 0           | Y Late Input Mode disabled                  |

|          | 1           | Y Late Input Mode enabled                   |

Figure 52. Mode selection table

## Initialization, continued

The Mode Register is loaded by the fmode operation. This causes the Aadd, Cadd and ABin2..o fields in the instruction word to be loaded into the Mode Register

WEITEK CORP 02

as shown by figure 53. fmode completes by the end of its first cycle.

| C BIT | NORMAL USE | MODE BIT | COMMENT                         |

|-------|------------|----------|---------------------------------|

| 0     | Encn0      | 0        | FPCN is disabled during fmode   |

| 1     | Encn1      | 0        |                                 |

| 2     | Mbin-      | 0        |                                 |

| 3     | Adst0      | 1        | ALU destination is C bus only   |

| 4     | Adst1      | 1        |                                 |

| 5     | Abin0      | M10      |                                 |

| 6     | Abin1      | M11      |                                 |

| 7     | Abin2      | M12      |                                 |

| 8     | Dadd0      | 0        |                                 |

| 9     | Dadd1      | 0        | ·                               |

| 10    | Dadd2      | 0        |                                 |

| 11    | Dadd3      | 0        |                                 |

| 12    | Dadd4      | 0        |                                 |

| 13    | IOCt0      | 0        | I/O nop specified               |

| 14    | IOCt1      | 0        |                                 |

| 15    | Cwen-      | 1        | C port register writes disabled |

| 16    | Cadd0      | M5       | · ·                             |

| 17    | Cadd1      | M6       |                                 |

| 18    | Cadd2      | M7       |                                 |

| 19    | Cadd3      | M8       |                                 |

| 20    | Cadd4      | M9       |                                 |

| 21    | Badd0      | 1        | fmode function code             |

| 22    | Badd1      | 1        |                                 |

| 23    | Badd2      | 0        |                                 |

| 24    | Badd3      | 0        |                                 |

| 25    | Badd4      | 0        |                                 |

| 26    | Aadd0      | MO       |                                 |

| 27    | Aadd1      | M1       | ,                               |

| 28    | Aadd2      | M2       |                                 |

| 29    | Aadd3      | M3       |                                 |

| 30    | Aadd4      | M4       |                                 |

| 31    | F0         | 0        | Miscellaneous function selector |

| 32    | F1         | 0        |                                 |

| 33    | F2         | 0        |                                 |

| 34    | Mbs-*      | Ō        |                                 |

Figure 53. Load Mode Register instruction format

## PRELIMINARY DATA

October 1987

#### Initialization, continued

Changing the contents of any bits in the Mode Register will have undefined effects on any currently executing instructions including I/O operations. The state of all registers should be initialized after execution of the fmode instruction.

Some combinations of modes are not allowed. These are detailed in figure 54.

| MODE #                                   | (1) | (2)        | (3)   | (4)      | (5)  | (6) | (7) | (8)      |            |

|------------------------------------------|-----|------------|-------|----------|------|-----|-----|----------|------------|

| Internal Bypass Mode (M0 = 1 and M1 = 1) | (1) | _          | ~     | ~        | ~    | ×   | 1   | ×        | 1          |

| Input Bypass Mode (M3 = 1)               | (2) | 1          | _     | ~        | 1    | 1   | ×   | ~        | 1          |

| Output Bypass Mode (M4 = 1)              | (3) | 1          | 1     |          | 1    | ×   | ~   | <i>~</i> | 1          |

| Y Late Input Mode (M12 = 1)              | (4) | <u>س</u>   | 1     | <i>~</i> | _    | 1   | ~   | · ·      | <u>س</u> ا |

| Double-Pump Mode (M9 = 1)                | (5) | ×          | ~     | ×        | ~    | _   | ×   | <i>~</i> | ×          |

| Coprocessor Load Mode (M6 = 1)           | (6) | <u>س</u> ا | ×     | 1        | ~    | ×   | _   | ×        | w          |

| Use of floadrc Operation                 | (7) | ×          | 1     | ~        | \ \r | ~   | ×   | _        | ×          |

| Use of NEUT-, STALL-, or ABORT- Inputs   | (8) | ~          | \ \ru | ~        | ~    | ×   | 1   | ×        | _          |

|                                          |     |            |       |          |      |     |     |          |            |

x = Should not be enabled together,  $\nu =$  Can be enabled together

Note: Although (7) and (8) are not selected by mode bits, the user is able to avoid the use of such functions or control lines.

Double-Pump Mode (5) requires floadrc (7) to be used every cycle.

Figure 54. Mode exclusion table

### RESET SEQUENCE

Before initializing the contents of the Mode Register, the WTL 3132/ 3332 must be set to a stable state after power up.

Repeating nop and I/O nop instructions for at least four cycles will flush the multiplier/accumulator pipeline and allow the internal states to become well-defined. Until this sequence terminates, the rest of the system

should ignore the contents of the data buses and the state of the ZERO, FPCN and FPEX pins.

The registers should then all be initialized to known values (including the Mode, Condition, Status and Tregs) while nops continue to be input. The WTL 3132/3332 is then able to begin normal operation.

#### Division

#### DIVIDE LOGIC UNIT

The WTL 3132/3332 have a divide logic unit. This unit consists of a look-up table ROM and three delay stages. The first cycle of the flut operation transfers the Aadd operand (a) to the divide logic unit. During the next two cycles this operand selects a seed value for the reciprocal of the operand (1/a) from the look-up table. This result is written to the Cadd register on the fourth cycle.

If the Internal Bypass Mode is enabled, the result can be copied to a multiplier/accumulator input port at the same time that the Cadd register is being written.

The look-up result is an IEEE single-precision number whose fraction is accurate to seven bits of precision. If the input is positive or negative infinity (greater than #7F800000 or less than #FF800000), the result is zero. If the input is zero, the result is #7FFFFFFF (which gets clamped to #7F800000 during refinement). flut does not update the Zero, Condition, or Status Registers.

#### NOTATION:

a = divisor (.f1)

$R_0 = \text{seed for } 1/a \text{ (.f31)}$

$R_1 =$ first approximation (.f31)

$R_2$  = second approximation (.f30)

b = dividend (.f0)

b/a = result (.f0)

#### ALGORITHM:

$R_1 = R_0 \times (2 - a \times R_0)$

$R2 = R1 \times (2 - a \times R1)$

| Cycle # | Opcode |       |       |    |      | 1/0          | Comment                               |

|---------|--------|-------|-------|----|------|--------------|---------------------------------------|

| 1       | flut   | .f1,  |       |    | .f31 |              | Ro (≃1/a)                             |

| 2       | fnop   |       |       |    |      |              |                                       |

| 3       | fnop   |       |       |    |      |              |                                       |

| 4       | fmna   | .f1,  | .f31, | 2, | .f30 |              | 2 - a × Ro                            |

| 5       | fnop   |       |       |    |      |              |                                       |

| 6       | fnop   |       |       |    |      |              |                                       |

| 7       | fmac   | .f31, | .f30, | 0, | .f31 |              | $R_1 = R_0 \times (2 - a \times R_0)$ |

| 8       | fnop   |       |       |    |      |              |                                       |

| 9       | fnop   |       |       |    |      |              |                                       |

| 10      | fmna   | .f1,  | .f31, | 2, | .f30 |              | $2-a \times R_1$                      |

| 11      | fnop   |       |       |    |      |              |                                       |

| 12      | fnop   |       |       |    |      | •            |                                       |