# JTAG Programmer Guide

Introduction

**Hardware**

JTAG Programmer Tutorial

**Designing Boundary Scan** and ISP Systems

**Boundary Scan Basics**

JTAG Parallel Download Cable Schematic

**Troubleshooting Guide**

**Error Messages**

Using the Command Line Interface

Standard Methodologies for Instantiating the BSCAN

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A. Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CORE Generator, CoreGenerator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Foundation, HardWire, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI 64/66, SelectI/O, Select-RAM, Select-RAM+, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaBlock, VersaRing, Virtex, WebLINX, XABEL, XACT*step*, XACT*step* Advanced, XACT*step* Foundry, XACT-Ploorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,500,609; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,000; 5,500,0005,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235; 5,737,631; 5,742,178; 5,742,531; 5,744,974; 5,744,979; 5,744,995; 5,748,942; 5,748,979; 5,752,006; 5,752,035; 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479;

5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1999 Xilinx, Inc. All Rights Reserved.

# **About This Manual**

This manual describes Xilinx's JTAG Programmer software, a tool used for In-system programming.

Before using this manual, you should be familiar with the operations that are common to all Xilinx's software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*.

### **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this page. You can also directly access some of these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                 |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tutorial             | Tutorials covering Xilinx design flows, from design entry to verification and debugging http://support.xilinx.com/support/techsup/tutorials/index.htm                                                                                                           |  |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                        |  |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                  |  |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which describe device-specific information on Xilinx device characteristics, including readback, boundary scan, configuration, length count, and debugging http://support.xilinx.com/partinfo/databook.htm |  |

| Resource       | Description/URL                                                                                                                               |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Xcell Journals | Quarterly journals for Xilinx programmable logic users http://support.xilinx.com/xcell/xcell.htm                                              |

| Tech Tips      | Latest news, design tips, and patch information on the Xilinx design environment http://support.xilinx.com/support/techsup/journals/index.htm |

### **Manual Contents**

This manual covers the following topics.

- "Introduction" chapter describes JTAG Programmer software.

- "Hardware" chapter provides information for connecting and using the XChecker Serial Cable or the Parallel Download Cable for system operation.

- "JTAG Programmer Tutorial" chapter documents the basic tasks needed to download programming to XC9500/XL/XV family devices in-system.

- "Designing Systems with FPGA's Enabled for Boundary-Scan Operations" chapter documents using the JTAG Programmer with FPGA devices.

- "Boundary Scan Basics" appendix contains reference information about boundary scan basics.

- "JTAG Parallel Download Cable Schematic" appendix has schematics for the XChecker Cable and the Parallel Download Cable.

- "Troubleshooting Guide" appendix contains troubleshooting information.

- "Error Messages" appendix provides a list of error messages that the JTAG Programmer may report. For most error messages a workaround is suggested.

- "Using the Command Line Interface" appendix documents the basics of using the JTAG Programmer from a command line in a workstation environment.

- "Standard Methodologies for Instantiating the BSCAN Symbol" appendix contains programming examples.

### **Conventions**

This manual uses the following typographical and online document conventions. An example illustrates each typographical convention.

## **Typographical**

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: -100

```

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

```

rpt_del_net=

```

Courier bold also indicates commands that you select from a menu.

```

\mathtt{File} \to \mathtt{Open}

```

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

· References to other manuals

See the *Development System Reference Guide* for more information.

Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

```

lowpwr ={on | off}

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

```

allow block block_name loc1 loc2 . . . locn;

```

### **Online Document**

The following conventions are used for online documents.

- Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a cross-reference within a book. Click the blue-underlined text to open the specified cross-reference.

# **Chapter 1**

### Introduction

This chapter introduces you to the basic concepts of Xilinx JTAG capabilities and Xilinx in-system programmable products. You can use JTAG Programmer to download, read back and verify design configuration data, to perform functional tests on any device, and to probe internal logic states of a Xilinx XC9500, XC9500XL, XC9500XV, Spartan or Virtex design. This chapter contains the following sections:

- "Programming and Verification Overview"

- "Required Files"

# **Programming and Verification Overview**

JTAG Programmer software uses sequences of JTAG instructions to perform the following programming and verification operations. The user need only select the desired operation; the software will execute all required JTAG commands transparently. For a description of JTAG instructions supported by Xilinx devices, see Appendix A.

Device operation options available to users are:

**Program**. Downloads the contents of the JEDEC or BIT file to the device programming registers.

**Verify**. Reads back the contents of the device programming registers and compares them with the JEDEC or BIT file.

Erase. Clears device configuration information.

**Functional Test**. Applies user-specified functional vectors from the JEDEC file to the device using the JTAG INTEST instruction, comparing results obtained against expected values. Reports any differences to the user.

**Blank Check**. Checks whether a device has been programmed or is erased.

**Readback Jedec**. Reads back the contents of device programming registers and creates a new JEDEC file with the results.

**Get Device ID**. Reads the contents of the JTAG IDCODE register. Displays contents for the user.

**Get Device Checksum**. Reads back the contents of device programming registers and calculates a checksum for comparison against the expected value.

**Get Device Signature/Usercode.** This value is selected by the user during fitting. The specified value is translated to binary values in the JEDEC file. During device programming these values are loaded into the JTAG USERCODE register. This function reads the contents of the USERCODE register and displays the result.

**Bypass**. Ignores this device when addressing devices in the JTAG boundary scan chain. This option is only available through chain operations.

### **Non-Volatile Device Data Security**

Any Xilinx XC9500/XL/XV device selected for programming can be secured with the Write Protect or Read Protect or both.

When enabled, Read Protect disables reading the programmed contents of a device (the IDCODE and USERCODE registers remain readable).

**Write Protect** allows only the reading of the programmed data. The device contents cannot be altered or re-programmed.

When both Read Protect and Write Protect are enabled, the device can be neither read nor re-programmed.

**Note:** Security options do not affect the accessibility of the bypass or boundary-scan register.

#### **User Feedback**

When using the graphical user interface, immediate feedback is provided by a scrolling log file and alert boxes. Detailed information regarding failure is located in the system log file, and is provided for both the PC and workstation based tool.

### **Required Files**

You need to provide JEDEC files for each XC9500/XL/XV CPLD device, BIT files for each Xilinx FPGA device (Virtex or Spartan) in the JTAG programming chain, and BSDL files for the remaining devices.

#### **JEDEC Files**

JEDEC files are XC9500/XL/XV CPLD programming files generated by the Xilinx fitter. They are ASCII text files containing programming information and, optionally, functional test vectors that can be used to verify the correct functional behavior of the programmed device. One JEDEC file is required for each XC9500/XL/XV device in the JTAG programming chain.

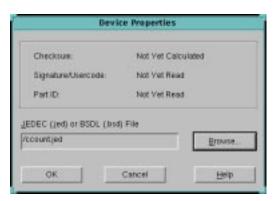

Use the device properties (File  $\rightarrow$  Properties) dialog to specify the location of JEDEC files for each XC9500/XL/XV device. The name of the JEDEC file is assumed to be <design name>.jed, but can be specified exactly by the user.

### **BSDL Summary**

The Boundary-Scan Description Language (BSDL) files use a subset of VHDL to describe the boundary scan features of a device. The JTAG Programmer automatically extracts the length of the instruction register from the BSDL file to place non-XC9500/XL/XV devices in bypass mode. One user-provided BSDL file is required for each type of non-XC9500/XL/XV device in the JTAG programming chain. XC9500/XL/XV BSDL files are located automatically by the JTAG Programmer.

Use the device properties dialog to specify the location of BSDL files for non-XC9500/XL/XV devices. The name of the BSDL file is assumed to be <device name>.bsd.

#### **BIT Files**

Bit files are Xilinx FPGA configuration files generated by the Xilinx FPGA design software. They are proprietary format binary files containing configuration information. One BIT file is required for each Xilinx FPGA in the JTAG boundary-scan chain.

Use the device properties (File  $\rightarrow$  Properties) dialog to specify the location of the BIT files for each Xilinx FPGA device. The required extension for BIT files is .bit.

### **Hardware**

This chapter gives specific information about using cables to download from the JTAG Programmer to devices in-system.

This chapter contains the following sections:

- "Download Cables" section

- "XChecker Hardware (Serial)" section

- "Parallel Cable" section

- "Flying Lead Connectors" section

- "Power Up Sequencing" section

#### **Download Cables**

There are two cables available for use with the JTAG Programmer. The first is an RS232 serial cable known as the XChecker Cable. The second is the Parallel Download Cable which can be connected to a PC's parallel printer port.

There are a few advantages to be considered in selecting a cable:

- The XChecker Cable connects to the serial port of both workstations and PCs.

- The Parallel Cable has better drive capability. The Parallel Cable can drive up to 10 XC9500/XL/XV devices in a boundary-scan chain, and the XChecker Cable can drive up to 4 XC9500/XL/XV devices.

- The Parallel Cable is at least 5 times faster.

**Note:** If you have a Parallel Download Cable proceed to *Parallel Cable*.

### **XChecker Hardware (Serial)**

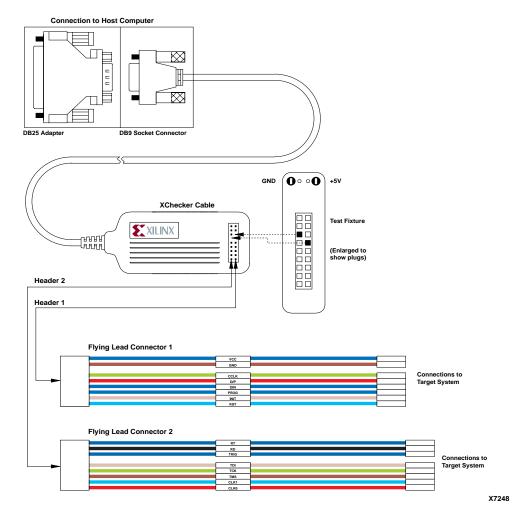

The XChecker hardware consists of a cable assembly with internal logic, a test fixture, and a set of headers to connect the cable to your target system.

Using the XChecker hardware requires either a standard DB-9 or DB-25 RS-232 serial port. If you have a different serial port connection, you need to provide the appropriate adapter. "XChecker Hardware and Accessories" figure shows the XChecker cable hardware and accessories.

The XChecker cable can be used with a single CPLD or several devices connected in a boundary-scan chain to download and read-back configuration and boundary-scan data.

Figure 2-1 XChecker Hardware and Accessories

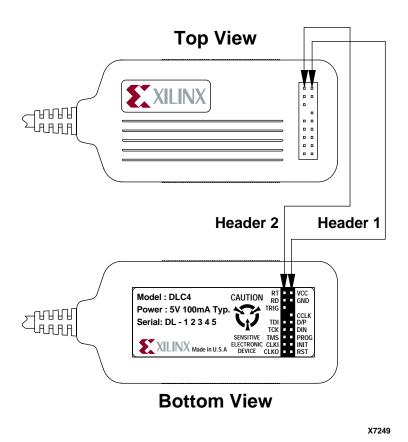

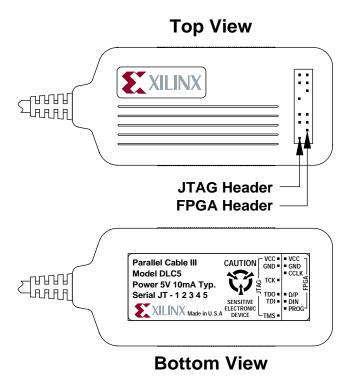

"XChecker Cable" figure shows top and bottom views of the XChecker cable.

### **XChecker Cable**

Figure 2-2 XChecker Cable

### **Connecting for System Operation**

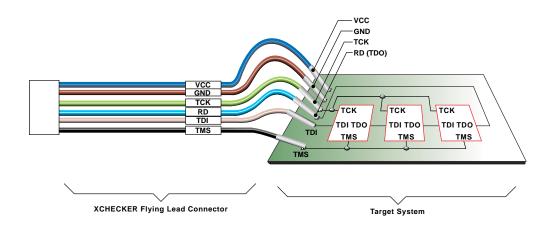

Connect the XChecker cable to the host system and your target system as shown in "XChecker Connections to JTAG Boundary-scan TAP" figure.

X7976

Figure 2-3 XChecker Connections to JTAG Boundary-scan TAP

#### **Cable Connections**

Connections between the cable assembly and the target system use only 6 of the sixteen leads. For connection to JTAG boundary-scan systems you need only ensure that the VCC, GND, TDI, TCK, TMS and RD (TDO) pins are connected.

Once installed properly, the connectors provide power to the cable, allow download and readback of configuration data, and provide for logic probe of device pins.

"XChecker Cable Connections and Definitions" table describes the pin connections to the target circuit board.

Table 2-1 XChecker Cable Connections and Definitions

| Name | Function                                                         | Connections                      |

|------|------------------------------------------------------------------|----------------------------------|

| VCC  | Power – Supplies $V_{CC}$ (5 V, 100 mA, typically) to the cable. | To target system V <sub>CC</sub> |

| GND  | Ground – Supplies ground reference to the cable.                 | To target system ground          |

Table 2-1 XChecker Cable Connections and Definitions

| Name     | Function                                                                                       | Connections                |

|----------|------------------------------------------------------------------------------------------------|----------------------------|

| RD (TDO) | Read Data – Read back<br>data from the target<br>system is read at this pin.                   | Connect to system TDO pin. |

| TDI      | Test Data In – this signal is used to transmit serial test instructions and data.              | Connect to system TDI pin. |

| TCK      | Test Clock – this clock<br>drives the test logic for all<br>devices on boundary-scan<br>chain. | Connect to system TCK pin. |

| TMS      | Test Mode Select – this signal is decoded by the TAP controller to control test operations.    | Connect to system TMS pin. |

| CLKI     | Not used.                                                                                      | Unconnected.               |

| CLKO     | Not used.                                                                                      | Unconnected.               |

| CCLK     | Not used.                                                                                      | Unconnected.               |

| D/P      | Not used.                                                                                      | Unconnected.               |

| DIN      | Not used.                                                                                      | Unconnected.               |

| PROG     | Not used.                                                                                      | Unconnected.               |

| INIT     | Not used.                                                                                      | Unconnected.               |

| RST      | Not used.                                                                                      | Unconnected.               |

| RT       | Not used.                                                                                      | Unconnected.               |

| TRIG     | Not used.                                                                                      | Unconnected.               |

#### **Baud Rates**

The XChecker Cable supports Baud rates as shown in Table 2-2.

Table 2-2 Valid Baud Rates

| Platform | 9600 | 19200 | 38400 |

|----------|------|-------|-------|

| IBM PC   | X    | X     | X     |

| SUN      | X    | X     | X     |

| HP 700   | X    | X     | X     |

### **Connecting the XChecker Cable**

There are two simple steps for connecting the cable:

- 1. Connect the cable to your host system serial port.

- 2. Connect the cable to your target system.

#### **Connecting the XChecker Cable**

The XChecker cable connects to your system RS-232 serial port. You may need a DB-9/DB-25 adapter, which accommodates most serial ports, so that you can connect the XChecker cable to your host system.

The JTAG Programmer software will automatically identify the XChecker cable when correctly connected to your computer. If you choose to, you may also select this connection manually. To set up a serial port manually:

${\tt Output} \to {\tt Cable Setup}$

Select **XChecker**, then click on **OK**. If you are using the XChecker Cable you may also select a BAUD rate. See Table 2-1, *Valid Baud Rates*.

#### **Connection to Your Target System**

You need appropriate pins on the target system for connecting the target system board to the header connection on the cable. These connectors must be standard 0.025—inch square male pins that have dedicated traces to the target system control pins. You connect to these pins with the flying lead connectors.

**Note:** The XChecker cable draws its power from the target system through  $V_{CC}$  and GND. Therefore, power to XChecker, as well as to the target system, must be stable. Do not connect any signals before connecting  $V_{CC}$  and ground.

**Note:** If your system's power is turned off before or during JTAG Programmer operations, the cable will not operate. Your system's power should be on during JTAG Programming operations.

**Note:** If the power has been momentarily interrupted, go to Output  $\rightarrow$  Cable Reset to reinitialize the XChecker cable. If you do not want to operate at maximum Baud rate, go to the Cable Communication Setup dialog box (Output  $\rightarrow$  Cable Setup...) and set a lower rate.

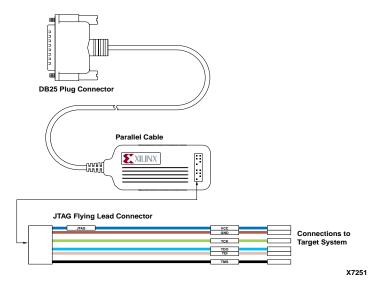

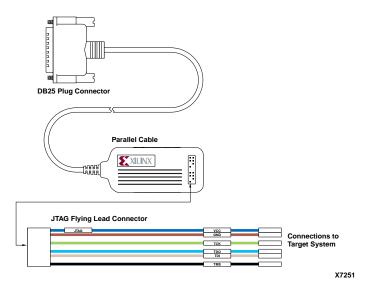

### **Parallel Cable**

The Parallel Download Cable consists of a cable assembly containing logic to protect your PC's parallel port and a set of headers to connect to your target system.

Using the Parallel Download Cable requires a PC equipped with an AT compatible parallel port interface with a DB25 standard printer connector. Figure 2-4 shows the Parallel Download Cable.

Figure 2-4 Parallel Download Cable and Accessories

The cable assembly contains logic designed to electrically isolate the target system from the parallel port of your PC host system.

The parallel download cable can be used with a single CPLD or several connected in a boundary-scan chain to download and readback configuration and boundary-scan data.

The transmission speed of the Parallel Download Cable is determined solely by the speed at which the host PC can transmit data through its parallel port interface.

Figure 2-5 shows top and bottom view of the Parallel Download Cable.

### **Parallel Cable**

X7252

Figure 2-5 Top and Bottom View of Parallel Download Cable

### **Connecting for System Operation**

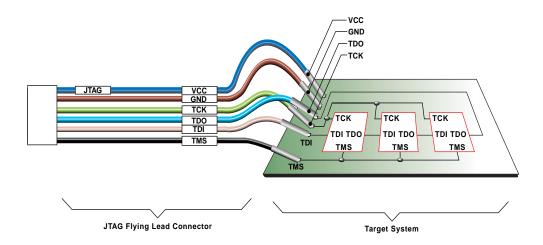

Connect the parallel cable to the host system and your target system as shown in Figure 2-6.

X8005

Figure 2-6 Parallel Download Cable Connection to JTAG Boundary-scan TAP

Appendix B contains schematic diagrams of the Parallel Download Cable.

#### **Configuring the Parallel Download Cable**

On PCs you can connect the parallel cable to your system's parallel printer port. The JTAG Programmer software will automatically identify the cable when correctly connected to your PC. If you choose to, you may also select this connection manually. To set up a parallel port manually:

$\mathtt{Output} \to \mathtt{Cable} \ \mathtt{Setup}$

Select the Parallel box and match to the port you are using, then click on OK.

### Flying Lead Connectors

The flying lead connector has a 9-pin (6 signals, 3 keys) header connector that fits onto the cable's JTAG header. The pin order is listed in Table 2-3. These header connectors are keyed to assure

proper orientation to the cable assembly.

The flying lead connector has six individual female connectors on one end that fit onto standard 0.025" square male pins. Each lead is labeled to identify the proper pin connection.

When you layout the printed circuit board for use with JTAG insystem programming and testing, a few adjustments will make the process of connecting and downloading easier.

- Provide pins on your printed circuit board for VCC, GND, TCK, TDO, TDI and TMS.

- These pins must be standard 0.025" square male pins that have dedicated traces to the target system control pins. You connect to these pins with the flying lead connector.

- Place pins on board so that flying leads can reach them. The length of our flying leads is six inches. While pins may be a couple inches apart, do not have any two JTAG pins more than six inches apart.

- Keep header pins on your board a minimum of 0.10" apart.

Table 2-3 Parallel Cable Connections and Definitions

| Name | Function                                                                                       | Connections                      |

|------|------------------------------------------------------------------------------------------------|----------------------------------|

| VCC  | Power – Supplies $V_{CC}$ (5 V, 10 mA, typically) to the cable.                                | To target system V <sub>CC</sub> |

| GND  | Ground – Supplies ground reference to the cable.                                               | To target system ground          |

| TCK  | Test Clock – this clock<br>drives the test logic for all<br>devices on boundary-scan<br>chain. | Connect to system TCK pin.       |

| TDO  | Read Data – Read back<br>data from the target<br>system is read at this pin.                   | Connect to system TDO pin.       |

| TDI  | Test Data In – this signal is used to transmit serial test instructions and data.              | Connect to system TDI pin.       |

| Name | Function                                                                   | Connections                |

|------|----------------------------------------------------------------------------|----------------------------|

| TMS  | Test Mode Select – this signal is decoded by the TAP controller to control | Connect to system TMS pin. |

|      | test operations.                                                           |                            |

Table 2-3 Parallel Cable Connections and Definitions

Figure 2-7 JTAG Cable and Leads (parallel cable shown)

### **Power Up Sequencing**

- 1. Connect your cable to your host computer.

- 2. Turn the power to your target system off, if possible.

- 3. The power for the drivers is derived from the target system. Connect the cable's GND wire to the corresponding signal on the target board. Next, connect VCC to the corresponding signal on the target board.

**Note:** Download cables will not operate if the target system's power is turned off before or during JTAG Programmer operations. Make

certain that this power connection is on and stable. Your system's power should be on during JTAG Programmer operations.

**Note:** JTAG Programmer will always initiate operations using a JTAG TAP controlled reset sequence. This performs the exact same operation as the assertion of the TRST pin; it initializes all devices JTAG state machines and internal registers.

- 4. Next connect the JTAG TAP inputs. Connect TCK, TDI, TMS and TDO to the target board. TRST is not supported by the XC9500/ XL/XV JTAG Download Cables. If any of your JTAG parts have a TRST pin, it should be connected to VCC.

- Power up the target system.

**Warning:** Cable protection ensures that the parallel port cannot be damaged through normal cable operation. For increased safety, please check that the power to the system controller is on before the target system is powered up.

# **Chapter 3**

# **JTAG Programmer Tutorial**

This chapter will take you through the basic steps involved in programming Xilinx devices in-system using the JTAG Programmer graphical user interface. This chapter contains the following sections:

- "Cable Setup" section

- "Selecting a Port for the Cable" section

- "Creating New Chain Descriptions" section

- "Configuring a Device In-System" section

- "Generating SVF Files" section

### **Cable Setup**

To setup your system to download configurations in-system you must first connect the JTAG Programmer parallel download cable or the XChecker cable. Cable setups and power sequencing are described in chapter 2, *Hardware*.

# Selecting a Port for the Cable

You may select a serial or parallel port for your cable from the JTAG Programmer Interface. To set up a port:

```

\mathtt{Output} \to \mathtt{Cable} \ \mathtt{Setup}

```

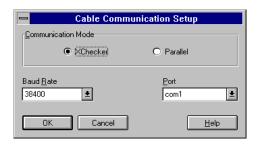

The Cable Communication Setup dialog box will appear.

Figure 3-1 Communications Dialog Box

Select the cable you are using and match to the port you are using, then click on OK. If you are using the XChecker Cable you may also select a BAUD rate. See Table 2-2, Valid Baud Rates.

Alternatively, you may use the Output  $\rightarrow$  Cable Auto Connect to allow the software to automatically identify and connect to whichever download cable is installed.

**Note:** Upon selecting any device operation, the JTAG Programmer will automatically connect to whichever cable is installed and powered up.

**Note:** If you accidentally or purposely power down your system while running JTAG Programmer, remember to select  $Output \rightarrow Cable Reset$  to reinitialize the cable after re-applying power.

# **Creating New Chain Descriptions**

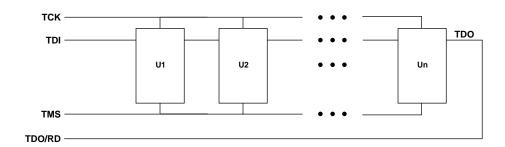

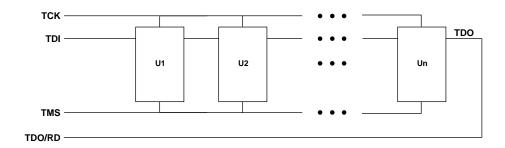

The device chain U1, U2, ... Un is a serial chain where U1 is the first device TDI enters and Un is the last device. Un must deliver the TDO (labelled RD on the XChecker cable) signal back to the cable. TMS and TCK signals enter all devices in parallel.

X8006

Figure 3-2 Device Chain

The chain description must contain all devices in the order that they appear in the JTAG programming chain.

Alternatively, you can use the Initialize Chain operation to automatically identify the devices in the system boundary-scan chain. You must then associate JEDEC files for XC9500/XL/XV CPLD devices, BIT files for Xilinx FPGA devices, and BSDL files for all other devices by using the device properties dialog box.

# **Configuring a Device In-System**

If you have created programming files (<filename>.jed) and are ready to download them to XC9500/XL/XV devices in-system through the JTAG chain, proceed as follows:

- 1. Make sure the cable is attached properly and the target board is turned on.

- 2. Invoke the JTAG Programmer Download Software menu by double-clicking the JTAG Programmer Download Software icon.

Figure 3-3 JTAG Programmer Icon

The JTAG Programmer will appear.

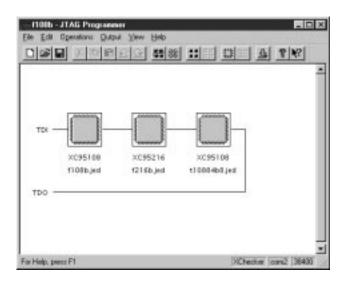

#### Figure 3-4 JTAG Programmer

3. Add a device for each part in your boundary-scan chain.

#### ${\tt Edit} \rightarrow {\tt Add} \ {\tt Device}$

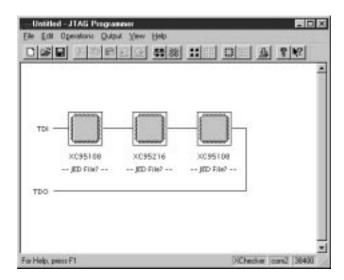

Or, if you have the cable set up and connected to a boundary-scan chain, you can use the automatic device identification feature of the JTAG Programmer to display the entire chain. To do this:

#### $\textbf{File} \rightarrow \textbf{Initialize Chain}$

The programmer goes out and finds all the parts in the chain, identifies them, and displays them in the JTAG Programmer. If the programmer finds a device it can't identify, it displays the device as an unknown part.

Figure 3-5 Automatic Device Identification

4. You need to specify a JEDEC file for each XC9500/XL/XV device in the boundary-scan chain, a BIT file for each Xilinx FPGA device, and a BSDL file for all other devices in the boundary-scan chain. Highlight the first device in the chain by clicking once on it and then select the JEDEC or BSDL file corresponding to the device.

#### $\mathtt{Edit} o \mathtt{Properties}$

Alternatively, you may double-click on the device icon.

The Device Properties dialog box appears

Figure 3-6 Device Properties

5. Type in the path name or click once on the browse key and find the appropriate file to assign to the highlighted part. Select JEDEC files for each XC9500/XL/XV device in the chain, BIT files for each Xilinx FPGA device, and BSDL files for the remaining devices. Repeat for each device in the chain.

Figure 3-7 Device Chain (unprogrammed)

### **Programming Xilinx CPLD and FPGA Devices**

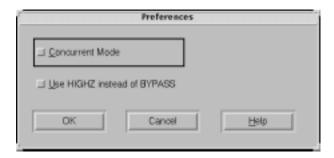

There are two preferences available that you may want to select before initiating a session. They are Concurrent Mode and Use HIGHZ instead of BYPASS. These options are selected as follows:

$\mathtt{File} o \mathtt{Preferences}$

The Preferences dialog box will appear.

Figure 3-8 Preferences

#### **Concurrent Mode**

The JTAG Programmer normally uses a sequential methodology when accessing Xilinx CPLDs for ISP operations. It selects a device to program and sets all other devices in the boundary-scan chain into BYPASS mode. Concurrent Mode erases, programs and verifies selected devices in the chain without placing these parts in BYPASS mode. This has the advantage of saving time by executing operations simultaneously.

For example, it takes few seconds to completely erase all the sectors of a device. If you have several devices in a chain, these erase times can add up. In concurrent mode the erasures can take place simultaneously, saving time.

**Note:** Concurrent mode is applicable only to Xilinx CPLD devices. Since Xilinx FPGA devices are SRAM based; their access method precludes this kind of operation.

#### Use HIGHZ instead of BYPASS

The JTAG Programmer usually places parts in BYPASS mode when other devices in the boundary-scan chain are being programmed.

This option places XC9500/XL/XV devices in high impedance mode instead. If you suspect that noise is degrading the integrity of ISP operations, use this mode to reduce the signal activity level in the system.

**Note:** If you decide to use HIGHZ instead of BYPASS you must be certain that your design can tolerate XC9500/XL/XV device pins floating. If these pins connect to memory enable pins, for instance, their floating values may inadvertently cause the devices to turn on, potentially damaging their drivers or parts downstream from them.

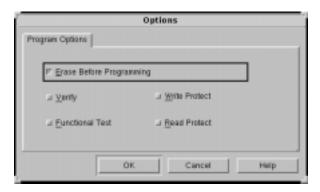

#### **Selecting Parts for Programming (Xilinx CPLD)**

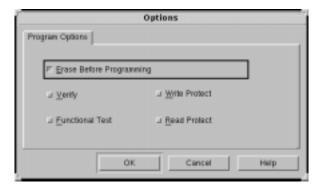

If your boundary-scan chain consists of only Xilinx CPLD devices, then you can select all XC9500/XL/XV devices at once with Edit  $\rightarrow$  Select All, or highlight each device individually, then:

$\mathtt{Operations} \to \mathtt{Program}$

The program options box appears. Select the desired programming options, then click **OK**.

Figure 3-9 Options

When the programming operation is complete, the programming status of each Xilinx programmable device is reported as shown:

Figure 3-10 Programmed Chain

#### **Selecting Parts for Programming (Xilinx FPGA)**

If your boundary-scan chain consists of only Xilinx FPGA devices, then you can select all Xilinx FPGA devices at once with Edit

select All or highlight each device individually, then:

${\tt Operations} \to {\tt Program}$

The programming options box appears. Select the desired options, then click OK.

### **Selecting Operations**

There are two ways to set up the chain for JTAG Programmer operations. The first is to highlight a part and select an operation for it using the Operations menu. You select an operation from the menu, then highlight the next part and select an operation for it, or you may highlight all parts and select an operation for all parts.

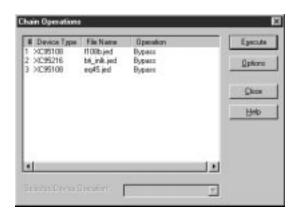

The other way is to use the Chain Operations dialog box. This presents you with a "spreadsheet" approach to boundary-scan chain. This method allows you select and execute operations for all the parts in the chain, all from the same dialog box. To access this dialog box:

${\tt Operations} \rightarrow {\tt Chain\ Operations...}$

Figure 3-11 Chain Operations

The dialog box appears. In the Operations column you may change the operation of any part by clicking once on the current device to highlight it, then clicking once on the down arrow adjacent to Selected Device Operation. This will produce a pull-down menu showing the operations you can set for that part.

**Note:** Bypass is the only supported mode of Operation for non-Fast-FLASH parts. These parts will appear under Device Type. Note that Bypass is selected as the default Operation of each foreign part.

Select the Execute button. Download will begin.

In either operation mode a pop-up menu appears and delivers processing messages. When processing has completed, a message log is available to examine the results of the execution.

### **Modifying a Chain**

The Edit menu provides easy means for inserting and deleting parts from a chain, as well as the means to assign a new JEDEC file to a part.

#### **Adding a Device**

To insert a device into the chain, use the Add Device command. First make sure that the prompt is at the location in the chain where you want to insert the device. If it is not, use either the mouse or the arrow keys to move it. Then insert the device as follows:

${\tt Edit} \rightarrow {\tt Add} \ {\tt Device}$

#### **Changing a Part**

To change the jedec file associated with a device in the chain, highlight the device and:

```

\textbf{Edit} \rightarrow \textbf{Properties}

```

Use the browse key to select another jedec file or simply enter the path and filename of the file. The program will associate the new file with the device.

**Note:** Each jedec assigns a device type to the device in the chain. If the jedec file was not created for the actual device you have on your board, an error will result when you attempt to program the device.

#### **Deleting a Part**

To delete an entry in the device chain, use the Cut command. All devices move up one entry in the chain.

$\mathbf{Edit} \to \mathbf{Cut}$

### Selecting the Entire Chain

To select the entire chain for an operation, use

```

\mathtt{Edit} \to \mathtt{Select} \ \mathtt{All}

```

To unselect the chain:

```

\texttt{Edit} \rightarrow \texttt{Unselect All}

```

**Note:** When operating in SVF mode, chain modifications are not allowed so as to ensure that the resulting SVF if self-consistent.

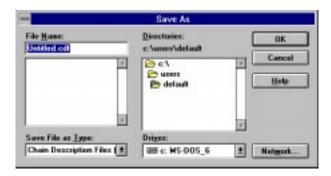

### **Saving the Chain Description**

To save a JTAG Programmer chain description for later use, create a Chain Description File (.cdf) using:

```

\textbf{File} \rightarrow \textbf{Save}

```

If the chain has not been previously saved, the Save As dialog box will appear. This screen will allow you to select a directory and path to place the file in. You can also name the file, but you should retain

the .cdf file extension. If you wish to save your file under another name than already selected, use:

```

File \rightarrow Save As...

```

To name your file, use the mouse to highlight Untitled or the old file name on the File Name line, then type in the name you want and click once on OK.

Figure 3-12 Saving a File

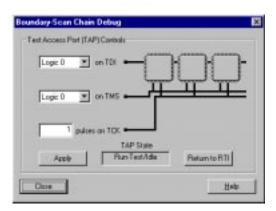

### **Debugging a Chain**

The debugger provides you with a method to apply boundary-scan test access port stimulus. This feature allows you to set TDI and TMS, then pulse TCK a specified number times. You can monitor TDO, TDI and TMS using an oscilloscope or logic probe to see if the boundary-scan chain is operating correctly. The debugger also displays the current TAP state and allows you to reset the chain to Run Test Idle.

To access the debugger:

```

\textbf{File} \rightarrow \textbf{Debug Chain}

```

The Boundary-Scan Chain Debug dialog box appears as shown in Figure 3-13.

Figure 3-13 Debug

The features of this dialog box operate as follows:

- The first selection box allows you to set a logic state for TDI. This state will not be set until you click on the Apply button.

- The second selection box allows you to set a logic state for TMS. This state will not be set until you click on the Apply button.

- The third selection box allows you to set a number of pulses to apply to TCK. These pulses will not be sent until you click on the Apply button. If you want to see the pulses again, click the Apply button as often as you want.

- The TAP State window displays the current state of the controller.

- The Return to RTI (Run Test Idle) button executes a Test Logic Reset, then returns to Run Test Idle.

## **Data Security Selection**

Any Xilinx CPLD device selected for programming can be secured with the Write Protect or Read Protect or both.

When enabled, Read Protect disables reading the programmed contents of a device (the Device ID and usercode/signature and boundary scan register remain readable).

Write Protect allows only the reading of the programmed data. The device contents cannot be altered or re-programmed.

When both Read Protect and Write Protect are enabled, the device can be neither read nor re-programmed.

To enable either security function simply place a check in the corresponding box when programming the device.

Figure 3-14 Data Selection (Program Options)

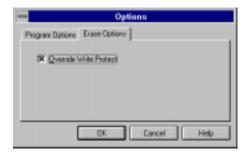

Data security operations can be overridden only by erasing the device. For Read Protection override, you simply erase the part. For Write Protection override, you must select the override write protect option from the Erase Options dialog box.

Figure 3-15 Data Selection (Erase Options)

## **Generating SVF Files**

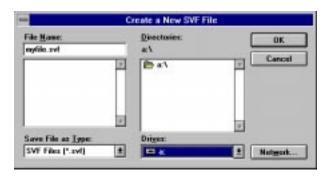

Serial Vector Format (SVF) files are used when programming XC9500/XL/XV devices on automatic test equipment (ATE). The JTAG Programmer allows you to create .svf files for use with ATE systems. To do this you need to create a new SVF file:

Output  $\rightarrow$  Create SVF File...

The Create a New SVF File dialog box will appear.

Figure 3-16 Create an SVF File

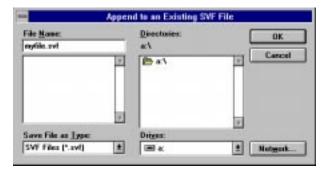

Select a name and a directory to create the new file in, then click **OK**. To append your vectors to an existing SVF file, use:

Output  $\rightarrow$  Append to SVF File...

The Append to an Existing SVF File dialog box will appear.

Figure 3-17 Append to an SVF File

Select a file to append to and click OK.

**Note:** Program, Verify, Erase, Functional Test, Get Device ID and Get Signature/Usercode are allowed operations in SVF mode.

After identifying the SVF file to be used for collection of SVF data, operate on the devices in your boundary-scan chain in the manner described previously. Remember that in SVF mode, chain editing

operations are not allowed to ensure that the resulting SVF file will be self-consistent.

Xilinx provides software on the Xilinx Website that converts SVF files into ATE vectors. Visit our site at www.xilinx.com for more information.

### Substituting with Version n Devices

If you generated SVF files for XC95108 or XC95216 Version 0 devices, the files will work without modification on any later version devices. If you wish, however, to take advantage of improved ISP capabilities available on later version silicon devices, and you are certain that you have such devices in your boundary-scan chain, then you can generate version specific SVF files using the following techniques:

#### Using the Batch Tool (jtagprog)

Invoke the tool to generate SVF files:

```

jtagprog -svf

```

When specifying the part\_type in the part command identify Version 1 silicon by appending " $_{\mathbf{v}n}$ " to the part name (where n is the version number device being used). For example, to specify a chain of Version 1 XC95216s and XC95108s:

```

part xc95216_v1:design216a xc95108_v1:design108

xc95216_v1:design216b

```

Next, specify operations as usual to generate the required SVF files.

#### **Using the JTAG Programmer**

In your \$XILINX/data directory you will notice BSDL files with the following names:

```

xc95108.bsd

xc95108_v1.bsd

xc95216.bsd

xc95216_v1.bsd

```

The BSDL files with the "\_v1" in their names describe the Version 1 silicon. Similarly, those with "\_v2" are for Version 2 devices. To get

the software to use Version 1 BSDL files for all devices, you must "trick" the application by renaming files as follows:

- 1. Rename xc95108.bsd to xc95108\_v0.bsd

- 2. Rename xc95216.bsd to xc95216\_v0.bsd

- 3. Rename xc95108\_v1.bsd to xc95108.bsd

- 4. Rename xc95216\_v1.bsd to xc95216.bsd

Invoke the JTAG Programmer and set it to generate SVF files as described earlier in this section. When you use the JTAG Programmer, it will default to using the xc95216.bsd and xc95108.bsd files to describe the parts. This will allow access to all Version 1 features.

When you are done programming, remember to change the file names back so that the software will work correctly in non-SVF modes:

- 1. Rename xc95108.bsd to xc95108\_v1.bsd

- 2. Rename xc95216.bsd to xc95216\_v1.bsd

- 3. Rename xc95108\_v0.bsd to xc95108.bsd

- 4. Rename xc95216\_v0.bsd to xc95216.bsd

# **Designing Boundary-Scan and ISP Systems**

This chapter gives design considerations for boundary-scan and ISP systems. It contains the following sections:

- "Connecting Devices in a Boundary-Scan Chain" section

- "FPGA Device Considerations" section

- "Bitstream Considerations" section

- "Device Set-up" section

## **Connecting Devices in a Boundary-Scan Chain**

All devices in the chain share the TCK and TMS signals. The system TDI signal is connected to the TDI input of the first device in the boundary-scan chain. The TDO signal from that first device is connected to the TDI input of the second device in the chain and so on. The last device in the chain has its TDO output connected to the system TDO pin. This configuration is illustrated in Figure 4-1.

Figure 4-1 Single Port Serial Boundary-Scan Chain

### **Design Rules for Boundary-Scan and ISP Systems**

The boundary-scan standard requires pull-up resistance to be supplied internally to the TDI and TMS pins by the chips, but no particular value is required. This allows vendors supply whatever they choose and still remain in full compliance. Because of this, very long boundary-scan chains, or chains using parts from multiple vendors, may present significant loading to the ISP drive cable. In these cases:

- 1. Use the latest Xilinx download cables (parallel cables with serial numbers greater than 5000, or any X-Checker cable).

- 2. Consider including buffers on TMS or TCK signals interleaved at various points on your JTAG circuitry to account for unknown device impedance.

- Some users have noted that their designs appear to experience erase time or programming time extension as the design progresses, particularly for long chains. This is probably due to switching noise.

- 3. Put the rest of the JTAG chain into HIGHZ mode by selecting the HIGHZ preference on JTAG Programmer when programming a troublesome part.

- This will limit the number of additional signals presented to the system and the troublesome part.

- 4. If free running clocks are delivered into boundary-scan devices, it may be necessary to disconnect or disable their entry into these devices during ISP or boundary-scan operations.

- Charge pumps, the heart of the XC9500/XL/XV ISP circuitry, require a modest amount of care. The voltages to which the pumps must rise are directly derived from the external voltage supplied to the VCCINT pins on the XC9500/XL/XV parts. Because these elevated voltages must be within their prescribed values to properly program the CPLD, it is vital that they be provided with very clean (noise free) voltage within the correct range. This suggests the first two key rules:

- 5. Make sure VCC is within the rated value: 5V + /- 5%.

- 6. Provide both 0.1 and 0.01 uF capacitors at every VCC point of the chip, and attached directly to the nearest ground.

### **FPGA Device Considerations**

JTAG Programmer supports the configuration of Xilinx FPGA devices through the boundary-scan test access port (TAP). In order to enable boundary-scan-based configuration capabilities for FPGA devices, you must design your systems and prepare your configuration bitstreams in the following manner.

### **Bitstream Considerations**

JTAG Programmer only accepts FPGA configuration files in the binary bitstream format (.bit). It does not allow configuration using the ASCII raw bits (.rbt) format.

**Note:** Express mode bitstreams cannot be used to configure devices via boundary-scan.

Make certain that the boundary-scan (BSCAN) symbol has been included in your design. If it has not then the bitstream will also not be usable for boundary-scan based configuration. Standard examples for instantiating the BSCAN symbol in FPGAs are included in Appendix F.

Keep your device bitstream files separate for each device in the boundary-scan chain. JTAG Programmer requires you to assign a single bit file to each device. It cannot manipulate composite bit files.

## **Device Set-up**

Xilinx recommends that all the mode pins of the devices be tied low before starting the configuration. This is recommended for all XC4000, XC5000 and Spartan device families.

In order to enable the boundary-scan circuitry in the device, you must install a pull down resistor on the INIT pin. The value of the pull down should be selected so as to draw the INIT pin to approximately 0.5V. Typically a pull down of approximately 1KOhm should accomplish this.

## **Verifying Device Configuration**

The XC4000 (not the XLA and XV), XC5000 and Spartan (not the SpartanXL) devices freeze if data errors occur during boundary-scan configuration. The only method for unlocking the frozen device is to

reset the power to the device or pulse the PROGRAM pin low. (This latter method would have to be accomplished manually since the download cables (when being used for boundary-scan operations), do not have control over the PROGRAM pin. Although this situation is rare, it is possible to design your system so as to detect if that condition has occurred. The JTAG Programmer software allows you to check for this in three ways:

- 1. Assume successful verification since it is a low probability event, simply configure the device and run. The drawback is that the failure of the device is then only detected at run-time.

- 2. Readback verify the configuration memory after configuring, readback the contents of the configuration memory and check against the source bitstream file. If the device has frozen, the returned bits will be incorrect. Since bit files can be large, this might be time consuming.

- 3. Tie a free pin on the device to ground after configuring, the software will perform an EXTEST instruction to read the device pin value. If the device has locked up, the pin value will not be read correctly.

#### **Device Behavior Notes**

Any verify operation executed immediately after configuration without boundary-scan functionality enabledwill fail because the test access port no longer exists. Always remember to instantiate the BSCAN symbol for reliable operation of your devices.

The implementation of boundary-scan based configuration of FPGAs precludes the use of concurrent ISP. For this reason, the concurrent mode preference is disabled (or ignored) when FPGAs are selected to be operated upon.

# Appendix A

# **Boundary Scan Basics**

## **Boundary Scan**

#### What is IEEE 1149.1?

Design complexity, difficulty of loaded board testing, and the limited pin access of surface mount technology led industry leaders to seek accord on a standard to support the solution of these problems.

JTAG Boundary Scan, formally known as IEEE Standard 1149.1, is primarily a testing standard created to alleviate the growing cost of designing and producing digital systems. The primary benefit of the standard is the ability to transform extremely difficult printed circuit board testing problems (that could only be attacked with ad-hoc testing methods) into well-structured problems that software can handle easily and swiftly.

The standard defines a hardware architecture and the mechanisms for its use to solve the aforementioned problems.

#### What can it be used for?

Although primarily a testing standard for on-chip circuitry, the proliferation of the standard has opened the door to a wide variety of applications. The standard itself defines instructions that can be used to perform functional and interconnect tests as well as built-in self test procedures.

Vendor-specific extensions to the standard have been developed to allow execution of maintenance and diagnostic applications as well as programming algorithms for reconfigurable parts. It is the latter that have been implemented (in addition to all the mandatory operations of the standard and some optional ones) in the FastFLASH family.

#### How does it work?

The top level schematic of the test logic defined by IEEE Std 1149.1 includes three key blocks:

#### The TAP Controller

This responds to the control sequences supplied through the test access port (TAP) and generates the clock and control signals required for correct operation of the other circuit blocks.

#### The Instruction Register

This shift register-based circuit is serially loaded with the instruction that selects an operation to be performed.

#### The Data Registers

These are a bank of shift register based circuits. The stimuli required by an operation are serially loaded into the data registers selected by the current instruction. Following execution of the operation, results can be shifted out for examination.

The JTAG Test Access Port (TAP) contains four pins that drive the circuit blocks and control the operations specified. The TAP facilitates the serial loading and unloading of instructions and data. The four pins of the TAP are: TMS, TCK, TDI and TDO. The function of each TAP pin is as follows:

**TCK** - this pin is the JTAG test clock. It sequences the TAP controller as well as all of the JTAG registers provided in the XC95108.

**TMS** - this pin is the mode input signal to the TAP Controller. The TAP controller is a 16-state FSM that provides the control logic for JTAG. The state of TMS at the rising edge of TCK determines the sequence of states for the TAP controller. TMS has an internal pull-up resistor on it to provide a logic 1 to the system if the pin is not driven.

**TDI** -this pin is the serial data input to all JTAG instruction and data registers. The state of the TAP controller as well as the particular instruction held in the instruction register determines which register is fed by TDI for a specific operation. TDI has an internal pull-up

resistor on it to provide a logic 1 to the system if the pin is not driven. TDI is sampled into the JTAG registers on the rising edge of TCK.

**TDO** - this pin is the serial data output for all JTAG instruction and data registers. The state of the TAP controller as well as the particular instruction held in the instruction register determines which register feeds TDO for a specific operation. Only one register (instruction or data) is allowed to be the active connection between TDI and TDO for any given operation. TDO changes state on the falling edge of TCK and is only active during the shifting of data through the device. This pin is three-stated at all other times

#### **JTAG TAP Controller**

The JTAG TAP Controller is a 16-state finite state machine, that controls the scanning of data into the various registers of the JTAG architecture. The state of the TMS pin at the rising edge of TCK is responsible for determining the sequence of state transitions. There are two state transition paths for scanning the signal at TDI into the device, one for shifting in an instruction to the instruction register and one for shifting data into the active data register as determined by the current instruction.

#### JTAG TAP Controller States

**Test-Logic-Reset**. This state is entered on power-up of the device whenever at least five clocks of TCK occur with TMS held high. Entry into this state resets all JTAG logic to a state such that it will not interfere with the normal component logic, and causes the IDCODE instruction to be forced into the instruction register.

**Run-Test-Idle**. This state allows certain operations to occur depending on the current instruction. For the XC9500/XL/XV family, this state causes generation of the program, verify and erase pulses when the associated in-system programming (ISP) instruction is active.

**Select-DR-Scan**. This is a temporary state entered prior to performing a scan operation on a data register or in passing to the Select-IR-Scan state.

**Select-IR-Scan**. This is a temporary state entered prior to performing a scan operation on the instruction register or in returning to the Test-Logic-Reset state.

**Capture-DR**. This state allows data to be loaded from parallel inputs into the data register selected by the current instruction on the rising edge of TCK. If the selected data register does not have parallel inputs, the register retains its state.

**Shift-DR**. This state shifts the data, in the currently selected register, towards TDO by one stage on each rising edge of TCK after entering this state.

**Exit1-DR**. This is a temporary state that allows the option of passing on to the Pause-DR state or transitioning directly to the Update-DR state.

**Pause-DR**. This is a wait state that allows shifting of data to be temporarily halted.

**Exit2-DR**. This is a temporary state that allows the option of passing on to the Update-DR state or returning to the Shift-DR state to continue shifting in data.

**Update-DR**. This state causes the data contained in the currently selected data register to be loaded into a latched parallel output (for registers that have such a latch) on the falling edge of TCK after entering this state. The parallel latch prevents changes at the parallel output of these registers from occurring during the shifting process.

**Capture-IR**. This state allows data to be loaded from parallel inputs into the instruction register on the rising edge of TCK. The least two significant bits of the parallel inputs must have the value 01 as defined by IEEE Std. 1149.1, and the remaining 6 bits are either hard-coded or used for monitoring of the security and data protect bits.

**Shift-IR**. This state shifts the values in the instruction register towards TDO by one stage on each rising edge of TCK after entering this state.

**Exit1-IR**. This is a temporary state that allows the option of passing on to the Pause-IR state or transitioning directly to the Update-IR state.

**Pause-IR**. This is a wait state that allows shifting of the instruction to be temporarily halted.

**Exit2-IR**. This is a temporary state that allows the option of passing on to the Update-IR state or returning to the Shift-IR state to continue shifting in data.

**Update-IR**. This state causes the values contained in the instruction register to be loaded into a latched parallel output on the falling edge of TCK after entering this state. The parallel latch prevents changes at the parallel output of the instruction register from occurring during the shifting process.

### JTAG Instructions Supported in FastFLASH Parts

JTAG Programmer software uses sequences of these JTAG instructions to perform programming and verification operations selected by the user. However, execution of individual JTAG instructions is not supported by this software.

#### **Mandatory Boundary Scan Instructions**

**BYPASS**. The BYPASS instruction allows rapid movement of data to and from other components on a board that are required to perform test operations.

**SAMPLE/PRELOAD**. The SAMPLE/PRELOAD instruction allows a snapshot of the normal operation of a components to be taken and examined. It also allows data values to be loaded onto the latched parallel outputs of the boundary scan shift register prior to the selection of other boundary-scan test instructions.

**EXTEST**. The EXTEST instruction allows testing of off-chip circuitry and board level interconnections.

#### **Optional Boundary Scan Instructions**

**INTEST**. The INTEST instruction allows testing of the on-chip system logic while the components are already on the board.

**HIGHZ**. The HIGHZ instruction forces all drivers into high impedance states.

**IDCODE**. The IDCODE instruction allows blind interrogation of the components assembled onto a printed circuit board to determine what components exist in a product.

**USERCODE**. The USERCODE instruction allows a user-programmable identification code to be shifted out for examination. This allows the programmed function of the component to be determined.

### FastFLASH Reconfiguration Instructions

**ISPEN**. The ISPEN instruction activates the FastFLASH part for insystem programming.

**FPGM**. The FPGM instruction is used to program the fuse locations at a specified address.

**FERASE**. The FERASE instruction is used to perform an erase of a block of fuse locations.

**FVFY**. The FVFY instruction is used to read the programming of the fuse locations at a specified address.

**ISPEX**. The ISPEX instruction loads the programmed values into the device memory. It then activates the device to operate according to the programmed values.

**FPGMI**. The FPGMI instruction is used to program fuse locations sequentially from a preset starting address.

**FVFYI**. The FVFYI instruction is used to read the programming of fuse locations sequentially for a preset starting address.

**FBULK**. The FBULK instruction is used to perform an erase of either all function blocks or all Fastconnect blocks of a device.

# **Appendix B**

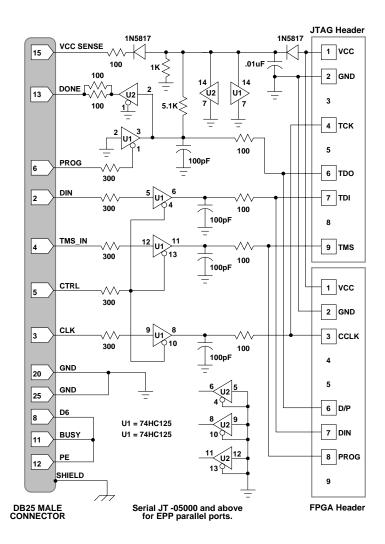

## **JTAG Parallel Download Cable Schematic**

This appendix contains a schematic of the Parallel Download Cable. It is included in case you want to build your own download cables. schematic, Figure B-1, is our current version of the Parallel Download Cable. If you want to build a parallel cable, this is the recommended schematic.

**Note:** You must use recommended lengths for parallel cables. Xilinx cables are typically six feet (about two meters) in length.

X7557

Figure B-1 Parallel Download Cable

# **Appendix C**

# **Troubleshooting Guide**

This chapter is a simple guide to understanding the more common issues you might encounter when configuring CPLDs with JTAG Programmer. These issues are likely to fall into three groups; communication, improper connections, and improper or unstable  $V_{CC}$ .

• "Communication" section

This section describes several issues that involve the integrity of the bitstream that JTAG Programmer transmits to the target CPLDs, and the correct connection of the boundary-scan chain.

• "Improper Connections" section

This section involves assigning configuration pins to invalid signals or voltage levels.

• "Improper or Unstable VCC" section

This section describes several causes of incorrect configuration sequences and incorrect responses from the target system.

"Boundary Scan Chain Errors" section

If you experience a consistent error that identifies a break in your boundary-scan chain, go to this section.

• "System Noise" section

If you experience intermittant problems characteristic of system noise, go to this section.

### Communication

Observing the following guidelines should minimize the communication difficulties that can occur between the cable hardware and the target system.

Troubleshooting C-1

Do not attach extension cables to the target system side of the cable; this can compromise configuration data integrity and cause checksum errors.

Attach the cable configuration leads firmly to the target system.

After connecting the target system, specify the chain configuration using the part command. Then use the "partinfo -id part\_name" command to read the IDCODE from each part in the system. This will verify the integrity of the boundary-scan chain. If you are using the Graphical User Interface:

```

\mathtt{Operations} \to \mathtt{Get} \ \mathtt{Device} \ \mathtt{ID}

```

Use the verify feature to assure integrity of the configuration data. You can do this from the command line with the –v option or in the interactive mode by specifying the verify command.

When using the JTAG Programmer software with the cable on a PC to download, the process may stop with data communications errors. This is caused by serial port communication inefficiencies in the Windows environment. To set your PC to better handle serial communications at 38400 baud, add (or modify) the following lines to the 386Enh section of your SYSTEM.INI file. This file is located in the Windows directory of your system.

```

COM1Buffer=32768

COM2Buffer=32768

COMBoostTime=10240

```

## **Improper Connections**

Always make sure that cable leads are connected properly.

**Note:** Connecting the cable leads to the wrong signal will cause permanent damage to cable internal hardware. You must connect  $V_{CC}$  to +5 V and GND to ground.

For workstations, you must have read and write permissions to the port to which you connect the cable. JTAG Programmer might issue a message stating that the cable is not connected to port ttyx. When you see this message, follow the check list below:

• The board must have the power on, since the cable uses power from the board.

Check the device driver using the following command string:

```

ls -1 /dev/ttya /dev/ttyb

```

The result should be the following:

```

crw-rw-rw- 1 root12,0 month date time /dev/ttya

crw-rw-rw- 1 root12,1 month date time /dev/ttyb

```

- Reconnect the cable to another valid port.

- Read the /etc/ttytab file. There should be two lines, as follows:

```

ttya`'/usr/etc/getty std.9600'' unknown off local

secure

ttyb`'/usr/etc/getty std.9600'' unknown off local

secure

```

If you use a port to connect a modem or a remote login, you cannot use that port. The port must be on. Consult your System Administrator if the information the /etc/ttytab file is different than what is listed in the aforementioned list.

# Improper or Unstable V<sub>CC</sub>

Never connect the control signals to the cable before  $V_{CC}$  and ground. Xilinx recommends the following sequence:

- 1. Turn off power to the target system.

- 2. Connect  $V_{CC}$  ground, and then the signal leads,

- 3. Turn on power to the target system.

**Warning:** The XChecker Cable has an internal FPGA. As with any CMOS device, the input/output pins of the internal FPGA should always be at a lower or equal potential than the rail voltage to avoid internal damage.

Make sure  $V_{CC}$  rises to a stable level within 10ms. Stable  $V_{CC}$  should be between 4.75 V and 5.25 V.

In the event of power glitches, reset the cable by selecting:

```

\mathtt{Output} \to \mathtt{Cable} \ \mathtt{Reset}

```

Troubleshooting C-3

## **Boundary Scan Chain Errors**

If you experience a consistent error that identifies a break in your boundary-scan chain but are unable to identify such a discontinuity then execute the following steps:

Create a command file to be used with the batch version of the JTAG Programmer (jtagprog). In this batch file specify your boundary-scan chain configuration using the part command and about 50 idcode queries as follows:

```

part xc9572:design72 xc95108:design108

partinfo -id design108

partinfo -id design108

partinfo -id design108

.

.

.

partinfo -id design108

quit

```

2. Save the file as test.cmd and then invoke the tool as follows:

```

jtagprog -batch test

```

3. The tool will execute the device id command 50 times before quitting. While this is going on use the oscilloscope to probe the pins of the boundary scan test access port (TAP) at the system entry point and at each individual part.

The boundary scan integrity check sequences the TAP through a TRST sequence (TMS set to 1, TCK pulsed 5 times) and then transitions all devices to the RunTest/Idle state (TMS set to 0, TCK pulsed once). Then, all parts are run through a CAPTURE -IR sequence while TDI is set to 1 (1s will be shifted in). If you look in the device BSDL files you will see the expected capture sequence defined in the "instruction capture" field. For all XC9500/XL/XV parts this sequence is a "1" followed by seven zeros. You should therefore see the "1" on TDO after the falling edge of the 4th TCK pulse after the TRST sequence. On the next TCK pulse TDO should return to zero.

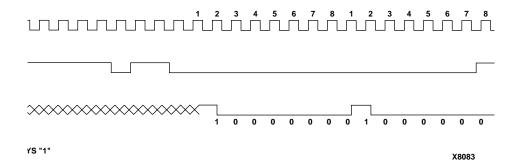

The CAPTURE -IR sequence consists of the following (starting from RunTest/Idle), as illustrated in Figure C-1.

- 1. TMS set to 1; TCK pulsed twice.

- 2. TMS set to 0; TCK pulsed twice.

- 3. TCK pulsed (number of bits in instruction register -1) times.

- 4. TMS set to 1; TCK pulsed twice.

- 5. TMS set to 0; TCK pulsed once.

Figure C-1 Sample Expected Waveform

Check for the following:

- The expected number of TCK pulses occur.

- The same TMS sequence occurs for each part.

- The TDO is not shorted or floating between parts, or floating at the system interconnect point.

- Make certain that all 4 TAP signals are getting into each part (Note that both TDI and TMS have internal pull-ups on them which could keep the device in TRST mode if TMS is not properly connected).

You may also use the **Debug Chain** dialog and a logic probe or oscilloscope to transition the TAP state machine directly and observe results.

Troubleshooting C-5

# **System Noise**

You can check for system noise by running the IDCODE instruction repeatedly. The IDCODE should read correctly 100% of the time. If by test you find that the instruction is working less than 100% of the time, you may be experiencing system noise.

To remedy a problem with system noise, select Use <code>HIGHZ instead of BYPASS</code> from the Preferences dialog box. This places devices into tri-state mode and reduces susceptibility to system noise. To find this box use:

#### $\textbf{File} \rightarrow \textbf{Preferences}$

The Preferences dialog box will appear. Place a check in the box adjacent to Use HIGHZ instead of BYPASS.

# **Appendix D**

# **Error Messages**

This section describes the error messages that JTAG Programmer may generate. Following each error message, there is a suggested workaround.

## **Error Messages**

```

Command file bat file.cmd is not found.

```

Make sure that the command file you specified is in the current directory or the environment search path. Make sure that the command file has the ".cmd" extension

```

Internal Error - Command table syntax error

Cmd=valid command.

```

This is an internal program error that normally should not occur. Try entering the command sequence again. If the error persists, try reinstalling your JTAG Programmer software. If the error reappears, call Xilinx Technical Support. Be prepared to duplicate the error and reference specific files or examples.

```

Cannot open output file file_name.

```

Check available disk space. Current directory or file must have write permission.

```

Cannot create output file file_name.

```

Check available disk space. Current directory or file must have write permission.

```

Cannot open input file file_name.

```

Make sure the *file\_name* file exists in your working directory or in the environment search path. Current directory or file must have write permission.

```

File file_name is not found.

```

The *file\_name* file does not exist in the current directory or search path. Make sure that the *file\_name* file exists in your working directory or in the environment search path.

```

Help file jtagprog.hlp is not accessible

```