# XCELL

THE NEWSLETTER FOR XILINX PROGRAMMABLE LOGIC USERS

Issue 7

Second Quarter 1992

CELL is back!

After a one-year intermission caused by lack of editing time (certainly not by lack of material), XCELL is back, and will again bring you technical information and timely availability updates on Xilinx devices and development software.

The XC4000 family now has three devices in full production, with one more available in sample quantity. Many new packaging and speed options for XC3000 and XC4000 devices are now available (see page 2).

Early this year, we acquired Plus Logic, and made it the EPLD division of Xilinx, dedicated to Programmable Logic Devices based on EPROM technology. The AND/OR structure and predictable performance of these devices are popular with designers accustomed to PAL\* devices. The two presently available Xilinx devices offer interesting advantages in speed and density.

Xilinx development systems have made great strides to become more powerful and easier to use.

We have also improved our applications support and have published the first version of a Xilinx Applications Handbook, appropriately called XAPP.

Expect more devices, new technologies, new and better software, additional interfaces and platform support from Xilinx and third-party vendors. And expect to read about it in XCELL.

Welcome back!

Peter Alfke, Editor

@1992 by Xilinx, Inc. All rights reserved

# Two New Software Tools: X-BLOX and Xilinx ABEL

Xilinx has recently introduced two new software tools that shorten design cycles, and increase productivity. X-BLOX™ and Xilinx ABEL software tools provide intelligent, high-level design entry capabilities that significantly reduce the need for gate-level design.

Using X-BLOX tools with existing design-entry tools, logic can be designed at the block-diagram level. Functional blocks, like adders and registers, can be specified in a schematic, and incorporated directly into the design without detailed logic design. The X-BLOX synthesis design tool, however, is much more than a macro library.

A rule-based expert system creates optimized Hard Macros for each of the X-BLOX modules in the schematic. Data paths of any widthare automatically accommodated, and the XC4000 dedicated carry logic is used wherever appropriate. The result is an XNF file that can be placed and routed just like any other.

Xilinx ABELalso augments existing design entry tools, by permitting functional blocks to be defined using the industry standard ABEL" Hardware Description Language instead of gates. As with X-BLOX tools, the resulting XNF file can be placed and routed using the standard Xilinx tools.

Targeted primarily at automated state-machine design, Xilinx ABEL uses One-Hot encoding. This technique exploits the large number of flip-flops contained in LCA devices, while minimizing the impact of the CLB fan-in restriction. One-Hot encoding usually provides the highest performance state machines.

More detailed descriptions of X-BLOX and Xilinx ABEL software tools appear later in this issue.

PAL is a trademark of AMD.

#### **Table of Contents**

| General                            |       |

|------------------------------------|-------|

| Product Availability               | 2     |

| Benchmarks                         | 4,5   |

| Xilinx EPLD Architecture           | 3     |

| XC3000-150                         | 6     |

| New Applications Data Base         | 7     |

| Training                           | 22,23 |

| Software                           | ,     |

| State Machines Using Xilinx ABEL   | 6     |

| X-BLOX: High-Level Schematic Entry |       |

| ADI Version 3.20 Now Shipping      | 8     |

| Integrated Cadence Design Environm |       |

| Enhancements to PPR                | 9     |

| Hard Macros Control 4K Placement   | 9     |

| Hardware                           |       |

| XC4000 Dedicated Carry Logic       | 10    |

| HardWire: Low-Cost LCA             | 11    |

| Boundary Scan For Board Test       | 12    |

| Thin Quad Flat Pack                | 19    |

| LFSR Counters                      | 19    |

| Pinouts                            | 20,21 |

| <b>Applications</b>                |       |

| LCA Performance                    | 13    |

| Faster Multiplexers in XC3000      | 14    |

| XC3000 Counters                    | 15.16 |

Accelerating XC4000 Counters

18

<sup>&</sup>quot; ABEL is a trademark of Data I/O Corp.

# LCA Component Availability (July 1990)

|           |              | 44 PIN          | 68                                      | PIN            | 84              | PIN            |                 | 100 PIN         |                 | 120 PIN        | 132            | PIN             | 156 PIN        | 160 PIN         | 164             | PIN                              | 175            | PIN            | 191 PIN        | 196 PIN                                 | 208 PIN       |

|-----------|--------------|-----------------|-----------------------------------------|----------------|-----------------|----------------|-----------------|-----------------|-----------------|----------------|----------------|-----------------|----------------|-----------------|-----------------|----------------------------------|----------------|----------------|----------------|-----------------------------------------|---------------|

|           |              | PLASTIC<br>PLCC | PLASTIC<br>PLCC                         | CERAMIC<br>PGA | PLASTIC<br>PLCC | CERAMIC<br>PGA | PLASTIC<br>POFP | CERAMIC<br>COFP | PLASTIC<br>TOFP | CERAMIC<br>PGA | PLASTIC<br>PGA | CERAMIC<br>COFP | CERAMIC<br>PGA | PLASTIC<br>POFP | CERAMIC<br>COFP | TOP<br>BRAZED<br>CERAMIC<br>COFP | PLASTIC<br>PGA | CERAMIC<br>PGA | CERAMIC<br>PGA | CERAMIC<br>COFP                         | PLAST<br>POFF |

|           |              | PC44            | PC68                                    | PG68           | PC84            | PG84           | PQ100           | CQ100           | TQ100           | PG120          | PP132          | PG132           | PG156          | PQ160           | CQ164           | CQ164                            | PP175          | PG175          | PG191          | CQ196                                   | PQ208         |

|           | -50          | CI              | CI                                      | CIM            |                 |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC2064    | -70          | CI              | CI                                      | CIM            |                 |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -100         | С               | С                                       | С              |                 |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -33          |                 |                                         |                |                 | МВ             |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC2018    | -50          | CI              | CI                                      |                | CI              | CIMB           |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -70          | CI              | CI                                      |                | CI              | CIMB           |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -100         | С               | С                                       |                | С               | С              |                 |                 | С               |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -70          |                 | CI                                      |                | CI              | CIMB           | CI              | CIMB            |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC3020    | -100         |                 | CI                                      |                | CI              | CI             | С               | С               |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -125         |                 | С                                       |                | С               | С              | С               |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -150         |                 |                                         |                | С               |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -70          | CI              | CI                                      |                | CI              | CIM            | С               |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC3030    | -100         | С               | CI                                      |                | CI              | CI             | С               |                 | С               |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -125         | С               | С                                       |                | С               | С              | С               |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -150         |                 |                                         |                | С               |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -70          |                 |                                         |                | CI              | CIMB           | CI              | СМВ             |                 |                | CI             | CI              |                |                 |                 |                                  |                |                |                |                                         |               |

| XC3042    | -100         |                 |                                         |                | CI              | CI             | CI              | С               | С               |                | CI             | CI              |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -125<br>-150 |                 |                                         |                | CI              | CI             | CI              | С               |                 |                | CI             | CI              |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -70          |                 |                                         |                | С               |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -            |                 |                                         |                | CI              |                |                 |                 |                 |                | CI             | CIM             |                | С               |                 |                                  |                |                |                |                                         |               |

| XC3064    | -100<br>-125 |                 | 100000000000000000000000000000000000000 |                | C               |                |                 |                 |                 |                | CI             | CI              |                | С               |                 |                                  |                |                |                |                                         |               |

|           | -150         |                 |                                         |                | c               |                |                 |                 |                 |                |                |                 |                | С               |                 |                                  |                |                |                |                                         |               |

|           | -70          |                 |                                         |                | CI              |                |                 |                 |                 |                |                |                 |                | а               | СМВ             | мо                               | C              | CIMB           | CI             | CI                                      | CI            |

|           | -100         |                 |                                         |                | CI              |                |                 |                 |                 |                |                |                 |                | a               | С               | МВ                               | a              | CIMB           | CI             | CI                                      | a             |

| XC3090    | -125         |                 |                                         |                | С               |                |                 |                 |                 |                |                |                 |                | c               |                 |                                  | C              | c              | C              | C                                       | C             |

|           | -150         |                 |                                         |                | С               |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

|           | -6           |                 |                                         |                | CI              |                | CI              |                 |                 | CIM            |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC4002A   | -5           |                 |                                         |                | С               |                | С               |                 |                 | С              |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| V04000    | -6           |                 |                                         |                | CI              |                | CI              | МВ              |                 | CIMB           |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC4003    | -5           |                 |                                         |                | С               |                | С               |                 |                 | С              |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC4003A   | -6           |                 |                                         |                | 4092            |                | 4092            | 4092            |                 | 4092           |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| AC4003A   | -5           |                 |                                         |                | 4092            |                | 4092            |                 |                 | 4092           |                |                 |                |                 |                 |                                  |                |                |                |                                         |               |

| XC4004A   | -6           |                 |                                         |                | 4Q92            |                |                 |                 |                 | 4Q92           |                |                 |                | 4092            |                 |                                  |                |                |                |                                         |               |

|           | -5           |                 |                                         |                | 4092            |                |                 |                 |                 | 4092           |                |                 |                | 4092            | ••••            |                                  |                |                |                |                                         |               |

| XC4005    | -6<br>-5     |                 |                                         |                | CI              |                |                 |                 |                 |                |                |                 | CIMB           | CI              | МВ              |                                  |                |                |                |                                         | CI            |

|           | -6           |                 |                                         |                |                 |                |                 |                 |                 |                |                |                 | C 4002         | C 4002          |                 |                                  |                |                |                |                                         | C 4002        |

| XC4006    | -5           |                 |                                         |                |                 |                |                 |                 |                 |                |                |                 | 4Q92<br>4Q92   | 4092<br>4092    |                 |                                  |                |                |                |                                         | 4092<br>4092  |

| essesse i | -6           |                 |                                         |                |                 |                |                 |                 |                 |                |                |                 | 4092           | 4092            |                 |                                  |                |                | 3092           | 3Q92                                    | 3092          |

| XC4008    | -5           |                 |                                         |                |                 |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                | 3092           |                                         | 3092          |

| VOINIC    | -6           |                 |                                         |                |                 |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                | CIMB           | мв                                      | CI            |

| XC4010    | -5           |                 |                                         |                |                 |                |                 |                 |                 |                |                |                 |                |                 |                 |                                  |                |                | С              | 400000000000000000000000000000000000000 | С             |

C Commercial (0 - 70°C) I Industrial (-40 - 80°C)

## **Current Software List.**

The following is a list of the current software revision levels for Xilinx's development system products, as of June 1, 1992.

XCHECKER-PC1 ver. 1.00

XCHECKER-WS ver. 1.00

DS112 Enhanced Serial Configuration PROM Programmer ver. 3.20

DS22-PC1 P-SILOS ver. 4.10

DS290-PC1 VIEWsim ver. 4.13

DS310-PC1 DASH-LCA ver. 4.0

DS343-AP1 Mentor Interface ver. 4.02

\* See page 8 for details.

DS355-PC1 OrCAD VST Pre-Release

DS371 Xilinx ABEL ver. 1.01

DS380 X-BLOX ver. 1.01

DS381 Cadence Design Kit ver. 4.00\*

DS390-PC1 VIEWdraw-LCA ver. 4.13

DS391-PC1 VIEWlogic Interface ver. 4.13

DS396 XEPLD Workview Library ver. 3.10

XACT 2000/3000 Development System

DS501-PC1 ver. 3.20

DS501-SN2 ver. 3.20 on SUN4

DS501-AP1 ver. 3.15 on Apollo

XACT 2000/3000/4000 Dev. System

DS502-PC1 ver. 1.21

DS502-SN2 ver. 1.21 on SUN4

DS502-AP1 ver. 1.11 on Apollo

M Military (-55 - 125°C)

B MIL-STD-883, Class B

# **Xilinx EPLD Architecture**

Similar in purpose to FPGAs, complex erasable programmable logic devices, commonly referred to as EPLDs, combine the advantages of LSI – smaller size, less cost, higher reliability – with the user's need to create applications-specific circuits without incurring the cost, delay, and risk of mask-programmed gate arrays.

Different from FPGAs, the EPLD architecture is based on programmable logic array technology for both the functional logic and the interconnect structure. Each device contains a number of programmable units, called Function Blocks, each containing nine output macrocells driven by a programmable AND/ OR array. A programmable Universal Interconnect Matrix (UIM) routes any device input or any macrocell output to the input of any Function Block, completely eliminating the issue of routability.

This unrestricted programmable interconnect structure, combined with the familiar AND/OR logic of the traditional PAL architecture, makes EPLDs easy to use and easy to understand.

The delay through a Xilinx EPLD device is not only predictable, but also constant. Any func-

tion that can be implemented in one pass through the device can run at the maximum specified device speed, 33 or 40 MHz.

Xilinx EPLDs offer two unique advantages over competing EPLD devices.

- The XC7236 and XC7272 contain dedicated high-speed arithmetic carry logic for efficient implementation of fast adders, subtractors, accumulators, and comparators. This overcomes a traditional EPLD weakness.

- The UIM can perform a logic-AND function without additional delay, which means that complex counters of any practical length (32 bits in the XC7236, 64 bits in the XC7272) can run at full speed, even synchronously loadable up/down counters.

No other programmable technology comes close to this performance. Traditional PLDs support no more than 16 bits at full speed, and all channel-routed FPGA devices must concatenate the carry chain, resulting in slower operation for longer counters.

The Xilinx EPLD Data Book provides detailed information on the two available Xilinx EPLDs, the XC7236 and the XC7272.

#### XC7236 and XC7272

The XC7272 is a design revision of the original Plus Logic FPGA 2020, while the XC7236 is a design revision of the original Plus Logic Hiper 2010. The product nomenclature was changed to denote the number of macrocells instead of the less relevant gate-count number. As the names imply, the XC7236 has 36 macrocells, and the XC7272 has 72. The XC7236 is the more recent design; it incorporates some feature enhancements beyond the XC7272. The following paragraphs and table describe the extended features of the XC7236 that are supported by the current version of the XEPLD translation software, version 3.1.

- The XC7236 has a direct feedback path from the macrocell output to the OR input of either the same macrocell, or the neighboring macrocell. This speeds up the direct feedback, especially in counters and arithmetic circuits, and it saves UIM connections.

- The XC7236 has one additional FastClock input, for a total of three.

- The XC7236 has selectable logic polarity on all device inputs to the UIM and on device outputs, independent of the feedback.

- The XC7236 allocation of private and shared product terms among the two OR gates feeding the ALU is more efficient; and the ALU function is more streamlined. These differences may result in better functionality, but the software usually isolates the user from such details.

|                                             | XC7236 | XC7272 |  |

|---------------------------------------------|--------|--------|--|

| Number of Macrocells                        | 36     | 72     |  |

| Number of Function Blocks                   | 4      | 8      |  |

| Number of inputs to each Function Block     | 21     | 21     |  |

| Number of product terms per Function Block  | 57     | 57     |  |

| Total number of available product terms     | 228    | 456    |  |

| Maximum number of p-terms available         | 17     | 16     |  |

| per Macrocell logic function                |        |        |  |

| Total number of signal pins                 | 36     | 72     |  |

| (input, output, I/O) (largest package)      |        |        |  |

| Maximum number of pins available for input  | 32     | 54     |  |

| (largest package)                           |        |        |  |

| Maximum number of pins available for output | 34     | 60     |  |

| (largest package)                           |        |        |  |

## **Benchmark Wars**

The proliferation of programmable logic manufacturers and architectures has created confusion in the user community. How fast and how dense are these competing devices? How can I compare Xilinx against Actel, or against Altera?

Some vendors have made benchmark claims not only for their own devices, but also for their competitors. This has lead to ridiculously misleading statements: Citing four specific benchmarks, one competitor recently claimed, in public, a two-times speed advantage over the XC4005, when in reality, the XC4005 executes these benchmarks 71% faster. Another competitor has given lengthy comparisons between anti-fuse-based FPGAs, SRAM-based FPGAs, and EPLDs. Most of the "results" were tainted.

Nobody should believe any benchmark claims that are based on one vendor's evaluation of his competitor. A mixture of ignorance and marketing enthusiasm will inevitably distort the results and make them meaningless. Let every manufacturer demonstrate the performance of his devices; leave the comparison to the user.

PRÉPco, an independent company headed by Stan Baker, known as an editor of Electronic Engineering Times, is coordinating an effort by all PLD manufacturers (including Xilinx) to come up with a set of standardized benchmarks. Each of us will report on our own devices, but all our claims will be verified by our toughest competitor. These benchmarks will, therefore, be accurate and trustworthy. They may

not be the answer to every question, and there is room for improvement, for bigger and perhaps more meaningful benchmarks. But we have made an historic beginning. Expect detailed results from PREPco late this year:

#### Programmable Electronics Performance Corporation

504 Nino Ave., Los Gatos, CA 95032 Phone: (408) 356-2169 Fax: (408) 356-0195

In the meantime, Xilinx has collected some benchmark data to explain the performance of typical circuits in three different Xilinx architectures: XC3000, XC4000, and XC7200 EPLD.

PA

#### Xilinx Benchmark Data

|                                                               |                     | XC7200 EPLD (-25) | XC3000 F | PGA (-150) | XC4000  | FPGA (-5) |

|---------------------------------------------------------------|---------------------|-------------------|----------|------------|---------|-----------|

| 16-Bit State-skipping Counter, Presettab                      | le, non-binary      | na                | 150 MHz  | 18 CLBs    | 111 MHz | 12 CLBs   |

| 16-Bit Binary Counter                                         | Max Speed           | 40 MHz            | 116 MHz  | 24 CLBs    | 111 MHz | 17 CLBs   |

| 16-Bit Unidirectional, Loadable Counter                       | Max Density         | 40 MHz            | 20 MHz   | 16 CLBs    | 40MHz   | 8 CLBs    |

|                                                               | Max Speed           | 40 MHz            | 34 MHz   | 23 CLBs    | 42 MHz  | 9 CLBs    |

| 16-Bit Up/Down Counter                                        | Max Density         | 40 MHz            | 20 MHz   | 16 CLBs    | 40 MHz  | 8 CLBs    |

| 1/4                                                           | Max Speed           | 40 MHz            | 30 MHz   | 27 CLBs    | 40 MHz  | 8 CLBs    |

| 16-Bit Loadable, Up/Down Counter                              | Max Density         | 40 MHz            | 20 MHz   | 16 CLBs    | 30 MHz  | 16 CLB    |

| TV N. Weller S. Erst R. Hell 1200 Extended protein            | Max Speed           | 40 MHz            | 30 MHz   | 27 CLBs    | 30 MHz  | 16 CLB    |

| 16:1 Multiplexer                                              |                     | 25 ns             | 16 ns    | 8 CLBs     | 16 ns   | 5 CLBs    |

| 16-Bit Decode from Input Pad                                  |                     | 25 ns             | 15 ns    | 4 CLBs     | 8 ns    | 0 CLBs    |

| 24-Bit Accumulator                                            |                     | 17 MHz            | 25 MHz   | 46 CLBs    | 32 MHz  | 13 CLB    |

| Data Path Benchmark<br>(32 inputs, 4:1 mux, register, 8 l     | oit shift register) | 40 MHz            | 60 MHz   | 16 CLBs    | 90 MHz  | 12 CLB    |

| Timer/Counter Benchmark (8-bit timer/counter, latch, mux,     | compare)            | 40 MHz            | 30 MHz   | 21 CLBs    | 40 MHz  | 21 CLB    |

| State-Machine Benchmark<br>(16 states, 40 transitions, 10 inp | outs, 8 outputs)    | 40 MHz            | _        |            | 44 MHz  | 13 CLB    |

| Arithmetic Benchmark<br>(4x4 multiplier, 8 bit accumulato     | r)                  | 12 MHz            | 18 MHz   | 23 CLBs    | 18 MHz  | 21 CLB    |

| 16-Channel, 32-Bit DMA                                        |                     | na                | na       |            | 20 MHz  | 72 CLB    |

#### Notes

- All speeds are worst-case temperature and voltage.

- 2. System speeds for slower parts, e.g. XC3000-100, -70, can be approximated by derating appropriately (0.67 for -100, 0.47 for -70).

# **Ten XC4010 Density Benchmarks**

| No. | Application                                                   | XC4010<br>Total Gate Count |

|-----|---------------------------------------------------------------|----------------------------|

| 1   | 16-Bit Barrel Shifter or Rotator                              |                            |

|     | 32CLBs i.e. 12 circuits per XC4010                            |                            |

|     | 496 gates, all combinatorial, 15.5 gates per CLB              | 5,952                      |

| 2   | 24-Bit Accumulator                                            |                            |

|     | 12 CLBs i.e. 33 circuits per XC4010                           | vo recursive menusa menusa |

|     | 583 gates, 168 of them in flip-flops, 48 gates per CLB        | 19,239                     |

| 3   | 32-Bit Identity Comparator                                    |                            |

|     | 9 CLBs i.e. 44 circuits per XC4010                            |                            |

|     | 135 gates, all combinatorial, 15 gates per CLB                | 5,940                      |

| 4   | 9-Bit Parity Checker                                          |                            |

|     | 1CLB i.e. 400 circuits per XC4010                             |                            |

|     | 28 gates, all combinatorial, 28 gates per CLB                 | 11,200                     |

| 5   | 16-Input Multiplexer                                          |                            |

|     | 5 CLBs i.e. 80 circuits per XC4010                            |                            |

|     | 31 gates, all combinatorial, 6 gates per CLB                  | 2,480                      |

| 6   | 16-Bit Loadable Counter                                       |                            |

|     | 8 CLBs i.e. 50 circuits per XC4010                            |                            |

|     | 280 gates, 112 of them in flip-flops, 35 gates per CLB        | 14,000                     |

| 7   | 100-MHz 24-Bit Programmable Divider                           |                            |

|     | 16 CLBs, i.e. 25 circuits per XC4010                          |                            |

|     | 400 gates, 180 of them in flip-flops, 25 gates per CLB        | 10,000                     |

| 8   | 16 x 8 FIFO                                                   |                            |

|     | 14 CLBs i.e.28 circuits per XC4010                            |                            |

|     | 600 gates, 48 in FF, 512 in RAM, 42 gates per CLB             | 16,800                     |

| 9   | 32 x 8 Shift Register                                         |                            |

|     | 11 CLB i.e. 36 circuits per XC4010                            |                            |

|     | conceptually 1536 gates, all in flip-flops, 139 gates per CLB | 55,296                     |

| 10  | 32 x 16 RAM                                                   |                            |

|     | 16 CLBs i.e. 25 circuits per XC4010                           |                            |

|     | 2100 gates, 2048 in RAM, 131 gates per CLB                    | 52,500                     |

The source for these gate count values is the LSI Logic Data Book of July 87:

- 1. 16-input mux = 31 gates x 16 = 496 gates.

- 2. 16-bit fast adder (LSI page 3-99) = 277 gates x 1.5 = 415, +24 flip-flops x 7 gates = 583 gates.

- 3. 8-bit comparator (LSI page 3-74) = 30 gates, x4 = 120 + 4-bit comparator, total: 135 gates.

- 4. 9-bit parity (LSI page 3-163) = 28 gates

- 5. 16-input mux = 31 gates.

- 6. 74161 = 70 gates (LSI page 3-115), x4 = 280 gates.

- 7. Conservative estimate: less than  $1.5 \times \#6$  for same functionality.

- 128 latches x 4 gates = 512 gates.

- 256 flip-flops x 6 gates = 1536 gates.

- 10: 512 latches x 4 bits = 2048 gates plus some addressing.

### XC3000-150

Xilinx is currently sampling XC3000 devices in the new -150 speed grade. These devices are 15% – 20% faster than XC3000-125 devices.

The T<sub>ILO</sub> delay, often used as an LCA benchmark, is reduced from 5.5 to 4.6 ns, with similar reductions in the other timing specifications. As a result, a 16-bit loadable counter, that operates at 28.5 MHz in the XC3000-125, can be clocked at 34 MHz in the XC3000-150, an improvement of 19%.

In new designs, it is sometimes possible to trade the additional speed against CLB usage. For example, in the XC3000-125, a 16-bit carry-lookahead adder settles in 36 ns, while a more complicated and more costly conditional-sum adder requires only 26.5 ns. In the XC3000-150, the settling time of the simple carrylookahead adder is reduced to 29.5 ns. This provides most of the performance advantage of the XC3000-125 conditional-sum adder, but requires 25% fewer CLBs.

If you would like to simulate your design in an XC3000-150 device, a new speeds file is available through the Xilinx Technical Bulletin Board. The speeds file is the specification data base used by simulators when calculating performance. This file may be downloaded to replace the one currently in your system.

Contact Xilinx for a copy of the XC3000-150 Data Sheet. Production quantities of XC3000-150 devices are expected to be available in September '92.

# **State Machines Using Xilinx ABEL**

The traditional medium for logic design is the schematic diagram. Sometimes, however, the system design process naturally leads to equations or truth tables. In these cases, conversion to gates is an unnecessary extra step. To eliminate it, Xilinx has introduced the Xilinx ABEL software package.

This software package permits blocks of logic to be defined using the ABEL\* High-level Design Language. These ABEL definitions can be compiled into LCA netlists without having to represent the logic as gates. An additional benefit is that Xilinx ABEL software optimizes the implementation of the logic to fit the LCA architecture.

State machines are especially suitable for definition by equations or tables. A particular state is entered if, and only if, the current state and the control inputs to the state machine meet a pre-determined set of criteria. Listing these criteria describes the state machine completely.

Given the description of the state machine, the Xilinx ABEL software implements it using a technique that is well-suited to the LCA architecture. While LCA devices provide a large number of flip-flops, the CLB function generators have limited fan-in, and this environment favors One-Hot Encoded (OHE) state machines.

In an OHE state machine, also known as a state-per-bit encoded state machine, one flip-flop is assigned to each state. While fewer flip-flops could be sufficient if states are encoded, flip-flips are not normally a critical resource in LCA designs; the critical resource is CLB function-generator inputs.

OHE minimizes the complexity of the next-state logic associated with each flip-flop by spreading the task across the larger number of flip-flops. With OHE, a flip-flop is only set when its specific state is entered. Identifying the current state by a single bit makes it easier to combine the current state information with the control inputs.

State machines using OHE are typically faster than those using conventional state encoding. The reduced logic complexity results in fewer levels of CLBs to define the operation of each flip-flop. Consequently, logic delays are lower, and clock rates can be higher.

The inexpensive Xilinx ABEL software is not limited to state machine design. The ABEL language can be used to define any logic that is more conveniently defined using equations rather than gates.

BN

\* ABEL is a trademark of Data I/O Corp.

# X-BLOX Provides High-Level Schematic Entry

Have you ever sketched a block diagram on the back of an envelope, and wondered how well it would work? X-BLOX tools make it easy to find out. With the X-BLOX synthesis design tools, you can enter your block diagram into the existing design-entry package, and then have it automatically implemented in an XC4000 LCA device.

Using X-BLOX, a library of 30 frequently used block-diagram functions are available to construct designs. This library contains registers, adders, and counters; even RAMs and ROMs are provided. If necessary these functions can be combined with gate-level logic and any other library elements that are available.

The X-BLOX library is not just a collection of macros, however. A rule-based expert system converts each X-BLOX module in your design into an optimized custom Hard Macro. These Hard Macros are implemented in a way that best exploits the LCA architecture.

Wherever possible, the Hard Macros utilize the advanced features of XC4000 LCA devices. All adder and counter macros exploit the dedicated carry logic for maximum performance and minimum CLB count. RAM and ROM macros are automatically created by the X-BLOX software, and MEMGEN is not required.

Hard Macros improve the performance of the design by carrying the functional structure of the design into the implementation phase. CLBs that are common to a particular function are kept together in the array. This improved placement enhances both the

routability and the performance.

X-BLOX tools make it easy to change designs. Function modules are interconnected by single-line busses that are easily modified. Consequently, adding or removing modules is a simple task.

Bus widths are controlled by a single parameter located anywhere in a data path. Editing this one parameter not only changes the bus width throughout the data path, but also changes the width of all the functional blocks in the path. Even RAMs automatically change their depth to match the number of address bits.

High-level design with the X-BLOX design tools shortens the design cycle without sacrificing performance. Your engineering productivity is increased; more importantly, your product goes to market sooner.

BN

# **New Applications Data Base**

In late January, we installed a call tracking and problem resolution database for the Technical Support Hotline. Instead of having to keep individual notes about phone calls, our Applications Engineers (AEs) now have quick and easy access to a central record of customers, technical questions, and known problems.

When you call the Hotline, our Customer Response Center (CRC) asks you for your name and then calls up your record. After your first call, you never have to tell us again the details of your company address and phone number, the type of Xilinx software that you have installed, and the computer it runs on.

Attached to your record are files for each of your previous calls.

Each call record includes information about: when the call was opened, the Applications Engineer to whom it was referred, the topic of your question or request, notes about your questions, whether the record is open or closed, and when it was closed. The CRC staff can see your entire call history at once, and refer your call to the Applications Engineer best able to answer your question.

The AE can browse through your call history and see what you have discussed with other engineers during previous calls to the Hotline.

If no AE is available to take your call, the CRC staff queues the call so that the next available AE can accept it and call you back. Similarly, if you want to leave a

message for an engineer who is not on phone duty that day, the CRC staff will queue it to the AE's message bin.

The database is not only for call tracking, it also contains records of common problems and their solutions. Using symptom keywords from your description of the problem, the AEs can search the database, using the captured expertise of our entire Applications group.

In the future, we plan to make this part of the database available to our users. You'll be able to browse through the Customer Access Database and either download or fax back to yourself detailed explanations of known problems. Look for it next year.

DE

# **ADI Version 3.20 Now Shipping**

Xilinx has just released the latest version of the ADI software used with XC2000 and XC3000 LCA devices. Many improvements have been made resulting in more demanding designs being routed automatically.

The new algorithm significantly improves both the density and the performance of almost any design. Using the new algorithm, most designs that failed to route with the old algorithm are now completed automatically.

When compared using the Xilinx rogues'gallery of difficult designs, ADI version 3.20 completely routed more designs than before, and provided implementations that operated faster. Specifically designed to route LCA devices, the new router outperforms third-party tools.

The new router uses net delays to direct its operation. Nets that are routed early have greater access to routing resources. If nets that are routed later become excessively slow, previously routed nets can be "ripped up" to accommodate them. Similarly, previously routed nets can be modified to accommodate those that cannot be routed with the remaining resources.

Flagnet and Weightnet constraints should no longer be necessary with the new router, and may even be counter-productive. Flagged nets are routed first, and cannot be ripped up. Consequently, the resources they use cannot be re-allocated by the router, and slow or unrouted nets may result.

Along with the new routing algorithm, there is a new placement algorithm. The new algorithm operates much faster than the old one, yet provides results that are almost as good. Selecting the new algorithm with the -Y option reduces the LCA compilation time, and thereby increases design

productivity.

Support for 3-state busses is greatly improved. TBUFs with a common 3-state control are automatically aligned in a column. This permits a vertical Longline to be used for the 3-state control. In addition, logic associated with the TBUFs is placed close to this column, improving both performance and routability.

TBUFs can also be named, using the BLKNM attribute. Naming TBUFs permits them to be referred to easily in constraints files, improving the user's ability to floorplan within the CLB array.

To improve the floorplanning of inputs and outputs, IOBs can now be constrained to one edge of the device, or to half an edge. This constraint is often adequate to simplify PCB layout. However, it has a much smaller impact on LCA routing than locking a signal to a specific pin.

# **Fully Integrated Design Environment from Cadence**

Under a new OEM agreements, Cadence Design Systems will integrate the Xilinx XACT development system into the Composer\*design environment. This combination will provide a complete top-down-design environment and the convenience of a single software vendor, since the complete package will be sold and supported by Cadence.

In addition to entering designs as schematics, high-level design languages such as VERILOG-XL\* and VHDL-XL\* will be available to designers. X-BLOX will also be integrated into the design environment.

The top-down-design process will be timing-driven, with board-level timing objectives being passed to the FPGA implementation software. Timing information from the resulting FPGA design will then be passed back to the board-level model for simulation.

This closed-loop approach permits systems designers greater visibility into their designs, and greater control over the design process. Consequently, system requirements will be met more reliably, and in less time.

All LCA families are to be supported, and FPGA design kits will be available from Cadence, starting in the third quarter of '92. Initially, the software will run on Sun workstations, with other platforms to follow. Valid design kits will also be available.

<sup>\*</sup> Composer, VERILOG-XL and VHDL-XL are trademarks of Cadence Design Systems, Inc.

# **Enhancements to PPR**

Version 1.20 of the XC4000 partition, place and route software (PPR) is now available. This version offers designers several new features, aimed at improving performance and increasing productivity. Partitioning, placement and routinghave been enhanced.

XC4000 designers can now control logic partitioning at the schematic level. New FMAPs and HMAPs operate similarly to CLBMAPs in XC3000; the user can specify how gates are combined into CLB function generators.

In critical paths, the logic partitioning affects the performance of a design. FMAPs and HMAPs force PPR to use the partitioning envisioned by the designer. Consequently, performance requirements are more predictable.

The placement process, which often has the greatest effect on performance, is initialized by a random seed value. This component of randomness causes repeated runs of PPR to result in different placements. The new version of PPR can automatically evaluate the placements resulting from a user-defined number of seed values, and choose the best.

A new routing feature also helps ensure that performance requirements are met. Version 1.20 permits a maximum net delay to be specified. PPR continues rerouting the design until the longest net delay is less than this maximum value.

If PPR is unable to meet the specification, after a number of attempts determined by the user, it tries to meet a second, less demanding specification. If this requirement is also unattainable, PPR increases the delay specification in fixed increments until the requirement can be met, or until

the delay exceeds a worst-delay specification. In the latter case, PPR leaves unrouted those nets that do not meet the specification. All these delay specifications and increments are user definable.

Other features of version 1.20 include better support for the wide edge decoders, and improved constraint handling. The new version also provides better support for back annotation of the schematic.

# Control XC4000 Placement with Hard Macros

Hard Macros in XC4000 are often associated with adders and counters that use the dedicated carry. However, Hard Macros can improve the performance of most functions that benefit from controlled placement for efficient routing. To supplement the XC4000 Hard Macro Library, which contains many common functions, the program HMGEN lets the user create his own Hard Macros.

Unlike Soft Macros that define only the logic function, a Hard Macro contains additional information that defines relative CLB placement and pinutilization, and may also include routing information. However, it is easy for the autorouter to provide efficient routing once a good CLB placement has been defined.

Once constructed, Hard Macros are used in schematics like any other macro. PPR places a Hard Macros in the CLB array, according to the needs of the other logic. However, within a Hard Macro, relative CLB locations are not changed, and the routing advantages designed into the macro can be exploited by PPR.

To create a non-arithmetic Hard Macro, the logic schematic of the macro is entered normally, using FMAPs and HMAPs to determine the logic partitioning. PPR is then used to create an LCA file that is edited in the XACT Design Editor (XDE) to provide the desired placement. Any input and output pads are deleted, and the design is unrouted. After design rule checking (DRC), the resulting LCA file can be converted into a Hard Macro using HMGEN. Arithmetic Hard Macros are best created by modifying an existing Hard Macro in XDE.

The creation of user-defined Hard Macros is not recommended for inexperienced designers. Besides requiring use of the XDE, defining a Hard Macro requires that the designer consider the impact of using the macro in the LCA device. Inputs and outputs must be positioned within the macro such that they communicate efficiently with surrounding logic; the effect the macro has on over-all routing must also be considered. As a further constraint, Hard Macros must be rectangular in shape; unused resources within the rectangle are not available to PPR for other logic.

HMGEN is not part of any released Xilinx product but is available free of charge from Xilinx.

BN

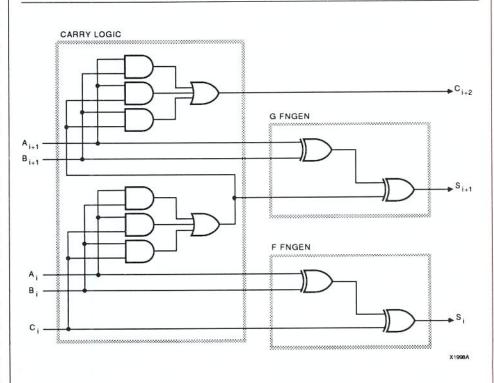

# **XC4000 Dedicated Carry Logic**

XC4000-series CLBs contain dedicated, hard-wired carry logic to accelerate and condense arithmetic functions such as adders and counters. Adders achieve carry delays as low as 750 ps/bit, while utilizing only half a CLB/bit. This is certainly denser than any other approach, and in most cases, faster.

The dedicated carry logic uses a simple ripple scheme for maximum flexibility. Adders and counters may be of any length, start anywhere in a column of CLBs, and have their MSB at either the top or the bottom. The carry can run up or down a column of CLBs, and can also run sideways at the top and bottom, accommodating very long adders and counters; when the adder or counter reaches the top or bottom of a column, it simply turns around and continues in the next one, and with no loss of performance.

Only the carry path of the adder is implemented in dedicated logic, as shown in the figure. Between CLBs, the carry is routed on special interconnect lines that are only available to the carry logic. This combination of dedicated logic and high-speed interconnect provides the high carry-propagation speed.

The carry network supplements the other resources in the CLB. The outputs from the carry chain are available as inputs to the CLB function generators. The adder sums are formed in these function generators, just as any other logic function.

In addition to the basic adder configuration, the carry logic and function generators may be configured to provide a subtracter or an adder/subtracter. All three functions can be modified to work with a single operand, providing incrementers and decrementers.

These incrementers and decrementers, together with the CLB flip-flops are used to generate the high-speed counters.

The performance achieved by the dedicated carry logic is outstanding; 16-bit adders and subtracters settle in 20.5 ns, and yet consume only eight CLBs. 32-bit adders and subtracters use 16 CLBs, and settle in 32.5 ns.

Loadable up counters and down counters use the same number of CLBs, and support clock frequencies of 40 MHz for 16 bits and 27 MHz for 32 bits. Non-loadable up/down counters also achieve these speeds and CLB counts, while loadable up/down counters are slightly slower, and required additional CLBs.

Currently, the user can access the dedicated carry logic in three ways. Firstly, Xilinx provides a library of Hard Macro adders and counters that use the carry logic. These Hard Macros may be incorporated directly into user designs at the schematic level. Alternatively, the user may generate his own Hard Macros using the HMGEN utility.

The third way to access the dedicated carry logic is through X-BLOX. All counters and arithmetic functions in X-BLOX are implemented with the carry logic. A Hard Macro of the appropriate size and functionality is automatically generated and used in the design.

In the future, it will be possible to access the dedicated carry logic at the schematic level.

For more information on the dedicated carry logic, please refer to the Xilinx Application Note *Using the Dedicated Carry Logic in XC4000* (XAPP 0013).

Conceptual Diagram of a Typical Addition (2 Bits/CLB)

# **Estimating Adder and Counter Performance**

In most LCA designs, performance cannot be estimated with any accuracy until after implementation. This is because the performance is affected by routing delays, and, prior to implementation, these are not known. However, in adders and counters using the XC4000 dedicated carry logic, delay estimation is possible.

The carry path in an adder uses dedicated interconnects between CLBs. These interconnects introduce a fixed delay, even when the carry passes from one CLB column to the next at the top or bottom of the array. This permits the routing delay to be incorporated into the CLB specifications published in the data sheet. As a result, the propagation delay through an adder can be calculated using only data-sheet specifications.

For a typical adder, this calculation can be reduced to a simple formula. In an XC4000-5, the maximum propagation delay from the operand input to the sum output of an N-bit adder is approximately

$$t_{pd} = 8.5 + 0.75 \,\text{N}$$

ns

This estimate does not include the delay from the operand source register to the adder or any additional delay reaching the destination register. However, it is still a useful benchmark.

For an N-bit counter, the minimum clock period that permits the carry path time to settle is approximately

$$t_{clk-clk} = 13 + 0.75 \, \text{N}$$

ns

For more information on the derivation and limitations of these formulae, please refer to the Xilinx Application Note *Estimating the Performance of XC4000 Adders and Counters* (XAPP 018).

BN

# Lower Cost for High-Volume Production

LCA devices are recognized as a cost-effective means of implementing logic during development and for limited volume production. However, for higher volume production, it may be necessary to reduce component costs. Masked gate arrays are an option, but converting a design to a gate array is costly in both time and money.

For mid-volume production, HardWire™ devices offer reduced component cost, avoiding the high cost of conversion because the mask-programmed HardWire devices are architecturally identical to their RAM-programmed counterparts. All the effort put into implementing the original design is re-used.

The HardWire mask is derived from the routed LCA file. Consequently, the HardWire device is guaranteed to be logically correct. The HardWire device is also guaranteed to meet, or beat, the worst-case delays of the RAM-based design. Logic partitioning, CLB locations and routing are all unchanged by the conversion, and mask-programmed interconnections are always faster.

Compare this automated, lowrisk approach to the gate-array conversion process: first, the netlist must be converted to gate-array format, followed by placement, routing, and simulation to verify the timing. These steps may need to be iterated several times to satisfy a critical timing requirement.

While gate arrays require a new set of test vectors to be developed for each design, Xilinx automatically generates test vectors for HardWire devices. Using dedicated scan-test logic built into the device, these test vectors provide 100% fault coverage.

HardWire device benefits go beyond the ease of conversion. An unexpected increase in the demand for a product that uses HardWire devices can easily be accommodated. Simply revert temporarily to the readily available programmable version that fits the same socket. Production is not delayed by complete dependence on a long-lead-time custom product.

RAM-based devices also simplify the addition of new features to extend the life of a product. Develop them in a RAM-programmable device in the production board and move the new design immediately into production, using RAM-programmed devices until a new HardWire device is available.

As production typically slows at the end of the product life cycle, it may again be more cost-effective to use RAM-programmed devices. Production is not constrained by minimum purchase requirements, and the standard devices will continue to be available as replacement parts.

Virtually all LCA designs are suitable for HardWire conversion. The only restriction is that correct operation may not depend upon some minimum delay; the HardWire device can be much faster. Such asynchronous design is considered bad practice, and a special design-rule-checking (DRC) program is used to evaluate all designs prior to conversion and to flag potential problems.

The first step in converting an LCA design to a HardWire design is to submit the design for evaluation. Once it is approved, prototype HardWire devices are available in six weeks. Production quantities follow eight weeks later.

Hard Wire versions of all three LCA families are available.

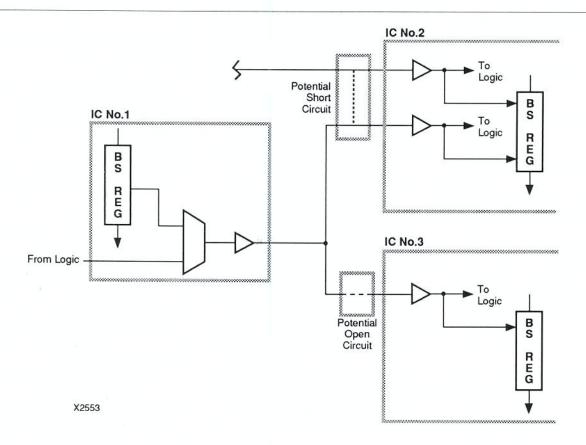

# **Boundary Scan Simplifies Board Test**

Testing of printed-circuit boards can be a major problem. While integrated circuits can be tested before insertion, there is no way to obtain such a high level of confidence in the interconnection network on which they depend. Simple open circuits and short circuits in the interconnect are fatal flaws, but are often difficult to detect.

Connectivity testing is a significant problem. As ICs become more complex, it is increasing difficult to control and observe the printed circuit traces between them. Probing the card with a "bed-of-nails" tester offers a possible solution, but, with denser packaging and devices surface-mounted to both sides of the board, even this becomes problematic.

Simplifying printed-circuitboard connectivity testing is the primary purpose of boundaryscan diagnostics. Circuitry associated with each pin permits a known signal to be driven onto every trace, and the signal to be checked at every destination. This test can be repeated with different signals to detect open and short circuits, and this can be done for every driver.

Test vectors are distributed to the drivers through a serial transmission path. The same path, which includes all inputs and outputs, is used to recover test results. The serial transmission scheme is standardized so that different vendors' products can work together. Its operation is defined by IEEE specification 1149.1, sometimes referred to as the JTAG specification after the committee that originated it.

IEEE 1149.1/JTAG boundaryscan testing is supported in XC4000-series LCA devices. Dedicated logic and pins provide a Test Access Port (TAP), as defined by the standard, and dedicated logic in the IOBs provide the boundaryscan Data Register and associated test functions.

Built-in self-test of the LCA device, which is optional under the IEEE specification, is not explicitly supported. However, the XC4000 LCA architecture permits internal logic to be connected to the TAP. Test logic can now be configured into the LCA device, and its operation controlled by the boundary-scan test system.

**Boundary-Scan Diagnostics**

#### Implementing Boundary Scan in XC3000

Although XC3000-series LCA devices do not contain dedicated boundary-scan logic, it is possible to configure an XC3000 to emulate boundary scan. This emulation consumes a significant amount of the LCA resources (almost all in an XC3020), and it is not suggested that boundary scan be built into a working design. However, because the RAM-based LCA device is reconfigurable, it can be configured for board testing, and then reconfigured for operation.

Four pins must be dedicated to the Test Access Port (TAP). Due to external interconnection requirements, these pins can probably not be re-used in the actual design. The TAP Controller, Instruction Register, Bypass Register and Test Data Output Buffer together with miscellaneous logic require 11 CLBs.

The CLB requirement for the Test Data Register depends upon the number of IOBs used, and how they are configured. Each requires between 0.5 and 1.5 CLBs, plus one CLB for each distinct 3-state control. While this may not allow every IOB to be bidirectional with an independent 3-state control, it will accommodate most designs.

A specific boundary-scan emulation must be created for each LCA design. This comprises the 11 CLBs of core logic, which is common to all emulations, and a Test Data Register concatenated from four macros according to the output usage in the design.

For more information on using boundary scan in the XC3000, see the Xilinx Application Note Boundary Scan Emulator for XC3000 (XAPP 007).

LCA Performance: Ask the Right Question

Before starting an LCA™ design, it is a good idea to do some quick performance calculations, just to make sure you are in the right ballpark. It is tempting to try estimating the highest speed that the design can achieve. However, it is usually much easier, and just as useful, to determine whether a predetermined speed can be attained.

Given the desired clock frequency, it is easy to estimate the logic complexity that can be supported. This complexity can then be compared to the functional requirements to determine feasibility. Only in marginal cases is a complete speed evaluation necessary.

Typically, a data path runs from a register, through some combinatorial logic to another register. In an LCA device, the shortest data path involves a CLB clock-to-output delay plus a CLB set-up time: a total of 9.5 ns in an XC3000-150. However, this time does not include any allowance for routing. Adding 4 ns for routing, the shortest data path is typically 13.5 ns.

If additional combinatorial CLBs are added into the data path, each level of CLB adds 4.5 ns, and additional routing delay is also introduced. Including a typical routing allowance, 8.5 ns should be added for each level of combinatorial CLB.

This simple speed-estimating procedure can also be reversed. If the system clock frequency is 30 MHz, the 33-ns period typically provides for two combinatorial CLBs between registered CLBs.

| Clock period       | 33   | ns |

|--------------------|------|----|

| Minimum delay      | 13.5 | ns |

| Remaining          | 19.5 | ns |

| Each combin. delay | 8.5  | ns |

| # of combin.       |      |    |

| CLBs possible      | 2    |    |

Including the function generator in the destination CLB, a total of three function generators can be cascaded. Knowing the number of function generators that can be cascaded, the design can be analyzed to determine whether or not it is feasible.

Of course, this is only a very rough calculation intended to establish feasibility; it neither establishes a performance limit, or guarantees that a level of performance can be achieved. It does, however, give some indication of the level of difficulty involved in the design.

In addition, critical areas can be identified prior to starting the design. It is better to accommodate critical areas from the outset, rather than "fix" them later. Conversely, if a design only requires a fraction of the capability available, it might be possible to multiplex some functions, and provide a less costly solution.

For information on how to use this procedure in other LCA devices, see the Xilinx Application Note LCA Speed Estimation: Asking the Right Question (XAPP 011).

BN

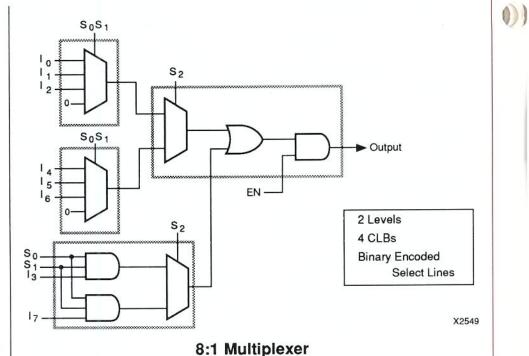

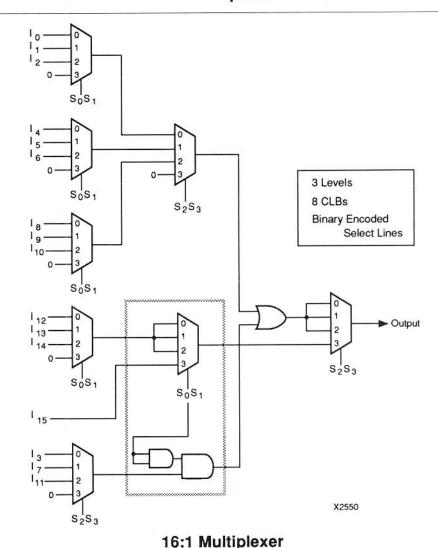

# Faster Multiplexers in XC3000

The traditional building block for large multiplexers in XC3000 is a dual 2-input MUX. This building block comprises two functions of three variables, and uses all five inputs to the CLB. A 4-input MUX cannot be constructed in a single CLB since it requires six inputs.

Using the dual 2-input MUX, larger multiplexers can be constructed using a conventional tree approach, with each select bit associated with one CLB level. This results in 8:1 multiplexers that use four CLBs in three levels, and 16:1 multiplexers that use eight CLBs in four levels.

However, a 3-input MUX can be implemented in only one CLB. Such 3-input MUX scan implement larger multiplexers that have less delay, while retaining the binary encoding of the select lines.

The 8:1 multiplexer, shown below, also provides an enable input. Again, four CLBs are used, but with only two levels of delay. The enable input permits the multiplexer to be expanded using only one additional level of CLBs. Decoded select lines are used to enable up to five 8:1 multiplexers into an OR gate. In this way, 3-level multiplexers with up to 40 inputs may be constructed.

For 16:1 multiplexers, the second design uses eight CLBs, and again has three levels of delay. It also has binary-coded inputs, and uses fewer CLBs than two 8:1 multiplexers with the necessary expansion logic.

BN

# **XC3000 Counters**

When selecting a counter design for a specific application, there are three primary considerations; does it meet the functional requirements, is it fast enough and could it use fewer LCA resources?

The functional requirements that must be considered include binary/non-binary operation, up, down and up/down counting, loadability, the provision of set/clear, count enable, and synchronous operation to permit output decoding. Speed and resource utilization are self-explanatory, and can often be traded against each other.

However, it must be realized that as a counter becomes more complex, it usually becomes both larger and slower. The table summarizes the characteristics of various counter designs available for the XC3000.

For a more detailed description of the designs mentioned below, see the individual Application Notes.

#### High-Speed Synchronous Prescaler Counter (XAPP 001)

This simple design provides a very basic non-loadable, up counter with a count-enable control. However, this simplicity permits it to be both the densest and the second fastest design. It is easy to convert the design into a down counter, but not possible to convert it into an up/down counter.

# Simple, Loadable, Up/Down Counter (XAPP 002)

Being loadable, this counter is unable to benefit from the prescaler technique, and a simple ripple-carry scheme is used throughout. Consequently, it is slower than the above design. The maximum clock frequency is inversely proportional to the length of the counter; the ripple-carry path incurs one  $T_{\rm ILO}$  delay for each two bits.

A modification to this counter almost doubles the maximum clock rate by dividing the carry path into two halves. With this modification, the carry path settles in approximately half the time. However, this modification requires one additional CLB.

# Synchronous Presettable Counter (XAPP 003)

In this design, speed is increased by replacing the serial gating of the ripple-carry path with parallel gating. Ideally, with arbitrarily wide gates, the carry-path settling time could be reduced to one gate delay.

However, with limited gate width, the settling time increases logarithmically with counter length; this is still a significant improvement over the linear increase seen previously, especially in longer counters. The additional speed is achieved at the cost of using more CLBs with more complex routing.

# Loadable Binary Counter (XAPP 004)

The loadable binary counter also uses parallel gating to accelerate the carry path. In this case, however, a more structured approach is taken. A fast lookahead-carry technique is used, resulting in a carry path with a consistent depth of gating. Consequently, there are many equally critical paths.

The regular structure lends itself to hand placement for maximum speed. The irregularity and smaller number of critical paths of XAPP 003 reduces its dependence on CLB placement, benefiting the automatic placement tools. XAPP 003 performance may be improved by re-routing a few critical paths, but it will not match an optimally placed XAPP 004.

#### Ultra-Fast Synchronous Counters (XAPP 014)

In some applications, such as clock division, the only requirement is a high clock rate. This counter is designed to fill that need. It is approximately twice as fast as XAPP 001 described above, but uses almost twice as many CLBs.

The key is the use of a prescaler technique, together with an active Longline to distribute the parallel count enable. This distribution scheme uses replicated flip-flops to eliminate delay but depends upon the predictability of the binary sequence.

#### Counter Performance in XC3000-150

|          | Loadable | Up | Down | Up/  | 8-1 | Bit  | 10- | Bit  | 12  | -Bit | 16        | -Bit | 20  | -Bit  | 24  | -Bit  | 32      | -Bit |

|----------|----------|----|------|------|-----|------|-----|------|-----|------|-----------|------|-----|-------|-----|-------|---------|------|

|          |          |    |      | Down | MHz | CLBs | MHz | CLBs | MHz | CLBs | MHz       | CLBs | MHz | CL Bs | MHz | CI Bs |         |      |

| XAPP 001 |          | •  |      |      | 80  | 5    | 68  | 8    | 65  | 9    | 65        | 14   | 63  | 17    | 63  | 21    | 1411 12 | OLDS |

| XAPP 002 | •        |    | •    | •    | 31  | 8    | 25  | 10   | 25  | 12   | 20        | 16   | 15  | 20    | 13  | 24    |         |      |

| XAPP 002 | •        |    |      |      |     |      |     |      |     |      | 28        | 17   | 13  | 20    | 13  | 24    |         |      |

| XAPP 003 |          |    |      |      | 39  | 8    |     |      | 32  | 15   | 31        | 20   |     |       |     |       |         |      |

| XAPP 004 |          |    |      |      |     |      |     |      | OL. | 13   | 34        |      |     |       |     |       |         |      |

| XAPP 004 |          |    |      |      |     |      |     |      |     |      |           | 23   |     |       |     |       | 23      | 49   |

| XAPP 014 |          |    |      |      |     |      |     |      |     |      | 30<br>116 | 27   |     |       |     |       | 23      | 56   |

## 150-MHz Presettable Counter in XC3000

Prescaling is an established technique for high-speed counters. Using a derivative of this technique, LCA devices can implement a presettable counter at the full 150-MHz togglerate of an XC3000-150. These counters can be up to 24-bits long.

In a prescaler counter, a small, very fast counter divides the clock rate. The divided clock is provided to a large, slower counter that is unable to settle at the fast clock rate. However, even when implemented synchronously, a conventional prescaler counter cannot be loaded; the technique depends upon the predictable binary sequence to ensure that the larger counter has adequate settling time.

If the prescaler counter is loaded with an arbitrary value, the binary sequence is broken, and the settling time of the larger counter is no longer guaranteed. To ensure an adequate settling time, either the clock frequency must be reduced significantly, or the values that can be loaded must be severely restricted.

To provide presettable prescaler counters, John Nichols of Fairchild Applications introduced a pulse-swallowing technique in 1970. It uses a dual-modulo prescaler that can divide the clock by 2<sup>n</sup> or 2<sup>n</sup>+1. See page 6-38 of the Xilinx 1992 Data Book for further information.

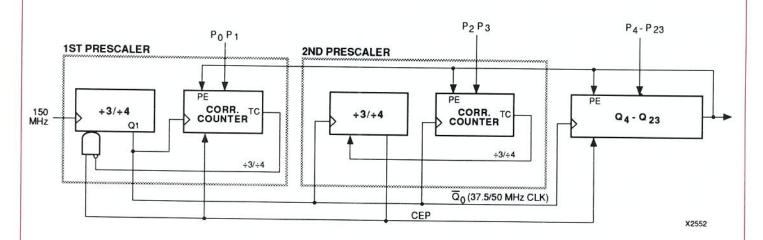

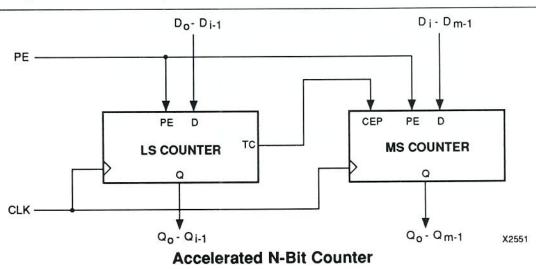

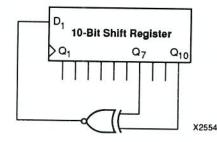

Twenty years later, Xilinx developed a variation of the the pulse-swallowing technique for use in LCA devices. This technique, called state-skipping, uses a dual-modulo prescaler that can divide by 2<sup>n</sup> or 2<sup>n</sup>-1.