THE QUARTERLY JOURNAL FOR XILINX PROGRAMMABLE LOGIC USERS

The Programmable Logic Company<sup>SM</sup>

# **Inside This Issue:**

#### **GENERAL**

| From The Fawcett:                   |

|-------------------------------------|

| The Next 10 Years 2                 |

| Guest Editorial: Who Should         |

| Supply FPGA Tools                   |

| 1994 Data Book Available 4          |

| Customer Success Story: Cabletron 5 |

| Literature Availability 6           |

| Upcoming Events7                    |

| Financial Results7                  |

| Component Availability 8            |

| Development Systems Availability 9  |

| Alliance Program Companies 10       |

| Training Opportunities 11           |

| FPGA Prices Continue to Fall 12     |

|                                     |

#### **PRODUCTS**

| introducing the Logic Professor | 13 |

|---------------------------------|----|

| XC4000-4 Boosts Performance     | 14 |

| XC3195 Benchmarks               | 15 |

| New Military Drawings           | 16 |

| New Serial PROMs                | 17 |

| Customer Survey Results         | 17 |

#### **DEVELOPMENT SYSTEMS**

| Synopsys and Xilinx      | 18 |

|--------------------------|----|

| XACT 5.0 Schedule Update | 19 |

| XEPLD 5.0 20-            | 21 |

| XChecker 3Volt Adapter   | 21 |

| New Xilinx EPLD Fitter   |    |

| ISDATA Improves Support  | 23 |

| Cadence Enhances Support | 23 |

#### **HINTS & ISSUES**

| XACT 5.0 Release:             |       |

|-------------------------------|-------|

| What's in the Box?            | 24-25 |

| Synopsys Design               |       |

| Methodology Notes             | 25    |

| Implementing High-Performance |       |

| RAM-Based FIFOs               | 26-29 |

| Questions & Answers           | 30-31 |

| FAX Response Form             | 32    |

|                               |       |

# **GENERAL FEATURES**

# Xilinx Celebrates 10 Great Years

Editor Bradly Fawcett ruminates on the past 10 years of Xilinx success and looks ahead to the next ten years...

See Page 2

# PRODUCT INFORMATION

# New Product:

# Meet Mr. Logic

Xilinx's new Logic Professor software will help you select the right EPLD for the job.

See Page 13

# Xilinx-Synopsys

Alliance member Synopsys and Xilinx establish a partnership to develop new FPGA tools...

See Page 18

# DESIGN TIPS & HINTS

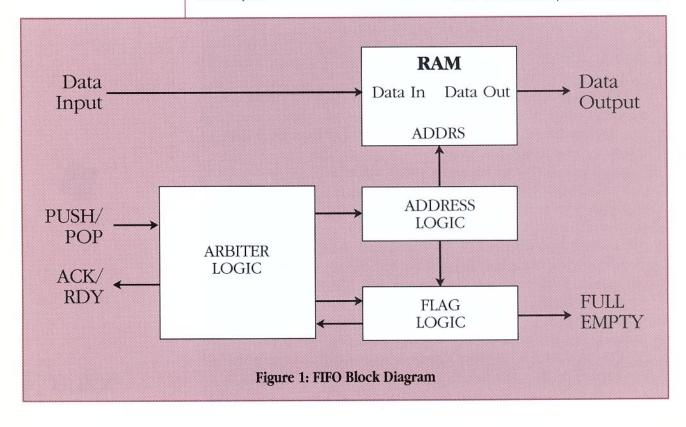

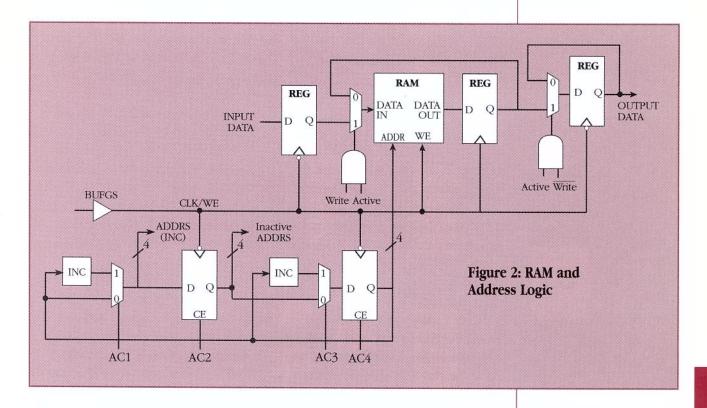

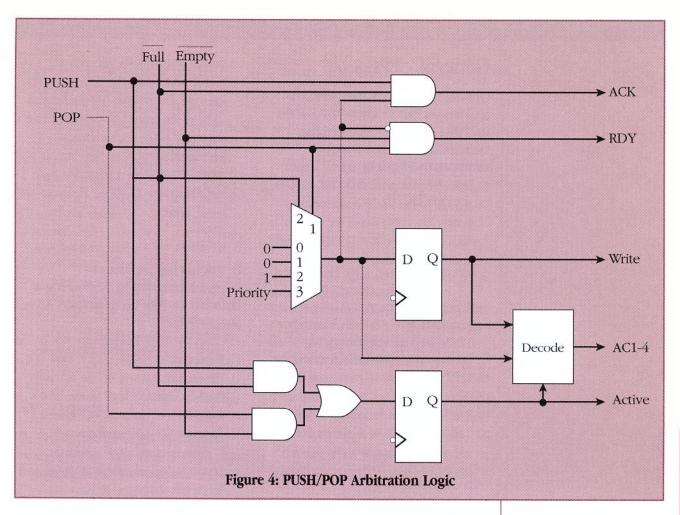

# **Fast FIFO Buffer** in the XC4000

Using XC4000 on-chip FIFOs for increased integration and performance.

See Page 26

# Looking Forward to the Next Ten Years

By BRADLY FAWCETT ◆ Editor

le m m m le co au th h lo gr

leading-edge technology to meet a market need. The market needed higher levels of logic integration combined with low risk and short time-to-market; the inspirational idea was high-density programmable logic based on SRAM programming and a gatearray-like logic cell array

architecture with programmable routing; the leading-edge technology was fine-geometry CMOS fabrication processes. FPGAs fulfill designers' needs by combining the speed and density of a custom gate array with the design flexibility of a programmable logic device.

#### The First 10 Years

FPGA technology has advanced dramatically in its first 10 years. The first FPGA, the XC2064, boasted a maximum of 1,200 gates (about 800 usable gates), 58 user I/Os, and a 20 MHz flip-flop toggle rate.

Designs were implemented on PC/XT systems using a graphical, interactive design editor in which the user defined the logic functions that went into each logic block.

Xilinx devices now reach 13,000 usable gates ANNIVERSARY

and 192 I/Os; even larger parts are on the immediate horizon. The fastest devices have toggle rates exceeding 250 MHz.

The third-generation FPGAs, the XC4000

family, includes dedicated system-integration features such as on-chip RAM, wide decoders, carry logic and built-in boundary scan test support. Designs are implemented on PCs or workstations, entered using schematics or HDLs, automatically mapped into the FPGA's logic resources and automatically placed and routed.

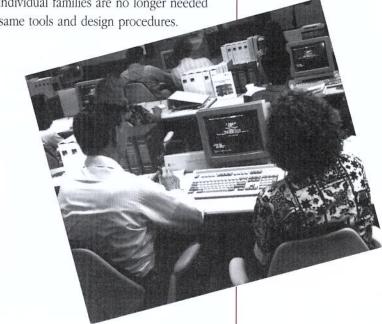

In the meantime, component prices have decreased dramatically, falling 25 to 30 percent each year. FPGAs are a cost-effective logic solution for thousands of applications, ranging from supercomputers to hand-held instruments, from central office switches to centrifuges, and from missile guidance systems to guitar synthesizers. (And, by the way, the venerable XC2064 is still a popular device, available now with toggle rates up to 130 MHz, and at a cost of less than \$5 when purchased in large quantities and plastic packages.)

#### The Next 10 Years

The FPGA market continues to grow by more than 30 percent annually, primarily as a result of continuing technology improvements. Continued innovation in FPGA architectures, VLSI circuit design, process technologies, and 'place and route' algorithms will lead to faster, denser, and more

cost-effective devices. FPGA technology is readily adaptable to the 3V, sub-half-micron, multi-metallayer IC technologies of the near future. Gate densities in the 50,000 to 100,000 gate range and system clock rates of 200 MHz should be achievable by the turn of the century.

On the software side, FPGAspecific synthesis technology will continue its rapid evolution, driven by the demand of a community of FPGA designers that has

XCELL

Please direct all inquiries, comments and submissions to:

Editor: Bradly Fawcett

Xilinx, Inc.

2100 Logic Drive San Jose, CA 95124

Phone: 408-879-5097 FAX: 408-879-4676

E-Mail: brad.fawcett@xilinx.com

©1994 Xilinx Inc. All rights reserved.

XCELL is published quarterly for customers of Xilinx, Inc. Xilinx, the Xilinx logo and XACT are registered trademarks; all XC-designated products, UIM, HardWire and XACT-Performance are trademarks; and "The Programmable Logic Company" is a service mark of Xilinx, Inc. All other trademarks are the property of their respective owners.

Continued on page 6

# Who Should Supply FPGA Implementation Tools?

by HANS SCHWARZ • Director, Development System Marketing

The three main steps of the FPGA development cycle are design entry, implementation, and verification. Xilinx was the first PLD vendor to offer an open system, in that the user can choose from a wide variety of design entry and verification tools from any of a number of third-party EDA vendors. However, Xilinx has been and remains the primary supplier of the design implementation software, often referred to as the 'place and route' or 'backend' tools, that support our FPGA families.

Some EDA vendors have recently entered the market with their own FPGA implementation tools, and a few new FPGA vendors are relying exclusively on third-party EDA vendors for their 'place and route' tools. These EDA suppliers suggest that they will eventually take over the market for FPGA implementation software.

While we appreciate the attractiveness of the FPGA tool market to the EDA suppliers, Xilinx must continue to develop and market the implementation tools that support our EPLD and FPGA products. The rationale behind this decision relates directly to the differing motivations of silicon vendors and EDA vendors for offering these products.

Our primary motivation is to sell programmable logic ICs. We develop implementation software because our users need a timely and economical solution — a solution that includes both IC devices and software. We want to expand the

programmable logic market by lowering the cost of the technology and making it easy to use. Thus, our software is priced as low as feasible to encourage the use of the technology. Furthermore, the software must take advantage of the special features of our architectures to provide all the performance and capacity that the ICs are designed to deliver.

The EDA vendors are motivated to sell only software, and must sell a common solution to address many needs. EDA vendors are more likely to develop 'general-purpose' software to address a broad market than to develop customized tools for a particular architecture. While this 'universality' is attractive to a customer interested in exploring solutions from multiple IC vendors, it may also inadequately address the unique features of a specific architecture and negate a silicon vendor's competitive advantages. So, while the EDA vendor tries to satisfy the desire for a universal environment ("learn on one system and it will work with every vendor"), the user needs to ask if this concept benefits the user, or if it's even true.

Similarly, Xilinx is highly motivated to improve the silicon efficiency and performance of the ICs. Therefore, after the initial software release, we have a

continue to develop and market the implementation tools that support our EPLD and FPGA products.

# The 1994 Data Book is Here

The new 1994 Xilinx Data Book is now available. It is a revision of the 1993 Data Book, with many improvements and 72 new pages.

New information in the 1994 Data Book includes AC timing parameters for the XC4000-4, XC3000A, XC3000L, and XC2000L FPGA families. Product specifications were added for the new XC3100A family, the XC7336 EPLD, and the XC7354 EPLD, as well as advance product information for the XC73144. Other additions include new package drawings, updated development system descriptions, updated quality and reliability information, and several new application notes.

If you have not yet received a copy of the 1994 Xilinx Data Book, please contact your local Xilinx sales representative or distributor.

#### **GUEST EDITORIAL**

Continued from page 3

strong motivation to improve the software and deliver updates to our users, thereby enhancing the capabilities of the ICs. Such motivation does not exist for the EDA vendor.

Xilinx believes that the following strategy can provide the tools needed to achieve the designer's goals:

- Provide for the use of popular, generalpurpose tools for the 'generic' portions of the design cycle: design entry and design verification.

- Provide low-cost, architecturally-specific implementation tools within the EDA vendor's framework.

- Provide a tight coupling between the two environments.

- Provide timely support for all new ar-

**66** We welcome the

opportunity to

benchmark ourselves

against the best that

others can offer.. 99

chitectures.

· Continue to improve the speed and density of the ICs through software improvements and enhancements.

This solution

offers universal capabilities at the front-end where design decisions are made. Tight coupling allows for excellent design analysis and feedback. The designer has access

to the software when the silicon is ready and accessibility to the features of each architecture.

To support these objectives, we established our Alliance Program in 1990 to work with key EDA vendors to provide a tight interface to popular entry and simulation tools. The more-recently formulated Syndicate Program focuses on FPGA interfaces and compilers for synthesis tools.

Through internal development of EPLD and FPGA implementation tools, Xilinx retains control over product introduction schedules, ensuring the timely availability of tools to support new leading-edge architectures. Furthermore, by developing our own implementation tools, we retain valuable in-house expertise and benefit from the synergy that results when both the designers of the IC architectures and the designers of the development tools work closely together on a continuing basis.

High-density programmable logic devices are becoming sufficiently pervasive that both silicon and EDA vendors will have opportunities to market implementation tools. We welcome the opportunity to benchmark ourselves against the best that others can offer. The resulting competition can only result in all suppliers being pushed harder to provide the best solutions, to the ultimate benefit of all users of PLD software development tools. •

# Fast-Rising Cabletron Chooses Xilinx For Time-to-Market, Synthesis Support

Cabletron Systems, reputedly a lean and mean operation, has never been content to rest on its laurels. Since 1983, the Rochester, NH, maker of wiring hubs, the "central nervous system" of local area networks, has seen annual revenues grow at a meteoric rate of 95 percent per year.

By creating "materials acquisition teams," purchasing teams comprised of finance, inventory planning and manufacturing personnel, Cabletron has been successful at shortening product delivery schedules from 50 to 35 days.

#### **Shared Philosophies**

When Cabletron considered designing Xilinx XC4010 FPGAs into a new universal hub called the MMAC-Plus, it found that Xilinx uses similar team approaches when the company combined sales representatives, field applications engineers and factory service personnel into its "Cabletron support team."

According to Julius Baskys of sales representative firm Genesis Associates, "Xilinx was put through rigorous evaluations along with a number of other programmable logic suppliers. Xilinx won the account based largely on three factors: a corporate commitment to surround Cabletron with the highest level of support for their project, a broad base of silicon products and our support of VHDL and synthesis through our alliances with Cadence and Synopsys."

#### **High-Density Design**

Several of the MMAC-Plus modules contain 22 XC4010 FPGAs (approximately 220,000 logic gates) each. The FPGAs are used to implement nearly all of the logic required for the design, including protocol converters and bus interfaces.

#### Rapid Time-to-Market With FPGAs and Synthesis

Getting the MMAC-Plus to market quickly was a top goal of the design

project. The design was entered using Verilog-HDL, synthesized with Synopsys tools and implemented in Xilinx devices. By switching from schematics to a high-level description language, Cabletron was able to minimize design entry and verification times. Time-to-production was further decreased by using fieldprogrammable Xilinx devices.

The MMAC-Plus universal bub uses 22 XC4010 FPGAs.

# Looking to the Future

Cabletron has already completed 25 different designs for high volume production using Xilinx XC4000 devices, testimony to the working relationship between the two companies. According to Dennis Rainville, Cabletron's Manager of Hardware Development, "We're especially excited about the recent announcement of a five-year partnership between Xilinx and Synopsys. Their joint efforts to streamline high-level design for FPGAs should help to further improve development cycles for our future products."

# **New Product Literature**

Learn about the newest Xilinx products and services through our extensive library of product literature. The most recent pieces are listed below. To order please contact your local Xilinx sales representative. •

| TITLE                                                  | DESCRIPTION                                                    | PART NUMBER |

|--------------------------------------------------------|----------------------------------------------------------------|-------------|

| FPGAs                                                  |                                                                |             |

| XC3000A Family Overview                                | Features/benefits                                              | #0010178-01 |

| XC4000 vs. Altera FLEX                                 | White paper                                                    | #0010189-01 |

| EPLDs                                                  |                                                                |             |

| XC7336 Family Datasheet                                | Technical data                                                 | #0010190-01 |

| XEPLD Translator Software Overview                     | Features/benefits                                              | #500650-01  |

| XC7000 vs. AMD MACH                                    | White paper/features comparison                                | #0010188-01 |

| Development Systems                                    |                                                                |             |

| Xilinx Development Systems<br>(with XACT 5.0) Overview | Features/benefits                                              | #0010101-03 |

| Corporate                                              |                                                                |             |

| 1994 Xilinx Databook                                   | Technical data on FPGAs, EPLDs,                                | #0401224-01 |

|                                                        | PROMs, and development systems.<br>Includes applications notes |             |

For a complete list, please contact your sales representative or see XCELL Issue #10.

#### THE FAWCETT

Continued from page 2

grown larger and continues to grow faster than the gate array design community. Increasingly, logic synthesis tools are incorporating knowledge of FPGA architectures, both logically and topologically, leading to more efficient resource utilization. Future FPGA architectures will be influenced by the needs and capabilities of these synthesis tools.

Bidirectional links will be established between the synthesis/simulation tools and the FPGA 'place and route' implementation tools, allowing time and area constraints to be easily passed back and forth. The result will be a top-down design methodology that encompasses design creation, analysis, and physical implementation in a seamless software environment, improving both designer productivity and silicon efficiency.

Besides replacing older logic technolo-

gies, SRAM-based FPGAs have brought an important new capability to systems design — the ability to reconfigure logic "on-the-fly" during system operation. The coming decade will see the continued expansion of reprogrammable end-use applications, such as advanced ASIC emulation systems. (This subject is worthy of a column of its own, so let's save it for a future XCELL ...)

Xilinx is proud to be the world's leading supplier of CMOS programmable logic, and we are looking forward to continuing to expand the high-density programmable logic market that we pioneered and developed. But most of all, we are looking forward to continuing to serve the needs of you — our customers — who have made this all possible. Thanks for a great ten years!

#### **UPCOMING EVENTS**

The fourth annual PLD Design Conference and Exhibit will be held April 11-13 at the San Jose Convention Center in San Jose, CA. This conference is intended for system-level engineers and engineering managers interested in the use of programmable logic devices. The first day is dedicated to tutorials, followed by two days of paper and panel sessions. Meanwhile, leading programmable logic and CAE suppliers will be exhibiting their products on the convention floor.

Xilinx products are prominently mentioned in several of the papers scheduled for presentation. Of particular interest is a Wednesday afternoon session on data communications applications that will feature case histories of three Xilinx-based designs. Bill Carter, Vice-President of Product Development for Xilinx, is a member of the Tuesday evening panel discussion on the future of programmable logic technology.

Our thanks to the many Xilinx users who submitted papers to this conference. Nearly 200 abstracts were submitted for the conference, and, with just 30 presentation slots available, the conference's technical program committee had to reject many worthy submissions.

The conference is sponsored by CMP Publications, the publishers of *Electronic Engineering Times*. For registration information, look for registration forms in *EE Times* magazine, or contact Kathleen Pizzo here at Xilinx (Tel: 408-879-5377 Fax: 408-879-4676). Be sure to drop by to visit us at the Xilinx booth!

Xilinx will be participating in several other conferences and workshops this spring. Look for Xilinx technical papers and/or product demonstrations at these upcoming industry forums:

Mid-Lantic Electronics Show March 29 - 30, King of Prussia, PA

IEEE Workshop on FPGAs for Custom Computing Machines (FCCM '94) April 10-13, Napa, California

Colloquium on Software Support & CAD Techniques For FPGAs April 13, London, England

Fourth Annual Advanced PLD & FPGA Day May 18, London, England

Canadian Workshop on FPGAs June 13-16, Kingston, Ontario

**Design Automation Conference (DAC)** June 6-10, San Diego, CA

PLD Design Conference June 21-23, Tokyo, Japan

# Mark Your Calendars

For further information about any of these conferences, contact Kathleen Pizzo (Tel: 408-879-5377 Fax: 408-879-4676).

#### FINANCIAL REPORT

# **Rapid Revenue Growth Continues**

Xilinx Inc. achieved double-digit growth in the third quarter of FY94 (ended Jan 1, 1994). Sales revenues rose to \$66.5 million, a 10.7 percent increase from the immediately preceding quarter. For the first nine months of the fiscal year, revenues increased 42 percent to \$181 million compared to the same period in the prior fiscal year. (Xilinx stock is traded on the NASDAQ exchange under stock symbol XLNX.)

Revenues from all Xilinx logic families increased during this quarter. The major contributors were the high-density XC4000 and high-speed XC3100 FPGA families, with sales increases of 30 and 35 percent, respectively, compared to the previous quarter. The XC3100 family set a Xilinx record for the fastest sales growth of any product line in its first year of introduction, generating a total of \$12 million in revenue over the last four quarters. •

#### **COMPONENT AVAILABILITY CHART - FEBRUARY 1994** $COD_E$ PINS TYPE • PLASTIC PLCC PC44 • • 44 N CERAMIC CLCC WC44 48 PLASTIC DIP PD48 . . . 64 PLASTIC VQFP VQ64 ++ 4 4 4 4 PLASTIC PLCC PC68 +++ 68 CERAMIC CLCC WC68 CERAMIC PGA PG68 PLASTIC PLCC PC84 WC84 CERAMIC CLCC • ... ... PG84 CERAMIC PGA 4 4 PLASTIC PQFP PQ100 4 4 4 4 4 4 4 4 4 4 4 + + PLASTIC TOFP TQ100 100 4 4 ++ ++ PLASTIC VQFP VQ100 • TOP BRZ. CQFP CB100 120 CERAMIC PGA +++ PG120 PP132 PLASTIC PGA 132 CERAMIC PGA PG132 . ++ TQ144 PLASTIC TQFP 144 CERAMIC PGA PG144 156 CERAMIC PGA PG156 ♦ ♦ NNN 160 44 PLASTIC PQFP PQ160 164 TOP BRZ. CQFP CB164 • **\* \*** PP175 PLASTIC PGA 175 ++ CERAMIC PGA PG175 176 PLASTIC TOFP TQ176 191 CERAMIC PGA PG191 196 TOP BRZ. CQFP CB196 . • PLASTIC PQFP PQ208 208 METAL MQFP MQ208 ♦ N • • 223 CERAMIC PGA PG223 PLASTIC BGA PB225 225 CERAMIC BGA WB225 CERAMIC BGA CG225 PQ240 PLASTIC PQFP 240 METAL MQFP MQ240 N 299 CERAMIC PGA PG299

<sup>♦ =</sup> Product currently shipping or planned N = New since last XCELL

|                        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       | Previous     | Cus     | RENT V      | FRSION       | Ry PLAT     | TEORM                    |                |

|------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|---------|-------------|--------------|-------------|--------------------------|----------------|

| PRODUCT<br>CATEGORY    | PRODUCT DESCRIPTION | Product<br>Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XILINX PART<br>NUMBER | VER.<br>REL. | PC1 5.0 | NC2<br>3.30 | SN2<br>4.1.x | AP1<br>10.4 | HP7<br>9.01              | LAST<br>UPDATE |

|                        |                     | ronenon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TVOMBER               | IXEL.        | 5.0     | 5.50        | 7.1.1        | 10,4        | 2.01                     | CIBAIL         |

| CORE FPGA              | DUAL PRODUCTS       | Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DC FO2                | 1.41         | 1.40    | 1.42        | 1 10         | 1.40        | 1.40                     | 07/02          |

| CORE EPLD              | XC2,3,4K SUPPORT    | CORE IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DS-502-xxx            | 1.41         | 1.42    | 1.42        | 1.42         | 1.42        | 1.42                     | 07/93          |

| MENTOR <sup>1</sup>    | XC7K SUPPORT        | CORE IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DS-550-xxx            | 4.00         | 4.10    |             | 4.10         | 4.10        |                          | 08/93          |

| MENTOR <sup>1</sup>    | V8                  | I/F AND LIBRARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DS-343-xxx            | 4.00         |         |             | 1.10         | 4.10        | 1.10                     | 02/93          |

| OrCad <sup>2</sup>     | Võ                  | I/F AND LIBRARIES I/F AND LIBRARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DS-344-xxx            | 1.00         | 4.22    | 4.20        | 1.10         | 1.10        | 1.10                     | 07/93          |

| Synopsys <sup>1</sup>  |                     | I/F AND LIBRARIES  I/F AND LIBRARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DS-35-xxx             | 4.22A        | 4.23    | 4.20        | 2.01         | 2.01        | 2.01                     | 06/93          |

| Viewlogic <sup>2</sup> | VisuDouu            | I/F AND LIBRARIES  I/F AND LIBRARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DS-401-xxx            | 2.00         | 4.15    |             | 3.01         | 3.01        | 3.01                     | 09/93          |

| Viewlogic <sup>2</sup> | ViewDraw            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-390-xxx            | 4.14         | 4.15    |             |              |             |                          | 06/93          |

| Viewlogic <sup>2</sup> | VIEWSIM             | I/F AND LIBRARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DS-290-xxx            | 4.14         | 4.15    |             | F 01         |             |                          | 06/93          |

|                        |                     | I/F AND LIBRARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DS-391-xxx            | 4.14         | 4.15    |             | 5.01         |             |                          | 06/93          |

| XABEL <sup>2</sup>     |                     | ENTRY, SIM, LIB, OPT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DS-371-xxx            | 1.03         | 4.30    | 1.01        | 1.03         | 4.04        |                          | 10/93          |

| X-BLOX <sup>1</sup>    |                     | Architectural Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DS-380-xxx            | 1.03         | 1.04    | 1.04        | 1.04         | 1.04        | 1.04                     | 10/92          |

| XILINX PACKAC          | GES .               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>一点一个批社区</b> 社      |              |         |             |              |             |                          |                |

| Mentor 8               | Standard            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-MN8-STD-xxx        | 1.00         |         |             | 1.10         | 1.10        | 1.10                     | 07/93          |

| MENTOR 8               | Extended            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-MN8-EXT-xxx        | 1.00         |         |             | 1.10         | 1.10        | 1.10                     | 07/93          |

| Mentor 7               | Standard            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-MN7-STD-xxx        | 1.00         |         |             |              | 1.10        |                          | 07/93          |

| MENTOR 7               | Extended            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-MN7-EXT-xxx        | 1.00         |         |             |              | 1.10        |                          | 07/93          |

| OrCad                  | Base                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-OR-BAS-xxx         | 1.10         | 1.20    |             |              |             |                          | 07/93          |

| OrCad                  | Standard            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-OR-STD-xxx         | 1.10         | 1.20    |             |              |             |                          | 07/93          |

| Synopsys               | Standard            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-SY-STD-xxx         | 1.01         |         |             | 1.10         | 1.10        | 1.10                     | 09/93          |

| Viewlogic              | BASE                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS-VL-BAS-xxx         | 1.10         | 1.20    |             | 1.20         |             |                          | 07/93          |