# YAMAHA" L S I

**OPL3 Low Voltage version**

#### **OVERVIEW**

YMF289B (OPL3-L) is a synthesizer chip developed specially for note PC, PCMCIA (type II) card. YMF289B is compatible with YMF262 which is de facto standard in sound card market. Special functions (power down mode, 3.3V power supply and etc.) are newly featured.

#### **■ FEATURES**

- Register-compatible with YMF262

- 1. Sound generation modes

- Two-operator mode

- Generates eighteen voices or fifteen voices plus five rhythm sounds simultaneously.

- Four-operator mode

- Generates six voices in four-operator mode plus six voices in two-operator mode, or generates six voices in four-operator mode plus three voices in two-operator mode plus five rhythm sounds simultaneously.

- 2. Eight selectable waveforms

- 3. Stereo output

- Sampling frequency is 44.1kHz.

- All registers are readable.

- Supports low power consumption mode (power down mode).

- 5V or 3.3V power supply.

- DAC interface compatible with YAC516 and YAC513.

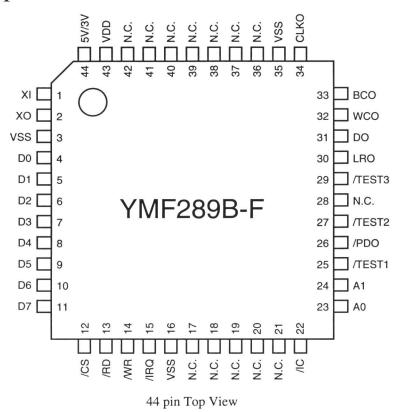

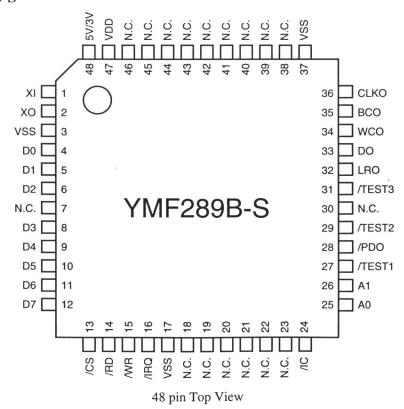

- 44-pin QFP (YMF289B-F) or 48-pin SQFP (YMF289B-S) package.

*OPL*<sup>™</sup> is a trade mark of YAMAHA Corporation which represents a full register compatibility with YAMAHA YM3812 (OPL2).

-YAMAHA CORPORATION:

YMF289B CATALOG

CATALOG No.: LSI-4MF289B2

1994.12

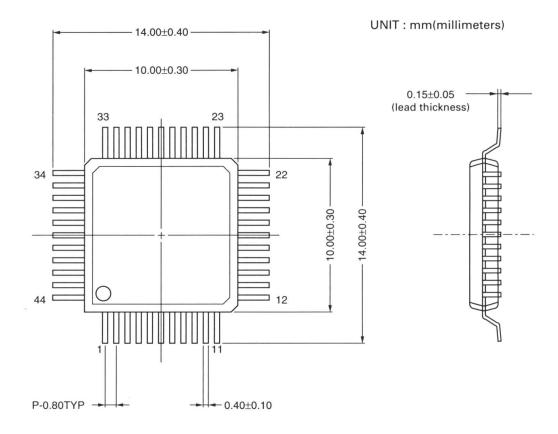

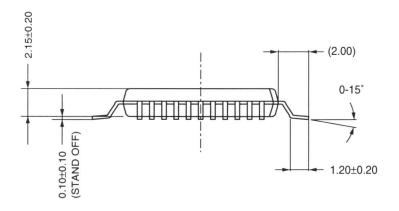

## ■ PIN OUT DIAGRAM

## • YMF289B-F

## • YMF289B-S

# **■ PIN DESCRIPTION**

| N     | 0.     | 1/0 |        | Facilities                                                           |

|-------|--------|-----|--------|----------------------------------------------------------------------|

| 44QFP | 48SQFP | I/O | Name   | Function                                                             |

| 1     | 1      | 1   | XI     | Crystal oscillator connection pin or master clock input (33.8688MHz) |

| 2     | 2      | 0   | XO     | Crystal oscillator connection pin                                    |

| 3     | 3      | -   | VSS    | Ground                                                               |

| 4     | 4      | I/O | D0     | CPU interface: data 0                                                |

| 5     | 5      | I/O | D1     | CPU interface: data 1                                                |

| 6     | 6      | I/O | D2     | CPU interface: data 2                                                |

| 7     | 8      | I/O | D3     | CPU interface: data 3                                                |

| 8     | 9      | I/O | D4     | CPU interface: data 4                                                |

| 9     | 10     | I/O | D5     | CPU interface: data 5                                                |

| 10    | 11     | I/O | D6     | CPU interface: data 6                                                |

| 11    | 12     | I/O | D7     | CPU interface: data 7                                                |

| 12    | 13     | 1   | /CS    | CPU interface: chip select                                           |

| 13    | 14     | 1   | /RD    | CPU interface: read enable                                           |

| 14    | 15     | 1   | /WR    | CPU interface: write enable                                          |

| 15    | 16     | OD  | /IRQ   | CPU interface: interrupt signal                                      |

| 16    | 17     | -   | VSS    | Ground                                                               |

| 22    | 24     | l+  | /IC    | Initial clear input                                                  |

| 23    | 25     | 1   | A0     | CPU interface: address 0                                             |

| 24    | 26     | T   | A1     | CPU interface: address 1                                             |

| 25    | 27     | I+  | /TEST1 | LSI test pin (Normally NC)                                           |

| 26    | 28     | 0   | /PDO   | Power down mode output                                               |

| 27    | 29     | l+  | /TEST2 | LSI test pin (Normally NC)                                           |

| 29    | 31     | l+  | /TEST3 | LSI test pin (Normally NC)                                           |

| 30    | 32     | 0   | LRO    | DAC interface: L/R clock output                                      |

| 31    | 33     | 0   | DO     | DAC interface: voice data output                                     |

| 32    | 34     | 0   | WCO    | DAC interface: word clock output                                     |

| 33    | 35     | 0   | всо    | DAC interface: bit clock output                                      |

| 34    | 36     | 0   | CLKO   | Clock output pin (16.9344MHz)                                        |

| 35    | 37     | *   | VSS    | Ground                                                               |

| 43    | 47     | -   | VDD    | +5V (or +3.3V) power supply                                          |

| 44    | 48     | 1   | 5V/3V  | 5V, 3.3V operation select (H: 5V, L:3.3V)                            |

All pins other than the above are N.C. Normally do not connect them.

Note) I+: Input pin with pull up resistor

OD: Open drain output pin

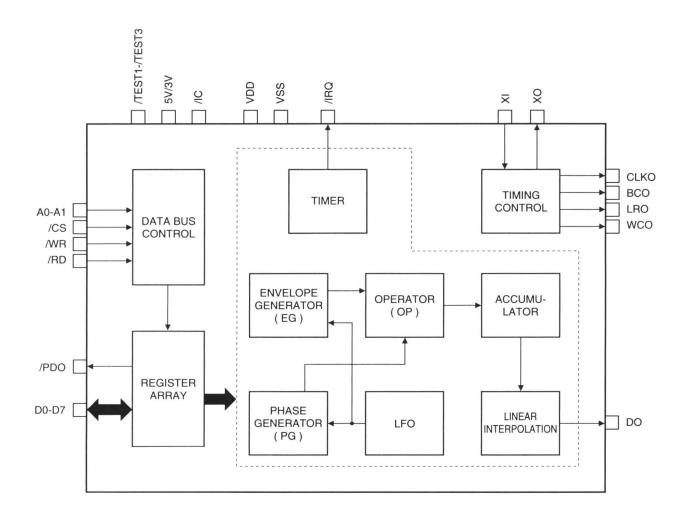

## ■ BLOCK DIAGRAM

# **■ FUNCTION OVERVIEW**

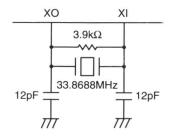

## 1. Master clock

The YMF289B synthesized frequency and envelope rate depend on the clock supplied from the XI pin. The YMF289B has a built-in self-oscillation circuit. Therefore, connect a 33.8688MHz (third overtone oscillation) crystal oscillator to the XI and XO pins as shown below.

#### 2. CPU interface

The FM performance, sound generation, and other functions of the YMF289B are controlled by writing data to the data registers described in "3. Register map". Data is written to and read from the registers over the data bus (D0 to D7). The data bus is controlled by address signals A0 and A1 and control signals /CS, /WR, and /RD. These signals set the data bus mode as shown below.

| /CS | /RD | /WR | A1  | A0 | Mode               |

|-----|-----|-----|-----|----|--------------------|

| Н   | X   | X   | X   | X  | Interactive mode   |

| L   | L   | H   | L   | L  | Status read mode   |

| L   | H   | L   | L/H | L  | Address write mode |

| L   | Н   | L   | X   | Н  | Data write mode    |

| L   | L   | H   | X   | Н  | Data read mode     |

X: Don't care

#### 2-1 Inactive Mode

When /CS is 'H', data bus (D0-D7) becomes high-impedance.

#### 2-2 Status Read Mode

The Status Register can be read from D0-D7 in this mode.

#### 2-3 Address Write Mode

In this mode data presented at D0-D7 will be latched as the register to be accessed. The A1 signal determines which register array is accessed: when A1 is 'L', register array 0 is selected: when A1 is 'H', register array 1 is selected.

<Caution>

Do not attempt to use the latched address until 56 (master clock) cycles have elapsed.

#### 2-4 Data Write Mode

Data written to D0-D7 will go to the previously specified register. Successive writes to the same register can be made without refreshing the address.

<Caution>

Do not attempt to change the latched address or write new data until 56 (master clock) cycles have elapsed.

#### 2-5 Data Read Mode

The previously specified register can be read from D0-D7 in this mode.

## 3. Register map

The YMF289B registers are made up of data registers, which control the LSI itself, and status registers, which show the status of the LSI.

Most of the data registers are compatible with the YMF262(OPL3). The YMF289B can read all the registers, even those not supported by the YMF262. However, the registers cannot be read in the power down mode. Initialization (/IC="L") clears all the registers.

#### 3-1 Data registers

| ADDRESS |         | REGISTER ARRAY 0 (A1='L') |          |             |        |     |      |       |                                                             | P              | EGIST | ER AR  | RAY 1    | (A1='H | l')  |          |

|---------|---------|---------------------------|----------|-------------|--------|-----|------|-------|-------------------------------------------------------------|----------------|-------|--------|----------|--------|------|----------|

| (HEX)   | D7      | D6                        | D5       | D4          | D3     | D2  | D1   | D0    | D7                                                          | D6             | D5    | D4     | D3       | D2     | D1   | D0       |

| 00H~01H |         |                           | LSI TEST |             |        |     |      |       | LSITEST                                                     |                |       |        |          |        |      |          |

| 02H     |         |                           |          | TIM         | ER 1   |     |      |       |                                                             |                |       |        |          |        |      | g jerkur |

| 03H     | TIMER 2 |                           |          |             |        |     |      |       |                                                             |                |       |        | 12 J. H. |        |      |          |

| 04H     | RST     | MT1                       | MT2      | MT2 ST2 ST1 |        |     |      |       |                                                             | CO             | NNEC  | TION S | EL       | 1      |      |          |

| 05H     |         | 30(2)                     |          |             |        |     |      |       |                                                             |                |       |        | NEW3     | *      | NEW  |          |

| 08H     | -7      | NTS                       |          |             |        |     |      |       | 1000<br>1000<br>1000<br>1000<br>1000<br>1000<br>1000<br>100 |                |       |        |          | CLR    | PD1  | PD0      |

| 20H~35H | AM      | VIB                       | EGT      | KSR         |        | MU  | JLT  |       | AM                                                          | VIB            | EGT   | KSR    |          | MU     | ILT  |          |

|         |         |                           |          |             | 3      | 2   | 1    | 0     |                                                             |                |       |        | 3        | 2      | 1    | 0        |

| 40H~55H | KS      | SL                        |          |             | Т      | L   |      |       | KSL                                                         |                |       | Т      | TL       |        |      |          |

|         | 1       | 0                         | 5        | 4           | 3      | 2   | 1    | 0     | 1                                                           | 0              | 5     | 4      | 3        | 2      | 1    | 0        |

| 60H~75H |         | Α                         | R        |             |        | D   | R    |       | AR                                                          |                |       | DR     |          |        |      |          |

|         | 3       | 2                         | 1        | 0           | 3      | _ 2 | _ 1  | 0     | 3                                                           | 2              | 1 1   | 0      | 3        | 2      | 1    | 0        |

| 80H~95H |         | S                         | SL.      |             |        | R   | R    |       | SL                                                          |                |       |        |          | RR     |      |          |

|         | 3       | 2                         | 1        | 0           | 3      | 2   | 1    | 0     | 3                                                           | 2              | 1     | 0      | 3        | 2      | 1    | 0        |

| A0H~A8H |         |                           | F        | -NUM        | BER (L | _)  |      |       | F-NUMBER (L)                                                |                |       |        |          |        |      |          |

|         | F7      | F6                        | F5       | F4          | F3     | F2  | F1   | F0    | F7                                                          | F6             | F5    | F4     | F3       | F2     | F1   | F0       |

| B0H~B8H |         |                           | KON      |             | BLOCK  | (   | F-NU | M (H) |                                                             |                | KON   |        | BLOCK    | <      | F-NU | M (H)    |

|         |         |                           |          | B2          | B1     | B0  | F9   | F8    |                                                             | 145            |       | B2     | B1       | B0     | F9   | F8       |

| BDH     | DAM     | DVB                       | RHY      | BD          | SD     | ТОМ | TC   | HH    |                                                             | and the second |       |        |          |        |      |          |

| C0H~C8H | *       | *                         | CHR      | CHL         |        | FB  |      | CNT   | *                                                           | *              | CHR   | CHL    |          | FB     |      | CNT      |

|         |         |                           |          |             | FB2    | FB1 | FB0  |       |                                                             |                |       |        | FB2      | FB1    | FB0  |          |

| E0H~F5H |         |                           |          |             |        |     | WS   |       |                                                             |                |       |        |          |        | WS   |          |

|         |         |                           |          |             |        | W2  | W1   | W0    |                                                             |                |       |        |          | W2     | W1   | _ Wo     |

#### Notes)

- 1. The register map is basically the same as that of the YMF262 except for the following:

- a) The NEW3, PD0, PD1, and CLR bits of registers 05H and 08H of REGISTER ARRAY 1 are newly defined.

- b) Bits D6 and D7 of registers C0 to C8H of register arrays 0 and 1 are not supported .

- 2. The LSI TEST registers are used for factory testing. Always set them to "0" during normal operation.

- 3. not used by the YMF289B may be used to expand the functions. Always set them to "0".

- 4. Bits indicated by ★ can be read, but are not supported functionally.

#### 3.2 Status register

| ΑI | DDRESS | STATUS REGISTER |     |     |    |    |      |    |      |  |  |  |

|----|--------|-----------------|-----|-----|----|----|------|----|------|--|--|--|

|    | (HEX)  | D7              | D6  | D5  | D4 | D3 | D2   | D1 | D0   |  |  |  |

|    | xx     | IRQ             | FT1 | FT2 |    |    | BUSY |    | BUSY |  |  |  |

#### YMF289B identification

When the status is read after initialization, the YM3812(OPL2) outputs 06H and the YMF262 outputs 00H.

The YMF289B outputs the same value as the YMF262, but since it can read all the data registers, it can be discriminated from the YMF262 by whether or not all the data registers can be read.

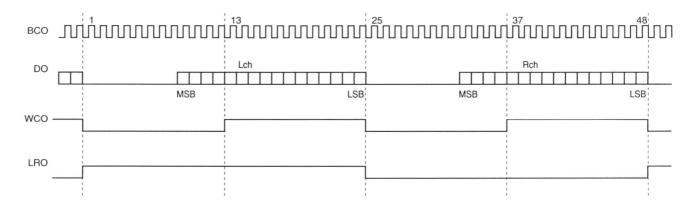

#### 4. DAC interface

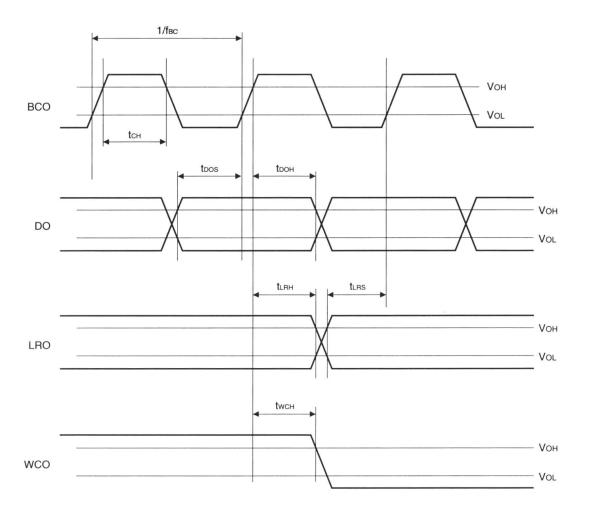

The YMF289B outputs the voice data as digital data. Therefore, an external D/A converter is necessary. The digital data is output MSB-first from the DO pin as 2's complement data. The sampling frequency is 44.1kHz. The relationship between the DO pin digital data and the control signals (BCO, WCO, LRO) is shown below.

BCO: 48fs duty 50% WCO: 2fs duty 50% LRO: fs duty 50%

## 5. Additional functions

The YMF289B has the following additional functions, as compared to the YMF262.

## 5-1 NEW3 bit

This bit enables the newly defined bits (PD0 bit, PD1 bit, CLR bit, BUSY flag). When this bit is "1", the bits above are enabled.

#### 5-2 PD0, PD1 bits

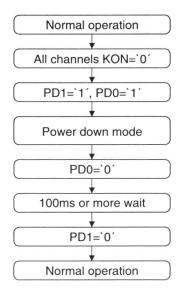

These bits set the power down mode. Always set and reset the power down mode in the following order:

#### Power down mode

In the power down mode, clock oscillation is completely stopped and there is much lower power consumption than during normal operation. At this time, synthesizing stops, but the registers retain their contents before the YMF289B enters the power down mode.

In the power down mode, all the DAC interface pins (CLKO, LRO, WCO, BCO, DO) are fixed at the "L" level and the /IRQ pin retains its state before the YMF289B enters the power down mode. Be sure to fix the input pins (including D0 to D7) at the "H" or "L" level.

#### <Caution>

If KON="1" when the machine returns from the power down mode, unexpected sound may be generated. Therefore, before switching to the power down mode, set all channels to <u>KON="0"</u>. As for the timer, when the machine returns from the power down mode, RST becomes "1" and the counter is reset.

#### 5-3 CLR bit

This bit clears all the data register bits except NEW and NEW3. CLR="1" clears the data registers and CLR="0" resets the data registers. The time required to clear the data registers is  $90\mu s$  (3000 cycles @ 33.8688NHz).

## 5-4 BUSY flag

This flag inhibits register access. It remains "1" until the data bus data is latched as an address, or is verified as register data.

#### 5-5 /PDO pin

This bit becomes "L" when the YMF289B shifted to the power down mode. When the YMF289B returns to normal operation, this bit becomes "H". Use this bit to control a YAC516 or other YMF289B peripheral LSI.

## ■ ELECTRICAL CHARACTERISTICS

## 1. Absolute maximum ratings

| Item                  | Symbol          | Rated value  | Unit |

|-----------------------|-----------------|--------------|------|

| Power supply voltage  | V <sub>DD</sub> | -0.3~7.0     | V    |

| Input voltage         | Vin             | -0.3~VDD+0.5 | V    |

| Operation temperature | Тор             | 0~70         | °C   |

| Storage temperature   | Тѕтс            | -50~125      | °C   |

## 2. Recommended operating conditions

| Item                  | Symbol          | Condition | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------|-----------|------|------|------|------|

| Power supply voltage  | V <sub>DD</sub> | 5V/3V="H" | 4.75 | 5.00 | 5.25 | V    |

|                       | VDD             | 5V/3V="L" | 3.00 | 3.30 | 3.60 | V    |

| Operating temperature | Тор             |           | 0    | 25   | 70   | °C   |

#### 3. DC characteristics

\*At recommended operating conditions.

| Item                          | Symbol            | Condition                 | Min.                 | Max.               | Unit |

|-------------------------------|-------------------|---------------------------|----------------------|--------------------|------|

| Power consumption             | PD                | V <sub>DD</sub> =5.0V, *1 | -                    | 150                | mW   |

|                               |                   | V <sub>DD</sub> =3.3V, *1 | -                    | 60                 | mW   |

|                               |                   | V <sub>DD</sub> =5.0V, *2 | -                    | 300                | μW   |

|                               |                   | V <sub>DD</sub> =3.3V, *2 | -                    | 200                | μW   |

| Input high level voltage (1)  | V <sub>I</sub> H1 | *3                        | 2.0                  | -                  | ٧    |

| Input low level voltage (1)   | VIL1              | *3                        | -                    | 0.8                | V    |

| Input high level voltage (2)  | V <sub>IH2</sub>  | *4                        | 0.7VDD               | -                  | V    |

| Input low level voltage (2)   | VIL2              | *4                        | -                    | 0.2V <sub>DD</sub> | V    |

| Input leakage current         | Lu                | *5                        | -10                  | 10                 | μА   |

| Input capacitance             | Cı                |                           | -                    | 10                 | pF   |

| Output high level voltage (1) | Vон1              | Іон=-80 [μΑ], *6          | V <sub>DD</sub> -1.0 | -                  | V    |

| Output low level voltage (1)  | V <sub>OL1</sub>  | loL=2 [mA], *6            | -                    | Vss+0.4            | V    |

| Output high level voltage (2) | V <sub>OH2</sub>  | Іон=-80 [μΑ], *7          | 2.4                  | -                  | ٧    |

| Output low level voltage (2)  | Vol2              | loL=2 [mA], *7            | -                    | 0.4                | V    |

| Output low level voltage (3)  | Vol3              | loL=2 [mA], *8            | -                    | 0.4                | V    |

| Output capacitance            | Со                |                           | -                    | 10                 | pF   |

| Pull-up resistance            | Rυ                | *9                        | 50                   | 400                | kΩ   |

Notes) \*1: fm1=33.8688MHz, normal operation

<sup>\*2:</sup> Power down mode

<sup>\*3:</sup> Applies to /TEST1 to TEST3, /IC, /WR/, /RD, /CS, A0 to A1, and D0 to D7.

<sup>\*4:</sup> Applies to XI and 5V/3V.

<sup>\*5:</sup> VIN=0-5V. Applies to /WR, /RD, /CS, A0 to A1, D0 to D7, XI, and 5V/3V.

<sup>\*6: 5</sup>V/3V="H". Applies to D0 to D7 (at output), /PDO, CLKO, BCO, LRO, WCO, and DO.

<sup>\*7: 5</sup>V/3V="L". Applies to D0 to D7 (at output), /PDO, CLKO, BCO, LRO, WCO, and DO.

<sup>\*8:</sup> Applies to /IRQ pin.

<sup>\*9:</sup> Applies to /IC, and /TEST1 to /TEST3.

# 4. AC characteristics

\*At recommended operating conditions.

| Item                          | Symbol          | Fig.       | Min.     | Тур.       | Max.           | Unit |

|-------------------------------|-----------------|------------|----------|------------|----------------|------|

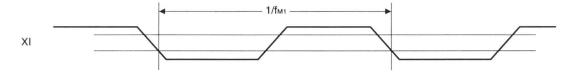

| Master clock frequency        | fмı             | Fig. 1     | -        | 33.8688    | -              | MHz  |

| Duty 1                        | D1              |            | 40       | 50         | 60             | %    |

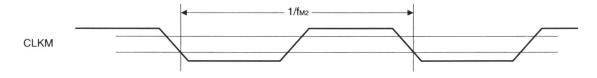

| Output master clock frequency | f <sub>M2</sub> | Fig. 2     | -        | 16.9344    | -              | MHz  |

| Duty 2                        | D2              |            |          | 50         | -              | %    |

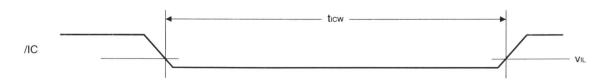

| Reset pulse width             | ticw            | Fig. 3     | 3000/fм1 | -          | -              | s    |

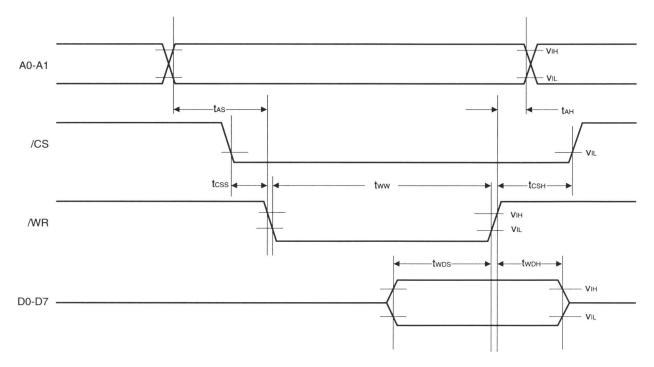

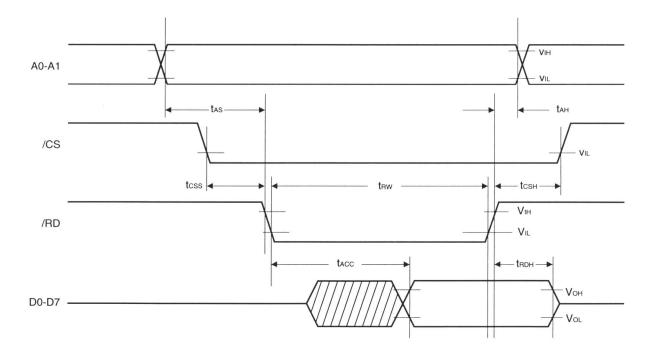

| Address setup time            | tas             | Figs. 4, 5 | 30       | -          | i <del>a</del> | ns   |

| Address hold time             | tан             | Figs. 4, 5 | 10       | -          | -              | ns   |

| Chip select setup time        | tcss            | Figs. 4, 5 | 5        | -          | -              | ns   |

| Chip select hold time         | tсsн            | Figs. 4, 5 | 10       | -          | -              | ns   |

| Write pulse width             | tww             | Fig. 4     | 50       | -          | -              | ns   |

| Write data setup time         | twos            | Fig. 4     | 10       | -          | -              | ns   |

| Write data hold time          | twoн            | Fig. 4     | 10       | :          | -              | ns   |

| Read pulse width              | trw             | Fig. 5     | 80       | -          | -              | ns   |

| Read data access time         | tacc            | Fig. 5     | ,=:      | -          | 60             | ns   |

| Read data hold time           | tпрн            | Fig. 5     | 10       | -          | -              | ns   |

| Bit clock frequency           | fвc             | Fig. 6     | -        | 48fs       | -              | MHz  |

| Bit clock high level time     | tсн             | Fig. 6     | 110      | 1-1        | -              | ns   |

| Data out setup time           | toos            | Fig. 6     | 100      | -          | -              | ns   |

| Data out hold time            | tрон            | Fig. 6     | 280      | -          | <u>:-</u>      | ns   |

| LR clock setup time           | tlrs            | Fig. 6     | 100      | -          | -              | ns   |

| LR clock hold time            | tlrh            | Fig. 6     | 280      | -          | -              | ns   |

| Word clock hold time          | twcн            | Fig. 6     | 280      | ? <b>-</b> | -              | ns   |

Fig. 1 Input Clock timing

Fig. 2 Output Clock Timing

Fig. 3 Setup Pulse Width

Fig. 4 CPU Write Timing

Fig. 5 CPU Read Timing

Fig. 6 DAC Interface Timing

## **■ EXTERNAL DIMENSIONS**

• YMF289B-F (44QFP)

## IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.