# YMZ705 ssgs

SSG & ADPCM Playback with Sequencer

### OVERVIEW

YMZ705(SSGS) is an automatic play LSI with synthesizer equivalent to two YM2149(SSG) and ADPCM playback function. By two internal sequencers, YMZ705 plays two different music simultaneously with up to six square wave plus two noise plus eight ADPCM voices at a time.

All the parameters for the synthesizer can be controlled directly by CPU even when the sequencers are in operation.

### **FEATURES**

- ●YMZ705 includes two systems of SSG synthesizer, each of which generates three square wave plus one noise so that it can generate up to six square wave plus two noise plus eight ADPCM voices simultaneously.

- The voice data that is made by digital mixing is outputted as analog signals from the built-in 12-bit floating D/A converter.

- With its sequencer function, YMZ705 is able to playback two songs at the same time from up to 64 songs stored in the external memory.

- With its 4-bit ADPCM playback function, YMZ705 is able to playback maximum eight voices at the same time from voice data of up to 64 voices stored in the external memory.

- A sampling frequency can be selected from 32kHz, 16kHz, 8kHz and 4kHz for each channel.

- An external memory up to 8 Mbytes can be connected to YMZ705 for storing music data and ADPCM data.

- For both SSG and ADPCM, the data can be controlled directly by CPU.

- For SSG, pan-pot can be set for six voices independently. For ADPCM, it can be set for eight voice sindependently.

- •+5V single power supply, silicon gate CMOS process.

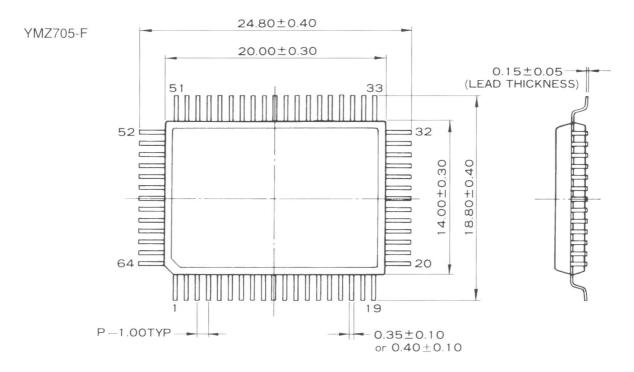

- ●64 pin plastic QFP(YMZ705-F).

YAMAHA CORPORATION

YMZ705 CATALOG CATALOG No. : -LSI4MZ705A2

1996. 10

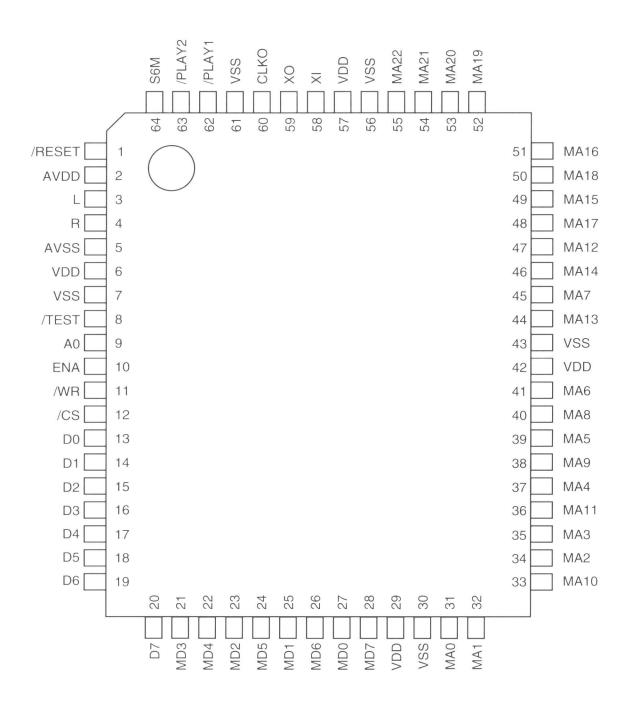

# PIN OUT DIAGRAM

YMZ705-F

<64pin QFP Top View>

# **■**PIN FUNCTION

| No. | Name   | I/O | Function                                  |

|-----|--------|-----|-------------------------------------------|

| 1   | /RESET | I+  | Reset input                               |

| 2   | AVDD   |     | +5V power supply (Analog)                 |

| 3   | L      | OA  | Analog output (Left channel)              |

| 4   | R      | OA  | Analog output (Right channel)             |

| 5   | AVSS   | -   | Ground (Analog)                           |

| 6   | VDD    | _   | +5V power supply                          |

| 7   | VSS    |     | Ground                                    |

| 8   | /TEST  | I+  | LSI test pin                              |

| 9   | AO     | I   | CPU interface Address select signal input |

| 10  | ENA    | I   | CPU interface Enable signal input         |

| 11  | /WR    | I   | CPU interface Write enable signal input   |

| 12  | /CS    | I   | CPU interface Chip select signal input    |

| 13  | D0     | I   | CPU interface Data bus                    |

| 14  | D1     | I   | Data bus                                  |

| 15  | D2     | I   | Data bus                                  |

| 16  | D3     | I   | Data bus                                  |

| 17  | D4     | I   | Data bus                                  |

| 18  | D5     | I   | Data bus                                  |

| 19  | D6     | I   | Data bus                                  |

| 20  | D7     | I,  | Data bus                                  |

| 21  | MD3    | I+  | External memory interface Data bus        |

| 22  | MD4    | I+  | Data bus                                  |

| 23  | MD2    | I+  | Data bus                                  |

| 24  | MD5    | I+  | Data bus                                  |

| 25  | MD1    | I+  | Data bus                                  |

| 26  | MD6    | I+  | Data bus                                  |

| 27  | MD0    | I+  | Data bus                                  |

| 28  | MD7    | I+  | Data bus                                  |

| 29  | VDD    |     | +5V power supply                          |

| 30  | VSS    |     | Ground                                    |

| 31  | MA0    | О   | External memory interface Address bus     |

| 32  | MA1    | 0   | Address bus                               |

| 33  | MA10   | O   | Address bus                               |

| 34  | MA2    | 0   | Address bus                               |

| 35  | MA3    | О   | Address bus                               |

| 36  | MA11   | 0   | Address bus                               |

| 37  | MA4    | O   | Address bus                               |

| 38  | MA9    | 0   | Address bus                               |

| 39  | MA5    | O   | Address bus                               |

| 40  | MA8    | О   | Address bus                               |

| 41  | MA6    | O   | Address bus                               |

| No. | Name   | I/O | Function                                                                         |

|-----|--------|-----|----------------------------------------------------------------------------------|

| 42  | VDD    | _   | +5V power supply                                                                 |

| 43  | VSS    | _   | Ground                                                                           |

| 44  | MA13   | О   | External memory interface Address bus                                            |

| 45  | MA7    | О   | Address bus                                                                      |

| 46  | MA14   | О   | Address bus                                                                      |

| 47  | MA12   | O   | Address bus                                                                      |

| 48  | MA17   | О   | Address bus                                                                      |

| 49  | MA15   | О   | Address bus                                                                      |

| 50  | MA18   | О   | Address bus                                                                      |

| 51  | MA16   | О   | Address bus                                                                      |

| 52  | MA19   | O   | Address bus                                                                      |

| 53  | MA20   | O   | Address bus                                                                      |

| 54  | MA21   | О   | Address bus                                                                      |

| 55  | MA22   | О   | Address bus                                                                      |

| 56  | VSS    |     | Ground                                                                           |

| 57  | VDD    | _   | +5V power supply                                                                 |

| 58  | XI     | I   | Crystal oscillator connection or external clock input pin (4.096MHz or 6.144MHz) |

| 59  | XO     | О   | Crystal oscillator connection pin                                                |

| 60  | CLKO   | О   | Master clock output                                                              |

| 61  | VSS    |     | Ground                                                                           |

| 62  | /PLAY1 | О   | Sequencer 1 'Play in progress' flag                                              |

| 63  | /PLAY2 | О   | Sequencer 2 'Play in progress' flag                                              |

| 64  | S6M    | I+  | Master clock frequency select signal ('H'=6.144MHz, 'L'=4.096MHz)                |

Note:

I+: Pin with built-in pull-up resistor

OA: Analog output pin

/TEST: To be open

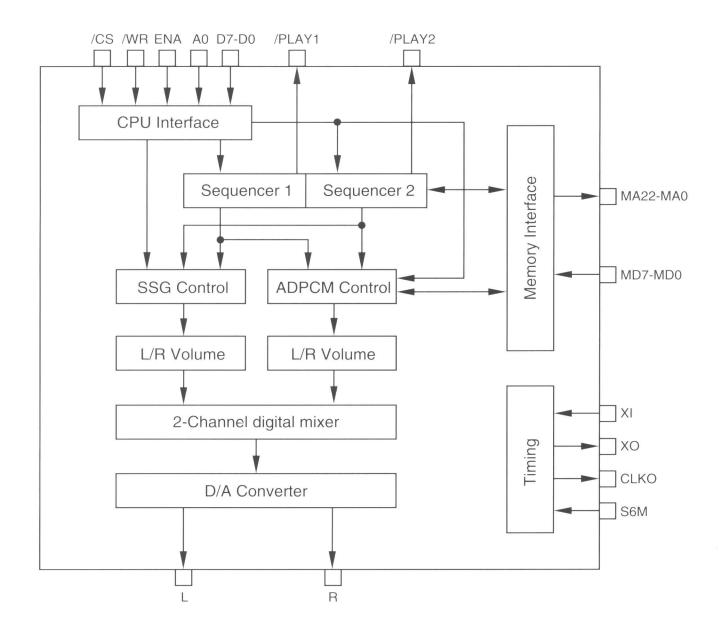

# **■**BLOCK DIAGRAM

#### **FUNCTIONS**

### 1. Clock signal oscillation XI, XO, CLKO

XI and XO pins are used to form a crystal oscillation circuit. The circuit generates either 4.096MHz or 6.144MHz.

External clock signal can be inputted through XI pin. At this time, XO pin must be open.

CLKO pin outputs the same frequency.

#### 2. Clock signal selection S6M

Set this pin to 'L' when the clock frequency is 4.096MHz, or to 'H' when 6.144MHz.

### 3. CPU interface /CS, /WR, ENA, A0, D7 to D0, /PLAY1, /PLAY2

Pins D7 to D0 accept command data from CPU.

Each of /CS, /WR, ENA and A0 controls writing of command data.

The mode varies according to the clock frequency selected with S6M pin.

| S6M | /CS | /WR | ENA | A0 | Function           |

|-----|-----|-----|-----|----|--------------------|

| L   | L   | L   | Н   | L  | Address write mode |

| L   | L   | L   | Н   | Н  | Data write mode    |

| L   | *   | *   | L   | *  | Inactive mode      |

| Н   | L   | L   | *   | L  | Address write mode |

| Н   | L   | L   | *   | Н  | Data write mode    |

| *   | Н   | *   | *   | *  | Inactive mode      |

| *   | *   | Н   | *   | *  | Inactive mode      |

<sup>\*:</sup> Don't care

/PLAY1 and /PLAY2 are 'L' when the sequencer 1 and sequencer 2 are in play respectively.

#### 4. External memory interface MA22 to MA0, MD7 to MD0

When reading data from external memory, address is outputted from MA22 to MA0 pins and data is inputted through MD7 to MD0 pins. MD7 to MD0 pins have built-in pull-up resisters.

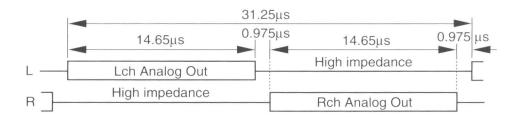

#### 5. DAC output L, R

Output of SSG synthesizer and playback voices of ADPCM are mixed at the digital mixer. The mixed digital signals are converted to analog signals with 12-bit 2-channel time sharing system, and then distributed to the L and R channels by analog switch.

#### 6. System reset /RESET

YMZ705 requires the system reset at turn on. When the pin is 'L', internal registers to "0" and generation of voice are stopped compulsorily.

# ■SSG synthesis control register map

| ADRS | Function             | D7 | D6 | D5    | D4           | D3          | D2           | D1         | D0   |

|------|----------------------|----|----|-------|--------------|-------------|--------------|------------|------|

| \$00 | Channel-1A Frequency |    |    | 8-bit | fine tone    | adjustment  |              |            |      |

| \$01 |                      |    |    |       |              | 4-b         | oit rough to | ne adjustr | ment |

| \$02 | Channel-1B Frequency |    |    | 8-bit | fine tone    | adjustment  |              |            |      |

| \$03 |                      |    |    |       |              | 4-b         | oit rough to | ne adjustr | nent |

| \$04 | Channel-1C Frequency |    |    | 8-bit | fine tone    | adjustment  |              |            |      |

| \$05 |                      |    |    |       |              | 4-b         | oit rough to | ne adjustr | nent |

| \$06 | Noise-1 Frequency    |    |    |       |              | 5-b         | oit Noise fr | equency    |      |

| \$07 | Mixer-1 Setting      |    |    |       | Noise        |             |              | Tone       |      |

|      |                      |    |    | С     | В            | А           | С            | В          | А    |

| \$08 | Channel-1A Volume    |    |    |       | М            | L3          | L2           | L1         | L()  |

| \$09 | Channel-1B Volume    |    |    |       | M            | L3          | L2           | L1         | LO   |

| \$0A | Channel-1C Volume    |    |    | ****  | М            | L3          | L2           | L1         | LO   |

| \$0B | Envelope-1 Frequency |    |    |       | 8-bit fine a | adjustment  |              |            |      |

| \$0C |                      |    |    |       | 8-bit rough  | n adjustmen | ıt           |            |      |

| \$0D | Envelope-1 Shape     |    |    |       | -            | CONT        | ATT          | ALT        | HOLD |

| \$10 | Channel-1A Pan-pot   |    |    |       |              | Р3          | P2           | P1         | P0   |

| \$11 | Channel-1B Pan-pot   |    |    |       |              | Р3          | P2           | P1         | P0   |

| \$12 | Channel-1C Pan-pot   |    |    |       |              | Р3          | P2           | PI         | P0   |

| \$20 | Channel-2A Frequency |    |    | 8-    | -bit fine to | ne adjustme | ent          |            |      |

| \$21 |                      |    |    |       |              | 4-b         | oit rough to | ne adjustn | nent |

| \$22 | Channel-2B Frequency |    |    | 8-    | bit fine to  | ne adjustme |              | · ·        |      |

| \$23 |                      |    |    |       |              | 4-b         | oit rough to | ne adjustn | nent |

| \$24 | Channel-2C Frequency |    |    | 8-    | -bit fine to | ne adjustme | ent          | 80)        |      |

| \$25 |                      |    |    |       |              | 4-b         | it rough to  | ne adjustn | nent |

| \$26 | Noise-2 Frequency    |    |    |       |              |             | oit Noise fr |            |      |

| \$27 | Mixer-2 Setting      |    |    |       | Noise        |             |              | Tone       |      |

|      |                      |    |    | С     | В            | А           | C            | В          | А    |

| \$28 | Channel-2A Pan-pot   |    |    |       | M            | L3          | L2           | L1         | LO   |

| \$29 | Channel-2B Pan-pot   |    |    |       | М            | L3          | L2           | L1         | LO   |

| \$2A | Channel-2C Pan-pot   |    |    |       | M            | L3          | L2           | L1         | LO   |

| \$2B | Envelope-2 Frequency |    |    |       | 8-bit fine ε | ıdjustment  |              |            |      |

| \$2C |                      |    |    |       |              | n adjustmen | t            |            |      |

| \$2D | Envelope-2 Shape     |    |    |       |              | CONT        | ATT          | ALT        | HOLD |

| \$30 | Channel-2A Frequency |    |    |       |              | Р3          | P2           | P1         | P0   |

| \$31 | Channel-2B Frequency |    |    |       |              | P3          | P2           | P1         | P0   |

| \$32 | Channel-2C Frequency |    |    |       |              | P3          | P2           | P1         | P()  |

| Note: | Contents of adda | ress \$00 to \$ | 50D and \$20 | to 2D ar | e register | compatible | with those of | YM2149(SSG). |

|-------|------------------|-----------------|--------------|----------|------------|------------|---------------|--------------|

|       | is don't a       | 0.00            |              |          |            |            |               |              |

7

# ■ADPCM control register map

| ADRS | Function                    | D7   | D6     | D5 | D4 | D3      | D2         | D1  | D0   |

|------|-----------------------------|------|--------|----|----|---------|------------|-----|------|

| \$40 | Channel-1 Voice designation | Samp | ling F |    |    | ADPCM V | oice numb  | er  |      |

|      | Sampling frequency          | S1   | S0     | N5 | N4 | N3      | N2         | N1  | N0   |

| \$41 | Channel-1 Volume            |      |        |    |    | L3      | L2         | L1  | LO   |

| \$42 | Channel-1 Pan-pot           |      |        |    |    | P2      | P1         | P0  |      |

| \$43 | Channel-1 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

| \$50 | Channel-2 Voice designation | Samp | ling F |    |    | ADPCM V | oice numb  | er  |      |

|      | Sampling frequency          | S1   | S0     | N5 | N4 | N3      | N2         | N1  | N0   |

| \$51 | Channel-2 Volume            |      |        |    |    | L3      | L2         | L1  | L0   |

| \$52 | Channel-2 Pan pot           |      |        |    |    | Р3      | P2         | P1  | P()  |

| \$53 | Channel-2 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

| \$60 | Channel-3 Voice designation | Samp | ling F |    | 1  | ADPCM V | oice numb  | er  | •    |

|      | Sampling frequency          | S1   | S0     | N5 | N4 | N3      | N2         | N1  | N0   |

| \$61 | Channel-3 Volume            |      |        |    |    | L3      | L2         | L1  | LO   |

| \$62 | Channel-3 Pan-pot           |      |        |    |    | Р3      | P2         | P1  | P0   |

| \$63 | Channel-3 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

| \$70 | Channel-4 Voice designation | Samp | ling F |    | 1  | ADPCM V | oice numb  | er  |      |

|      | Sampling frequency          | S1   | S0     | N5 | N4 | N3      | N2         | N1  | N0   |

| \$71 | Channel-4 Volume            |      |        |    |    | L3      | L2         | L1  | LO   |

| \$72 | Channel-4 Pan-pot           |      |        |    |    | Р3      | P2         | P1  | P0   |

| \$73 | Channel-4 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

| \$80 | Channel-5 Voice designation | Samp | ling F |    |    | ADPCM V | oice numbe | er  |      |

|      | Sampling frequency          | S1   | S0     | N5 | N4 | N3      | N2         | N1  | N0   |

| \$81 | Channel-5 Volume            |      |        |    |    | L3      | L2         | Ll  | LO   |

| \$82 | Channel-5 Pan-pot           |      |        |    |    | Р3      | P2         | P1  | P0   |

| \$83 | Channel-5 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

| \$90 | Channel-6 Voice designation | Samp | ling F |    | 1  | ADPCM V | oice numbe | er  |      |

|      | Sampling frequency          | S1   | S()    | N5 | N4 | N3      | N2         | NI  | N0   |

| \$91 | Channel-6 Volume            |      |        |    |    | L3      | L2         | Ll  | L0   |

| \$92 | Channel-6 Pan-pot           |      |        |    |    | Р3      | P2         | P1  | P0   |

| \$93 | Channel-6 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

| \$A0 | Channel-7 Voice designation | Samp | ling F |    | I  | ADPCM V | oice numbe | er  |      |

|      | Sampling frequency          | S1   | SO     | N5 | N4 | N3      | N2         | N1  | N0   |

| \$A1 | Channel-7 Volume            |      |        |    |    | L3      | L2         | LI  | L0   |

| \$A2 | Channel-7 Pan-pot           |      |        |    |    | Р3      | P2         | P1  | P()  |

| \$A3 | Channel-7 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

| \$B0 | Channel-8 Voice designation | Samp | ling F |    | 1  | ADPCM V | oice numbe | er  |      |

|      | Sampling frequency          | S1   | SO     | N5 | N4 | N3      | N2         | NI  | NO   |

| \$B1 | Channel-8 Volume            |      |        |    |    | L3      | L2         | L1  | LO   |

| \$B2 | Channel-8 Pan-pot           |      |        |    |    | P3      | P2         | P1  | P0   |

| \$B3 | Channel-8 KEY ON, LOOP      |      |        |    |    |         |            | KON | LOOP |

Note: is don't care.

# ■Sequencer and mix level control register map

| ADRS | Function                        | D7   | D6  | D5  | D4        | D3          | D2          | D1         | D0  |

|------|---------------------------------|------|-----|-----|-----------|-------------|-------------|------------|-----|

| \$F0 | Sequencer-1                     |      |     |     |           | Music       | number      |            |     |

|      | Music designation, PLAY, REPEAT | PLAY | REP | PD5 | PD4       | PD3         | PD2         | PD1        | PD0 |

| \$F1 | Sequencer-1 Tempo               |      |     |     | (         | b-bit tempo | adjustmer   | nt         |     |

| \$F2 | Sequencer-2                     |      |     |     |           | Music       | number      |            |     |

|      | Music designation, PLAY, REPEAT | PLAY | REP | PD5 | PD4       | PD3         | PD2         | PD1        | PD0 |

| \$F3 | Sequencer-2 Tempo               |      |     |     | (         | b-bit tempo | adjustmer   | nt         |     |

| \$F4 | Sequencer-1                     |      |     |     | ADPCM     | channel     |             |            |     |

|      | Occupation channel(ADPCM)       | 8    | 7   | 6   | 5         | 4           | 3           | 2          | 1   |

| \$F5 | Sequencer-2                     |      |     |     | ADPCM     | channel     |             |            |     |

|      | Occupation channel(ADPCM)       | 8    | 7   | 6   | 5         | 4           | 3           | 2          | 1   |

| \$F6 | Sequencer-1                     |      |     | S   | SG2 chann | el          | S           | SG1 chann  | iel |

|      | Occupation channel(SSG)         |      |     | С   | В         | А           | C           | В          | А   |

| \$F7 | Sequencer-2                     |      |     | S   | SG2 chann | el          | S           | SG1 chann  | iel |

|      | Occupation channel(SSG)         |      |     | С   | В         | А           | C           | В          | A   |

| \$F8 | SSG-ADPCM Mix level             |      |     |     |           | 4-t         | oit SSG lev | el adjustm | ent |

Note: is don't care.

# ■8M byte Play data ROM address map

| ADDRESS                | DATA(8bit)                                  |  |

|------------------------|---------------------------------------------|--|

| \$000000 ~<br>\$00003F | ADPCM Voice No.0 ~ 63 Data start address(L) |  |

| \$000040 ~<br>\$00007F | ADPCM Voice No.0 ~ 63 Data start address(M) |  |

| \$000080 ~<br>\$0000BF | ADPCM Voice No.0 ~ 63 Data start address(H) |  |

| \$0000C0 ~<br>\$0000FF | ADPCM Voice No.0 ~ 63 Data end address(L)   |  |

| \$000100 ~<br>\$00013F | ADPCM Voice No.0 ~ 63 Data end address(M)   |  |

| \$000140 ~<br>\$00017F | ADPCM Voice No.0 ~ 63 Data end address(H)   |  |

| \$000180 ~<br>\$0001BF | Music No.0 ~ 63 Data start address(L)       |  |

| \$0001C0~<br>\$0001FF  | Music No.0 ~ 63 Data start address(M)       |  |

| \$000200 \<br>\$00023F | Music No.0 ~ 63 Data start address(H)       |  |

| \$000240 \<br>\$7FFFF  | ADPCM Voice data and music data area        |  |

# **ELECTRICAL CHARACTERISTICS**

### 1. Absolute maximum ratings

| Item                          | Symbol | Rating                   | Unit                 |

|-------------------------------|--------|--------------------------|----------------------|

| Power supply voltage          | VDD    | $-0.5 \sim 7.0$          | V                    |

| Input voltage                 | Vı     | $-0.5 \sim V_{DD} + 0.5$ | V                    |

| Output voltage                | Vo     | $-0.5 \sim V_{DD} + 0.5$ | V                    |

| Operating ambient temperature | Тор    | $0 \sim 70$              | $^{\circ}\mathbb{C}$ |

| Storage temperature           | Tstg   | $-50 \sim 125$           | $^{\circ}$ C         |

# 2.Recommended operating conditions

| Item                          | Symbol | Min. | Тур.           | Max. | Unit                 |

|-------------------------------|--------|------|----------------|------|----------------------|

| Power supply voltage          | Vdd    | 4.75 | 5.0            | 5.25 | V                    |

| Operating ambient temperature | Тор    | 0    | 25             | 70   | $^{\circ}\mathbb{C}$ |

| Clock frequency               | fmclk  |      | 4.096 or 6.144 |      | MHz                  |

# 3.DC characteristics (under recommended operating conditions)

| Item                      | Symbol           | Condition                   | Min.                 | Max.    | Unit |

|---------------------------|------------------|-----------------------------|----------------------|---------|------|

| Consumed current          | Idd              | fmclk=4.096MHz              |                      | 20      | mA   |

| Input voltage H level (1) | Vihi             | XI                          | 3.5                  | VDD+0.3 | V    |

| Input voltage L level (1) | Vill             |                             | -0.3                 | 1.0     | V    |

| Input voltage H level (2) | V <sub>IH2</sub> | All input pins except XI    | 2.2                  | VDD+0.3 | V    |

| Input voltage L level (2) | VIL2             |                             | -0.3                 | 0.8     | V    |

| Output voltage H level    | Voh              | Iон=-0.1 mA                 | V <sub>DD</sub> -1.0 |         | V    |

| Output voltage L level    | Vol              | IoL=2.0mA *1                |                      | 0.4     | V    |

| Input leakage current     | Iti              | V <sub>1</sub> =0 ~ 5.0V *2 | -10                  | 10      | μΑ   |

| Pull-up resistor          | Ru               | *3                          | 30                   | 300     | kΩ   |

Note: \*1: Applied to all output pins except L, R, and XO.

# 4. Analog characteristics (under recommended operating conditions)

| Item                  | Symbol | Condition | Min. | Тур. | Max. | Unit |

|-----------------------|--------|-----------|------|------|------|------|

| Analog output voltage | Voa    | L, R *1   |      | 4.96 |      | V    |

Note\*1: AVDD=5.0V, maximum volume, no load, peak to peak.

<sup>\*2:</sup> Applied to D7 to D0 (in case of input status), A0, /WR, XI, /CS and ENA pins.

<sup>\*3:</sup> Applied to MD7 to MD0, /RESET, /TEST and S6M pins.

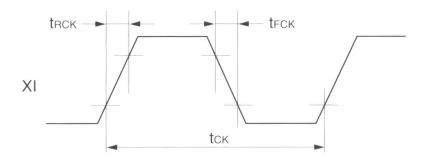

5.AC characteristics (under recommended operating conditions)

| Item                              | Symbol | Min.    | Typ.      | Max. | Unit |

|-----------------------------------|--------|---------|-----------|------|------|

| Master clock frequency (4.096MHz) | tck    |         | tvck/2 *1 |      | ns   |

| (6.144MHz)                        |        |         | tvck/3    |      | ns   |

| Input clock rise time             | trck   |         |           | 10   | ns   |

| Input clock fall time             | teck   |         |           | 10   | ns   |

| Input clock duty                  | D      | 40      | 50        | 60   | %    |

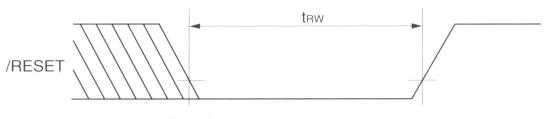

| Reset pulse width                 | trw    | 75*tvck |           |      | ns   |

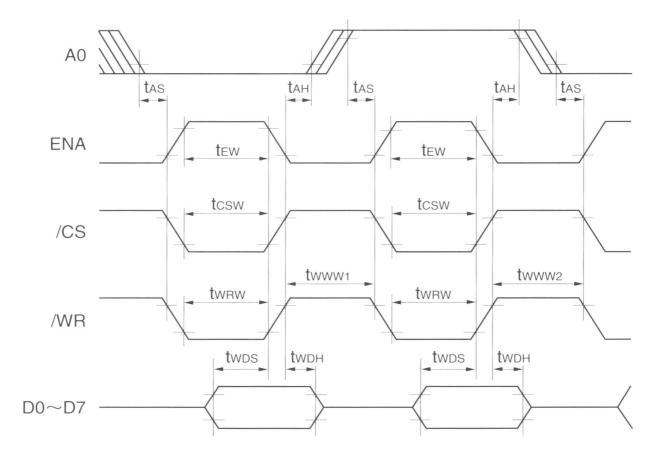

| A0 set-up time *2                 | tas    | 5       |           |      | ns   |

| A0 hold time *3                   | tah    | 5       |           |      | ns   |

| Chip select pulse width *4        | tcsw   | tck+20  |           |      | ns   |

| Write pulse width *4              | twrw   | tck+20  |           |      | ns   |

| ENA pulse width *4                | tew    | tck+20  |           |      | ns   |

| Write wait time(1) *5             | twwwi  | 2*tvck  |           |      | ns   |

| Write wait time(2) *5             | twww2  | 65*tvck |           |      | ns   |

| Write data set-up time *6         | twds   | 80      |           |      | ns   |

| Write data hold time *6           | twdh   | -5      |           |      | ns   |

| Memory access time *7             | trac   |         |           | 250  | ns   |

Note: Output load capacitance CL=50(pF).

- \*1: tvck=488.28ns. Internal operation clock cycle(2.048MHz).

- \*2: tas is determined by the later timing of "both /CS and /WR turn 'L" or "ENA turns 'H".

- \*3: tah is determined by the earlier timing of "both /CS and /WR turn 'H" or "ENA turns 'L"".

- \*4: Overlapping time of each pulse width.

- \*5: twww1 and twww2 are determined by the longer period of "/CS and /WR are 'H'" or "ENA is 'L"".

- \*6: twps and twph are determined by the earlier timing of "both /CS and /WR turn 'H'" or "ENA turns 'L"".

- \*7: The time from the moment address has been settled to the moment data has been settled.

Fig.1 Master clock timing

Fig.2 Reset timing

Fig.3 CPU interface timing

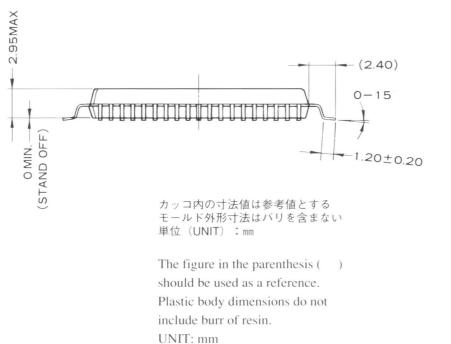

# **EXTERNAL DIMENSIONS**

NOTE: The LSIs for surface mount need especial consideration on storage and soldering condisions. For derailed information, please contact your nearest agent of yamaha.

### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

Note) The specifications of this product are subject to improvement changes without prior notice.

AGENCY-■ Tokyo Office ■ U.S.A. Office

# YAMAHA CORPORATION

Address inquiries to :

Semi-conductor Sales Department

■ Head Office 203, Matsunokijima, Toyooka-mura.

Iwata-gun, Shizuoka-ken, 438-01 Electronic Equipment business section Tel. 0539-62-4918 Fax. 0539-62-5054

2-17-11, Takanawa, Minato-ku, Tokyo, 108

Tel. 03-5488-5431 Fax. 03-5488-5088

■ Osaka Office 3-12-9, Minami Senba, Chuo-ku,

Osaka City, Osaka, 542 Shinsaibashi Plaza Bldg, 4F Tel. 06-252-7980 Fax. 06-252-5615

YAMAHA Systems Technology 100 Century Center Court, San Jose, CA 95112 Tel. 408-467-2300 Fax. 408-437-8791