# Dual-Port Buffer Controller

**PRELIMINARY**

- Direct 16-Bit Buffer Addressing

- Fully Downward Compatible With The AIC-300F

- DMA Handshake Logic

- Overrun Control

- Dual-Port Circular FIFO Buffer Control

- Buffer Sizes From 256 To 64K Locations

- Port Priority Resolver

- Two-Wire Arbitration Logic

- Optimized For Use With AIC-010 Or AIC-011 Programmable Storage Controller Chip

- Ideal For Use In Local Area Network Applications

- Single +5V Power Supply

- 44-Pin Surface Mount Package

Section One Overview

The Adaptec AIC-301 Dual-Port Buffer Controller is specifically designed to simplify the buffering and increase throughput of block-oriented, high-performance, peripheral controllers. Its primary functions are: to allow low-cost static RAM to be utilized as a dual-port circular FIFO; to supervise data transfers to the buffer; to reduce the possibility of host overruns of the peripheral; and to allow for high-speed DMA transfers. The device contains logic for resolving peripheral/host requests by giving priority to the peripheral and placing effectively a hold request to the host. The AIC-301 also implements a two-wire arbitration circuit and provides DMA handshaking. This device represents a significant savings in component count for high-performance, block-oriented, device controllers and provides performance capabilities that previously had not been cost effective for microcomputers.

The AIC-301 is intended for use in intelligent controllers utilizing a low-cost microprocessor for supervision of the controller function. The device is software configurable, via a multiplexed microprocessor I/O bus as provided by the Intel 8085 family of microprocessors, and is adaptable to other microprocessor I/O techniques. The AIC-301 is fully downward compatible with the AIC-300F, and is optimized for use with the Adaptec AIC-010 or AIC-011 Programmable Storage Controller ships in the design of a low-cost, high-performance, disk controller.

AIC-301 2 adaptec

| Symbol           | Pin            | Type | Name and Function                                                                                                                                                                                                                                                               |

|------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>  | 1              | IN   | +5 Volts                                                                                                                                                                                                                                                                        |

| CS               | 2              | IN   | CHIP SELECT: Asserting CS allows the microprocessor to access the registers of the AIC-301.                                                                                                                                                                                     |

| A0-A7/<br>A8-A15 | 3-10           | OUT  | BUFFER ADDRESS LINES: Bits 0-7 for addressing low-order address of buffer in the direct addressing mode. In the AIC-300F compatible, multiplexed mode, with more than 10-bit addressing, these lines are multiplexed low- and high-order addresses.                             |

| SHP or -A8       | 12             | OUT  | STROBE HOST POINTER: Buffer address Bit 8 in the direct addressing mode. This is the clocking signal for loading high-order address bits into an external host address register in applications using more than 10-bit addressing, in the AIC-300F compatible multiplexed mode. |

| SDP or -A9       | 12             | OUT  | STROBE DEVICE POINTER: Buffer address Bit 9 in the direct addressing mode. This is the clocking signal for loading high-order address bits into external disk address register in applications using more than 10-bit addressing, in the AIC-300F-compatible multiplexed mode.  |

| ALE              | 13             | IN   | ADDRESS LATCH ENABLE: This control signal latches the address on the A/DO-7 lines and identifies the bits as register address.                                                                                                                                                  |

| -RST             | 14             | IN   | RESET: This line, when asserted, resets all registers in the AIC-301 and sets Bit 0 of Register 59.                                                                                                                                                                             |

| -PORT A R        | EQ 15          | IN   | PORT A REQUEST: Requests a Port A data transfer into or out of the buffer.                                                                                                                                                                                                      |

| -CLK             | 16             | IN   | CLOCK: This is the primary clock for the part. Its period should be greater than RAM access time +100 ns.                                                                                                                                                                       |

| A10              | 17             | IN   | BUFFER ADDRESS LINE: Buffer address Bit 10 in the direct addressing mode.                                                                                                                                                                                                       |

| -RD              | 18             | IN   | READ: -RD and CS active cause the data on the A/D lines to be read from the specified register.                                                                                                                                                                                 |

| -WR              | 19             | IN   | WRITE: -WR and CS active cause the data on the A/D lines to be written into the specified register.                                                                                                                                                                             |

| A/D0-7           | 20-21<br>23-28 | I/O  | MULTIPLEXED ADDRESS/DATA: These are tri-state Address/Data lines which interface with a multiplexed microprocessor Address/Data bus.                                                                                                                                            |

| Symbol     | ymbol Pin Ty <sub>l</sub> |     | Name and Function                                                                                                                                                                                                  |  |  |

|------------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GND        | 22                        | IN  | GROUND.                                                                                                                                                                                                            |  |  |

| A11-A13    | 29-31                     | IN  | BUFFER ADDRESS LINES: Buffer address Bits 11-13 in the direct addressing mode.                                                                                                                                     |  |  |

| -MS/-MOE   | 32                        | OUT | MEMORY SELECT/MEMORY OUTPUT ENABLE: Chip select or ou put enable for the buffer memory RAM chips. This is controlled by Register 55.                                                                               |  |  |

| -WE        | 33                        | OUT | WRITE ENABLE: -WE enables data to be written into the RAM buffer and deasserting -WE enables data to be read from the RAM buffer.                                                                                  |  |  |

| BSY OUT    | 34                        | OUT | BUSY OUT: Either set directly by the microprocessor or, in an arbitration request mode, the Busy Out will be activated when Busy In and Select in are inactive. The arbitration mode assures an arbitration phase. |  |  |

| BSY IN     | 35                        | IN  | BUSY IN: Active when other devices are actively accessing the bus.                                                                                                                                                 |  |  |

| SEL OUT    | 36                        | OUT | SELECT OUT: Set by the microprocessor as Bit 6, Register 52 (Channel Control).                                                                                                                                     |  |  |

| SEL IN     | 37                        | IN  | SELECT IN: Active indicates a bus select status. SEL IN will reset the arbitration latch.                                                                                                                          |  |  |

| -ET/A15    | 38                        | OUT | ENABLE TARGET: Set by the microprocessor as Bit 7 of Register 53 or buffer address Bit 15 in the direct addressing mode.                                                                                           |  |  |

| -EI/A14    | 39                        | OUT | ENABLE INITIATOR: Set by the microprocessor as Bit 6 of Register 53 or buffer address Bit 14 in the direct addressing mode.                                                                                        |  |  |

| -BIE       | 40                        | OUT | BUS IN ENABLE: Used to clock data into external latches from the bus for writing into the buffer.                                                                                                                  |  |  |

| -BOE       | 41                        | OUT | BUS OUT ENABLE: Used to clock data out of external latches for transfer onto the bus. Asserted when arbitration latch is set.                                                                                      |  |  |

| LO         | 42                        | OUT | LATCH OUT: Used to gate data into external latches after reading from buffer via Port B.                                                                                                                           |  |  |

| PORT B ACI | K 43                      | IN  | PORT B ACKNOWLEDGE: Used to acknowledge data has been received or sent from the buffer via Port B (DMA Handshake).                                                                                                 |  |  |

| PORT B REG | Q 44                      | OUT | PORT B REQUEST: The request for a data transfer via Port B (DMA Handshake).                                                                                                                                        |  |  |

The AIC-301 is divided into four basic subfunctions:

- Buffer Control

- Priority Resolver

- DMA Control

- Arbitration

When used in a CPU environment, the AIC-301 will work well with the DMA control devices available to provide host processor memory addressing, or it may be used in an external I/O bus system such as SCSI.

**Buffer Control:** The buffer control function provides read and write address registers as well as Memory Select (-MS) and Read/Write (-WE) signaling. These signals are used to read or write data from the RAM buffer.

**Priority Resolver:** The priority resolver allows the typically synchronous peripheral to have priority over the host requests. This is fairly crucial in disk controller applications where, in a 10 Mb/sec system, a data byte has to be transferred exactly once every 800 nsecs.

**DMA Control:** The DMA control generates a request to the host (PORT B REQ), gates into or out of the buffer the appropriate data, and waits for a correctly timed acknowledge (PORT B ACK).

**Arbitration:** The arbitration logic of the AIC-301 provides for a two-wire arbitration scheme where either SEL IN or BSY IN indicate a bus busy state. The device allows for stacking a request for arbitration when the bus is in the bus busy state. The arbitration logic can be set up to be AIC-300F compatible or fully SCSI compatible through Register 55, Bit 3.

The AIC-301 is capable of handling buffer sizes from 256 bytes to 64K bytes. The chip provides up to 16 buffer address signals necessary for this, along with a Memory Select (-MS) signal and a Read/Write (-WE) signal. The AIC-301 supports two modes of addressing, to control buffer sizes up to 64K bytes.

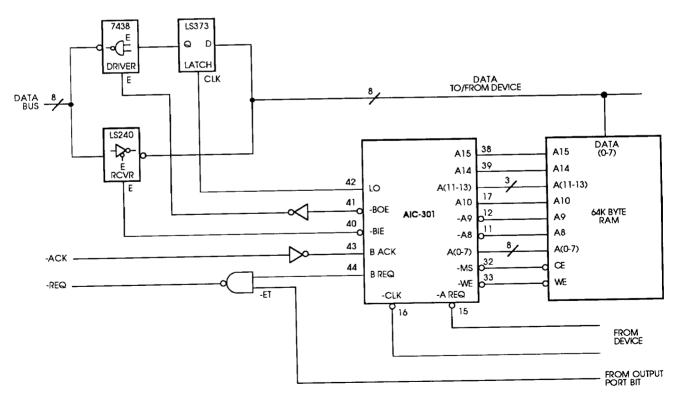

In the direct addressing mode, the AIC-301 can be set up to address up to 64K bytes of RAM directly. The size of buffer to be controlled is specified through the use of Registers 54 and 55. In the case of a 32K byte buffer, the output function on pin 39 (-EI) will be disabled and A14 will be enabled, while for a 64K byte buffer, the output function on pin 38 (-ET) will also be disabled and A15 will be enabled. An example of a 64K direct addressing application is shown in Figure 1.

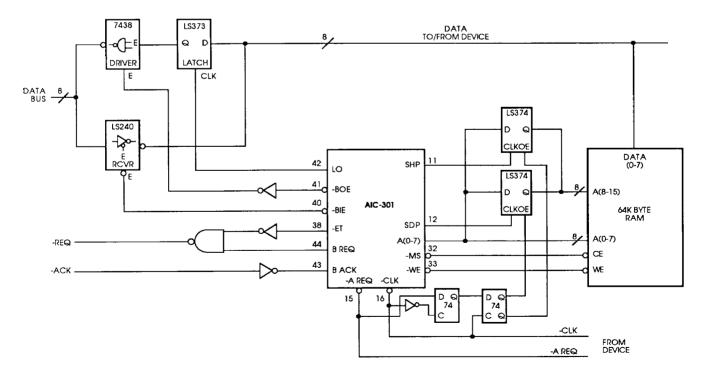

In the multiplexed addressing mode, the higher-order lines (A8-A15) and the lower-order lines (A0-A7) are multiplexed, coming out of the chip, on pins A0-A7. Two external tri-state registers are required for the high-order address lines A8-A15. These registers hold a copy of the internal counters, Registers 5B and 5D. These registers are updated on the CLK cycle following an increment of the internal counters (5B or 5D) if a PORT A cycle is not required, or on the CLK cycle following a write of 5B or 5D by the microprocessor. A word of caution: the microprocessor update of these external registers is not prioritized and, therefore, should only be done when PORT A and PORT B operations have quiesced. The AIC-301 updates the external registers by emitting the appropriate A8 through A15 on address lines A0 through A7 and then pulses either SHP or SDP appropriately. In normal operation, these updates will occur after every 256 bytes, transferred by either port.

FIGURE 1. DIRECT ADDRESSING APPLICATION EXAMPLE

When slow microprocessors are used, double pulsing of SHP and SDP will occur because of the internal synchronization circuit; however, the address for both pulses is valid.

The CLK cycle determines the access time requirement for the buffer RAMs, along with the address valid time for the AIC-301. For a 200 ns CLK period, 100 ns access-time RAM is needed for proper operation.

For proper interleaved Port A-Port B operation, the maximum rate at which Port A requests should occur is once for every two CLK cycles. This will allow PORT B REQ/ACK cycles to occur at one-half the CLK rate. Note that Port A cycles always have priority over Port B and high-order address register updates.

An example of the Multiplexed Addressing mode is shown in Figure 2. There are two programming requirements for this mode that are not obvious.

- 1. Because LS374s do not have a reset pin, a reset of the pointers using Register 59 is not adequate. A microprocessor load of 00<sub>H</sub> to the higher-order pointer registers (5B<sub>H</sub> and 5D<sub>H</sub>) is also required.

- 2. Any time the higher-order pointer registers are set-up, they have to be set-up twice; once to set the internal register, and once to update the external LS374.

FIGURE 2. MULTIPLEXED ADDRESSING APPLICATION EXAMPLE

The AIC-301 Buffer Controller chip is viewed as eleven internal registers and three external registers by the support processor. Table 1 shows each register and its function. A more detailed breakdown of the registers follows.

TABLE 1. REGISTER TABLE

| nternal Registers   | Description/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Register 52         | Control register for the host bus, for arbitration control.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Register 53         | DMA control register. Starts DMA operations and defines data direction for bus and device data transfers.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Register 54         | Buffer size register defines the size of the buffer to determine the roll-over point, creating a circular buffer.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Register 55         | Control register for specifying the operating mode of the AIC-301.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Register 59         | Only Bit 0 is used. When Bit 0 is set, all registers in the AIC-301 will be reset. Any write to this register will reset WAP, RAP, and SP.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Registers 5A and 5B | 16-bit Read Address Pointer, used to address the buffer on read cycles.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Registers 5C and 5D | 16-bit Write Address Pointer, used to address the buffer on write cycles.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Registers 5E and 5F | 16-bit Stop Pointer, used to prevent the host from overrunning the peripheral device. The Stop Pointer is compared with the Host Pointer by a comparator whose high-order bits are enabled by the contents of Register 54. When the two pointers are equal, DMA Request/Acknowledge cycles are halted and the Done bit is set. If a new, high-order, stop point is set, DMA Request/Acknowledge cycles will begin again, if the appropriate READ LATCH or WRITE LATCH is still on. |  |  |  |

| External Registers  | Description/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Register 50         | Register 50 decode is used to allow the support processor access to the host data bus. Register 50 decode and -WR assert LO.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Register 51         | Register 51 decode is used to allow the support processor to access the high-order byte o the data bus in 16-bit applicationsRD and -WR operate the same as Register 50.                                                                                                                                                                                                                                                                                                           |  |  |  |

| Register 70         | Register 70 decode is used to allow the support processor to access the buffer. A read wi cause -MS to be active. A write will cause -MS and -WE to be active.                                                                                                                                                                                                                                                                                                                     |  |  |  |

### 4.1 INTERNAL REGISTER DESCRIPTION

|       | 52 HOST INTERFACE CONTROL (READ/WRITE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0 | ARBITRATION: Setting this bit will cause the AIC-301 to wait for both SEL IN and BSY IN to become inactive; and then set the arbitration latch after a minimum of 1-1/2 and a maximum of 2-1/2 clock cycles. BSY OUT AND -BOE will then be asserted after a minimum of four clock cycles in the SCSI compatible mode, or at the same time arbitration latch is set in the AIC-300F compatible mode, if no other devices have arbitrated for the SCSI bus. The state of BSY OUT can also be read on this bit. Setting this bit to zero will clear arbitration. |

| Bit 1 | NOT USED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bit 2 | -BIE: Bus In Enable is latched in this register and then ORed with a hardware-generated -BIE for DMA. This allows the microprocessor access to the host data bus.                                                                                                                                                                                                                                                                                                                                                                                             |

| Bit 3 | -BOE: Bus Out Enable is latched and then ORed with a hardware-generated -BOE for DMA. This allows the processor to enable the data bus to the host bus.                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bit 4 | SELECT IN: Allows processor to sample the state of the SEL IN pin (READ ONLY).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bit 5 | BUSY IN: Allows processor to sample the state of the BSY IN pin (READ ONLY).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Bit 6 | SELECT OUT: When set, causes the SEL OUT pin in active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Bit 7 | BUSY OUT: When set, causes the BSY OUT pin in active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 53 DMA CONTROL (READ/WRITE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bit 0 | NOT USED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bit 1 | ACKNOWLEDGE: This bit samples the state of the PORT B ACK pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bit 2 | WRITE LATCH: Setting this bit will start DMA hardware of Port B to transfer data from the host to the RAM buffer. Bit 4 9ROP/WOP) must be in the WOP mode.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bit 3 | READ LATCH: Setting this bit will cause the DMA hardware of Port B to transfer data from the RAM buffer to the host. Bit 4 (ROP/WOP) must be in the ROP mode.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bit 4 | ROP/WOP: This is set for a read operation of the peripheral. A PORT A REQ will cause data to transfer from the peripheral to the RAM buffer. This is reset for a write operation to the peripheral A PORT A REQ will cause data to be transferred to the peripheral from the buffer.                                                                                                                                                                                                                                                                          |

|       | 53 DMA CONTROL (READ/WRITE) (CONTINUED)                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3it 5 | DMA DONE: When a DMA operation to/from the host is being performed and the stop pointer equals the appropriate address pointer, this bit will be set after PORT B REQ and PORT B ACK are inactive (READ ONLY). |

| Bit 6 | ENABLE INITIATOR: When set, out -EI will be active low, if this function is not disabled (Register 55).                                                                                                        |

| 3it 7 | ENABLE TARGET: When set, output -ET will be active low, if this function is not disabled (Register 55).                                                                                                        |

|       | 54 BUFFER SIZE (WRITE)                                                                                                                                                                                         |

|       | BUFFER SIZE: The different buffer sizes can be specified as follows:                                                                                                                                           |

|       | 00 = 256-Byte Buffer                                                                                                                                                                                           |

|       | 01 = 512-Byte Buffer                                                                                                                                                                                           |

|       | 03 = 1K-Byte Buffer                                                                                                                                                                                            |

|       | 07 = 2K-Byte Buffer                                                                                                                                                                                            |

|       | 0F = 4K-Byte Buffer<br>1F = 8K-Byte Buffer                                                                                                                                                                     |

|       | 1F = 8K-Byte Buffer 3F = 16K-Byte Buffer                                                                                                                                                                       |

|       | 7F = 32K-Byte Buffer                                                                                                                                                                                           |

|       | FF = 64K-Byte Buffer                                                                                                                                                                                           |

|       | 55 MODE CONTROL (WRITE)                                                                                                                                                                                        |

| Bit 0 | EXTENDED ADDRESSING ENABLE                                                                                                                                                                                     |

| Bit 1 | -EI/A14 ENABLE                                                                                                                                                                                                 |

| Bit 2 | -ET/A15 ENABLE                                                                                                                                                                                                 |

| Bit 3 | ARBITRATION MODE                                                                                                                                                                                               |

| Bit 4 | -MS/-MODE ENABLE                                                                                                                                                                                               |

| Bit 5 | NOT USED                                                                                                                                                                                                       |

#### 55 MODE CONTROL (WRITE) (CONTINUED)

The value loaded in this register controls the operating mode of the AIC-301. The AIC-301 can be set up to address up to 64K bytes directly. Following a reset, this Register contains 00, which makes the chip completely AIC300F compatible. Other modes of addressing, arbitration and memory selection can be set up as follows:

00H = 1K direct addressing, old arbitration scheme, -MS output (AIC-300F compatible)

01H = 16K direct addressing, new arbitration scheme, -MS output

03H = 32K direct addressing, new arbitration scheme, -MS output

07H = 64K direct addressing, new arbitration scheme, -MS output

08H = 1K direct addressing, new arbitration scheme, -MS output

09H = 16K direct addressing, old arbitration scheme, -MS output

0BH = 32K direct addressing, old arbitration scheme, -MS output

0FH = 64K direct addressing, old arbitration scheme, -MS output

10H = 1K direct addressing, old arbitration scheme, -MOE output

11H = 16K direct addressing, new arbitration scheme, -MOE output

13H = 32K direct addressing, new arbitration scheme, -MOE output

17H = 64K direct addressing, new arbitration scheme, -MOE output

18H = 1K direct addressing, new arbitration scheme, -MOE output

19H = 16K direct addressing, old arbitration scheme, -MOE output

1BH = 32K direct addressing, old arbitration scheme, -MOE output

1FH = 64K direct addressing, old arbitration scheme, -MOE output

Note: If the specified buffer size of register 54 is greater than the selected addressing mode, then byte-wide multiplexed addressing mode is assumed.

#### 59 RESET CONTROL (WRITE)

Bit 0 REGISTER RESET: If this bit is set, all registers are held in RESET until this bit is turned off.

A low input on the -RST pin will set this bit.

#### Bits 1-7 NOT USED

Note: Any write to this register will reset WAP, RAP, and SP. If external, high-order, address registers are used, they will not be reset.

|          | 5A RAP (0-7) (READ/WRITE)               |

|----------|-----------------------------------------|

| Bits 0-7 | Read Address Pointer Bits 0 through 7   |

|          | 5B RAP (8-15) (READ/WRITE)              |

| Bits 0-7 | Read Address Pointer Bits 8 through 15  |

|          | 5C WAP (0-7) (READ/WRITE)               |

| Bits 0-7 | Write Address Pointer Bits 0 through 7  |

|          | 5D WAP 98-15) (READ/WRITE)              |

| Bits 0-7 | Write Address pointer Bits 8 through 15 |

|          | 5E STOP (0-7) (READ/WRITE)              |

| Bits 0-7 | Stop Pointer Bits 0 through 7           |

|          | 5F STOP (8-15) (READ/WRITE)             |

| Bits 0-7 | Stop Pointer Bits 8 through 15          |

|          |                                         |

### 4.2 DATA TRANSFER DESCRIPTION

In the AIC-301 Dual-Port Buffer Controller, data transfer can take place in two possible ways:

- 1. Synchronously with the peripheral (Port A transfer) or,

- 2. Asynchronously with the host (Port B transfer).

In the case of Port A transfers, a byte is transferred after every time pin 14 (PORT A REQ) is asserted. This line is sampled on the falling edge of the signal on pin 15 (-CLK), and the data transfer takes place on the next cycle after PORT A REQ is asserted.

The direction of the transfer is determined by the value of Bit 4 in Register 53. If it is set, then a read operation is performed from the peripheral. The contents of the WAP registers (5C and 5D) are used to select a buffer address, and Memory Select (-MS) and Write Enable (-WE) are used to write the information into the buffer.

If Register 53, Bit 4, is reset, a write operation to the peripheral is performed. The RAP registers (5A and 5B) are used to generate a buffer address, and the data is read when Memory Select (-MS) is active. the ideal time for the peripheral to sample the data from the buffer RAM, in this case, is at the falling edge of -CLK following the PORT A REQ.

In the case of Port B transfers, data is transferred under the control of the AIC-301 chip. Again, the direction of the transfer is controlled by the contents of the ROP/WOP bit (Register 53, Bit 4), and either Write Latch or Read Latch (Register 53, Bit 1 or Bit 2).

If the ROP/WOP bit it set and Read Latch is on, then data is transferred from the buffer to the host. The contents of the RAP registers (5A and 5B) are used to generate the addresses. The data is latched into an external latch using the output signal on pin 37 (LO). -BOE is also asserted and the data is made available to the host. A PORT B REQ is sent to the host and the data is placed on the bus. After an acknowledge is received, -BOE is deasserted.

If Bit 4 in Register 53 is reset and Write Latch is on, then data is transferred from the host bus to the buffer. The contents of the WAP registers (5C and 5D) are used to generate the buffer address, -BIE is asserted to enable the external receiver.

Note: During a host data transfer, the top buffer address that can be accessed is controlled by the Stop Pointer (Registers 5E and 5F).

A detailed description of the data transfers in two fundamental AIC-301 operations follows:

- 1. Read

- Single Block

- Multiple Block

- 2. Write

- Single Block

- Multiple Block

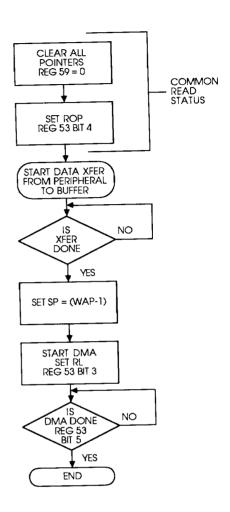

#### 5.1 INITIALIZATION

Initialization is done after power on reset. It is not required thereafter:

- Reset chip by strobing pin 13 and set Register 59 to 00<sub>H</sub> (clear reset).

- 2. Set maximum size of RAM buffer by loading Register 54 with buffer size.

- 3. Set mode control, if necessary, by loading Register 55 with address range, arbitration and memory enable.

#### 5.2 SINGLE BLOCK READ

- 1. Clear all pointers (set Register 59 to 0).\*

- 2. Set-up for read operation (set Register 53, Bit 4).

- 3. Transfer data to buffer (WAP will increment on each transfer).

- 4. At completion of transfer from device, set SP to (WAP-1) and set read latch for DMA read operation (Register 53, Bit 3). RAP will increment for each REQ ACK cycle.

- 5. Monitor DMA Done bit (Register 53, Bit 5) to determine when the DMA transfer is complete (RAP equals SP).

- \* In the multiplexed addressing mode, after setting Register 59 to 0, also set RAPH (Register 53) and WAPH (Register 5D) to 0.

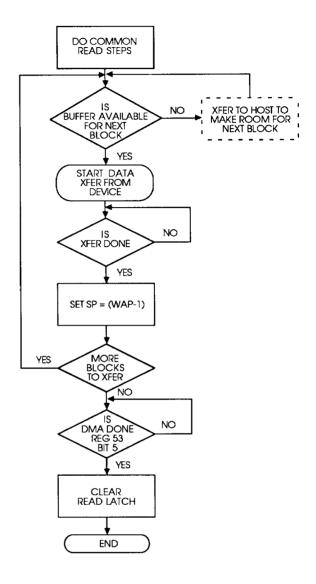

#### 5.3 MULTIPLE BLOCK READ

- 1. Do the same first four operations as a single block read.

- 2. Read RAP to ensure that next block may be transferred from the device without overrunning the RAP.

- 3. Begin transfer of next block to buffer (WAP will increment on each transfer).

- 4. At end of transfer, set SP to new (WAP-1) address.

- 5. If DMA Done occurred, a restart of the DMA transfer will occur when the new SP address is set.

- 6. Return to Step 2 if more blocks are to be transferred.

- 7. Wait for DMA Done and clear Read Latch.

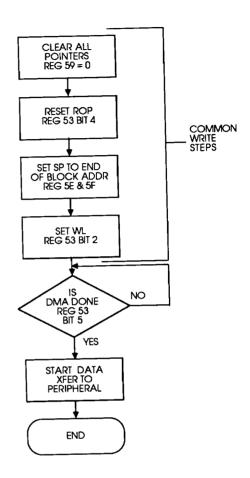

### 5.4 SINGLE BLOCK WRITE

- 1. Clear all pointers (set Register 59 to 0).\*

- 2. Reset Read OP in DMA control (Register 53, Bit 4).

- 3. Set SP to the address at the end of the block to be transferred.

- 4. Set the Write Latch (Register 53, Bit 2). This causes the DMA cycles to begin.

- 5. Monitor DMA Done bit (Register 53, Bit 5) to determine when DMA transfer is complete (WAP equals SP).

- 6. Transfer to the peripheral may now begin.

- \* In the multiplexed addressing mode, after setting Register 59 to 0, also set RAP<sub>H</sub> (Register 53) and WAP<sub>H</sub> (Register 5D) to 0.

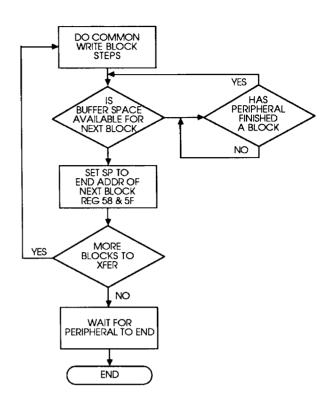

#### 5.5 MULTIPLE BLOCK WRITE

- 1. Do the same first five operations as Single Block Write.

- 2. Begin block transfer to peripheral.

- 3. Check that there is enough buffer for the next block without overrunning the RAP. If buffer space is available, set SP to end of next block.

- 4. If DMA Done was on, setting the new SP address will clear it and renew DMA transfers.

#### 5.6 EXTERNAL REGISTERS

In addition to these data transfer operations, certain data transfers are possible that happen external to the AIC-301 chip. These have to do with accesses to external Registers 50, 51, and 70.

A Read/Write to Register 50 by the support processor is used to directly access the host data bus. During a read to Register 50, if Bit 2 of Register 52 (-BIE) was previously set, the -BIE line (pin 35) will be asserted. The host data latch contents will then be placed on the data bus. During a write to Register 50, if Bit 3 of Register 52 (-BOE) was previously set, the LO line (pin 37) will first be asserted, allowing the support processor data to be latched. This will be followed by -BOE (pin 36) being asserted, allowing the latched data to become available on the host data bus. Typical configurations were shown in Figures 1 and 2.

An access to Register 70 is used by the support processor to access the data in the buffer. The address is generated by the AIC-301 chip and is based on the contents of RAP (Registers 5A and 5B) if Register 53, Bit 4 is reset (WOP); and on the contents of WAP (Registers 5C and 5D) if Register 53, Bit 4 is set (ROP). The address pointer (RAP or WAP0 is not incremented by a Register 70 access.

In the 16-bit addressing mode, to ensure proper operation during a Register 70 access, both RAP Registers (5A and 5B) and both WAP Registers (5C and 5D) must be loaded with the same value. Also, ensure that the Read Latch bit (R53, Bit 3) and the Write Latch bit (R53, Bit 2) are both 0 and the ROP/WOP bit (R53, Bit 4) is 1.

The arbitration circuit is designed to allow rapid arbitration in two-wire arbitration systems.

The AIC-301 can be set up to arbitrate in one of two ways. The first method maintains compatibility with the AIC-300F and requires the use of external circuitry (such as that found in the Adaptec SCSI interface adapter, the AIC-500) to meet the full SCSI arbitration timing requirements. The second method incorporates all the logic necessary to fully meet the SCSI timing without the need for additional circuitry. The mode of arbitration to be used is controlled by setting up Register 55 appropriately. Arbitration is initiated by setting Register 52, Bit 0.

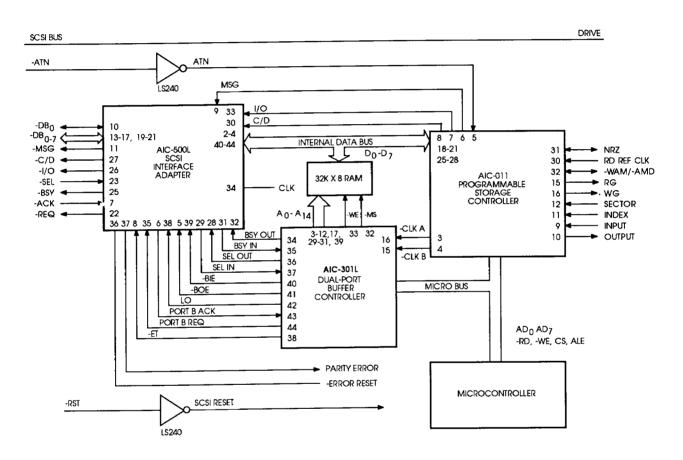

Based on the AIC-301 and the AIC-010, an extremely powerful SCSI-based controller can be built. All that is needed to complete the design is a microprocessor, some program ROM, buffer RAM, and a SCSI interface chip like the Adaptec AIC-500. The AIC-500 complements the arbitration logic in the AIC-301, allowing the designer to build a full-function SCSI controller that supports Disconnect/Reconnect/Arbitration, Bus Parity, 1:1 Interleave, and the latest SCSI revision command set. A block diagram of such a controller is shown below.

The above design is based on a 32K byte buffer size. If a 64K byte buffer needs to be directly addressed, the -ET function on pin 38 must be disabled (Register 55, Bit 2) and A15 must be enabled. The -ET function may then be provided through an output bit in the microcontroller.

# 8.1 ABSOLUTE MAXIMUM RATINGS

| Ambient Temperature Under Bias            | 0°C to 70°C    |

|-------------------------------------------|----------------|

| Ambient Temperature Order Blas            | -65°C to 150°C |

| Storage Lemneranire                       |                |

| Voltage On Any Pin With Respect To Ground |                |

| Power Dissipation                         | 0.5 Watt       |

Note: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**8.2** D.C. CHARACTERISTICS (Test Conditions:  $V_{CC} = 5.0V \pm 5\%$ ,  $V_{SS} = 0V$ ,  $0^{\circ}C < T < 70^{\circ}C$ )

| Symbol                               | Parameter                               | Min  | Max                  | Units | Conditions                                                             |

|--------------------------------------|-----------------------------------------|------|----------------------|-------|------------------------------------------------------------------------|

|                                      | Input Low Voltage (All Inputs)          | -0.5 | 0.8                  | V     |                                                                        |

| V <sub>IL</sub><br>V <sub>IH</sub>   | Input High Voltage (All Inputs)         | 2.0  | V <sub>CC</sub> +0.5 | V     |                                                                        |

| v <sub>.</sub> iн<br>V <sub>OL</sub> | Output Low Voltage (All Outputs)        | -0.2 | 0.4                  | V     | $I_{OL} = 2 \text{ mA}$                                                |

| VOH                                  | Output High Voltage (All Outputs)       | 2.4  |                      | V     | $I_{OH} = 400 \mu A$                                                   |

| Icc                                  | Supply Current ( $T_A = 70^{\circ}C$ )  |      | 85                   | mA    | $V_{CC} = 5.5$                                                         |

| IIL                                  | Input Leakage                           | -2.0 | 2.0                  | μΑ    | $0 < V_{\text{IN}} < V_{\text{CC}}, T_{\text{A}} = 25^{\circ}\text{C}$ |

| IOL                                  | Output Leakage (Off State)              | -10  | 10                   | μΑ    | 0 <v<sub>OUT<v<sub>CC</v<sub></v<sub>                                  |

| C <sub>IN</sub>                      | Device Input Capacitance (All Inputs)   |      | 10                   | pF    |                                                                        |

| C <sub>OUT</sub>                     | Device Output Capacitance (All Outputs) |      | 15                   | pF    |                                                                        |

| $C_L$                                | External Load Capacitance (All Outputs) |      | 50                   | pF    |                                                                        |

CAUTION: STATIC-SENSITIVE DEVICE. HANDLE WITH CARE.

# 8.3 A.C. TIMING CHARACTERISTICS

(Test Conditions:  $V_{CC} = 5.0V \pm 5\%$ ,  $V_{SS} = 0V$ ,  $0^{\circ}C < T < 70^{\circ}C$ )

###

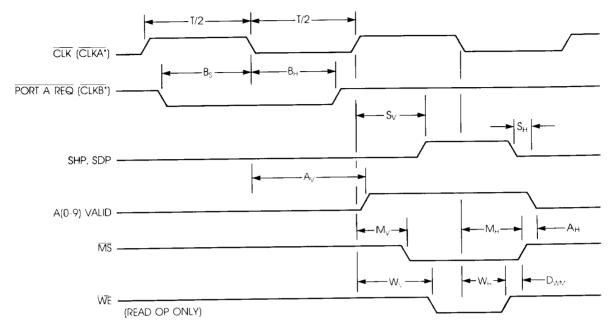

# **8.3.1** BUFFER RAM INTERFACE (Test Conditions: $V_{CC} = 5.0V \pm 5\%$ , $V_{SS} = 0V$ , $0^{\circ}C < T < 70^{\circ}C$ )

\*CONNECTS TO THESE SIGNALS ON THE AIC-010 OR THE AIC-100 IN DISK CONTROLLER APPLICATIONS.

| Symbol          | Parameter                   | Min | Max | Units |

|-----------------|-----------------------------|-----|-----|-------|

| T               | CLK Period                  | 180 |     | ns    |

| T/2             | CLK Half Cycle              | 90  |     | ns    |

| $B_{S}$         | -CLKB   to -CLKA   (Set-Up) | 90  |     | ns    |

| $B_{H}$         | -CLKA   to -CLKB   (Hold)   | 20  |     | ns    |

| Av              | -CLKA ∮ to ADRS Valid       |     | 100 | ns    |

| $A_{H}$         | -MS † to ADRS -Valid (Hold) | 35  |     | ns    |

| My              | -CLKA to -MS t              |     | 45  | ns    |

| MH              | -CLKA ↓ to -MS ↓            | 20  | 60  | ns    |

| Wv              | -CLKA ↑ to -WE ↓            |     | 60  | ns    |

| W <sub>H</sub>  | -CLKA + to -WE +            | 10  | 40  | ns    |

| Sv              | -CLKA † to SHP, SDP †       | 20  | 50  | ns    |

| SH              | SHP, SDP ↓ to ADRS -Valid   | 10  |     | ns    |

| D <sub>WM</sub> | -WE † to -MS †              | 10  |     | ns    |

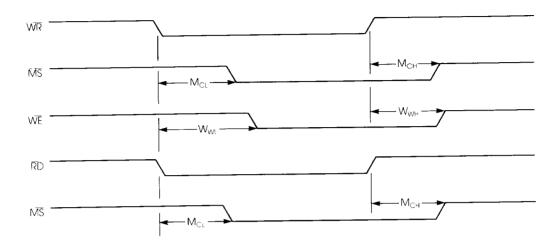

# 8.3.2 READ/WRITE REGISTER 70

| Symbol          | Parameter             | Min | Max | Units |

|-----------------|-----------------------|-----|-----|-------|

| M <sub>CL</sub> | -WR or -RD ↓ to -MS ↓ |     | 75  | ns    |

| M <sub>CH</sub> | -WR or -RD to -MS     |     | 75  | ns    |

| WwL             | -WR ↓ to -WE ↓        |     | 70  | ns    |

| wwl<br>Wwh      | -WR to -WE            |     | 50  | ns    |

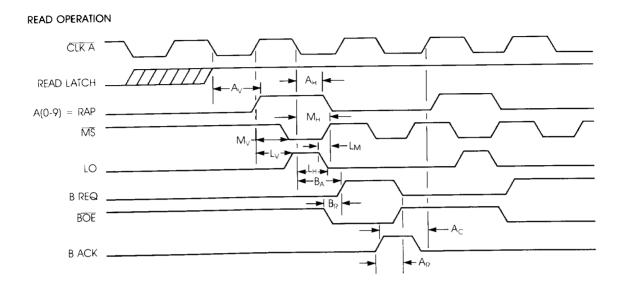

## 8.3.3 BUFFER TO HOST INTERFACE

| Symbol         | Parameter              | Min | Max | Units |

|----------------|------------------------|-----|-----|-------|

| <br>Ау         | -CLKA ↓ to ADRS Valid  |     | 100 | ns    |

| A <sub>H</sub> | -CLKA ↓ to ADRS -Valid | 35  |     | ns    |

| Mγ             | -CLKA ↓ to -MS ↓       |     | 45  | ns    |

| M <sub>H</sub> | -CLKA   to -MS         | 20  | 60  | ns    |

| L <sub>V</sub> | -CLKA to LOt           |     | 60  | ns    |

| L <sub>H</sub> | -CLKA   to LO †        | 10  | 40  | ns    |

| L <sub>M</sub> | LO   to -MS            | 10  |     | ns    |

| B <sub>A</sub> | -CLKA ↓ to BREQ ↑      | 45  | 140 | ns    |

| B <sub>R</sub> | -BOE ↓ to BREQ ↑       | 45  | 110 | ns    |

| A <sub>C</sub> | BACK to -CLKA (Set-Up) | 20  |     | ns    |

| A <sub>R</sub> | BACK ↑ to BREQ ↓       |     | 40  | ns    |

| 1/             |                        |     |     |       |

NOTE: A PORT A REQ cycle has priority over a DMA cycle: i.e., PORT A REQ is not active during the falling edge of -CLK, the following cycle is available for DMA. If PORT A REQ is active, -BIE will be disabled for one -CLK cycle.

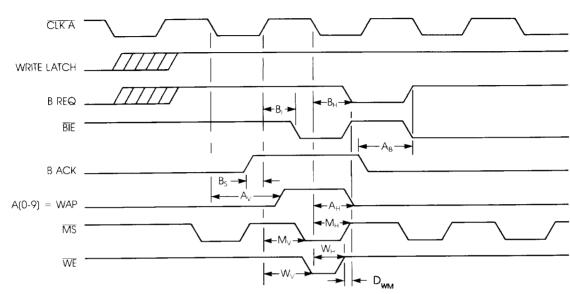

## 8.3.4 HOST TO BUFFER INTERFACE

| Symbol             | Parameter              | Min | Max | Units |

|--------------------|------------------------|-----|-----|-------|

| <br>B <sub>I</sub> | -CLKA to -BIE          |     | 60  | ns    |

| $B_{H}$            | -CLKA ↓ to BREQ ↓      |     | 50  | ns    |

| $B_{S}$            | BACK to -CLKA          | 30  |     | ns    |

| Ay                 | -CLKA ↓ to ADRS Valid  |     | 100 | ns    |

| $A_{H}$            | -CLKA ↓ to ADRS -Valid | 35  |     | ns    |

| My                 | -CLKA to -MS           |     | 45  | ns    |

| M <sub>H</sub>     | -CLKA ↓ to -MS †       | 20  | 60  | ns    |

| $W_V$              | -CLKA to -WE           |     | 60  | ns    |

| $W_{H}$            | -CLKA ↓ to -WE ↑       | 10  | 40  | ns    |

| D <sub>WM</sub>    | -WE to -BIE to -MS t   | 10  |     | ns    |

| AB                 | BACK   to BREQ         |     | 40  | ns    |

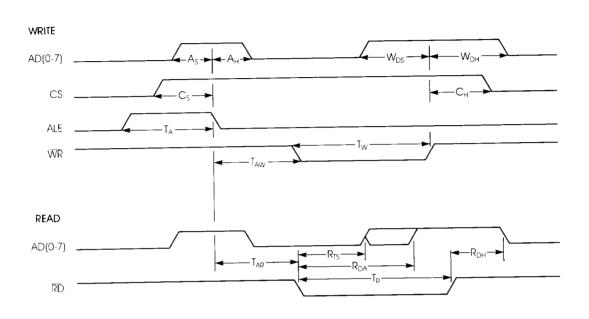

# 8.3.5 MICROPROCESSOR INTERFACE

| Symbol             | Parameter                   | Min | Max | Units |

|--------------------|-----------------------------|-----|-----|-------|

| <br>Т <sub>А</sub> | ALE Width                   | 60  |     | ns    |

| $T_{AW}$           | ALE ↓ to -WR ↓              | 30  |     | ns    |

| $T_{AR}$           | ALE ↓ to -RD ↓              | 30  |     | ns    |

| Tw                 | -WR Width                   | 160 |     | ns    |

| $T_{R}$            | -RD Width                   | 215 |     | ns    |

| As                 | ADRS Valid to ALE ↓         | 20  |     | ns    |

| A <sub>H</sub>     | ALE   to ADRS -Valid        | 10  |     | ns    |

| C <sub>S</sub>     | CS Valid to ALE ↓           | 15  |     | ns    |

| C <sub>H</sub>     | -RD or -WR   to CS          | 10  |     | ns    |

| W <sub>DS</sub>    | Write Data Valid to -WR     | 70  |     | ns    |

| W <sub>DH</sub>    | -WR to Write Data -Valid    | 0   |     | ns    |

| RTS                | -RD ↓ to AD(0-7) Out Active | 10  |     | ns    |

| R <sub>DS</sub>    | -RD ↓ to Read Data Valid    |     | 150 | ns    |

| R <sub>DH</sub>    | -RD ↓ to Read Data -Valid   | 20  | 50  | ns    |

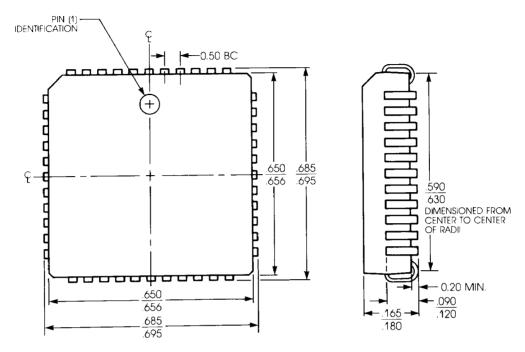

44-LEAD PLASTIC SURFACE MOUNT PACKAGE