# SCSI Interface Adapter

- Asynchronous DataTransfer To 1.5 Mbytes/Sec

- Supports Target Role

- Parity Generation And Checking

- Complements AIC-300

Arbitration And Meets

SCSI Specification

- SCSI Bus Signals Driven Under Microprocessor Control

- High Current Outputs Drive SCSI Bus Directly

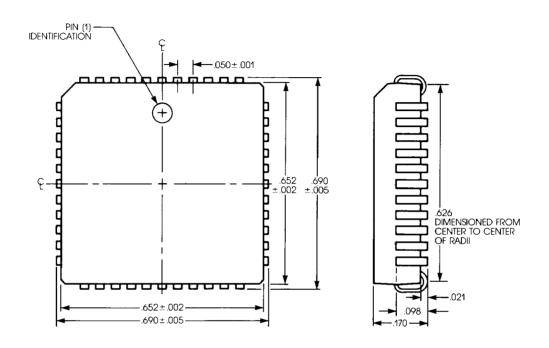

- Available in 44-Pin PLCC Package

#### **OVERVIEW**

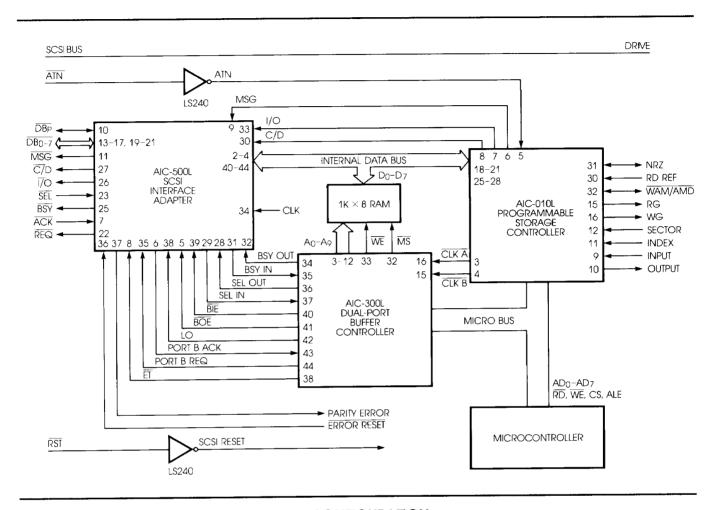

The AIC-500 is designed to simplify the implementation of a SCSI host interface-based disk controller. It is intended to be used in designs based around the Adaptec Programmable Storage Controller, the AIC-010; and the Adaptec Dual-Port Buffer Controller, the AIC-300. The AIC-500 comes in a 44-pin J-pack and has the high-current drivers needed to directly connect to the SCSI bus.

The AIC-010, AIC-300, AIC-500, and the buffer RAM are all that is needed to design an extremely powerful and cost effective controller which is resident o the disk drive. In most applications, the microcontroller that is directly present on the drive can be shared between

the drive-related and the controller-related functions. With a dedicated processor, this same set can be used to build edxtremely hgh-performance SCSI controllers which connect to drive level interfaces like ST412/506, ESDI, and SMD.

<sup>©</sup> Copyright Adaptec, Inc. 1982, 1987. All rights reserved. The information contained in this data sheet is subject to change without notice. No part of this document may be copied or reproduced in any form without prior written consent from Adaptec, Inc.

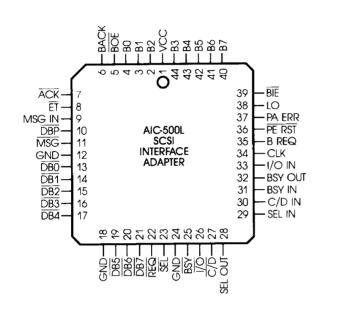

# PIN DESCRIPTION

| SYMBOL          | PIN            | TYPE     | TYPE NAME AND FUNCTION                                                                                                               |  |

|-----------------|----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |                |          | SCSI LINES                                                                                                                           |  |

| ACK             | 7              | SCSI I   | ACKNOWLEDGE: Used to acknowledge data has been received or sent on SCSI bus.                                                         |  |

| DBP             | 10             | SCSI I/O | DATA BIT PARITY: SCSI bus parity bit.                                                                                                |  |

| MSG             | 11             | SCSI O   | MESSAGE: Used to select a message phase on the SCSI bus.                                                                             |  |

| DBO to DB7      | 13-17<br>19-21 | SCSI I/O | DATA BITS 0-7: SCSI bus data lines.                                                                                                  |  |

| REQ             | 22             | SCSI O   | REQUEST: The request for data transfer on SCSI bus.                                                                                  |  |

| SEL             | 23             | SCSI I/O | SELECT: Indicates a bus select status.                                                                                               |  |

| BSY             | 25             | SCSI I/O | BUSY: Active when any device is accessing the SCSI bus.                                                                              |  |

| /0              | 26             | SCSI O   | INPUT/OUTPUT: Used to select the direction of data movement on the SCSI bus with respect to the initiator.                           |  |

| C/D             | 27             | SCSI O   | COMMAND/DATA: Used to select command or data transfer on SCSI bus.                                                                   |  |

|                 |                |          | CONTROLLER LINES                                                                                                                     |  |

| V <sub>cc</sub> | 1              |          | +5 Volts.                                                                                                                            |  |

| BO to B7        | 2-4<br>40-44   | ΠL I/O   | DATA BUS 0-7: Connects to buffer RAM data pins.                                                                                      |  |

| ВОЕ             | 5              | TTL 1    | BUS OUT ENABLE: Connects to AIC-300. Used to clock data out of internal latches for transfer onto SCSI bus.                          |  |

| PORT B ACK      | 6              | TTL O    | PORT B ACK: Connects to AIC-300. The acknowledge for a Port B data transfer.                                                         |  |

| ET              | 8              | TTL I    | ENABLE TARGET: Connects to AIC-300. Provides microcode and hardware access to disable all drivers on the SCSI bus, except BUSY.      |  |

| MSG IN          | 9              | TTL I    | Connects to I/O port which drives MSG.                                                                                               |  |

| GND             | 12, 18, 24     |          | GROUND.                                                                                                                              |  |

| SEL OUT         | 28             | TTL I    | SELECT OUTPUT: Connects to the AIC-300. Used as an input from the AIC-300 to indicate when to drive the select line on the SCSI bus. |  |

| SEL IN          | 29             | TTL O    | SELECT INPUT: Connects to the AIC-300. Used to pass the select line from the SCSI bus to the AIC-300.                                |  |

| C/D IN          | 30             | TTL I    | Connects to I/O port which drives $\overline{\mathbb{C}}/\mathbb{D}$ .                                                               |  |

| BSY IN          | 31             | TTL O    | BUSY INPUT: Connects to AIC-300. Used to pass busy to the AIC-300 to indicate when other devices are actively accessing the bus.     |  |

| BSY OUT         | 32             | TTL I    | BUSY OUTPUT: Connects to AIC-300. Used as an input from the AIC-300 to indicate when to drive the busy line on the SCSI bus.         |  |

| I/O IN          | 33             | TTL I    | Connects to I/O port which drives I/O.                                                                                               |  |

| CLK             | 34             | TTL I    | CLOCK: Used for clock input between 2.5 MHz and 5 MHz.                                                                               |  |

| SYMBOL     | PIN | TYPE  | NAME AND FUNCTION                                                                                                                                                                                                                                                        |

|------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PORT B REQ | 35  | TTL I | PORT B REQ: Connects to AIC-300. The request for a Port B data transfer.                                                                                                                                                                                                 |

| PE RST     | 36  | TTL I | PARITY ERROR RESET: When held high, the AIC-500 checks SCSI bus parity and indicates a parity error by setting logic 1 (high) on the PA/ERR pin. When held low, parity is passed through the AIC-500 to the controller buffer with the PA/ERR line being the parity bit. |

| PA/ERR     | 37  | TTL O | PARITY <u>ERROR</u> : Logic 1 indicates a parity error detected on the SCSI bus when PE RST is held high. When the PE RST line is held low, parity will be passed to the controller bufffer by using the PA/ERR line as the parity bit for each byte.                    |

| LO         | 38  | TTL I | LATCH OUT: Connects to AIC-300. Gates data into internal latches after reading data from buffer.                                                                                                                                                                         |

| BIE        | 39  | TTL I | BUS IN ENABLE: Connects to AIC-300. Used to enable data from bus for writing data into buffer.                                                                                                                                                                           |

#### **FUNCTIONAL DESCRIPTION**

The AIC-500 is divided into four basic subfunctions:

- Parity Generation/Checking

- Arbitration

- SCSI Bus Drivers and Receivers

- REQ/ACK Handshake and Data Latch

PARITY GENERATION/CHECKING: The AIC-500 parity generation/checking logic will latch parity errors or pass parity through the AIC-500 in order to maintain buffer parity. The AIC-500 always generates SCSI bus parity on inbound SCSI transfers and during the selection phase.

ARBITRATION: The AIC-500 complements the AIC-300 arbitration logic to provide correct SCSI bus timing. On the SCSI interface, this provides a two-wire arbitration scheme where either SEL or BSY indicate a bus busy state.

SCSI BUS DRIVERS AND RECEIV-ERS: The AIC-500 has the 48 mA open-collector outputs necessary for driving the control and data line of a single-ended SCSI bus directly. REQ/ACK HANDSHAKE AND DATA LATCH: The AIC-500 complements the AIC-300 REQ/ACK handshake timing by latching the SCSI data for an outbound data transfer before completing the transfer into the controller buffer. This speeds data transfer across the bus by reducing the REQ/ACK timing restraints for the SCSI bus transfers.

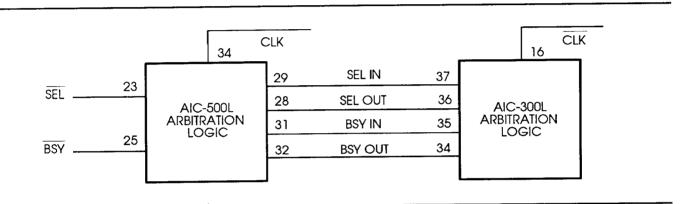

FIGURE 1. TYPICAL FULL SCSI CONTROLLER CONFIGURATION

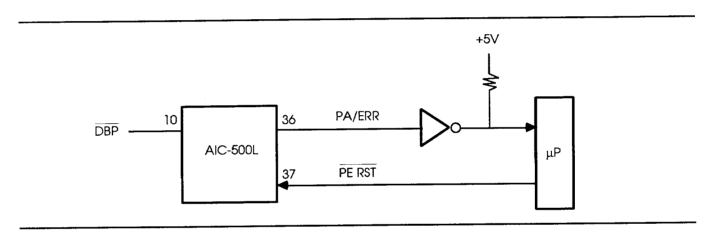

## **Parity**

The AIC-500 provides increased data integrity by generating and checking SCSI bus odd parity on the SCSI bus transfers. Parity may also be kept on data in the controller buffer by passing a parity bit from the AIC-500 through the buffer.

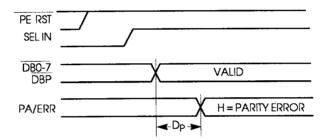

When checking SCSI bus parity, the  $\overline{PE}$  RST (pin 36) line must be held high. When a parity error occurs, the PA/ERR (pin 37) line will be asserted

(logic 1) and latched. To clear the error condition, the  $\overline{\text{PE RST}}$  (pin 36) line must be driven to a low level. Appropriate error recovery may then take place. See Figure 2 for a block diagram demonstrating this type of operation.

To pass SCSI bus parity from the AIC-500 to the controller buffer, the PE RST (pin 36) line must be in the

low state. The AIC-500 will then pass the parity bit for the data on to the controller buffer.

The AIC-500 always generates and checks SCSI bus odd parity, but the controller need not implement the parity feature. To disable parity checking by the AIC-500, the PERST (pin 37) line should be held in a logic 1 state and the PA/ERR line may be ignored.

FIGURE 2. CHECKING SCSI BUS PARITY

#### **Arbitration**

The AIC-500 complements the logic of the AIC-300 to provide maximum SCSI bus performance in all phases and to ensure conformance with the SCSI specification. The AIC-300 implements the two-wire arbitration logic, waiting for a bus free state (no  $\overline{\rm BSY}$  or  $\overline{\rm SEL}$ ) then asserts BSY and the correct SCSI bus ID.

See Figure 3 for a block diagram demonstrating the AIC-300 and AIC-500 interface of lines used during arbitration. The AIC-500 controls the timing of the lines being driven on the bus. The clock rate for the AIC-500 may vary between 2.5 MHz and 5 MHz. A 5 MHz clock input

on pin 34 will provide maximum SCSI bus performance for the AIC-500. To calculate the timings at the SCSI interface, use the following equations:

Bus Free Delay Min = T \* 3 Bus Free Delay Max = T \* 4

FIGURE 3. BLOCK DIAGRAM OF SCSI BUS ARBITRATION LOGIC

#### **ABSOLUTE MAXIMUM RATINGS**

| Ambient Temperature Under Bias            | 0°C to 70°C             |

|-------------------------------------------|-------------------------|

| Storage Temperature                       | 55°C to 150°C           |

| Voltage on Any Pin with Respect to Ground | $-0.3  V_{CC}$ to +7.0V |

| Power Dissipation                         |                         |

| Power Supply Voltage                      | 4.75 to 5.25 Volts      |

NOTE: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## D.C. CHARACTERISTICS ( $V_{cc} = 5.0V \pm 5\%$ , $V_{ss} = 0V$ , $T_{cl} = 0 \approx +70^{\circ}C$ )

| SYMBOL           | PARAMETER                                                                                         | MIN | MAX             | UNITS | CONDITIONS                                |

|------------------|---------------------------------------------------------------------------------------------------|-----|-----------------|-------|-------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage (All Except ACK)                                                                |     | 8.0             | V     |                                           |

| V <sub>IH</sub>  | Input High Voltage (All Inputs)                                                                   | 2.0 | V <sub>CC</sub> | V     |                                           |

| V <sub>IL</sub>  | Input Low Voltage (ACK)                                                                           |     | 0.6             | V     |                                           |

| V <sub>OL</sub>  | Output Low Voltage (TTL Pins)                                                                     |     | 0.4             | ٧     | I <sub>OL</sub> = 2 mA                    |

| V <sub>OL</sub>  | Output Low Voltage (SCSI Pins)                                                                    |     | 0.5             | ٧     | $I_{OL} = 48  \text{mA}$                  |

| V <sub>OH</sub>  | Output High Voltage (TTL Pins)                                                                    | 2.4 |                 | ٧     | I <sub>OH</sub> = -400 μA                 |

| 1 <sub>IL1</sub> | Input Leakage (B REQ, LO, BOE, BIE, ET, SEL OUT, BSY OUT, CD IN, 10 IN, MSG IN, PE RST, CLK, ACK) | -10 | +10             | μА    | 0 < V <sub>IN</sub> < V <sub>CC</sub>     |

| loli             | Output Leakage (B0, B1, B2, B3, B4, B5, B6, B7)                                                   | -10 | +10             | μА    | 0.45 <v<sub>ОUТ <v<sub>CC</v<sub></v<sub> |

| l <sub>OL2</sub> | Output Leakage (SEL, BSY, DB0, DB1, DB2, DB3, DB4, DB5, DB6, DB7, DB8)                            | -50 | +50             | μА    | 0.45 <v<sub>ОИТ <v<sub>СС</v<sub></v<sub> |

| V <sub>HSY</sub> | Hysteresis Voltage (ACK Only)                                                                     | 200 |                 | mV    |                                           |

| lccs             | Standby Current                                                                                   |     | 600             | μΑ    | T <sub>Q</sub> = 70°C                     |

| lcc              | Supply Current                                                                                    |     | 30              | mA    | T <sub>Q</sub> = 70°C                     |

| C <sub>IN</sub>  | Input Capacitance                                                                                 |     | 15              | рF    |                                           |

NOTE: STATIC SENSITIVE DEVICE. HANDLE WITH CARE.

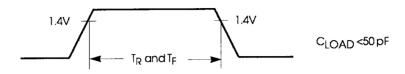

# A.C. TEST CONDITIONS ( $V_{CC} = 5.0V \pm 5\%$ , $V_{SS} = 0V$ , $T_{CC} = 0 \approx +70$ °C)

## **SCSI BUS PARITY TIMING**

| SYMBOL         | PARAMETER                         | MIN | MAX | UNITS |

|----------------|-----------------------------------|-----|-----|-------|

| D <sub>P</sub> | Data Valid to Parity Error Detect |     | 100 | ns    |

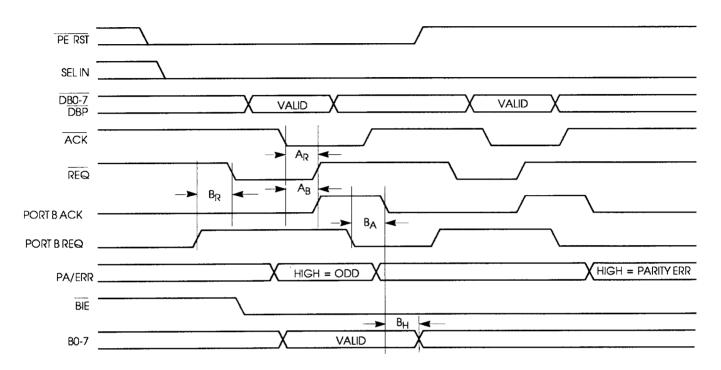

#### WRITE OPERATION

| SYMBOL         | PARAMETER                    | MIN | MAX | UNITS |

|----------------|------------------------------|-----|-----|-------|

| A <sub>R</sub> | ACK ↓ to REQ ↑               | 75  | 55  | ns    |

| A <sub>B</sub> | ACK ↓ to PORT B ACK ↑        | 75  | 50  | ns    |

| $B_R$          | PORT B REQ ↑ to REQ ↓        | 40  | 20  | ns    |

| B <sub>A</sub> | PORT B REQ                   | 40  | 25  | ns    |

| B <sub>H</sub> | PORT B ACK ↓ to Data Invalid | 75  | 40  | ns    |

The PA/ERR line in the timing diagram above shows odd parity being passed from the AIC-500 to the controller buffer when the PE RST line is held low, as it is during the first data transfer. During the second data transfer, the PE RST line is held high; therefore, the PA/ERR line indicates parity error on the SCSI bus when high.

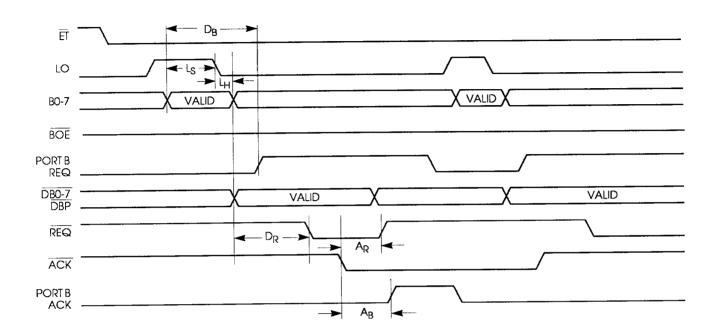

# **READ OPERATION**

| SYMBOL         | PARAMETER                         | MIN | MAX | UNITS |

|----------------|-----------------------------------|-----|-----|-------|

| L <sub>S</sub> | PORT B Data Valid to LO           | 0   |     | ns    |

| <u></u>        | LO ↓ to PORT B Data Invalid       | 25  |     | ns    |

| $A_R$          | ACK ↓ to REQ ↑                    |     | 80  | ns    |

| A <sub>B</sub> | REQ ↓ to PORT B ACK ↑             |     | 80  | ns    |

| $D_R$          | SCSI Bus Data Valid to REQ ↓      | 55  |     | ns    |

| D <sub>B</sub> | PORT B Data Valid to PORT B REQ 1 | 90  |     | ns    |

## **PACKAGING INFORMATION**