**PRELIMINARY**

## **Buffer Data Management**

- Buffer Sizes From 256 To 64K Bytes

- Buffer Size Of 16K Bytes Accessed Directly

- DMA Handshake Logic

- Supervises Data Transfers

To Buffer With Overrun

Control

- Dual-Port Circular FIFO Buffer Control

- Port Priority Resolver Resolves Host/Peripheral Requests

#### **SCSI** Interface

- Arbitration Logic Allows Stacking

- Programmable Request For Arbitration While SCSI Bus In Busy State

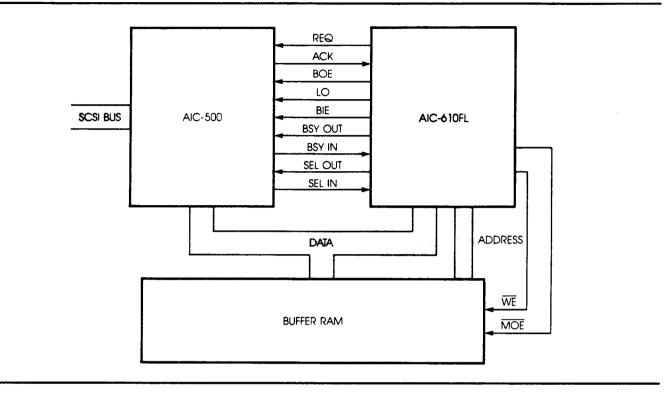

- Simplified SCSI Interface Implementation With AIC-500 SCSI Interface Adapter

#### Peripheral Data Controller

- Controls Embedded, ST412/506, ESDI, And SMD Interface Hard Disk Drives

- Works With All Disk Encoding Schemes

- User-Modifiable RAM-Based Control Store

- User-Programmable Internal 32-Bit, 48-Bit ECC Polynomial, And 16-Bit CRC, Or Variable Length External Polynomial

- Transfer Rate Up To 15 Mbits/Sec

- Soft- Or Hard-Sector Drives

- Multiple Sector Transfer

- Sector-Level Defect Handlina

- Noninterleaved Operation

- User-Programmable

Sector Length Up To A Full

Track

#### Processor Interface

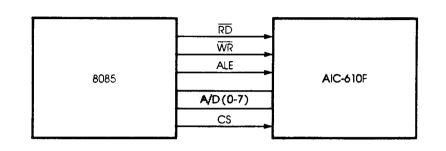

- Multiplexed Address/ Data Bus Interface

- Interrupt Driven Operation

#### **Technologies**

- CMOS

- Software Compatible With AIC-011/AIC-301

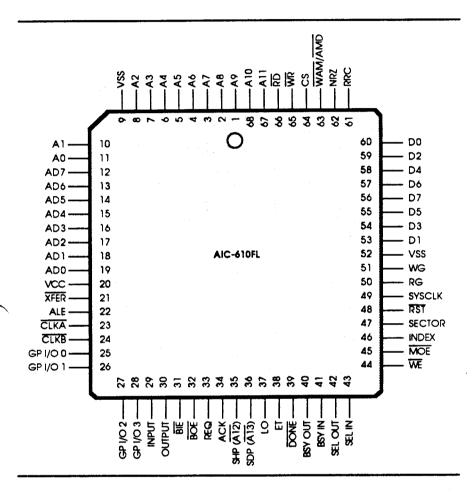

- 68 Pin PLCC

<sup>©</sup> Copyright Adapted, Inc. 1986, 1987, 1988. All rights reserved. User is licensed to make copies of software contained in this document for use with parts manufatured by Adapted, and for no other use. The information contained in this data sheet is subject to change without notice. No part of this document may be copied or reproduced in any form without prior written consent from Adapted, Inc.

#### **OVERVIEW**

The Adaptec AIC-610F Integrated Programmable Storage Controller (IPSC) provides the major portion of the functions that are necessary to implement a high-performance disk or tape controller or an intelligent disk drive. The functions of the AIC-610F can be categorized as a serial data transfer controller responsible for data transfer to and from the peripheral, and a buffer management controller responsible for data transfer to and from the buffer memory. In addition, the AIC-610F has been designed for easy interface to support processors and the SCSI host bus.

The AIC-610F is capable of supporting most drive interfaces, including Embedded, ST412/506, ESDI, and SMD. In other words, the AIC-610F can be used with 3-1/2 inch, 5-1/4 inch, and 8 inch hard drives; and either floppy, optical, or tape drives.

The AIC-610F has a fully userprogrammable RAM-based sequencer, which allows for a flexible mode of operation, full compatibility with various drives, and also allows user-defined specialized track formats.

The AIC-610F performs ECC/CRC generation, checking and correction. The error correction algorithm used by the AIC-610F is user-programmable with a 32-bit or 48-bit PRESET or RESET ECC polynomial, or an external variable length polynomial.

The IPSC also performs serialization and deserialization of peripheral data and has search and verify capabilities.

On the buffer management side, the AIC-610F allows low cost static RAM to be used as a dual-port circular FIFO. The AIC-610F supervises data transfers to the buffers, thereby reducing the possibility of overruns while allowing high-speed DMA transfers.

The chip also implements a twowire arbitration circuit for resolving host peripheral requests by giving the priority to the peripheral and placing a hold on the host. Finally, the AIC-610F is interrupt-based, allowing for a more efficient data transfer mechanism.

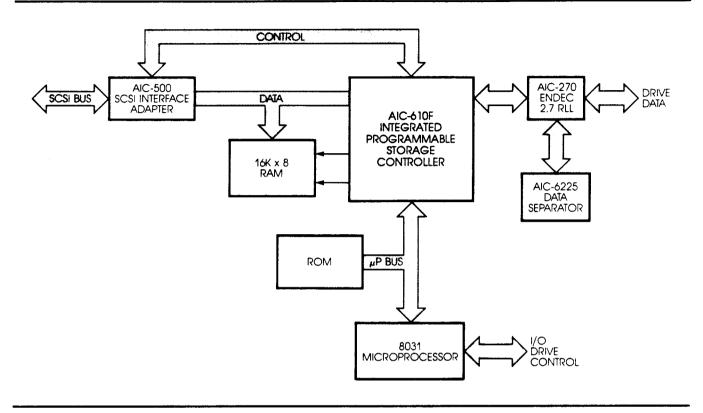

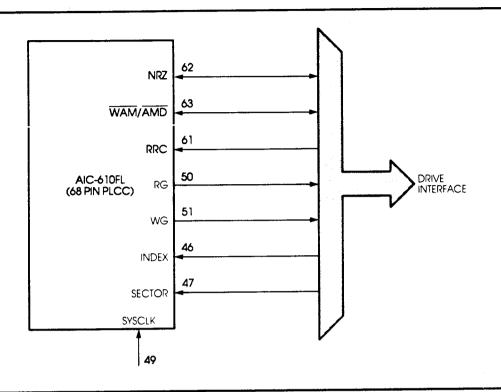

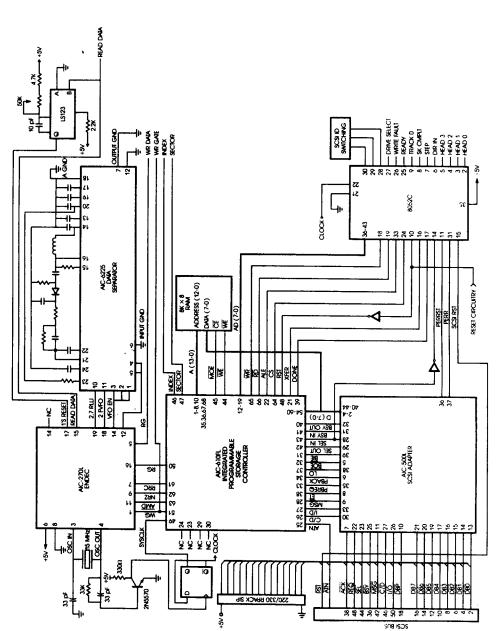

Based on the functions discussed above, the AIC-610F forms the core of a three-chip set: the AIC-610F IPSC, the AIC-270 (or AIC-250) ENDEC, and the AIC-6225 Data Separator. These chips, combined with the necessary drivers and receivers (i.e., the AIC-500, providing the necessary SCSI Interface) and a low-cost microprocessor, provide all that is required to implement a high-performance, full-featured controller.

The AIC-610F controls read/write functions for a mass storage device. The AIC-610F provides serialization/deserialization, formatting, function sequencing, and error processing. In addition, the chip provides a dual-ported buffer management control function in systems requiring the use of a buffer between the host bus and the controller due to available bus bandwidth.

The AIC-250 provides the write precompensation, write address mark/address mark detect, and NRZ to/from MFM conversion functions required in ST412/506-type drive interface applications. The AIC-270 differs in the encode/decode scheme, providing NRZ to/from 2,7 RLL code conversion functions. This method of encoding can increase the effective capacity and data transfer rate of a drive by as much as 100%.

The AIC-6225 Data Separator provides the complete data separator function, allowing the clock signal to be separated from the data. The AIC-6225 requires no adjustments and has selectable outputs of synchronized data for RLL codes or decoded MFM (NRZ).

The AIC-500 provides the necessary drivers and receivers to interface the AIC-610F directly to the SCSI bus.

Finally, the AIC-610F is designed to work with either a local processor or a host processor. The choice is up to the designer and is a function of the host system's available bus bandwidth and board space design considerations. Accordingly, the microcode for the control of the AIC-610F will be based in system RAM or on a local (EP)ROM.

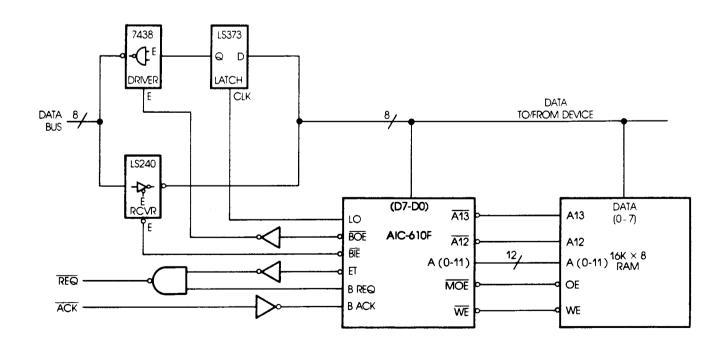

Figure 1 illustrates a typical application of the AIC-610F controller used with an AIC-270 ENDEC, an AIC-6225 data separator, an AIC-500 SCSI interface adapter, a processor, ROM, and a 16K x 8 RAM buffer for a SCSI controller.

FIGURE 1. AIC-610F BASED SCSI CONTROLLER

TABLE 1. PIN DESCRIPTION

| MICROPROCESSOR INTERFACE SIGNALS |                                                                                                                                                                                                                                                        |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SYMBOL                           | PIN                                                                                                                                                                                                                                                    | TYPE                                                                                                                             | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| A/D0-7                           | 12-19                                                                                                                                                                                                                                                  | 1/0                                                                                                                              | MULTIPLEXED ADDRESS/DATA: These are three-state address/data lines which interface with a multiplexed microprocessor address/data bus.                                                                                                                                                                                         |  |  |  |  |

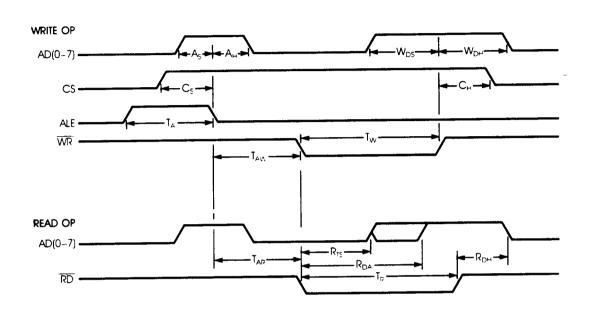

| ALE                              | 22                                                                                                                                                                                                                                                     | IN                                                                                                                               | ADDRESS LATCH ENABLE: This control signal latches the address on the A/D0-A/D7 lines and identifies the bits as a register address.                                                                                                                                                                                            |  |  |  |  |

| XFER                             | 21                                                                                                                                                                                                                                                     | OUT                                                                                                                              | DATA TRANSFER/STOPPED INTERRUPT: Indicates the start of the data transfer to or from the buffer memory or a stopped condition.                                                                                                                                                                                                 |  |  |  |  |

| DONE                             | 39                                                                                                                                                                                                                                                     | OUT                                                                                                                              | DMA DONE INTERRUPT: Occurs when the Read Access Pointer (RAP) = Stop Pointer (SP) during a read cycle, or when Write Address Pointer (WAP) = SP during a DMA write cycle. This indicates completion of the host data transfer and allows the microprocessor to do the necessary function of updating the SP if it is required. |  |  |  |  |

| CS                               | 64                                                                                                                                                                                                                                                     | IN                                                                                                                               | CHIP SELECT: Active high input, used to select the chip during processor bus cycle access.                                                                                                                                                                                                                                     |  |  |  |  |

| WR                               | 65                                                                                                                                                                                                                                                     | iN                                                                                                                               | VRITE: Signal from the microprocessor to enable data to be written from the Abus to a specified register.                                                                                                                                                                                                                      |  |  |  |  |

| RD                               | 66                                                                                                                                                                                                                                                     | IN                                                                                                                               | READ: Signal from the microprocessor to enable data from a specified register out onto the A/D bus.                                                                                                                                                                                                                            |  |  |  |  |

| RST                              | 48                                                                                                                                                                                                                                                     | IN                                                                                                                               | RESET: A low input sets an internal reset latch that stops all operations within the chip and deasserts RG, WG, WAM, and NRZ outputs. Registers $50_{\rm H}$ through $7E_{\rm H}$ are reset. All special outputs are set to the high state.                                                                                    |  |  |  |  |

|                                  |                                                                                                                                                                                                                                                        | ,                                                                                                                                | BUFFER INTERFACE                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| A0-A11                           | 1-8<br>10-11<br>67-68                                                                                                                                                                                                                                  | applications with less than or equal to 14 bits of addressing. In applications with less than or equal to 14 bits of addressing. |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SHP/A12                          | 35 OUT STROBE HOST POINTER: Buffer address bit 12 in applications with buffer size or less addressing. This is the clocking signal for loading high-order address an external host address register in applications using more than 14-bit addressing. |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SDP/A13                          | 36                                                                                                                                                                                                                                                     | OUT                                                                                                                              | STROBE DEVICE POINTER: Buffer address bit 13 in applications with buffer size of 14-bit or less addressing. This is the clocking signal for loading high-order address bits into external device address register in applications using more than 14-bit addressing.                                                           |  |  |  |  |

| D0-D7                            | 53-60                                                                                                                                                                                                                                                  | 1/0                                                                                                                              | DATA BUS: Byte parallel data lines to and from the buffer. These lines are tri-stated at the rising edge of ALE.                                                                                                                                                                                                               |  |  |  |  |

| WE                               | 44                                                                                                                                                                                                                                                     | OUT                                                                                                                              | WRITE ENABLE: Asserting WE enables data to be written into the RAM buffer.                                                                                                                                                                                                                                                     |  |  |  |  |

TABLE 1. PIN DESCRIPTION (Continued)

|                                                                                     |     |                                                                                                     | BUFFER INTERFACE (Continued)                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL                                                                              | PIN | TYPE                                                                                                | NAME AND FUNCTION                                                                                                                                                                                                                                                 |

| MOE                                                                                 | 45  | OUT                                                                                                 | MEMORY OUTPUT ENABLE: Enables data to be read from RAM buffer.                                                                                                                                                                                                    |

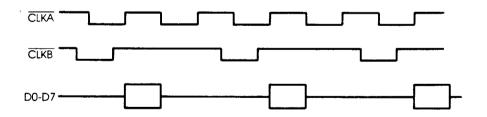

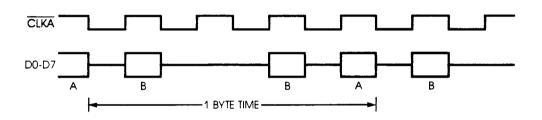

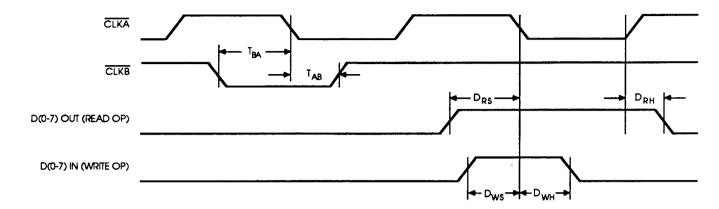

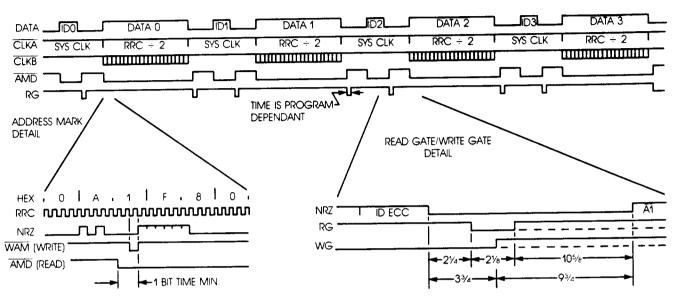

| CLKA                                                                                | 23  | 1/0                                                                                                 | CLOCK A: During a read or write operation, the output of this signal is derived from the input RRC. Otherwise, it is derived from the input SYSCLK. The relationship between the input clock and CLKA is controlled by the contents of Register 7F <sub>H</sub> . |

| CLKB                                                                                | 24  | 1/0                                                                                                 | CLOCK B: A pulse which overlaps the negative edge of CLKA and occurs whenever a byte is transferred to/from data bus pins D0-D7.                                                                                                                                  |

|                                                                                     |     |                                                                                                     | SYSTEM BUS INTERFACE                                                                                                                                                                                                                                              |

| BIE                                                                                 | 31  | OUT                                                                                                 | BUS IN ENABLE: Used to gate data out of external latches from the bus for writing into the buffer.                                                                                                                                                                |

| BOE                                                                                 | 32  | OUT                                                                                                 | BUS OUT ENABLE: Used to gate data out of external latches for transfer onto the bus. Asserted when arbitration latch is set.                                                                                                                                      |

| REQ                                                                                 | 33  | OUT                                                                                                 | REQUEST: The request for a data transfer to or from the buffer (DMA Handshake).                                                                                                                                                                                   |

| ACK                                                                                 | 34  | IN                                                                                                  | ACKNOWLEDGE: Used to acknowledge data has been received from or sent to the buffer (DMA Handshake).                                                                                                                                                               |

| LO                                                                                  | 37  | ОИТ                                                                                                 | LATCH OUT: Used to clock data into external latches after reading from buffer.                                                                                                                                                                                    |

| BSY OUT                                                                             | 40  | OUT                                                                                                 | BUSY OUT: Either set directly by the microprocessor or in an arbitration request mode the BSY OUT will be activated when BSY IN and SEL IN are inactive. The arbitration mode assures an arbitration phase.                                                       |

| BSY IN                                                                              | 41  | IN                                                                                                  | BUSY IN: Active when other devices are actively accessing the bus.                                                                                                                                                                                                |

| SEL OUT                                                                             | 42  | OUT                                                                                                 | SELECT OUT: This pin is used to request selection by the host bus. SEL OUT is set by the microprocessor setting Bit 6, Register 52 (Channel Control).                                                                                                             |

| SEL IN                                                                              | 43  | IN                                                                                                  | SELECT IN: Active indicates a bus select status. SEL IN will reset the arbitration latch.                                                                                                                                                                         |

|                                                                                     |     |                                                                                                     | PERIPHERAL INTERFACE SIGNALS                                                                                                                                                                                                                                      |

| INDEX 46 IN INDEX: input for the index pulse received from the poof nine bits wide. |     | INDEX: Input for the index pulse received from the peripheral. Must be a minimum of nine bits wide. |                                                                                                                                                                                                                                                                   |

| SECTOR                                                                              | 47  | IN                                                                                                  | SECTOR: Input for the sector pulse received from drives that are hard-sectored.<br>Must be minimum of nine bits wide.                                                                                                                                             |

| RG                                                                                  | 50  | ОИТ                                                                                                 | READ GATE: Enables the external phase-lock loop to lock onto the read data stream coming from the storage device.                                                                                                                                                 |

| wG                                                                                  | 51  | OUT                                                                                                 | WRITE GATE: Is used to enable or gate the writing of NRZ data out to the storage device.                                                                                                                                                                          |

TABLE 1. PIN DESCRIPTION (Continued)

| PERIPHERAL INTERFACE SIGNALS (Continued) |                                                                                                                                                                                                                                              |      |                                                                                                                                                                                                                                                    |  |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYMBOL                                   | PIN                                                                                                                                                                                                                                          | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                  |  |  |  |

| RRC                                      | 61                                                                                                                                                                                                                                           | IN   | READ REFERENCE CLOCK: A multiplexed input sourced from the VFO oscillator during read gate. Otherwise from the write oscillator. This is the primary clock for the AIC-610 and must be present at all times, including during the reset operation. |  |  |  |

| NRZ                                      | 62                                                                                                                                                                                                                                           | 1/0  | NRZ: Read data input from the storage device when RG is active. Write data to the storage device when WG is active.                                                                                                                                |  |  |  |

| WAM/AMD                                  | 63                                                                                                                                                                                                                                           | 1/0  | WRITE ADDRESS MARK/ADDRESS MARK DETECT: A one-bit wide pulse is output when write gate is active and an address mark is to be written. When read gate is active, a low level input to indicate address mark detect.                                |  |  |  |

|                                          |                                                                                                                                                                                                                                              |      | MISCELLANEOUS SIGNALS                                                                                                                                                                                                                              |  |  |  |

| GP I/O 0<br>or WR 6E                     | 25                                                                                                                                                                                                                                           | 1/0  | GENERAL PURPOSE I/O LINE 0: A user-programmable I/O line for use as an input or an output. This pin can also be programmed as a decoded output for a write to address 6E <sub>H</sub> .                                                            |  |  |  |

| GP <u>I/O 1</u><br>or RD 6E              | 26                                                                                                                                                                                                                                           | 1/0  | GENERAL PURPOSE I/O LINE 1: A user-programmable I/O line for use as an input or an output. This pin can also be programmed as a decoded output for a read from address 6E <sub>H</sub> .                                                           |  |  |  |

| GPI/O3<br>or WR6F                        | 27                                                                                                                                                                                                                                           | 1/0  | GENERAL PURPOSE I/O LINE 2: A user-programmable I/O line for use as an input or an output. This pin can also be programmed as a decoded output for a write to address 6F <sub>H</sub> .                                                            |  |  |  |

| GP 1/O 3<br>or RD 6F                     | 28                                                                                                                                                                                                                                           | 1/0  | GENERAL PURPOSE I/O LINE 3: A user-programmable I/O line for use as an input or an output. This pin can also be programmed as a decoded output for a read from address 6F <sub>H</sub> .                                                           |  |  |  |

| INPUT                                    | 29                                                                                                                                                                                                                                           | IN   | INPUT PIN: The state of this pin is sampled by reading Register 7E <sub>H</sub> , Bit 4. The input pin is also a branch input to the sequencer RAM.                                                                                                |  |  |  |

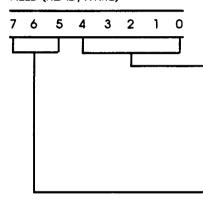

| OUTPUT                                   | JTPUT 30 OUT OUTPUT PIN: Controlled by bit 2 of the control block (AO <sub>H</sub> thru B7 <sub>H</sub> ) of the RAM. It can be used to monitor the sequencer RAM or synchronize exter circultry to a particular state of the sequencer RAM. |      | OUTPUT PIN: Controlled by bit 2 of the control block ( $A0_H$ thru $B7_H$ ) of the sequencer RAM. It can be used to monitor the sequencer RAM or synchronize external circuitry to a particular state of the sequencer RAM.                        |  |  |  |

| ĒĪ                                       | 38                                                                                                                                                                                                                                           | ОИТ  | ENABLE TARGET: A microprocessor settable signal to enable the target.                                                                                                                                                                              |  |  |  |

| SYSCLK                                   | 49                                                                                                                                                                                                                                           | IN   | SYSCLK: A clock input used to derive the CLKA output when not reading or writing data. SYSCLK must be present whenever the AIC-610 is to be used in any way.                                                                                       |  |  |  |

| V <sub>SS</sub>                          | 9,52                                                                                                                                                                                                                                         | GND  | GROUND.                                                                                                                                                                                                                                            |  |  |  |

| V <sub>CC</sub>                          | 20                                                                                                                                                                                                                                           | PWR  | +5 Volts.                                                                                                                                                                                                                                          |  |  |  |

### **FUNCTIONAL DESCRIPTION**

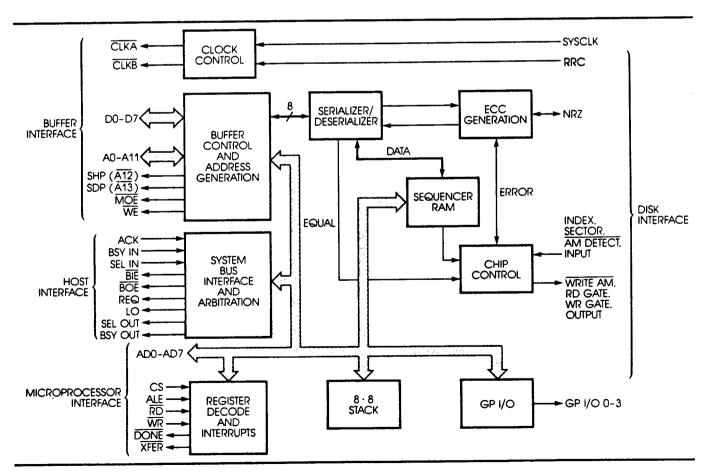

Internal to the AIC-610F Integrated Programmable Storage Controller chip are four main functional blocks:

- Microprocessor Interface

- Peripheral Data Control

- Sector Format Sequencer

- Data Flow

- Buffer Management

- Buffer Control

- Priority Resolver

- DMA Control

- System Bus Interface

- Arbitration

# Microprocessor Interface

The microprocessor Interface is an eight-bit multiplexed bus such as is found on the Intel 8085 family of processors. Other microprocessors (the Z80 or the 6800) can be utilized by multiplexing their address and data lines, and generating the necessary control lines. With some external circuitry, a 16-bit multiplexed or separate address and data bus can also be supported.

The AIC-610F decodes addresses from  $50_{\rm H}$  to  ${\rm FF_{H_{\perp}}}$  in order to prevent erroneous operation, no other addresses are used. The device architecture is structured to allow the firmware of the processor to determine what functions are to be incorporated in the control unit design.

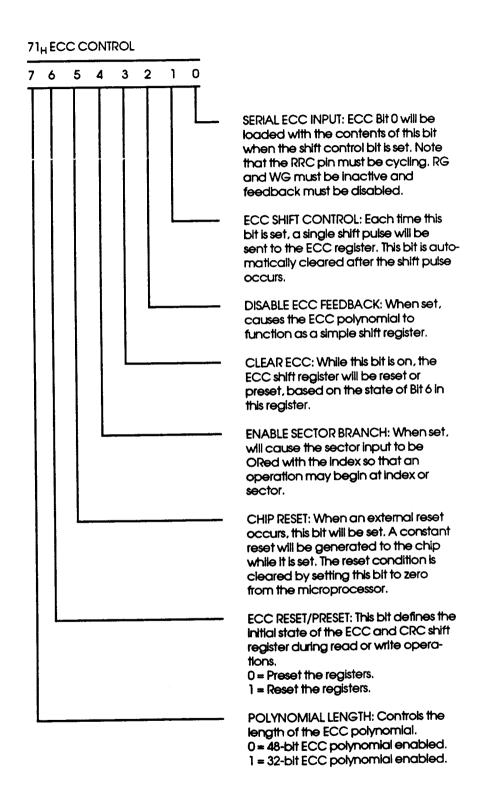

The user has the ability to select the ECC or CRC for Error Detection and Correction (EDAC). Furthermore the user may select the ECC polynomial that is optimum for the media and the encoding scheme being used. The AIC-610F provides an internal 32-bit or 48-bit programmable ECC capability. The user can also use an external variable length ECC if required. The standard 16-bit CRC is used for error detection and is typically used on ID fields or with floppy and tape devices. Note: The CRC and ECC may be initialized with a reset or preset (Register 71<sub>H</sub>, Bit 6).

# Peripheral Data Control

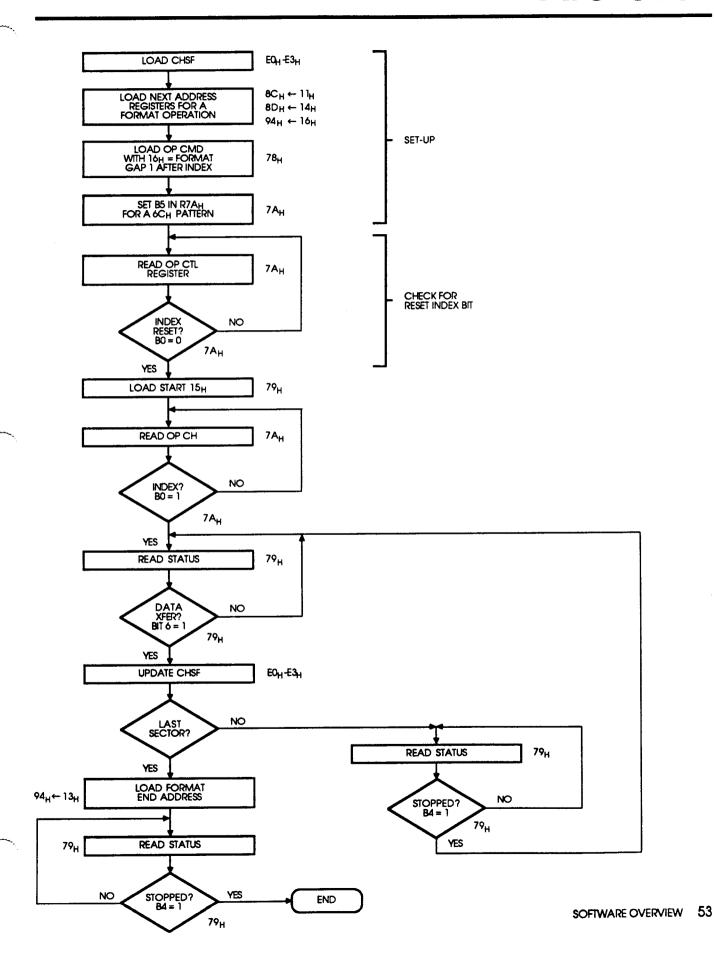

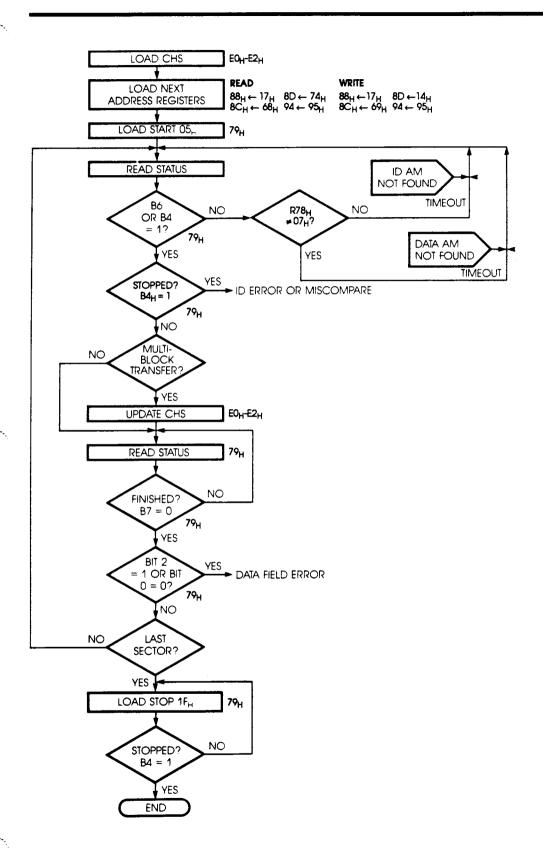

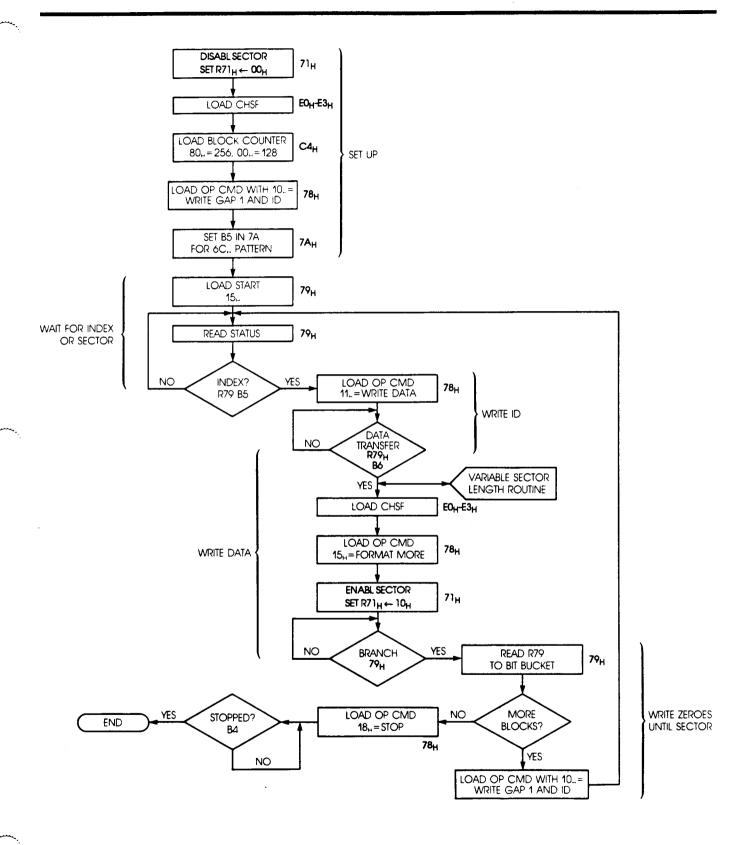

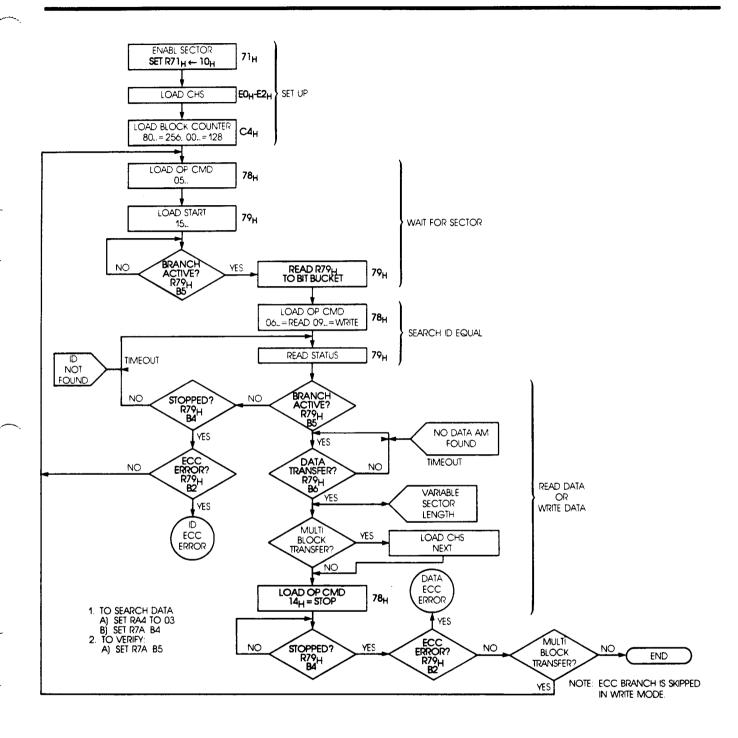

SECTOR FORMAT SEQUENCER: The sector format sequencer performs the basic sequencing function for a mass storage device which includes:

- Read ID

- Read ID and Read Data (or Read Operation)

- Read ID and Write Data (or Write Operation)

- Write ID and Write Data (or Format Operation)

These functions can be modified to perform the search data and verify data functions.

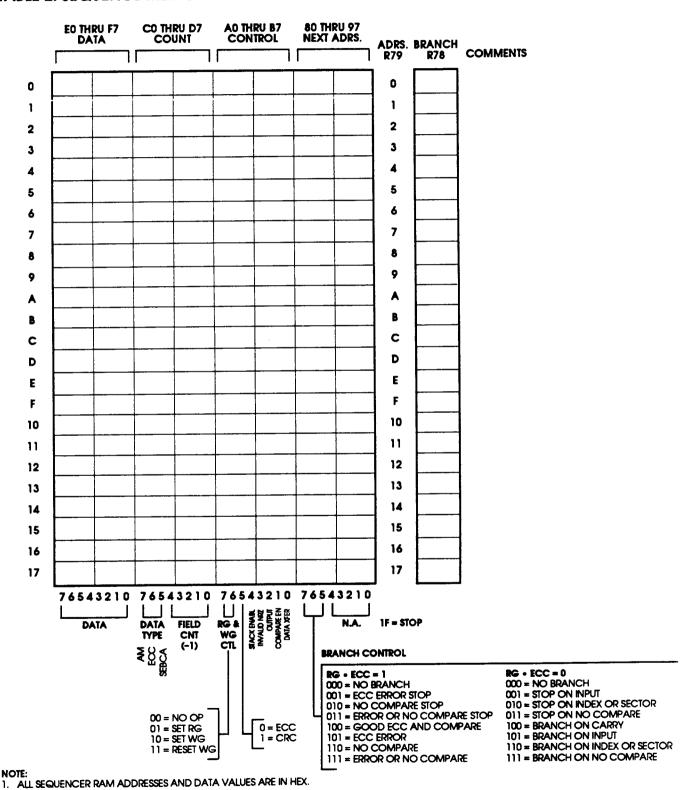

The sequencer consists of 96 bytes of RAM, organized as a 24 x 4 byte matrix. These locations have to be set-up at initialization time for the proper operation of the chip. Under firmware control, the AIC-610F can be made to sequence through different types of operations. The user can control the timing relationships between various output signals and can monitor the different input lines to branch to various sequencer locations.

The controller chip also has other registers that can be used to control the definition of the track format. Using these registers, features such as gap length, sync characters, and ECC polynomiais, can be controlled. The track layout (sector size and sector data fill character) can also be flexibly defined.

FLOW: DATA The data flow portion of the controller chip is composed of the ECC logic and a serializer/deserializer. Data to be written to the peripheral enters the device in 8-bit parallel format. The data is serialized and run through an ECC generator. The AIC-610F outputs NRZ serial bits. The bits include serialized constants required for address marks, gaps, and ID fields, as well as serialized data and ECC generator output.

# Buffer Management

When used in a CPU environment, the AIC-610F will work well with the DMA control devices available to provide host processor memory addressing. The next three paragraphs describe its ability to support this function.

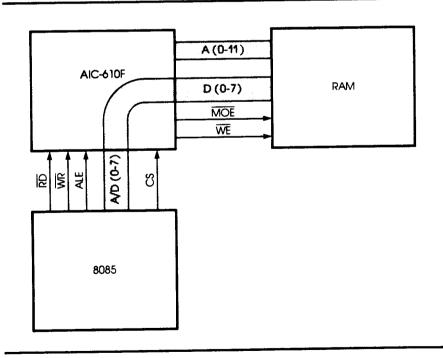

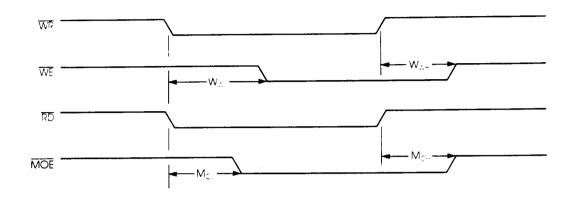

**BUFFER** CONTROL: The buffer control function provides read and write address registers, <u>as well</u> as Memory Outp<u>ut Enable</u> (MOE) and Write Enable (WE) signals. These signals are used to read or write data from the RAM buffer.

PRIORITY RESOLVER: The priority resolver allows the typically syn-

chronous peripheral to have priority over the host requests. This is crucial in peripheral controller applications where, in a 10 Mb/sec system, a data byte must be transferred exactly once every 800 nsecs.

DMA CONTROL: The DMA control generates a request to the host (REQ), gates the appropriate data into or out of the buffer, and walts for a correctly timed acknowledge (ACK).

# System Bus Interface

The AIC-610F has the necessary signals to interface to a host or

system bus. It also provides logic to arbitrate for the system bus.

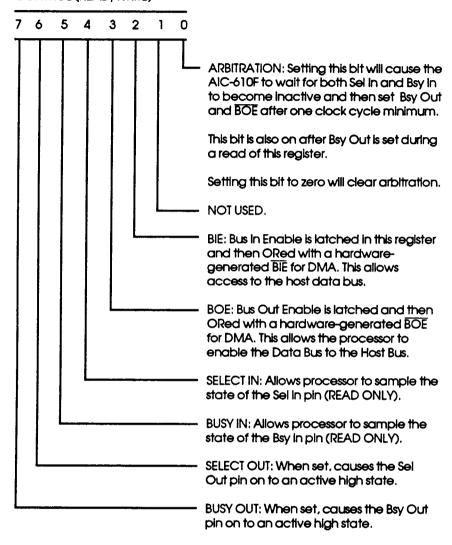

ARBITRATION: The arbitration logic of the AIC-610F provides for a two-wire arbitration scheme where either Select In or Busy In indicate a system bus busy state. The device allows for a request to be stacked for arbitration when the bus is in the bus busy state. The arbitration logic will request the bus for arbitration when both Select in and Busy In are inactive for a minimum of one clock time.

Figure 2 is a block diagram of the AIC-610F which identifies the different functional blocks.

FIGURE 2. FUNCTIONAL BLOCK DIAGRAM

#### **FUNCTIONAL OPERATION**

The functional operation of the AIC-610F can be broken down into two parts. The first portion is the control of data to and from the peripheral. This involves the support processor, sequencer RAM, and various registers to exercise the necessary peripheral data control operation. The other portion is the buffer management of data to and from the buffer.

# Peripheral Data Path Control

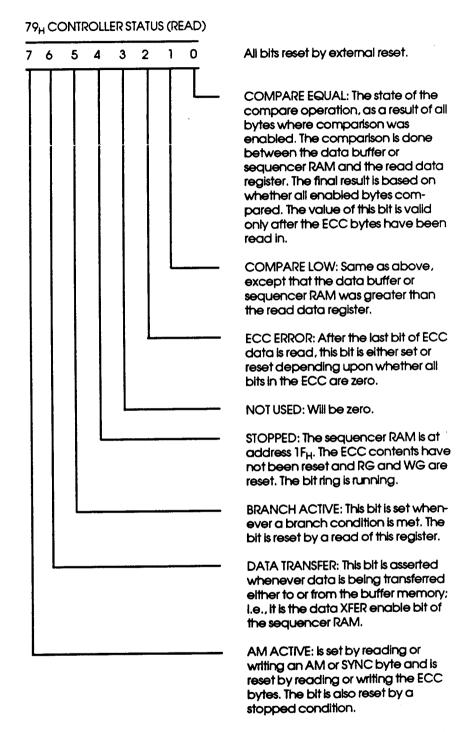

The control of data to and from the peripheral is controlled by the contents of the sequencer RAM. The sequencer RAM consists of 96 bytes, organized as 24-by-four words. The four bytes can be broken down into Data, Count, Control, and Next Address Fields. The operation of the AIC-610F revolves around the branch register (Register  $78_{H}$ ) and the status/start register (Register 79H). Register 79<sub>H</sub> is first loaded with the address where the sequencer is to begin execution. Thereafter, the AIC-610F sequences through the RAM and the next address is executed. If a successful branch condition occurs, the next address based on the contents of Register 78<sub>H</sub>. Otherwise, it is based on the contents of the next address field at that address. By setting different branch conditions, based on internal or external events, the chip can be made to sequence through different operations.

The AIC-610F also has a stack that is eight-bytes deep. By enabling the stack during a read process, information read from the drive can be pushed on to the stack. These bytes can then be popped

by the microprocessor at a lower speed to examine ID fields and similar information.

During a read process from the peripheral, the AIC-610F has the ability to compare the data being received on a byte-for-byte basis with Information found in other locations. When looking for the ID field, the data received is compared to the byte in the data field of the sequencer RAM. This feature is also used during a data field search operation where the information is compared to the data in the external buffer.

If an error is detected after a read data operation, the syndrome is saved in an ECC register and will not be reset until a new read operation is started. For EDAC, Bit 5 of the control field  $(A0_{HC}B7_{H})$ determines if CRC or ECC is to be used. Registers 71<sub>H</sub>-77<sub>H</sub> control the ECC function. Using these registers, the processor can determine if the error is correctable and calculate the error pattern and displacement from the beginning of the sector. After the error pattern is determined, it is used to correct data bytes in the RAM buffer. The recommended 32-bit ECC polynomial is a computer selected pattern that will correct eight-bit single burst errors. A 48-bit ECC polynomial is available under a license agreement from Adaptec.

The internal operations of the AIC-610F are driven by the Read Reference Clock (RRC). The functions of the AIC-610F are based on the Bit-Ring oscillator. Once the AIC-610F synchronizes with the byte boundary of the incoming bit stream, Bit-Ring 0 will correspond to the first bit (LSB) in each byte.

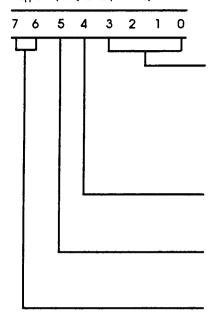

Based on the RRC and SYSCLK Inputs, the AIC-610F generates and drives CLKA. During actual data transfers between the AIC-610F and the storage device, CLKA is derived from the RRC. At all other times, CLKA is derived from the SYSCLK Input. The relationship between CLKA and RRC or SYSCLK is based on the contents of the clock control register (Register 7FH). NOTE: The frequency of SYSCLK has no bearing on the processor interface.

CLKA and CLKB are used internally to generate the external RAM buffer address. CLKB should be interpreted as the beginning of a controller chip memory access with a CLKA period equal to RAM cycle access time. The data bus D(7-0) will contain valid data when CLKA is high. The following section on data buffering and transfers explains this operation in detail.

CLKA and CLKB can also be input signals, thus allowing the AIC-610F to function as a buffer controller. This is particularly applicable when there are two controllers on one board, such as an AIC-610F and an AIC-010 Controller. In this case, the AIC-010 clock outputs (CLKA and CLKB) can drive the buffer management functions of the AIC-610F.

Table 2 shows the sequencer RAM which is located from address  $80_H$  to  $FF_H$ . A copy of this table can be used by the user as a worksheet to modify the given sequencer maps or generate a new map based on specific requirements.

**TABLE 2. SEQUENCE MEMORY BIT MAP**

# Buffer Management

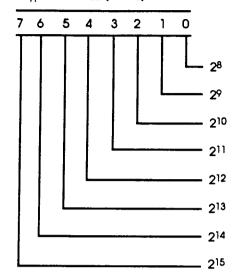

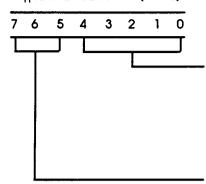

The AIC-610F can manage buffer sizes from 256 bytes to 64K bytes. The AIC-610F has the necessary registers for DMA control, buffer size, and stop pointers. It also provides the Memory Output Enable (MOE) signal and Write Enable (WE) signal. The AIC-610F has two modes of operation of up to 16K addressing and up to 64K addressing.

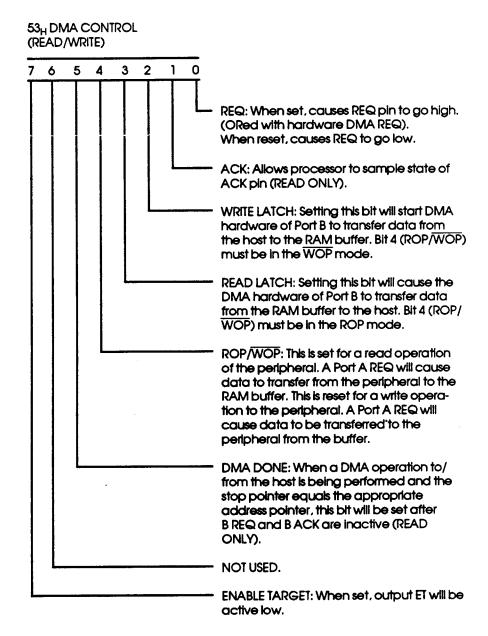

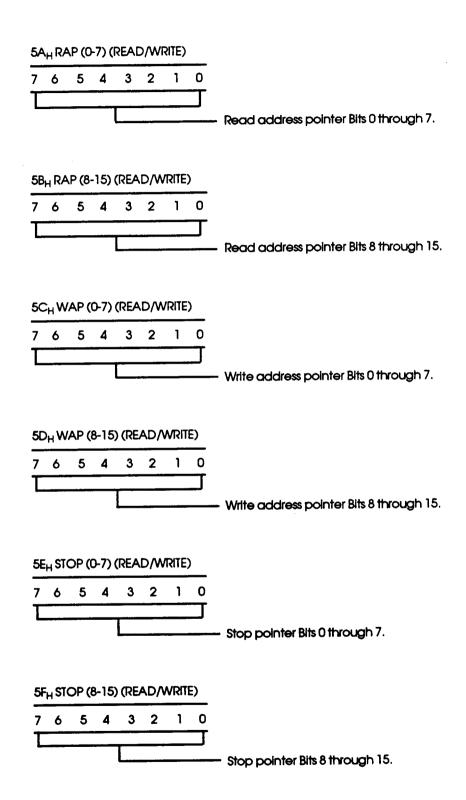

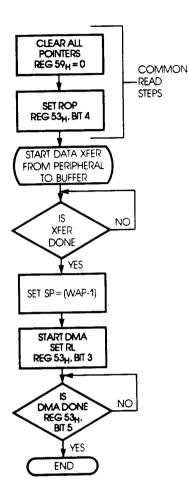

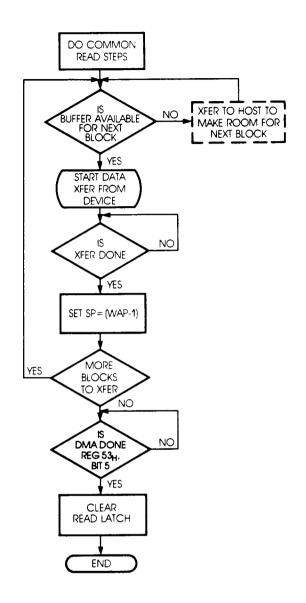

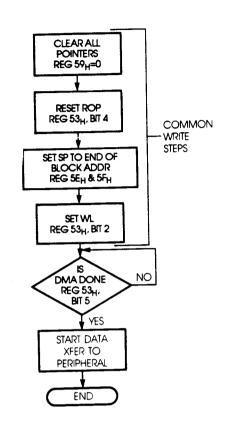

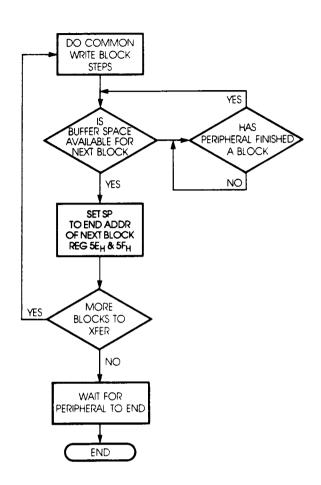

The ROP/ $\overline{\text{WOP}}$  bit (Read Operation/Write Operation Register 53<sub>H</sub>, Bit 4) controls the direction of data transfer. The WAP registers contain the Write Address Pointer. The RAP registers contain the Read Address Pointer. The SP registers contain the Stop Pointer. The relation of these pointers is described by explaining the actual mechanism of data transfers.

The effectiveness of a controller design is based on its ability to transfer data to and from the peripheral as fast and as accurately as physically possible through Error Detection and Correction (EDAC).

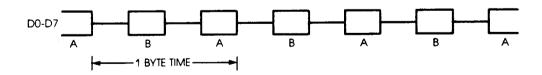

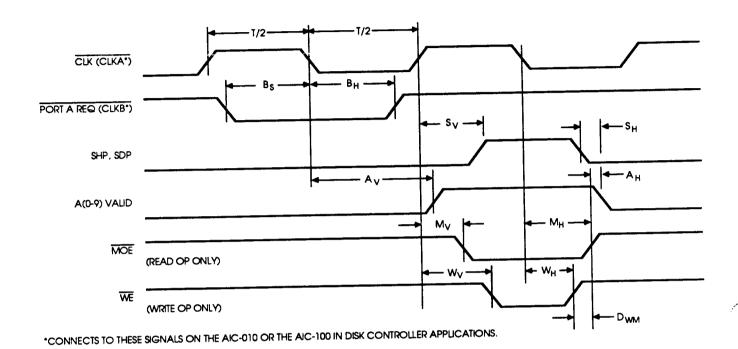

PORT A TRANSFER: The data byte transferred between the AIC-610F and the RAM buffer is called a Port A transfer. Since the drive is continuously spinning during a read or write operation, a byte has to be transferred from/to the AIC-610F controller chip every 800 ns (10 MHz operation). The AIC-610F chip either indicates the availability of a byte (during peripheral read) or requests a byte (during peripheral write), once every bytetime through the CLKB line. The appropriate address in the RAM is generated by the AIC-610F from a set of pointers present in the chip.

For a read operation from the peripheral, the ROP/WOP bit must be set. The contents of the WAP registers (Registers 5C<sub>H</sub> and 5D<sub>H</sub>) are used to select the buffer address, and WE is used to write information into the buffer.

For a write operation to the peripheral, the ROP/WOP bit must be reset. The RAP registers are used to generate the buffer address, and data is read when MOE is active. The AIC-610F samples the data from the buffer RAM at the falling edge of CLKA following a Port A REQ (CLKB).

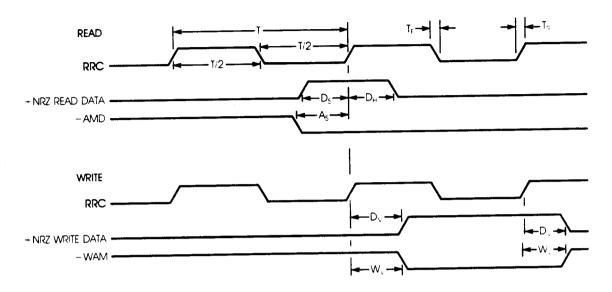

FIGURE 3. AIC-610F PORT A DATA BYTE TRANSFER TIMING

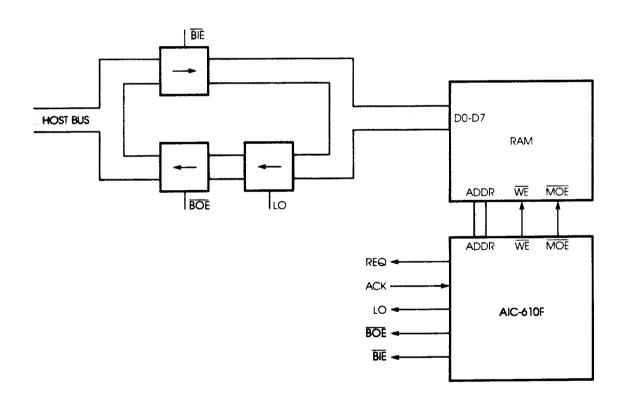

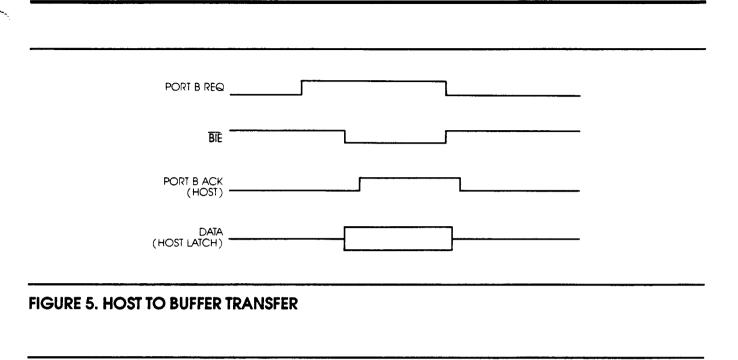

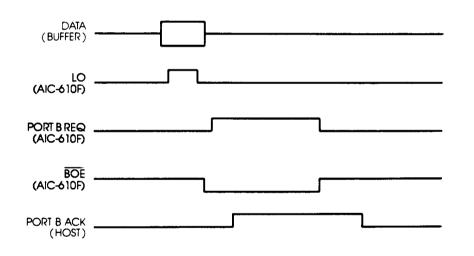

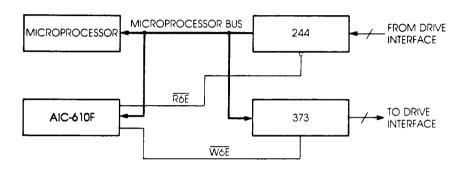

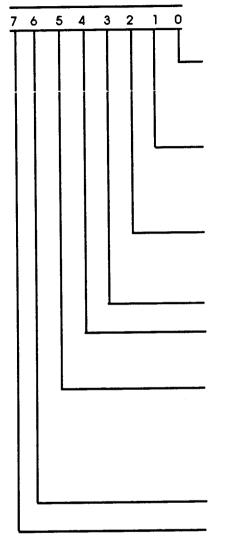

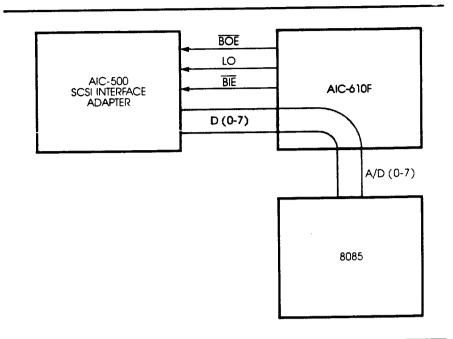

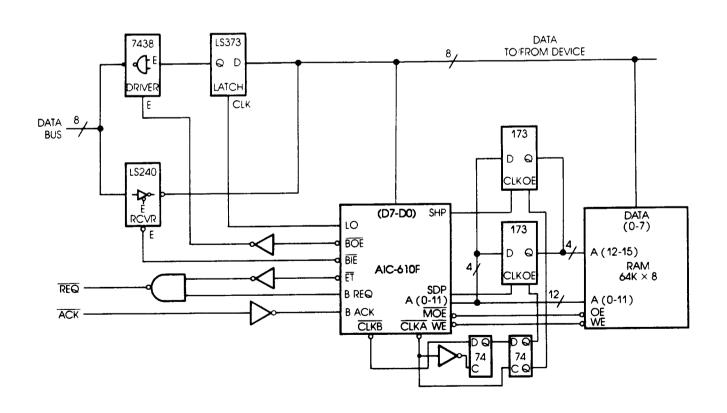

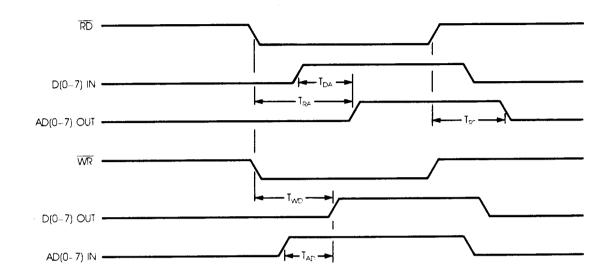

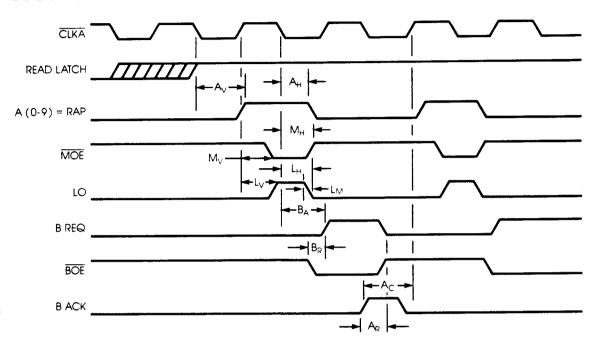

PORT B TRANSFER: The data transfer between the RAM buffer and the host is initiated and controlled by the AIC-610F and is referred to as Port B transfer. The AIC-610F generates the necessary request signal (REQ), RAM buffer address, and control signals. It also generates the host bus latch control signals. The block dlagram is shown in Figure 4. The AIC-610F uses the Request signal (REQ) to initiate the transfer which is completed after an Acknowledge (ACK) is received.

If the ROP/WOP bit (Register 53H. Bit 4) is set and the Read Latch is on (Register 53<sub>H</sub>, Bit 3), then data is transferred from the buffer to the host. The contents of the RAP reg-Isters (Registers 5A<sub>H</sub> and 5B<sub>H</sub>) are used to generate the addresses. The data is latched out into an external latch with the LO signal and then BOE signal enables the data to the host bus. A Request (REQ) is sent to the host. After an Acknowledge (ACK) is received. the BOE is deasserted.

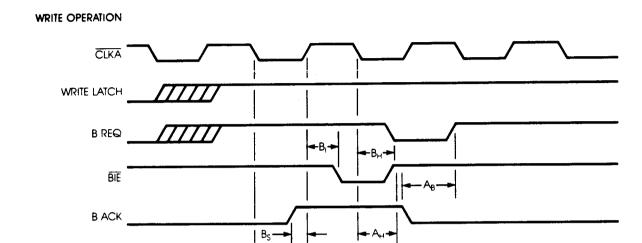

If the ROP/WOP bit is reset and the Write Latch is on (Register 53H, Bit 2), then data is transferred from the host bus to the buffer. The contents of the WAP registers (Registers  $5C_H$  and  $5D_H$ ) are used to generate the buffer address. The BIE line is asserted to enable an external receiver.

The relationships among the different control signals during Port B Host/Buffer transfers are shown in Figures 5 and 6.

FIGURE 4. BLOCK DIAGRAM OF THE PORT B TRANSFER

FIGURE 6. BUFFER TO HOST TRANSFER

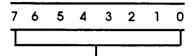

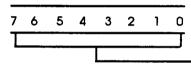

DATA TRANSFER OVERVIEW: In a controller design, the AIC-610F provides all the necessary signals to interface to the host and the peripheral. The controller also generates the necessary control signals to access the buffer, alternating between Port A and Port B transfers. While the Port A transfer is synchronous in nature (at the data transfer frequency), the Port B transfer is asynchronous and is based on a REQ/ACK handshake with the host.

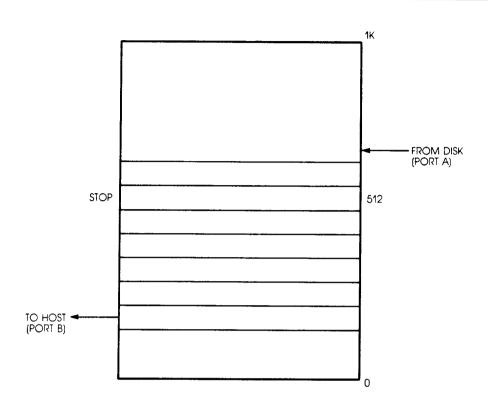

Thus during any data transfer operation, even though the access to the buffer is interleaved between Port A and Port B, the AIC-610F controller chip should stay at least one sector ahead of the host. This is necessary to keep error detection and correction transparent to the host. The AIC-610F has an Internal stop pointer (Register 5E<sub>H</sub> and 5F<sub>H</sub>) used to prevent overruns. An overview of the buffer operation is shown in Figure 9.

# FIGURE 7. DUAL PORT BUFFER TIMING OVERVIEW (FREQUENCY CLKA = FREQUENCY RRC/2)

FIGURE 8. DUAL PORT BUFFER TIMING OVERVIEW (FREQUENCY CLKA = FREQUENCY RRC/4)

#### FIGURE 9. BUFFER OPERATION OVERVIEW

During a read operation while data is being transferred into the buffer from the drive (Port A transfer), the previous sector can be transferred to the host (Port B transfer). The stop pointer is set to the end of the sector being transferred to the host, preventing an overrun. At the conclusion of a successful sector read, the stop pointer can be updated to point to the end of this sector. Now this sector can also be transferred to the host, while yet another sector is read in.

The AIC-610F has a built-in priority resolver circuit which allows the synchronous peripheral to have priority over a host request. This is particularly crucial in disk controller applications. For example, in 10 Mb/Sec systems, a data byte has to be transferred once every 800 ns.

TABLE 3. AIC-610F REGISTER SUMMARY

| 50 <sub>H</sub> | DATA BUS<br>ACCESS (0-7)                                                             | 51 <sub>H</sub> | DATA BUS<br>ACCESS (8-15)                                                                  | 52 <sub>H</sub> | HOST INTF CTL                                                                                | 53 <sub>H</sub> | DMA CTL                                                                                            |

|-----------------|--------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------|

|                 | 7 HOST<br>6 HOST<br>5 HOST<br>4 HOST<br>3 HOST<br>1 HOST<br>0 HOST                   |                 | 7 HOST<br>6 HOST<br>5 HOST<br>4 HOST<br>3 HOST<br>2 HOST<br>1 HOST<br>0 HOST               |                 | 7 BSY OUT 6 SEL OUT 5 BSY IN 4 SEL IN 3 BOE 2 BIE 1 NOT USED 0 ARBITRATION                   |                 | 7 ENBL TARGET 6 NOT USED 5 DMA DONE 4 ROP / WOP 3 READ LATCH 2 WRITE LATCH 1 ACK 0 REQ             |

| 54 <sub>H</sub> | BUFFER SIZE                                                                          | 59 <sub>H</sub> | RESET CTL                                                                                  | 5A <sub>H</sub> | RAP (0-7)                                                                                    | 5B <sub>H</sub> | RAP (8-15)                                                                                         |

|                 | 7 215<br>6 214<br>5 213<br>4 212<br>3 211<br>2 210<br>1 29<br>0 28                   | (WR)            | 7 NOTUSED 6 NOTUSED 5 NOTUSED 4 NOTUSED 3 NOTUSED 2 NOTUSED 1 NOTUSED 0 REG RST (52-5F)    | (R/W)           | 7 RAP 7<br>6 RAP 6<br>5 RAP 5<br>4 RAP 4<br>3 RAP 3<br>2 RAP 2<br>1 RAP 1<br>0 RAP 0         | (R/W)           | 7 RAP 15<br>6 RAP 14<br>5 RAP 13<br>4 RAP 12<br>3 RAP 11<br>2 RAP 10<br>1 RAP 9<br>0 RAP 8         |

| 5C <sub>H</sub> | WAP (0-7)                                                                            | 5D <sub>H</sub> | WAP (8-15)                                                                                 | 5E <sub>H</sub> | STOP (0-7)                                                                                   | 5F <sub>H</sub> | STOP (8-15)                                                                                        |

| (R/W)           | 7 WAP 7<br>6 WAP 6<br>5 WAP 5<br>4 WAP 4<br>3 WAP 3<br>2 WAP 2<br>1 WAP 1<br>0 WAP 0 | (R/W)           | 7 WAP 15<br>6 WAP 14<br>5 WAP 13<br>4 WAP 12<br>3 WAP 11<br>2 WAP 10<br>1 WAP 9<br>0 WAP 8 |                 | 7 SIOP 7<br>6 SIOP 6<br>5 SIOP 5<br>4 SIOP 4<br>3 SIOP 3<br>2 SIOP 2<br>1 SIOP 1<br>0 SIOP 0 |                 | 7 STOP 15<br>6 STOP 14<br>5 STOP 13<br>4 STOP 12<br>3 STOP 11<br>2 STOP 10<br>1 STOP 9<br>0 STOP 8 |

| 6E <sub>H</sub> | EXT ADDRS<br>DECODE                                                                  | 6F <sub>H</sub> | EXT ADDRS<br>DECODE                                                                        |                 |                                                                                              |                 |                                                                                                    |

|                 | 7 NOTUSED 6 NOTUSED 5 NOTUSED 4 NOTUSED 3 NOTUSED 2 NOTUSED 1 NOTUSED 0 NOTUSED      |                 | 7 NOT USED 6 NOT USED 5 NOT USED 4 NOT USED 3 NOT USED 2 NOT USED 1 NOT USED 0 NOT USED    |                 |                                                                                              |                 |                                                                                                    |

**NOTE:**  $\delta E_H$  and  $\delta F_H$  are external address decodes that can be addressed through the AIC- $\delta$  10F. The actual bits in the register are not used.

TABLE 3. AIC-610F REGISTER SUMMARY (Continued)

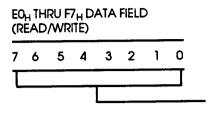

| 70 <sub>H</sub> | BUFFER DATA                                                                                                                  | 71 <sub>H</sub> | ECC CONTROL                                                                                                                                                    | 72 <sub>H</sub> | ECC (32-39)<br>ECC (16-23)                                                                                               | 72 <sub>H</sub> | POLY (1-8)                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| R/W             | 7 BUFFER 6 BUFFER 5 BUFFER 4 BUFFER 3 BUFFER 1 BUFFER 0 BUFFER                                                               | w               | 7 SEL 32 /48 BIT ECC<br>6 RESET / PRESET ECC<br>5 CHIP RESET (78-7F)<br>4 EN SECTOR BRCH<br>3 CLEAR ECC<br>2 DISABL FEEDBACK<br>1 SHIFT ECC<br>0 SERIAL ECC IN | R               | 7 ECC 23/39<br>6 ECC 22/38<br>5 ECC 21/37<br>4 ECC 20/36<br>3 ECC 19/35<br>2 ECC 18/34<br>1 ECC 17/33<br>0 ECC 0-16/0-32 | w               | 7 POLY 8<br>6 POLY 7<br>5 POLY 6<br>4 POLY 5<br>3 POLY 4<br>2 POLY 3<br>1 POLY 2<br>0 POLY 1                                  |

| 73 <sub>H</sub> | ECC (40-47)<br>ECC (24-31)                                                                                                   | 73 <sub>H</sub> | POLY (9-16)                                                                                                                                                    | 74 <sub>H</sub> | POLY (1-8)/(17-24)                                                                                                       | 75 <sub>H</sub> | POLY (9-16)/(25-32)                                                                                                           |

| R               | 7 ECC 31/47<br>6 ECC 30/46<br>5 ECC 29/45<br>4 ECC 28/44<br>3 ECC 27/43<br>2 ECC 26/42<br>1 ECC 25/41<br>0 ECC 24/46         | W               | 7 POLY 16<br>6 POLY 15<br>5 POLY 14<br>4 POLY 13<br>3 POLY 12<br>2 POLY 11<br>1 POLY 10<br>0 POLY 9                                                            | w               | 7 POLY 8/24<br>6 POLY 7/23<br>5 POLY 6/22<br>4 POLY 5/21<br>3 POLY 4/20<br>2 POLY 3/19<br>1 POLY 2/18<br>0 POLY 1/17     | w               | 7 POLY 16/32<br>6 POLY 15/31<br>5 POLY 14/30<br>4 POLY 13/29<br>3 POLY 12/28<br>2 POLY 11/27<br>1 POLY 10/26<br>0 POLY 9/25   |

| 76 <sub>H</sub> | POLY(17-24)/(33-40)                                                                                                          | 77 <sub>H</sub> | POLY(25-31)/(41-47)                                                                                                                                            | 78 <sub>H</sub> | BRANCH/NA                                                                                                                | 79 <sub>H</sub> | W START ADR/<br>R READ STATUS                                                                                                 |

| w               | 7 POLY 24/40<br>6 POLY 23/39<br>5 POLY 22/38<br>4 POLY 21/37<br>3 POLY 20/36<br>2 POLY 19/35<br>1 POLY 18/34<br>0 POLY 17/33 | w               | 7 NOTUSED<br>6 POLY 31 /47<br>5 POLY 30 / 46<br>4 POLY 29 / 45<br>3 POLY 28 / 44<br>2 POLY 27 / 43<br>1 POLY 26 / 42<br>0 POLY 25 / 41                         | R<br>W/R        | 7 NOTUSED 6 NOTUSED 5 NOTUSED 4 BRCH/NA 4 3 BRCH/NA 3 2 BRCH/NA 2 1 BRCH/NA 0                                            | R<br>W/R        | 7 AM ACTIVE 6 DATA XFER 5 BRCH ACTIVE 4 STOPPED 3 NOT USED 2 ECC ERR 1 COMPARE LOW 0 COMPARE EQUAL                            |

| 7A <sub>H</sub> | OP CTL                                                                                                                       | 78 <sub>H</sub> | WAM CTL                                                                                                                                                        | 7C <sub>H</sub> | SYNC CTL                                                                                                                 | 7D <sub>H</sub> | GPI/O CTL                                                                                                                     |

| W/R             | 7 INHIBIT CARRY 6 NOT USED 5 SUPRES XFER 4 SRCH OP 3 NOT USED 2 NRZ DATA IN 1 SECTOR PAST O INDEX PAST                       | w               | 7 WAM AT BR7 6 WAM AT BR6 5 WAM AT BR5 4 WAM AT BR4 3 WAM AT BR3 2 WAM AT BR2 1 WAM AT BR1 0 WAM AT BRO                                                        | w               | 7 SYNC MATCH 6 SYNC MATCH 5 SYNC MATCH 4 SYNC MATCH 3 SYNC MATCH 2 SYNC MATCH 1 SYNC MATCH 0 SYNC MATCH                  | w               | 7 ENABL RD R6F 6 ENABL SET R6F 5 ENABL RD R6E 4 ENABL SET R6E 3 ENABL GP3 OUT 2 ENABL GP2 OUT 1 ENABL GP1 OUT 0 ENABL GP0 OUT |

| 7E <sub>H</sub> | GPI/O                                                                                                                        | 7F <sub>H</sub> | CLK CII.                                                                                                                                                       | 7F <sub>H</sub> | STACK READ/<br>POP TOP OF STACK                                                                                          |                 |                                                                                                                               |

| R<br>R/W        | 7 NOT USED<br>6 NOT USED<br>5 OUTPUT<br>4 BRCHIN<br>3 GPI/O3<br>2 GPI/O2<br>1 GPI/O1<br>0 GPI/O0                             | w               | 7 SEL CLKA FREQ 6 SEL CLKA FREQ 5 NOT USED 4 SEL CLKA FREQ 3 SEL CLKA, CLKB DIR 2 SYNC CMPR CTL 1 SYNC CMPR CTL 0 SYNC CMPR CTL                                | R               | 7 STACK<br>6 STACK<br>5 STACK<br>4 STACK<br>2 STACK<br>2 STACK<br>1 STACK<br>0 STACK                                     | _               |                                                                                                                               |

# **Register Description**

#### 504 PROCESSOR/HOST BUS ACCESS

A Register 50H decode is used to allow the support processor to access the host data bus. In either the read or write process, the host data bus is bridged across the AIC-610F to the support processor.

WRITE: A Register  $50_H$  decode and a write from the microprocessor  $\overline{(WR)}$  asserted) causes LO to be asserted, followed by the  $\overline{\text{BOE}}$  line being asserted. This allows the data passed through the AIC-610F from the support processor to be latched first before being enabled to the host data bus.

READ: During a Register 50H decode and a read from the microprocessor (RD asserted), the BIE line is enabled. This allows the processor to read the available host data through the AIC-610F.

#### 51<sub>H</sub> PROCESSOR/HOST BUS ACCESS (HIGH ORDER BYTE)

A Register 51<sub>H</sub> decode is used to allow the support processor to access the high order byte of the data bus in 16-bit applications. Read and write operations are similar to Register 50<sub>H</sub>.

#### 52<sub>H</sub> HOST INTERFACE CONTROL (READ/WRITE)

#### 54<sub>H</sub> BUFFER SIZE (WRITE)

#### Examples:

- Set Register 54<sub>H</sub> to 03<sub>H</sub> for a 1K byte buffer.

- Set Register 54<sub>H</sub> to 1F<sub>H</sub> for an 8K byte buffer.

**NOTE:** When a buffer size greater than 16K bytes is set, address pins  $\overline{A12}$  and  $\overline{A13}$  function as Set Host Pointer (SHP) and Set Device Pointer (SDP), respectively.

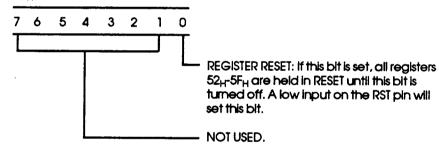

#### 59H RESET CONTROL (WRITE)

NOTE: Any write to this register will reset WAP, RAP, and SP. If external high-order address latches are used they will not be reset. Therefore, it will be necessary to execute a set Register  $5B_H$  and Register  $5D_H$  to zero. This will generate the required SHP and SDP strobes.

#### 6EH EXTERNAL REGISTER ACCESS/EXTERNAL BUFFER ENABLE

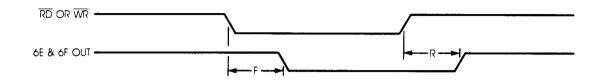

A read or write to this register can be made to generate a negative pulse on two (of the four) GP I/O pins. Thus Register  $6E_{\rm H}$  is addressed through the AIC-610F, yet its function is to enable an external buffer or clock an external latch. This pulse can be used to simplify the interface to various drive interfaces such as ESDI. Figure 10 shows how Register  $6E_{\rm H}$  may be used.

## FIGURE 10. REGISTERS 6EH AND 6FH USAGE

#### 6FH EXTERNAL REGISTER ACCESS/EXTERNAL BUFFER ENABLE

A read or write to this register can be made to generate a negative pulse on two of the four GP I/O pins. Thus Register  $\delta F_H$  is addressed through the AIC- $\delta 10F$ , yet its function is to enable an external buffer or clock an external latch. This pulse can be used to simplify the interface to various drive interfaces.

**NOTE:** Before using Registers  $6E_H$  and  $6F_H$ , the GP I/O control register (Register  $7D_H$ ) must be set up for required function.

#### 70<sub>H</sub> PROCESSOR/RAM BUFFER ACCESS

Register  $70_H$  decode is used to allow the support processor to access the buffer. A read (on Register  $70_H$ ) causes the processor data bus to be bridged to the RAM data bus via the AIC-610F.  $\overline{\text{MOE}}$  is asserted and  $\overline{\text{WE}}$  is set up for read/write operations.

The address selected is the contents of the WAP register if the ROP/WOP (Register  $53_{H}$ , Bit 4) is set (read disk). Otherwise, it is the contents of the RAP register if the ROP/WOP bit is reset.

NOTE: See special requirements, described in the hardware section, for a buffer greater than 16K.

#### 72<sub>H</sub> ECC SYNDROME (16-23)/ ECC SYNDROME (32-39) (READ)

48-BIT ECC SYNDROME: This bit is an OR of the ECC syndrome, Bits 0 through 32. Whenever one of these bits is set, this bit will also be set. This OR is gated by the appropriate length selected.

32-BIT ECC SYNDROME: This bit is an OR of the ECC syndrome, Bits 0 through 16. Whenever one of these bits is set, this bit will also be set. This OR is gated by the appropriate length selected.

48-BIT ECC SYNDROME—ECC BITS 33 THROUGH 39: Bit 39 is in Bit 7 of Register 72<sub>H</sub>.

32-BIT ECC SYNDROME—ECC BITS 17 THROUGH 23: Bit 23 is in Bit 7 of Register 72<sub>H</sub>.

#### 72HECC POLY (1-8) (WRITE)

Each bit corresponds to a feedback path being enabled; i.e., if Bit 0 (i.e., Poly Bit 1) in the register is on, the output (ECC 47) will be XORed with the data in and then XORed with ECC Bit 0 and the result is the input to ECC Bit 1. This register represents Bits 1 to 8 for the 48-bit ECC polynomial. Register 72<sub>H</sub>, Bit 7, represents Bit 8 of the 48-bit ECC polynomial.

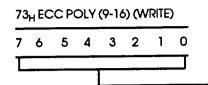

#### 73<sub>H</sub> ECC SYNDROME (24-31)/ ECC SYNDROME (40-47) (READ)

48-BIT ECC SYNDROME—ECC BITS 40 THROUGH 47: Bit 47 is in Bit 7 of Register 73<sub>H</sub>.

32-BIT ECC SYNDROME-ECC BITS 24 THROUGH 31: Bit 31 is in Bit 7 of Register 73<sub>H</sub>.

Each bit corresponds to a feedback path being enabled; i.e., if Bit 0 (i.e., Poly Bit 9) in the register is on, the output (ECC 47) will be XORed with the data in and then XORed with ECC Bit 8 and the result is the input to ECC Bit 9. This register represents Bits 9 to 16 for the 48-bit ECC polynomial. Bit 7 represents Bit 16 of the 48-bit ECC polynomial.

74H ECC POLY (1-8)/ ECC POLY (17-24) (WRITE)

48-BIT ECC POLYNOMIAL: This register represents polynomial from 17 to 24 for the 48-bit ECC polynomial. Bit 7 represents Bit 24 of the polynomial.

32-BIT ECC POLYNOMIAL: This register represents polynomial from 1 to 8 for the 32-bit ECC polynomial. Bit 7 represents Bit 8 of the polynomial.

75H ECC POLY (9-16)/ ECC POLY (25-32) (WRITE)

48-BIT ECC POLYNOMIAL: This register represents polynomial from 25 to 32 for the 48-bit ECC polynomial. Bit 7 represents Bit 32 of the polynomial.

32-BIT ECC POLYNOMIAL: This register represents polynomial from 9 to 16 for the 32-bit ECC polynomial. Bit 7 represents Bit 16 of the polynomial.

#### 76<sub>H</sub> ECC POLY (17-24)/ ECC POLY (33-40) (WRITE)

48-BIT ECC POLYNOMIAL: This register represents polynomial from 33 to 40 for the 48-bit ECC polynomial. Bit 7 represents Bit 40 of the polynomial.

32-BiT ECC POLYNOMIAL: This register represents polynomial from 17 to 24 for the 32-bit ECC polynomial. Bit 7 represents Bit 24 of the polynomial.

#### 77<sub>H</sub>ECC POLY (25-31)/ ECC POLY (41-47) (WRITE)

48-BIT ECC POLYNOMIAL: This register represents polynomial from 41 to 47 for the 48-bit ECC polynomial. Bit 7 represents Bit 47 of the polynomial.

32-BIT ECC POLYNOMIAL: This register represents polynomial from 25 to 31 for the 32-bit ECC polynomial. Bit 7 represents Bit 31 of the polynomial.

NOT USED.

NOTE: Registers 74<sub>H</sub> through 77<sub>H</sub> are not reset by the reset latch.

#### 78<sub>H</sub> BRANCH/NEXT ADDRESS (READ/WRITE)

BRANCH/NEXT ADDRESS: Writing Bits 0-4 sets the sequencer branch address register. When a sequencer branch condition is met, the sequencer will jump to this address. A read of this register (Bits 0-4) gives the next address the sequencer will execute, except during a search for AM.

NOT USED.

NOTE: The COMPARE bits and ECC ERROR bit remain valid for the last read until the next sequencer word which reads or writes an ECC is executed.

#### 79H SEQUENCER START (WRITE)

START ADDRESS: A write to Bits 0-4 will start the sequencer at the appropriate address. This register may only be set when Register 79H, Bit 4 (STOPPED), Indicates the sequencer is in the correct initial stopped state.

NOT USED.

NOTE: In normal operation, it should not be necessary to stop the sequencer by setting a 1FH to Register 79H. However, when a sync character is missed and the microprocessor timer expires, the AIC-610F should be stopped and restarted to retry the operation. The recommended way to do this is in a loop that sets  $1F_H$  to Register  $79_H$  and then examines the stopped bit. If not stopped, repeat the  $1F_H$  to  $79_H$ . The AIC-610F will typically stop the first time, but occasionally two or three loops may be required.

The start or stop of the sequencer may take from 0 to 8 RRC cycles.

#### 7AH OPERATION CONTROL (READ/WRITE)

INDEX PAST: Index pulse from the device has been detected since the last time this register was read. Reading this bit while index is present does not reset the bit.

SECTOR PAST: Sector pulse has been received from the device since the last read of this register. Reading this bit while sector is present does not reset the bit.

NRZ DATA IN: An input of "1" on the NRZ data pin while read gate was on has occurred since the last time this register was accessed.

NOT USED: Will be a one.

SEARCH OPERATION: This bit must be set whenever a data field compare is required.

SUPPRESS TRANSFER: CLKB will not be generated when this bit is on. Also, during WG, the data field will be written with the contents of the sequencer RAM data or during RG compared with the contents of sequencer RAM data.

NOT USED.

INHIBIT DATA FIELD CARRY: When set, the carry/load of the sequencer for the data field will be inhibited. After a carry has occurred, this bit will be reset. This is used to cause the sequencer to execute its present address again. For this time, however, the count field will start at 00 and count down (256 cycles will be executed).

7BH WAM CONTROL (WRITE ONLY)

WRITE ADDRESS MARK CONTROL: The WAM/AMD pin will go active for each bit cell time corresponding to the bits set in this register during a write address mark operation. This is used to indicate to external logic when the clock pulse should be deleted from the outgoing data stream after encoding. This, then, creates an illegal pattern which becomes the Address Mark.

7CH SYNC DETECT CONTROL (WRITE ONLY)

SYNC DETECT CONTROL: A match between this register and the serial NRZ read data input will cause a sync detect (if AMD input is active). It will also cause the bit ring to start at zero and data to be gated into the ECC. Only those bits enabled by Register 7F<sub>H</sub> can be set for comparison.

NOTE: Only those bits enabled by Register  $7F_H$  can be set for comparison. Any don't-care bits must be set to zero. Whenever Read Gate is turned on, the Bit-Ring oscillator stops within two byte times. For this reason, the sequencer word, which turns on RG, must have a count of 01<sub>H</sub>. At this point, the AIC-610F starts to shift in the data on the NRZ pin. The bit stream is compared with the contents of this register in order to obtain byte sync. In addition to byte sync, an AM detect must also be observed on pin 63 (of the 68 pin PLCC) for the Bit Ring oscillator to start up. This comparison is independent of the Compare Enable function in the sequencer RAM which is normally used for additional qualification, such as differentiating between ID Address Mark and Data Address Mark.

Some sync characters like FE<sub>H</sub> can cause problems if the chip is not set up property. This is because a floating NRZ line (read and write gates not active) shifts 1's into the sync comparison register. When read gate is turned on over the preamble, an FEH is framed, causing improper alignment. This can be avoided by first turning on the invalid NRZ bit (Bit 3 in control field) along with read gate for a few byte times. After this, the next word should have a count of 01<sub>H</sub> which is then followed by the sync word.

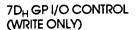

GP I/O DIRECTION CONTROL: When set, these bits enable the corresponding bits of the GP I/O register to the output pins. When these bits are zero, the pins are the source of the GPI/O register; I.e., inputs are gated to the bus when a read of GP I/O is done.

W6E CONTROL: When set along with Bit 0, this bit will disable GP !/O register Bit 0 as an output and enable a set Register 6E<sub>H</sub> output puise. When zero, the GP I/O register is the output.

R6E CONTROL: Same function as above, except a read pulse for Register  $6E_H$  will be output from pin 1.

W6F CONTROL: Same function as above, except a write pulse for Register  $\delta F_H$  will be output from pin 2.

R6F CONTROL: Same function as above, except a read pulse for Register  $\delta F_H$  will be output from pin 3.

NOTE: To set up the AIC-610F for 6EH or 6FH decode, first set Bits 0 to 3 before setting Bits 4 to 7 (i.e., write a OF<sub>H</sub>, followed by FF<sub>H</sub>).

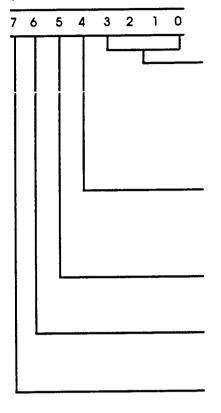

#### 7EH GP I/O (READ/WRITE)

GP I/O BITS 0-3: General purpose input/output bits (Bits 0-3) are independently programmable for direction of data on the four pins and each bit has a gated latch that holds data for output purposes only. A read of this register will gate the contents of the input pin.

INPUT PIN: An external input that may be used as a branch condition for the sequencer RAM.

**OUTPUT PIN: This bit indicates the** state of the output bit in the sequencer RAM.

NOT USED.

NOTE: Register 7D<sub>H</sub> must be set up prior to accessing Register 7E<sub>H</sub>.

data transfer will be equal to

SYSCLK frequency. 11 = CLKA will not provide valid

information.

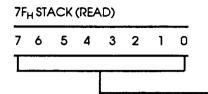

STACK: A read of this register will read and pop the top of the 8-byte stack. The stack wraps around on the 8th pop.

80H THRU 97H NEXT ADDRESS FIELD (READ/WRITE)

**NEXT ADDRESS: This is the address** the sequencer will go to after the down counter has reached zero and a branch has not been taken. There are 24 possible next-address locations (00 to 17). Addresses from 18 to 1F establish a stopped condition.

BRANCH CONDITIONS: Branch conditions when both ECC and read gate are active. These branches are taken at the end of ECC time.

000 = Continue, next address used.

001 = Stop on ECC error.

010=Stop on no compare equal.

011 = Stop on no compare equal or ECC error.

100 = Branch on good ECC and compare equal.

101 = Branch on ECC error.

110=Branch on no compare equal.

111 = Branch on no compare equal or ECC error.

Branch condition at all other times. These branches are taken when the operations specified by that word are complete.

000 = Continue, next address used.

001 = Stop If INPUT is active.

010 = Stop If INDEX or SECTOR is active.

011 = Stop on no compare equal.

100 = Branch on carry (expiration of count).

101 = Branch on INPUT active.

110=Branch on INDEX or SECTOR active.

111 = Branch on no compare equal.

NOTE: The compare equal flag is checked after the ECC bytes have been read in. The compare equal flag is reinitialized when read gate is turned on.

CO<sub>H</sub> THRU D7<sub>H</sub> COUNT FIELD (READ/WRITE)

COUNT: These bits are the initial value of the sequencer counter when a new state is entered. Bits 0 thru 4 of the counter are set to Bits 0 thru 4 of the counter field, respectively. The counter is decremented on bit ring 7. When it reaches zero, a new state will be accessed from the sequencer RAM. The value specified here must be one less than the count to be executed (for a count of 256, set  $FF_H$ ).

DATA TYPE: When the DATA TRANS-FER bit (Control Byte, Bit 0) of the sequencer RAM is off, these bits are decoded for data type as indicated below:

000=Normal.

100=Address Mark.

010=ECC. During an ECC Read/Write, one additional byte of data is read/written due to the one byte delay in ECC computation.