# ALTOS

486

System Reference

## 486 System Reference

#### **ACKNOWLEDGEMENTS**

CP/M is a registered trademark of Digital Research, Inc.

XENIX is a trademark of Microsoft Inc.

UNIX is a trademark of Bell Laboratories

#### FEDERAL COMMUNICATIIONS COMMISSION NOTICE

#### WARNING

This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions manual, may cause interference to radio communications.

It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment.

Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

## **About This Manual**

This manual is written for a system programmer or analyst requiring hardware and software reference information for system configuration and program modification.

## Contents

| PAGE                                                                          | SUBJECT                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-1<br>1-3<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4                                 | SYSTEM SOFTWARE OPERATING SYSTEMS SYSTEM MONITOR DIAGNOSTICS OPTIONS                                                                                                                                          |

| 2-1<br>2-1<br>2-3<br>2-5<br>2-7                                               | DOMED CUDDIV                                                                                                                                                                                                  |

| 3-1<br>3-1<br>3-1<br>3-4                                                      | INTRODUCTION                                                                                                                                                                                                  |

| 4-1<br>4-1<br>4-1<br>4-3<br>4-3<br>4-4<br>4-4<br>4-4                          | CPU BOARD 80186 MICROPROCESSOR MEMORY DEVICES MEMORY MANAGEMENT UNIT (MMU) FLOPPY DISK DRIVE WORKNET                                                                                                          |

| 5-1<br>5-1<br>5-3<br>5-3<br>5-4<br>5-6<br>5-7<br>5-12<br>5-13<br>5-23<br>5-24 | INTRODUCTION CENTRAL PROCESSING UNIT (CPU) HARDWARE OVERVIEW 80186 MICROPROCESSOR ARCHITECTURE Addressing Modes Direct Memory Access (DMA) Operation Programmable Timer Operation Interrupt Control Operation |

| PAGE         | SUBJECT                                         |

|--------------|-------------------------------------------------|

| <b>5</b> 05  |                                                 |

| 5-25<br>5-25 | Z-80A I/O CONTROLLER Functional Description     |

| 5-26         | Z-80A I/O Processor Memory                      |

| 5-20<br>5-27 | 80186/Z-80A Communnications                     |

| 5-28         | Host/Controller Communication                   |

| 5-28         | Controller Initialization                       |

| 5-29         | Channel Initialization                          |

| 5-29         | Channel Transmit Operation                      |

| 5-29         | Channel TTY Receive Operation                   |

| 5-29         | Channel Ring Buffered Receive Operation         |

| 5-30         | Modem Status Operation                          |

| 5-3Ø         | REGISTER DEFINITIONS                            |

| 5-3Ø         | Initialization Register                         |

| 5-31         | Control Registers                               |

| 5-32         | Communication Channel Registers                 |

| 5-36         | HARD DISK CONTROLLER HARDWARE OVERVIEW          |

| 5-36         | T NTRODUCT TON                                  |

| 5-36         | FUNCTIONAL DESCRIPTION                          |

| 5-36         | Disk Drive Description                          |

| 5-36         | Head Selection                                  |

| 5-39         | Formatting Guidelines                           |

| 6-1          | 6. FIRMWARE INTERFACE                           |

| 6-1          | · ·                                             |

| 6-1          |                                                 |

| 6-3          | Monitor Location                                |

| 6-4          | Debugger Program                                |

| 6-5          | Entering the Debugger Program                   |

| 6-5          | Executing a Debugger Command (An example)       |

| 6-12         | 486 Monitor's System Call Interface             |

| 6-18         | Power-up Test                                   |

| 6-19         | Power-up Test Error Reporting Scheme            |

| 6-19         | Power-up Test Descriptions                      |

| A-1          | APPENDIX A. 486 CPU JUMPERING SPECIFICATIONS    |

| D. 1         | ADDENIALA DE DODUI COMPROMICONO                 |

| <b>D-1</b>   | APPENDIX B. PORT CONNECTIONS                    |

|              | ILLUSTRATIONS                                   |

|              | INDUSTRALIONS                                   |

| 1-2          | Figure 1-1 Altos Model 486 Computer System      |

| 3-2          | Figure 3-1 Bus Architecture                     |

| 4-2          | Figure 4-1 System Block Diagram                 |

| 5-2          | Figure 5-1 CPU Board Block Diagram              |

| 5-8          | Figure 5-2 Master/Slave PIC Configuration       |

| 5-9          | Figure 5-3 Interrupt Request                    |

| 5-37         | Figure 5-4 Hard Disk Controller Board Circuitry |

| 5-4Ø         | Figure 5-5 Sector Format                        |

| A-1          | Figure A-1 CPU Jumper Locations                 |

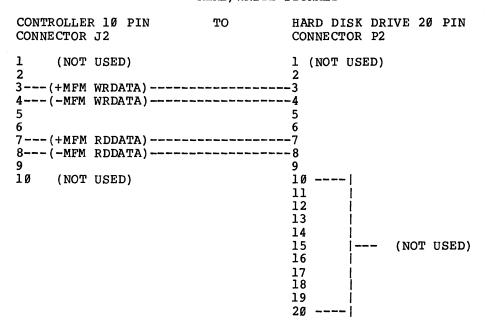

| B-5          | Figure B-l Hard Disk Drive                      |

#### TABLE OF CONTENTS

#### PAGE SUBJECT TABLES 5-5 Table 5-1 Chip Select Register Offsets 5-5 Table 5-2 DMA Register Offsets 5-6 Table 5-3 Timer Control Register Offsets 5-8 Table 5-4 Interrupt Controller Register Offsets 5-1Ø Table 5-5 System Maskable Interrupts 5-11 Table 5-6 Master PIC Register Offsets 5-12 Table 5-7 80186 Microprocessor Predefined Types and Default Priority 5-13 Table 5-8 System Memory Map 5-14 Table 5-9 Memory Management Relocation Register 5-22 Table 5-10 Violation Port Bits 5-23 Table 5-11 Control Port Address Offsets 5-23 Table 5-12 Control Bits 5-24 Table 5-13 PIA Port Address Offsets 5-25 Table 5-14 Floppy Disk Control Port Address Offsets 5-25 Table 5-15 Floppy Disk Controller Port Address Offsets 5-25 Table 5-16 Z80 Port Assignments 5-26 Table 5-17 SIOA Port Address Offsets 5-26 Table 5-18 SIOB Port Address Offsets 5-26 Table 5-19 Z-80A Memory Addressing 5-28 Table 5-20 Internal Hard Disk Connectors Table 5-21 Disk Data Format 5-40 Table 5-22 Conversion from Byte Offset to Sector 5-41 Number 6-3 Table 6-1 Monitor Memory Map Debugger Support Commands 6 - 4Table 6-2 6-6 Table 6-3 Debugger's Command Syntax 6-13 Table 6-4 Monitor System Calls Table 6-5 6-16 Peripheral I/O Parameter Block Layout 6-17 Table 6-6 Peripheral I/O Parameter Block Definition 6-18 Table 6-7 Power-up Test Structure

# System Overview 1

| PAG E                           | SUBJECT                                                                            |

|---------------------------------|------------------------------------------------------------------------------------|

| 1-1                             | FEATURES AND CAPABILITIES                                                          |

| 1-3<br>1-3<br>1-3<br>1-3<br>1-3 | SYSTEM SOFTWARE Operating Systems XENIX Concurrent CP/M System Monitor Diagnostics |

| 1-4                             | OPTIONS                                                                            |

| 1-4                             | RELATED DOCUMENTS                                                                  |

|                                 | ILLUSTRATIONS                                                                      |

| 1-2                             | Figure 1-1. Altos Model 486 Computer System                                        |

#### FEATURES AND CAPABILITIES

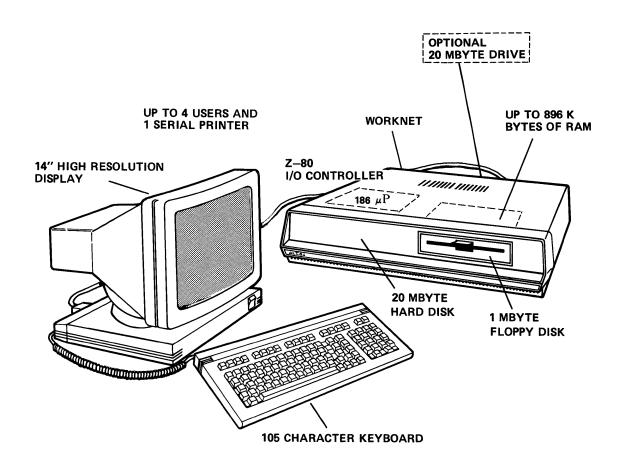

The Altos 486 is a general purpose 16-bit microcomputer system with al Mbyte floppy disk and 20 Mbyte hard disk storage capacity in a desktop design. See Figure 1-1. The 486 supports up to four users and a serial printer. The WorkNet port lets you network the 486 system with up to 30 other Altos computer systems (such as the 186, 586/986, 586T/986T, and the 68000).

The 486 combines the low cost data sharing and communications capability of an intelligent terminal with the computer power necessary to tackle sophisticated business and scientific problems. The adjustable, low-glare CRT offers a high-resolution display. The adjustable, low-profile keyboard offers 105 keys in the format of a dedicated word processor.

The 486 system provides the following features:

- o The Intel 80186 microprocessor with expanded instruction set, built-in direct memory access channels and an interrupt controller and operates at 8Mhz.

- o Z-80A I/O processor for high speed data transfer.

- o 512 Kbytes of standard main memory; expandable to 896 Kbytes.

- o 5-1/4 inch, double-sided, double density floppy disks with 1 Mbyte storage capacity.

- Network communications using the WorkNet interface.

- o Five RS232 serial ports.

- Optional 20 Mbyte add-on hard disk for a total of 40 Mbytes of hard disk storage capacity.

- o Comprehensive system diagnostics support.

Figure 1-1 Altos Model 486 Computer System

#### SYSTEM SOFTWARE

The 486 uses several software programs to help run the system. These are the operating system, utilities, diagnostics, and the monitor programs. Applications and languages are not discussed in this manual.

#### OPERATING SYSTEMS

The 486 system supports two multiuser operating systems: XENIX and Concurrent CP/M. These are described below.

#### XENIX Operating System

This multiuser system complements a large number of applications such as office automation, database management, and communications. It is the Microsoft 16-bit microcomputer implementation of the UNIX operating system developed by Bell Laboratories.

The XENIX operating system supports program development and many software applications. XENIX features a hierarchial file system, compatibility between file, device, and interprocess I/O, asynchronous processing, a command language interpreter, a large number of subsystems and utilities, excellent file security, user-friendly menus, flexible memory use and compatiblity with a large number of high level languages.

#### Concurrent CP/M Operating System

Concurrent CP/M (Control Program for Microprocessors) is a multiuser operating system for 16-bit microcomputers. CP/M provides record and file locking with password protection for use in business settings where data base integrity is essential. CP/M also features extensive error handling and reporting, real-time capabilities, and data and time stamps and files.

#### SYSTEM MONITOR

The system monitor programs and modules reside permanently in the PROMs of the 486 and provide initial system checks and exercise initial coordination and control of the system. The Monitor includes an extensive set of power-up tests used to identify hardware faults in the system, and a debugger program to help find problems in users' programs.

#### DIAGNOSTICS

The diagnostics programs for the 486 are contained in a separate diskette supplied with the system. These SDX (system diagnostics executive) programs help you isolate problems in system operation. They are described in the Diagnostics manual along with selected system utility programs.

#### **OPTIONS**

Listed below are the options for the 486 System which are available through upgrade kits (U/K).

o An additional 384 Kbytes of RAM for a total of 896 Kbytes of main memory.

#### NOTE

The standard system is configured with 512 Kbytes of memory. 256 Kbytes are on the CPU board and the other 256 Kbytes are on a pair of memory boards (128 Kbytes each). The memory upgrade kit provides a 512 Kbyte board which is then exchanged with one of the existing 128 Kbyte memory boards.

o An optional 20 Mbyte add-on hard disk drive unit.

#### RELATED DOCUMENTS

The following Altos publications on the Model 486 Computer System may be referenced to supplement your overall understanding.

690-15889-001 Setting Up Your 486 Workstation

690-15927-001 Altos 486 SDX Diagnostic Manual

690-15683-001 486 Maintenance Manual

690-15998-001 486 Illustrated Parts List Manual

The Setting Up and Diagnostic Manuals are shipped with the system. The Maintenance Manual and Illustrated Parts List Manual can be purchased.

```

PAG E

SUBJ ECT

2-1

SYSTEM SPECIFICATIONS

2-1

DESCRIPTION

2-1

Rear Panel Connectors and Controls

2-2

POWER REQUIREMENTS

2-2

AC Power

2-2

Heat Dissipation

2-2

CPU OVERALL DIMENSIONS

2-2

ENVIRONMENTAL REQUIREMENTS

2-2

Ambient Temperature

2-2

Relative humidity

2-3

SPECIFICATIONS

2-3

Microprocessor

2-3

Memory

2-3

OTHER SYSTEM SPECIFICATIONS

2-3

POWER SUPPLY SPECIFICATIONS

2-5

FLOPPY DISK DRIVE

2-5

POWER REQUIREMENTS

2-5

DC Power

2-5

Heat Dissipation

2-5

OVERALL DIMENSIONS

2-5

ENVIRONMENTAL REQUIREMENTS

2-5

Operating Temperature

2-5

Non-operating Temperature

2-6

PERFORMANCE SPECIFICATIONS

2-7

HARD DISK DRIVE

2-7

POWER REQUIREMENTS

2-7

DC Power

2-7

AC Power

2-7

Heat Dissipation

2-7

OVERALL DIMENSIONS

2-7

ENVIRONMENTAL REQUIREMENTS

2-7

Operating Temperature

2-7

Non-operating Temperature

2-8

PERFORMANCE SPECIFICATIONS

```

#### SYSTEM SPECIFICATIONS

The following specifications describe the overall dimensions, power, environmental, and performance requirements for the 486 Computer System.

#### DESCRIPTION

Central Processor (CPU) Floppy Disk Drive Hard Disk Drive WorkNet

#### Rear Panel Connectors and Controls

AC Power ON/OFF Switch

AC Power Input Receptacle

AC Fuse Holder

System Reset Button

Serial RS232 Ports: five 25 pin "D" connectors

WorkNet RS422 Port: 15 pin "D" connector

WorkNet is a local area network capable of supporting up to 30 other Altos computers.

Serial RS232 Ports support asynchronous terminals and printers.

#### POWER REQUIREMENTS

#### AC Power

| Volts             | 115       | 230       |

|-------------------|-----------|-----------|

| Hertz             | 6 Ø       | 5Ø        |

| Amperes (Maximum) | 3         | 2         |

| Fuse Type         | 4A - 250V | 2A - 25ØV |

| Fuse Size         | 3AG       | 3 AG      |

#### Heat Dissipation

| Watts        | 180 |

|--------------|-----|

| BTU per/Hour | 614 |

#### CPU OVERALL DIMENSIONS

| Height | (inches)               |          | 3.5 |

|--------|------------------------|----------|-----|

| Width  | (inches)               |          | 17  |

| Length | (inches)               |          | 15  |

| Weight | (Free standing weight) | (pounds) | 20  |

#### ENVIRONMENTAL REQUIREMENTS

To ensure best performance from the 486 System, avoid extremes in temperature or humidity. These conditions are likely causes of floppy and hard disk drive malfunctions. For further information about environmental constraints, refer to the ENVIRONMENTAL REQUIREMENTS for specific components. It is recommended that you position the 486 System so that disk drives are maintained in a horizontal position.

|                     |     |      | (       | 0        |      |     | (  | )  |

|---------------------|-----|------|---------|----------|------|-----|----|----|

| Ambient Temperature | 59  | to   | 90      | F        | (15  | to  | 32 | C) |

| Relative Humidity   | 20  | to   | 8Ø      | ( E      | erce | ent | )  |    |

| Temperature         |     |      | <b></b> | <b>.</b> |      |     |    |    |

| (Maximum wet bulb N | on- | cond | aen     | SII      | ıg   |     |    |    |

| Degree Farenheit)   |     |      |         |          |      |     | 78 |    |

#### MICROPROCESSOR

| Intel - 80186                     | 1  |

|-----------------------------------|----|

| Address/Data Bus (bits)           | 16 |

| Processor Speed (Megahertz)       | 8  |

| DMA Channels                      | 2  |

| Programmable Interrupt Controller | 1  |

| Programmable 16-bit Timers        | 3  |

| Zilog - Z8Ø                       | 1  |

| Address Bus (bits)                | 16 |

| Data Bus (bits)                   | 8  |

| Processor Speed (Megahertz)       | 4  |

#### MEMORY

| Standard | 512 | Kbytes        |

|----------|-----|---------------|

| Maximum  | 896 | <b>KBytes</b> |

#### OTHER SYSTEM SPECIFICATIONS

Electrostatic Discharge Dissipation 10 KV (with no hard errors) 300Pf

Agency Approvals FCC, Class A, UL, CSA Designed to meet VDE, IEC

#### POWER SUPPLY SPECIFICATIONS

o Output Voltages and Maximum Rated Loads

Output 1: +5.0V at 15.0 A

Output 2: +12 V at 4.0 A (surging to 7 A for 10 sec to start disk)

Output 3: -12 V at 0.5 A

Continuous Output Power is 153 watts

o Overall Regulation (from all causes)

Output 1:  $\pm$  3% max at 75% load  $\pm$  25% load change Output 2:  $\pm$  5% max at 60% load  $\pm$  40% load change Output 3:  $\pm$  5% max at 60% load  $\pm$  40% load change

o Noise and Ripple

Output 1: 100 mV p-p max Output 2: 100 mV p-p max Output 3: 200 mV p-p max Input Voltage (at all rated load conditions)

U.S.: 95 VAC to 130 VAC single phase Europe: 190 VAC to 260 VAC single phase

o Efficiency at maximum continuous output power and nominal line input:

70% min; forced air cooling available, approximately 30 cfm.

Overvoltage protection threshold

Output 1:  $6.25 \text{ V} \pm \emptyset.75 \text{ V}$

o Temperature Range

Ø to 50 degrees C ambient

o Mean Time Between Failures

20,000 hours (continuous)

o Safety and Emissions Requirements

UL and CSA mandatory VDE approvable

#### FLOPPY DISK DRIVE

#### POWER REQUIREMENTS

#### DC Power

| Volts<br>Amperes | (typical) |          | +5.0<br>0.6  |

|------------------|-----------|----------|--------------|

| Volts<br>Amperes | (typical  | Seeking) | +12.0<br>0.7 |

| t Dissipat       | tion      |          |              |

#### Heat

#### Watts

| Continuous Seek (typical) | 11.4 |

|---------------------------|------|

| Standby (typical)         | 9.0  |

| Motor off (typical)       | 5.6  |

#### OVERALL DIMENSIONS

#### (Except for front panel)

|        | (inches) (inches) | 1.62<br>5.75 |

|--------|-------------------|--------------|

| Length | (inches)          | 8.0          |

#### (Front Panel)

| Height (inches)               | 1.65 |

|-------------------------------|------|

| Width (inches)                | 5.83 |

| Total overall Weight (pounds) | 2.9  |

#### ENVIRONMENTAL REQUIREMENTS

### Operating Temperature 41 to 109.4 F (5 to 43 C)

```

Relative humidity

(percent non-condensing)

20 to 80

(Maximum wet bulb temperature) 85oF (29oC)

```

Non-operating Temperature -4 to 125 F (-20 to 51.5 C)

Relative humidity (percent) 5 to 95

#### PERFORMANCE SPECIFICATIONS

|                                                                                                     | Double Density             |  |  |

|-----------------------------------------------------------------------------------------------------|----------------------------|--|--|

| Memory capacity                                                                                     |                            |  |  |

| Unformatted                                                                                         |                            |  |  |

| Disk (Megabytes)<br>Track (Kilobytes)                                                               | 1<br>6.25                  |  |  |

| Number of:                                                                                          |                            |  |  |

| Cylinders<br>Head/Cylinder<br>Total Tracks (80 per side)                                            | 80<br>2<br>160             |  |  |

| Transfer Rate (Kilobits/sec)                                                                        | 250                        |  |  |

| Rotational Latency (milliseconds average) 100                                                       |                            |  |  |

| Access Time                                                                                         |                            |  |  |

| Track to Track (ms) Average (ms) Motor Starting Time (ms) Settling Time (ms) Head loading Time (ms) | 3<br>94<br>250<br>15<br>50 |  |  |

| Encoding Method<br>Index                                                                            | MFM<br>1                   |  |  |

| Rotational Speed (rpm)                                                                              | 300                        |  |  |

| Disk Diameter (inches)                                                                              | 5.250                      |  |  |

| Track Density (Tracks per inches)                                                                   | 96                         |  |  |

#### HARD DISK DRIVE

#### POWER REQUIREMENTS

#### DC Power

| Volts Steady State: (percent) Amperes (typical) (Maximum) Ripple (Maximum percent allowed with equivalent resistive load) Start Surge: (Maximum percent) Amperes (Maximum) (10 Seconds typical) | +12<br>±5<br>1<br>1.2<br>±10<br>2.5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Volts (±5 percent) Amperes (typical) (Maximum) Ripple (Maximum percent allowed with equivalent resistive load)                                                                                  | +5<br>Ø.4<br>Ø.5                    |

| AC Power                                                                                                                                                                                        |                                     |

| None required                                                                                                                                                                                   |                                     |

| Heat Dissipation                                                                                                                                                                                |                                     |

| Watts (typical) (Maximum)                                                                                                                                                                       | 14<br>17                            |

| OVERALL DIMENSIONS                                                                                                                                                                              |                                     |

| Height (inches) Width (inches) Length (inches) Weight (pounds)                                                                                                                                  | 1.63<br>5.88<br>8.0<br>4.5          |

| ENVIRONMENTAL REQUIREMENTS                                                                                                                                                                      |                                     |

| Operating Temperature 40 to 122 F (                                                                                                                                                             | o<br>4 to 50 C)                     |

| Relative humidity (percent non-condensing) (Maximum wet bulb temperature)                                                                                                                       | 8 to 8Ø<br>78oF (26oC)              |

| Non-operating Temperature -40 to 135 F (-4                                                                                                                                                      |                                     |

| Relative humidity (percent)                                                                                                                                                                     | 8 to 80                             |

#### PERFORMANCE SPECIFICATIONS

#### Memory Capacity:

Unformatted

| Drive (Megabytes)<br>Surface (Megabytes)<br>Track (Kilobytes)<br>Cylinder (Kilobytes) | 25.5<br>6.38<br>10.416<br>41.664 |  |  |

|---------------------------------------------------------------------------------------|----------------------------------|--|--|

| Formatted                                                                             |                                  |  |  |

| Drive (Megabytes) Surface (Megabytes) Track (Kilobytes) Sector (bytes) Sector/track   | 20<br>10<br>8<br>512<br>16       |  |  |

| Number of:                                                                            |                                  |  |  |

| Cylinders<br>Head/Cylinder<br>Data Tracks<br>Surfaces<br>Disks                        | 612<br>4<br>2448<br>4<br>2       |  |  |

| Transfer rate (Megabits/sec.) 5.0                                                     |                                  |  |  |

| Access Time                                                                           |                                  |  |  |

| Average Latency (ms)                                                                  | 8.33                             |  |  |

| Seek Time (including settling ti<br>Single Track (ms)<br>Average (ms)<br>Maximum (ms) | me)<br>15<br>85<br>190           |  |  |

| Rotational Speed (rpm)                                                                | 3600                             |  |  |

| Recording Density                                                                     |                                  |  |  |

| Areal (TPI x BPI) (Mbits/sq.in.)<br>Linear (MFM)<br>Radial (Tracks per inch)          | 5.90<br>10000<br>588             |  |  |

| Disk Diameter (inches)                                                                | 5.250                            |  |  |

# System Architecture 3

#### PAGE SUBJECT

- 3-1 INTRODUCTION

3-1 BUS STRUCTURE

3-4 MEMORY ARBITRATION

#### ILLUSTRATIONS

3-2 Figure 3-1. Bus Architecture

#### INTRODUCTION

This chapter describes the architecture of the 486 Computer System through a discussion of the bus structure and memory arbitration unit.

#### BUS STRUCTURE

The CPU is made up of various physical data and address buses that determine the general architecture of the system. Refer to Figure 3-1.

The major buses are the XLA Bus, MP (Mapped Address) Bus, AD (Address) Bus, BD (Buffered Data) Bus, ZDØ-7 Bus, LA (Logical Address) Bus, MD Bus, and Z8Ø Address Bus.

The AD bus is a multiplexed 16-bit address/data bus from the 80186 microprocessor and is the main bus of the system. The AD bus "spawns" all the other buses in the system.

Figure 3-1 Bus Architecture

The 80186 requires a 20-bit address to access all the possible locations in main memory; a 16-bit address can only access 65,536 bytes of memory. The processor creates this 20-bit address by appending four low order zeros (A0 through A3) to the 16-bit segment address (which specifies a 64K segment of memory) and combining this with a 16-bit offset address (which specifies a location within the segment). This 20-bit bus is called the logical address (LA) bus.

The LA Bus is created from the AD Bus when the addresses are latched at ALE time and held for the entire bus cycle. The boot and diagnostic PROM are addressed via the LA bus. When the LA bus is buffered, the XLA bus is developed.

The XLA bus provides virtual memory capability through relocation registers residing between the bus and the main memory. This means that if the data ,during a DMA transfer, is not in physical memory location it will be transferred into memory from the disk by the relocation registers addressing space process.

The CPU board design is divided into two major hardware sections, the 80186 section and the Z80 section. The XLA Bus connects these two major sections together so that either processor can access the main memory.

The BD Bus is within the 80186 section, it is the (Buffered) Bus which is created from the multiplexed AD Bus. The BD Bus is an I/O bus. All devices which are in the I/O space of the 80186 processor send and receive data on this bus.

The Mapped Address Bus is created through the Memory Management Unit (MMU). One function of the MMU is to create page addressing to memory. Another function of the Memory Management Unit is to protect the operating system from normal user access.

Within the Z80 section is the ZD0-7 (Data) Bus which is used by the Z80 Microprocessor to transfer eight data bits from the SIO ports to main memory and the 186 through the MD (Memory Data bus).

Located on the ZDØ-7 Bus are the SIO controllers for the five RS232 channels, two timer devices and a small amount of RAM and ROM. The Z8Ø address bus is used to access locations in the local 2K of RAM, for transferring instruction codes from the local control ROM and to interface the XLA bus for Z8Ø I/O processing.

#### MEMORY ARBITRATION

These are all the buses for the 486 system. You will note that both the Z80 and 80186 processors require main memory access. To allow both the Z80 and 80186 buses to share main memory, a central arbitration unit is used. This arbitration unit controls access to main memory.

The central arbitration unit is a three way arbiter - arbitrating requests between the 186 and Z80 and a refresh cycle. When a memory cycle has been allowed access to the bus, that request will be the only one serviced on the bus. A requesting memory cycle cannot interrupt a currently executing cycle.

A refresh cycle must take place at lease every 15.6 us to recharge the dynamic RAM chips. If all three requests arrive at the central arbiter at the same time, the refresh cycle has highest priority and the 80186 cycle has second priority. Lower priority requests are cued and later executed.

#### PAGE SUBJECT 4-1 INTRODUCTION 4-1 CPU BOARD 4-1 80186 Microprocessor 4-3 Memory Devices Memory Management Unit (MMU) 4-3 4-4 Floppy Disk Drive 4 - 4WorkNet 4 - 4Z-80A I/O Processor 4-4 HARD DISK CONTROLLER BOARD

4-2 Figure 4-1. System Block Diagram

ILLUSTRATION

#### INTRODUCTION

This chapter provides a general description of the 486 system. Figure 4-1 shows a block diagram of the main subsystems which make up the 486. These include the CPU board and the hard disk controller board which are briefly described below.

#### CPU BOARD

The CPU board is a multi-functional subsystem that contains the main processor, the I/O processor, the floppy disk drive controller, 256 Kbytes of main memory, the memory management unit, the memory arbitration logic and the I/O ports for all peripheral interfacing.

#### 80186 MICROPROCESSOR

The 486 Computer System is designed around the Intel 80186 microprocessor. It performs most of the central processing unit functions, with the capabilities for Direct Memory Access (DMA), programmable Timers, and Interrupts. It is an integrated circuit housed in a special 68 pin package.

Figure 4-1 System Block Diagram

The basic features of the 80186 Microprocessor are as follows:

- o 16-bit address/data bus

- o 8 Mhz clock

- o Two independent DMA channels

- o Programmable Interrupt Controller

- o Programmable 16-bit timers

In addition, it can address up to 1 megabyte of memory in banks of 64 Kbytes and over 65,000 I/O ports. The CPU performs 8 and 16-bit arithmetic functions in binary or decimal.

The 80186's internal programmable interrupt control (PIC) acts as a slave to the master external PIC. It is through this master/slave setup that the microprocessor services system and internal interrupts.

The two DMA (Direct Memory Access) channels handle requests from the disk drives and WorkNet port. One channel is for the hard and floppy disks DMA requests; the other is for networking.

#### MEMORY DEVICES

The system provides four separate memory components to handle the various memory requirements of the system. These are the "main" memory, the system PROM, Z-80A RAM, and Z-80A ROM.

The standard main memory contains 512 Kbytes of dynamic RAM which is upgradeable to 896 Kbytes. 256 Kbytes are on the CPU board; the remainder are on two memory cards. The PROM contains the power-up tests, the debugger and various boot device drivers.

The Z-80A processing circuitry has 4K of ROM and 2K of RAM for I/O. The ROM contains the control program and the static RAM performs temporary storage and data buffering.

#### MEMORY MANAGEMENT UNIT (MMU)

The MMU creates page memory addressing and contains a mapper and protection circuitry. The MMU circuitry is also responsible for switching the system between user and the protected supervisor mode. In user mode, the system executes the shell or application programs, such as a word processing or an accounting program, for example. In the supervisor mode, monitor programs can be run. In addition, I/O operations can only take place in the supervisor mode, and for operating systems like XENIX, the kernel must run in this state.

#### FLOPPY DISK DRIVE

The floppy disk circuitry is controlled through the 765 chip and interrupts the microprocessor via the 8255 parallel interface port. Control and read/write signals to and from the disk drive are handled through connector J7 on the CPU. The PLL (Phase Lock Loop) aids the 765 in recovering MFM (Modified Frequency Modulation) data.

#### WORKNET

WorkNet enables the 486 to be connected to a network of other Altos computers using synchronous data link control (SDLC). WorkNet conforms to an RS422 electrical standard.

To implement WorkNet, the 486 systems dedicates one of its two DMA channels for this function. A circuit then generates 800 KHz for the network baud rate.

## Z-80A I/O PROCESSOR

The Z-80A I/O processor runs a control program that resides in a PROM that is local to the Z-80A. It also uses a small amount of static RAM for temporary storage and buffering. The I/O processor communicates with the central processor via system memory locations and interrupts. It supports five RS232 channels.

The Z-80A 64K of memory space is divided into two halves. The upper 32K is mapped into the system memory and the lower 32K is mapped into the local PROM and static RAM. The Z-80A can access the full 512 Kbytes of memory but must do so in blocks of 32 Kbytes each.

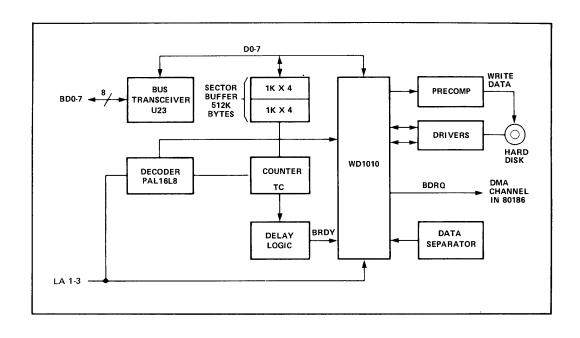

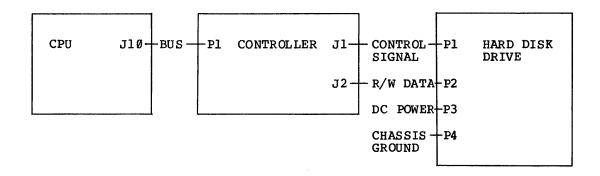

## HARD DISK CONTROLLER BOARD

The other major subsystem of the 486 is the Hard Disk Controller unit. The main component on the board is the WD1010 Winchester chip. The WD1010 Winchester drive controller chip controls the Hard Disk Drive. Read/write instructions from the microprocessor enter the Hard Disk Controller board through the J10 connector. The command is then sent to the WD1010 Controller which controls and monitors a 512 byte buffer used to hold read or write data. One hard disk sector 512 bytes of information. Data is transferred to and from the 20 Mbyte disk drive.

```

PAGE

SUBJECT

5-1

INTRODUCTION

5-1

CENTRAL PROCESSING UNIT (CPU) HARDWARE OVERVIEW

5-3

80186 MICROPROCESSOR ARCHITECTURE

5-3

Addressing Modes

5-4

Direct Memory Access (DMA) Operation

Programmable Timer Operation

5-6

Interrupt Control Operation

5-7

5-12

MEMORY ADDRESSING

MEMORY MANAGEMENT UNIT

5-13

5-23

SYSTEM CONTROL PORT

5-24

FLOPPY DISK CONTROLLER OPERATION

5-24

Programming

5-25

Z-80A I/O CONTROLLER

5-25

Functional Description

Z-80A I/O Processor Memory

5-26

5-27

80186/Z-80A Communnications

5-28

Host/Controller Communication

5-28

Controller Initialization

Channel Initialization

Channel Transmit Operation

5-29

5-29

5-29

Channel TTY Receive Operation

5-29

Channel Ring Buffered Receive Operation

5-30

Modem Status Operation

5-30

REGISTER DEFINITIONS

5-3Ø

Initialization Register

5-31

Control Registers

5-32

Communication Channel Registers

5-36 HARD DISK CONTROLLER HARDWARE OVERVIEW

5-36 INTRODUCTION

5-36 FUNCTIONAL DESCRIPTION

5-36

Disk Drive Description

5-36

Head Selection

5-39

Formatting Guidelines

```

# **ILLUSTRATIONS**

| PAGE                              | SUBJECT                                |                                                                                                                             |

|-----------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

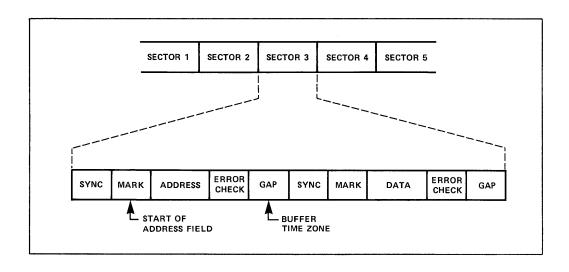

| 5-2<br>5-8<br>5-9<br>5-37<br>5-40 | Figure 5-2<br>Figure 5-3<br>Figure 5-4 | CPU Board Block Diagram Master/Slave PIC Configuration Interrupt Request Hard Disk Controller Board Circuitry Sector Format |

# TABLES

| 5-8<br>5-10<br>5-11 | Table 5-3 Table 5-4 Table 5-5 Table 5-6 | Chip Select Register Offsets DMA Register Offsets Timer Control Register Offsets Interrupt Controller Register Offsets System Maskable Interrupts Master PIC Register Offsets 80186 Microprocessor Predefined Types and Default Priority |

|---------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-13                |                                         | System Memory Map                                                                                                                                                                                                                        |

| 5-14                | Table 5-9                               | Memory Management Relocation Register                                                                                                                                                                                                    |

|                     |                                         | Violation Port Bits                                                                                                                                                                                                                      |

| 5-23                | Table 5-11                              | Control Port Register Offsets                                                                                                                                                                                                            |

| 5-23                | Table 5-12                              | Control Bits                                                                                                                                                                                                                             |

| 5-24                | Table 5-13                              | PIA Port Address Offsets                                                                                                                                                                                                                 |

| 5-25                | Table 5-14                              | Floppy Disk Control Register Offsets                                                                                                                                                                                                     |

|                     |                                         | Floppy Disk Controller Register Offsets                                                                                                                                                                                                  |

| 5-25                | Table 5-16                              | Z80 Port Assignments                                                                                                                                                                                                                     |

| 5-26                | Table 5-17                              | SIOA Register Offsets                                                                                                                                                                                                                    |

|                     |                                         | SIOB Register Offsets                                                                                                                                                                                                                    |

|                     |                                         | Z-80A Memory Addressing                                                                                                                                                                                                                  |

| 5-28                | Table 5-20                              | Internal Hard Disk Connectors                                                                                                                                                                                                            |

| 5-4Ø                | Table 5-21                              | Disk Data Format                                                                                                                                                                                                                         |

### INTRODUCTION

This chapter discusses the subsystem functions of the 486 system that are of interest to a system programmer. First an overview of the function is provided, then any programmable characteristics are discussed followed by addressing and register information for that function. As identified in the previous chapter, the main subsystems of the 486 are the CPU board and the Hard Disk Controller board.

# CENTRAL PROCESSING UNIT (CPU) HARDWARE OVERVIEW

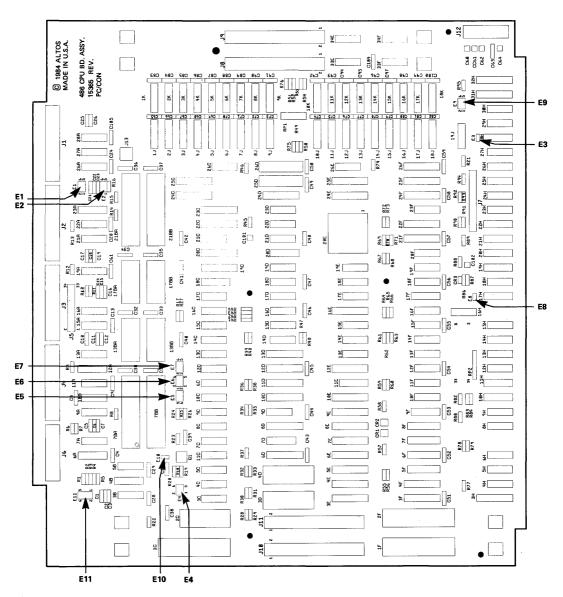

The Central Processing Unit (CPU) printed circuit board performs most of the major functions for the 486 system. Refer to Figure 5-1.

The CPU printed circuit board is designed around two major sections of hardware, the 80186 section and the Z-80A section. Within the 186 section are the 186 microprocessor, the floppy disk controller, the boot ROM, the main memory, the memory management unit, the parallel interface controller (8255), and programmable interrupt controller (8259) IC chips.

Figure 5-1 CPU Board Block Diagram

The Z-80A section contains an intelligent serial I/O controller circuitry that provides high speed data transfer to and from the user terminals. Within the Z-80A section is the Z-80A microprocessor, three Z-80A SIO controllers for five channels, two timer devices and a small amount of RAM and ROM.

### 80186 MICROPROCESSOR ARCHITECTURE

This section describes the architecture of the 80186 microprocessor within the 486 system, specifically the addressing modes, the DMA function and programmable timers.

### Addressing Modes

There are three addressing schemes done through the 80186 in the 486 system: 1) operand addressing, 2) external port or register addressing, and 3) main memory addressing. Memory addressing is discussed later in this chapter.

### Operand Addressing

The 80186 Microprocessor has eight operand addressing modes. Two addressing modes are provided for instructions that operate on internal register or immediate operands and six addressing modes are provided to specify the location of an operand in a memory segment.

A memory operand address consists of two 16-bit components: a segment base and an offset. The segment base is supplied by a 16-bit segment register either implicity chosen by the addressing mode or explicitly chosen by a segment override prefix. The offset is calculated by summing any combination of the following three address elements.

The displacement (an 8- or 16-bit immediate value contained in the instruction)

The base (contents of either the BX or BP base registers)

The index (contents of either the SI or DI index registers)

For more information on operand addressing modes, refer to the data book.

### Port and Register Addressing

The port or register addresses are composed of a programmable base address and an offset. A list of these offset values are provided in Tables 5-1 through 5-19.

To obtain the physical address for a port or an external register, the offset address is added to the base address. The base address refers to a particular address range in the I/O space. For example, if the base address were programmed to start at 1000 and if the floppy status register were being addressed, the offset address, 280 (hex), would be added to the base address, and the result would be 1280 (hex).

#### NOTE

The default base address in this system is 1000.

The starting address is defined by the PACS register of the 80186 as programmed by the user. For more information on programming the PACS register, refer to the data book.

Pheripheral chip select lines, PCSØ\* through PCS3\*, on the 80186 chip are used to select this starting address range block in the I/O space, PCSØ\* enables block 1000, PCS1\* enables block 2000 and so forth. See the internal PCS register offsets in Table 5-1. An MPCS register determines the mode of operation of the peripheral chip selects. Refer to the data book for more information on this function.

### NOTE

Do not confuse a register or port address offset with a memory offset. A memory offset is used to construct the 20 bit address. Refer to discussions on Bus Structure in Chapter 3 and Memory Addressing later in this chapter.

### Direct Memory Access (DMA) Operation

Direct Memory Access (DMA) can be instructed, by the Hard Disk Drive Controller printed circuit board, the Floppy Disk Drive Controller chip or the WorkNet, to access the full contents of main memory. Data can be transferred directly from memory to I/O, memory to memory, or I/O to I/O, without the intervention of the microprocessor. This leaves the mircroprocessor free for other tasks.

The 80186 microprocessor provides two independent high-speed DMA channels. Each channel has six registers in the control block that define that channel's specific operation, see Table 5-1. The control registers consist of a 20-bit source pointer, a 20-bit destination pointer, a 16-bit transfer counter and a 16-bit control word. Data may be transferred in eight bit or sixteen bit transfers.

Data transfers may be either source or destination synchronized, that is, either the source of the data or the destination of the data may request the data transfer. In addition, DMA transfers may be unsynchronized, that is, transfers take place continually until the correct number of transfers has occurred.

To perform a DMA channel transfer, the channel program provides information that describes the operation by loading values into channel registers. DMA cycles can run in either Supervisor or User state and must be permitted to run without triggering access protection mechanism.

Table 5-1 Chip Select Register Offset

| ADDRESS (HEX)                        | DESCRIPTION                                                            |

|--------------------------------------|------------------------------------------------------------------------|

| AØ H<br>A2 H<br>A4 H<br>A6 H<br>A8 H | UPPER MEM CS LOWER MEM CS PACS REGISTER MID RANGE MEM CS MPCS REGISTER |

Table 5-2 DMA Register Offsets

| ADDRESS (HEX) | DESCRIPTION         | CHANNEL |

|---------------|---------------------|---------|

| FFCØH         | SOURCE POINTER      | CH Ø    |

| FFC2H         | SOURCE POINTER      | CH Ø    |

| FFC4H         | DESTINATION POINTER | CH Ø    |

| FFC6H         | DESTINATION POINTER | CH Ø    |

| FFC8H         | TRANSFER COUNT      | CH Ø    |

| FFCAH         | CONTROL WORD        | CH Ø    |

| FFDØH         | SOURCE POINTER      | CH 1    |

| FFD2H         | SOURCE POINTER      | CH 1    |

| FFD4H         | DESTINATION POINTER | CH 1    |

| FFD6H         | DESTINATION POINTER | CH 1    |

| FFD8H         | TRANSFER COUNT      | CH 1    |

| FFDAH         | CONTROL WORD        | CH 1    |

# Programmable Timer Operation

There are three internal 16-bit programmable timers in the 80186 microprocessor, although only two are pinned out. The other timer is for real time applications and generating delayed signals. One of the two pinned out timers is used for generating a baud clock signal at 1.2288 Mhz. The other pinned out timer is used for the system clock.

The timers are controlled by eleven 16-bit registers in the internal peripheral control block, see Table 5-3. The count register contains the current value of the timer. It can be read or written at any time independent of whether the timer is running or not. The value of the register will be incremented for each timer event. Each of the timers is equipped with a MAX COUNT register, which defines the maximum count the timer will reach. After reaching the MAX COUNT register value, the timer count value will reset to zero during that same clock, i.e., the maximum count value is never stored in the count register itself.

The timers have several programmable options:

- o All three timers can be set to halt or continue on a terminal count.

- o Timers Ø and l can select between internal and external clocks, alternate between MAX COUNT registers and be set to retrigger on external events.

- o The timers may be programmed to cause an interrupt on terminal count.

Table 5-3 Timer Control Register Offsets

| <u> </u> | ADDRESS (HEX)                                                                                   | l | FUNCTION                                                                                                                                                    |  | TIMER NO.                                                                       | _1 |

|----------|-------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------|----|

|          | FF50H<br>FF52H<br>FF54H<br>FF56H<br>FF58H<br>FF5CH<br>FF5CH<br>FF5CH<br>FF56H<br>FF60H<br>FF60H |   | COUNT REGISTER MAX COUNT A MAX COUNT B MODE/CONTROL COUNT REGISTER MAX COUNT A MAX COUNT B MODE/CONTROL COUNT REGISTER MAX COUNT A MAX COUNT A MODE/CONTROL |  | TIMER Ø TIMER Ø TIMER Ø TIMER Ø TIMER 1 TIMER 1 TIMER 1 TIMER 2 TIMER 2 TIMER 2 |    |

|          |                                                                                                 |   |                                                                                                                                                             |  |                                                                                 |    |

## Interrupt Control Operation

Internal and external interrupts provide a means of stopping the normal processing flow in order to handle unexpected or difficult situations.

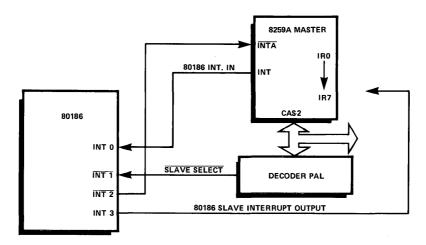

The system operates in the RMX Mode and requires an external master Programmable Interrupt Controller (PIC), the Intel 8259, to handle and service interrupts. As stated earlier, the 80186 contains a built-in PIC which acts as a slave to the external PIC. The internal 80186 resources will be monitored through the internal interrupt controller. See Figure 5-2 for a block diagram of the master/slave PIC setup.

When an internal interrupt takes place, the internal slave Interrupt Controller, residing in the 80186 Microprocessor, resolves priorities and generates an internal interrupt request to the external master PIC. Internal interrupts are from Timers and DMA channels and can be disabled by their own control registers or by mask bits within the interrupt controller. There are 15 registers in the internal peripheral control block, see Table 5-4.

The external master PIC resolves priorities among all the external interrupt sources and issues an interrupt to the 80186 Microprocessor. The 80186 Microprocessor then causes an interrupt acknowledge cycle to take place. After the interrupt condition is serviced the system continues with the user program.

Five pins on the 80186 are dedicated for the interrupt function:

NMI - Non-Maskable Interrupt is typically used for parity errors or a reset.

INTØ - Input is used as the 186 CPU interrupt.

INT1 - Input is used as a slave select input.

INT2 - Output is used as an acknowledge output.

INT3 - Output is to the PIC.

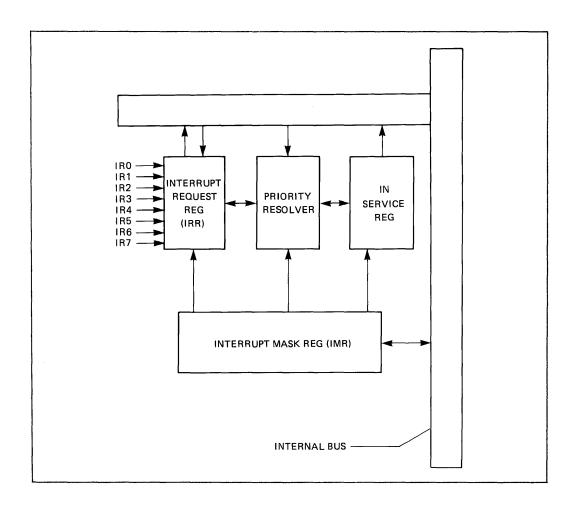

There are eight different levels of system interrupts, interpreted by the PIC, (in order of importance to the system.) The lower the Bit Designation Number is, the more important the interrupt. Therefore, all Memory Mangagement Interrupts are handled before all I/O Port Interrupts. Table 5-5 lists the interrupts in numeric order (and order of importance.) Figure 5-3 illustrates the interrupt activity which are discussed briefly in the following paragraphs.

Interrupt Request Register (IRR) and In-Service Register (ISR)

The interrupts at the IR input lines are handled by two registers in cascade, the interrupt Request Register (IRR) and the in-Service Register (ISR). The IRR is used to store all the interrupt levels which are requesting service, and the ISR is used to store all the interrupt levels which are being serviced.

Figure 5-2. Master/Slave PIC Configuration

Table 5-4 Interrupt Controller Register Offsets

| ADDRESS (HEX) | FUNCTION                    |

|---------------|-----------------------------|

|               |                             |

| FF22H         | EOI                         |

| FF24H         | POLL                        |

| FF26H         | POLL STATUS                 |

| FF28H         | MASK                        |

| FF2AH         | PRIORITY MASK               |

| FF2CH         | IN-SERVICE                  |

| FF2EH         | INTERRUPT REQUEST           |

| FF3ØH         | INTERRUPT CONTROLLER STATUS |

| FF32H         | TIMER CONTROL               |

| FF34H         | DMA Ø CONTROL               |

| FF36H         | DMA 1 CONTROL               |

| FF38H         | INTO CONTROL                |

| FF3AH         | INT1 CONTROL                |

| FF3CH         | INT2 CONTROL                |

| FF3EH         | INT3 CONTROL                |

|               |                             |

Figure 5-3 Interrupt Request

## Priority Resolver

This logic block determines the user-defined priorities of the bits set in the IRR. The highest priority is selected and strobed into the corresponding bit of the ISR during INTA\* pulse.

The Interrupt Mask Register (IMR) allows the user to prevent (mask) an interrupt. During a particular application, if the parity failure interrupt occurs, it can be ignored. The mask allows the user to state at a given time which of those interrupts, listed in Table 5-5 is going to be accepted.

| Mnemonic     | Description                 | <b>Bit</b><br>  Designation |

|--------------|-----------------------------|-----------------------------|

|              |                             |                             |

| MMINT        | MEMORY MANAGEMENT INTERRUPT | IRØ                         |

|              | NOT USED                    | IRl                         |

| AINT         | ALTOSNET INTERRUPT          | IR2                         |

| INTRQ        | INTERRUPT REQUEST           | IR3                         |

| INTERNAL INT | CPU INTERNAL INTERRUPT      | IR4                         |

|              | NOT USED                    | IR5                         |

| IOPINT       | ZDØ-7 BUS INTERRUPT         | IR6                         |

| TMRINT       | TIMING INTERRUPT            | IR7                         |

Table 5-5 System Maskable Interrupts

# Master PIC Operation

When the Altos 486 Computer System is powered up, the CPU loads the initialization command word and operation command word into the PIC's internal registers, see Table 5-6. The initialization command word provides the starting address of the service routines, while the operation command word provides the mode of operation. This mode is described below:

Fully Nested Mode - After the initialization sequence IRØ has the highest priority and IR7 the lowest.

This mode permits the PIC to operate as described above. The commands initially entered in the PIC internal registers are instructions which include what mode to enter and use. The initial command instructions can be permanently loaded in the PIC internal registers so that it will always operate in the same mode, or the loading instructions can be modified as conditions change by reprogramming the device.

Every interrupt is assigned a type code that identifies it. A table containing up to 256 pointers defines the proper interrupt

service routine for each interrupt. Table 5-7 shows the 80186 Microprocessor predefined types and default priorities.

The Microprocessor then multiplies the 8-bit vector by four which becomes the address in a vector table. The significant five bits of the vector are user-programmable while the lower three bits are generated by the priority logic. These bits represent the encoding of the priority level requesting service. The significant five bits of the vector are programmed by writing to the interrupt vector register at offset 20H.

Table 5-6 Master PIC Register Offsets

| Address (HEX) | Function      | Туре    | - |

|---------------|---------------|---------|---|

| 2СØН          | READ OR WRITE | CONTROL |   |

| 2С2Н          | READ OR WRITE | CONTROL |   |

Table 5-7 80186 Microprocessor Predefined Types and Default Priority

| <br> Interrupt Name                           | Vector<br>Type | Default<br>  Priority |                        |

|-----------------------------------------------|----------------|-----------------------|------------------------|

| Divide Error  <br>  Exception                 | Ø              | *1                    | DIV,1DIV               |

| Single Step  <br>  Interrupt                  | 1              | 12**2                 | All                    |

| INMI                                          | 2 .            | 1                     | All i                  |

| Breakpoint  <br>  Interrupt                   | 3              | *1                    | INT                    |

| INTO Detected   Overflow                      | 4              | *1                    | INTO                   |

| Exception  <br> Array Bounds  <br>  Exception | 5              | *1                    | B OU ND                |

| Unused-Opcode  <br>  Exception                | 6              | *1                    | Undefined  <br>Opcodes |

| ESC Opcode<br>  Exception                     | 7              | *1***  <br>           | ESC Opcodes            |

| Timer 0 interrupt                             |                | 2A****                |                        |

| Timer l interrupt                             |                | 2B****                | ļ                      |

| Timer 2 interrupt                             | 19             | 2C****                |                        |

| Reserved                                      | 9              | 3                     | 1                      |

| DMA Ø interrupt                               | 10             | 4                     | l l                    |

| DMA   interrupt                               | 11             | 5<br>  6              |                        |

| INTO interrupt                                | 12             | [ 6 ]                 | Į.                     |

| INTl interrupt                                | 13             | 1 7                   |                        |

| INT2 interrupt                                | 14             | 8                     |                        |

| INT3 interrupt                                | 15             | 9                     |                        |

#### NOTES:

- \*1. These are generated as the result of an instruction execution.

- \*\*2. Generated by the Single-Step flag bit TF in the status word. Once this bit is set, an internal single step interrupt will occur after the next instruction has been executed. The interrupt clears the TF bit and uses an internally supplied vector of 1. The IRET instruction is used to set the TF bit and transfer control to the next instruction to be single-stepped.

- \*\*\*\*3. All three timers constitute one source of request to the interrupt controller. Among the timer interrupts, priority 2A is higher priority than 2B and 2B is higher than 2C. Each Timer interrupt has a separate vector type number.

- 4. Default priorities for the interrupt sources are used only if you do not program each source into a unique priority level.

- \*\*\*5. The escape opcode (part of the instruction word that designates the function performed by a given instruction) will cause a trap only if the proper bit is set in the peripheral control block relocation register.

### MEMORY ADDRESSING

Memory is addressed by a two component address, consisting of a 16-bit base segment and a 16-bit offset value, derived from a combination of pointer registers, instruction pointer, and immediate values.

The 16-bit base values are contained in the one of four internal segment registers. The physical address is calculated by shifting the base value LEFT by four bits and adding the 16-bit offset value to yield a 20-bit physical address. This allows the 80186 to access up to 1 Mbyte of physical main memory, if it were available for the system. With expansion memory, the 486 system can hold up to 896 Kbytes of main memory. 512 Kbytes is contained in the standard configuration. Table 5-8 shows a memory map of the system.

Table 5-8 System Memory Map

| Memory                                                                                                     | Locations                                   | Contents                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00000 -<br>00400 -<br>00476 -<br>01000 -<br>FC000 -<br>FFFC0 -<br>FFFEC -<br>FFFEC -<br>FFFEE -<br>FFFFE - | 007FF Down Up FFFBF FFFDF FFFEB FFFED FFFEF | System's interrupt vector table   Monitor's working area   Monitor's stack area   User's memory space   Monitor program   Monitor's "copy right" statement   Monitor's bootstrap program   PROM release and version number   PROM checksum   Power-up jump vector |

#### MEMORY MANAGEMENT UNIT

The MMU (memory management unit) performs memory mapping and management, and provides access protection and violation detection for the mapped locations.

## Memory Mapping

The MMU changes the upper eight bits of the XLA bus, generates four attribute protection bits to the BD bus, then combines these bits with the remaining lower bits from the XLA bus to produce the mapped address bus to main memory.

The translation of the XLA bus to the MP bus is controlled by a "mapper" in the MMU circuitry. The mapper is a collection of 256 relocation registers, see Table 5-9. Each register maps a 4K byte page of main memory. This gives a possible total of 1 Mbyte of memory.

Memory mapping is important in a multi-user environment because it keeps different users' programs from interfering with the operating system and with each other. Allocation of memory for each user is performed by the operating system.

### Protection Function

Memory protecton allows several different programs ("tasks" or "processes") to use the same physical memory without interfering with the operating system and other user programs. Before running a particular program, the CPU sets up the MMU to map the logical address space of the CPU into the physical memory reserved for that program.

Programs can not interfere with the operating system because each could access only its own portion of the physical memory as

determined by the map. This is done through the protection attribute bits discussed later in this section.

Two types of maps reside in the MMU, one for the operating system and one for user programs. In user mode, a user map is selected and the processor may not execute priviledged I/O. These are instructions whose execution could compromise the integrity of the operating system.

The set of priviledged instructions only includes I/O instructions. The operating system always changes the CPU to be in user mode before transferring control to a user program. Therefore, if the MMU maps are accessed by I/O instructions, a user program cannot access the maps. Of course, all other I/O must also be done by the operating system, since only it can execute I/O instructions.

Table 5-9 Memory Management Relocation Registers

| 1      | LOGICAL     |                       |

|--------|-------------|-----------------------|

| BLOCK  | ADDRESS     | ATTRIBUTE AND MAPPING |

| NUMBER | RANGE       | PORT ADDRESS OFFSETS  |

| İ      | İ           |                       |

| ØØ     | 00000-00FFF | 000                   |

| j Øl   | 01000-01FFF | 002                   |

| Ø2     | 02000-02FFF | 004                   |

| j Ø3   | 03000-03FFF | 006                   |

| Ì      | 1           |                       |

| 04     | 04000-04FFF | 008                   |

| Ø5     | 05000-05FFF | ØØA                   |

| Ø6     | 06000-06FFF | ØØC                   |

| l Ø7   | 07000-07FFF | ØØE                   |

| ĺ      | 1           | <u>'</u>              |

| Ø8     | 08000-08FFF | 010                   |

| j Ø9   | 09000-09FFF | Ø12                   |

| ØA     | ØAØØØ-ØAFFF | 014                   |

| ØB     | ØBØØØ-ØBFFF | Ø16                   |

| 1      | i           |                       |

| l ØC   | ØCØØØ-ØCFFF | Ø18                   |

| ØD     | ØDØØØ-ØDFFF | Ø1A                   |

| j ØE   | ØEØØØ-ØEFFF | ØlC                   |

| ØF     | ØFØØØ-ØFFFF |                       |

| 1      |             |                       |

| 10     | 10000-10FFF | 020                   |

| 11     | 11000-11FFF | 022                   |

| 12     | 12000-12FFF | 024                   |

| 13     | 13000-13FFF | Ø 26                  |

| 1      | ļ           |                       |

| 14     | 14000-14FFF | 028                   |

| 15     | 15000-15FFF |                       |

| 16     | 16000-16FFF | Ø2C                   |

| 17     | 17000-17FFF | 02E                   |

|        |             |                       |

Table 5-9 (Cont'd): Memory Management Relocation Registers

| LOGICAL   BLOCK   ADDRESS   ATTRIBUTE AND MAPPING   NUMBER   RANGE   PORT ADDRESS OFFSETS | <br>        |

|-------------------------------------------------------------------------------------------|-------------|

| NUMBER   RANGE   PORT ADDRESS OFFSETS                                                     | :<br> <br>: |

| 18                                                                                        |             |

| 19                                                                                        |             |

| 19                                                                                        |             |

| 1A                                                                                        |             |

| 1B                                                                                        |             |

| 1B                                                                                        |             |

| 1D                                                                                        |             |

| 1D                                                                                        |             |

| 1D                                                                                        |             |

| 1E   1E000-1EFFF   03B                                                                    |             |

| • == • ==== • • ==== •                                                                    |             |

| Tr   Tropp-Trrr   DDE                                                                     |             |

| 1 !                                                                                       |             |

| 20   20000-20FFF   040                                                                    |             |

|                                                                                           |             |

| 21   21000-21FFF   042                                                                    |             |

| 22   22000-22FFF   044                                                                    |             |

| 23   23 Ø Ø Ø – 23 FFF   Ø 46                                                             |             |

|                                                                                           |             |

| 24   24000-24FFF   048                                                                    |             |

| 25   25000-25FFF   04A                                                                    |             |

| 26   26000-26FFF   04C                                                                    |             |

| 27   27000-27FFF   04E                                                                    |             |

|                                                                                           |             |

| 28   28000-28FFF   050                                                                    |             |

| 29   29000-29FFF   052                                                                    |             |

| 2A   2A000-2AFFF   054                                                                    |             |

| 2B   2B000-2BFFF   056                                                                    |             |

|                                                                                           |             |

| 2C   2CØØØ-2CFFF   Ø58                                                                    |             |

| 2D 2D000-2DFFF 05A                                                                        |             |

| 2E                                                                                        |             |

| 2F   2F000-2FFFF   05E                                                                    |             |

|                                                                                           |             |

| 30 30000-30FFF 060                                                                        |             |

| 31   31000-31FFF   062                                                                    |             |

| 32   32000-32FFF   064                                                                    |             |

| 33   33000-33FFF   066                                                                    |             |

| JJ   JJEET   000                                                                          |             |

| 34   34000-34FFF   068                                                                    |             |

| 34   34000-34FFF   068<br>  35   35000-35FFF   06A                                        |             |

|                                                                                           |             |

| 36   36000-36FFF   06C                                                                    |             |

| 37   37000-37FFF   06E                                                                    |             |

|                                                                                           |             |

| 38   38000-38FFF   070                                                                    |             |

| 39   39000-39FFF   072                                                                    |             |

| 3A 3A000-3AFFF   074                                                                      |             |

| 3B   3B000-3BFFF   076                                                                    |             |

5-15

Table 5-9 (Cont'd): Memory Management Relocation Registers

| 1       | LOGICAL              | !                     |

|---------|----------------------|-----------------------|

| l Droom | •                    |                       |

| BLOCK   | ADDRESS              | ATTRIBUTE AND MAPPING |

| NUMBER  | I RANGE              | PORT ADDRESS OFFSETS  |

|         |                      |                       |

| 20      | 1 20000 20000        | 470                   |

| 1 3C    | 3C000-3CFFF          | Ø78                   |

| 3D      | 3DØØØ-3DFFF          | 1 07 A i              |

| 3E      | 3E000-3EFFF          | 07C                   |

|         |                      |                       |

| 3F      | 3FØØØ-3FFFF          | [ Ø7 E ]              |

| 4Ø      | 40000-40FFF          | l Ø8Ø I               |

| 41      | 41000-41FFF          | i 082 i               |

| 42      | 42000-42FFF          | 084 i                 |

| •       |                      |                       |

| 43      | 43000-43FFF          | Ø86                   |

| 1       | l                    |                       |

| i 44    | 44000-44FFF          | i ø88 i               |

| •       |                      | ·                     |

| 45      | 45000-45FFF          | [                     |

| 46      | 46000-46FFF          | l Ø8C l               |

| 47      | 47000-47FFF          | Ø8E                   |

| 1 4/    | 1 4/000 4/111        | 1 505                 |

|         | !                    |                       |

| 48      | 48000-48FFF          | 090                   |

| 49      | 49000-49FFF          | i 092 i               |

| i 4A    | 4A000-4AFFF          |                       |

|         |                      | 094                   |

| 4 B     | 4B000-4BFFF          | 096                   |