# ALTOS 586T/986T

### 586T/986T System Reference Manual

|  |  |  | • |

|--|--|--|---|

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

### **Federal Communications Commission Notice**

### Warning

This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions manual, may cause interference to radio communications.

It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment.

Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

THE INFORMATION IN THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. NEW EDITIONS OF THIS DOCUMENT WILL INCORPORATE CHANGES AS THEY ARE PUBLISHED.

### **Acknowledgements**

CP/M-86, MP/M, and MP/M-86 are registered trademarks of Digital Research, Inc.

Z80 is a trademark of Zilog, Inc.

Multibus is a trademark of Intel Corporation.

UNIX is a trademark of Bell Laboratories.

XENIX is a trademark of Microsoft Corporation and is a microcomputer implementation of the UNIX operating system.

### **About This Manual**

This manual is intended for system programmers, engineers, technicians, and others who need to understand the internal operation of the 586T and 986T. It presents information about functions that are internally programmed and those that can be programmed by the user.

Those who need information about signal names, voltages, pin assignments, and specific circuit elements, should consult the Altos 586T/986T Maintenance Manual (P/N 690-15602-001).

### **Manual Conventions**

Certain conventions are followed in the descriptions and diagrams used in this manual. Those which may not be obvious are listed below.

| ~      |      |    | <br>   |

|--------|------|----|--------|

| 1 · ^  | 27   | an | <br>on |

| $\sim$ | 11 V |    |        |

#### Meaning

\*

The asterisk symbol, following a capitalized, bolded mnemonic indicates a "not" function or an active low signal. Example: CSINT\*.

Hexadecimal notation

A hexadecimal number is indicated by an "H" following the number. Example: 29H

Some terms are used interchangably and mean the same thing:

System Bus and Multibus

Counter-timer and programmable interval timer

Byte bus and 8-bit bus

System memory and main memory

I/O and peripheral

### **Contents**

| Chapter 1                  | L:       | In    | tro   | đu          | cti     | ior       | 1     | to         | tì  | ı e | 58  | 36 I | :/9 | 86    | T  |     |    |      |

|----------------------------|----------|-------|-------|-------------|---------|-----------|-------|------------|-----|-----|-----|------|-----|-------|----|-----|----|------|

| Chapter 2                  | 2:       | Sy    | ste   | m l         | laı     | r dw      | a:    | re         |     |     |     |      |     |       |    |     |    |      |

| Chapter 3                  | 3:       | Ce    | ntr   | al          | Pı      | 00        | e     | ssi        | .ng | gt  | Ini | t    | Fu  | ınc   | ti | .or | ıs |      |

| Hardwa                     | are      | 04    | erv   | iev         | ₹.      | •         | •     | •          | •   | •   | •   | •    | •   | •     | •  | •   | •  | 3-3  |

| System                     | n Ir     | ite:  | rfa   | ces         | 3.      | •         | •     | •          |     | •   | •   | •    | •   |       | •  |     |    | 3-13 |

| Syster                     | n Ir     | nit:  | ial   | iza         | ati     | Lor       | 1     | and        | 1 ( | ρę  | era | ıti  | or  | ١.    | •  | •   | •  | 3-14 |

| Addr es                    | ssir     | ıg .  |       | •           | •       | •         | •     | •          | •   | •   | •   | •    | •   | •     | •  | •   | •  | 3-19 |

| Chapter 4                  | l :      | Co    | ntr   | <b>01</b> . | Lei     | c E       | 30    | ard        | 1   | ?ur | ıct | ic   | ns  | 3     |    |     |    |      |

| Hardwa<br>CPU-Co           | are      | 0     | erv   | iev         | ٧.      |           |       |            |     |     |     |      |     |       |    |     |    | 4-3  |

| CPU-Co                     | onti     | ol    | ler   | Iı          | nte     | erf       | a     | ce         |     |     |     |      |     |       |    |     |    | 4-10 |

| Contro                     | 116      | r     | Ini   | tia         | a 1 i   | iza       | t     | ior        | 1.  |     |     | Ĭ    |     |       | -  |     | -  | 4-16 |

| Contro                     | 1116     | r     | Sea   | uei         | nCe     | 28        |       |            | •   | •   | •   | Ĭ    | •   | •     | •  | •   | •  | 4-17 |

| Addres                     | ssir     | na .  |       |             |         |           |       | •          |     | Ţ   | •   |      | •   | •     | •  | •   | •  | 4-22 |

|                            |          | - 5   | •     | •           | •       | •         | •     | •          | ٠   | •   | •   | •    | •   | •     | •  | •   | ٠  |      |

| Chapter 5                  | <b>:</b> | St    | ora   | qe          | De      | i ve      | LC    | es         |     |     |     |      |     |       |    |     |    |      |

| Stream<br>Hard I<br>Floppy | nino     | T     | ape   | Üı          | nit     | ٠.        |       |            |     |     |     |      |     |       |    |     |    | 5-3  |

| Hard I                     | Disk     |       |       |             |         |           | _     |            | •   |     | •   | •    | •   | _     | •  |     |    | 5-11 |

| Floppy                     | Di       | sk    |       | •           |         | •         |       | •          |     | •   |     | •    |     |       |    | •   |    | 5-13 |

|                            |          |       | • •   | •           | •       | ٠         | •     | •          | ٠   | •   | •   | •    | •   | •     | •  | •   | •  | -    |

| Chapter 6                  | <b>:</b> | Sv    | ste   | m I         | Fi      | rmv       | 1a    | re         |     |     |     |      |     |       |    |     |    |      |

| 586 T/S                    | 861      | M T   | oni   | to          | r 1     | Pro       | oa:   | ran        | n _ |     | _   | _    |     | _     |    | _   |    | 6-3  |

| Monito                     | or (     | 'Omi  | man   | ds.         | • •     |           |       |            |     | ·   |     | •    |     | •     | •  | •   | •  | 6-7  |

| System                     | C        | mm    | and   | 9           | Ĭ.      | Ĭ.        | •     | Ť          | •   | Ĭ.  | Ţ   | Ĭ    | Ĭ.  |       | ·  | Ĭ   | •  | 6-12 |

| System<br>RAM Ba<br>Monito | 986      | מ ו   | ehu   | aa.         | •<br>•r | •         | •     | •          | •   | •   | •   | •    | •   | •     | •  | •   | •  | 6-13 |

| Monite                     | or (     | 370   | tom   | 99          | 5 T     |           | •     | •          | •   | •   | •   | •    | •   | •     | •  | •   | •  | 6-17 |

| Monito                     | or (     | JOD.  | tro   | 1 1         | 21/     | ro<br>Sol | •     | •          | •   | •   | •   | •    | •   | •     | •  | •   | •  | 6-22 |

| Contro                     | 111      | - OII | B O S | ~4.         | ₽.÷     | JC.       | N     | •<br>> r c | •   | •   | •   | •    | •   | •     | •  | •   | •  | 6-22 |

| CONCI                      | 7110     | - L.  | boa   | Lu          | Ι.      | L T 11    | IL WY | ure        | •   | •   | •   | •    | •   | •     | •  | •   | •  | 0-23 |

| Annondi -                  |          |       |       |             |         |           |       |            |     |     |     |      |     |       |    |     |    |      |

| Appendice                  |          |       |       | <b>.</b>    | , n     |           |       | <b>~</b> - |     | . 7 | α-  | •    |     | . 7 7 |    | _   |    |      |

| Append                     |          |       |       |             |         |           |       |            |     |     |     |      |     |       |    |     |    |      |

| Append                     |          |       |       |             |         |           |       |            |     |     |     |      |     |       |    |     |    |      |

| Append                     | 11X      | C:    | Co    | nti         | ro]     | LΙE       | er:   | Вс         | a   | rd  | Jυ  | ımr  | er  | S     |    |     | •  | C-T  |

### ILLUSTRATIONS

| Figure                       | Title                                                                                |

|------------------------------|--------------------------------------------------------------------------------------|

| 1-1.                         | Altos 586T/986T Computer System with Terminal 1-3                                    |

| 2-1.                         | System Block Diagram 2-5                                                             |

| 3-1.<br>3-2.<br>3-3.<br>3-4. | Dynamic Relocation                                                                   |

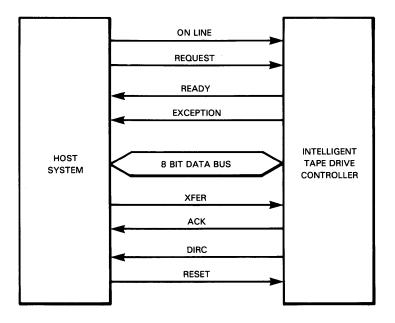

| 4-1.<br>4-2.<br>4-3          | Simplified Block Diagram 4-3 Interrupt Controller 4-6 QIC-02 Interface 4-8           |

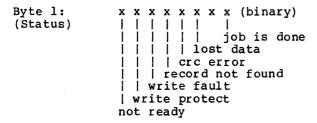

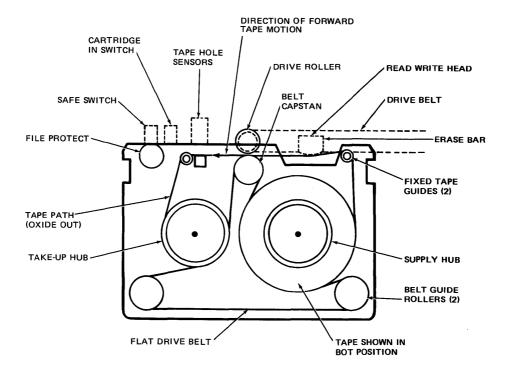

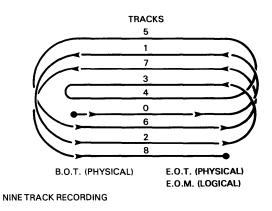

| 5-1.<br>5-2<br>5-3           | 1/4-inch Tape Cartridge 5-6<br>Serpentine Recording 5-7<br>QIC-24 1/4-inch Streaming |

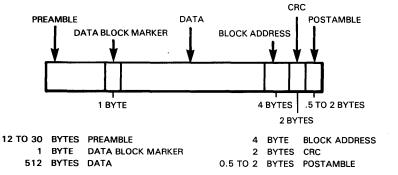

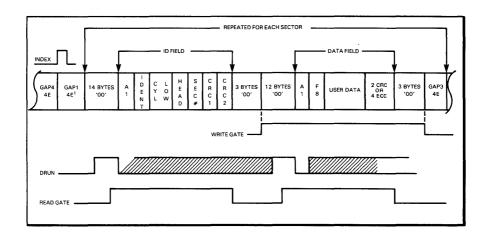

| 5-4                          | Tape Format 5-11 Hard Disk Sector Format 5-13                                        |

| 6-1<br>6-2                   | Memory Map Altos 586T/986T 6-4 IOPB Mapping for Altos 586T/986T . 6-21               |

| TABLES                       |                                                                                      |

| Table                        | Title                                                                                |

| 3-1.                         | Interrupt Priority Levels 3-10                                                       |

| 3-2.<br>3-3.                 | Z80 Memory Map 3-12 Control Bits Port Definition                                     |

|                              |                                                                                      |

| 3-4                          | (Port 58H)                                                                           |

| 3-5.                         | Memory Management I/O Port Definition 3-22                                           |

| 3-6.                         | Memory Management I/O                                                                |

| 3-7.                         | Port Addresses                                                                       |

| 3-8.                         | Violation Port (78)                                                                  |

| 3-9.                         | Error Address Port 2 3-34                                                            |

| 3-10.                        | Z80 I/O Addresses 3-35                                                               |

|                              |                                                                                      |

### TABLES

| Table        | Title                              |     |

|--------------|------------------------------------|-----|

| 4-1.         | Local Memory Map 4-5               | ;   |

| 4-2.         | Tape Command Bit Definition 4-9    | )   |

| 4-3.         | Hard Disk Interface Parameter      |     |

|              | Block 4-1                          | . 4 |

| 4-4.         | Streaming Tape Interface           |     |

|              | Parameter Block 4-1                | . 5 |

| 4-5.         | Floppy Disk Interface              |     |

|              | Parameter Block 4-1                | . 6 |

| 4-6.         | I/O Decoder Addresses 4-2          | 4   |

| 4-7.         | SDH Register (External)4-2         | : 4 |

| 4-8.         | Input Port 4-2                     | :5  |

| 4-9.         | Floppy Port 4-2                    | 25  |

| 4-10.        | Tape Port 4-2                      | :6  |

| 4-11.        | Data Transfer Port 4-2             | :6  |

| 5-1.         | Performance Specifications         |     |

| J-1.         | (Tape)5-4                          | ı   |

| 5-2          | 4-to-5 Run Length Limited Code 5-5 | :   |

| 5-3.         | Tape Status Bytes 5-9              |     |

| 5-4.         | Performance Specifications         |     |

| J 4.         | (Hard Disk) 5-1                    | 2   |

| 5-5.         | Performance Specifications         |     |

| <i>J J</i> . | (Floppy Disk) 5-1                  | Δ   |

|              | (ETOKKI DIBK)                      | . 4 |

### Chapter 1 Introduction to the 586T/986T

| Overview             | • | • | • | • | • | • |  | • | • | • | 1-3 |

|----------------------|---|---|---|---|---|---|--|---|---|---|-----|

| Hardware Features .  |   |   |   |   |   |   |  |   |   |   | 1-4 |

| Capabilities         |   |   |   |   |   |   |  |   |   |   |     |

| Options              |   |   |   |   |   |   |  |   |   |   |     |

| Operating Systems .  |   |   |   |   |   |   |  |   |   |   |     |

| Related Publications |   |   |   |   |   |   |  |   |   |   |     |

| Specifications       |   |   |   |   |   |   |  |   |   |   |     |

Figure 1-1. Altos 586T/986T Computer System.

### Overview

The Altos 586T/986T is a powerful, multiuser, multitasking system designed to meet the needs of micro and mini-computer users. It supports industry-standard operating systems and languages, communications, and business application software. The 8086-based, 16-bit architecture of the 586T/986T can perform larger, more comprehensive tasks for more users than an 8-bit system.

#### **Hardware Features**

The 586T/986T has the following hardware features:

o Multiple processor CPU board-

8086 central processing unit operating at 10 MHz Z80A serial I/O processor

- o 586T has 512 Kbytes of Main Memory 986T has 1 Mbyte of Main Memory Both systems use byte parity error checking

- o Intelligent Controller board for Hard Disk, Streaming Tape, and Floppy Disk units.

- o Integral 40 or 80 Mbyte Winchester drive, 1 Mbyte Floppy Disk drive, and 60 Mbyte cartridge Streaming Tape unit.

- o WorkNet Local Area Network port (RS422)

- Firmware for self-diagnostics at power-up.

- o Time-of-day clock with battery back-up.

- Power fail detection circuitry.

### **Capabilities**

The 586T/986T has these outstanding performance features:

- o <u>Multiple processing</u>. Ten serial RS232 channels on the 986T support up to nine users, plus a serial printer. The 586T supports five users and a serial printer. The systems can handle hard disk, tape, and floppy disk operations concurrently.

- o <u>Memory Management</u>. A proprietary memory management system provides logical-to-physical address translation and contiguous physical memory blocks for each task.

This reduces the need for swapping users or tasks out to disk. The system also provides write and access protection to each assigned block of memory.

o <u>Hard Disk Control</u>. The Hard Disk Controller can:

perform multiple sector read and writes;

cross over track and sector boundaries;

do automatic, transparent retries;

perform overlapped seeking when two drives

are connected and accessed concurrently.

Cartridge Tape Back-up. The 586T and 986T provide cartridge streaming tape back-up for the Hard Disk (up to 60 megabytes per DC600A cartridge).

### **Options**

Several configurations are possible by adding options to the standard systems.

- o <u>Memory Expansion</u>. Memory on the 586T can be expanded to 1 Mbyte by adding a 512 Kbyte Memory Expansion board. (The 986T contains 1 Mbyte of memory as standard equipment).

- o <u>Hard Disk Expansion</u>. The systems support hard disk expansion through two connectors on the rear panel, H.D. EXPANSION and H.D. RADIAL#1, to which data and control cables can be attached.

- o <u>Communications</u>. A Communications printed circuit board supporting SNA or X.25 protocol and four serial (RS232) channels can be installed in lieu of the serial expander board on both the 586T and 986T systems.

### **Operating Systems**

The 586T and 986T run the following operating systems:

- o Concurrent CP/M-86

- o XENIX version 3.0 RTS (Run Time)

### **Related Publications**

The following publications are available from Altos:

| Part Number | <u>Title</u>                       |

|-------------|------------------------------------|

| 15602       | System Maintenance Manual          |

| 16177       | Setting-Up Guide                   |

| 16333       | Illustrated Parts List             |

| 15494       | Introduction to Concurrent CP/M-86 |

| 13499       | Introduction to XENIX              |

| 14646       | WorkNet                            |

### **Specifications**

### Physical Characteristics

| Width  | 16 7/8"    |

|--------|------------|

| Height | 6 <b>"</b> |

| Depth  | 18"        |

| Weight | 36 lbs.    |

### Environmental and Safety Standards

Meets FCC Class A requirements

UL and CSA approved

Ambient Temperature Range 50 - 90 degrees F (15 -32 degrees C)

Relative Humidity non-condensing 20-80%

Power dissipation 300 Watts

### Chapter 2 System Hardware

| Introduction                  |  |  |  | 2-3 |

|-------------------------------|--|--|--|-----|

| Physical Description          |  |  |  |     |

| Central Processing Unit (CPU) |  |  |  |     |

| Controller Board              |  |  |  |     |

| Serial I/O Expander Board     |  |  |  |     |

| 512 Kbyte RAM Expansion Board |  |  |  |     |

|  |  | • |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

### Introduction

This chapter summarizes the system's printed circuit board hardware. The system's I/O devices are discussed in Chapter 5.

### **Physical Description**

The basic 586T/986T system is built around the following subsystems: a CPU printed circuit board, a Controller printed circuit board, a floppy disk drive, hard disk drive, and streaming tape unit. These components comprise the 586T system.

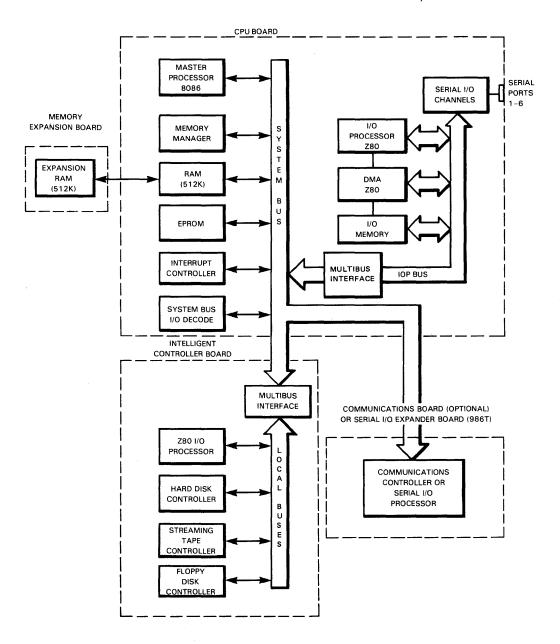

The 986T system includes two more printed circuit boards: a serial expander board which adds four ports to the system, and a 512-Kbyte expansion memory board (see the System Block Diagram, Figure 2-1).

Following is a brief description of the above subsystems.

### Central Processing Unit (CPU) Board

The CPU board is the heart of the system; it contains the master processor for high level problem solving and efficient servicing of the Controller board Hard Disk, Streaming Tape, and Floppy Disk interrupts. A slave I/O processor, a Z80A, handles character interrupts from the serial I/O channels. There are six on-board RS232 ports which can connect to five ASCII terminals and a serial printer or any combination determined by the operating system.

The principal circuits are as follows:

- o 8086 master processor with its peripherals

- o Interrupt Controller and System Timer

- o 512 Kbytes of RAM memory with parity generation and parity error detection

- o Memory Manager and Control circuit

- o EPROM

- o Bus Interface Controller

- o Port Decoder

- o I/O Processor including Z80A CPU, three Z80A SIO/0s, two 8254 timers, and Z80A PIO

CPU board functions are discussed in detail in Chapter 3. The I/O Processor is discussed in detail in Appendix A.

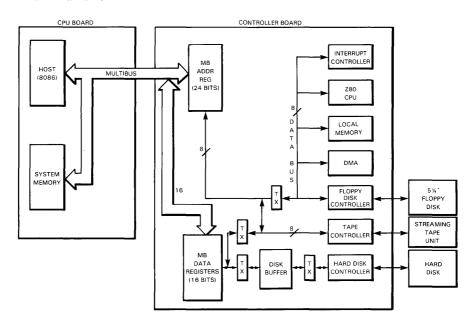

Figure 2-1. System Block Diagram.

### **Controller Board**

The Controller board interfaces to the CPU board and provides channels and control for the system's hard disk(s), floppy disk, and streaming tape unit. These devices are locally controlled by an on-board Z80A processor which receives initial I/O commands from the host processor on the CPU board via command words (parameter blocks). When an I/O operation is completed, a status byte in the command word is updated and the command word is returned to the host.

The following major circuits are contained on the Controller board:

- o Multibus Interface

- o Z8ØA CPU

- o 16Kbyte RAM

- o 8Kbyte PROM

- o AMD 9517 DMA Controller

- o AMD 9519 Interrupt Controller

- o WD2010 Hard Disk Controller

- o 2Kbyte Hard Disk Buffer

- o NEC 765 Floppy Disk Controller

- o Streaming Tape Controller

Controller board functions are described in Chapter 4.

### Serial I/O Expander Board

A Serial I/O Expander board is standard on the 986T (optional on the 586T). It contains a stand-alone I/O processor identical in operation to the I/O Processor on the CPU board. When it is installed, it expands the number of serial channels and RS232 ports by four.

The following hardware is used:

- o Z8ØA CPU

- o Two Z80A SIO/0s

- o Two AMD 9513 system timing counters

- o 8219 Bus Controller

The I/O Processor on the Expander board is discussed in detail in Appendix  ${\tt A.}$

### 512 Kbyte RAM Expansion Board

A RAM Expansion board increases system memory to 1 Mbyte of dynamic RAM. It is standard on the 986T, optional on the 586T.

## Chapter 3 Central Processing Unit Functions

| Introduction                                   |       |       |      |       |   |   |   | 3-3  |

|------------------------------------------------|-------|-------|------|-------|---|---|---|------|

| Hardware Overview                              |       |       |      |       |   |   |   | 3-3  |

| 8086 Master Processor                          | and   | Syst  | em 1 | Memor | y |   |   | 3-3  |

| Memory Organization                            |       |       |      |       | • |   |   | 3-3  |

| Memory Organization<br>Memory Segmentation     |       |       |      |       |   |   |   | 3-4  |

| 8086 Address Genera                            | tion  |       |      |       |   | • |   | 3-5  |

| Altos Memory Manager.                          |       |       |      |       | • |   |   | 3-7  |

| Altos Memory Manager.<br>General Concepts      |       |       |      |       | • | : | • | 3-7  |

| Memory Manager Oper                            | atio  | n     |      |       | • |   |   | 3-8  |

| Memory User Types .                            |       |       |      |       | • | • | • | 3-8  |

| Memory User Types .<br>Memory Management Vio   | lati  | on De | tect | ion   | • | • | • | 3-9  |

| Interrupt Controller.                          |       |       |      |       | • | • | • | 3-10 |

| Interrupt Controller.<br>System Counter Timer. | • •   | • •   | • •  | • •   | • | • | • | 3-10 |

| I/O Processor                                  |       |       |      |       | • | • | • | 3-11 |

| Z80A Processor                                 | • •   |       | • •  | • •   | • | • | • | 3-11 |

| I/O Processor Memor                            |       |       |      |       |   |   |   |      |

| Z80A DMA Controller                            | y • • | • •   | • •  | • •   | • | • | • | 3-12 |

| 790A T/O Addressing                            | • •   | • •   | • •  | • •   | • | • | • | 3-12 |

| Z80A I/O Addressing                            | • •   | • •   | • •  | • •   | • | • | • | 3-12 |

| Calendar Clock                                 |       |       | • •  | • •   | • | • | • | 3-12 |

| System Interfaces                              | • •   | • •   | • •  | • •   | • | • | • | 3 13 |

| System Bus                                     | • •   | • •   | • •  | • •   | • | • | • | 3-13 |

| Conicl I/O Interior                            | ace.  | • •   | • •  | • •   | • | • | • | 3-13 |

| Serial I/O Interfaces                          | • •   | • •   | • •  | • •   | • | • | • | 3-14 |

| RS232C                                         | • •   | • •   | • •  | • •   | • | ٠ | • | 3-14 |

| RS422 (WorkNet)                                | • •   | • • . | • •  | • •   | • | • | • | 3-14 |

| System Initialization a                        | nd O  | perat | ion  | • •   | • | • | • | 3-14 |

| 8086 Reset and Initia                          | liza  | tion  |      |       | • | • | • | 3-14 |

| Maximum and Minimum                            | Mode  | es .  |      |       | • | • | • | 3-15 |

| User Mode and System                           | Mode  |       |      |       | • | • |   | 3-15 |

| Control Bits                                   |       |       |      |       | • | • |   | 3-16 |

| Addressing                                     |       |       |      |       |   |   |   | 3-19 |

| I/O Port Decoder                               |       |       |      |       |   | • |   | 3-19 |

| Memory Management I/O                          | Port  | t Def | init | ion   |   |   |   | 3-21 |

| Memory Management I/O                          | Port  | t Add | ress | ses.  |   |   |   | 3-23 |

| Z80A I/O Addresses                             |       |       |      |       |   |   |   |      |

|                                                | •     |       |      |       | - | - | • |      |

### Introduction

The Central Processing Unit (CPU) board contains the system master processor together with its peripherals, and the character I/O processor and channels. Of interest to the systems engineer and programmer are the programmable devices, memory, and buses; how the system is initialized, its operation, and the addresses of ports and I/O devices.

### **Hardware Overview**

### 8086 Master Processor and System Memory

The 8086 microcomputer chip is the system master processor. It carries out the instructions of the resident operating system and application programs. To achieve maximum throughput and speed, I/O tasks are downloaded by the 8086 to I/O processor subsystems.

The 8086 is a 16-bit microprocessor with 16 data lines and 20 address lines. The address lines provide one megabyte of memory space (2\*\*20 = 1 megabyte). The 8086 assigns a separate 64K byte space for I/O devices and addresses these by the 16 lines, A0 - A15.

### **Memory Organization**

The 8086 organizes memory in arrays of 8-bit bytes. A byte may be stored at an even or an odd address. The 8086 always fetches a word (two bytes) at a time from an even boundary (even-numbered address). Therefore, for maximum processing speed, a word should be stored on an even boundary so that it can be fetched in a single operation. A word stored at an odd boundary requires two fetches.

A word is always stored with the most significant byte in the higher memory location. For example, when 53D7H is stored at memory location 934H, it is stored as follows:

> start of address 935H | D 7 5 3

start of address 934H

### **Memory Segmentation**

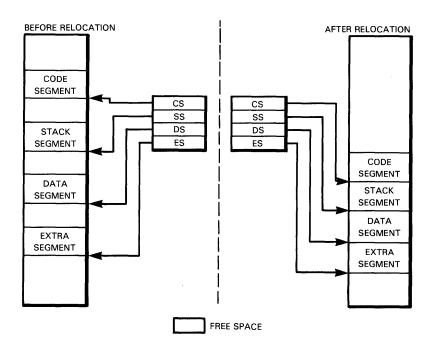

Memory segmentation is a method of efficiently using available memory. Memory space is divided into blocks or segments, each with a base address. Segments can then be moved to provide maximum free space when needed. This is done by placing segments contiguously, or by moving them out to disk. This technique is also known as dynamic memory allocation.

The 8086 divides memory space into 64K byte segments. The location of the segment depends on the value stored in the segment register. There are four types of segment registers, CS, DS, SS, and ES. To obtain more information about segment register operations refer to the 8086 Family User's Manual published by Intel.

Figure 3-1 illustrates the concept of memory segmentation. A segment is relocated in memory simply by changing the base address. However, the 16-bit base address only defines a 64K block. An actual physical address requires 20 bits.

Figure 3-1. Dynamic Relocation

The following section describes how a physical address is generated.

#### 8086 Address Generation

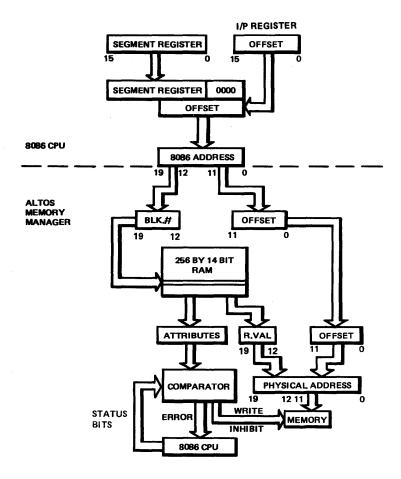

Application programs generally deal with logical, rather than physical addresses, since it is a function of the computer to provide physical addresses for memory locations and I/O devices. The 8086 generates logical addresses for each address-value in a program. A logical address is then translated into a physical address (see Figure 3-2).

Figure 3-2. Memory Management Block Diagram

As shown in Figure 3-2, a 16-bit value is placed in the segment register representing the segment's current location. The register is then shifted left four positions and zeros are appended to the four least significant positions. A 16-bit offset value representing the address in the instruction (from the program) is added to this value. The resulting 20-bit number is the 8086 logical address.

The memory segmentation technique used by the 8086 provides some limited access protection because an offset cannot go beyond the 64K boundary of the segment (2 to the power of 16 = 64K) unless the base value in the segment register is altered. However, the 8086 does not protect against segment overlap. Further, any program may access a segment register at any time. The Altos Memory Management circuit overcomes these limitations (see the following section).

### **Altos Memory Manager**

### **General Concepts**

The Altos Memory Manager extends the 8086 memory management facility. It supports

- o Write protection

- o Access protection

- o Limit checking

- o Non-contiguous memory allocation.

One megabyte of system memory is organized as 256 pages of 4-kilobytes each. Each page has a number of memory protection attributes and can be mapped into any 4 kilobyte block of physical memory. The attribute and mapping bits for all 256 pages of memory are stored in static RAM.

Memory protection, violation detection, and memory mapping all take place during a memory access. When memory is accessed, the mapping bits are used to map the page into the physical memory location. At the same time, the attribute bits are examined to test the validity of the access.

If the access violates any of the attributes, then an interrupt is generated and the address of the access is latched. The CPU can ascertain what the error was by reading the Violation Port (78) and the Error Address ports (60H to 6FH). See tables 3-8 and 3-9.

### **Memory Manager Operation**

See Figure 3-2 for the following discussion. One megabyte of memory address space is divided into 256 pages of 4K (4096) bytes. Each page is numbered from 00 to FF (hexadecimal) and accompanied by six flag and control bits (attributes). This data is stored in a 256 x 14-bit RAM. The RAM is addressed by the eight most-significant bits of the 8086 address. When a memory access is made, a page number (relocation value) is selected to replace the eight most-significant bits of the 8086 logical address and form a 20-bit physical address.

The Memory Management RAM may be accessed through I/O ports 200H to 3FEH to examine the address and attributes of a particular page (see Memory Management I/O Ports and Table 3-6).

### **Memory User Types**

The 8086 memory segmentation scheme divides memory use into four types as shown in Figure 3-1. The Altos 586T/986T further identifies two types of memory users:

- o 8086 applications or operating system users, and

- o Other bus masters.

Each page of memory can be protected from access (either read or write) by application programs. It can also be protected from write access by any of the memory users. For example, the Memory Manager has provisions for protecting each memory page against System Mode memory writes (see User Mode and System Mode for an explanation of System Mode), thus making the page read only. The same page can be marked to disallow access by an Application Mode program.

Finally, the Memory Manager implements the concept of "privileged" instructions. A privileged instruction can only be executed via a request to the operating system. This prevents one problem subprogram from issuing instructions to an I/O device being used by another problem subprogram. All I/O and interrupt

disabling instructions are treated by the 586T/986T as privileged instructions. Applications programs must run with interrupts enabled and make I/O access requests through the operating system. Actual I/O accesses by an application program while it is running are inhibited. An attempt by an applications program to perform an I/O operation causes a System Call interrupt (see Interrupt Controller).

### **Memory Management Violation Detection**

The memory management violation detection circuitry detects operations that violate the attributes of any particular page in memory. For instance, if a page in memory is flagged as a stack boundary page, and a push is performed within the 128-byte guard band at the bottom of the page, then a violation is detected and a nonmaskable interrupt is generated.

Other violations also cause nonmaskable interrupts. They are RAM parity errors, system bus timeout errors, and invalid instruction violations.

All of these violations are latched and can be read at the Violation Port (Port 78). The bits in the violation port are defined in Table 3-7. The violation port is a read-only port. Two bits have been added to the violation port that are not violation bits. They are simply status bits generated by jumpers for use by the system or by automatic testing equipment.

When a violation is detected the address is latched along with the USER MODE bit (see User Mode and System Mode). This gives the system software more information about the violation. This information can be read at ERROR ADDRESS PORT 1 and ERROR ADDRESS PORT 2. The bit definitions for these ports are listed in Tables 3-8 and 3-9.

After a violation has occurred, further violations will not produce nonmaskable interrupts until the current violation has been cleared. Violations can be cleared by performing an I/O instruction to the CLEAR VIOLATION PORT (Port 70h).

Normally, only one violation bit will be set in the violation port if an error occurs. However, if

another violation occurs before the first violation has been cleared, then the new violation will be detected and latched. Thus, more than one violation bit could be set. No information is given about which violation occurred first. Only the address of the first violation is latched.

Under Xenix, the panic trap violation number is read from the Violation Port.

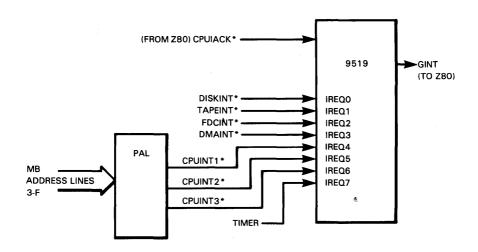

# Interrupt Controller

The interrupt controller is an 8259A-2 device. Port addresses are listed in table 3-4. There are eight interrupt request inputs each of which can be masked on or off. Table 3-1 lists the interrupt request signals in order of decreasing priority.

Bit Interrupt Request Signal Priority IRØ System Call 1 IRl 2 Timer Interrupt IR2 3 Hard Disk Interrupt IR3 Tape Interrupt IR4 I/O Processor Interrupt 5 IR5 INT4 6 7 IR6 INT5 IR7 8 Floppy Disk Interrupt

Table 3-1. Interrupt Priority Levels

# **System Counter Timer**

The system counter timer is an 8254 device located on the system data bus. It is accessed by the 8086 through I/O ports that are listed in Table 3-4 and provides the baud rate for serial port 6 and the system timer interrupt.

There are three counter timers in the 8254:

Counter Timer  $\emptyset$  is used to generate the baud rate for serial port 6.

Counter timer 1 is used as a prescaler for counter timer 2. In other words, the output of counter timer 1 is connected to the input of counter timer 2.

Counter timer 2 output is the system timer interrupt which is connected to the 8259A-2 interrupt controller.

The counting rate for counter 0 and counter 1 is 5 MHz and the counter rate for counter 2 is determined by the output of counter 1.

## I/O Processor

The I/O processor services the system's serial I/O ports. Detailed operation of the I/O Processor is provided in Appendix A. The following is a summary of the hardware. The CPU board contains a Z80A CPU, Z80A DMA, three Z80A SIO's, two 8254 counter timers (or programmable interval timers), 8K x 8 EPROM, 2K x 8 static RAM, 58176A Calendar Clock, 8219 bus arbiter and interface logic.

## **Z80A Processor**

The I/O processor communicates with the host CPU (8086) via calls to system memory locations and CPU interrupts. When the 280A is initialized by an interrupt (IOP Channel Attention) from the 8086, it addresses and then executes a control program residing in local EPROM memory (see I/O Processor Memory). The 280A also employs a small amount (2K) of static RAM for temporary storage and buffering.

## I/O Processor Memory

The Z80A has 64 KB of memory space divided in two halves. The upper 32 KB is mapped to system memory, the lower 32 KB to local EPROM and static RAM. The Z80A can access any part of the 1 MB of system memory

space, but must do so in blocks of 32 KB. This is accomplished by pre-loading a block number register. When the Z80A accesses system memory, it places the block number on Multibus address lines 15 to 19. The Z80A supplies the remainder of the address on its 16 address lines.

Table 3-2 defines the Z80A memory space.

| Memory Type   | Z80A Address   | Range         |

|---------------|----------------|---------------|

| EPROM         | 00h to 1FFFH   | (8K)          |

| STATIC RAM    | 2000 to 27FFH  | (2K)          |

| SYSTEM MEMORY | 8000h to FFFFH | (32KB blocks) |

|               |                | 1             |

Table 3-2. Z80A Memory Map

#### **Z80 DMA Controller**

The Z80A DMA Controller performs dual port data transfer from any of the synchronous serial channels to local memory or system memory. It has the ability to terminate a data transfer as the result of a pattern match.

## **Z80 I/O Addressing**

The Z80A has a 256 byte I/O address space. The I/O addresses for the various peripherals are shown in Table 3-10. Use only addresses shown in the table since not all of the I/O addresses are uniquely decoded.

## Calendar Clock

This CMOS device keeps date and time even when the system power is off. When the system power is off, the clock is powered by a replaceable lithium battery, which has a normal life of two to five years.

# System Interfaces

## System Bus

The Altos 586T/986T system bus is electrically similar to the Intel Multibus. Signals and signal timing are the same. A standard multibus board can be connected to the 586T or 986T system.

There are, however, some differences between the 586T/986T system bus and the Multibus, as listed below.

- o A PARITY ERROR\* signal has been added. This active low signal indicates that a system memory parity error was detected during the current bus cycle. The parity error signal will be valid at least 25 nanoseconds before XACK\* goes active.

- o The INIT\* signal is being driven with a low power Schottky part instead of an open collector driver.

- o Two interrupt request signals, INT4 and INT5 are available for use by an external Multibus board.

- o The signal AACK\* has been added. This is an advanced bus acknowledge signal. When memory is accessed, this active-low signal will be asserted at least 120 nanoseconds before data is valid on the bus.

#### **CPU-Controller Interface**

The CPU board interfaces with the Controller board via the system bus and the Multibus. An 8289 Bus Arbiter exercises control over the system bus to determine which bus master, 8086, Z80A, or Controller board CPU has control. When the Controller board CPU has control, data is transferred through data transceivers by Multibus control logic on the Controller board. Address information is translated directly from the system bus to the Multibus.

## Serial I/O Interfaces

#### **RS232C**

The serial I/O interface consists of three SIOs and two 8254 counter timers. Each SIO supports two serial output ports for a total of six serial I/O ports. Four additional serial I/O ports can be added via a serial expander board. The counter timers are multi-timing elements for the SIOs under software control. The Z80A SIOs are general purpose, dual channel, parallel-to-serial converter/controller devices. The serial channels are normally configured for RS232C asynchronous operation. However, channels 1 and 5 can be strapped (via jumpers) for RS232C synchronous operation (see APPENDIX B).

## RS422 (WorkNet)

Channel 3 can be strapped for operation as an 800 kilobit networking port (RS422) (see WorkNet manual, P/N 690-14646-002).

# System Initialization and Operation

#### 8086 Reset and Initialization

When a power-on or reset condition occurs, the 8086 begins execution at physical address FFFF0H in system memory. A jump instruction at that location points to the beginning of EPROM memory at FE000H. The 8086 executes the code in EPROM, which initializes the system and loads the operating system.

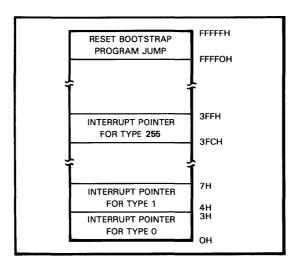

Certain memory locations are reserved by the 8086 for its operations (see Figure 3-3). Locations from 0H to 3FFH are reserved for interrupt pointers. Locations FFFF0H to FFFFFH (top of memory) are reserved for the bootstrap program.

Figure 3-3. Reserved Memory Locations

## Minimum and Maximum Modes

The 8086 is strapped for maximum mode operation, which means that an 8288 bus controller is used to generate bus timing and control signals compatible with the Multibus architecture.

# User Mode and System Mode

The ALTOS 586T and 986T accomplish system memory protection and system configuration protection with the help of a USER MODE bit. The system is in user mode when the bit is set. Application programs should always run in user mode. Conversely, when the bit is not set, the system is said to be in SYSTEM MODE. Operating systems run in system mode.

The system is initialized in system mode and stays in system mode until the User Mode bit is set. All instructions are allowed in system mode. In user mode, I/O instructions are not allowed.

To enter user mode the operating system sets a User Mode Request bit (bit  $\emptyset$ ) in the Control Bits Port (58H). The system then enters user mode when interrupts are enabled. Interrupts must be enabled so that user mode system calls may be processed. Whenever a non-maskable interrupt, maskable interrupt acknowledge, or system reset occurs, the system jumps out of user mode.

All I/O operations are inhibited when the system is in user mode. This prevents application programs from changing the memory management ports or reinitializing the peripherals. Interrupts may not be disabled when in user mode. If they are, then an Invalid Instruction violation is detected and the memory manager produces a non-maskable interrupt which resets the user mode bit.

The normal exit procedure from user mode is through a System Call interrupt (see Table 3-1). A System Call interrupt is generated whenever an I/O instruction is performed while in user mode.

Note that bus masters other than the 8086 may not perform I/O instructions to any port in the range 0000H to 03FFH.

## **Control Bits**

Three system control bits may be written through the Control Bits Port (58H). They are:

- o Request User Mode

- Enable Non-Maskable Interrupt

- o Warm Start Bit

The Request User Mode bit is set as described under User Mode and System Mode.

The Enable Non-Maskable Interrupt bit enables non-maskable interrupts when set to 1. It is disabled at power-up or reset and is intended primarily for diagnostic purposes.

The Warm Start bit is accessible for use by system software, but is not actually used. It indicates whether the system was initialized by a power-up or by the reset switch. Power-up always clears this bit, but reset sets the bit. If the bit is set to a 1, the system start was a warm start (reset).

Table 3-3 shows bit definition.

Table 3-3. Control Bits Port Definition (Port 58H)

| ВІТ | BIT NAME                      | TRUE |

|-----|-------------------------------|------|

| Ø   | Request User Mode             | 1    |

| 1   | Not Used                      | 1    |

| 2   | Enable Non-maskable Interrupt | 1    |

| 3   | Not Used                      | 1    |

| 4   | Not Used                      | 1    |

| 5   | Not Used                      | 1    |

| 6   | Not Used                      | 1    |

| 7   | Not Used                      | 1    |

| 8   | Warm Start Bit, Not Used      | 1    |

| 9   | Not Used                      | 1    |

| 10  | Not Used                      | 1    |

| 11  | Not used                      | 1    |

| 12  | Not Used                      | 1    |

| 13  | Not Used                      | 1    |

| 14  | Not Used                      | 1    |

| 15  | Not Used                      | 1    |

<sup>\*</sup> This bit is set to 0 at power-up.

# **Addressing**

# I/O Port Decoder

The 8086 can support both 8-bit and 16-bit I/O for a total of 65,536 addressable ports. Not all address combinations are used in this application. For eight bit I/O operations, the 8086 uses half of the 16-bit data bus for even I/O addresses and the other half for odd I/O addresses. Even addresses cause data to be moved over Data Bus bits 0 through 7.

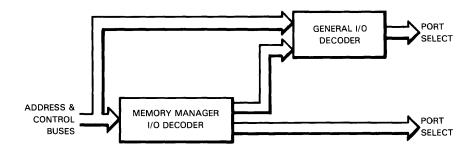

The block diagram for the 586T/986T I/O port decoder is shown in Figure 3-4. The decoder has two parts: The memory manager port decoder and the general I/O port decoder.

Table 3-4 shows the hex addresses, port size and functions for the I/O ports. Note that port sizes are shown as  $\emptyset$ , 8, or 16 bits, where:

- Means the port is 8 or 16-bit access, but does not use the data bus.

- 8 means 8-bit access, using the data bus.

- 16 means 16-bit access, using the data bus.

Figure 3-4. I/O Port Decoder Block Diagram

Table 3-4. 8086 I/O Port Addresses

NOTE: Ports 0000H through 003FH are not decoded

| Hex Address                                    | Port Size<br>(in bits) | Function and Comments                                                                                                                        |  |

|------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0040h to 0047                                  | Ø                      | Clear System Call                                                                                                                            |  |

| 0048h to 004FH                                 | Ø                      | Channel attention Ø<br>(reserved for future bus<br>master channel attentions)                                                                |  |

| 0050h to 0057H                                 | Ø                      | Z80A I/O Processor Chan att.                                                                                                                 |  |

| 0058h to 005FH                                 | 16                     | Control Bits Port -<br>Write Only. See Table 3-3.                                                                                            |  |

| 0060h to 0067H                                 | 16                     | Error Address 2 - Read<br>Only. See Table 3-9.                                                                                               |  |

| 0068h to 006FH                                 | 16                     | Error Address 1 - Read<br>Only. See Table 3-8.                                                                                               |  |

| 0070h to 0077H                                 | Ø                      | Clear Violation Port                                                                                                                         |  |

| 0078h to 007FH                                 | 16                     | Violation Port - Read<br>Only. See Table 3-7.                                                                                                |  |

| * * * INT                                      | ERRUPT CONT            | TROLLER PORTS * * *                                                                                                                          |  |

| 0080<br>0081<br>0082<br>0083<br>0084H to 00FFH | 8                      | ICW2, ICW3, ICW4, or OCW1 Decoded but not used ICW1, OCW2, or OCW3 Decoded but not used Do not use these ports!!! They map into ports 80-83. |  |

| * * * 8254 SYSTEM TIMER PORTS * * *            |                        |                                                                                                                                              |  |

| Ø100H                                          |                        | Decoded but not used                                                                                                                         |  |

| Ø1Ø1H                                          | 8                      | Control Word Register -<br>Write Only                                                                                                        |  |

| Ø102H                                          |                        | Decoded but not used                                                                                                                         |  |

Table 3-4 (Cont'd). 8086 I/O Port Address Definitions

| Hex Address                   | Port Size<br>(in bits) | Function and Comments                                                                             |

|-------------------------------|------------------------|---------------------------------------------------------------------------------------------------|

| Ø103H                         | 8                      | Counter 2                                                                                         |

| 0104h                         |                        | Decoded but not used                                                                              |

| Ø1Ø5H                         | 8                      | Counter 1                                                                                         |

| Ø1 Ø6 H                       |                        | Decoded but not used                                                                              |

| Ø1 Ø7                         | 8                      | Counter Ø                                                                                         |

| Ø1Ø8H to Ø1FFH                |                        | Do not use these ports!!! They map into the system timer ports (100-107).                         |

| * * *                         | MEMORY MAN             | NAGEMENT PORTS * * *                                                                              |

| 0200H to 03FFH 0400H to FFFFH | 16                     | Memory Management Ports Even addresses only. See Tables 3-5 and 3-6. Reserved for system bus I/O. |

# Memory Management I/O Port Definition

The following table shows the bit definition of the Memory Management ports. A detailed explanation of each bit follows on the next page. Table 3-6 is a listing of the port addresses.

| Table 3 | 3-5. | Memory | Management | I/O | Port | Definition |

|---------|------|--------|------------|-----|------|------------|

|---------|------|--------|------------|-----|------|------------|

|     | Map and Attribute Bit Definition |      |

|-----|----------------------------------|------|

| Bit | Bit Name                         | True |

| ø   | Physical Address 12              | 1    |

| 1   | Physical Address 13              | 1    |

| 2   | Physical Address 14              | 1    |

| 3   | Physical Address 15              | 1    |

| 4   | Physical Address 16              | 1 1  |

| 5   | Physical Address 17              | 1    |

| 6   | Physical Address 18              | 1    |

| 7   | Physical Address 19              | 1    |

| 8   | Not Used, Undefined              |      |

| 9   | Not Used, undefined              |      |

| 10  | Not Used, Undefined              |      |

| 11  | Allow I/O Processor Write        | 1    |

| 12  | Allow System Write               | 1    |

| 13  | Stack Boundary Page              | 1    |

| 14  | Allow User Access                | 1    |

| 15  | Allow User Write                 | 1    |

Following is a detailed description of each bit:

### **Bits**

Ø through 7 define the physical address of the page in memory. Suppose that port 268H (port for page 34H) has bits Ø through 7 set to 57H. This would reposition logical addresses 34000H-34FFFH into physical memory locations 57000H-57FFFH. The port addresses for each page in memory are listed in Table 3-1.

8, 9 and 10 are undefined.

ll is the Allow I/O Processor Write bit; when this bit is set to a l, it allows any bus master other than the 8086 to write to that page in memory.

12 is the Allow System Write bit. When this bit is set to a 1, the 8086 in SYSTEM MODE(not USER MODE) is allowed to perform a write to that page in memory.

- 13 is the Stack Boundary Page bit. When set to a 1, this bit indicates to the violation detection circuitry that the stack may not grow below that page in memory.

- 14 is the Allow User Access bit. When this bit is set to a 1, the 8086 in user mode can perform reads or writes to that page in memory.

- 15 is the Allow User Write bit. When this bit is set to 1, the 8086 in user mode can perform memory writes to that page in memory.

#### NOTE

For the 8086 to write a page in USER MODE, both bits 14 and 15 should be set for that page.

If a read or write to a memory page is attempted and it conflicts with any of the attribute bits, a memory violation is generated. See Memory Management Violation Detection.

# Memory Management I/O Port Addresses

The 256 by 14 bit RAM portion of the Memory Manager is accessed through 256 I/O ports having even numbered addresses from 200H through 3FEH. The memory page number and the logical address range for each port is listed in Table 3-6.

Table 3-6. Memory Management I/O Port Addresses

|        | LOGICAL                    |                       |

|--------|----------------------------|-----------------------|

| BLOCK  | ADDRESS                    | ATTRIBUTE AND MAPPING |

| NUMBER | RANGE                      | PORT ADDRESS          |

|        |                            |                       |

| 00     | 00000-00FFF                | 0200                  |

| 01     | 01000-01FFF                | 0202                  |

| 02     | 02000-02FFF                | 0204                  |

| 03     | 03000-03FFF                | 0206                  |

| 04     | 04000-04FFF                | 0208                  |

| Ø5     | 05000-05FFF                | Ø 2 Ø A               |

| 96     | 06000-06FFF                | Ø 2 Ø C               |

| Ø7     | 07000-07FFF                | Ø 2Ø E                |

|        | D7000 D7111                | V 20 4                |

| Ø8     | Ø8ØØØ-Ø8FFF                | Ø 21 Ø                |

| Ø9     | 09000-09FFF                | 0212                  |

| ØA     | ØAØØØ-ØAFFF                | Ø 21 4                |

| ØB     | ØBØØØ-ØBFFF                | 0216                  |

| ØC     | ØCØØØ-ØCFFF                | Ø218                  |

| ØD     | ØDØØØ-ØDFFF                | Ø21A                  |

| ØE     | ØEØØØ-ØEFFF                | Ø21C                  |

| ØF     | ØFØØØ-ØFFFF                | 021 E                 |

| 1      | DI DDD DIIII               | 9211                  |

| 10     | 10000-10FFF                | Ø22Ø                  |

| 11     | 11000-11FFF                | 0222                  |

| 12     | 12000-12FFF                | 0224                  |

| 13     | 13000-13FFF                | Ø 226                 |

| 14     | 14000-14FFF                | Ø228                  |

| 15     | 15000-14FFF<br>15000-15FFF | 022A                  |

| 16     | 16000-15FFF<br>16000-16FFF | 022C                  |

| 17     | 17000-10FFF<br>17000-17FFF | 022E                  |

| 1      | 1/000-1/111                | 622E                  |

| 18     | 18000-18FFF                | Ø 23 Ø                |

| 19     | 19000-19FFF                | Ø232                  |

| 1A     | 1A000-1AFFF                | Ø23 <b>4</b>          |

| 1B     | 1B000-1BFFF                | Ø236                  |

| 1c     | 1C000-1CFFF                | Ø238                  |

| 1D     | 1D000-1CFFF                | 023A                  |

| 1 1 E  | 1D000-1DFFF<br>1E000-1EFFF | 023A<br>023C          |

| 1F     | 1E000-1EFFF<br>1F000-1FFFF | 0 23 E                |

| 14     | TEAMA_TEELE                | N 72 E                |

Table 3-6 (Cont'd). Memory Management I/O Port Addresses

| <del></del> | <u></u>                    | ,                     |

|-------------|----------------------------|-----------------------|

|             | LOGICAL                    |                       |

| BLOCK       | ADDRESS                    | ATTRIBUTE AND MAPPING |

| NUMBER      | RANG E                     | PORT ADDRESS          |

| 20          | 20000-20FFF                | 0240                  |

| 21          | 21000-21FFF                | 0242                  |

| 22          | 22000-22FFF                | 0244                  |

| 23          | 23000-23FFF                | 0246                  |

| 24          | 24000-24FFF                | 0248                  |

| 25          | 25000-25FFF                | 024A                  |

| 26          | 26000-26FFF                | Ø24C                  |

| 27          | 27000-27FFF                | Ø24E                  |

| 28          | 28000-28FFF                | Ø 25 Ø                |

| 29          | 29000-29FFF                | Ø 252                 |

| 2A          | 2A000-2AFFF                | Ø 25 4                |

| 2B          | 2B000-2BFFF                | Ø 256                 |

| 25          | 20000-20111                | <b>5250</b>           |

| 2C          | 2CØØØ-2CFFF                | Ø 25 8                |

| 2D          | 2DØØØ-2DFFF                | Ø25A                  |

| 2E          | 2EØØØ-2EFFF                | Ø25C                  |

| 2F          | 2F000-2FFFF                | Ø 25 E                |

| 30          | 30000-30FFF                | Ø 26 Ø                |

| 31          | 31000-31FFF                | 0262                  |

| 32          | 32000-32FFF                | 0264                  |

| 33          | 33000-33FFF                | 0266                  |

| 34          | 34000-34FFF                | 0268                  |

| 35          | 35000-35FFF                | Ø 26 A                |

| 36          | 36000-35FFF<br>36000-36FFF | Ø 26 C                |

| 37          | 37000-37FFF                | Ø 26 E                |

| 3/          | 3/888-3/555                | ₩ 20 E                |

| 38          | 38000-38FFF                | Ø 27 Ø                |

| 39          | 39000-39FFF                | Ø 27 2                |

| 3A          | 3AØØØ-3AFFF                | 0274                  |

| 3B          | 3B000-3BFFF                | 0276                  |

| 3C          | 3C000-3CFFF                | 0278                  |

| 3D          | 3DØØØ-3DFFF                | Ø 27 A                |

| 3E          | 3EØØØ-3EFFF                | Ø 27 C                |

| 3F          | 3FØØØ-3FFFF                | 027 E                 |

|             | OLDED STIFF                | V 2 / L               |

Table 3-6 (Cont'd). Memory Management I/O Port Addresses

|            | <del>,</del> |                       |

|------------|--------------|-----------------------|

|            | LOGICAL      |                       |

| BLOCK      | ADDRESS      | ATTRIBUTE AND MAPPING |

| NUMBER     | RANGE        | PORT ADDRESS          |

|            |              |                       |

| 40         | 40000-40FFF  | Ø 28 Ø                |

| 41         | 41000-41FFF  | Ø 282                 |

| 42         | 42000-42FFF  | Ø284                  |

| 43         | 43000-43FFF  | Ø286                  |

|            |              |                       |

| 44         | 44000-44FFF  | 0288                  |

| 45         | 45000-45FFF  | Ø28A                  |

| 46         | 46000-46FFF  | Ø28C                  |

| 47         | 47000-47FFF  | Ø28E                  |

| 40         | 40000 4000   | 4004                  |

| 48         | 48000-48FFF  | 0290                  |

| 49         | 49000-49FFF  | 0292                  |

| 4A         | 4A000-4AFFF  | 0294                  |

| 4B         | 4B000-4BFFF  | 0296                  |

| 4C         | 4C000-4CFFF  | 0298                  |

| 4D         | 4D000-4DFFF  | Ø 29 A                |

| 4 E        | 4E000-4EFFF  | Ø 29 C                |

| 4F         | 4F000-4FFFF  | Ø 29 E                |

|            | 11 000 11111 | 5252                  |

| 5Ø         | 50000-50FFF  | Ø 2AØ                 |

| 51         | 51000-51FFF  | Ø 2A2                 |

| 52         | 52000-52FFF  | Ø 2A4                 |

| 53         | 53000-53FFF  | Ø2A6                  |

|            |              |                       |

| 54         | 54000-54FFF  | Ø2A8                  |

| 55         | 55000-55FFF  | Ø2AA                  |

| 56         | 56000-56FFF  | Ø 2AC                 |

| 57         | 57000-57FFF  | Ø 2AE                 |

| 58         | 58000-58FFF  | Ø 2BØ                 |

| 59         | 59000-59FFF  | 0 2B0<br>0 2B2        |

| 5A         | 5A000-5AFFF  | 02B2<br>02B4          |

| 5B         | 5B000-5BFFF  | 02B6                  |

| 35         | JD000-JDEFF  | 2200                  |

| 5C         | 5CØØØ-5CFFF  | Ø2B8                  |

| 5D         | 5DØØØ-5DFFF  | Ø2BA                  |

| 5 E        | 5E000-5EFFF  | Ø 2BC                 |

| 5 <b>F</b> | 5F000-5FFFF  | Ø 2B E                |

|            |              |                       |

Table 3-6 (Cont'd). Memory Management I/O Port Addresses

| ĺ      | LOGICAL         |                       |

|--------|-----------------|-----------------------|

| BLOCK  | ADDRESS         | ATTRIBUTE AND MAPPING |

| NUMBER | RANG E          | PORT ADDRESS          |

|        |                 |                       |

| 6Ø     | 60000-60FFF     | Ø 2CØ                 |

| 61     | 61000-61FFF     | Ø2C2                  |

| 62     | 62000-62FFF     | Ø 2C4                 |

| 63     | 63000-63FFF     | Ø2C6                  |

|        |                 |                       |

| 64     | 64000-64FFF     | Ø 2C8                 |

| 65     | 65000-65FFF     | Ø2CA                  |

| 66     | 66000-66FFF     | Ø2CC                  |

| 67     | 67000-67FFF     | Ø2CE                  |

|        |                 |                       |

| 68     | 68000-68FFF     | Ø 2DØ                 |

| 69     | 69000-69FFF     | Ø2D2                  |

| 6A     | 6AØØØ-6AFFF     | Ø2D4                  |

| 6B     | 6B000-6BFFF     | Ø 2D6                 |

| ]      | 02022 02111     | J = J V               |

| 6C     | 6CØØØ-6CFFF     | Ø2D8                  |

| 6D     | 6DØØØ-6DFFF     | Ø2DA                  |

| 6 E    | 6E000-6EFFF     | Ø2DC                  |

| 6F     | 6F000-6FFFF     | Ø 2DE                 |

|        |                 | <u> </u>              |

| 7 Ø    | 70000-70FFF     | Ø 2 E Ø               |

| 71     | 71000-71FFF     | Ø 2 E 2               |

| 72     | 72000-72FFF     | Ø 2 E 4               |

| 73     | 73000-73FFF     | Ø 2E6                 |

|        |                 | <u> </u>              |

| 74     | 74000-74FFF     | Ø 2 E 8               |

| 75     | 75000-75FFF     | Ø 2 E A               |

| 76     | 76000-76FFF     | Ø 2 E C               |

| 77     | 77000-77FFF     | 02EE                  |

| 1      |                 |                       |

| 78     | 78000-78FFF     | Ø2FØ                  |

| 79     | 79000-79FFF     | 02F2                  |

| 7A     | 7A000-7AFFF     | 02F4                  |

| 7B     | 7B000-7BFFF     | Ø2F6                  |

|        | 5 5 5 7 5 1 1 1 | 5210                  |

| 7C     | 7CØØØ-7CFFF     | Ø2F8                  |

| 7D     | 7D000-7DFFF     | Ø2FA                  |

| 7E     | 7E000-7EFFF     | 02FC                  |

| 7F     | 7FØØØ-7FFFF     | 02FE                  |

| L      |                 | <b></b>               |

Table 3-1 (Cont'd). Memory Management I/O Port Addresses

|          | LOGICAL                    |                       |

|----------|----------------------------|-----------------------|

| BLOCK    | ADDRESS                    | ATTRIBUTE AND MAPPING |

| NUMBER   | RANGE                      | PORT ADDRESS          |

|          |                            |                       |

| 8Ø       | 80000-80FFF                | Ø3ØØ                  |

| 81       | 81000-81FFF                | Ø3Ø2                  |

| 82       | 82000-82FFF                | Ø3Ø4                  |

| 83       | 83000-83FFF                | Ø3Ø6                  |

|          |                            |                       |

| 84       | 84000-84FFF                | Ø3Ø8                  |

| 85       | 85000-85FFF                | Ø3ØA                  |

| 86       | 86000-86FFF                | Ø3ØC                  |

| 87       | 87000-87FFF                | Ø3ØE                  |

|          |                            |                       |

| 88       | 88000-88FFF                | Ø31Ø                  |

| 89       | 89000-89FFF                | Ø312                  |

| 8A       | 8A000-8AFFF                | 0314                  |

| 8B       | 8B000-8BFFF                | Ø316                  |

|          |                            |                       |

| 8C       | 8CØØØ-8CFFF                | Ø318                  |

| 8D       | 8DØØØ-8DFFF                | Ø31A                  |

| 8E       | 8E000-8EFFF                | Ø31C                  |

| 8F       | 8FØØØ-8FFFF                | Ø31E                  |

|          |                            |                       |

| 90       | 90000-90FFF                | 0320                  |

| 91       | 91000-91FFF                | 0322                  |

| 92       | 92000-92FFF                | Ø32 <b>4</b>          |

| 93       | 93000-93FFF                | Ø326                  |

| 94       | 94000-94FFF                | Ø328                  |

| 95       | 95000-95FFF                | Ø328                  |

| 96       |                            |                       |

| 96<br>97 | 96000-96FFF                | Ø32C                  |

| 97       | 97000-97FFF                | Ø32E                  |

| 98       | 98000-98FFF                | 0330                  |

| 99       | 99000-99FFF                | Ø332                  |

| 9A       | 9A000-99FFF<br>9A000-9AFFF | Ø332<br>Ø334          |

| 9B       | 9B000-9BFFF                | Ø334<br>Ø336          |

| 30       | ייים ב-שששטנ               | #330                  |

| 9C       | 9C000-9CFFF                | Ø338                  |

| 9D       | 9D000-9DFFF                | Ø33A                  |

| 9E       | 9E000-9EFFF                | Ø33C                  |

| 9F       | 9FØØØ-9FFFF                | Ø33E                  |

| 91       | JI DUD-JI I I              | 9331                  |

Table 3-6 (Cont'd). Memory Management I/O Port Addresses

|        |             | T                     |

|--------|-------------|-----------------------|

|        | LOGICAL     |                       |

| BLOCK  | ADDRESS     | ATTRIBUTE AND MAPPING |

| NUMBER | RANG E      | PORT ADDRESS          |

|        |             |                       |

| AØ     | A0000-A0FFF | 0340                  |

| Al     | Al000-Alfff | Ø3 <b>4</b> 2         |

| A2     | A2000-A2FFF | 0344                  |

| A3     | A3000-A3FFF | 0346                  |

|        | 34666 34DDD | #240                  |

| A4     | A4000-A4FFF | 0348<br>034A          |

| A5     | A5000-A5FFF |                       |

| A6     | A6000-A6FFF | Ø34C                  |

| A7     | A7000-A7FFF | Ø34E                  |

| A8     | A8000-A8FFF | Ø35Ø                  |

| A9     | A9000-A9FFF | Ø352                  |

| AA     | AAØØØ-AAFFF | Ø354                  |

| AB     | ABØØØ-ABFFF | Ø356                  |

| ]      |             | <b>7350</b>           |

| AC     | AC000-ACFFF | 0358                  |

| AD     | ADØØØ-ADFFF | Ø35A                  |

| AE     | AEØØØ-AEFFF | Ø35C                  |

| AF     | AFØØØ-AFFFF | Ø35E                  |

| ВØ     | BØØØØ-BØFFF | Ø36Ø                  |

| Bl     | B1000-B1FFF | Ø362                  |

| B2     | B2000-B2FFF | Ø364                  |

| В3     | B3000-B3FFF | 0366                  |

|        |             | 72.0                  |

| B4     | B4000-B4FFF | 0368                  |

| B5     | B5000-B5FFF | Ø36A                  |

| B6     | B6000-B6FFF | 036C                  |

| В7     | B7000-B7FFF | Ø36 E                 |

| В8     | B8000-B8FFF | 0370                  |

| B9     | B9000-B9FFF | Ø372                  |

| BA     | BA000-BAFFF | 0374                  |

| BB     | BB000-BBFFF | 0376                  |

|        |             |                       |

| BC     | BC000-BCFFF | 0378                  |

| BD     | BDØØØ-BDFFF | Ø37A                  |

| BE     | BE000-BEFFF | 037C                  |

| BF     | BFØØØ-BFFFF | Ø37 E                 |

Table 3-6 (Cont'd). Memory Management I/O Port Addresses

|          | LOGICAL                    |                       |

|----------|----------------------------|-----------------------|

| BLOCK    | ADDRESS                    | ATTRIBUTE AND MAPPING |

| NUMBER   | RANGE                      | PORT ADDRESS          |

|          |                            |                       |

| CØ       | CØØØØ-CØFFF                | Ø38Ø                  |

| Cl       | C1000-C1FFF                | Ø382                  |

| C2       | C2000-C2FFF                | Ø384                  |

| С3       | C3000-C3FFF                | Ø386                  |

| C4       | C4000-C4FFF                | Ø388                  |

| C5       | C5000-C5FFF                | 038A                  |

| C6       | C6000-C6FFF                | Ø38C                  |

| C7       | C7000-C7FFF                | 038E                  |

| C,       | C/UUD-C/FFF                | A20 F                 |

| C8       | C8000-C8FFF                | Ø39Ø                  |

| C9       | C9000-C9FFF                | Ø392                  |

| CA       | CA000-CAFFF                | 0394                  |

| СВ       | CB000-CBFFF                | Ø396                  |

| cc       | CC000-CCFFF                | Ø398                  |

| CD       | CDØØØ-CDFFF                | Ø39A                  |

| CE       | CEØØØ-CEFFF                | Ø39C                  |

| CF       | CFØØØ-CFFFF                | Ø39E                  |

| DØ       | DØØØØ-DØFFF                | Ø3AØ                  |

| DI DI    | D1000-D0FFF                | 03A2                  |

| D1<br>D2 | D2000-D1FFF<br>D2000-D2FFF | 03A2<br>03A4          |

| D3       | D3000-D2FFF<br>D3000-D3FFF | 03A4<br>03A6          |

| 23       | DJ000 DJIII                | <b>85A</b> 0          |

| D4       | D4000-D4FFF                | Ø3A8                  |

| D5       | D5000-D5FFF                | Ø3AA                  |

| D6       | D6000-D6FFF                | Ø3AC                  |

| D7       | D7000-D7FFF                | Ø3AE                  |

| D8       | D8000-D8FFF                | Ø3BØ                  |

| D9       | D9000-D9FFF                | Ø3B2                  |

| DA       | DAØØØ-DAFFF                | Ø3B4                  |

| DB       | DB000-DBFFF                | Ø3B6                  |

| DC       |                            | #2po                  |

| DD       | DC000-DCFFF                | Ø3B8                  |

|          | DDØØØ-DDFFF                | Ø3BA                  |

| DE<br>DF | DE000-DEFFF<br>DF000-DFFFF | 03BC<br>03BE          |

| DE       | ממשםט-טבנדד                | MODE                  |

Table 3-6 (Cont'd). Memory Management I/O Port Addresses

|                | LOGICAL     |                       |

|----------------|-------------|-----------------------|

| BLOCK          | ADDRESS     | ATTRIBUTE AND MAPPING |

| NUMBER         | RANGE       | PORT ADDRESS          |

| NUMBER         | KANGE       | PORT ADDRESS          |

| EØ             | EØØØØ-EØFFF | Ø3CØ                  |

| El             | El000-Elfff | Ø3C2                  |

| E2             | E2ØØØ-E2FFF | Ø3C4                  |

| E3             | E3000-E3FFF | Ø3C6                  |

| '              |             |                       |

| E4             | E4000-E4FFF | Ø3C8                  |

| E5             | E5000-E5FFF | Ø3CA                  |

| E6             | E6000-E6FFF | Ø3CC                  |

| E7             | E7000-E7FFF | Ø3CE                  |

|                |             | j                     |

| E8             | E8000-E8FFF | Ø3DØ                  |

| E9             | E9000-E9FFF | Ø3D2                  |

| EA             | EAØØØ-EAFFF | Ø3D4                  |

| EB             | EBØØØ-EBFFF | Ø3D6                  |

|                |             |                       |

| EC             | ECØØØ-ECFFF | Ø3D8                  |

| ED             | EDØØØ-EDFFF | Ø3DA                  |

| EE             | EE000-EEFFF | Ø3DC                  |

| EF             | EFØØØ-EFFFF | Ø3DE                  |

| FØ             | Dagga Babbb | a 2 ma                |

| F1             | FØØØØ-FØFFF | Ø3EØ                  |

|                | F1000-F1FFF | Ø3E2                  |

| F2<br>F3       | F2000-F2FFF | Ø3E4                  |

| r <sub>3</sub> | F3000-F3FFF | Ø3E6                  |

| F4             | F4000-F4FFF | Ø3E8                  |

| F5             | F5000-F5FFF | Ø3EA                  |

| F6             | F6000-F6FFF | Ø3EC                  |

| F7             | F7000-F7FFF | 03EE                  |

| i              |             | 2022                  |

| F8             | F8000-F8FFF | Ø3FØ                  |

| F9             | F9000-F9FFF | Ø3F2                  |

| FA             | FA000-FAFFF | Ø3F4                  |