Advanced Micro Devices, Inc.

AmSYS29/10A Microprogram Development System

**User's Manual**

059920027-002 \$15.00

|          | REVISION RECORD                        |             |  |

|----------|----------------------------------------|-------------|--|

| REVISION |                                        | DESCRIPTION |  |

| 01       | Preliminary Issue                      |             |  |

| 08/20/82 |                                        |             |  |

| Α        | Initial Release                        |             |  |

| 1/10/83  |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          | ······································ |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

|          |                                        |             |  |

059920027-002

Publication No.

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1982, 1983 Advanced Micro Devices Printed in U.S.A. Address comments concerning this manual to:

ADVANCED MICRO DEVICES

Microcomputer Systems

Publications Department

P.O. Box 453

Sunnyvale, CA 94086

#### PREFACE

This manual provides complete installation, operation, and interface information for the Advanced Micro Devices AmSYS29/10A\* Microprogram Development System. In addition, the manual includes thorough coverage on the theory of operation of the AmSYS29/10A system.

The information in this publication is believed to be accurate in all respects. However, no responsibility is assumed for errors that might appear in this publication. Advanced Micro Devices disclaims responsibility for any consequences resulting from the use thereof. No part of this manual may be copied or reproduced in any form without prior written permission from AMD.

These products are intended for use only as described in this document.

Advanced Micro Devices cannot be responsible for the proper functioning of undescribed features or parameters.

The information presented herein to configure the RAM boards is applicable only to the Am96/1064 board. The Am97/0064 board does not require configuration; if your system uses this board, configuration information is redundant.

Interconnect information and schematic drawings are contained in a separate drawing package.

Detailed information on the AMD Writable Control Store is presented in AMD document 059920003-001, High Speed Writable Control Store User's Manual.

This manual is intended to be used in conjunction with the following AMD documents:

AmSYS29/10 Microprogram Support Software User's Manual 059910514-001

AMDOS 29 Operating System User's Manual 059910500-001

<sup>\*</sup> AmSYS is a trademark of Advanced Micro Devices, Inc.

### TABLE OF CONTENTS

| 1. | GENERAL INFORMATION Introduction Physical Description Functional Description Hardware Features Software Microprogram Generation Software | 1-1<br>1-1<br>1-2<br>1-4<br>1-6<br>1-12 |

|----|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|    | Example Files                                                                                                                            | 1-15                                    |

| 2. | INSTALLATION                                                                                                                             | 2-1                                     |

|    | Introduction                                                                                                                             | 2-1                                     |

|    | Unpacking and Inspection Preparation for Use                                                                                             | 2-1<br>2-1                              |

| 3. | OPERATION                                                                                                                                | 3-1                                     |

|    | Introduction                                                                                                                             | 3-1                                     |

|    | Diskette Insertion                                                                                                                       | 3-1                                     |

|    | System Initialization Operation                                                                                                          | 3-3                                     |

| 4. | SYSTEM SOFTWARE                                                                                                                          | 4-1                                     |

|    | Introduction                                                                                                                             | 4-1                                     |

|    | AMDOS29 Operating System                                                                                                                 | 4-1                                     |

|    | Microprogram Support Software                                                                                                            | 4-3                                     |

| 5. | THEORY OF OPERATION                                                                                                                      | 5-1                                     |

|    | Introduction                                                                                                                             | 5-1                                     |

|    | System Processor                                                                                                                         | 5-1                                     |

|    | Microprogrammed Controller                                                                                                               | 5-10                                    |

|    | Clock Control Logic Card                                                                                                                 | 5-12                                    |

|    | Writable Control Store Card                                                                                                              | 5-22                                    |

|    | Microprogram Sequencer (Computer Control Unit) Card                                                                                      | 5-26                                    |

| 6. | Amsys29/10A INTERFACE                                                                                                                    | 6-1                                     |

|    | Microprogrammed Controller System Clock                                                                                                  | 6-1                                     |

|    | External Prototype Connection                                                                                                            | 6-5                                     |

|    | Interface Signal Functions                                                                                                               | 6-6                                     |

|    | Microprogram Address Bus (MPAO-MPA11)                                                                                                    | 6-10                                    |

|    | Sequencer Disable ((SQE)                                                                                                                 | 6-10                                    |

|    | Microprogram Data Bus<br>Oscillator Input                                                                                                | 6-11                                    |

|    | Controlled Oscillator                                                                                                                    | 6-11<br>6-12                            |

|    | System Clock                                                                                                                             | 6-12                                    |

|    | System Clock Control                                                                                                                     | 6-13                                    |

|    | Monitor Bits                                                                                                                             | 6-13                                    |

|    | Address Breakpoint Sync Pulse                                                                                                            | 6-14                                    |

|    | Interrupt 5                                                                                                                              | 6-14                                    |

|    | Trap bits                                                                                                                                | 6-14                                    |

|    | Test Condition Multiplexer Inputs                                                                                                        | 6-15                                    |

|    | 16-Way Branch Test Inputs                                                                                                                | 6-15                                    |

|    | Interrupt Vector Inputs                                                                                                                  | 6-15                                    |

|    | Main Memory Data Bus                                                                                                                     | 6-17                                    |

|    | Signal Connector Information                                                                                                             | 6-16                                    |

### LIST OF ILLUSTRATIONS

| Figure | Title                                                 | Page |

|--------|-------------------------------------------------------|------|

| 1-1    | Controls and Indicators                               | 1-5  |

| 1-2    | AmSYS29/10A Block Diagram                             | 1-7  |

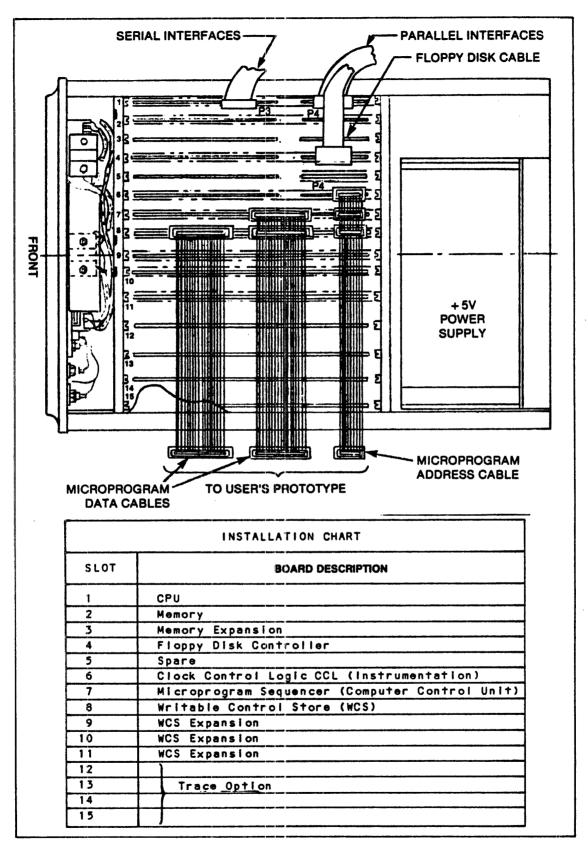

| 1-3    | System Mainframe Configuration                        | 1-9  |

| 2-1    | Voltage Test Points                                   | 2-6  |

| 2-2    | Board Edge Connectors                                 | 2-7  |

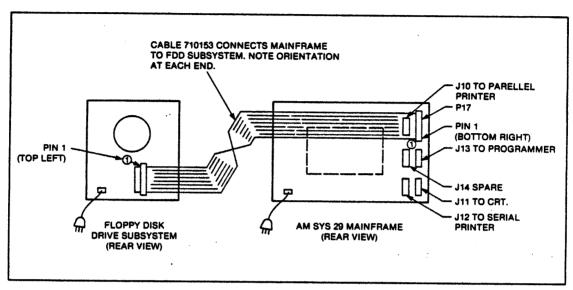

| 2-3    | AmSYS29/10A Interconnection Diagram                   | 2-8  |

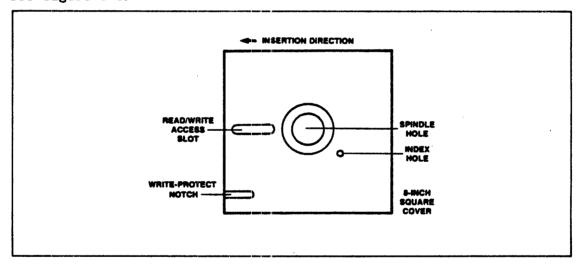

| 3-1    | Floppy Diskette                                       | 3-1  |

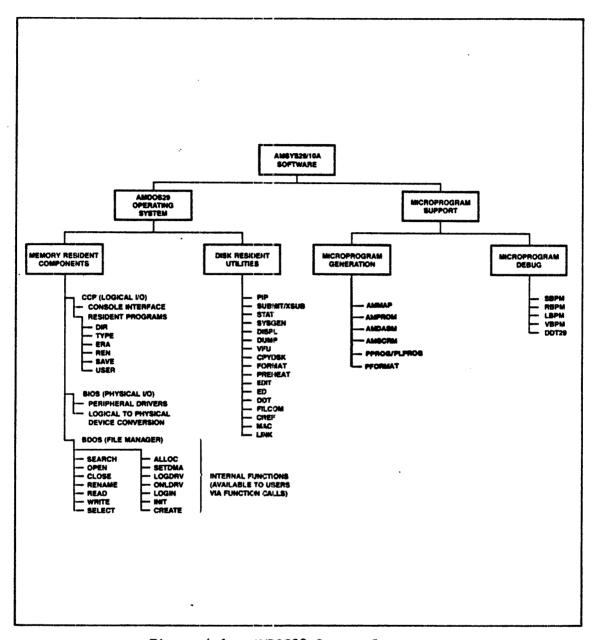

| 4-1    | AMDOS29 System Structure                              | 4-3  |

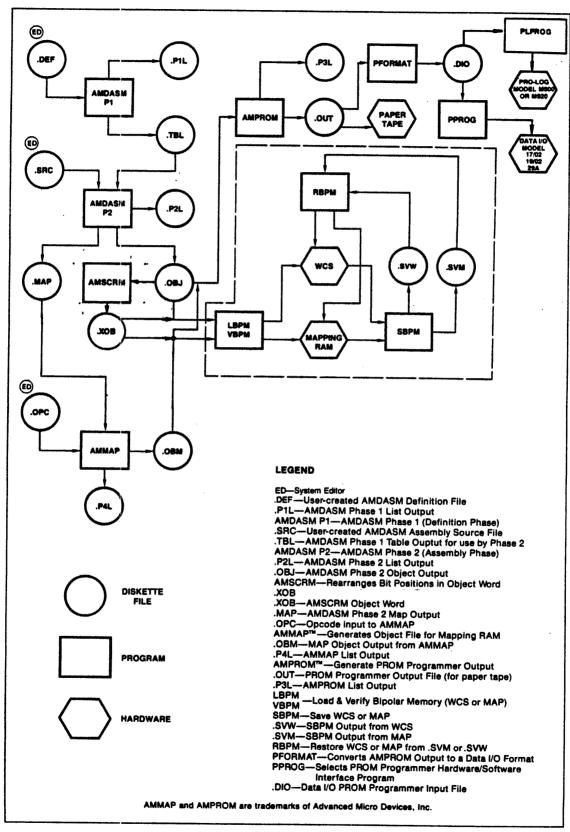

| 4-2    | Microprogram Support Software Relationship            | 4-4  |

| 5-1    | Detailed Block Diagram of AmSYS29/10A                 | 5-2  |

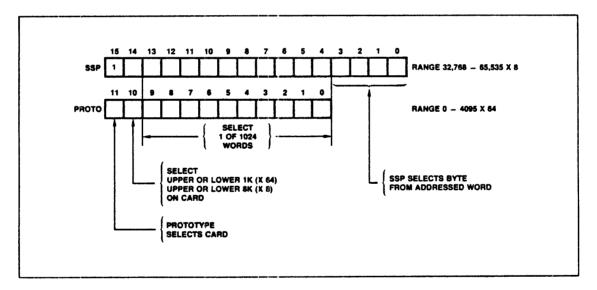

| 5-2    | Page Register Bit Allocations                         | 5-7  |

| 5-3    | Floppy Disk Interface Operation                       | 5-8  |

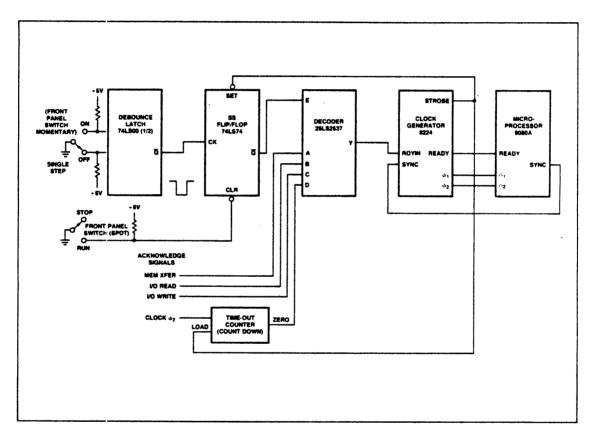

| 5-4    | Single Step Control                                   | 5-9  |

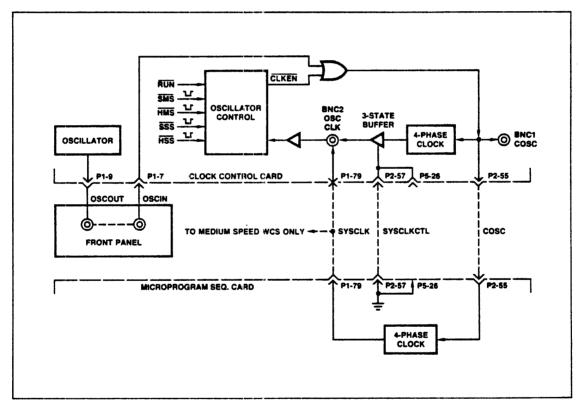

| 5-5    | Clock Control Logic                                   | 5-13 |

| 5-6    | Oscillator Control Timing                             | 5-15 |

| 5-7    | System Clock Generator Circuits                       | 5-17 |

| 5-8    | Control Register Bit Assignments                      | 5-17 |

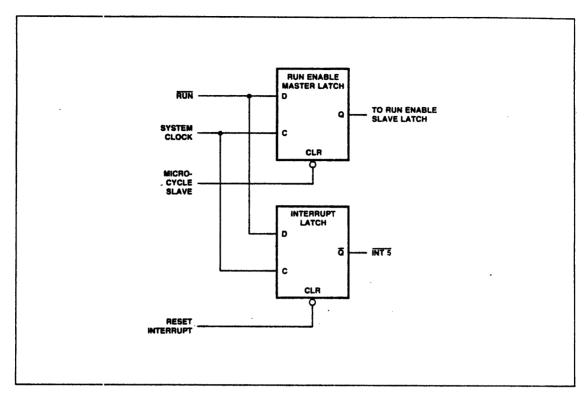

| 5-9    | Interrupt and Run Enable Latch Relationships          | 5-19 |

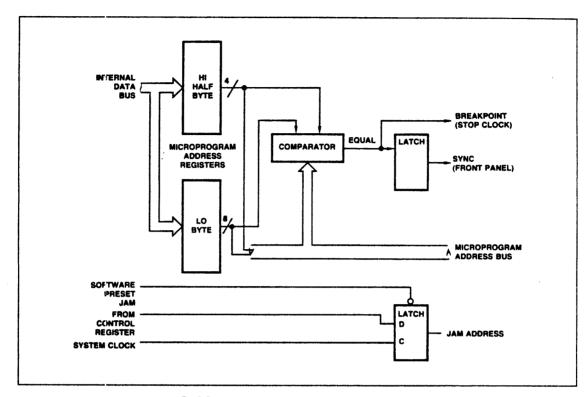

| 5-10   | Microprogram Address Register                         | 5-21 |

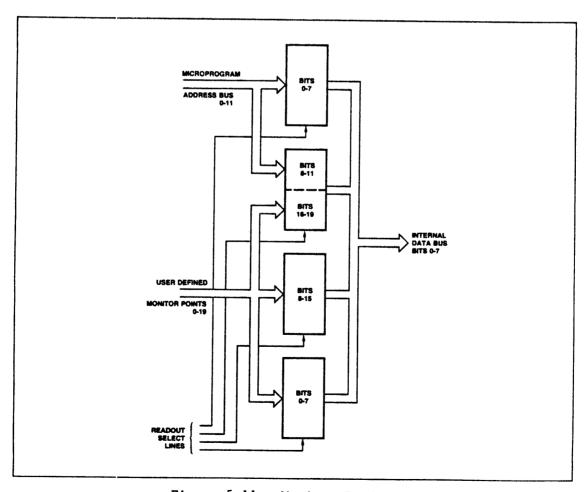

| 5-11   | Monitor Register                                      | 5-23 |

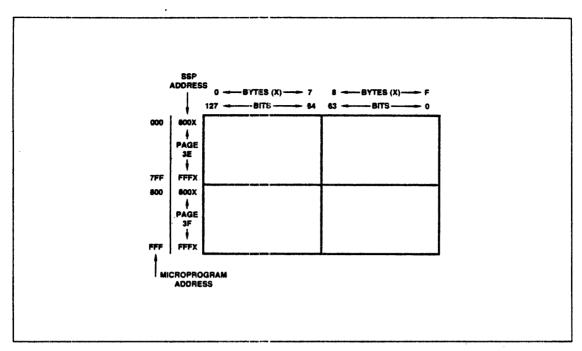

| 5-12   | Operation of WCS                                      | 5-24 |

| 5-13   | Microprogram Addresses from System Processor          | 5-24 |

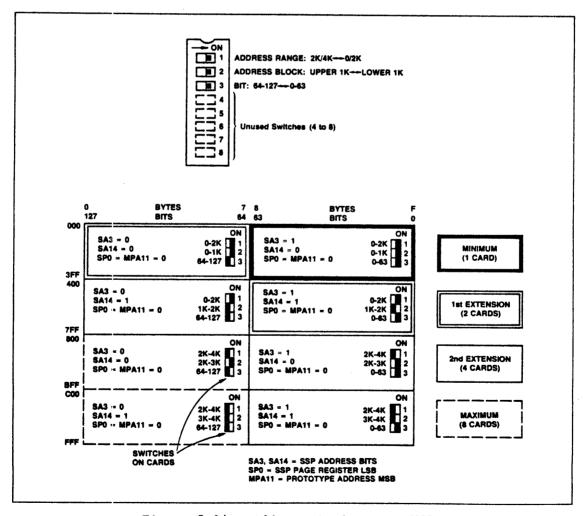

| 5-14   | Address Assignment, WCS                               | 5-25 |

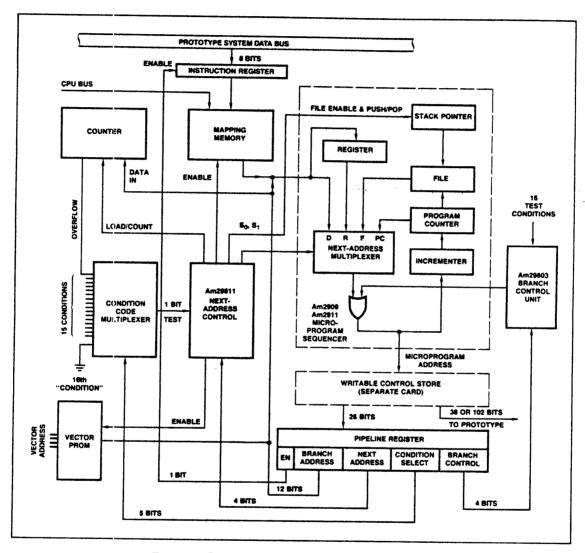

| 5-15   | Microprogram Sequencer                                | 5-27 |

| 5-16   | Microprogram Address Sequencer                        | 5-28 |

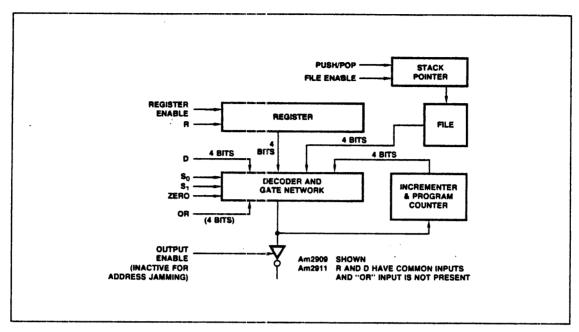

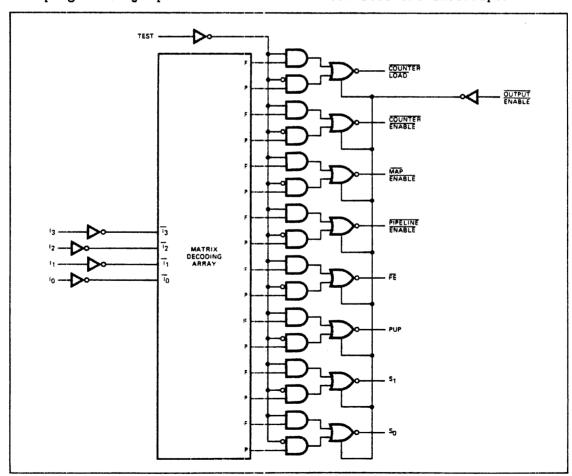

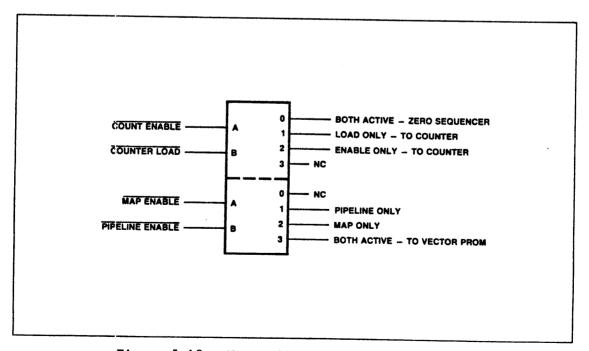

| 5-17   | Next-Address Control Unit                             | 5-32 |

| 5-18   | Next-Address Control Decoding                         | 5-33 |

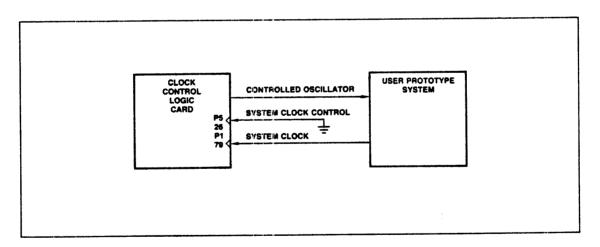

| 6-1    | Microprogrammed Controller System Clock Block Diagram | 6-2  |

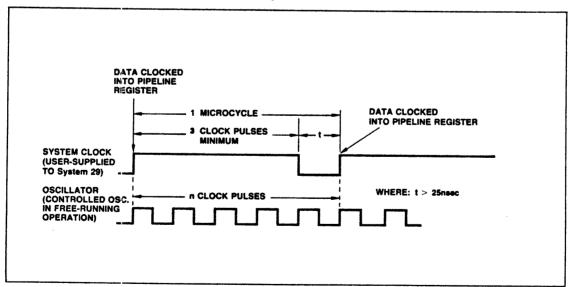

| 6-2    | Microprogrammed Controller System Clock Timing        | 6-3  |

| 6-3    | Connection Required for User-Generated System Clock   | 6-5  |

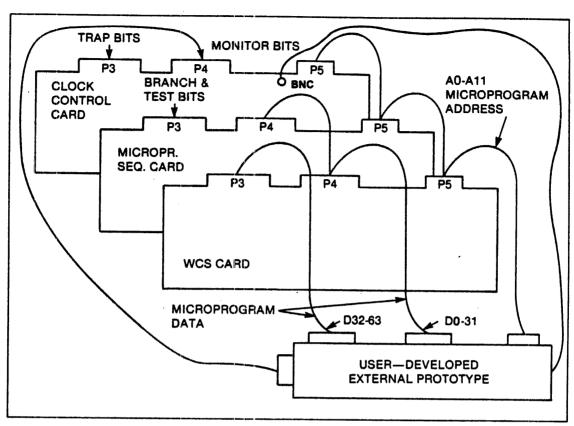

| 6-4    | Connection of External Prototype Package to AmSYS29   | 6-7  |

| 6-5    | System Clock Interfacing                              | 6-12 |

| 6-6    | User-Supplied System Clock Timing                     | 6-13 |

| 6-7    | Microprogram Sequencer                                | 6-15 |

### LIST OF TABLES

| Table    | Title                                               | Page             |

|----------|-----------------------------------------------------|------------------|

| 1-1      | AmSYS29/10A Units, Assemblies, and Options          | 1-3              |

| 1-2      | Power Requirements                                  | 1-4              |

| 1-3      | AmSYS29/10A Ports and Addressing                    | 1-4              |

| 2-1      | Board Jumper and Strapping Information              | 2-2              |

| 2-2      | J10 (Parallel Printer)                              | 2-3              |

| 2-3      | Jll (CRT Terminal)                                  | 2-3              |

| 2-4      | Jl2 (Serial Printer)                                | 2-3              |

| 2-5      | J13 (PROM Programmer or Reader/Punch)               | 2-4              |

| 2-6      | J14 (Spare)                                         | 2-4              |

| 2-7      | Pl7 (Floppy Disk Drive)                             | 2-5              |

| 5-1      | System 29 Bus vs. Intel Multibus                    | 5-3              |

| 5-2      | Input/Output Addresses                              | 5 <del>-</del> 6 |

| 5-3      | Page Address Allocations                            | 5-8              |

| 5-4      | Clock Control Logic Card Address Allocations        | 5-14             |

| 5-5      | Control Register Bits                               | 5-18             |

| 5-6      | Status Register                                     | 5-20             |

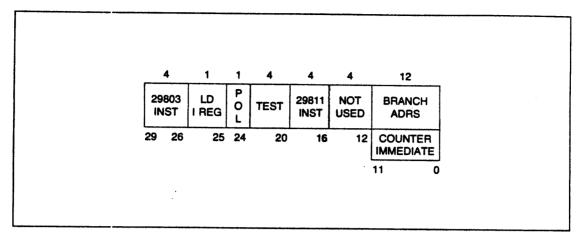

| 5-7      | Functions of Next-Address Control Unit              | 5-29             |

| 5-8      | Pipeline Register Bit Assignments                   | 5-31             |

| 5-9      | Branch Test Conditions                              | 5-35             |

| 6-1      | Address Pin Assignments for WCS, MPS, and CCL Cards | 6-8              |

| 6-2      | Data Pin Assignments for WCS Card                   | 6-8              |

| 6-3      | Clock and Control Pin Assignments                   | 6-9              |

| 6-4      | Monitor Bit Pin Assignments                         | 6-9              |

| 6-5      | Test Bit Pin Assignments                            | 6-10             |

| 6-6      | Interface Signals                                   | 6-11             |

| 6-7      | System 29 Signal Chart                              | 6-17             |

| 6-8      | Connector Chart for Pl                              | 6-18             |

| 6-9      | Connector Chart for P2                              | 6-19             |

| 6-10     | Connector Chart for P3                              | 6-20             |

| 6-11     | Connector Chart for P4                              | 6-21             |

| 6-12     | Connector Chart for P5                              | 6-22             |

| Appendia | k A ASMDEMO Program                                 | A-1              |

# CHAPER 1 GENERAL INFORMATION

#### INTRODUCTION

AmSYS29/10A is an engineering tool designed to aid development of microprogrammed target systems. Designers of high-speed computers use bit-slice architecture, like the 2900 family, and microprogramming to optimize processor performance. The microprogrammed processor is more versatile and offers higher performance than the fixed instruction set microprocessor. However, this versatility demands development tools specific to microprogrammed machines.

AmSYS29/10A provides the bit-slice designer with the software development and hardware debug tools which have been available to MOS microprocessor developers. AmSYS29/10A is a Microprogram Development System offering symbolic assembly language development of microcode, high-speed control store emulation, target-system clock control, and logic state monitoring.

During the development cycle of a microprogrammed system, the greatest challenges are writing a microprogram for a user-defined microinstruction format, and debugging the prototype hardware and microprogram in the target environment. AmSYS29/10A supplies the designer with the AMDASM meta-assembler to support microprogram development. The meta-assembler allows definition of a mnemonic instruction set for any microinstruction format. AMDASM, with the language definition table, then assembles the microprogram source file of symbolic code into a binary object file.

During hardware and software integration, AmSYS29/10A greatly reduces debug time by emulating critical parts of the target system. AmSYS29/10A provides a writable control store replacing control store PROM with high-speed RAM. Target system clock control by the clock control logic allows single-step, multiple-step, and full-speed execution with multiple breakpoints. Software is provided to set the RUN address to any location, monitor and display the microinstructions (up to 128 bits) and 32 logic points, and edit the writable control store contents.

A microprogram sequencer is provided on a card as an evaluation vehicle for microprogram familiarization and software module testing. The microprogram sequencer, when combined with the clock control logic and writable control store, forms a complete microprogrammed controller for testing and debugging prototype hardware.

Software provided with AmSYS29/10A includes a disk operating system with a full set of file management commands and input-output routines required for peripheral communications. Additional software is provided for generating, loading, saving, and debugging microprograms. Microcode checkout functions allow the user to display, modify, locate, store,

verify, and control target system execution via the CRT console or system mainframe front panel.

An optional high-speed trace unit is available that provides measurements of logic events and allows target system monitoring during full speed debugging. High-speed trace selectively records, under user-specified parameters, up to 48 bits of 256 words at a 10-MHz rate.

Eight 48-bit triggers specify data to be stored, turn data storage on or off, and provide additional hardware breakpoints to the Clock Control Logic (CCL). High-speed trace can be expanded to 96 bits of data storage and 96-bit triggers. Time tags can be stored with each event data storage to record the number of master clock pulses that have occurred prior to the event. Time tags also can be expanded. A standard time tag can be configured with a minimum of 16 bits up to a maximum of 48 bits. The time tag expansion has a 32-bit count.

#### PHYSICAL DESCRIPTION

The basic AmSYS29/10A consists of the mainframe cabinet and dual floppy disk drive cabinet; optional items include a CRT terminal and printer. Table 1-1 lists the major units, assemblies, and options of the AmSYS29A. Table 1-2 lists physical, environmental, and power specifications for AmSYS29/10A mainframe and associated floppy disk drives.

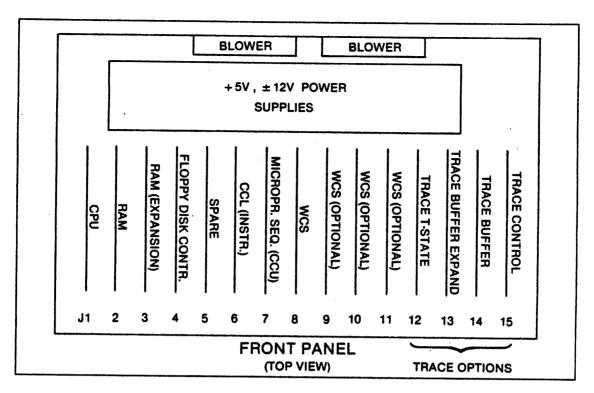

The AmSYS29/10A mainframe contains the central processor, single/double density floppy disk controller, 64K RAM, writable control store, microprogram sequencer, and clock control logic boards mounted in a 15-slot motherboard. The mainframe cabinet also contains +12Vdc, -12Vdc, and +5Vdc power supplies. Cooling for the cabinet is provided by two fans that move the air across the cards and power supplies.

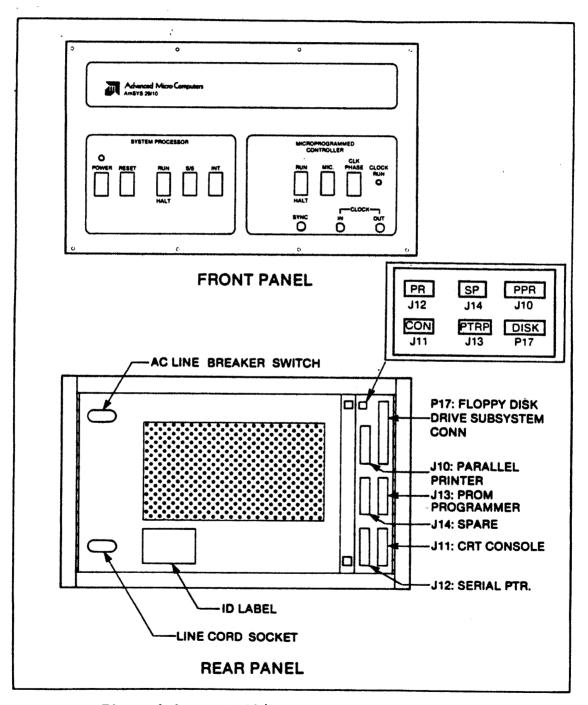

The system mainframe front panel, figure 1-1, contains control switches, indicators, and connectors for the system processor and microprogrammed controller sections of the system mainframe.

The system mainframe rear panel contains five 25-pin connectors and one 50-pin connector for attaching peripherals to the system, and a master power switch. Table 1-3 lists the rear connector ports and addresses. Figure 1-1 shows the rear panel and connectors.

Table 1-1. AmSYS29/10A Units, Assemblies, and Options

| BASIC SYSTEM                         | Support Processor:                           | CPU card with 4 serial ports (RS232), 3 parallel 8-bit ports                                                                                                                                                                                             |

|--------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                                              | System memory card, 64K bytes                                                                                                                                                                                                                            |

|                                      |                                              | Single/double density floppy disk controller                                                                                                                                                                                                             |

|                                      | ·                                            | 5V, 75A switching power supply                                                                                                                                                                                                                           |

|                                      | ·                                            | 12V, 1.7A linear power supplies                                                                                                                                                                                                                          |

|                                      |                                              | Dual floppy disk drives (housed in a separate cabinet)                                                                                                                                                                                                   |

|                                      | Microprogrammed<br>Controller:               | Writable control store card, 1K x 64 bits. The system is pre-wired for 4 cards.                                                                                                                                                                          |

| NOTE<br>Equipment can be             | •                                            | Microprogram sequencer with on-board 256 X 12 mapping RAM                                                                                                                                                                                                |

| factory-equipped<br>115V/60Hz, 220V, |                                              | Instrumentation (clock control logic) card, 10 MHz                                                                                                                                                                                                       |

| 50Hz, 110V/50Hz,<br>or 240V/50Hz.    |                                              | Blank diskettes (2)                                                                                                                                                                                                                                      |

| Software:                            | AMDOS 29                                     | Disk Operating System                                                                                                                                                                                                                                    |

|                                      | Microprogram Gen-                            |                                                                                                                                                                                                                                                          |

|                                      | eration Software:                            | AMDASM microprogram assembler                                                                                                                                                                                                                            |

|                                      |                                              | AMSCRM, AMPROM post-processing programs                                                                                                                                                                                                                  |

|                                      |                                              | PROM programmer software (for Data I/O Model 7, 9, 17 or 19 and Pro-Log M900 or 920).                                                                                                                                                                    |

|                                      |                                              | AMMAP PROM mapping assembler                                                                                                                                                                                                                             |

|                                      | Microprogram Sup-<br>port Software:          | Loads, verifies, saves, and restores programs from diskette to either WCS or map RAM                                                                                                                                                                     |

| •                                    |                                              | DDT29 debugger for the microcode in WCS: displays address, data and 20 monitor bits (single level trace); strings commands; single/multiple steps; break point on address, data, or control bits; jams address; displays and stores data in mapping RAM. |

| NOTE The software is licensed.       |                                              | Am9080A software (relocatable assembler and dynamic debugger including diassembler and trace capability)                                                                                                                                                 |

| PERIPHERALS Option                   | 8/8210                                       | Console, 12 inch, 24 lines x 80 characters, CRT display, key board                                                                                                                                                                                       |

|                                      | •                                            | Line printer,220 lines/minute, 132 columns.<br>Serial interface                                                                                                                                                                                          |

|                                      | •                                            | Dot matrix character printer: 7 x 7 dot matrix print head, 120 CPS print speed. Parallel interface                                                                                                                                                       |

| CARDS                                | 29/2064<br>290106 **<br>29/9040<br>990015 ** | Writable control store (WCS) card, 1K x 64 bits, 35 ns access Writable control store (WCS) card, 1K x 64 bits, 60 ns access Instrumentation (Clock Control Logic CCL) card, 10 MHz sys cli Instrumentation (Clock Control Logic CCL) card, 5 MHz sys cli |

| SERVICES                             | 29/6310                                      | High speed trace                                                                                                                                                                                                                                         |

|                                      | 29/6312                                      | Trace buffer card, expands high speed trace to 96 bits; in cludes 6 8-bit data pods and 1, 2-clock input clock pod. Trace time tag expansion card adds 256 x 32 bits of time tag storage to 96-bit high speed trace; includes clock pod.                 |

|                                      | 8/8250                                       | Diskettes, package of 10 - blank                                                                                                                                                                                                                         |

|                                      | 0,0250                                       | • • •                                                                                                                                                                                                                                                    |

|                                      | 8/8653                                       | PROM programmer cable, for connecting Amsys29 to a Data I/O Model 7, 9, 17, or 19                                                                                                                                                                        |

Peripheral not included. System includes drivers that will support this peripheral.

Obsolete, listed for reference only. Supported by AmSYS29/10A drivers.

Table 1-2. Power Requirements

| All +/- 10%          | 110V/60Hz                     | 110V/50Hz    | 220V/50Hz     | 240V/50Hz    |  |

|----------------------|-------------------------------|--------------|---------------|--------------|--|

| Mainframe            | 4.00A                         | 4.00A        | <b>2.</b> 00A | 2.00A        |  |

| CRT Console          | 0.50A                         | 0.50A        | 0.25A         | 0.25A        |  |

| Floppy Disk Drive    | 1.50A                         | 1.50A        | 0.75A         | 0.75A        |  |

| Frequency            | +5Hz                          | <u>+</u> 5Hz | <u>+</u> 5Hz  | <u>+</u> 5Hz |  |

| Circuit Breakers     | 10A                           | 10A          | 10A           | 10A          |  |

| Fuses                |                               |              |               |              |  |

| F102 (spare)         | 3A SB                         | 3A SB        | 1.5A SB       | 1.5A SB      |  |

| F103 (PS C)          | 3A SB                         | 3A SB        | 1.5A SB       | 1.5A SB      |  |

| F104 (PS B)          | 3A SB                         | 3A SB        | 1.5A SB       | 1.5A SB      |  |

| F105 (PS A)          | 3A SB                         | 3A SB        | 1.5A SB       | 1.5A SB      |  |

| F106 (Fans & 12V PS) | 2A FB                         | 2A FB        | 1.OA FB       | 1.OA FB      |  |

| Floppy Disk Drive    | 3A SB                         | 3A SB        | 1.5A SB       | 1.5A SB      |  |

| CRT Console          | 1A SB                         | la SB        | 0.5A SB       | 0.5A SB      |  |

| SB = Slow            | SB = Slow-blow FB = Fast blow |              |               |              |  |

Table 1-3. AmSYS29/10A Ports and Addressing

| Originating Card/Plug                          | Port<br>Addr.<br>(hex)                     | Type and<br>Baud Rate                                        | Rear<br>Panel<br>Connector | Device                                                    |

|------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|----------------------------|-----------------------------------------------------------|

| CPU P5<br>CPU P5<br>CPU P5<br>CPU P5<br>CPU P4 | 60,61<br>64,65<br>68,69<br>6C,6D<br>70,71, | Serial 9600<br>Serial 9600<br>Serial 600<br>Serial 110/9600* | J11<br>J12<br>J13<br>J14   | CRT Console<br>Serial Printer<br>PROM Programmer<br>Spare |

| FDC P4**                                       | 72,73                                      | Parallel<br>Parallel                                         | J10<br>P17                 | Parallel Printer<br>FDD Subsystem                         |

\*Depending upon jumper configuration as shown in table 2-1.

\*\*CPU I/O ports 7C, 7D, 7E, 7F are used to communicate with the floppy disk controller board.

#### **FUNCTIONAL DESCRIPTION**

The AmSYS29/10A development system supports microprogram development and verifies operation of target system hardware in the microprogrammed environment. Application of the AmSYS29/10A development system begins with definition of the microinstruction format for the target system. Each section of a proposed system is controlled by parallel control lines that form a formatted microinstruction or control word. A microprogram is a series of microinstructions whose changing bit patterns control operation of the proposed target system. Each field of microinstruction represents different control functions, constants, or variable data.

AMDASM is a meta-assembler program that is used to define the microword length and mnemonics for functions, addresses, and the operation control

fields in the microinstruction. These definitions are stored on disk by AMDASM in the form of a lookup table. This table defines the assembly language for that particular microinstruction set. A microcode program can then be written in this newly-defined assembly language and assembled by AMDASM to produce an object-code file on disk.

Figure 1-1. AmSYS29/10A Controls and Indicators

The microprogrammed controller integrates the microcode object file into the target system hardware. The writable control store replaces the target system microcode store, which is usually high-speed ROM, with RAM. LBPM (Load Bipolar Memory) is used to load the microcode object file created by AMDASM into the writable control store. DDT29 (Dynamic Debug Tool) interfaces the clock control logic, which controls the target system clock, to the user console, thus providig clock, addressing, and breakpoint control within the target system. The system can single-step through the microprogram and monitor the microinstructions, microaddress, and target system operations on the system console. Errors in microcode can be corrected immediately from the console. As the confidence level in the microprogram increases, full-speed testing can proceed in the target system under breakpoint control. The optional high-speed trace provides logic state monitoring of the target system during full-speed operation.

When the microprogram has been fully debugged, it is reassembled using AMDASM to create a new object file. The new object code is reloaded into writable control store and verified. The debugged object file is then broken into PROM-size files, via the program AMPROM, and burned into high-speed PROMs, via the program PPROG or PLPROG. These PROMs are placed into the target system. Testing of this final configuration and subsequent production line testing of the microprogrammed system can also be accomplished by the AmSYS29/10A with high-speed trace option installed.

#### HARDWARE FEATURES

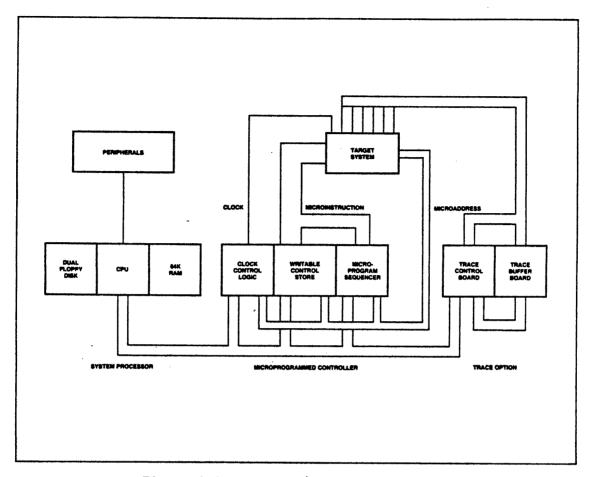

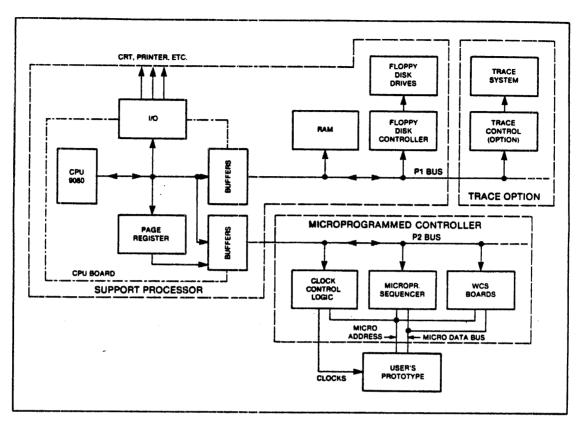

AmSYS29/10A is divided into three main areas of support hardware: the system processor, microprogrammed controller, and optional high-speed trace. Figure 1-2 is a system block diagram of the AmSYS29/10A.

The system processor comprises a CPU card, 64K memory card, single/double density dual floppy disk drive cabinet, and peripheral support options. These options include the CRT console, line printer, and PROM programmer. The microprogrammed controller consists of the writable control store cards, microprogram sequencer card, and clock control logic. The optional high-speed trace unit forms a part of the microprogrammed controller and consists of a trace control and trace buffer board.

The mainframe cabinet also contains power supplies for both the system processor and microprogrammed controller. Three +5 Vdc power supplies at 25A each and a +/-12 Vdc power supply at 1.7A provide the system power.

Figure 1-2. AmSYS29/10A Block Diagram

#### **CPU CARD**

The CPU card is located in the system mainframe. The principal circuits on the CPU card are the Am9080A microprocessor together with its support circuits, bus drivers, receivers, and system clock. In addition to the microprocessor, the CPU card contains circuits to accomplish seven other functions:

- Seven input/output ports

- Floppy disk interface circuits (DMA)

- Microprogrammed controller interface

- Initialization

- Bus control

- Clock control

- Priority interrupt

The input/output ports are the means by which the CPU communicates with the peripheral devices. There are four serial ports and three general-purpose 8-bit parallel ports.

Serial ports communicate with the CRT terminal at 9600 baud, a line printer at 9600 baud, and either a paper-tape reader/punch or a PROM programmer at 600 baud. The fourth port is a spare, factory-configured to 9600 baud but user configurable by a jumper to 110 baud. Each

serial port has an Am9551 universal synchronous-asynchronous receiver-transmitter (USART), which serializes outgoing data and deserializes incoming data, simultaneously if desired. The USART also keeps track of its own operational status, so that the microprocessor can dispatch a new character to the USART immediately when the latter has finished serially transmitting the preceding character, and can accept an incoming character as soon as the USART has deserialized it.

General-purpose parallel ports consist of a single Am9555 programmable peripheral interface, which is user accessible through the connectors at the top of the CPU card. The user must provide the interface circuitry at the terminals of the Am9555. This is shipped configured to interface to a Centronics-compatible printer. The CPU card has sockets for installing interface circuits.

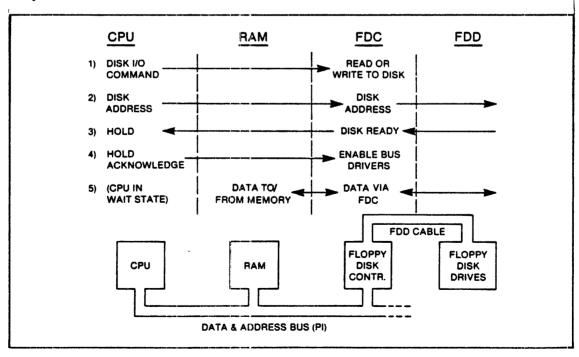

The floppy-disk interface sets-up direct memory access operations in the appropriate direction and keeps the microprocessor in the wait state while a DMA operation is in progress. Data transferred to or from the disk does not involve the microprocessor. There are two disk drives; the disk on drive A typically contains the system software, and that on drive B is a mass storage area.

During a DMA operation or initialization, the system bus must be kept available at all times so that a data byte can be transmitted to or from memory without notice. Therefore, other elements of the CPU card must be prevented from using the bus at such times. The bus control enforces this prohibition.

Using the microprogrammed controller interface, the CPU issues commands to receive status information from the prototype system and its microprogram.

The clock control implements the operation designated by pressing the front panel RUN or SINGLE STEP switch.

The priority interrupt ranks interrupt requests from four different sources and feeds them in order of rank to the microprocessor for its response. Interrupts 5 and 7 are used currently. Interrupt 5 is the instrumentation clock stopped interrupt and 7 is the system interrupt.

Figure 1-3. System Mainframe Configuration

#### **MEMORY CARD**

The memory card is located in the system mainframe and contains 64K bytes of dynamic memory with on-board refresh. The card contains 32 dynamic RAM integrated circuits, each storing 16,384 bits in a 16,384 x 1 format. Eight of these circuits hold the corresponding bits of 16,384 bytes and are addressed simultaneously.

#### SINGLE/DOUBLE-DENSITY FLOPPY DISKS

The dual disk drive cabinet contains two independent eight-inch floppy disk drives (drive A and drive B) and associated power supply. The dual-density floppy disk controller, located in the mainframe, provides the interface between the CPU card in the system mainframe and two floppy disk drives. The controller contains write protect logic, CRC generation and verification logic, and automatic track seek-verify logic in addition to the read/write circuits. Each disk drive uses IBM-compatible\* soft-sectored double-density eight-inch diskettes. Each diskette has a maximum memory capacity of 512K bytes. The controller also allows single density diskettes to be used. Each drive has a front panel activity indicator that is lighted when the associated disk drive is active.

<sup>\*</sup> IBM media specification GA21-9257-1

The CRT console is a full-duplex ASCII data terminal. Data is exchanged between the CRT console and the system mainframe via a 9600-baud RS232 port. The CRT console includes keyboard, CRT monitor, associated logic circuits, and power supply. Cursor addressing is provided to allow updating screen pages without scrolling; this capability is required when using high-speed trace.

#### LINE PRINTER (OPTION)

The line printer option is no longer offered.

#### **PROM PROGRAMMER (OPTION)**

The AmSYS29/10A operating system includes routines to drive a PROM programmer. The PROM programmer is connected to the 600-baud serial I/O port of the AmSYS29/10A mainframe. Support is available for various models of Data I/O and Pro-Log PROM programmers.

#### WRITABLE CONTROL STORE CARD

The writable control store card is configured as 1K x 64 bits of RAM which provides the target system microcode control store. The RAM has a maximum access time of 35 nanoseconds over the commercial temperature range. The mother board contains slots for four writable control store cards, allowing the basic writable control store supplied with the system to be expanded to 4K words in depth and 64 bits in width or 2K words by 128 bits width. The card provides an eight-bit interface to the system bus that allows the user to examine and update the contents.

#### CLOCK CONTROL LOGIC CARD

The clock control logic (CCL) card provides console control of the target system during emulation. The card takes one slot in the motherboard and communicates with the system processor over the system P2 bus. Control of the target system is accomplished via the microprogram address bus and clock control lines. The clock control logic card allows the user to single step one clock cycle, microstep one instruction cycle, multiple step, or run full speed emulation. The clock control logic also allows the user to set a breakpoint address, force a jump to a new address, monitor 32 logic points (including 12 address lines), and set a halt from the front panel, hardware, or software.

#### **HIGH-SPEED TRACE CARD (OPTION)**

The high-speed trace option allows monitoring of target system logic states during full-speed emulation. High-speed trace allows the user to selectively record, at a 10-MHz rate, up to 48 bits for a depth of 255 words. Eight 48-bit-wide general-purpose comparators are provided. These comparators allow the user to set a trigger sequence, to specify the data to be stored, and to provide two additional hardware breakpoints to the clock control logic. Time tags can be stored with each occurrence of the specified data storage to record the time (in increments of master clock pulses) of the event. Time tag storage uses 16 or 32 bits of data in the basic configuration. The high-speed trace unit can be expanded to 96 bits of data storage by the addition of an optional memory buffer board. This option also expands the eight trigger comparators from 48 bits wide to 96 bits wide.

#### MICROPROGRAM SEQUENCER CARD

The microprogram sequencer card provides a complete pipelined computer control unit that includes an address sequencer and an op code mapping memory for addressing the microcode contained on the writable control store (WCS) cards. The op code mapping memory is a 256 by 12-bit RAM that is used to store the starting addresses of microcode subroutines. The op code mapping memory translates an 8-bit instruction fetch from main memory into a starting address for the WCS microcode.

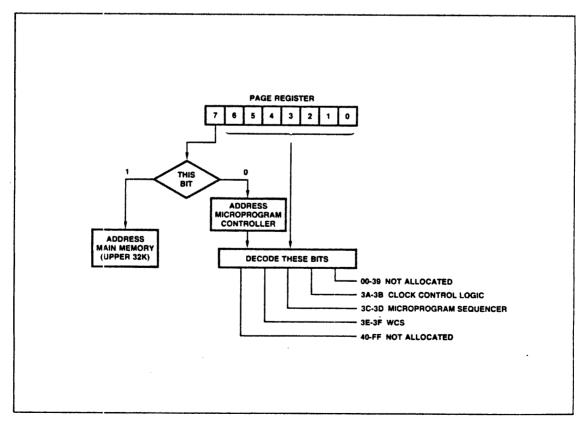

The microprogram sequencer card can be automatically paged into the upper 32K address range of the system processor by invoking the appropriate microprogramming support software command. Once paged into the system processor, the op code mapping memory can be loaded, verified, modified, and saved as required.

The card also contains a branch control unit, a pipelined register, and a next address controller. The next address controller determines the source of the next microinstruction to be executed, routing to the microprogram address sequencer, the output of the mapping memory, the pipeline register, the sequencer program counter, or the sequencer stack. The pipeline register stores 26 bits from the writable control store, and permits the address of the next microinstruction to be determined while the previous instruction is being executed by the target. In addition, this board provides 16 bits for conditional branching, controlled by external signals provided by the user, and four bits for multiway branching to one of 16 addresses.

The AmSYS29/10A system provides a complete software package that consists of a comprehensive disk operating system, microprogram generation software, microprogram support software, and example files.

#### **OPERATING SYSTEM**

AMDOS29 is a CP/M-compatible disk operating system that performs file management of floppy disk files and contains all input/output routines required for peripheral communications. AMDOS29 provides the basic capability to load programs for execution and service system requests made by executing programs. When the operating system has been loaded by the bootstrap operation, the command processor, disk I/O drivers, and device I/O drivers are resident in high memory. The operating system is then ready to load and service programs. The operating system is fully described in the AMDOS29 Operating System Manual. Functionally, each command issued at the console takes temporary control of the system and performs the appropriate operation. Except for intrinsic commands, each command exists as a separate file that is loaded into the transient program area (TPA) for execution.

File management utilities included in AMDOS29 are:

DIR Display file names.

PIP Copy specified file or files.

CPYDSK Copy all files on a diskette.

TYPE Display file contents.

DUMP Display selected file contents.

DUMP Dump file in hexadecimal and ASCII.

ERA Erase file.

SAVE Save memory contents as a file.

REN Rename file.

FORMAT Initialize a diskette by formatting.

SYSGEN Copy the operating system onto tracks 0 and 1.

The utility for submitting a job is:

SUBT/XSUB Submit command stream for processing.

Utilities for resource management are:

VFU Printer control.

STAT Display file and option characteristics.

AMUSRITY User-created TTY driver loaded with BIOS at boot.

Utilities for program generation are:

File editor to create and update ASCII files.

MAC 8080/8085/Z80 relocatable macroassembler.

PREHEAT Prepares assembler object files (AMDASM/MAC) for

PROM programmer drivers.

LINK Links relocatable object files produced by MAC.

LIB Forms library of relocatable files produced by MAC.

PPROG Data I/O Models 17 or 19 PROM programmer driver

PLPROG DDT Pro-Log M900 & M920 PROM Programmer driver. Dynamic debug tool to debug MAC programs.

For complete details see AMDOS 29 Operating System User's Manual.

#### **MICROPROGRAM GENERATION SOFTWARE**

AMDASM is a meta-assembler that assembles user-generated prototype microcode into machine language. AMDASM is a two-phase assembler. The first phase is a definition phase that allows the user to define the microword length, constants, and formats used to write source programs for the prototype system. The second phase is a two-pass assembler. In the first pass, the source program statements are read and values are assigned to labels and constants. In the second pass, the source program executable statements are translated by the definition phase output into binary format for prototype execution. The following is a list of AMDASM programs.

AMDASM Phase I (definition) of meta-assembler that permits user to define microword length, constants, and formats used to write source programs for prototype systems.

Phase 2 (assembly) of meta-assembler that reads source programs and assigns labels and constants. Source program executable statements are translated into binary format for prototype execution of the user-developed microcode.

AMPROM Post processor that permits conversion of binary object code to a form corresponding to the PROM organization of the developed system. Word width must be consistent with the width of the developed system.

AMSCRM Post processor that permits the user to reassign bit positions of microword contents by specifying source and destination bit positions and the length of each field to be moved, thus producing a reorganized microcode object file.

AMMAP Generates microprogram entry point addresses that are loaded into the MPS mapping RAM to decode instructions and generate microprogram starting addresses.

#### MICROPROGRAM SUPPORT SOFTWARE

The microprogramming debug software contains a number of programs that support the prototype microcode development. The debug programs are described as follows:

LBPM Loads microcode from disk file into WCS card memory or loads microcode entry points from disk file into MPS card op code mapping RAM.

VBPM Verifies loaded contents of WCS card memory or of MPS card mapping RAM.

SBPM Saves WCS card memory contents or MPS card op code mapping RAM contents on a disk file.

RBPM Restores file previously saved on diskette to WCS card memory.

DDT29 Dynamic debugging tool that permits display and modification of portions of WCS card memory or MPS card opcode mapping RAM. Controls halt/run states of microprogrammed controller clock. Loads address breakpoints and addresses for jamming into Clock Control Logic card registers. Permits display of Clock Control Logic card status register. Stores data in one-byte increments into particular locations of WCS card or MPS card memories. Permits 20 monitor bits (single level trace) to be displayed. Allows automatic stepping through the microcode and the convenient display of relevant data (microcode address and data, and monitor bits).

#### **EXAMPLE FILES**

The following example files are included to allow the user to become familiar with definition files, source files, execution, and debugging. Most files have comments on their headers which describe the purpose of the file.

| ASMDEMO.SUB  | This submit file, when executed with the command SUBMIT ASMDEMO JUMP, will display the JUMP.DEF and JUMP.SRC files, execute AMDASM, then display the print files. SUBMIT and DISPL utilities should be studied first. |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDTDEMO.SUB  | This submit file loads the small program generated from ASMDEMO.SUB, and executes and displays some DDT29 commands.                                                                                                   |

| JUMP.DEF     | A definition file for the above demonstration programs.                                                                                                                                                               |

| JUMP.SRC     | A source file that is assembled and executed by the above submit files.                                                                                                                                               |

| AM29CPU.DEF  | A definition file for the AM2900 family.                                                                                                                                                                              |

| AM29203.SRC  | A sample source file for the AM29203.                                                                                                                                                                                 |

| CONTROLR.DEF | A definition file for the AM29116.                                                                                                                                                                                    |

| CONTROLR.SRC | A sample source file to exercise the CONTROLR.DEF statements and demonstrate their usage.                                                                                                                             |

| DISKCTLR.DEF | An AM29116 definition file. This file uses the same AM29116 mnemonics and instruction layout as the CONTROLR.DEF file; however, the invocation of the instruction is different and worthy of study.                   |

| DISKCTLR.SRC | A source file for a high-performance disk controller that uses the DISKCTLR.DEF file.                                                                                                                                 |

## CHAPTER 2 INSTALLATION

#### INTRODUCTION

This chapter provides instructions for initial inspection, preparation for use, peripheral device interconnection, and initialization of the AmSYS29/10A support processor. For detailed information on the individual peripheral devices, refer to the appropriate manual for that device.

#### **UNPACKING AND INSPECTION**

Inspect the shipping cartons immediately for evidence of damage or mishandling during transit. When there is evidence of severe damage, request the carrier's agent to be present when the carton is opened. If the carrier's agent is not present, retain the carton and all shipping materials for the agent's inspection. Report all shipping damage to the carrier immediately.

#### NOTE

If there is evidence of damage to the equipment, DO NOT attempt any servicing of the equipment. Any attempt to service the equipment, without the express consent of the Advanced Micro Devices Field Service Manager, voids the warranty.

When all equipment is removed from the shipping cartons and it is ascertained that there is no obvious shipping damage, inventory the equipment received against the enclosed packing slip. If any discrepancies are noted, notify Advanced Micro Devices immediately. It is suggested that all salvageable shipping materials be retained in case the product must be shipped in the future.

#### PREPARATION FOR USE

Prior to interconnecting the AmSYS29/10A units and applying power to the mainframe, proceed as follows:

Check line input power and ratings on floppy disk drive and mainframe to ensure supplied power is correct.

- 2. Open top and bottom access covers on mainframe cabinet.

- 3. Remove packing material.

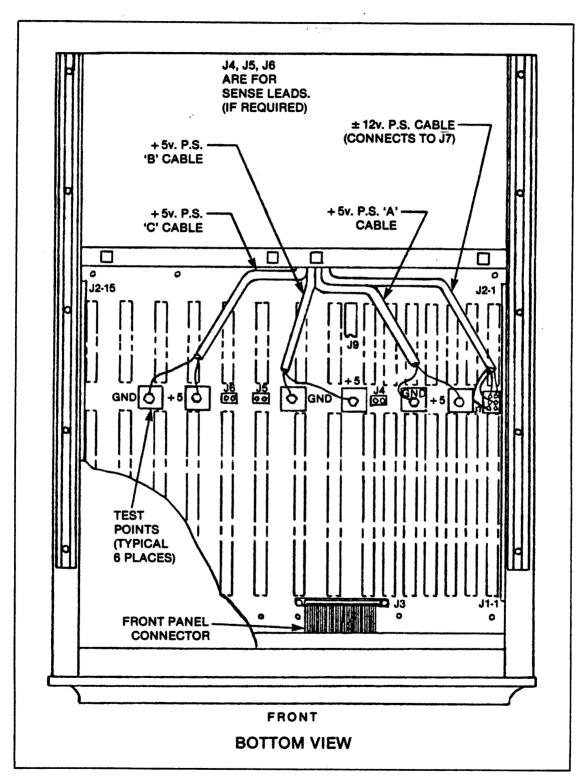

- 4. It is normally not necessary to check DC voltages during installation. However, if voltage checking is desired, use a DVM (or equivalent device) to check the connector pins shown in figure 2-1.

- 5. Verify that board jumpers and switches are set per table 2-1.

- 6. Ensure that all boards are well seated and in their assigned slots on the motherboard, as shown in figure 2-2.

- 7. Ensure that ribbon cables are connected to correct board edge connectors shown in figure 2-2.

- 8. Unpack and set up peripheral devices.

- 9. Connect CRT and floppy disk drives to system main frame cabinet back-panel with cables provided. See figure 2-3 for proper location. Pin assignments for back-panel connectors are shown in tables 2-2 through 2-7.

- 10. Connect AC power to the AmSYS29/10A mainframe, CRT, printer, and floppy disk drives.

- 11. Ensure that processor front-panel RUN/HALT switch is in the RUN position.

#### NOTE

Appendix A contains a demo program available on the supplied system disks. This program can be used to verify system operation.

Table 2-1. Board Jumper and Strapping Information

```

Jumpers and switches on floppy disk controller board (6120)

Jumpers: 3 and 8

Switch 1: all open (off)

Switch 2: 1 open; 2-6 closed (on)

Strapping of 64K RAM (1064) board:

2 to

3

38 to 39

55 to 56

63 to 64

88 to 95

17 to 18

43 to 44

57 to 58

65 to 66

92 to 93

31 to 32

46 to 48

59 to 60

67 to 68

*135 to 133

88 to 95 *135 to 139

34 to 35

53 to 54

61 to 62

*Note:

135 is connected to both 133 and 139.

97/0064 board requires no user configuration.

Strapping of CPU board:

2-3

110 baud on spare I/O port

1-2 9600 baud on spare I/O port

```

Table 2-2. JlO (Parallel Printer)

| PIN                   | SIGNAL                              | PIN                        | SIGNAL                                     |

|-----------------------|-------------------------------------|----------------------------|--------------------------------------------|

| 1<br>2<br>3<br>4<br>5 | DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 | 10<br>11<br>12<br>13<br>14 | GROUND GROUND GROUND NC DATA STROBE GROUND |

| 7<br>8<br>9           | DATA7<br>DATA8<br>GROUND            | 16<br>17<br>18-25          | GROUND<br>BUSY<br>NC                       |

Table 2-3. Jll (CRT Terminal)

| PIN  | SIGNAL              |

|------|---------------------|

| 1    | NC                  |

| 2    | RX DATA             |

| 3    | TX DATA             |

| 4    | :NC                 |

| 5    | REQUEST TO SEND     |

| 6    | DATA TERMINAL READY |

| 7    | GROUND              |

| 8-25 | NC                  |

Table 2-4. J12 (Serial Printer)

| PIN                                                    | SIGNAL                                                                                           |  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8-19<br>20<br>21-25 | NC RX DATA TX DATA CLEAR TO SEND REQUEST TO SEND DATA TERMINAL READY GROUND NC DATA SET READY NC |  |

Table 2-5. J13 (PROM Programmer Or Reader/Punch)

| PIN   | SIGNAL              |

|-------|---------------------|

| 1     | NC                  |

| 2     | RX DATA             |

| 3     | TX DATA             |

| 4     | NC                  |

| 5     | REQUEST TO SEND     |

| 6     | DATA TERMINAL READY |

| 8-19  | GROUND              |

| 20    | DATA SET READY      |

| 21-25 | NC                  |

Table 2-6. J14 (Spare)

| PIN   | SIGNAL              |  |  |

|-------|---------------------|--|--|

| 1     | NC                  |  |  |

| 2     | RX DATA             |  |  |

| 3     | TX DATA             |  |  |

| 4     | CLEAR TO SEND       |  |  |

| 5     | REQUEST TO SEND     |  |  |

| 6     | DATA TERMINAL READY |  |  |

| 7     | GROUND              |  |  |

| 8-19  | NC                  |  |  |

| 20    | DATA SET READY      |  |  |

| 21-25 | NC                  |  |  |

Table 2-7. P17 (Floppy Disk Drive)

| PIN | SIGNAL NAME                                                                      | PIN    | SIGNAL NAME |

|-----|----------------------------------------------------------------------------------|--------|-------------|

| 2   | TC 43*                                                                           | 1      | GROUND      |

| 4   |                                                                                  | 3      | GROUND      |

| 6   | منته (بالأمل كال منته خواه دايله دايله منته بالأم والمنا بالمنا                  |        | GROUND      |

| 8   |                                                                                  | 5<br>7 | GROUND      |

| 10  | TWO SIDED*                                                                       | 9      | GROUND      |

| 12  | aller allegische auto-auto mitte auso vorbe aller auss voren aus proposition aus | 11     | GROUND      |

| 14  | SIDE SELECT*                                                                     | 13     | GROUND      |

| 16  | IN USE*                                                                          | 15     | GROUND      |

| 18  | HEAD LOAD*                                                                       | 17     | GROUND      |

| 20  | INDEX*                                                                           | 19     | GROUND      |

| 22  | READY*                                                                           | 21     | GROUND      |

| 24  |                                                                                  | 23     | GROUND      |

| 26  | DS01*                                                                            | 25     | GROUND      |

| 28  | DS02*                                                                            | 27     | GROUND      |

| 30  | DS03*                                                                            | 29     | GROUND      |

| 32  | DS04*                                                                            | 31     | GROUND      |

| 34  | DIRECTION*                                                                       | 33     | GROUND      |

| 36  | STEP*                                                                            | 35     | GROUND      |

| 38  | WRITE DATA*                                                                      | 37     | GROUND      |

| 40  | WRITE GATE*                                                                      | 39     | GROUND      |

| 42  | TRACK DATA*                                                                      | 41     | GROUND      |

| 44  | WRITE PROTECT*                                                                   | 43     | GROUND      |

| 46  | READ DATA*                                                                       | 45     | GROUND      |

| 48  |                                                                                  | 47     | GROUND      |

| 50  |                                                                                  | 49     | GROUND      |

Figure 2-1. Voltage Test Points

Figure 2-2. Board Edge Connectors

Figure 2-3. AmSYS29/10A Interconnection Diagram

## CHAPTER 3 OPERATION

#### INTRODUCTION

Read the descriptions of diskette insertion and system bootstrap operation before proceeding with system initialization.

#### **DISKETTE INSERTION**

Diskettes must be inserted into the dual-drive floppy disk unit openings with label up and the write protect notch toward the floppy disk drive. See figure 3-1.

Figure 3-1. Floppy Diskette

Exercise care when handling diskettes so as not to touch the recording surface exposed through the openings on the cover. Use good quality diskettes, Dysan part number 800838 or equivalent; poor quality diskettes cause excessive wear of the read/write head.

#### CAUTION

Information stored on the diskette can be destroyed by static electricity discharge from a person touching the equipment. Synthetic carpets, in particular, can cause a build-up of static electricity. Periodic application of Neutro Stat (or equivalent) antistatic spray can retard the static electricity build-up; however a safer solution is to install the system on an antistatic mat (see Velostat type 1854 4'x 8' x 1/8" as manufactured by 3M-Static Control Systems, St. Paul, Minn. 55101, or equivalent).

The floppy disk unit engages with the diskette when the door is closed. The door is closed by pushing the top of the door down until it latches.

#### CAUTION

Do not replace diskettes while programs or commands are being executed. DO NOT TURN THE POWER ON OR OFF WHILE A DISKETTE IS IN THE UNIT. Otherwise, a track of data may be destroyed. If drive units must be powered down when a red activity indicator is lighted, open drive unit door and remove diskette before powering down.

#### **FLOPPY DISKETTE**

The floppy diskette is sealed in an 8-inch square cover that is lined to minimize static electricity. When not in use, the diskette should be kept in the storage envelope provided with each diskette. When the write-protect notch is covered with a tape strip, the diskette is write-enabled. Some commands, such as the SUBMIT command, require that the accessed diskette be write-enabled. Files on the diskette can be write protected by removing the tape strip from the write-protect notch. Each diskette is shipped with several tape strips. Store diskettes in normal work areas where temperatures are within the range of 50-125 degrees Fahrenheit (27-50C), and do not allow diskettes to be exposed to magnetic flux lines such as can be present around large power supply transformers. Do not allow the diskettes to be exposed to direct sunlight for any extended period of time.

#### **BLANK DISKETTE FORMATTING PROCEDURE**

Diskettes provided with AmSYS29/10A are preformatted in soft sector format. The index address mark, record identification fields, and gaps are prerecorded. During normal use, the soft sector format is untouched while data field records are changed and updated as required by the user. Occasionally, an index address mark or record identification field can be inadvertently erased from the diskette. An erasure can result, for example, if the system is powered down while a diskette is engaged in the floppy disk drive unit.

Usually, when part of the diskette formatting is erased or when a diskette has a physical fault that prevents correct formatting, an error message is displayed at the CRT console. The error message form is n PERM ERR DISK x, where n is an error number that indicates the type of error and x indicates the floppy disk drive unit (A or B) that contains the permanent error. No error message is displayed at the CRT console when an index address mark is erased. Instead, the floppy disk drive unit activity indicator remains lighted, and communication with the diskette via the CRT console is impossible. To restore the index address marks on the erased diskette: 1) remove the erased diskette; 2) get the format procedure from another (backup) diskette; 3) reformat the

erased diskette by performing the diskette formatting procedure described in the AMDOS29 Operating System manual.

#### NOTE

Data on the diskette is erased during formatting.

Diskette formatting is accomplished by invoking the AMDOS29 utility FORMAT, which records the required information into the index address mark area, record identification fields, and gaps. Blank diskettes purchased from AMD are preformatted in single density. Diskettes purchased elsewhere must be formatted before being used with AmSYS29/10A.

#### SYSTEM INITIALIZATION OPERATION

Diskettes containing the AmSYS29/10A software are provided with the system. The operating system and certain selected utilities are on the system diskette. To initialize the system and load the operating system, perform the following steps:

- 1. Make sure that all the peripheral devices have their power switches turned on.

- 2. Set the AmSYS29/10A front panel power ON/OFF switch to ON and the RUN/HALT switch to RUN.

- 3. Insert the system diskette into drive A (the lower drive).

- 4. Press the RESET switch on the system cabinet. The bootstrap operation begins. The red LED on drive A lights to indicate that drive A is being selected to load the operating system.

- 5. When the system boot is complete, the following message is displayed:

AMDOS29 64K, VERSION 3.0

6. The system executes the PROFILE.SUB file, if one exists on the disk. If a PROFILE. SUB file exists, the commands in the file are echoed one by one to the console as they are executed.

#### 7. The prompt

A>

then appears. When the system prompt appears, the system is ready to accept the user's first command.

During initial system installation, it is wise to make a backup copy of the system diskettes. To copy the system diskettes, enter:

CPYDSK

The system responds with:

SOURCE ON A, DESTINATION ON B

Insert a blank diskette into drive B and press the RETURN (NEW LINE) key. The system begins to copy the diskette in drive A onto the diskette in drive B. A message is displayed to indicate the track being copied. When track 76 has been copied, insert another blank disk into drive B and press the RETURN (NEW LINE) key to make another copy. Enter CONTROL-C (CONTROL and C keys simultaneously) to terminate the copy operation.

Next, it is useful to obtain a hard copy of the directory that is on each system diskette. To select the printer, enter:

STAT LST: = UL1:

(for a parallel printer - otherwise a serial printer is assumed) followed by:

CONTROL-P (CONTROL and P keys simultaneously)

To list the directory, enter:

DIR

The directory is displayed on the CRT and printed at the same time. Attach the directory listing to the diskette envelope for reference. Insert the next diskette and list that directory. After all directories have been printed, discontinue display printing by entering:

CONTROL P

At this point, another diskette can be selected for the work to be done next.

The editor is resident on the system disk when it is shipped from the factory. If the editor is required, see the ED User's Manual for usage information.

## CHAPTER 4 SYSTEM SOFTWARE

#### INTRODUCTION

AmSYS29/10A software can be divided into two general categories: operating system software and microprogram support software. As shown in figure 4-1, the operating system software can be further divided into the memory resident operating system components and disk resident utilities. Microprogram support software includes microprogram generation software and microprogram debug software. This chapter briefly describes each software product; detailed descriptions are provided in the AMDOS29 Operating System User's Manual and the Microprogram Support Software User's Manual.

#### **AMDOS29 OPERATING SYSTEM**

AMDOS29, a CP/M\* 2.2-compatible operating system, consists of the Basic Input/Output System (BIOS), the Basic Disk Operating System (BDOS), and the Console Command Processor (CCP). The operating system resides in high memory (locations DCOO-FFFFH); user programs are loaded into the transient program area (TPA), locations 0100H to DBFFH. These memory locations change from time to time; however, memory location 0005H is always a JMP to start of the operating system. BIOS provides the drivers for accessing the physical devices, including the floppy disk drive, and provides the interface to system peripheral devices such as a line printer and CRT console. This component thus defines the hardware environment. Specific user-system configurations (logical-to-physical device assignment) can be examined and altered by means of the statistics (STAT) utility.

BDOS is the file-management component, controlling logical access to the files on the diskettes. BDOS incorporates primitive commands to enable disk-drive and file-manipulation operations such as: search for a file by name; file create, open/close, read/write, rename; disk-drive select, reset, and interrogation; and set diskette memory buffer address. A detailed description of program usage of the BIOS and BDOS primitives is contained in the AMDOS29 Interface Guide.

Interface between the user's CRT console and the remainder of the system is provided by CCP, which executes commands for functions such as: list file directives, display file contents, and execute user programs and . AmSYS29 utilities.

<sup>\*</sup> CP/M is a trademark of Digital Research Corporation.

As shown in figure 4-1, some utilities are intrinsic to AMDOS29 and reside permanently in CCP; others are disk resident and are executed in memory under CCP. The following description defines the utility programs supported by AMDOS29.

| _ | DIR          | **                                                         |

|---|--------------|------------------------------------------------------------|

| • |              | List file directory.                                       |

| • | TYPE         | Display contents of specified file.                        |

| • | ERA          | Erase specified file or files.                             |

| • | REN          | Rename specified file.                                     |

| • | SAVE         | Save memory on a diskette file.                            |

| • | USER         | Change user area on diskette.                              |

| • | PIP          | Perform inter-media data transfer.                         |

|   | SUBMIT/XSUB  |                                                            |

|   | SOBRITI ASOB | Submit specified file of commands for batch processing.    |

| • | STAT         | Identify or alter current peripheral-device as             |

|   |              | signments; display specified diskette and file             |

|   |              | characteristics.                                           |

| • | SYSGEN       | Duplicate AMDOS region of one diskette (tracks             |

| - |              | 0 and 1) on another diskette.                              |

| _ | DISPL        |                                                            |

|   | DISFL        | Display ASCII coded file on console (screen-<br>oriented). |

| • | DUMP         | Dump file, in hex format, to console.                      |

| • | VFU          | Pormland Will deformand on the 100 cms                     |

|   | 710          | Download VFU information to 120 CPS parallel printer.      |

| • | CPYDSK       | Copy contents of one diskette to another.                  |

| • | FORMAT       | Initialize a diskette for single or double                 |

|   |              | density use.                                               |

| • | PREHEAT      | PROM programming utilities.                                |

| • | ED           | Text editor.                                               |

| • | DDT          |                                                            |

| _ | FILCOM       | Program debugging tool.                                    |

| • | FILCOM       | Perform ASCII or binary compare of two files.              |

The BDOS internal-function utilities are illustrated in figure 4-1 and briefly defined below for reference only; refer to the System User's Interface Guide for a detailed description of the internals.

| _ | CEADON |                                                                 |

|---|--------|-----------------------------------------------------------------|

| • | SEARCH | Search directory for specific filename.                         |

| • | OPEN   | Open file for operations.                                       |

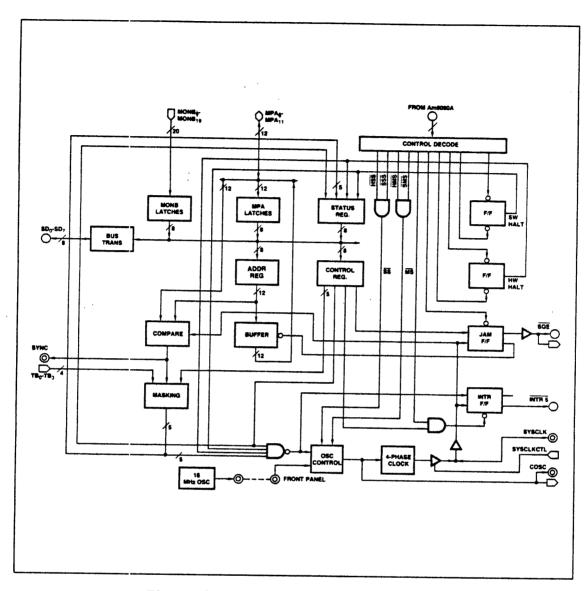

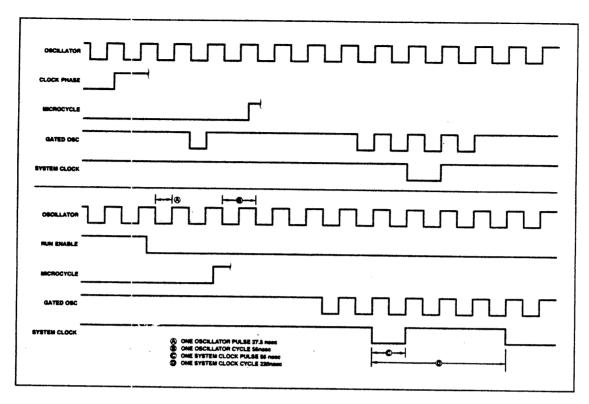

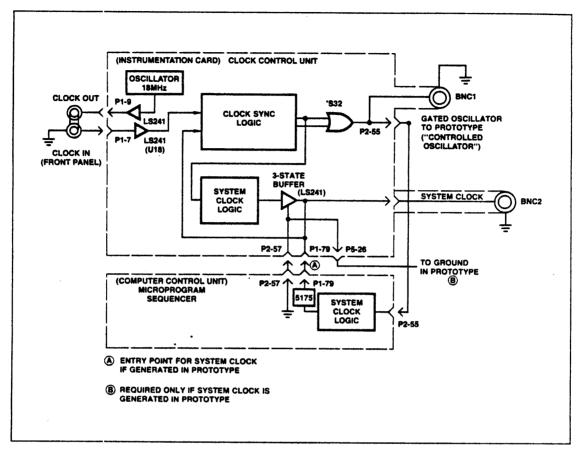

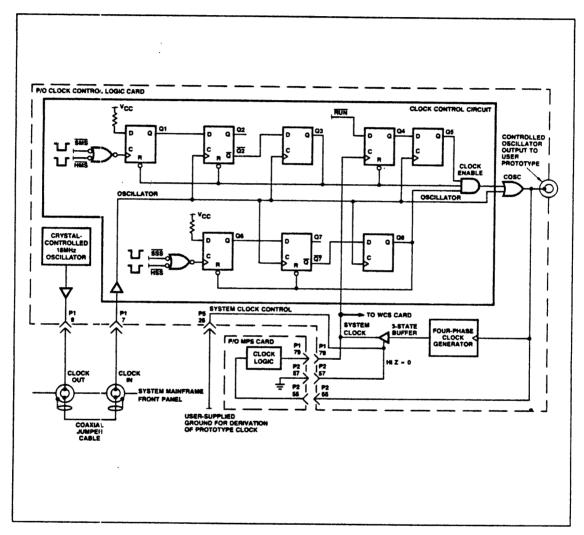

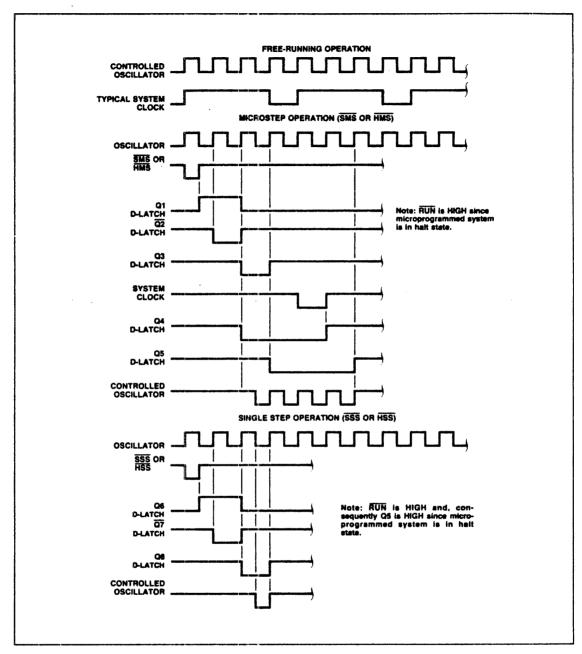

| • | CLOSE  | Close file after operation.                                     |