Advanced

Micro

Computers

A subsidiary of

Advanced Micro Devices

Am95/4005 MonoBoard Computer

**User's Manual**

|                                         | REVISION RECORD                                 |  |  |  |  |

|-----------------------------------------|-------------------------------------------------|--|--|--|--|

| REVISION                                | DESCRIPTION                                     |  |  |  |  |

| 01                                      | Preliminary Issue                               |  |  |  |  |

| (4/27/79)                               |                                                 |  |  |  |  |

| Α                                       | Manual Released                                 |  |  |  |  |

| (8/24/79)                               |                                                 |  |  |  |  |

| В                                       | Manual updated to correct documentation errors. |  |  |  |  |

| (10/2/79)                               |                                                 |  |  |  |  |

| С                                       | Manual Reprinted                                |  |  |  |  |

| (4/25/80)                               |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

| *************************************** |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

|                                         |                                                 |  |  |  |  |

| Publication No.                         | Address                                         |  |  |  |  |

REVISION LETTERS I, O, Q AND X ARE NOT USED

Copyright © 1979, 1980 Advanced Micro Computers Printed in U.S.A.

00680120

Address comments concerning this manual to:

ADVANCED MICRO COMPUTERS

Publications Department 3340 Scott Boulevard Santa Clara, CA 95051

#### **CORRECTION SHEET**

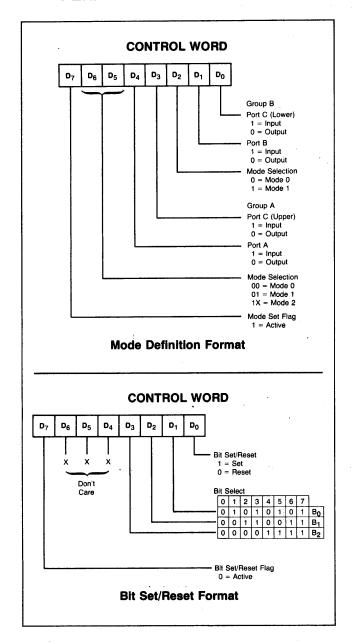

The Am9555 Programmable Peripheral Interface has been replaced on the 95/4005 MonoBoard by the Am8255A Programmable Peripheral Interface. All references in this manual to the Am9555 should be considered as references to the Am8255A.

#### **PREFACE**

This manual provides general information, an installation and interface guide, programming information, principles of operation, and service information for the Advanced Micro Computers AMC 95/4005 MonoBoard Computer. Additional information can be obtained from the following documents.

AMD 8080A/9080A MOS Microprocessor Handbook

AMD Schottky and Low Power Schottky Data Book

Am8251-Am9551 Data Sheet

Am9555A/8255A Data Sheet

Am9517 Data Sheet

Am9511 Data Sheet

Am9519 Data Sheet

Am9517 Application Note

Algorithm Details for the Am9511 Arithmetic Processor Unit

Designing Interrupt Systems with the Am9519 Universal Interrupt Controller This manual is intended for use by system designers familiar with microcomputer architecture that utilizes the Multibus<sup>†</sup>. The information presented is sufficient to support normal installation, system interface, and programming needs; a basic theory of operation and schematic diagrams are included to assist in isolating system problems.

In this manual both active-high (positive true) and active-low (negative true) signals appear in the text. To eliminate confusion, and simplify presentation, the following convention will be adhered to within this manual. Whenever a signal is active-low (negative true), its mnemonic is followed by an asterisk \* (i.e., MEMR\* denotes an active-low signal). For a signal that is active-high the asterisk is omitted (i.e., IORW denotes an active-high signal).

The information in this manual is believed to be accurate and complete at the time it was printed. However, AMC reserves the right to change specifications without notice. No responsibility is assumed for errors that might appear in this manual. No part of this manual may be copied or reproduced in any form without prior written permission from AMC.

<sup>&</sup>lt;sup>†</sup>Multibus is a trademark of Intel Corporation

### TABLE OF CONTENTS

| 1. | GENERAL INFORMATION                           |                             |    | Am9555 Operation Control Word Format     | 3-6         |

|----|-----------------------------------------------|-----------------------------|----|------------------------------------------|-------------|

|    | Introduction                                  | 1-1                         |    | Am9555 Bit Set/Reset                     | <b>J</b> -0 |

|    | Physical Description                          | î-î                         |    | Control Word                             | 3-6         |

|    | Functional Description                        | 1-1                         |    | Am9555 Port C Status Read                | 3-6         |

|    | Specifications                                | $\frac{1}{1} - \frac{1}{4}$ |    | Interrupt Control Programming            | 3-16        |

|    |                                               | 7-4                         |    | Am9519 Addressing                        | 3-16        |

|    |                                               |                             |    | Am9519 Initialization                    | 3-16        |

| 2. | INSTALLATION AND INTERFACE                    |                             |    | Am9519 Command                           | 5-10        |

|    | THE THE THE THE THE THE                       |                             |    | Descriptions                             | 3-17        |

|    | Introduction                                  | 2-1                         |    | Am9519 Status Read                       | 3-20        |

|    | Unpacking and Inspection                      | 2-1                         |    | Multimode Direct Memory Access           |             |

|    | Power Requirements                            | 2-1                         |    | (DMA) Controller Programming             | 3-21        |

|    | Cooling Requirements                          | 2-1                         |    | Am9517 Addressing                        | 3-21        |

|    | User Selectable Options                       | 2-1                         |    | Am9517 Command Register                  | 3-21        |

|    | Serial I/O Interface                          | 2-1                         |    | Am9517 Command Register                  | 3-21        |

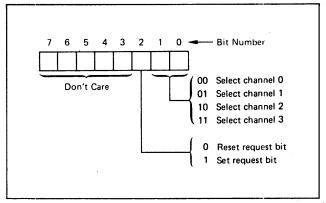

|    | Baud Rate Selection                           | 2-1                         |    | Am9517 Request Register                  | 3-22        |

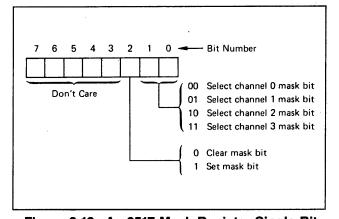

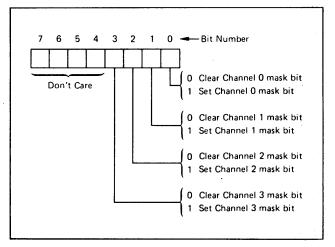

|    | Priority Interrupt Jumpers.                   | 2-3                         |    | Am9517 Mask Register                     | 3-22        |

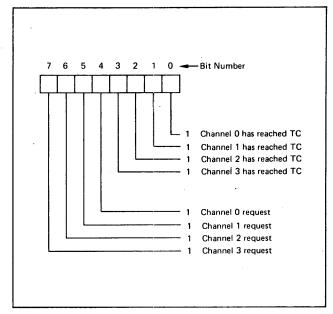

|    | Parallel I/O Jumper Option.                   | 2-3<br>2-3                  |    | Am9517 Temporary Register                | 3-22        |

|    | Memory Selection                              | 2-3<br>2-4                  |    | Am9517 Clear First/Last                  | 3-22        |

|    | Am9080 Ready Timing Option.                   | 2-4                         |    |                                          | 3-23        |

|    | APIL Clock for Ontion 100                     | 2-4<br>2-4                  |    | Flip/Flop Command<br>Am9517 Master Clear | 3-23        |

|    | APU Clock for Option 100 Multi-Master Control | 2-4<br>2-5                  |    | Am9517 Master Crear                      | 3-23        |

|    | Intenface Possinements                        | 2-5<br>2-5                  |    | Arithmetic Processing Unit               | 3-23        |

|    | Interface Requirements Serial I/O Interface   | 2-5<br>2-5                  |    | Programming                              | 3-23        |

|    | Danallol I/O Interface                        |                             |    | Programming                              |             |

|    | Parallel I/O Interface                        | 2-5                         |    | Am9511 Addressing                        | 3-23        |

|    | Auxiliary Connector P2 Bus Interface          | 2-6<br>2-6                  |    | Am9511 Initialilzation                   | 3-23        |

|    | bus interrace                                 | 2-0                         |    | Am9511 Data Formats                      | 3-23        |

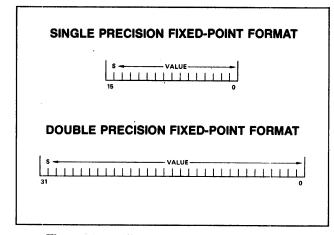

|    |                                               |                             |    | Fixed-Point                              | 3-24        |

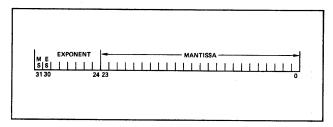

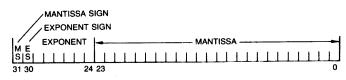

| 3. | OPERATION AND PROGRAMMING                     |                             |    | Floating-Point                           | 3-24        |

| ٥. | OPERATION AND PROGRAMMING                     |                             |    | Am9511 Command Descriptions              | 3-25        |

|    | Introduction                                  | 2 1                         |    | Am9511 Status Read                       | 3-25        |

|    | Introduction                                  | 3-1                         |    |                                          |             |

| ٠  | Address Assignment                            | 3-1                         | 1  | THEORY OF OPERATION                      |             |

|    | Bus Override and Boot Control                 | 2 1                         | 4. | THEORY OF OPERALION                      |             |

|    |                                               | 3-1                         |    | Turking disability                       | A 1         |

|    | Memory Select PROM                            | 2 2                         |    | Introduction                             | 4-1         |

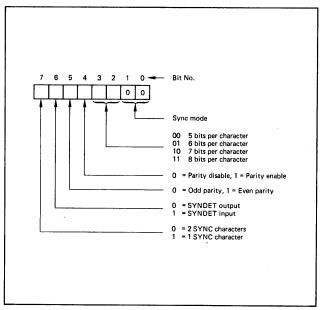

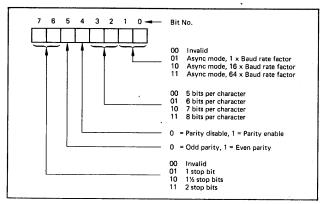

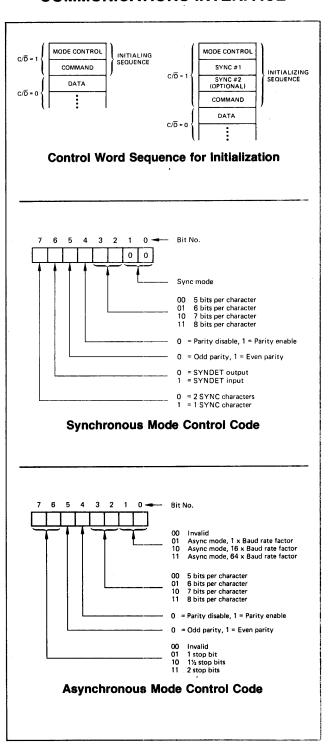

|    | Programming<br>Serial I/O Interface           | 3-3                         | ÷  | Central Processing Unit                  | A 1         |

|    |                                               | 2 2                         |    | (CPU) Group                              | 4-1         |

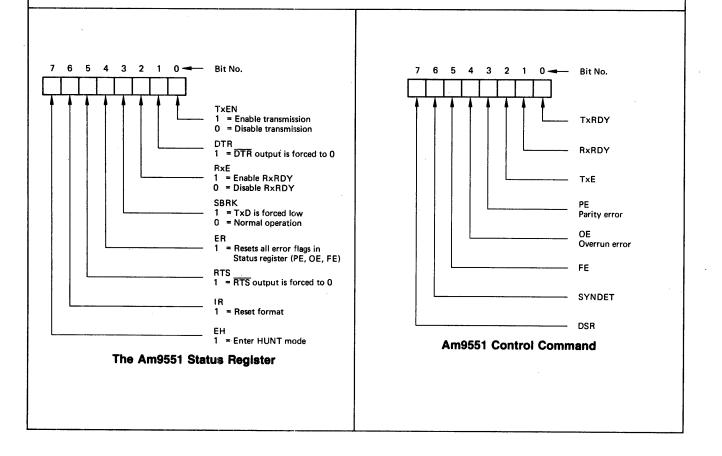

|    | ProgrammingAm9551 Initialization              | 3-3                         |    | Multi-Master Bus Control                 | 4-3         |

|    | Amorea Made Instruction                       | 3-3                         |    | On-Board Memory                          | 4-4         |

|    | Am9551 Mode Instruction                       | 2.4                         |    | Read Only Memory (ROM/                   |             |

|    | Word Format                                   | 3-4                         |    | E-PROM)                                  | 4-4         |

|    | Am9551 Sync Characters                        | 3-4                         |    | Random Access Memory (RAM).              | 4-4         |

|    | Command Instruction                           | 2 [                         |    | I/O Address Decoding                     | 4-5         |

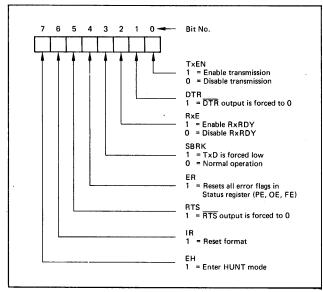

|    | Word Format                                   | 3-5                         |    | Serial I/O Interface                     | 4-5         |

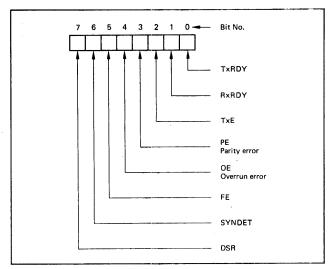

|    | Am9551 Status Read                            | 3-5                         |    | Parallel I/O Interface                   | 4-7         |

|    | Parallel I/O Interface                        | 2 6                         |    | Interrupt Controller                     | 4-8         |

|    | Programming                                   | 3-6                         |    | Arithmetic Processing                    | 4 ^         |

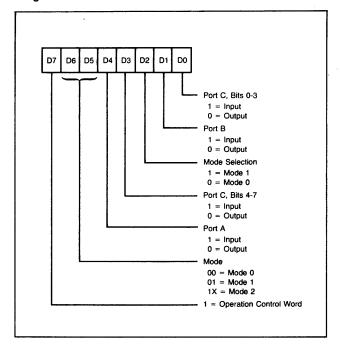

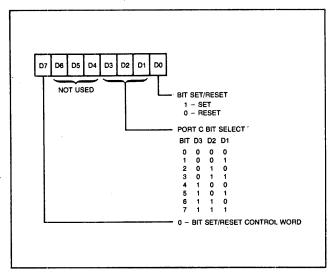

|    | Am9555 Addressing                             | 3-6                         |    | Unit (APU)                               | 4-9         |

|    | Am9555 Initialization                         | 3-6                         |    | Direct Memory Access                     | 1 0         |

|    |                                               |                             |    | Controller                               | 4-9         |

### **TABLE OF CONTENTS (Cont.)**

| APPE        | ENDIXES                                          |            | 3-19. | Am9511 Status Register Bit Definitions       | 3-25     |

|-------------|--------------------------------------------------|------------|-------|----------------------------------------------|----------|

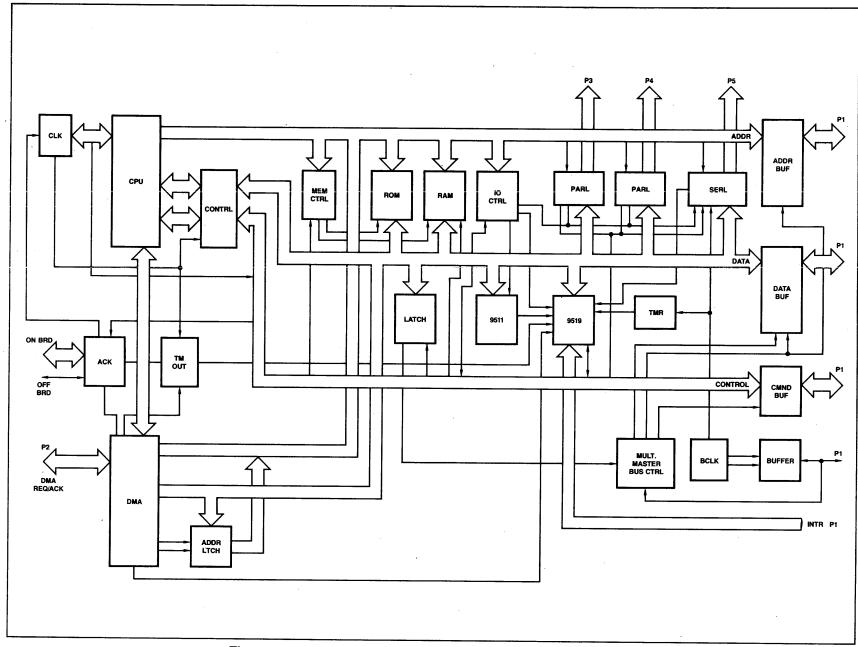

| Α.          | Command Summaries                                | A-1<br>B-1 | 4-1.  | AMC 95/4005 MonoBoard Computer Block Diagram | 4-1      |

| B.<br>C.    | Instruction Set Summary ASCII Character Set      | C-1        |       | Computer brock bragiam                       | -11      |

| D.          | Service Information                              | D-1        |       |                                              |          |

|             |                                                  | -          | TABLE | S                                            |          |

| FIG         | JRES                                             |            | 1-1.  | Specifications                               | 1-5      |

| •           |                                                  |            | 2-1.  | RS232C Data Set                              | 2-2      |

| 1-1         |                                                  |            | 2-2.  | 20mA Current Loop                            | 0.0      |

|             | Computer Block Diagram                           | 1-2        | 2 2   | Interface Jumpers                            | 2-2      |

| 2-1         |                                                  | 2.6        | 2-3.  | RS232C Data Processing Terminal Interface    | 2-2      |

| 2 2         | Terminator                                       | 2-6        | 2-4.  | Serial I/O Connector P5                      | 2-2      |

| 2-2         |                                                  |            | 2-4.  | Pin Assignments                              | 2-3      |

|             | Timing (Continuous Bus                           | 2-14       | 2-5.  | Baud Rate Selection                          | 2-3      |

| 2-3         | Control)                                         | 2-14       | 2-6.  | Priority Interrupt                           | 2-5      |

| 2-3         | Timing (Continuous Bus                           |            |       | Jumpers                                      | 2-4      |

|             | Control)                                         | 2-14       | 2-7.  | Memory Jumper Connections                    | 2-4      |

| 3-1         |                                                  |            | 2-8.  | Parallel I/O Mating                          |          |

| 0 1         | Control Code                                     | 3-4        |       | Connections                                  | 2-5      |

| 3-2         |                                                  | • .        | 2-9.  | Parallel I/O Connector                       |          |

| _           | Control Code                                     | 3-4        |       | P3 Pin Assignments                           | 2-5      |

| 3-3         |                                                  |            | 2-10. | Parallel I/O Connector                       |          |

| _           | Instruction Word Format                          | 3-5        |       | P4 Pin Assignments                           | 2-6      |

| 3-4         |                                                  | 3-5        | 2-11. | Parallel I/O Socket                          |          |

| 3-5         | • Am9555 Operation Control                       |            |       | Compatible Line Drivers                      | 2-6      |

|             | Word Format                                      | 3-6        | 2-12. | Connector P2 Pin                             |          |

| 3-6         | <ul> <li>Bit Set/Reset Control</li> </ul>        |            |       | Assignments                                  | 2-6      |

|             | Word Format                                      | 3-16       | 2-13. | System Bus Connector P1                      | 0 7      |

| 3-7         | •                                                | 0.16       | 0 1/1 | Assignments                                  | 2-7      |

|             | Requirements                                     | 3-16       | 2-14. | AMC 95/4005 Bus DC Characteristics           | 2-8      |

| 3-8         |                                                  | 2 20       | 2_15  | AMC 95/4005 Bus Exchange                     | 2-0      |

| 2 0         | Definition                                       | 3-20       | 7-15. | AC Characteristics (2MHz                     |          |

| 3-9         | . Am9517 Command Register<br>Control Word Format | 3-21       |       | Clock)                                       | 2-10     |

| 2_1         | O. Am9517 Mode Register                          | 3-21       | 2-16. | AMC 95/4005 Continuous                       | _ 10     |

| 3-1         | Control Word                                     | 3-21       | _ 10. | Bus Control AC Charac-                       |          |

| 3_1         | 1. Am9517 Request Register                       | J-21       |       | teristics (2MHz Clock)                       | 2-11     |

| <b>J</b> -1 | Data Word                                        | 3-22       | 2-17. | AMC 95/4005 Bus Exchange                     |          |

| 3-1         | 2. Am9517 Mask Register                          | ·          |       | AC Characteristics (3MHz                     |          |

| -           | Single-Bit Instruction                           | 3-22       |       | Clock)                                       | 2-12     |

| 3-1         | 3. Am9517 Mask Register                          |            | 2-18. | AMC 95/4005 Continuous                       |          |

|             | Four-Bit Instruction                             | 3-22       |       | Bus Control AC Charac-                       |          |

| 3-1         | 4. Am9517 Status Word Format                     | 3-23       |       | teristics (3MHz Clock)                       | 2-13     |

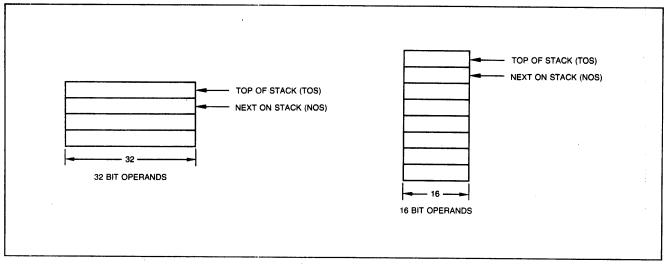

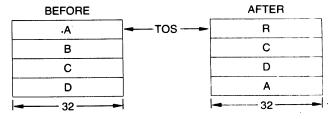

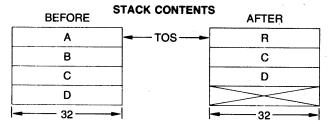

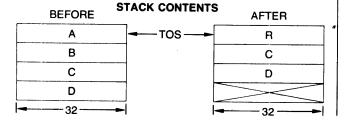

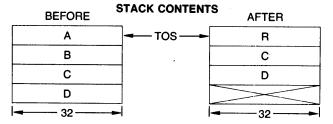

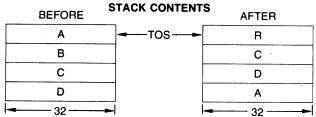

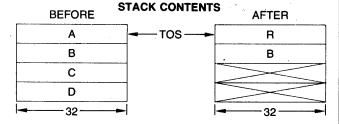

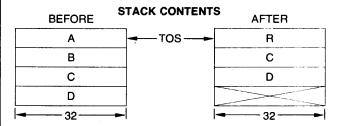

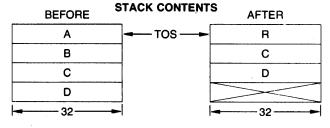

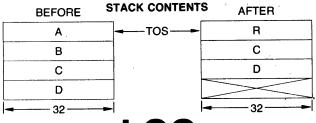

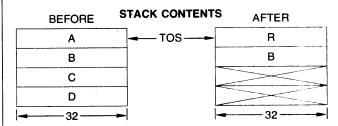

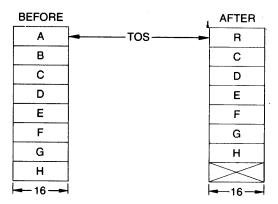

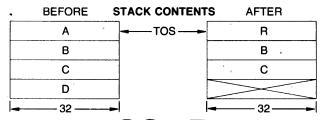

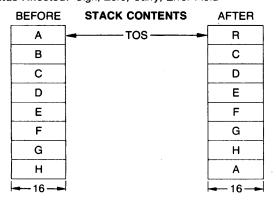

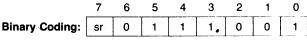

| 3-1         | 5. Am9511 Data Stack                             |            | 3-1.  | I/O Port Addresses                           | 3-2      |

|             | Configuration                                    | 3-24       | 3-2.  | RAM Selection                                | 3-3      |

|             | 6. Fixed-Point Word Formats                      | 3-24       | 3-3.  | ROM Selection                                | 3-3      |

| 3-1         | 7. Floating-Point Word                           | 0.61       | 3-4.  | Parallel I/O Port                            | <u> </u> |

|             | Formats                                          | 3-24       |       | Configuration Summary                        | 3-7      |

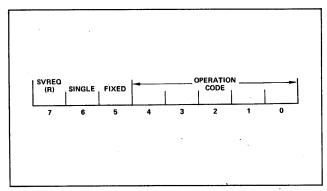

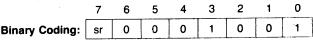

| ે ≺_1       | 8 Am9511 Command Format                          | 3-25       |       |                                              |          |

# CHAPTER 1 GENERAL INFORMATION

#### 1-1. INTRODUCTION

The AMC 95/4005 MonoBoard Computer (MBC) is a complete microcomputer on a single board. It is fully compatible with Intel iSBC board products. The AMC 95/4005 offers substantially increased performance with the 3MHz option. Major functional capabilities of the AMC 95/4005 include the following:

Standard 2MHz and optional 3MHz clock rate.

Comprehensive Direct Memory Access (DMA) capability with four fully independent channels, including a built-in Memory-to-Memory transfer capability as well as software-initiated DMA requests.

Special purpose Arithmetic Processing Unit (APU) that operates concurrently with the CPU to provide both fixed-point, floating-point and transcendental computational capability.

Eight fully-programmable vectored priority interrupt channels with provisions for software-generated interrupts.

Serial priority bus master for multi-master operation.

Provision for software set override to permit MonoBoard to retain control of bus regardless of requests by other masters.

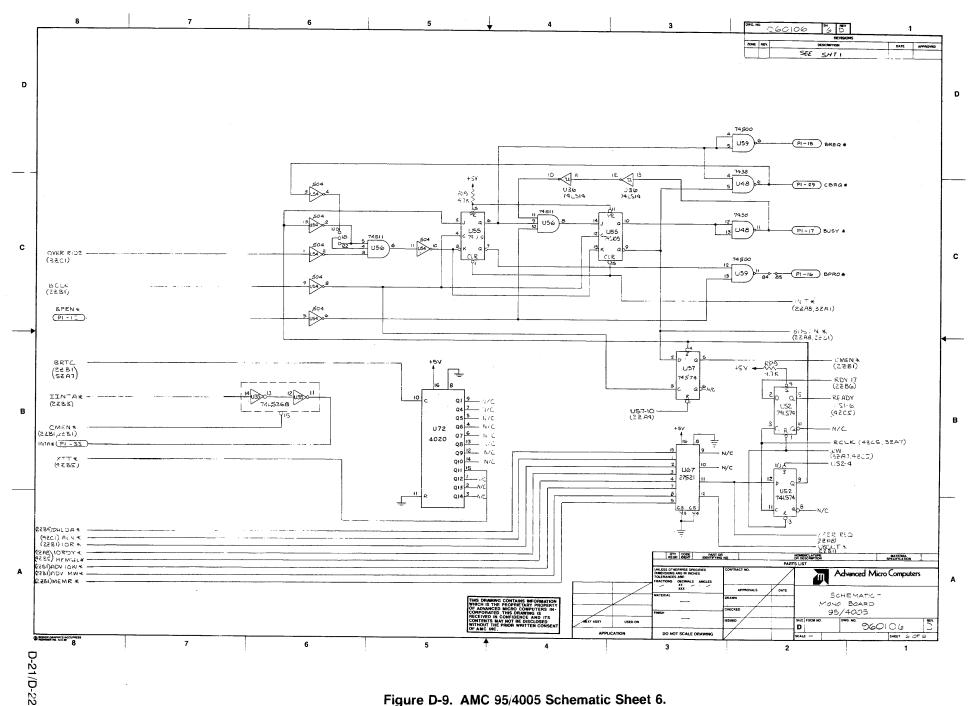

Serial Communications Interface with a 20mA current loop or RS232C capability and 13 switch selectable baud rates up to 9600 baud.

Parallel I/O Interface with 48 programmable I/O lines and sockets for drivers and receivers.

4 kilobytes of on-board read/write Random Access Memory (RAM)

Sockets for up to 16 kilobytes of on-board Read Only Memory (ROM/E-PROM)

Memory can be reconfigured by PROM programming.

Bootstrap program can be placed in on-board ROM and selected by poweron or initialization and then program disabled.

#### 1-2. PHYSICAL DESCRIPTION

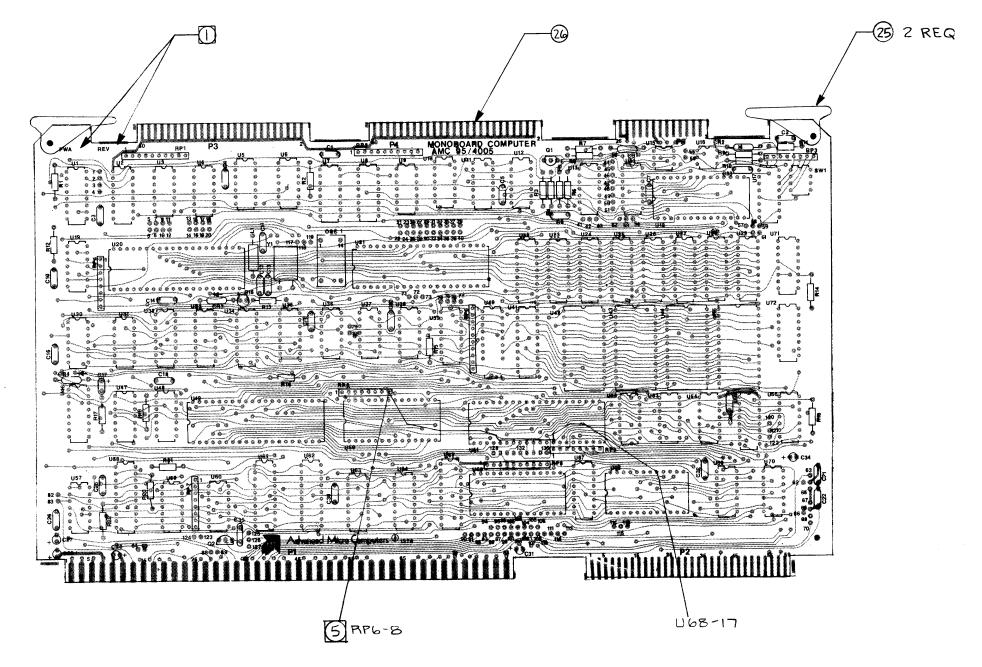

The AMC 95/4005 MonoBoard Computer (MBC) is a four layer printed circuit board with MSI TTL and LSI MOS circuits. Five edge connectors provide bus and peripheral interface capabilities. Physical characteristics of the AMC 95/4005 are:

**Board Dimensions**

Width 30.48 cm (12.00 inches)

Depth 17.15 cm (6.75 inches)

Thickness 1.50 cm (0.60 inches)

Environmental Requirements

Operating Temperature O°C to 55°C

Relative Humidity Up to 90% without condensation

Storage Temperature -40°C to +75°C

#### 1-3. FUNCTIONAL DESCRIPTION

The AMC 95/4005 MonoBoard Computer (MBC) is a complete microcomputer on a single board. The board is fully form-factor and bus compatible with Intel iSBC 80 single board products and is designed to operate with other bus masters in a serial priority multimaster environment. However, while

maintaining mechanical and interface compatibility with the iSBC 80 series, the AMC 95/4005 offers significantly higher throughput and increased computational power over the iSBC 80 boards.

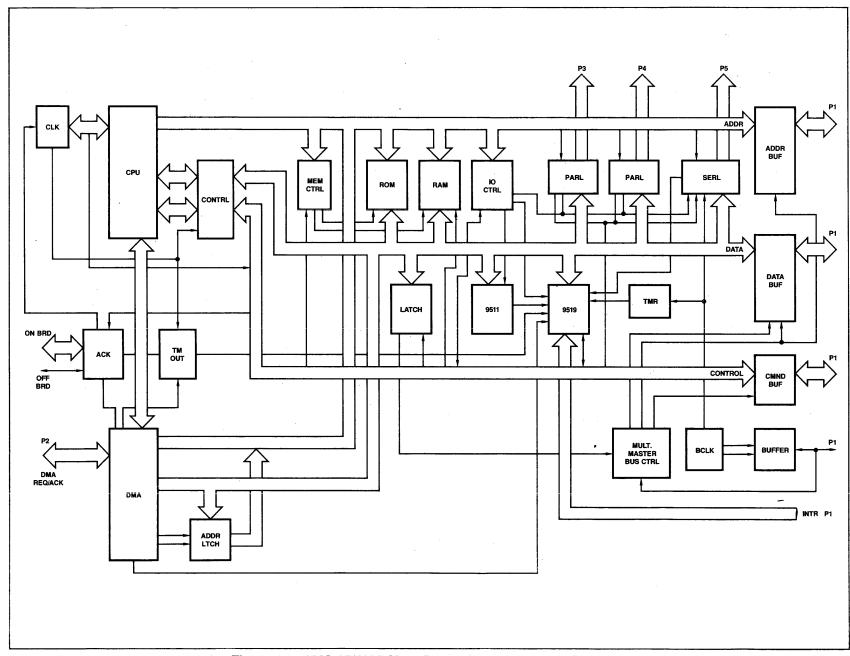

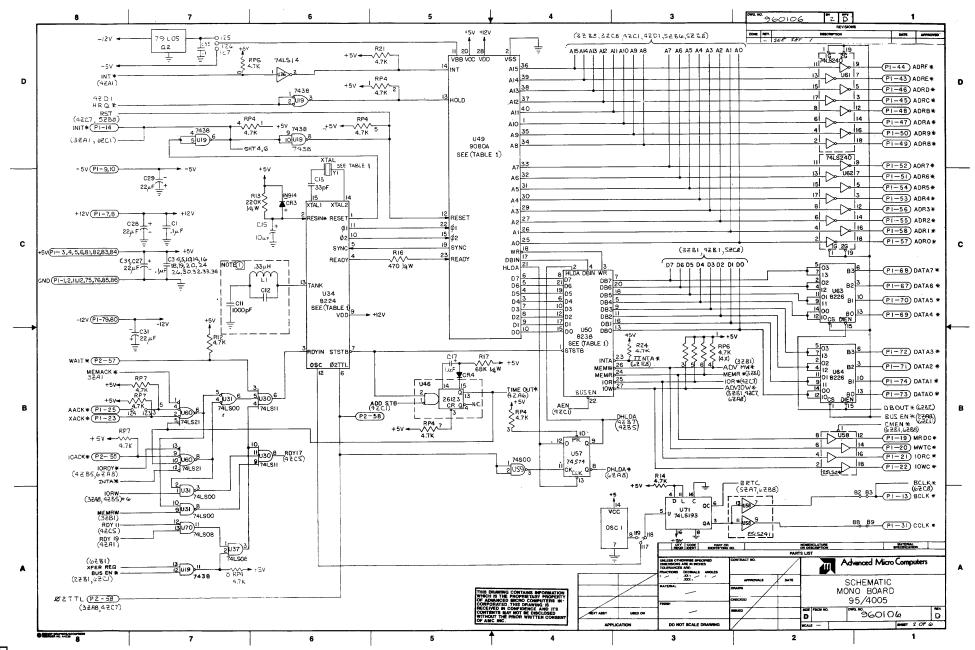

The standard board contains an Am9080A microprocessor which operates at 2MHz. a Multimode Direct Memory Access Controller, an Arithmetic Processor Unit, and a programmable eight level priority interrupt system. Additional features include: 4K bytes of RAM memory, sockets for up to 16K bytes of ROM and E-PROM memory, 48 programmable parallel I/O lines with sockets for line drivers or terminators, a programmable synchronous/asynchronous RS232C or 20mA current 1000 communication interface. switch selectable baud rate generator, and bus drivers for off-board memory and input/output expansion. Figure 1-1 is a block diagram of the AMC 95/4005.

A 3MHz version is available which substantially increases throughput. The 3MHz version provides all the features of the 2MHz board with an Am9080A-1 for 3MHz operation.

Direct addressing of up to 64K bytes of memory is supported by the 16-bit address bus of the Am9080. An external stack, located anywhere in RAM, can be used as a last-in/first-out stack to store the contents of the program counter, flags, accumulator, or any of the six general purpose registers. A 16-bit stack pointer controls the addressing of this external stack, which provides subroutine nesting that is bounded by memory size or 64K bytes, whichever is greater.

The Am8224 provides an oscillator, power-up controls, and two clock signals by dividing the frequency of the crystal oscillator by nine. The two clock signals (phase one and phase two) define the CPU minor cycle.

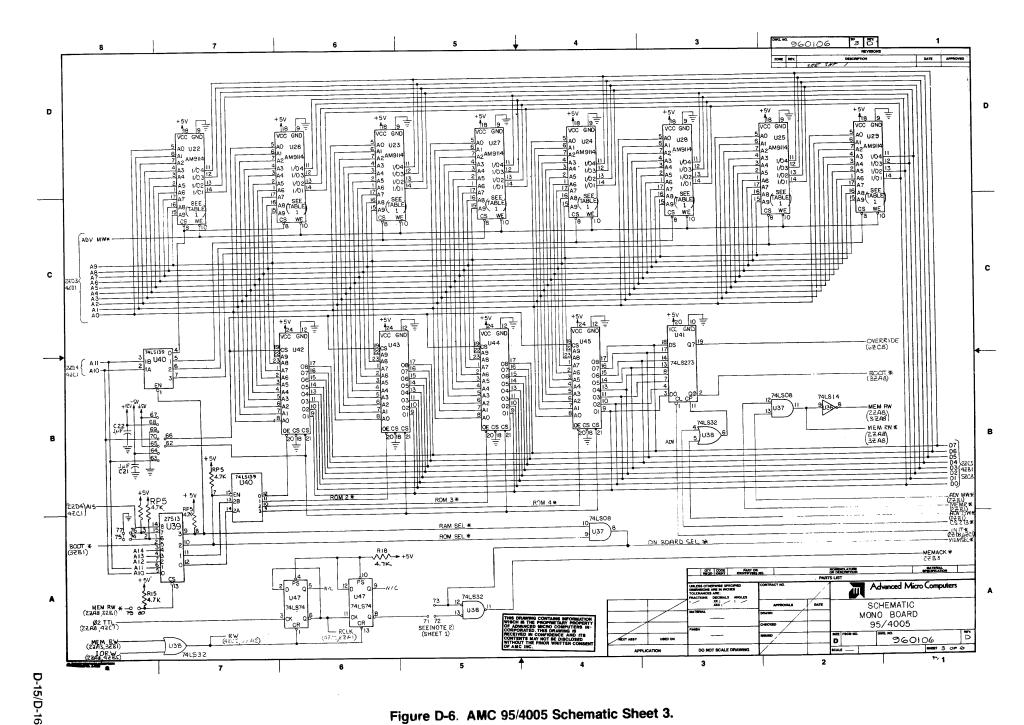

The Am8228 buffers the Data Bus and demultiplexes control signals to generate memory read/write and I/O read/write signals. The on-board memory system provides up to 4K bytes of read/

write random access memory using eight Am9114 1024 by 4-bit static memory chips. Up to 16K bytes of read only memory can be installed using four Am9732 or equivalent 4K by 8-bit E-PROM chips. Alternatively, four Am9708 or 9716 equivalent memory chips, or pin compatable ROMs/PROMs, can be used if less on-board memory is required. All of the on-board memory can be disabled to permit off-board memory selection. The address to memory chip location relationship can be changed by reprogramming a single address decode PROM. This enables users to insert their existing ROM or PROM resident programs in any memory chip location. Discrete logic associated with the memory system supplies the MEMSEL\* and MEMACK\* signals. The MEMACK\* signal indicates to the CPU that on-board memory has been selected. MEMSEL\* indicates to the bus control PROM that on-board memory. is selected.

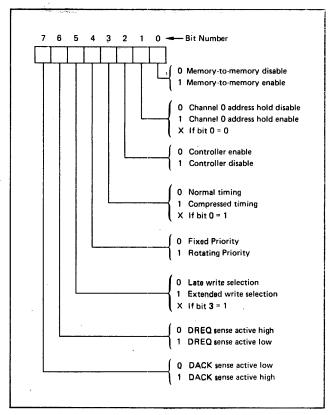

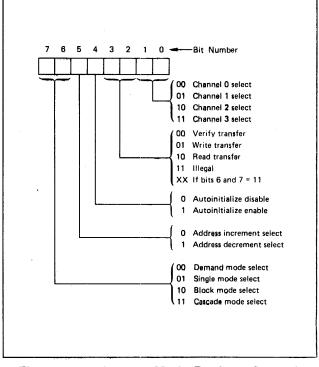

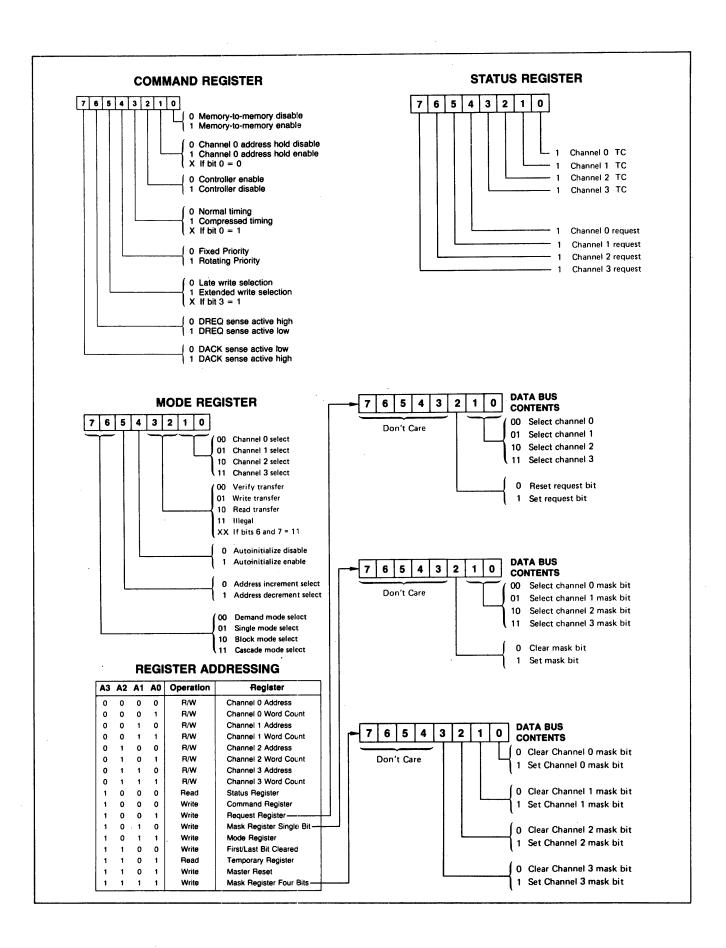

An Am9517 provides four fully-independent channels of direct memory access capability. DMA transfers can be performed at up to a 1.5 megabyte per second rate. Each DMA channel may be programmed to perform I/O-to-memory or memory-to-I/O operation. Channels 0 and 1 can also be programmed for memory-to-memory block moves. Each of the DMA channels can be programmed to autoinitialize at the conclusion of the specified transfer interval. This allows repetitive DMA operations for CRT display refresh or memory buffer transfers to/from high-speed disk to be accomplished without reprogramming the DMA channel. In addition to the memoryto-memory block transfer capability on channels 0 and 1, each of the DMA channels can be programmed to operate in one of three transfer modes.

First, a block transfer mode provides for uninterrupted transfer of an entire block of data; second, a demand transfer mode provides for uninterrupted transfer as long as the demand signal is present; and third, a single transfer mode allows the I/O and CPU to

Figure 1-1. AMC 95/4005 MonoBoard Computer Block Diagram.

interleave the use of available memory cycles. DMA transfers can be initiated by hardware or software. This allows diagnostic software to be incorporated in the user's system.

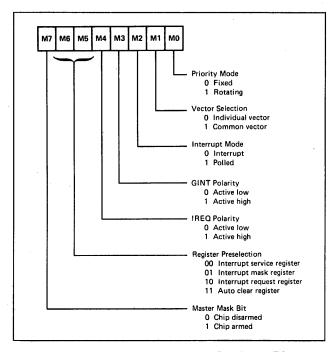

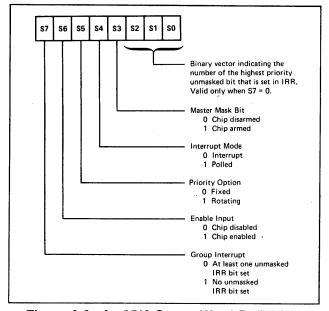

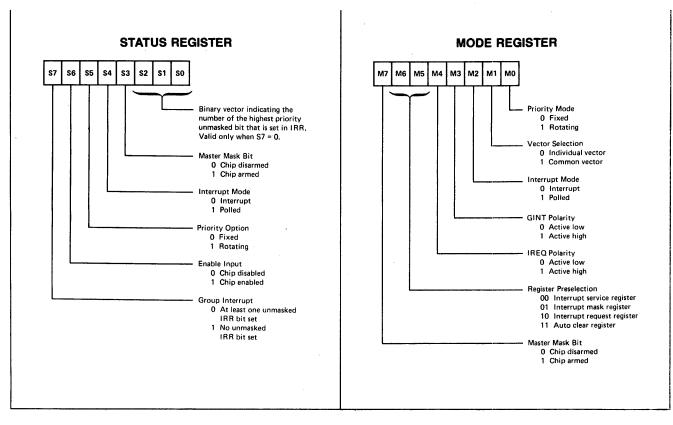

An Am9519 provides the basis for an eight channel vectored priority interrupt system. Each channel is associated with its own unique fourbyte location in an internal response The eight channels can be programmed to perform priority resolution on either a fixed or rotating basis in either an interrupt or polled mode, allowing the user flexibility to establish interrupt service priorities based upon his unique Interrupts can also be requirements. initiated by software command, thereby permitting the hardware to resolve the priorities of software tasks and allowing maintenance and diagnostic programs to be incorporated into the user's system.

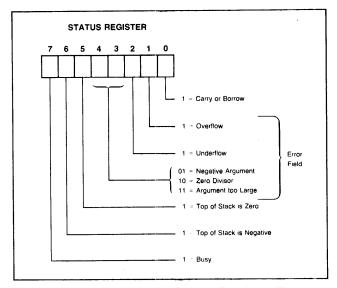

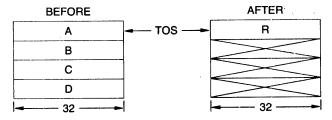

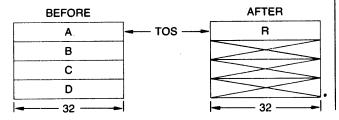

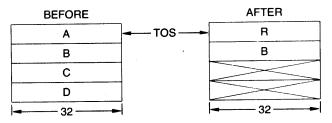

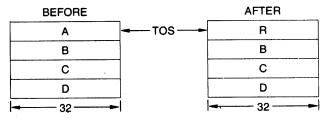

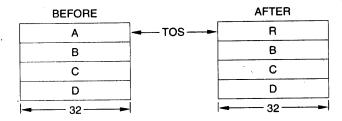

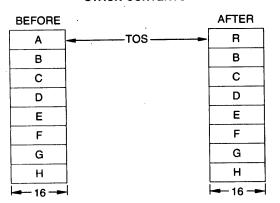

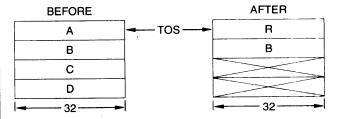

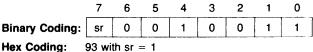

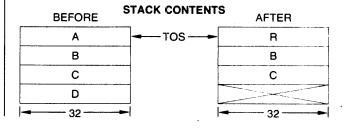

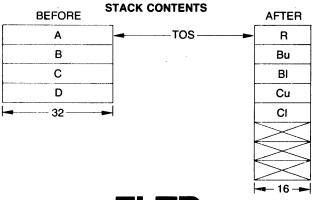

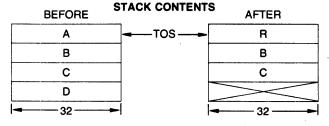

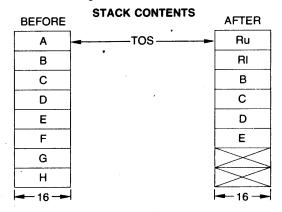

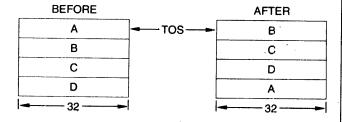

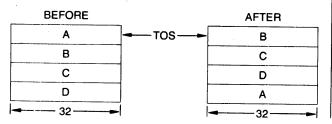

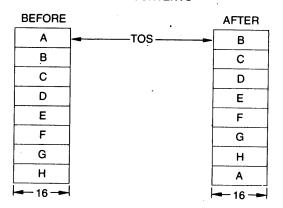

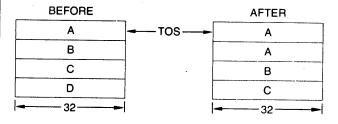

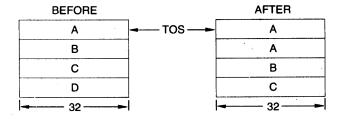

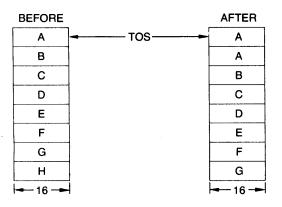

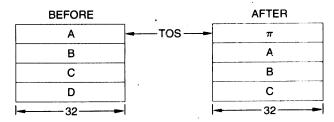

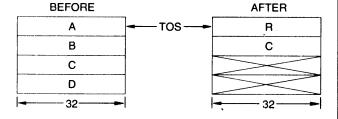

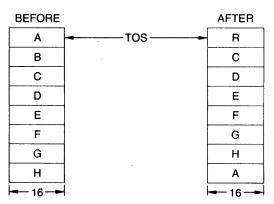

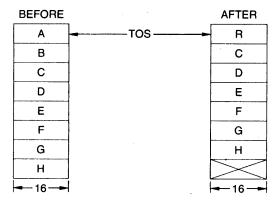

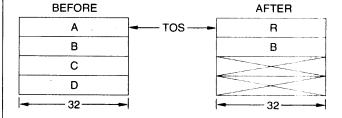

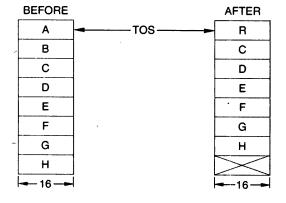

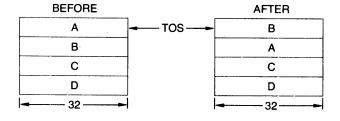

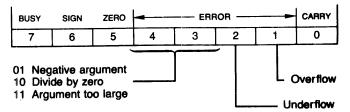

An Am9511 Arithmetic Processing Unit (APU) and its associated circuitry provide a full complement of fixed and floating point arithmetic and a variety of floating point transcendental and mathematical operations. All internal APU functions can operate concurrently with the CPU. Transfers to and from the APU are handled by the CPU. An Endof-Process signal (EOP\*) is issued by the APU, and can be used as an interrupt to the CPU to help coordinate program execution. All transfers (including operand, result, status and command information) are via the data bus. Operands required for APU operations are received from the data bus and stored in an internal stack. The 8-bit bytes received during a CPU write operation are assembled into 16-bit or 32-bit operands. As each successive operand is assembled in the internal stack, each previous operand is moved down one place in the stack. The last operand entered before an Am9511 command is executed resides at the top of the stack (TOS); the next to last operand entered is next on the stack

(NOS). When the Am9511 executes a command, the operands are obtained from TOS and NOS. Operation results are stored on the TOS, and the contents of the TOS are placed on the data bus during a CPU read operation. Each subsequent read operation reads NOS.

programmable communications interface, using an Am9551 USART, provides either a 20mA current loop interface or a standard RS232C communications interface. The Am9551 provides full duplex. double buffered transmit and receive capabilities. A switch selectable baud rate generator provides the common baud rates between 50 and 9600 baud. communications interface can be programmed to implement the desired synchronous or asynchronous serial data transmission protocol. Data format. control character format, parity and transmission rate are all under program control. Parity, overrun, and framing error detection are all incorporated on the programmable communications inter-Command and control lines, face. serial data lines, and signal ground lines are brought out to a 26-pin RS232C compatible connector.

The system contains 48 programmable parallel I/O lines implemented by using two Am9555 Programmable Peripheral Interface chips. System software can configure the I/O lines to sets of input, output or bidirectional input/ output ports. To take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and termination characteristics for each application. The programmable I/O lines and signal ground lines are brought out to two 50-pin edge connectors.

#### 1-4. SPECIFICATIONS

Specifications for the AMC 95/4005 MonoBoard Computer are listed in table 1-1.

#### TABLE 1-1. SPECIFICATIONS.

Word Size Instruction: 8, 16 or 24 bits Data: 8 bits Memory Addressing On-Board ROM/E-PROM: O-FFFH (using 1K devices) On-Board RAM: 3000-3FFFH (when using 1K or 2K ROMs) All on-board addresses can be disabled for off-board memory expansion. Memory Capacity On-Board ROM/E-PROM: Sockets for 16K bytes (using 4K devices) On-Board RAM: 4K bytes static (eight Am9114 chips) Off-Board Expansion: Up to 64K bytes Serial I/O Address Control: EDH Data: ECH Parallel I/O Address Connector P3: CONTROL: E7H Port A: E4H Port B: E5H Port C: E6H Connector P4: CONTROL: EBH Port A: E8H Port B: E9H Port C: EAH Parallel I/O Capacity: 48 Programmable lines Serial Communications Characteristics Synchronous: 5 to 8-bit characters Internal or External Character Synchronization 5 to 8-bit characters Asynchronous: Break Character Generation 1, 1 1/2, or 2 Stop bits False start bit detector Serial Baud Rates: Switch Selectable (See table 2-2) Interrupt Controller Addressing Control: C3H Data: C2H Latch: EØH

#### TABLE 1-1. SPECIFICATIONS. (Cont.)

-12V ±5%

| DMA Controller Addressing       |          |

|---------------------------------|----------|

| Channel O Address:              | вон      |

| Channel O Word Count            | B1H      |

| Channel 1 Address:              | B2H      |

| Channel 1 Word Count            | взн      |

| Channel 2 Address:              | B4H      |

| Channel 2 Word Count:           | B5H      |

| Channel 3 Address:              | B6H      |

| Channel 3 Word Count:           | B7H      |

| Command and Status Register:    | B8H      |

| Request Register:               | В9Н      |

| Mask Register (Single Bit)      | BAH      |

| Mode Register:                  | BBH      |

| Clear First/Last Flip-Flop      | BCH      |

| Temporary Register:             | BDH      |

| Master Clear:                   | BDH      |

| Mask Register (Four Bits):      | BFH      |

| Arithmetic Processing Unit Addr | essing   |

| Control:                        | C1H      |

| Data:                           | СОН      |

| Power Requirements              |          |

| V <sub>CC</sub>                 | +5v ±5%  |

| V <sub>DD</sub>                 | +12V ±5% |

|                                 |          |

| $v_BB$                          | -5V ±5%  |

|                                 |          |

|                 | Without.ROM<br>Memory |       |  |  |  |

|-----------------|-----------------------|-------|--|--|--|

|                 | Max Typica            |       |  |  |  |

| Icc             | 3.2A                  | 2.0A  |  |  |  |

| IDD             | . 300mA               | 190mA |  |  |  |

| I <sub>BB</sub> | 1mA                   | 1mA   |  |  |  |

| IAA             | 25mA                  | 20mA  |  |  |  |

V<sub>AA</sub>

#### NOTE:

A -5 volt regulator is used to supply -5 volts to the Am9080. When 2708 E-PROMs are used, an external -5 volts must be supplied.

### TABLE 1-1. SPECIFICATIONS. (Cont.)

Am9511 Command Execution Times

| Command             |                                         | μSE            | c I       |

|---------------------|-----------------------------------------|----------------|-----------|

| Command<br>Mnemonic | Description                             | 95/4005/2      | 95/4005/3 |

|                     | 32-bit floating-point inverse cosine    | 3152-4141      | 2101-2761 |

| ACOS                | 32-bit floating-point inverse sine      | 3116-3970      | 2077-2647 |

| ASIN                | 32-bit floating-point inverse tangent   | 2496-3268      | 1664-2179 |

| ATAN                | 32-bit fixed-point sign change          | 12-14          | 8.0-9.3   |

| CHSD                | 32-bit floating-point sign change       | 8-10           | 5.3-6.7   |

| CHSF                | 32-Dit floating-point sign change       | 10-12          | 6.7-8.0   |

| CHSS                | 16-bit fixed-point sign change          | 1920-2440      | 1280-1627 |

| cos                 | 32-bit floating-point cosine            | 10-12          | 6.7-8.0   |

| DADD                | 32-bit fixed-point add                  | 98-106         | 65-71     |

| DDIV                | 32-bit fixed-point divide               | 96-106         | 64-71     |

| DMUL                | 32-bit fixed-point multiply, lower      | 92-112         | 61-75     |

| DMUU                | 32-bit fixed-point multiply, upper      | 18 <b>-</b> 20 | 12.0-13.3 |

| DSUB                | 32-bit fixed-point subtract             | 1898-2440      | 1265-1627 |

| EXP                 | 32-bit floating-point exponentiation    | 28-184         | 19-123    |

| FADD                | 32-bit floating-point add               |                | 52.0-61.3 |

| FDIV                | 32-bit floating-point divide            | 78 <b>-</b> 92 | 31-112    |

| FIXD                | 32-bit floating-point to 32-bit         | 46-168         | 31-112    |

|                     | fixed-point conversion                  | 46 100         | 21 72     |

| FIXS                | 32-bit floating-point to 16-bit         | 46-108         | 31-72     |

|                     | fixed-point conversion                  | 00 470         | 10 115    |

| FLTD                | 32-bit fixed-point to 32-bit            | 28-172         | 19-115    |

|                     | floating-point conversion               |                | 01 0 50 0 |

| FLTS                | 16-bit fixed point to 32-bit            | 32-78          | 21.3-52.0 |

|                     | floating-point conversion               |                | 10 0 55 0 |

| FMUL                | 32-bit floating-point multiply          | 74-84          | 49.3-56.0 |

| FSUB                | 32-bit floating-point subtraction       | 36-186         | 24-124    |

| LOG                 | 32-bit floating-point common logarithm  | 2238-3566      | 1492-2377 |

| LN                  | 32-bit floating-point natural logarithm | 2140-3478      | 1427-2319 |

| NOP                 | No operation                            | 2              | 1.3       |

| POPD                | 32-bit stack pop                        | 6<br>6<br>5    | 4.0       |

| POPF                | 32-bit stack pop                        | 6              | 4.0       |

| POPS                | 16-bit stack pop                        | 5              | 3.3       |

| PTOD                | Push 32-bit TOS onto stack              | 10             | 6.7       |

| PTOF                | Push 32-bit TOS onto stack              | 10             | 6.7       |

| PTOS                | Push 16-bit TOS onto stack              | 8              | 5.3       |

| PUPI                | Push 32-bit floating-point π onto TOS   | 8              | 5.3       |

| PWR                 | 32-bit floating-point X to the Y power  | 4146-6016      | 2764-4011 |

| SADD                | 16-bit fixed-point add                  | 8-9            | 5.3-6.0   |

| SDIV                | 16-bit fixed-point divide               | 42-48          | 28-32     |

| SIN                 | 32-bit floating-point sine              | 1898-2404      | 1265-1603 |

| SMUL                | 16-bit fixed-point multiply, lower      | 42-48          | 28-32     |

| SMUU                | 16-bit fixed-point multiply, upper      | 40-49          | 27-33     |

| SQRT                | 32-bit floating-point square root       | 392-436        | 261-291   |

| SŠUB                | 16-bit fixed-point subtract             | 14-16          | 9.3-11    |

| TAN                 | 32-bit floating-point tangent           | 2448-2944      | 1632-1963 |

| XCHD                | Exchange 32-bit stack operands          | 13             | 8.6       |

| XCHS                | Exchange 16-bit stack operands          | 9              | 6.0       |

# CHAPTER 2 INSTALLATION AND INTERFACE

#### 2-1. INTRODUCTION

This section provides information for installing and interfacing the AMC 95/4005 MonoBoard Computer (MBC). These instructions include unpacking and inspection, power requirements, cooling requirements, user selectable options, bus interface characteristics, and connector pin assignments.

#### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request the carrier's agent to be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection. Shipping damages should be immediately reported to the carrier.

#### NOTE

Do not attempt to service the board yourself as this will void the warranty:

It is suggested that salvageable shipping cartons and packing materials be saved for use in case the product must be shipped in the future.

#### 2-3. POWER REQUIREMENTS

The AMC 95/4005 requires +5, -5, +12V, and -12V power supply inputs. The current required from these supplies is listed in table 1-1. Ensure that the power supply has sufficient current to accomodate the AMC 95/4005 requirements.

#### 2-4. COOLING REQUIREMENTS

The AMC 95/4005 dissipates approximately 500 gram-calories/minute (2.1 Btu/minute), and adequate air circulation must be provided to prevent a temperature rise above 55°C (130°F).

#### 2-5. USER SELECTABLE OPTIONS

The AMC 95/4005 is designed as a general purpose microcomputer; therefore, several optional jumpers might be necessary before operation. The following paragraphs provide instructions for optional jumper configurations.

#### 2-6. SERIAL I/O INTERFACE

The serial I/O interface is designed to interface both RS232C devices or a 20mA current loop device such as the tele-The configuration, as shipped from the factory, is jumpered for an RS232C interface as shown in table 2-1. installed Jumpers must be jumper pins 46 and 50 and jumper pins 47 and 48 when the Data Set Ready and Clear to Send signals are required on Connector P5. The jumper configuration for a 20mA current loop is shown in table 2-2. If an RS232C interface is used, the Am9551 can be configured to function as a data set or a data processing terminal. Connector pin assignments for connecting the P5 connector to a terminal and a modem are shown in tables 2-3 and 2-4.

#### 2-7. BAUD RATE SELECTION

A crystal controlled baud rate generator provides an on-board baud rate clock for serial I/O interface. The baud rate is selectable via a four position dip switch. Table 2-5 shows the baud rate as a function of the switch settings.

TABLE 2-1. RS232C INTERFACE JUMPERS.

| 95                       | 51                               | lumpon                                    | Connection                                                                      |  |

|--------------------------|----------------------------------|-------------------------------------------|---------------------------------------------------------------------------------|--|

| Pin                      | Mnemonic                         | Jumper                                    | Connection                                                                      |  |

| 3<br>19<br>17<br>9<br>25 | RxD<br>TxD<br>CTS*<br>TxC<br>RxC | 53-52<br>42-41<br>49-51<br>61-59<br>60-61 | P5-3 (RECEIVED DATA) P5-5 (TRANSMITTED DATA) Ground U17-9 (CLOCK) U17-9 (CLOCK) |  |

TABLE 2-2. 20mA CURRENT LOOP INTERFACE JUMPERS.

| 9551                                 |                                                  | lumpon                                                             | Connection                                                                                                               |  |

|--------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                  | Mnemonic                                         | Jumper                                                             | connection                                                                                                               |  |

| 19<br>24<br>23<br>17<br>9<br>25<br>3 | TxD<br>DTR*<br>RTS*<br>CTS*<br>TxC<br>RxC<br>RxD | 42-43<br>46-44<br>48-49, 47-51<br>49-48<br>59-61<br>61-60<br>53-54 | P5-25 (TTY TX) P5-6 (TTY RDR CONTROL) 9551 PIN 17 (CTS) 9551 PIN 23 (RTS) BAUD RATE CLK BAUD RATE CLK P5-22 (TTY RX RET) |  |

In the asynchronous mode, TxC and RxC can be connected to externally supplied clocks via jumpers 57-61 and 58-60.

TABLE 2-3. CONNECTOR P5 TO TERMINAL CONNECTOR PIN ASSIGNMENTS.

| Pin                                                               | Signal                                                                                                                                                          | DB-25<br>Pin No.                                               | Pin                                                                        | Signal                                                                                                                                            | DB-25<br>Pin No.                                                       |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | CHASSIS GND Not Used TRANSMITTED DATA Not USed RECEIVED DATA TTY RDR CONTROL REQUEST TO SEND Not Used CLEAR TO SEND Not Used DATA SET READY Not Used SIGNAL GND | 1<br>14<br>2<br>15<br>3<br>16<br>4<br>17<br>5<br>18<br>6<br>19 | 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | DATA TERM READY/TX CLK DATA CARRIER RET TTY RDR CONTROL Not Used Not Used Not Used Not Used TTY RX RET/RX CLK TTY RX TTY RX RET TTY TX SIGNAL GND | 20<br>8<br>21<br>9<br>22<br>10<br>23<br>11<br>24<br>12<br>25<br>23<br> |

TABLE 2-4. CONNECTOR P5 TO MODEM CONNECTOR PIN ASSIGNMENTS.

| Pin              | Signal            | RS232C<br>Pin No. |

|------------------|-------------------|-------------------|

| 1                | CHASSIS GND       | 1                 |

| 2                | Not Used          |                   |

| 3                | TRANSMITTED DATA  | 3                 |

| 1<br>2<br>3<br>4 | Not Used          |                   |

| 5                | RECEIVED DATA     | 2                 |

| 5<br>6<br>7      | TTY RDR CONTROL   |                   |

| 7                | REQUEST TO SEND   | 5                 |

| 8                | Not Used          |                   |

| 9                | CLEAR TO SEND     | 4                 |

| 10               | Not Used          |                   |

| 11               | DATA SET READY    | 20                |

| 12               | Not Used          |                   |

| 13               | SIGNAL GND        | 7                 |

| 14               | DATA TERM READY/  | 6/15              |

|                  | TX CLK            |                   |

| 15               | DATA CARRIER RET  |                   |

| 16               | TTY RDR CONTROL   |                   |

| 17               | Not Used          |                   |

| 18               | Not Used          |                   |

| 19               | Not Used          |                   |

| 20               | Not Used          |                   |

| 21               | Not Used          | <br>17            |

| 22               | TTY RX RET/RX CLK | 17                |

| 23<br>24         | TTY TX RET        |                   |

| 24<br>25         | TTY TX            |                   |

| 26               | SIGNAL GND        | , <b></b>         |

| 20               | SIGNAL GIND       |                   |

#### 2-8. PRIORITY INTERRUPT JUMPERS

The priority interrupt jumper matrix provides for eight out of sixteen possible interrupts to be jumpered to the eight interrupt controller inputs. When the .833msec real time clock interrupt is selected, the system can be interrupted at a fixed rate to service some real time event. Table 2-6 shows the possible jumper configurations for the interrupt controler inputs.

#### 2-9. PARALLEL I/O JUMPER OPTION

The parallel I/O section is configured for Am8216/8226 bidirectional bus

TABLE 2-5. BAUD RATE SELECTION.

| BAUD                                                                                         | Sı                                        | witch P                              | ositi                                               | on                                             |  |  |

|----------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------|-----------------------------------------------------|------------------------------------------------|--|--|

| DAUD                                                                                         | 4                                         | 3                                    | 2                                                   | 1                                              |  |  |

| 50<br>75<br>110<br>134.5<br>150<br>200<br>300<br>600<br>1200<br>1800<br>2400<br>4800<br>9600 | 0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>1<br>1<br>1<br>1<br>0<br>0 | 1<br>1<br>0<br>1<br>0<br>0<br>1<br>1<br>1<br>1<br>0 | 0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>1<br>0 |  |  |

| 1 = open p                                                                                   | 1 = open position                         |                                      |                                                     |                                                |  |  |

drivers at ports E4H and E8H. As delivered from the factory, jumpers are installed between jumper pins 2 and 3, and between jumper pins 23 and 24; this ties the Am8216/8226 DIEN\* inputs to pin 6 of ports E6H and EAH, thereby configuring both ports E4H and E8H as bidirectional ports. Either or both ports can be configured as input or output ports with the following changes.

| CONFIGU-<br>RATION | PORT | REMOVE   | E IN: | STALL  |

|--------------------|------|----------|-------|--------|

| Input              | E4H  | 2 and    | 3 1   | and 2  |

| Input              | E8H  | 23 and 2 | 24 21 | and 23 |

| Output             | E4H  | 2 and    | 3 2   | and 4  |

| Output             | E8H  | 23 and 2 | 24 22 | and 23 |

All lines for ports E6H and EAH are jumper connected to their line driver/terminator sockets. This allows complete flexibility for signal interchange when operating in mode 2.

TABLE 2-6. PRIORITY INTERRUPT JUMPERS.

| Signal                      | Pin No.              | Column 1<br>Jumper Pins | Column 2<br>Jumper Pins | INT Input |

|-----------------------------|----------------------|-------------------------|-------------------------|-----------|

| XTT* (RTC)<br>ERROR* (9512) | On-Board<br>On-Board | 107<br>113              |                         |           |

| EOP* (9517)                 | On-Board             | 105                     |                         |           |

| TIME OUT                    | On-Board             | 103                     |                         |           |

| INT 11*                     | On-Board             | 109                     |                         |           |

| INT 51A* (TxRDY)            | On-Board             | 112                     | 108                     | IRQ0*     |

| INT 51B* (RxRDY)            | On-Board             | 111                     | 106                     | IRQ1*     |

| SPARE                       | On-Board             | 110                     | 104                     | IRQ3*     |

| IRQ7*                       | P1-36                | 90                      | 102                     | IRQ4*     |

| IRQ6*                       | P1 <b>-</b> 35       | 91                      | 100                     | IRQ4*     |

| IRQ5*                       | P1 <b>-</b> 38       | 92                      | 98                      | IRQ5*     |

| IRQ4*                       | P1-37                | 93                      | 96                      | IRQ6*     |

| IRQ3*                       | P1-40                | 95                      | 94                      | IRQ7*     |

| IRQ2*                       | P1-39                | 97                      |                         | -1147     |

| IRQ1*                       | P1-42                | 99                      |                         |           |

| IRQO*                       | P1-41                | 101                     |                         |           |

#### 2-10. MEMORY SELECTION

To customize the AMC 95/4005 board for the type of memory devices being used. jumper connections must be made as shown on table 2-7. The memory address to memory device relationship is controlled by the address decoder PROM at As delivered, the PROM location U39. is programmed as shown in figure D-2. Information on how to program the PROM

TABLE 2-7. MEMORY JUMPER CONNECTIONS.

| Function                                                     | M                       |                        |                    |               |

|--------------------------------------------------------------|-------------------------|------------------------|--------------------|---------------|

| runction                                                     | Am9708                  | Am9716                 | Am9732             | 2758          |

| Address<br>Address<br>+12V to<br>pin 19<br>GND to            | 76-77<br>74-75<br>66-68 | 76-77 <sup>-</sup><br> |                    | <br><br>66-69 |

| pin 19<br>A10<br>A11<br>-5V to<br>pin 21<br>+5V to<br>pin 21 | <br>62-64<br>           | 66-70<br><br><br>62-65 | 66-70<br>62-63<br> |               |

for unique system requirements is presented in chapter 3. A jumper must be connected between jumper pins 79 and 80 to enable on-board memory.

#### 2-11. Am9080A READY TIMING OPTION

The MonoBoard Computer has a set of jumper pins associated with the 9080A Ready input. When operating with the 3MHz option, one wait state is required for a ROM. A jumper is installed between jumper pins 71 and 72 to delay the MEMACK\* signal and ensure the wait state. When operating with a 2MHz clock, the jumper is removed between jumper pins 71 and 72 and a jumper is installed between jumper pins 72 and

#### 2-12. APU CLOCK FOR 95/4005/3

When operating a 3MHz MonoBoard, the Am9511 APU operates on a 3MHz clock. Jumper pins 114, 115 and 116 allow the user to use the 3MHz phase two TTL clock or the APU internal clock. For APU operation with the phase two TTL clock, install a jumper between jumper pins 114 and 115. For the APU to operate on its internal clock, remove the jumper between jumper pins 114 and

115 and install a jumper between pins 115 and 116.

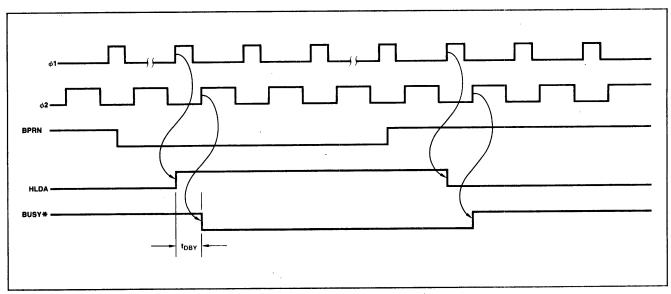

#### 2-13. MULTI-MASTER CONTROL

The board, as shipped, is configured for serial bus priority resolution; a jumper is connected between jumper pins 84 and 85. Remove this jumper to configure the board for parallel priority resolution. Jumper pins 120, 121, and 122 select the conditions that cause the board to give up control of the bus. When a jumper is connected between jumper pins 120 and 121, the MonoBoard will retain control until another external bus request is received. When a jumper is connected between jumper pins 121 and 122, the MonoBoard gives up control after each bus transfer. shipped, a jumper is connected between pins 121 and 122.

#### 2-14. INTERFACE REQUIREMENTS

The following paragraphs identify the board external connections and bus signal characteristics and timing.

#### 2-15. SERIAL I/O INTERFACE

The serial I/O interface communicates with an external devie via 26-pin PC edge connector P5. An external device can be connected to P5 using a 3M 3462-0001 flat cable connector or a TI H312113 or AMP 1-583715-1 solder connector. When connected to a DB-25 connector, the connector pins are numbered differently. Table 2-4 is a pin list for connector P5 and includes a cross reference to standard RS232C pin numbering.

#### 2-16. PARALLEL I/O INTERFACE

The parallel I/O interface communicates with external I/O devices via two 50-pin double sided edge connectors P3 and P4. External devices can be attached to P3 or P4 using one of the mating connectors listed in table 2-8. Tables 2-9 and 2-10 provide a pin list for

TABLE 2-8. PARALLEL I/O MATING CONNECTORS.

| Connector<br>Type | Vendor                     | Part No.                                               |

|-------------------|----------------------------|--------------------------------------------------------|

| Flat Cable        | 3M<br>Amp                  | 3415-0001<br>2-86792-3                                 |

| Soldered          | AMP<br>VIKING<br>TI        | 2-583715-3<br>3VH25/1JV-5<br>H312125                   |

| Wire-wrap         | TI<br>VIKING<br>CDC<br>ITT | H311125<br>3VH25/1JND-5<br>VPB01B25D00A1<br>EC4A050A1A |

| Crimp             | AMP                        | 1-583717-1                                             |

TABLE 2-9. PARALLEL I/O CONNECTOR P3 PIN ASSIGNMENTS.

| ASSIGNMENTS.                                                                                                                                  |         |                                                                                                                                                 |                                                                                                                                                |        |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| Pin                                                                                                                                           |         | Signal                                                                                                                                          | Pin                                                                                                                                            | Signal |  |  |

| 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23<br>25<br>27<br>29<br>31<br>33<br>35<br>37<br>39<br>41<br>43<br>45<br>47<br>49 | Port E6 | Bit 7 Bit 6 Bit 5 Bit 5 Bit 2 Bit 2 Bit 2 Bit 2 Bit 5 Bit 5 Bit 5 Bit 5 Bit 5 Bit 7 Bit 5 Bit 7 Bit 5 Bit 10 Bit 10 Bit 10 Bit 10 Bit 10 Bit 10 | 2<br>4<br>6<br>8<br>10<br>12<br>14<br>16<br>18<br>20<br>22<br>24<br>26<br>28<br>30<br>32<br>34<br>36<br>38<br>40<br>42<br>44<br>46<br>48<br>50 | GND    |  |  |

|                                                                                                                                               |         |                                                                                                                                                 |                                                                                                                                                |        |  |  |

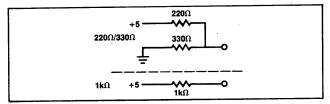

connectors P3 and P4. TTL line drivers compatible with the I/O driver sockets in the parallel I/O interface are Parallel I/O listed in table 2-11. interface lines can be terminated by either a  $220\Omega/330\Omega$  divider or a  $1K\Omega$ pull-up as shown in figure 2-1.  $220\Omega/330\Omega$  divider is stocked by distributors under Intel part number and Semiconductor iSBC-901 National part number BLC-901. The 1KΩ pull-up is stocked under Intel part number iSBC-902 and National Semiconductor part number BLC-902.

#### 2-17. AUXILIARY CONNECTOR P2

Connector P2 is a 60-pin double sided edge connector that provides interface to the DMA Controller and various other signals. Table 2-12 is a pin list for connector P2.

TABLE 2-10. PARALLEL I/O CONNECTOR P4 PIN ASSIGNMENTS.

| Pin                                                |         | Signal                                          | Pin                                                | Signal |

|----------------------------------------------------|---------|-------------------------------------------------|----------------------------------------------------|--------|

| 1<br>3<br>5<br>7<br>9<br>11<br>13                  | Port E9 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 | 2<br>4<br>6<br>8<br>10<br>12<br>14<br>16           | GND    |

| 17<br>19<br>21<br>23<br>25<br>27<br>29<br>31       | Port EA | Bit 3 Bit 2 Bit 1 Bit 0 Bit 4 Bit 5 Bit 6 Bit 7 | 18<br>20<br>22<br>24<br>26<br>28<br>30<br>32       |        |

| 33<br>35<br>37<br>39<br>41<br>43<br>45<br>47<br>49 | Port E8 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 | 34<br>36<br>38<br>40<br>42<br>44<br>46<br>48<br>50 | GND    |

#### 2-18. BUS INTERFACE

This section describes the signals that interface the MonoBoard Computer to the external system bus. signals shown with an asterisk (\*) following the signal

Figure 2-1. Parallel I/O Line Terminator.

TABLE 2-11. PARALLEL I/O SOCKET COMPATIBLE LINE DRIVERS.

| Driver | Characteristic                                         | Sink Current |

|--------|--------------------------------------------------------|--------------|

| 7438   | I, OC                                                  | . 48mA       |

| 7437   | I.                                                     | 48mA         |

| 7432   | NI                                                     | 16mA         |

| 7426   | I, 0C                                                  | 16mA         |

| 7409   | NÍ, OC                                                 | 16mA         |

| 7408   | NI                                                     | 16mA         |

| 7403   | I, 0C                                                  | 16mA         |

| 7400   | I                                                      | 16mA         |

| Note:  | I = inverting;<br>NI = non-inverti<br>OC = open collec |              |

TABLE 2-12. CONNECTOR P2 PIN ASSIGNMENTS.

| Pin | Mnemonic | Function                   |

|-----|----------|----------------------------|

| 14  | SVACK*   | 9511 SVACK                 |

| 39  | SVREQ*   | 9511 SVREQ                 |

| 40  | DRQ0     | DMA Request O              |

| 42  | DACKO*   | DMA Acknowledge 0          |

| 44  | DRQ1     | DMA Request 1              |

| 46  | DACK1*   | DMA Acknowledge 1          |

| 48  | DRQ2     | DMA Request 2              |

| 50  | DACK2*   | DMA Acknowledge 2          |

| 52  | DRQ3     | DMA Request 3              |

| 54  | DACK3*   | DMA Acknowledge 3          |

| 56  | EOP*     | External End-Of-           |

| 55  | IOACK*   | Process<br>I/O Acknowledge |

| 57  | WAIT*    | External ready             |

| 58  | Ø2 TTL   | Ø2 TTL OUT                 |

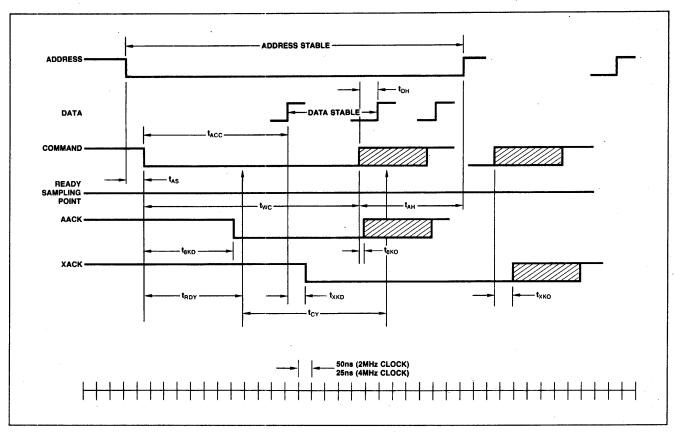

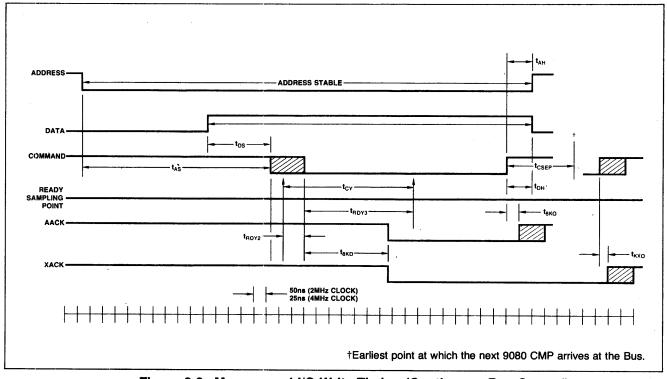

name are active-low signals. Connector P1 is an 86-pin double sided edge connector that provides the bus interface for the AMC 95/4005. Table 2-13 is a pin list for connector P1. DC characteristics for the bus interface are given in table 2-14. AC characteristics are given in tables 2-15 through 2-18 with timing shown in figures 2-2

through 2-4. When the MonoBoard is being used with another bus master, the BPRN\* input (P1-15) to the master assigned the highest priority must be tied low. The BPRN\* input to each master with the next lower priority must be connected to the BPRO\* output (P1-16) of the next higher priority master.

TABLE 2-13. SYSTEM BUS CONNECTOR P1 PIN ASSIGNMENTS.

|                   |                                                                | (Compone                                                           | ent Side)                                                                                                                                                                   |                                                                | (Circui                                                               | t Side)                                                                                                                                          |

|-------------------|----------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Pin                                                            | Mnemonic                                                           | Description                                                                                                                                                                 | Pin                                                            | Mnemonic                                                              | Description                                                                                                                                      |

| Power<br>Supplies | 1<br>3<br>5<br>7<br>9<br>11                                    | GND<br>+5<br>+5<br>+12<br>-5<br>GND                                | Signal GND<br>+5 VDC<br>+5 VDC<br>+12 VDC<br>-5 VDC<br>Signal GND                                                                                                           | 2<br>4<br>6<br>8<br>10<br>12                                   | GND<br>+5<br>+5<br>+12<br>-5<br>GND                                   | Signal GND<br>+5 VDC<br>+5 VDC<br>+12 VDC<br>-5 VDC<br>Signal GND                                                                                |

| Bus<br>Controls   | 13<br>15<br>17<br>19<br>21<br>23<br>25<br>27<br>29<br>31<br>33 | BCL K* BPRN* BUSY* MRDC* IORC* XACK* AACK* BHEN* CBRQ* CCLK* INTA* | Bus Clock Bus Priority In Bus Busy Mem. Read Command I/O Read Command XFER Acknowledge Advance Acknowledge Not Used Common Bus Request Constant Clock Interrupt Acknowledge | 14<br>16<br>18<br>20<br>22<br>24<br>26<br>28<br>30<br>32<br>34 | INIT* BPRO* BREQ* MWTC* IOWC* INH1* INH2* ADR10* ADR11* ADR12* ADR13* | Initialize Bus Priority Out Bus Request Mem. Write Command I/O Write Command Inhibit 1 (RAM) Inhibit 2 (ROM) Not Used Not Used Not Used Not Used |

| Interrupts        | 35<br>37<br>39<br>41                                           | IRQ6*<br>IRQ4*<br>IRQ2*<br>IRQ0*                                   | Interrupt Requests                                                                                                                                                          | 36<br>38<br>40<br>42                                           | IRQ7*<br>IRQ5*<br>IRQ3*<br>IRQ1*                                      | Interrupt Requests                                                                                                                               |

| Addresses         | 43<br>45<br>47<br>49<br>51<br>53<br>55                         | ADRE* ADRC* ADRA* ADR8* ADR6* ADR4* ADR2* ADRO*                    | Address Bus                                                                                                                                                                 | 44<br>46<br>48<br>50<br>52<br>54<br>56<br>58                   | ADRF* ADRD* ADRB* ADR9* ADR7* ADR5* ADR3* ADR1*                       | Address Bus                                                                                                                                      |

| Data              | 59<br>61<br>63<br>65<br>67<br>69<br>71                         | DATE* DATC* DATA* DAT8* DAT6* DAT4* DAT2* DAT0*                    | Not Used<br>Not Used<br>Not Used<br>Not Used<br>Data Bus                                                                                                                    | 60<br>62<br>64<br>66<br>68<br>70<br>72<br>74                   | DATF* DATD* DATB* DAT9* DAT7* DAT5* DAT5* DAT3*                       | Not Used<br>Not Used<br>Not Used<br>Not Used<br>Data Bus                                                                                         |

| Power<br>Supplies | 75<br>77<br>79<br>81<br>83<br>85                               | GND<br>-12<br>+5<br>+5<br>GND                                      | Signal GND<br>Reserved<br>-12 VDC<br>+5 VDC<br>+5 VDC<br>Signal GND                                                                                                         | 76<br>78<br>80<br>82<br>84<br>86                               | GND<br>-12<br>+5<br>+5<br>GND                                         | Signal GND<br>Reserved<br>-12 VDC<br>+5 VDC<br>+5 VDC<br>Signal GND                                                                              |

TABLE 2-14. AMC 95/4005 BUS DC CHARACTERISTICS.

| Signals     | Symbol          | Parameter<br>Description | Test<br>Conditions      | Min | Max   | Units |

|-------------|-----------------|--------------------------|-------------------------|-----|-------|-------|

| ADRQ*-ADRF* | VOL             | Output Low Voltage       | $I_{OL} = 50mA$         |     | 0.6   | ٧     |

| ADDRESS     | VOH             | Output High Voltage      | $I_{OH} = -10mA$        | 2.4 |       | ٧     |

|             | VIL             | Input Low Voltage        |                         |     | 0.95  | ٧     |

|             | VIH             | Input High Voltage       |                         | 2.0 |       | V     |

|             | IIL             | Input Current at Low V   | $V_{IN} = 0.45$         |     | -0.25 | mΑ    |

|             | IIH             | Input Current at High V  | $V_{IN} = 5.25V$        |     | 10    | μА    |

|             | CL              | Capacitive Load          |                         |     | 18    | pF    |

| MRDCI*,     | VOL             | Output Low Voltage       | $I_{OL} = 32mA$         |     | 0.4   | ٧     |

| MWTC*,      | VOH             | Output High Voltage      | $I_{OH} = -5.2$ mA      | 2.4 |       | ٧     |

| IORC*,      | I <sub>LH</sub> | Output Leakage High      | $v_0 = 2.4$             |     | 40    | μA    |

| IOWC*       | ILL             | Output Leakage Low       | $V_0 = 0.4$             |     | -40   | μA    |

|             | СL              | Capacitive Load          |                         |     | 15    | pF    |

| DATAO-      | V <sub>OL</sub> | Output Low Voltage       | $I_{OL} = 50mA$         |     | 0.6   | ٧     |

| DATA7       | VOH             | Output High Voltage      | $I_{OH} = -10mA$        | 2.4 |       | V     |

|             | VIL             | Input Low Voltage        |                         |     | 0.95  | V     |

|             | VIH             | Input High Voltage       |                         | 2.0 |       | V     |

|             | IIL             | Input Current at Low V   | $V_{IN} = 0.45$         |     | -0.25 | mA    |

|             | TLH             | Output Leakage High      | $V_0 = 5.25$            |     | 100   | μA    |

|             | ILL             | Output Leakage Low       | $v_0 = 0.45$            |     | 100   | μА    |

|             | CL              | Capacitive Load          |                         |     | 18    | pF    |

| INTI*       | VIL             | Input Low Voltage        |                         |     | 0.8   | ٧     |

|             | VIH             | Input High Voltage       |                         | 2.0 |       | ٧     |

|             | IIL             | Input Current at Low V   | $V_{IN} = 0.4V$         |     | -2.2  | mA    |

|             | IIH             | Input Current at High V  | $V_{IN} = 5.5V$         |     | 1     | mA    |

|             | CL              | Capacitive Load          |                         |     | 18    | pF    |

| BPRN*,      | VIL             | Input Low Voltage        |                         |     | 0.8   | ٧     |

| XACK*,      | V <sub>IH</sub> | Input High Voltage       |                         | 2.0 |       | V     |

| AACK*       | IIL             | Input Current at Low V   | $V_{IN} = 0.5$          |     | -2.6  | mA    |

|             | IIH             | Input Current at High    | $V_{IN} = 2.7V$         |     | 0.30  | ) mA  |

|             | CL              | Capacitive Load          |                         |     | 18    | рF    |

| BUSY*       | V <sub>OL</sub> | Output Low Voltage       | I <sub>OL</sub> = 25 mA |     | 0.4   | ٧     |

TABLE 2-14. AMC 95/4005 BUS DC CHARACTERISTICS. (Cont.)

| Signals           | Symbol          | Parameter<br>Description | Test<br>Conditions        | Min | Max  | Units |

|-------------------|-----------------|--------------------------|---------------------------|-----|------|-------|

| OPEN<br>COLLECTOR | CL              | Capacitive Load          |                           |     | 20   | pF    |

| INIT*             | V <sub>OL</sub> | Output Low Voltage       | I <sub>OL</sub> = 32 mA   | •   | 0.6  | V     |

| (SYSTEM           | VOH             | Output High Voltage      | OPEN COLLECTOR            |     |      |       |

| RESET)            | VIL             | Input Low Voltage        |                           |     | 0.7  | ٧     |

|                   | VIH             | Input High Voltage       |                           | 2.0 |      | ٧     |

|                   | IIL             | Input Current at Low V   | V <sub>IN</sub> = 5.5     |     | 0.1  | mA    |

|                   | IIH             | Input Current at High V  | $V_{IN} = 0.3$            |     | -0.7 | mA    |

|                   | CL              | Capacitive Load          |                           |     | 38   | pF    |

| BCLK*             | VOL             | Output Low Voltage       | I <sub>OL</sub> = 48 mA   |     | 0.5  | ٧     |

|                   | VOH             | Output High Voltage      | $I_{OH} = -1 \text{ mA}$  | 2.7 |      | ٧     |

|                   | Շլ              | Capacitive Load          |                           |     | 18   | pF    |

| EXT INTR*         | VIL             | Input Low Voltage        |                           |     | 0.8  | ٧     |

|                   | VIH             | Input High Voltage       | `                         | 2.0 |      | ٧     |

|                   | IIL             | Input Current at Low V   | $V_{IN} = 0.4V$           | 6.8 |      | mA    |

|                   | IIH             | Input Current at High V  | V <sub>IN</sub> = 5.5V    |     | 2    | mA    |

|                   | CL              | Capacitive Load          |                           |     | 18   | pF    |

| PORT E4           | VOL             | Output Low Voltage       | I <sub>OL</sub> = 20 mA   |     | •45  | ٧     |

| and E8            | VOH             | Output High Voltage      | .I <sub>OH</sub> = -12.mA | 2.4 |      | ٧     |

| BIDIREC-          | VIL             | Input Low Voltage        |                           |     | •95  | ٧     |

| TIONAL            | VIH             | Input High Voltage       |                           | 2.0 |      | ٧     |

| DRIVERS           | IIL             | Input Current at Low V   | V <sub>IN</sub> = 0.45    |     | 5.25 | mΑ    |

|                   | ILH             | Output Leakage High      | $V_0 = 5.25$              |     | .30  | mA    |

|                   | ILL             | Output Leakage Low       | $V_0 = 0.45$              |     | 5.25 | mΑ    |

|                   | CL              | Capacitive Load          |                           |     | 18   | pF    |

| Am9555            | VOL             | Output Low Voltage       | $I_{OL} = 1.7 \text{ mA}$ |     | .45  | ٧     |

| DR IVER/          | v <sub>OH</sub> | Output HIgh Voltage      | I <sub>OH</sub> = -50 μA  | 2.4 |      | ٧     |

| RECEIVER          | VIL             | Input Low Voltage        |                           |     | .8   | ٧     |

|                   | ٧ <sub>IH</sub> | Input High Voltage       |                           | 2.0 |      | ٧     |

|                   | IIL             | Input Current at Low V   | $V_{IN} = 0.45$           |     | 10   | μА    |

|                   | IIH             | Input Current at High V  | V <sub>IN</sub> = 5.0     |     | 10   | μΑ    |

|                   | CL              | Capacitive Load          |                           |     | 18   | pF    |

TABLE 2-15. AMC 95/4005 BUS EXCHANGE AC CHARACTERISTICS (2MHz CLOCK).

|                   | 0ve         | rall        | Read        | d           | Memory      | Write       |                                              |

|-------------------|-------------|-------------|-------------|-------------|-------------|-------------|----------------------------------------------|

| Para-<br>meter    | Min<br>(ns) | Max<br>(ns) | Min<br>(ns) | Max<br>(ns) | Min<br>(ns) | Max<br>(ns) | Description                                  |

| tAS               | 52          |             | 52          |             | 52          |             | Address Setup Time to Command                |

| t <sub>AH</sub>   |             |             |             |             | 79          |             | Address Hold Time                            |

| t <sub>DS</sub>   | 52          |             |             |             | 52          | :           | Data Setup Time to Command                   |