Advanced Micro Computers Distributed by Advanced Micro Devices

# Am96/4016 AmZ8000 Evaluation Board

**User's Manual**

|                 | REVISION RECORD   |             | D                           |

|-----------------|-------------------|-------------|-----------------------------|

| REVISION        |                   | DESCRIPTION |                             |

| 01              | Preliminary Issue |             |                             |

| (7/27/79)       |                   |             |                             |

| Α               | Manual Released   |             |                             |

| (11/8/79)       |                   |             |                             |

| $\mathcal{L}$   | UPPACE ON         | UP/DOWN     | LOADING                     |

| (21-JAN-80)     |                   |             |                             |

|                 |                   |             | -                           |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             | ·                           |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

|                 |                   |             |                             |

| Publication No. |                   |             |                             |

| 00680131        |                   |             | Address comments concerning |

REVISION LETTERS I, O, Q AND X ARE NOT USED

Copyright © 1979 Advanced Micro Computers Printed in U.S.A.

Address comments concerning this manual to:

ADVANCED MICRO COMPUTERS

**Publications Department** 3340 Scott Boulevard Santa Clara, CA 95051

### **PREFACE**

This manual is written for people who are thoroughly versed in the use of microcomputers. Many sections will contain more information than you need, and we encourage you to use the table of contents as a guide for your reading.

The information in this manual is believed to be accurate and complete at the time it was printed. However, AMC reserves the right to change specifications without notice. No responsibility is assumed for errors that might appear

in this manual. No part of this manual may be copied or reproduced in any form without prior written permission from AMC.

Publications related to this manual include:

AmZ8002 CPU Data Sheet AmZ8000 Family Interface Manual AmZ8000 Data Book AmZ8001/2 Processor Instruction Set Am96/4016-ASM Assembler Manual

# **TABLE OF CONTENTS**

| 1. | INTRODUCTION                |    | (H n) Set Half-Carry             |

|----|-----------------------------|----|----------------------------------|

|    |                             |    | Flag3-6                          |

|    | Description1-1              |    | (LOAD d:file,x) Down             |

|    | The CPU1-3                  |    | Load3-6                          |

|    | Memory1-7                   |    | $(M \times y, z)$ Move Memory3-6 |

|    | Input/Output1-7             |    | (NM) Enter Normal Mode3-6        |

|    | Software1-8                 |    | (P n) Set Parity Flag3-6         |

|    |                             |    | (P = x) Fill Program             |

|    |                             |    | Counter3-6                       |

| 2. | HARDWARE INSTALLATION AND   |    | (RHn = x) Fill High-             |

|    | INTERFACING                 |    | Byte Register3-6                 |

|    |                             |    | (RLn = x) Fill Low-              |

|    | Unpacking and Inspection2-1 |    | Byte Register3-6                 |

|    | Symbols2-1                  |    | (Rn = x) Fill Word               |

|    | Installation Overview2-1    |    | Register3-6                      |

|    | Rom/E-Prom Sockets2-1       |    | (SAVE d:file,x,y)                |

|    | Parallel I/O Driver/        |    | Up Load3-6                       |

|    | Terminators2-1              |    | (SM) Enter System Mode3-7        |

|    | Edge Connectors2-4          |    | (S n) Set Sign Flag3-7           |

|    | Keyboard/Display            |    | (S x) Display and                |

|    | Installation2-14            |    | Substitute Memory3-7             |

|    | Prototyping and             |    | (T m,n) Trace3-7                 |

|    | Memory-Expansion            |    | (V n) Set Overflow Flag3-7       |

|    | Boards2-14                  |    | (X) Display All                  |

|    | Amsys 8/8                   |    | Registers3-7                     |

|    | Interconnection2-14         |    | (XF) Display Flags3-7            |

|    | Jumper Options2-15          |    | (X n) Display Word               |

|    |                             |    | Register3-8                      |

|    |                             |    | (XP) Display Program             |

|    |                             |    | Counter3-8                       |

| 3. | OPERATION WITH THE MONITOR  |    | (Z n) Set Zero Flag3-8           |

|    |                             |    | Monitor I/O Support for          |

|    | Overview of Operations3-1   |    | User Programs3-8                 |

|    | Monitor Functions and       |    | AmSYS 8/8 Up/Down                |

|    | User Controls3-1            |    | Loading3-10                      |

|    | Monitor Commands3-3         |    |                                  |

|    | (ASM) Execute Assembler3-3  |    |                                  |

|    | (B x,y,z) Software          | 4. | PRINCIPLES OF OPERATION          |

|    | Breakpoint3-5               |    |                                  |

|    | (C n) Set Carry Flag3-5     |    | Power-Up Sequence4-1             |

|    | [(cr) after B or T]         |    | CPU Functions4-1                 |

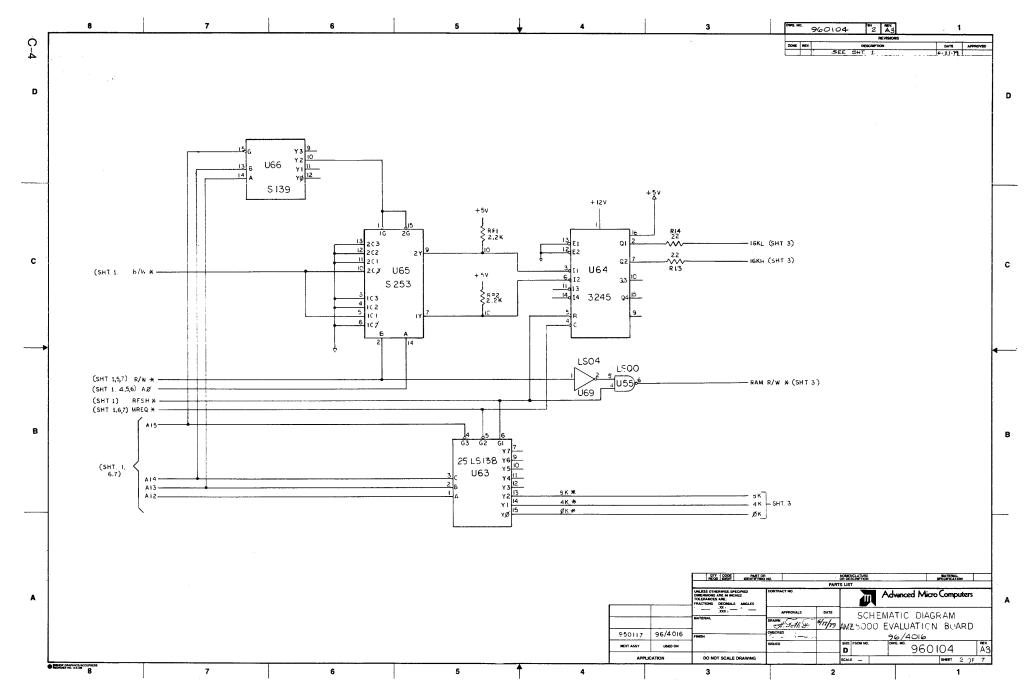

|    | Single-step3-5              |    | Bus Structure4-2                 |

|    | (D n) Set Decimal-Adjust    |    | Memory4-4                        |

|    | Flag3-5                     |    | Peripheral Decoding4-4           |

|    | (D x,y) Display Memory3-5   |    |                                  |

|    | (E x) Hardware              |    |                                  |

|    | Breakpoint3-5               | 5. | PERIPHERAL PROGRAMMING           |

|    | (F x,y,z) Fill Memory3-5    |    |                                  |

|    | (G x) Éxecute Program3-6    |    | Parallel I/05-1                  |

|                     | Serial I/05-3              | 2-1          | Rom/E-Prom Addresses       |

|---------------------|----------------------------|--------------|----------------------------|

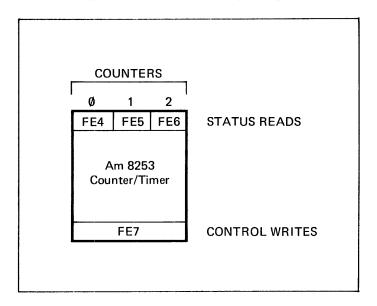

|                     | Counter/Timer5-7           |              | and Sockets2-3             |

|                     |                            | 2-2          | Driver/Terminators for     |

|                     |                            |              | Parallel Ports2-3          |

| Appe                | endixes                    | 2-3          | Other Driver/Terminator    |

|                     |                            |              | Circuits for P32-3         |

| Α.                  | CPU Bus Buffering          | 2-4          | P1 Connector Pins2-5       |

|                     | Characteristics at P2A-1   | 2 <b>-</b> 5 | P2 Connector Pins2-6       |

| В.                  | ASCII Character SetB-1     | 2-6          | P3 Connector Pins2-11      |

| C.                  | Service Parts and          | 2-7          | P4 Connector Pins2-12      |

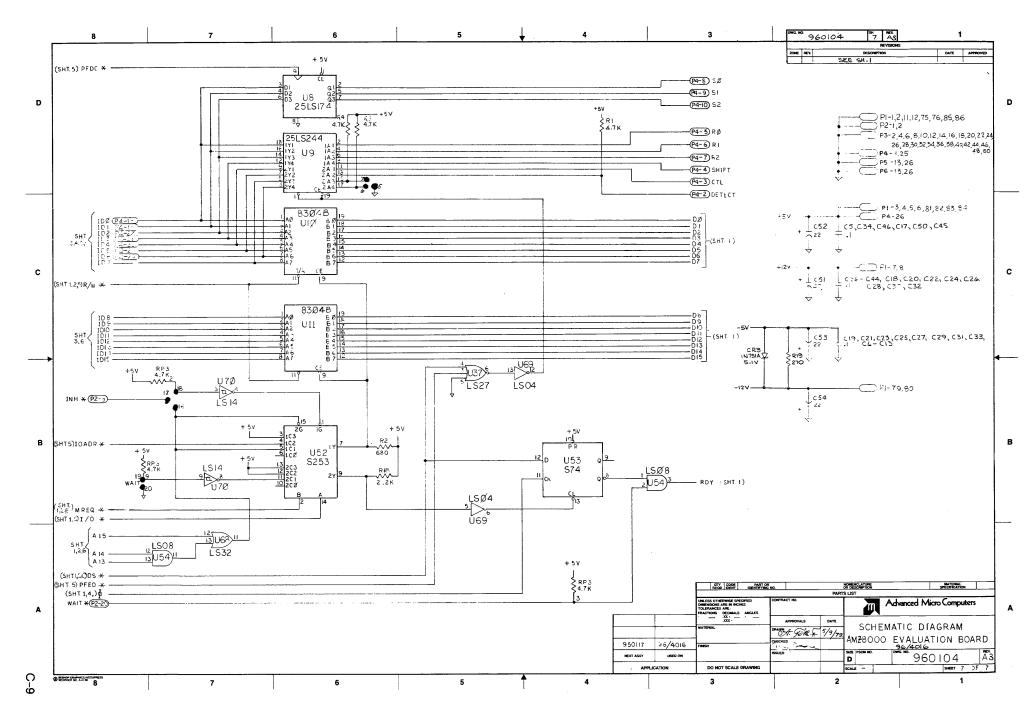

| •                   | Schematics                 | 2-8          | P5 Connector Pins2-12      |

|                     |                            | 2-9          | P6 Connector Pins2-13      |

|                     |                            | 3-1          | Monitor Command Summary3-4 |

| Figu                | ires                       | 3-2          | Monitor I/O Control        |

| ' '9'               |                            | <b>-</b>     | Block3-9                   |

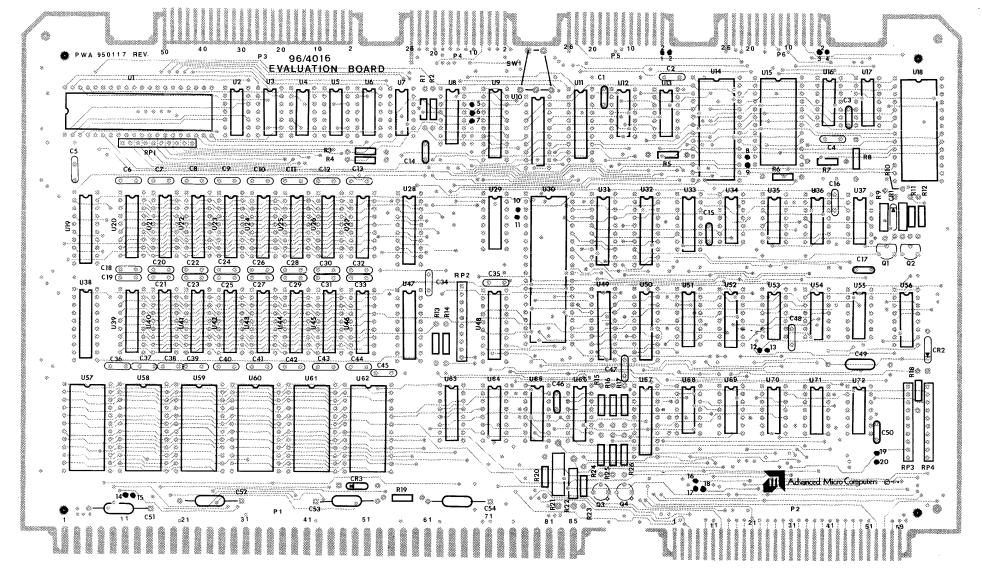

| 1-1                 | Board Layout1-2            | 4-1          | Peripheral                 |

| 1-2                 | Block Diagram1-5           |              | Addresses4-6/4-7           |

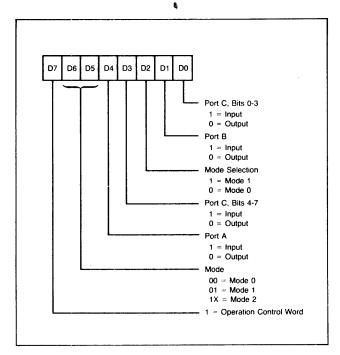

| 1-3                 | Standard Configurations1-6 | 5-1          | Am8255A Operation          |

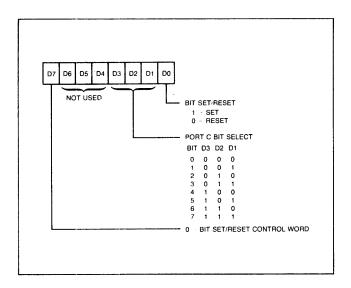

| 1-4                 | Memory-Addressing          | _            | Control Word Format5-2     |

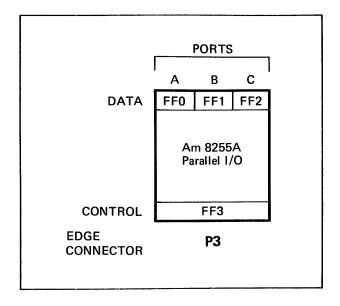

| _ '                 | Potential1-8               | 5-2          | Am8255A Bit Set/Reset      |

| 2-1                 | Edge Connectors and IC     |              | Control Word Format5-2     |

| <u></u>             | Sockets2-2                 | 5-3          | Am8255A Address5-4         |

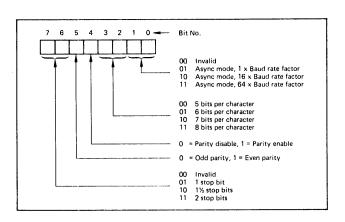

| 2-2                 | Connecting to the          | 5-4          | Am9551 Asynchronous        |

| <i>L</i> – <i>L</i> | Amsys 8/82-7               | •            | Mode Control Code5-4       |

| 2-3                 | Connecting to Keyboard/    | 5-5          | Am9551 Control Command5-5  |

| 2-5                 | Display Console2-8         | 5-6          | Am9551 Synchronous         |

| 2-4                 | Jumper Option2-9           | 0 0          | Mode Control Code5-5       |

| 3-1                 | Memory Address3-2          | 5-7          | Am9551 Addresses5-6        |

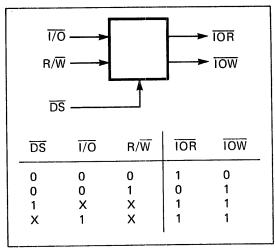

| 4-1                 | IOR* and IOW Decoding4-3   | 5 <b>-</b> 8 | Am9551 Status Register5-6  |

| 4-2                 | Bus Structure4-3           | 5 <b>-</b> 9 | Am8253 Control Byte        |

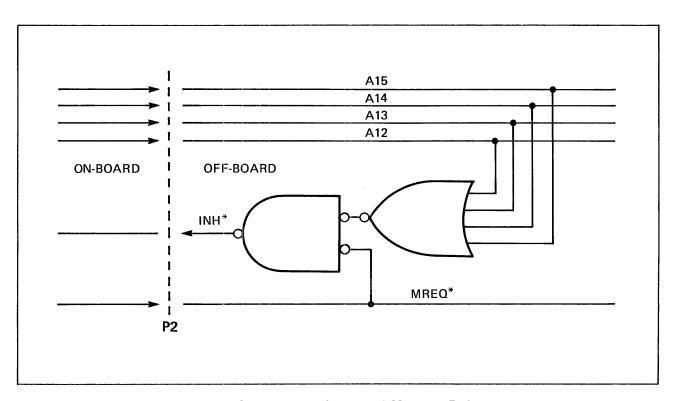

| 4-3                 | Customizing Off-Board      | 3-3          | Format5-9                  |

| 4-5                 | Memory References4-5       | 5-10         | Am8253 Control Byte        |

|                     | Hellory Kererences         | 3.10         | Definition5-9              |

| Tab                 | lac                        | 5-11         | Am8253 Control Byte        |

| ιαυ                 | 103                        | <b>→</b> 11  | to Latch Count5-10         |

| 1_1                 | Specifications             | 5-12         |                            |

# CHAPTER 1 INTRODUCTION

#### 1-1. DESCRIPTION

The Am96/4016 Evaluation Board is a complete single-board microcomputer built around the new 16-bit AmZ8000 microprocessor. Used with a standard CRT or the low-cost keyboard/display console available as an option, it provides an excellent means of testing the advanced capabilities of this remarkably versatile CPU. Used with Advanced Micro Computer's new AmSYS 8/8 Development System, the entire AmZ8000 instruction set can be macroassembled to create very powerful programs for execution on the Evaluation Board.

The fully assembled and tested board has the following features:

#### Standard Features

- AmZ8002 CPU (non-segmented)

- 8 kilobytes of dynamic RAM, expandable off-board

- Up to 12 kilobytes of ROM or E-PROM, expandable off-board

- 4-kilobyte ROM Monitor, with breakpoint, single-step and up/down-load commands

- Buffered CPU bus available at edge of board

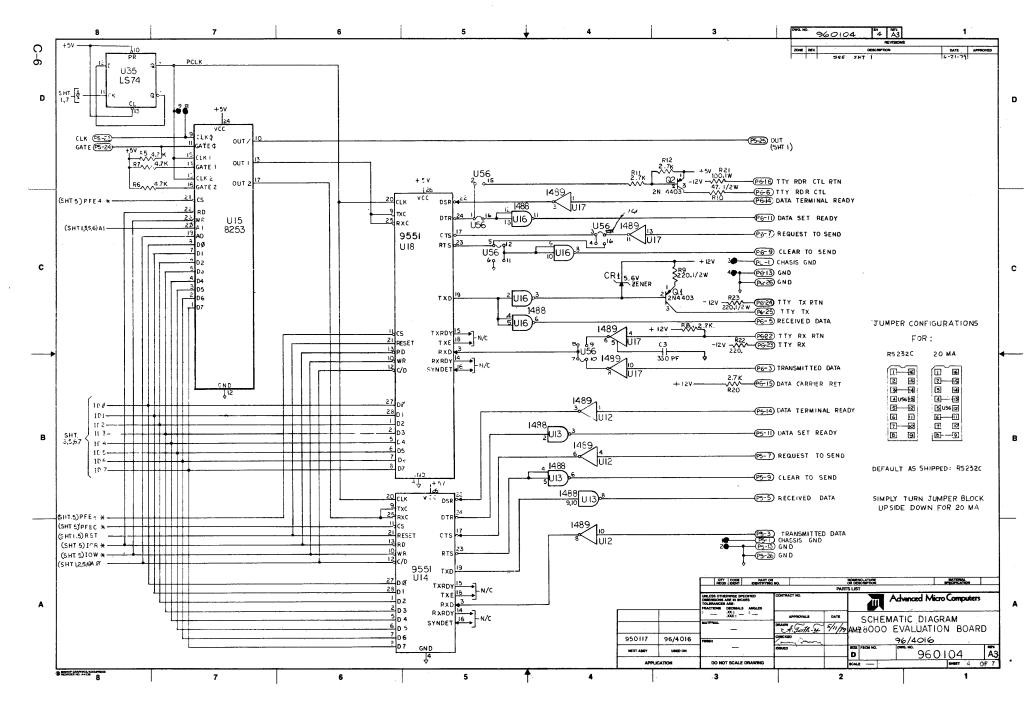

- Two programmable serial I/O ports (RS232C and 20mA)

- A programmable counter/timer channel associated with one serial port

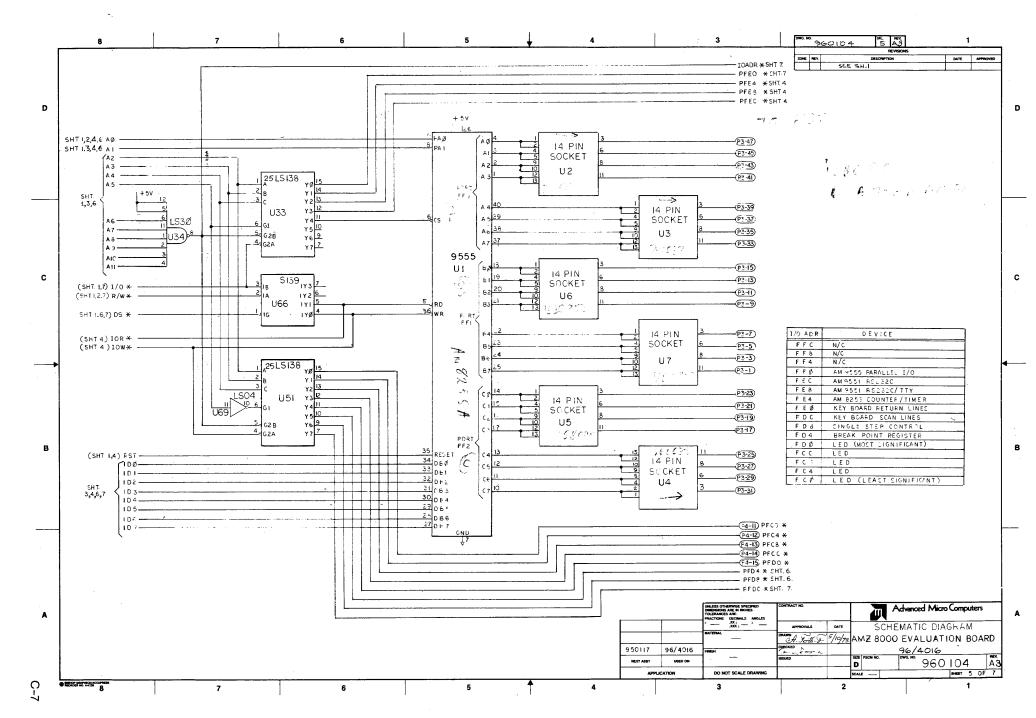

- 24 programmable parallel I/O lines (three 8-bit ports)

- Fits in Multibus<sup>†</sup> or iSBC<sup>†</sup> card cage

<sup>†</sup>Trademarks of Intel Corporation

## Optional Features

- One-pass Assembler in ROM

- Keyboard/Display console

- CRT terminal

- Universal prototyping board

- CPU-bus backplane (2 or 3 slots)

- Six-board card cage

- 64-kilobyte memory expansion

- Complete AmSYS 8/8 Development System, with diskette storage, interface utilities and PASCAL-like macroassembler for the AmZ8000 series

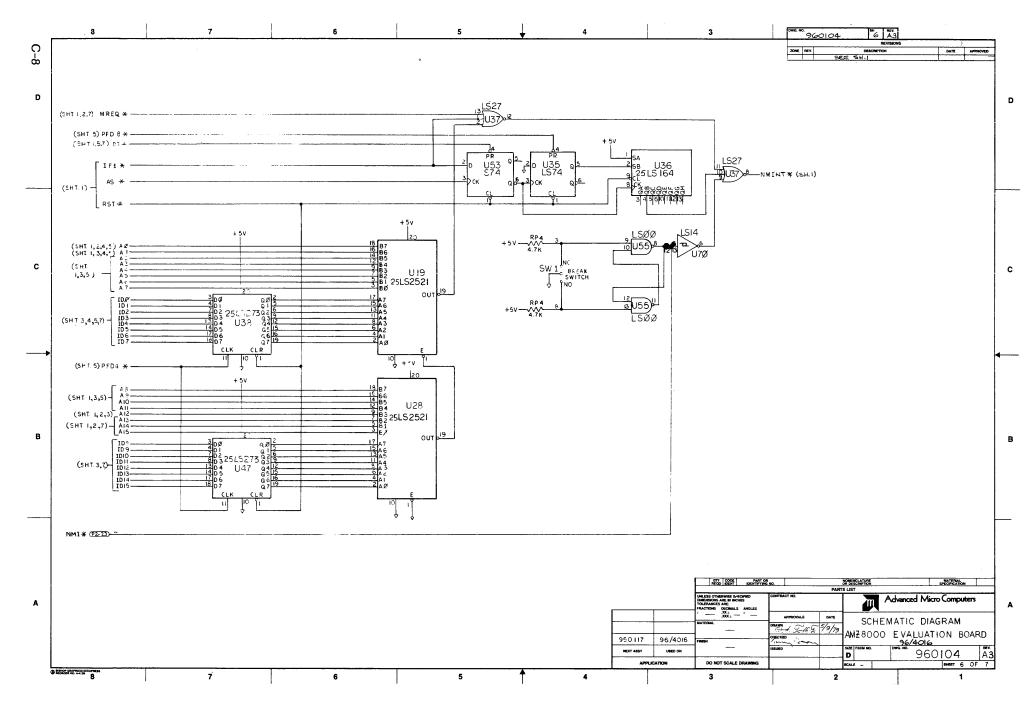

Programs can be entered and executed in either the stand-alone or Development System configuration. Specialized circuits or external expansion boards can also be attached in either mode. The entire CPU bus is buffered and brought to the edge of the board for interconnection, as are extra I/O ports for serial and parallel transfers on the data bus.

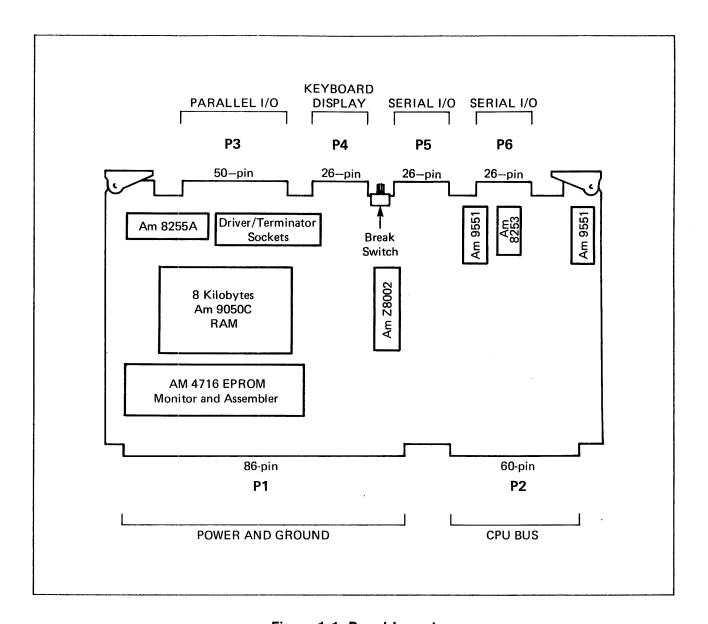

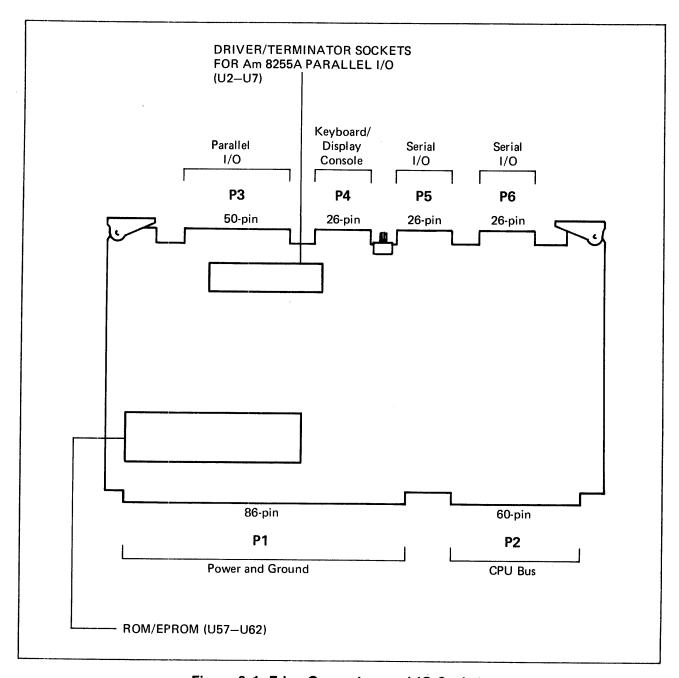

Figure 1-1 illustrates the board layout. The lower two edge connectors are physically compatible with the Multibus standard, although the P1 edge connector uses only power and ground in the standard Multibus card cage.

All four top edge connectors on the board are used for I/O. The P3 connector has 24 programmable lines divided into three 8-bit ports for data and handshaking. The P4 connector is also parallel but designed specifically for the optional keyboard/display console that can be attached to the Evaluation Board. The P5 and P6 connectors both carry programmable lines for asynchronous or synchronous serial data. The P5 connector also carries control I/O for an on-board programmable counter/timer channel.

Figure 1-1. Board Layout

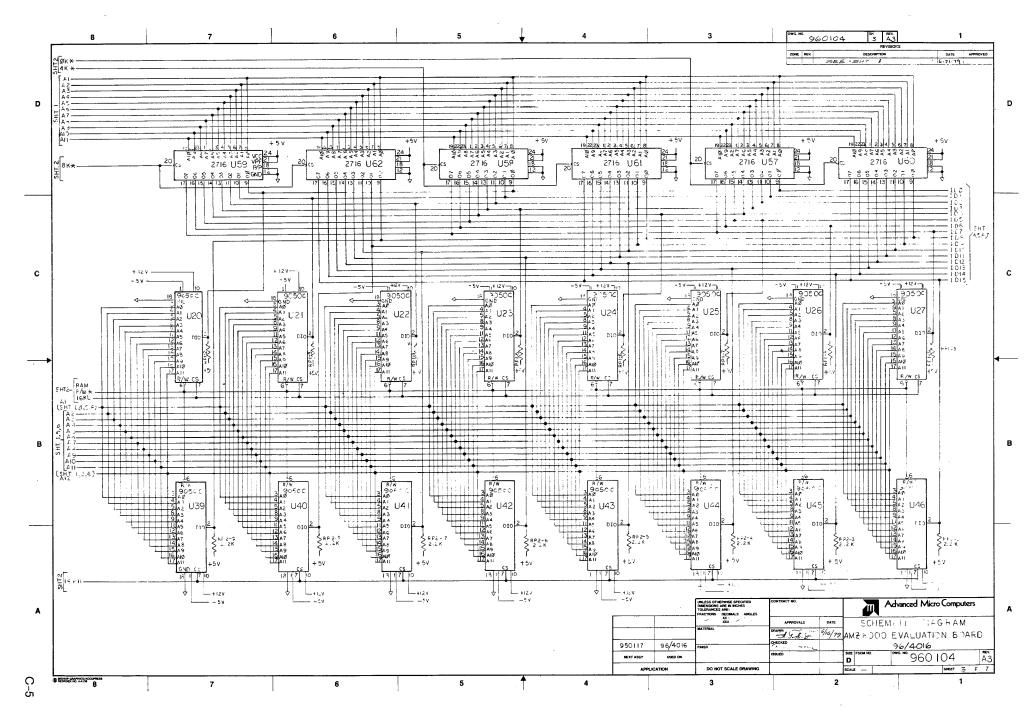

The AmZ8002 CPU is in the center of the board. At the upper right are the two Am9551 USARTs for serial I/O, surrounding the Am8253 counter/timer circuit which clocks them. The Am8255A parallel I/O circuit is in the upper left, next to six sockets for driver/terminators on the parallel port lines. Sixteen Am9050C dynamic RAM circuits provide the 8 kilobytes of user memory. The Monitor and optional Assembler programs are contained in six Am4716 E-PROMs.

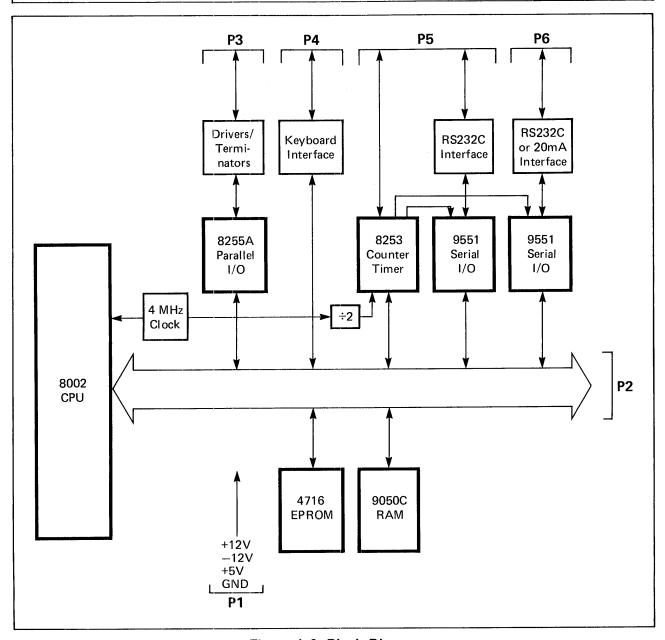

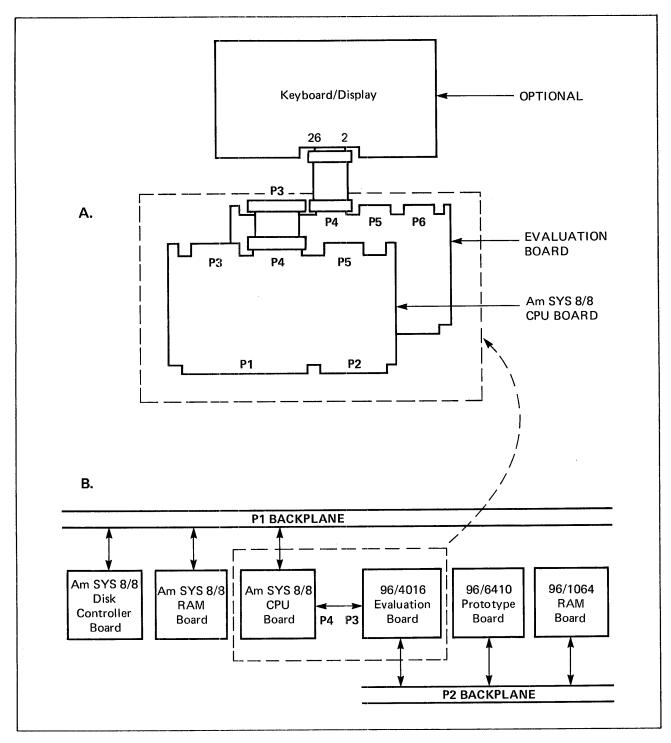

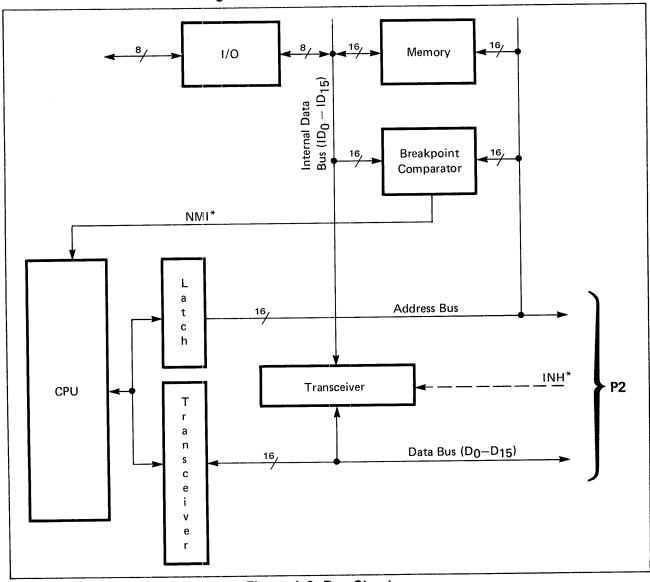

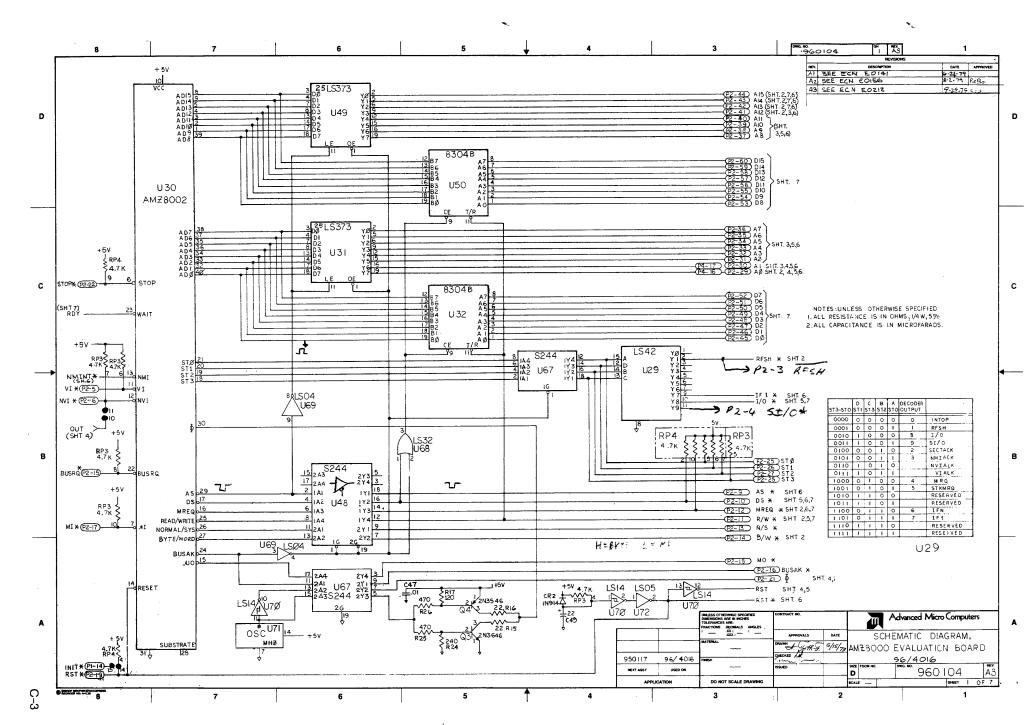

Figure 1-2 shows a block diagram of the board. The system buses (address, data and control) emerge from the CPU and service all circuits, terminating at the P2. The address and data buses, which are multiplexed in the CPU, are separated into two separate 16-bit buses on the board. The diagram shows more clearly the difference between the P5 and P6 serial I/O ports; one has a counter/timer channel available and the other can be changed from RS232C to 20mA current-loop (TTY) interfacing.

Memory-expansion boards and prototyping boards carrying any AmZ8002-compatible circuits (such as DMAs or even multiple CPUs) can be attached at P2. Specialized circuits can also be attached at P3, P5 and P6. P5 is particularly useful for event-counting process control circuits or foreign host computers.

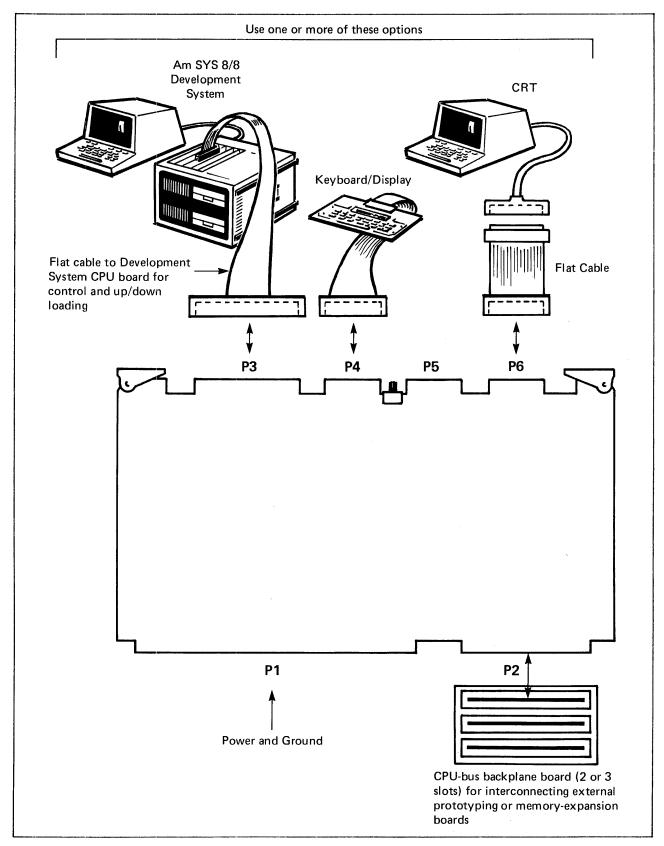

Figure 1-3 illustrates the range of standard plug-in configurations supported by the board's Monitor program. If attachments to the board are limited to any one or more of these three choices, application programming and execution can begin immediately without having to program the I/O circuits.

When the AmSYS 8/8 is attached for up/down loading of programs, the Development System's console can communicate with the Evaluation Board to control all functions.

The Development System contains a comprehensive set of hardware and software resources to fully utilize AmZ8000 capabilities. The system includes dual diskette drives, 64K bytes of RAM, serial and parallel ports, and a multi-Existing programming supmaster bus. port includes a CPM-compatible operating system with linking loader, editor and debugger and a PASCAL-like macroassembler, 8080 AmZ8000 assembler and AmZ8000 translator. High-level languages, including PASCAL, are available. See the AmSYS 8/8 brochure for more details.

Table 1-1 gives a summary list of specifications for the Evaluation Board

#### 1-2. THE CPU

The AmZ8002 microprocessor is a register-oriented CPU with exceedingly well organized minicomputer-like architecture. Sixteen general-purpose registers, each of them two-bytes (one 16-bit word) wide, are available to the user. Over 100 instructions, and 400 combinations of instructions, can be used to manipulate data between the CPU registers, memory and I/O.

The CPU can operate in two modes—system and normal—with separate relocatable stacks for each mode. This allows a distinction between privileged and protected instructions, as well as great flexibility in allocating the system's use of memory. In either mode, ten status conditions are continuously reported:

- 1. Internal operation

- 2. Instruction fetch, first word

- 3. Instruction fetch, subsequent word

- 4. Memory request, data

- 5. Memory request, stack

- 6. Memory refresh cycle

- 7. I/O cycle

- 8. Interrupt acknowledge, non-maskable

- 9. Interrupt acknowledge, non-vectored

- 10. Interrupt acknowledge, vectored

# **TABLE 1-1. SPECIFICATIONS**

| <br>                        |                                                                                                                                                                                                                                                                                                                    |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                         | AmZ8002 (non-segmented)                                                                                                                                                                                                                                                                                            |

| Time Base                   | 4MHz crystal oscillator                                                                                                                                                                                                                                                                                            |

| Serial I/O                  | Two RS232C serial ports with software-programmable baud rates. One port jumper-selectable for 20mA current-loop (TTY) operation.                                                                                                                                                                                   |

| Parallel I/O                | 24 parallel I/O lines (three 8-bit ports). Also provides interconnection to AmSYS 8/8 Development System.                                                                                                                                                                                                          |

| RAM Memory                  | 8K bytes of on-board dynamic memory; CPU refreshed (transparent).                                                                                                                                                                                                                                                  |

| ROM Space                   | 12K bytes of ROM/EPROM space provided in six sockets; ROM monitor occupies two sockets.                                                                                                                                                                                                                            |

| Counter/Timer               | Three 16-bit programmable interval counter; two counters used for serial I/O baud rate control; third counter available to user.                                                                                                                                                                                   |

| Power                       | -12VDC @ .085A, +12VDC @ .06A, +5VDC @ 1.65A (without optional keyboard/display console), or +5VDC @ 2.0A (with optional keyboard/display console).                                                                                                                                                                |

| Dimensions                  | 12.0" (305 mm) x 6.75" (172 mm); MULTIBUS form factor with six edge connectors (P1 through P6).                                                                                                                                                                                                                    |

| Memory<br>Addressing        | ROM space: 0-2FFF(H) RAM space: 4000-5FFF(H)                                                                                                                                                                                                                                                                       |

| Environmental<br>Conditions | O to 55°C ambient in free-air space with relative humidity to 90% without condensation.                                                                                                                                                                                                                            |

| Edge-of-Card<br>Connectors  | P1: 86-Pin for power, ground, and initialize. P2: 60-Pin CPU bus P3: 50-Pin parallel I/O for up/down-load from AmSYS 8/8 Development System. P4: 26-Pin interface for optional keyboard/display board. P5: 26-Pin RS232 and counter/timer interface. P6: 26-Pin RS232 or 20mA current loop for CRT or TTY console. |

| <br>Monitor                 | 4K ROM monitor included at addresses 0-OFFF(H)                                                                                                                                                                                                                                                                     |

Assembler

Optional ASCII, one-pass, line assembler in ROM

Up/Down-Load

Capability

Can be plugged into AmSYS 8/8 Development System to provide up-load and down-load capability. Can also by used with other computer systems to execute AmZ8000 code.

Optional

Keyboard/

Display

Same physical form as Am96/4016

Evaluation Board with attaching standoff connectors and interconnection ribbon cable.

Figure 1-2. Block Diagram

Figure 1-3. Standard Configurations

Only three of these status outputs (2, 6 and 7) are needed by the Evaluation Board's internal functions, but all are available at the P2 edge connector.

The interrupt and trap structure is particularly powerful, with very fast response to external devices and illegal conditions.

Special instructions and hardware features support multiprogramming and multiprocessing. In an asynchronous chain of CPUs, critical resources can be shared without sacrificing throughput.

#### 1-3. MEMORY

The Evaluation Board's dynamic RAM is refreshed by the CPU. Additional memory, either dynamic or static, can be added off-board through the P2 edge connector. AMC will supply a 64-kilo-byte memory-expansion board for this purpose which has self-contained refreshing. There is a provision for substituting off-board memory during accesses to the on-board memory's address space.

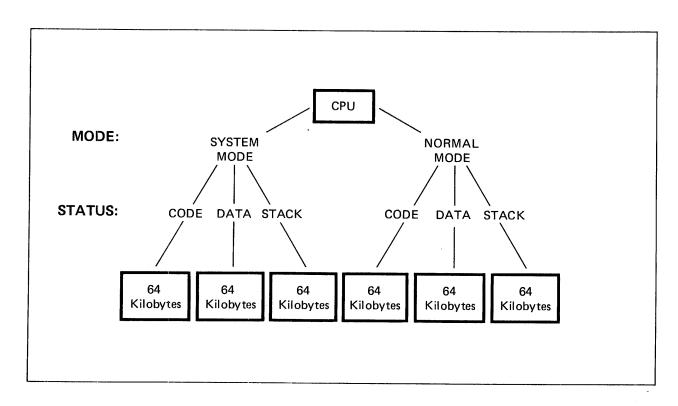

Depending on your use of CPU functions, a very large amount of memory can be used. The CPU's 16 address lines can directly access 64 kilobytes. However, if the various distinctions between operating mode (system and normal) and memory-access status (instruction, data and stack) are used to differentiate memory resources, up to 384 kilobytes can be addressed as illustrated in figure 1-4.

### 1-4. INPUT/OUTPUT

Memory space and I/O space are differentiated by a memory-request line and other status outputs from the CPU. The CPU can use 16-bit I/O port addresses, allowing up to 64K ports, although in the Evaluation board implementation the upper four address bits are not decoded

and often the lower one or two address bits are used for sub-addressing within peripheral circuits.

The Evaluation Board also implements only 8-bit I/O transfers on the four top edge connectors (P3 through P6). These are the lower 8 bits on the data bus.

The 24 parallel I/O lines of the Am8255A circuit at P3 can be configured to transfer data in a variety of ways, with or without handshaking. standard configuration, this edge connector is used for up/down loading between the AmSYS 8/8 Development System and the Evaluation Board. The circuit has a bit set/reset function that increases the efficiency of handshake software. The sockets provided for driver or terminator circuits allow further characterization of these ports for special applications. Ground lines are interleaved with signal lines for better noise immunity at this edge connector.

The two Am9551 USART (universal synchronous/asynchronous receiver/transmitter) circuits attached to the P5 and P6 edge connectors can be programmed for a broad range of full-duplex, doubly-buffered communication protocols, with many automatic overhead features. The baud rate is controlled by two of the three programmable channels in the Am8253 counter/timer circuit.

As mentioned above, no programming of I/O circuits is necessary when the Evaluation Board is used in one of the standard configurations illustrated in figure 1-3. The Monitor program will initialize these circuits for you.

### 1-5. SOFTWARE

The Evaluation Board's ROM-based Monitor program provides complete systeminitialization functions and over two dozen user commands for access to CPU registers and memory. It features breakpoint, single-step and trace functions, as well as up-load and down-load functions for use with the AmSYS 8/8 Development System. Any AmZ8000 instruction whether privileged (system mode) or protected (normal mode) can be entered in hex format using only the Monitor.

The optional ROM-based mnemonic Assembler simplifies instruction entry. Most of the full AmZ8000 instruction set can be used with this one-pass line-by-line Assembler, which also supports forward symbolic references. It is an excellent tool for gaining a feel of AmZ8000 instructions without the need for a complete macroassembler, which is available on the AmSYS 8/8.

The full CPU instruction set can be used to create very powerful application programs. The 110 basic instructions have permutations around operand addressing modes, plus autoincrement and autodecrement facilities. Code written for the AmZ8002 is source-compatible with the AmZ8001 microprocessor

Most instructions are between one and three 16-bit words in length. Instructions and hardware are available to operate on bits, 4-bit digits (BCD), 8-bit bytes, 16-bit words, 32-bit long words, 64-bit quad words, byte strings and word strings.

String instructions are auto-incrementing or auto-decrementing block transfers. The strings can be up to 64 kilo-bytes in length, the entire directly-addressable memory, and the transfers are interruptible. It is this facility that gives the CPU an intrinsic DMA capability.

Figure 1-4. Memory-Addressing Potential

# CHAPTER 2 HARDWARE INSTALLATION AND INTERFACING

# 2-1. UNPACKING AND INSPECTION

Upon receipt of this equipment, inspect both the equipment and the shipping carton immediately for evidence of damage during transit. If the shipping carton is damaged or water-stained. request the carrier's agent to be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, save the carton and packing material for the agent's inspection. Shipping damages should be reported immediately to the carrier. Do not attempt to service the board yourself as this will void the warranty.

#### NOTE

When one of the standard configurations illustrated in Figure 1-3 has been ordered from AMC, only the following installation connections need be considered:

| Edge<br>Connection | External<br>Connection                                                     |

|--------------------|----------------------------------------------------------------------------|

| Р3                 | AmSYS 8/8 Development System CPU board (P3), as illustrated in figure 2-2. |

| P4                 | Keyboard/LED Display Board (Am96/4016-KBD), as illustrated in figure 2-3.  |

| P6                 | CRT or other RS232C term-inal.                                             |

# 2-2. SYMBOLS

A special symbolism is used in this and subsequent sections to denote active-low signal levels. An asterisk (\*) following a signal name, rather than a bar over the name, means that the signal is active-low (negative-true). For example, WAIT\* is active when its voltage potential is low.

# 2-3. INSTALLATION OVERVIEW

Figure 2-1 illustrates the hardware connectors and sockets that may require setup before the board can be used. These are the six edge connectors, P1 through P6, plus sockets for ROM or E-PROM and the sockets for parallel-I/O driver or terminator circuits. Each of these groups is discussed individually below.

#### 2-4. ROM/E-PROM SOCKETS

The board contains six sockets for fixed-address ROM or E-PROM. A11 boards are shipped with at least two E-PROMs installed, which contain the 4-kilobyte Monitor program. If you ordered the optional line-by-line 8kilobyte Assembler, the remaining four E-PROM sockets will also be filled. Table 2-1 is therefore only advisory and will not require installation of additional ICs unless you intend to alter the use of ROM space or install the Assembler circuits later.

# 2-5. PARALLEL I/O DRIVER/TERMINATORS

When the board is ordered, the driver and terminator circuits listed in table 2-2 are provided.

Figure 2-1. Edge Connectors and IC Sockets

TABLE 2-1. ROM/EPROM ADDRESSES AND SOCKETS

| Program   | Addresses                                                                          | Socket #                 |

|-----------|------------------------------------------------------------------------------------|--------------------------|

| Monitor   | 0 - OFFF (even)<br>0 - OFFF (odd)                                                  | U57<br>U60               |

| Assembler | 1000 - 1FFF (even)<br>1000 - 1FFF (odd)<br>2000 - 2FFF (even)<br>2000 - 2FFF (odd) | U58<br>U61<br>U59<br>U62 |

TABLE 2-2. DRIVER/TERMINATORS FOR PARALLEL PORT

| Device  | Function   | Socket # |

|---------|------------|----------|

| 74LS37  | Driver     | U2       |

| 74LS37  | Driver     | U3       |

| 74LS37  | Driver     | U4       |

| iSBC902 | Terminator | U5       |

| iSBC902 | Terminator | U6       |

| iSBC902 | Terminator | U7       |

TABLE 2-3. OTHER DRIVER/TERMINATOR CIRCUITS FOR P3

| Drivers                                                                                                              | Terminators                                                                                  |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 7438,74LS38<br>7437,74LS37<br>7432,74LS32<br>7426,74LS26<br>7409,74LS09<br>7408,74LS08<br>7403,74LS03<br>7400,74LS00 | Intel iSBC 901<br>Intel iSBC 902<br>National BLC 901<br>National BLC 902<br>National BLC 903 |

Non-standard uses of the P3 edge connector may require different devices for these sockets. Some of the possible devices are listed in table 2-3. Alternatively, the sockets can be jumpered for direct connection to the Am8255A pins.

#### 2-6. EDGE CONNECTORS

A minimum of two edge connectors must be used to operate the board. Power (+12V, -12V, +5V) and ground must be supplied through the P1 connector. A system console must also be connected on one of the remaining connectors: either P4 for the AMC-supplied keyboard/display console or P6 for a user-supplied terminal.

Many additions to these required connections are possible, as indicated in the list of edge-connector characteristics and applications below. This list is normally not needed if you are installing a standard configuration illustrated in figure 1-3.

Note that connectors P1 and P2 have their odd-numbered pins on the component side of the board, whereas the remaining connectors have them on the solder side. The abbreviation N/C in the pin-connection lists means no connection.

P1 - an 86-pin connector physically (but not electrically) compatible to the Multibus and iSBC-80 formats. It is used only for power and ground, except that pin 14 can be used for external initializing (reset) when jumpered for this function (see figure 2-4). The pin connections are shown in table 2-4.

P2 a 60-pin connector physically compatible with the Multibus and iSBC-80 formats. It carries buffered signals from all CPU lines except +5V, which is on the P1 connector, and DE-COUPLE which is not used on the AmZ8002. The address/data bus from the CPU is demultiplexed into separate address and data buses. The CPU's RESET\* line is connected directly to the RST\* line on P2, although RST\* also resets the Am9551 USARTs and the Am8255A PIO. One additional line, INH\* is used to control of addressing on/off-board memory.

This connector is used to interface a prototyping board and/or external memory boards. An optional backplane is available for this purpose.

If the CPU is disabled via the BUSRQ\* input, an off-board device can take control over most of the signals on this connector to access memory and peripherals on the Evaluation Board. The pin connections are shown in table 2-5.

P3 a 50-pin connector to the six driver/terminator sockets of the Am8255A parallel I/O circuit. The 24 active lines are divided into three 8-bit ports (addresses FFO, FF1 and FF2, where the upper four address bits are not decoded). port can be programmed independently for input or output to match the functions of the driver or terminator ICs that insert in sockets through U7.

TABLE 2-4. P1 CONNECTOR PINS

| Component Side                                      | Solder Side                                            |

|-----------------------------------------------------|--------------------------------------------------------|

| 1 GND 3 +5V 5 +5V 7 +12V 9 N/C 11 GND 13 N/C 15 N/C | 2 GND 4 +5V 6 +5V 8 +12V 10 N/C 12 GND 14 INIT* 16 N/C |

TABLE 2-5. P2 CONNECTOR PINS

| Component Side                                                                                | Solder Side                                                                                 |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1 GND 3 N/C 5 VI* 7 N/C 9 AS* 11 R/W* 13 N/S* 15 BUSRQ* 17 MI* 19 RST* 21 PHI (clock) 23 NMI* | 2 GND 4 N/C 6 NVI* 8 INH* 10 DS* 12 MREQ* 14 B/W* 16 BUSAK* 18 MO* 20 WAIT* 22 STOP* 24 N/C |

| 25 ST0                                                                                        | 26 ST1                                                                                      |

| 27 ST2                                                                                        | 28 ST3                                                                                      |

| 29 A0                                                                                         | 30 A1                                                                                       |

| 31 A2                                                                                         | 32 A3                                                                                       |

| 33 A4                                                                                         | 34 A5                                                                                       |

| 35 A6                                                                                         | 36 A7                                                                                       |

| 37 A8                                                                                         | 38 A9                                                                                       |

| 39 A10                                                                                        | 40 A11                                                                                      |

| 41 A12                                                                                        | 42 A13                                                                                      |

| 43 A14                                                                                        | 44 A15                                                                                      |

| 45 D0                                                                                         | 46 D1                                                                                       |

| 47 D2                                                                                         | 48 D3                                                                                       |

| 49 D4                                                                                         | 50 D5                                                                                       |

| 51 D6                                                                                         | 52 D7                                                                                       |

| 53 D8                                                                                         | 54 D9                                                                                       |

| 55 D10                                                                                        | 56 D11                                                                                      |

| 57 D12                                                                                        | 58 D13                                                                                      |

| 59 D14                                                                                        | 60 D15                                                                                      |

Figure 2-2. Connecting to the AmSYS 8/8

Figure 2-3. Connecting the Keyboard/Display Console

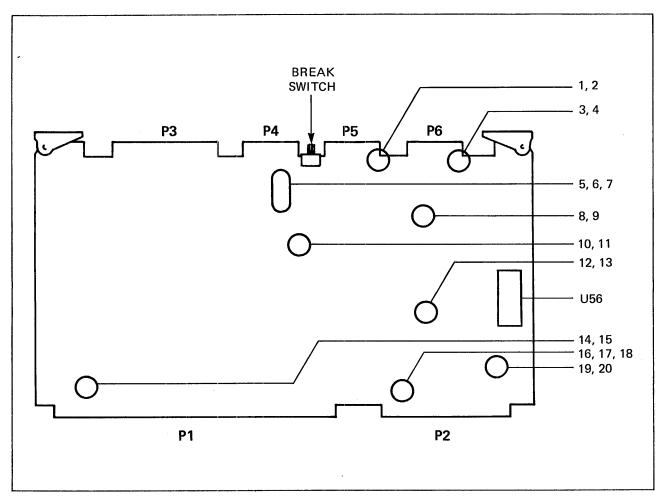

Figure 2-4. Jumper Option

When the AmSYS 8/8 Development System is used, P3 of the Evaluation Board is connected to P4 of the Development System's CPU board (Am95/4005) for up/down loading and control from the Development System's console. This is illustrated in figure 2-2b.

The pin connections are shown in table 2-6. See the Am8255A Data Sheet for more details.

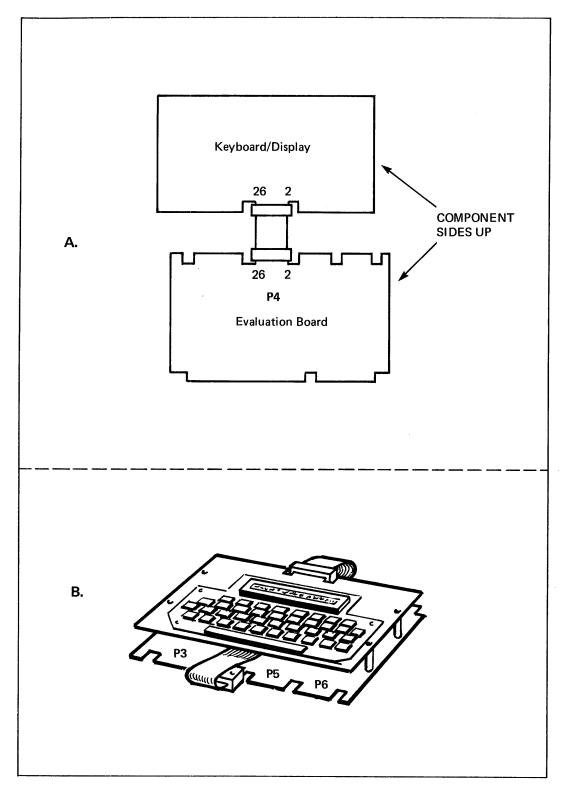

P4 - 26-pin connector used to attach the optional keyboard/display console (Am96/4016-KBD), or for general-purpose parallel I/O.

The cable-connection method for the keyboard/display console is illustrated in figure 2-3.

The pin connections listed in table 2-7 include keyboard return and scan lines (RO-R2, SO-S2) and port addresses for LED characters (Ports FCO through FDO).

P5 - 26-pin connector to the RS232C interface of one of the two Am9551 serial I/O circuits, plus three pins connected to channel O of the Am8253 counter/timer circuit.

This connector can be used for time-controlled serial I/O (e.g., process controllers), a host computer other than the AmSYS 8/8 Development System, or any other RS232C serial device.

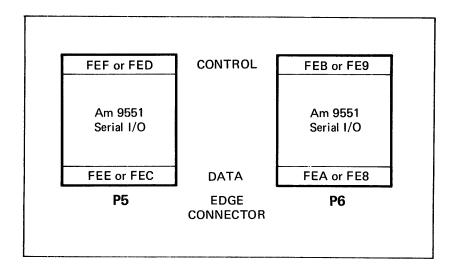

The I/O port address for data through this connector is FEF or FED (they are equivalent).

The pin connections are given in table 2-8. Parenthesized numbers are the corresponding EIA pin numbers for RS232C. See the Am9551 and Am8253 Data Sheets for more details.

P6 - 26-pin connector to the RS232C or 20mA current-loop (TTY) interface of one of the two Am9551 serial I/O circuits.

The RS232C interface is factory-set. To obtain a 20mA current-loop interface, turn the jumper at U56 180 degrees (see figure 2-4), and reprogram for baud rate.

This connector can be used for a system console (terminal) or any other serial I/O device. When using an RS232 type CRT Terminal, it is usually necessary to connect the Clear To Send signal to the Request To Send signal. This connection can sometimes be made on the CRT Terminal. Alternatively, the Clear To Send line can be grounded on the Evaluation board by removing the jumper between U56 pins 3 and 14 and connecting an insulated jumper between U56 pins 3 and 6.

The I/O port address for data through this connector is FEB or FE9 (they are equivalent).

The pin connections are given in table 2-9. Parenthesized numbers are the corresponding EIA pin numbers for RS232C. See the Am9551 Data Sheet for more details.

TABLE 2-6. P3 CONNECTOR PINS

| Solder Side                                                                             | Component Side                                                               |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1 PB7 (Port FF1) 3 PB6 5 PB5 7 PB4 9 PB3 11 PB2 13 PB1 15 PB0                           | 2 GND 4 GND 6 GND 8 GND 10 GND 12 GND 14 GND 16 GND                          |

| 17 PC3 (Port FF2)<br>19 PC2<br>21 PC1<br>23 PC0<br>25 PC4<br>27 PC5<br>29 PC6<br>31 PC7 | 18 GND 20 GND 22 GND 24 GND 26 GND 28 GND 30 GND 32 GND                      |

| 33 PA7 (Port FF0)<br>35 PA6<br>37 PA5<br>39 PA4<br>41 PA3<br>43 PA2<br>45 PA1<br>47 PA0 | 34 GND<br>36 GND<br>38 GND<br>40 GND<br>42 GND<br>44 GND<br>46 GND<br>48 GND |

| 49 N/C                                                                                  | 50 GND                                                                       |

**TABLE 2-7. P4 CONNECTOR PINS**

| Solder Side                                                  | Component Side                                             |

|--------------------------------------------------------------|------------------------------------------------------------|

| 1 GND                                                        | 2 KEYBOARD DETECT                                          |

| 3 CTL                                                        | 4 SHIFT                                                    |

| 5 R0                                                         | 6 R1                                                       |

| 7 R2                                                         | 8 S0                                                       |

| 9 S1                                                         | 10 S2                                                      |

| 11 PFCO* 13 PFC8* 15 PFDO* 17 A1 19 ID1 21 ID3 23 ID5 25 GND | 12 PFC4* 14 PFCC* 16 A0 18 ID0 20 ID2 22 ID4 24 ID6 26 +5V |

TABLE 2-8. P5 CONNECTOR PINS

|                                                                       | Solder Side                                                                                                                  | (RS232)                                | Component Side (RS232)                                                                                                                             |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23<br>25 | CHASSIS GND TRANSMITTED DATA RECEIVED DATA REQUEST TO SEND CLEAR TO SEND DATA SET READY SIGNAL GND N/C N/C N/C N/C CLKO OUTO | (2)<br>(3)<br>(4)<br>(5)<br>(6)<br>(7) | 2 N/C<br>4 N/C<br>6 N/C<br>8 N/C<br>10 N/C<br>12 N/C<br>14 DATA TERM RDY (20)<br>16 N/C<br>18 N/C<br>20 N/C<br>22 N/C<br>24 GATEO<br>26 SIGNAL GND |

TABLE 2-9. P6 CONNECTOR PINS

|                                                   | Solder Side                                                                                                   | (RS232)                                              | Component Side                                                                                                                                   | (RS232)                      |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 10 28 k 3 5 7 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 | RECEIVED DATA REQUEST TO SEND CLEAR TO SEND DATA SET READY SIGNAL GND DATA CARRIER RTN N/C N/C N/C N/C TTY RX | (1)<br>(2)<br>(3)<br>(4)<br>(5)<br>(6)<br>(7)<br>(8) | 2 N/C 4 N/C 6 TTY RDR CONTROL 8 N/C 10 N/C 12 N/C 14 DATA TERM RDY 16 TTY RDR CONTROL RTN 18 N/C 20 N/C 22 TTY RX TRN 24 TTY TX RN 26 SIGNAL GND | (20)<br>(21)<br>(24)<br>(25) |

# 2-7. KEYBOARD/DISPLAY INSTALLATION

When using the optional keyboard/display console, the following installation method should be used.

Orient the Evaluation Board and the keyboard/display board so that their component sides are facing up and the P4 connector of the Evaluation Board faces the only edge connector of the keyboard/display board. Place the flat cable between the two connectors so that the even pins of the Evaluation Board connect to the even pins of the keyboard/display board, as shown in Fold the cable between figure 2-3a. the boards so that the board spacers lock into the holes on the boards, as shown in figure 2-3b. Both boards will then have their component sides facing down.

# 2-8. PROTOTYPING AND MEMORY-EXPANSION BOARDS

Prototyping and memory-expansion boards can be connected to the CPU bus via P2. AMC offers the following optional products to accommodate these functions:

- Universal Prototyping Board for Multibus (Am96/9410)

- 64-kilobyte dynamic RAM board for standard Multibus and Evaluation Board (Am96/1064).

- Two- and three-board backplane for P2 edge connector (Am96/4016-2S and Am96/4016-3S)

- Six-board Multibus-compatible card cage with cooling fan (Am95/6440).

A card cage with power supplies is also available (Am95/6448)

Prototyping boards can contain any type of circuitry, including circuits that capture the system buses. The AmZ8002 bus is described further in the section entitled Principles of Operations.

Expansion memory can be of any type compatible with the available pins and the buffered electrical characteristics at P2 (see appendix A). Dynamic-memory refresh may be done on the external board or it may use the CPU refresh cycle, as does the on-board RAM.

The 64K RAM board supplied by AMC is compatible with both the Evaluation Board (through P2) and with standard Multibus slave applications (through P1). In either configuration, only one of the two Multibus edge connectors is enabled. Due to this dual use, dynamic refresh is handled on the memory board itself rather than relying on the AmZ8002. The P2 connector of the memory board supports 16 address bits whereas its P1 connector supports 20 bits.

#### 2-9. AmSYS 8/8 INTERCONNECTION

When an AmSYS 8/8 Development System is used, P3 of the Evaluation Board is connected to P4 of the Development System's CPU board as illustrated in figure 2-2. A cable (Am96/4016-PCBL) for connecting P3 to P4 is available from AMC. Alternatively, a cable can be fabricated by using two Scotchflex card edge connectors (3M part #3415-0001) and one foot of Scotchflex flat cable (3M part #3306/50).

A diskette-based program named HOST is supplied with the Development System for communication between the Development System and the Evaluation Board. Execution of this utility on the Development System allows Evaluation Board operations to be controlled through the Development-system console. However, if the Am96/4016-KBD keyboard/display console is attached, it takes priority over all other consoles as the monitor console.

The Development System can be used for programming work simultaneously with execution of programs on the Evaluation Board. The P1 but serves the AmSYS 8/8 while the P2 bus serves the Evaluation Board. In this case, separate consoles may be needed. However, communication or transfers between the Evaluation Board and the Development System require the HOST program to be in execution.

# 2-10. JUMPER OPTIONS

Several jumpers, illustrated in figure 2-4, can be connected to modify the standard functions of the Evaluation Board. There is a Break switch for regaining CPU control, two jumpers for grounding external I/O devices to the board, one for timing an external device, one for selecting RS232C or TTY serial interface, one for enabling an initialization line, one for enabling an inhibit line, and one for disabling the memory-cycle Wait state.

All jumpers are unconnected when the board is shipped; the jumpers (12, 13) associated with the Break switch are connected, but the Break switch itself is normally open. Wire-wrapping between the jumper posts will affect the board's functions as described below.

BREAK SWITCH - When pressed, it asynchronously generates a non-maskable interrupt (NMI\*) to the CPU, which forces control back to the Monitor program. This circuit is connected via a trace between jumpers 12 and 13. If the NMI\* line on P2 is to be used, the Break switch must be disabled by cutting the trace connecting jumpers 12 and 13. The wire-wrap pins at 12 and 13 can be used to reconnect the Break switch at a later time.

Jumper 1,2 - When jumpered, it connects the chassis ground of the external serial I/O device at P5 to the Evaluation-Board ground.

Jumper 3,4 - When jumpered, it connects the chassis ground of the external serial I/O device at P6 to the Evaluation-Board ground.

Jumper 5,6,7 - Used by the Monitor to determine baud rate at P6 as follows:

9600 baud - all open 2400 baud - connect 6 to 5 300 baud - connect 7 to 5 110 baud - connect 6 to 5 and 7 to 5

Jumper 8,9 - When jumpered, it connects the 2MHz clock (4MHz + 2) to counter 0 of the Am8253 counter/timer circuit, which is available externally through P5.

Jumper 10,11 - When jumpered, it connects the OUTØ output of the Am8253 at P5 to the NVI\* line, thereby generating periodic nonvectored interrupts.

Jumper 12,13 - These jumpers are factory-connected by a trace to enable the Break switch. If NMI\* is used at P2, the trace must be cut. The jumpers can be reconnected later by wire wrapping.

Jumper U56 - Unplugging and rotating this jumper 180 degrees changes the P6 interface from RS232C to 20mA current loop (TTY). The Am9551 must be reprogrammed for baud rate if 20mA is used.

Jumper 14,15 - When jumpered, it enables pin 14 on the P1 Multibus connector to be an INIT\* input. When the INIT\* line is low, it resets the CPU, USARTs and parallel I/O circuit.

INSTALLED

FLL OUT Jumper 16,17,18 - When jumpered 16-to-17, the INH\* line on the P2 connector becomes an active-low output , whenever on-board memory space (0000-5FFF) is addressed, thereby disabling off-board memory. When jumpered 17-to-18, the INH\* line becomes an input for all memory ac-

cesses, thereby disabling on-board

memory when the line is low.

Jumper 19,20 - When jumpered, it disables the Wait cycle normally inserted between the T2 and T3 cycles of on-board memory cycles.

IN 29% FASTER.

# CHAPTER 3 OPERATION WITH THE MONITOR

### 3-1. OVERVIEW OF OPERATIONS

When the Evaluation Board is powered up, the ROM-based Monitor program initailizes the standard board configurations illustrated in figure 1-3. It then displays an asterisk (\*) prompt.

Immediately thereafter, any Monitor command described in the following pages can be entered, including the commands that invoke the Assembler or up/down-loads from the AmSYS 8/8 Development System.

The Monitor will communicate with any console in the standard configuration (figure 1-3), although precedence is always given to the keyboard/display console attached at the P4 edge connector whenever it is present. If the AmSYS 8/8 Development System is attached to P3, the Monitor will also communicate with its console if the HOST program is running on the Develop-When the keyboard/ disment System. play console at P4 plus the Development System at P3 are attached, inputs may be received from both but outputs from the board will go only to the keyboard/display console. With consoles only at P3 and P6 (nothing at P4), the first one to communicate with the Evaluation Board becomes the system console and receives output.

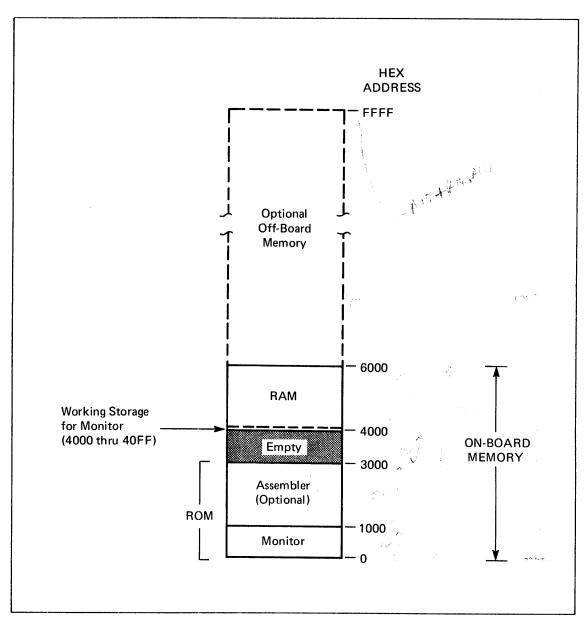

The on-board memory space accessible to the Monitor includes hex addresses 0 through 5FFF, as indicated in figure 3-1. Both the Monitor and the optional Assembler also use up to 100 hex bytes each of RAM starting with address 4000 for the system stack and working storage at various times.

If the P3, P4 and P6 edge connectors are used for non-standard I/O (i.e., any way other than that illustrated in figure 1-3), or if the P5 connector is used, the I/O circuits controlling these connectors must be reprogrammed after initialization by the Monitor. The Peripheral Programming chapter discusses the methods for doing this.

Since the line-by-line Assembler is an option with the Evaluation Board, a description of it is given in a separate manual entitled Am96/4016-ASM Assembler User's Manual.

# 3-2. MONITOR FUNCTIONS AND USER CONTROLS

The Monitor allows you to perform the following functions:

Examine, fill or substitute memory locations

Examine or fill CPU registers

Execute a program starting at any location

Single-step through a program

Specify breakpoints

Call the line-by-line Asssembler

Initiate and manage up/down loading from the AmSYS 8/8 Development System

There are two sets of operating modes for the Monitor:

Normal/System Modes - These modes differentiate between the abilities to execute protected and privileged AmZ8000 instructions, respectively. The Monitor always comes up in Normal Mode; any hex or Assembler instructions can be entered, but

Figure 3-1. Memory Address

only protected instructions are executed. The SM command drops you into System Mode. These modes correspond to the CPU's distinction between Normal and System modes.

Command/Program Modes - These modes differentiate occasions when you are directly interfacing with the Monitor versus interfacing with the Assembler or an application program. In Program Mode, the Monitor acts as a slave to the other program being executed and services that program's needs. The G or ASM commands, which execute programs, exemplify actions that cause a change from Command Mode to Program Mode. In Program Mode, calls can be made to the Monitor either through the SC instruction or through direct keyboard entry at program input points. Direct keyentry must be preceded by board the ESC (escape) key, and this only works when the Monitor is driving I/O for the application program.

An asterisk (\*) is used for command prompting. However, since the keyboard/display console has only one line of display characters, the prompt does not appear on this console if a line of data is displayed in response to the previous command. When commands are used that require no display in response, the command prompt will appear on the keyboard/display console just as on conventional CRT or printer consoles.

There are two text-editing functions: The last character entered can be deleted with the DEL key on RS232C consoles or the RUBOUT key on Teletype (TTY) consoles. Also, the entire current line of entry can be deleted with the Control X key pair.

If unrecognized commands are entered, the Monitor will respond with a question mark (?).

### 3-3. MONITOR COMMANDS

The Monitor commands are listed according to functional categories in table 3-1. Upper case characters are literal lower-case characters entries. variable entries. The commands are described in detail on the pages that follow, according to the alphabetical order of the command mnemonic; the commands are enclosed in parantheses which should not be entered as All memory adpart of the command. dress and CPU register values (the x,y,z parameters) are hexidecimal. All CPU register numbers, flag values and other m.n parameters are decimal.

In addition to these commands, any AmZ8000 hex-format instructions can be entered through the Monitor, without the Assembler. The Monitor initializes the program counter at hex 1000 and the stack pointer (register R15) at hex 40AE. System calls (the 7F instruction followed by a non-zero reference value) will display the reference value when the program exits to the Monitor.

Blank spaces separating single-character commands and variables are optional.

All addresses are 16 bits long. Memory reference always return words and instructions always begin on word boundries (even addresses).

# 3-4. (ASM) EXECUTE ASSEMBLER

Invokes the line-by-line Assembler, which is assumed to reside in ROM hex addresses 1000 through 2FFF. It will immediately prompt you for input. See the Am96/4016-ASM User's Manual for instructions on how the Assembler is operated.

# TABLE 3-1. MONITOR COMMAND SUMMARY

| Display memory Display and substitute memory Display program counter Display all CPU registers Display word register Display flags | D x,y<br>S x<br>XP<br>X<br>X n<br>XF              |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Fill memory Fill program counter Fill high-byte register Fill low-byte register Fill word register                                 | F x,y,z<br>P=x<br>RHn=x<br>RLn=x<br>Rn=x          |

| Move memory                                                                                                                        | M x,y,z                                           |

| Set carry flag Set decimal-adjust flag Set half-carry flag Set overflow flag Set parity flag Set sign flag Set Zero flag           | C n<br>D n<br>H n<br>V n<br>P n<br>S n<br>Z n     |

| Execution Functions                                                                                                                |                                                   |

| Execute assembler Execute program Enter system mode Enter normal mode Hardware breakpoint Software breakpoint Single-step Trace    | ASM G x SM NM E x B x,y,z (cr) after B or T T m,n |

| Up/Down Loading                                                                                                                    |                                                   |

| Down Load<br>Up Load                                                                                                               | LOAD d:file,x<br>SAVE d:file,x,y                  |

#### 3-5. (B x,y,z) SOFTWARE BREAKPOINT

Sets two or three software breakpoint addresses (x,y and optionally z) and starts execution at the current program counter address. Only the first breakpoint encountered is used; the others are discarded when any one breakpoint is reached.

This command executes to, but not including, instruction x. Unlike the hardware breakpoint command (Ex), this command cannot be used in ROM space.

User code is modified temporarily by inserting a system call at the break-point address, but the code is restored upon break. Thus the breakpoints are cleared everytime and do not stay set.

Output includes the program counter (PC) at break and the first word of the next instruction (NI) to be executed.

You might need to set the program counter (P=x) prior to entering this command.

#### 3-6. (C n) SET CARRY FLAG

Sets or resets the carry (C) flag to n=1 or 0. See the XF command for displaying flags.

#### 3-7. [(cr) after B or T] SINGLE-STEP

After a B (breakpoint) or T (trace) command has been executed, single carriage returns (cr) will execute and display subsequent instructions one at a time. This single-step mode is disabled with any macro-type command such as G, ASM, LOAD or SAVE.

#### 3-8. (D n) SET DECIMAL-ADJUST FLAG

Sets or resets the decimal-adjust (DA) flag to n = 1 or 0. This syntax takes precedence over the Display Memory (D x,y) command. See the XF command for displaying flags.

#### 3-9. (D x,y) DISPLAY MEMORY

Displays the contents of memory at addresses x through y. Up to eight hexidecimal words, plus their ASCII byte equivalents and beginning address are displayed on each line. Bytes with no ASCII equivalent are represented by an underline (this character may vary with your terminal).

The y ending address is optional and if missing is assumed equal to x. The least significant bit of each address x and y is cleared to insure display on word boundries.

Display of locations Ø or 1 can conflict with the Dn command. To avoid this conflict, these addresses can be represented by ØØ and Ø1, respectively. This is not necessary, however, in the case of a range such as DØ.F.

The ASCII equivalents displayed in the right-hand column are useful for identifying alphanumeric data.

#### 3-10. (E x) HARDWARE BREAKPOINT

Sets a hardware breakpoint at address x. It stays set until changed. Setting to zero has the same effect as a clear. Control is returned to Monitor following completion of instruction if the address is encountered during user program execution.

A breakpoint should not be set to the address immediately following a system call because unpredictable results will occur.

#### 3-11. (F x,y,z) FILL MEMORY

The contents of memory words from the x address through the y address are filled with the 16-bit value z. The least significant bit of each address x and y is cleared to insure fill on word boundries (even addresses). If y is missing, it is assumed equal to x.

The new LDPR Monitor command has the form:

3-12. (G:

LDPR d:file.ext

DE

s nored in-

Executes ning at m itted, ex address i command ( a breakpo program e

LDPR reads the binary file named file.ext on drive d from the AmSYS 8/8 and transfers the program to the Evaluation Board memory. The drive, file name and extension (if any) must all be specified. must be a binary file (type .BIN) produced by MACRO8000 or LINK8000 on Amsys 8/8.

/erflow command w Flag

You might ter (P=x)

The binary file includes destination addresses for the Also, a transfer address (main entry point) is automatically used to set the AmZ8000 program counter Therefore, the user can start the program simply with G, rather than G followed by an address.

nd for

3-13. (H

Sets or r\_ rrag to n = 1 or 0. See the XF command for displaying flags.

# 3-14. (LOAD diffle,x) DOWN LOAD

Reads the object program named "file" drive "d" from the AmSYS 8/8 Development System into the Evaluation Board memory beginning at memory address x. The "file" name must be in the AmSYS 8/8 format with the disk drive specified. The HOST program must be running on the Development System. \_\_ I ( WIA MOST)

If this command is entered from the Development System, a prompt, consisting of the currently logged-in diskette identifier in parentheses, will appear on your console. (d)

See the next section entitled AmSYS 8/8 Up/Down Loading if you are assembling programs on the Development System.

#### 3-15. (M x,y,z) MOVE MEMORY

Moves the contents of memory from address x through address y to addresses z through z+(y-x). Memory is moved as Therefore, the least 16-bit words. significant bit of addresses x and z are cleared to ensure a memory move on word boundries (even addresses). Also, when address y is an even address, addresses x through y+1 are moved to addresses z through z+(y-x+1).

#### 3-18. (P = X) FILL PROGRAM COUNTER

Fills the program counter with the address x. The counter can be displayed with the XF command.

#### 3-19. (RHn = x) FILL HIGH-BYTE REGISTER

Fills the high-byte register n (where n = 0 to 7) with the 8-bit hex value x. The register can be displayed with the Xn command.

#### 3-20. (RLn = x) FILL LOW-BYTE REGISTER

Fills the low-byte register n (where n = 0 to 7) with the 8-bit hex value x. The register can be displayed with the Xn command.

#### 3-21. (Rn = x) FILL WORD REGISTER

Fills the general-purpose register n (where n = 0 to 15) with the 16-bit hex value x. The register can be displayed with the Xn command.

#### 3-22. (SAVE d:file,x,y) UP LOAD

Writes the contents of Evaluation Board memory between the addresses x and y to the AmSYS 8/8 Development System disk "d" on the "file" specified. If the file already exists, it will be deleted

and recreated. The "file" name must be in the AmSYS 8/8 format with the disk drive specified, and the HOST program must be executing.

If this command is entered from the Development System, a prompt, consisting of the currently logged-in diskette identifier in parentheses, will appear on your screen. These simply acknowledge communications received from the Evaluation Board Monitor.

See the next section entitled AmSYS 8/8 Up/Down Loading if you are assembling programs on the Development System.

#### 3-23. (SM) ENTER SYSTEM MODE

Drops you into the CPU's System Mode, in which all privileged instructions can be executed. The Monitor is initialized at power-up in Normal (protected) Mode.

#### 3-24. (S n) SET SIGN FLAG

Sets or resets the sign (S) flag to n = 1 or 0. This syntax takes precedence over the Display and Substitute Memory command. The XF command can be used to display the flags.

### 3-25. (S x) DISPLAY AND SUBSTITUTE MEMORY

Displays the contents of the memory word at address x and waits for your substitution. A 16-bit hex value will replace the contents of the word at address x and advance to the next word. A carriage return only will advance to the next word without substitution. A period (.) will terminate substitution and return to the Monitor's command mode.

Substitutions of addresses  $\emptyset$  or 1 can conflict with the Sn command. To avoid

this conflict, these addresses may be represented by  $\emptyset\emptyset$  and 21, respectively.

#### 3-26. (T m,n) TRACE

Executes m instructions beginning at the current program counter address and displays each instruction in sequence. If n is specified, the display occurs in intervals of n instructions. This command is useful only for CRT or printer consoles, as an alternative to manual single-stepping.

You might need to set the program counter (P=x) before entering this command.

Care should be taken not to trace over system calls because unpredictable results will occur.

#### 3-27. (V n) SET OVERFLOW FLAG

Sets or resets the parity/overflow (P/V) flag to n=1 or 0. This command is equivalent to the Set Parity Flag (Pn) command. The flags can be displayed with the XF command.

#### 3-28. (X) DISPLAY ALL REGISTERS

Displays the contents of all 16 CPU registers, plus the program counter (PC) and flags.

#### 3-29. (XF) DISPLAY FLAGS

Displays the six flags contained in the CPU's Flag and Control Word. The bit-setting of the flag immediately follows its mnemonic. The flags are:

- C Carry

- Z Zero

- S Sign

- P Parity or overflow (P/V)

- D Decimal adjust (DA)

- H Half-carry

#### 3-30. (X n) DISPLAY WORD REGISTER

Displays the 16-bit contents of CPU register n, where n=0 to 15. Register 15 is the stack pointer and is initialized during power-up to 40AE.

### 3-31. (XP) DISPLAY PROGRAM COUNTER

Displays the address contained in the program counter register.

#### 3-32. (Z n) SET ZERO FLAG

Sets or resets the zero (Z) flag to n = 1 or 0. The flags can be displayed with the XF command.

### 3-33. MONITOR I/O SUPPORT FOR USER PROGRAMS

I/O through the serial or parallel ports can be done either by your program, through the CPU's I/O instructions in system mode, or by the Monitor.

To use the Monitor for I/O, these general steps are followed:

- 1. Store a block of four 16-bit control words in memory.

- Store the beginning address of this block in register R1.

- 3. Execute the SC instruction using a value of zero (a non-zero value will be interpreted as a program exit which will return control to the monitor).

The block of four 16-bit control words is ordered as shown in table 3-2. The function code is stored in the most significant byte of word one; the least significant byte of word one contains the response code. Words two, three and four provide the address of the file name, the beginning address of

data, and the number of bytes to be written on read as described in the following function code description.

Read Control Statement (function code 0) - This command is intended for use by the assembler. It transfers the user call command line to the specified area in the same form as the Read Console function code 1

Read Console (function code 1) - Reads a single line from the console. The file name address is unused. The data length represents a maximum and is replaced by the actual length. A console message is always terminated by a carriage return. The response code is nomally zero unless the message was truncated, in which case, the response code is 1.

Write Console (function code 2) - Writes a single line to the console. The file name address is unused. The data length represents the write length. The system provides no automatic end of line thus, the message must contain any required carriage return or line feed codes. The response code is zero.

Write Line Printer (function code 3) - Outputs a single line to the line printer. The file name address is unused. The data length represents the write length. All printer controls must be user supplied. The System 8/8 host must be connected and its monitor in execution. The response code is zero.

Open Disk File (function code 4) - Prepares a disk file to be read. The data address and length are unused. The file name address points to the address of the file name, which must be thir-

TABLE 3-2. MONITOR I/O CONTROL BLOCK

| Word | Byte        | Contents                                                                                                                                                                                                                                              |

|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | High        | Function Code  1 = Read from console  2 = Write to console  3 = Write line printer  4 = Open disk file  5 = Close disk file  6 = Created disk file  7 = Read disk sector  8 = Write disk sector  0 = Read Control statement                           |

|      | Low         | No entry. Response code is stored here after I/O.                                                                                                                                                                                                     |

| 2    | High<br>Low | Address at which the file name is stored.                                                                                                                                                                                                             |

| 3    | High<br>Low | Beginning address of data to be written or read. Data written must include any necessary carriage return, line feeds etc. Data read will include them also.                                                                                           |

| 4    | High<br>Low | Length in number of bytes. It indicates either the total number of bytes to be written, or the maximum number of bytes to be read. The total number of bytes read up to and including the carriage return is stored here upon return to user program. |

teen characters long and in AMDOS format e.g., A:FILEbbbbEXT. The response code is zero if the file was opened, 1 if not found, 2 if a disk error occurred, and 3 if the file is already open. The Sytem 8/8 host must be connected and its monitor in execution.

Close Disk File (function code 5) -Closes a file. The data address and length are unused. The file name address points to the address of the file name, which must be thirtheen characters long and in AMDOS format (See function code 4). The response code is zero if the file was closed, 1 if not found, 2 if a disk error occurred, and 3 if not previously opened or created. The Sytem 8/8 host must be connected and its monitor in execution.

Write Disk Sector (function code 8) -Write one disk sector (128 bytes) Both be given.

re-opened. The Sytem 8/8 host must be

connected and its monitor in execution.

the file name and record address must The data length is unused. The next sequentioal sector on the specified file will be written with the contents of that data area. sponse code is zero if no errors, 1 if no disk space, 2 if a disk error occurred, or 3 if this file was not previously created. Attempting to write to an opened file will also return code The System 8/8 host must be connected and its monitor in execution.

HE CONTRACTOR OF THE RESERVE OF THE PROPERTY O

section should be called HOST The AND MONITOR COMMUNICATION.

Create Disk File (function cod The data addre The file order: length are unused. address specifies the address at the file name is stored. The fil must be thirteen characters long AMDOS format. The response c zero if the file was created, 1 file space, 2 if a disk error occ and 3 if the file is already o If a prior file exist created. will be deleted before the new The Sytem 8/8 host mu created. connected and its monitor in exec

Creates a disk file and prepares The capabilities should be listed in a more reasonable

- Assemble (or assemble and link) AmZ8000 sourc. (or MACRO8000 with MACRO8000 LINK8000) on Amsys 8/8.

- Download programs to the Evaluation Board with the LOAD Monitor command or LDPR Monitor command, as described later in this section.

- Store programs by uploading the memory image from the Evaluation Board to a file on AmSYS 8/8. The file is uploaded with the SAVE Monitor command and can later be downloaded again with the LOAD Monitor command.

Read Disk Sector (function code 7) -Reads one disk sector (128 bytes) Both the file name and record address must be given. The data length is returned. The next sequential sector on the specified file will be transferred to the data area. The response code is zero if no errors, 1 if end of file occurred, 2 if a disk error occurred, or 3 if this file was not previously opened or an attempt is made to read a created file. If a created file is to be read, it must be closed and acting system supports a utility HOST, which communicates with the Evaluation Board Monitor. The HOST utility interfaces with AMDOS8 for service calls to read the console, print lines, and process disk requests.

The program is activated like any other AMDOS8 program: by typing in its name, in this case HOST. It will respond with the message SYSTEM 8/8 Z8000 HOST followed by a prompt which consists of the currently logged-in disk drive in parentheses, e.g., (A).

After an up or down load, the HOST program can be terminated with the Control L and END sequence so that execution on the Evaluation Board may proceed conexecution with unrelated currently under the Development System's oper-The message system. ating upon termination. SHUTDOWN appears This soft shutdown is provided so that the program can close any files left open.

The Control L entry indicates to the HOST program that the command to follow is meant for it. The Control L END sequence is currently the only user command to the HOST program. All other commands entered from the AmSYS 8/8 console (i.e., those without Control L) are transmitted to the Evaluation Board for interpretation. Upon transmission. the Development System will acknowledge this with its prompt. The Evaluation Board will acknowledge reception of the command with its prompt, another more specific response, or both. Thus, the Development System console can effectively become the Evaluation console.

The HOST program can issue five error messages, which are explained below.

COMMAND ERROR - Invalid Control L command.

Z8000 MESSAGE PENDING - A prior message to the Evaluation Board CPU has not yet been acted upon.

80 CHARACTERS EXCEEDS MESSAGE Re-enter your message using fewer characters.

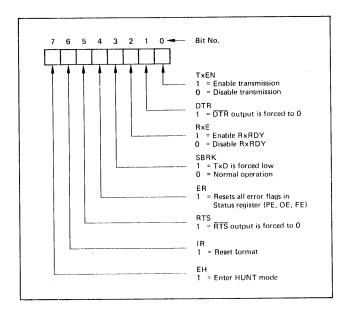

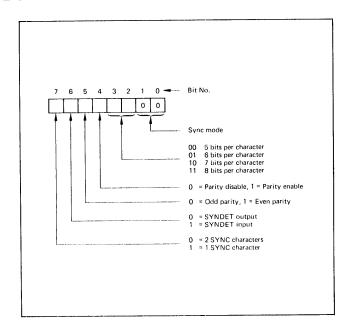

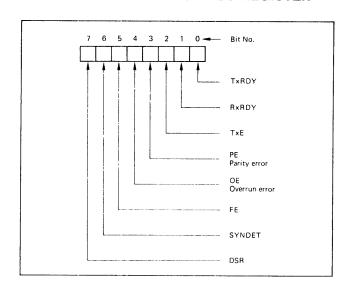

ILLEGAL REQUEST FROM Z8000 - The Development System has received an unrecognized message from the Evaluation Board.