Advanced

Micro

Computers

A subsidiary of

Advanced Micro Devices

# Am96/4018 AmZ8000 Evaluation Board

**User's Manual**

|           | REVISION RECORD   |  |

|-----------|-------------------|--|

| REVISION  | DESCRIPTION       |  |

| 01        | Preliminary Issue |  |

| (7/13/81) |                   |  |

| Α         | Manual Released   |  |

| (8/21/81) |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

|           |                   |  |

Publication No. 059910622-001

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1981 Advanced Micro Computers Printed in U.S.A.

Address comments concerning this manual to:

ADVANCED MICRO COMPUTERS

Publications Department

3340 Scott Boulevard

Santa Clara, CA 95051

## **PREFACE**

This manual provides general information, an installation and interface guide, and programming information, and principles of operation for the Advanced Micro Computers Am96/4018 AmZ $8000^{\dagger}$  Evaluation Board. Additional information concerning components of the Am96/4018 is available in the the following documents:

- AmZ8001/2 Processor Instruction Set

- AmZ8000 User's Manual

- AmZ8000 Family Data Book

- AmZ8001/AmZ8002 Processor Interface

- AmZ8000 Microprocessor Specification

- Zilog, Z8001 CPU/8002 CPU Product Spec.

- AmZ8001 Data Sheet

- AmZ8002 Data Sheet

- AMD Shottky and Low Power Shottky Data Book

- Am8251-Am9551 Data Sheet

- Am8255/Am8255-5 Data Sheet

- Am8253 Data Sheet

- 8259A Data Sheet (Intel)

<sup>†</sup>Z8000 is a trademark of Zilog, Inc.

# **TABLE OF CONTENTS**

| 1. | INTRODUCTION                       |    | Move Memory Contents4-10 Set Normal Mode4-10 |

|----|------------------------------------|----|----------------------------------------------|

|    | Descriptionl-l                     |    | Output Data To I/O Port4-11                  |

|    | The CPU1-3                         |    | Display/Set Program Counter4-11              |

|    | Memory1-4                          |    | Display/Alter Registers4-11                  |

|    | Input/Output1-4                    |    | Substitute Memory Contents4-12               |

|    | Software1-9                        |    | Save Memory Contents Through                 |

|    |                                    |    | Parallel I/O Port4-12                        |

|    |                                    |    | Save Memory Contents Through                 |

| 2. | INSTALLATION AND INTERFACING       |    | Serial I/O Port4-13                          |

|    |                                    |    | System Mode4-13                              |

|    | Unpacking and Inspection2-1        |    | Trace4-13                                    |

|    | Installation Overview2-1           |    | Untrace4-14                                  |

|    | ROM/E-PROM Sockets2-2              |    | Register Display4-14                         |

|    | Parallel I/O Driver/Terminators2-5 |    | Display Flag and Control Word4-14            |

|    | Edge Connectors2-5                 |    | Set/Reset Flag Control                       |

|    | Keyboard/Display Installatin2-7    |    | Words Bits4-15                               |

|    | Prototyping and Memory-            |    | Monitor Console I/O Support4-15              |

|    | Expansion Boards2-10               |    | GHOST - Am96/4018 Host                       |

|    | Development System Inter-          |    | Facility4-17                                 |

|    | connection2-11                     |    | Transparent Mode4-17                         |

|    | Jumper Options2-11                 |    | Download Mode4-19                            |

|    |                                    |    | Upsave Mode4-19                              |

|    |                                    |    | GHOST Error Messages4-20                     |

| 3. | PERIPHERAL PROGRAMMING             |    |                                              |

|    |                                    |    |                                              |

|    | Parallel I/03-1                    |    |                                              |

|    | Serial I/03-3<br>Counter/Timer3-7  | 5. | LINE-BY-LINE ASSEMBLER (ASM)                 |

|    |                                    |    | Environment5-1                               |

|    |                                    |    | Functions5-1                                 |

| ,  |                                    |    | ASM Call5-1                                  |

| 4. | AmZ8001 AND AmZ8002 MONITORS       |    | Up/Down Loading5-2                           |

|    |                                    |    | Output5-2                                    |

|    | Introduction4-1                    |    | Sample Program5-3                            |

|    | Installation4-1                    |    | Statements5-3                                |

|    | Monitor Commands4-2                |    | Special Characters5-3                        |

|    | Keyboard/Display Console4-2        |    | Delimiters5-5                                |

|    | Line-By-Line Assembler4-6          |    | Symbols5-5                                   |

|    | Breakpoints4-6                     |    | Numeric Constants5-5                         |

|    | Display Memory Contents4-6         |    | Opcodes5-6                                   |

|    | Hardware Breakpoint4-7             |    | Labels5-6                                    |

|    | Fill Memory4-8                     |    | Address Constants5-6                         |

|    | Help4-8                            |    | Absolute Address Constants5-6                |

|    | Go To User Program4-9              |    | Symbolic Constants5-6                        |

|    | Input From I/O Port4-9             |    | Strings5-7                                   |

|    | Load File Through Parallel         |    | Expressions5-7                               |

|    | I/O Port4-9                        |    | Directives5-7                                |

|    | Load File Through Serial           |    | End Diretive5-7                              |

|    | I/O Port4-10                       |    | Byte Directive5-8                            |

|    |                                    |    |                                              |

|      | Word Directive5-8                | 3-3.         | Am9551 Asynchronous Mode         |

|------|----------------------------------|--------------|----------------------------------|

|      | Long Directive5-9                |              | Control Code3-5                  |

|      | Const Directive5-9               | 3-4.         | Am9551 Control Command3-5        |

|      | Quit Directive5-10               | 3-5.         | Synchronous Mode Control Code3-6 |

|      | Instructions5-10                 | 3-6.         | Am9551 Status Register3-6        |

|      | Opcodes5-10                      | 3-7.         | Am8253 Control Byte Format3-9    |

|      | Operands5-11                     | 3-8.         | Am8253 Control Byte              |

|      | Instruction Summary5-11          |              | Definition3-10                   |

|      | Alphabetical Listing of          | 3-9.         | Am8253 Control Byte to           |

|      | Instructions5-27                 |              | Latch Count3-10                  |

|      | Error Messages5-37               | 4-1.         | Memory Address4-3                |

|      |                                  | 5-1.         | Sample Program5-4                |

|      |                                  | 6-1.         | Bus Structure6-4                 |

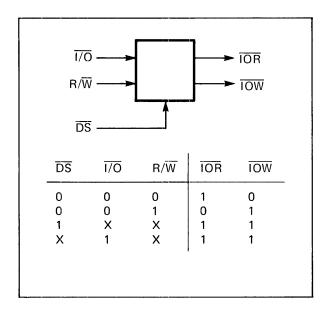

| 6.   | PRINCIPLES OF OPERATION          | 6-2.         | IOR* and IOW* Decoding6-5        |

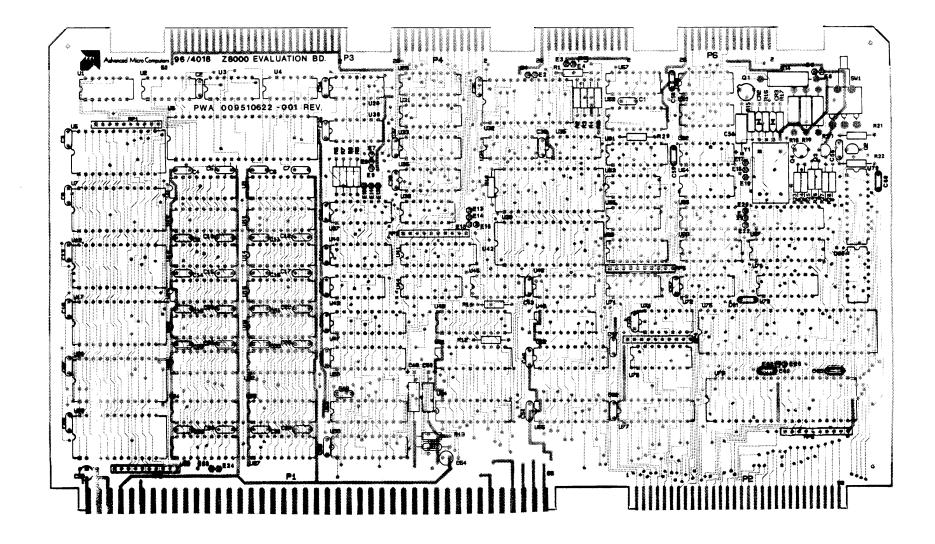

|      | •                                | C-1.         | Component Location DiagramC-2    |

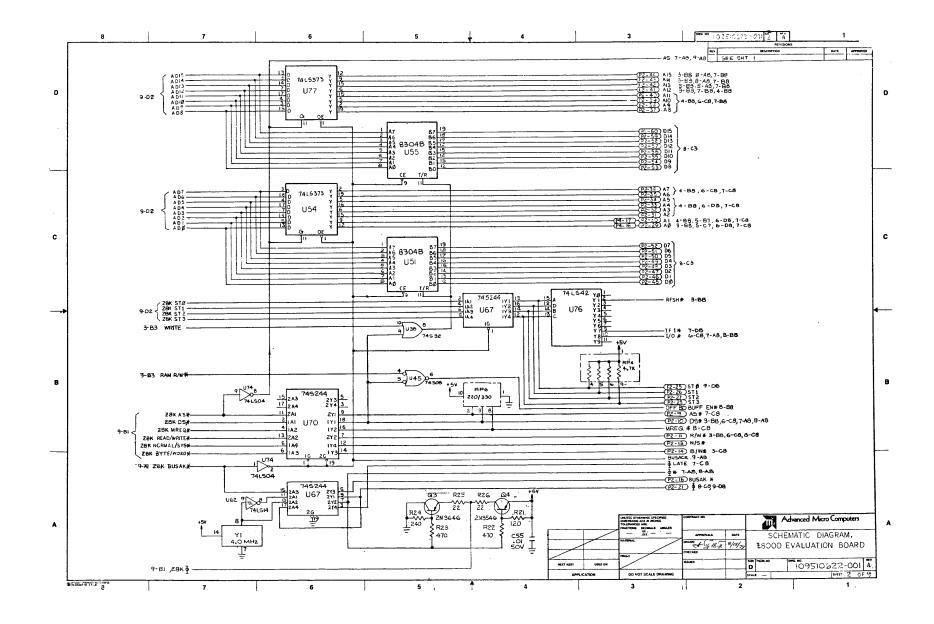

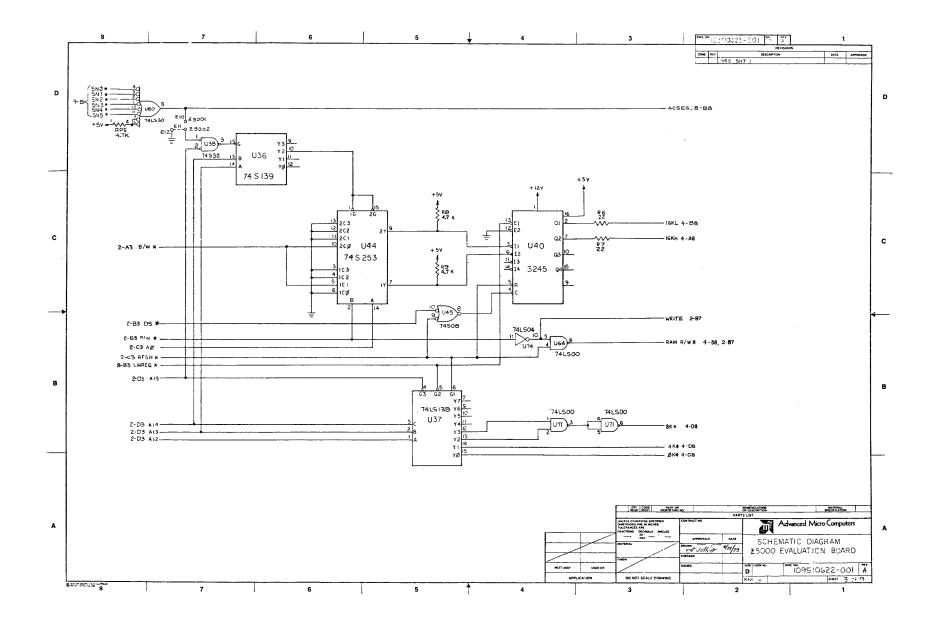

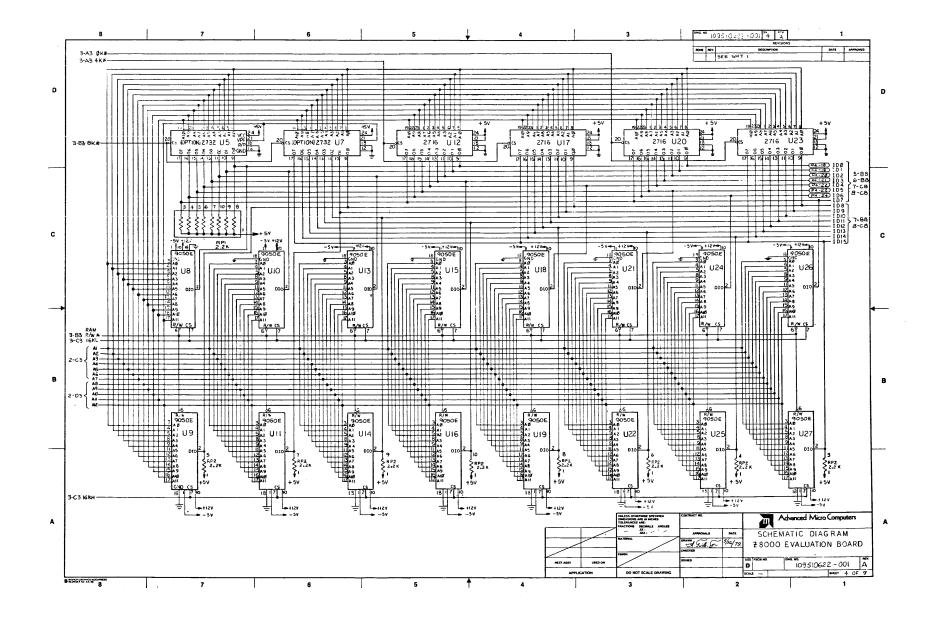

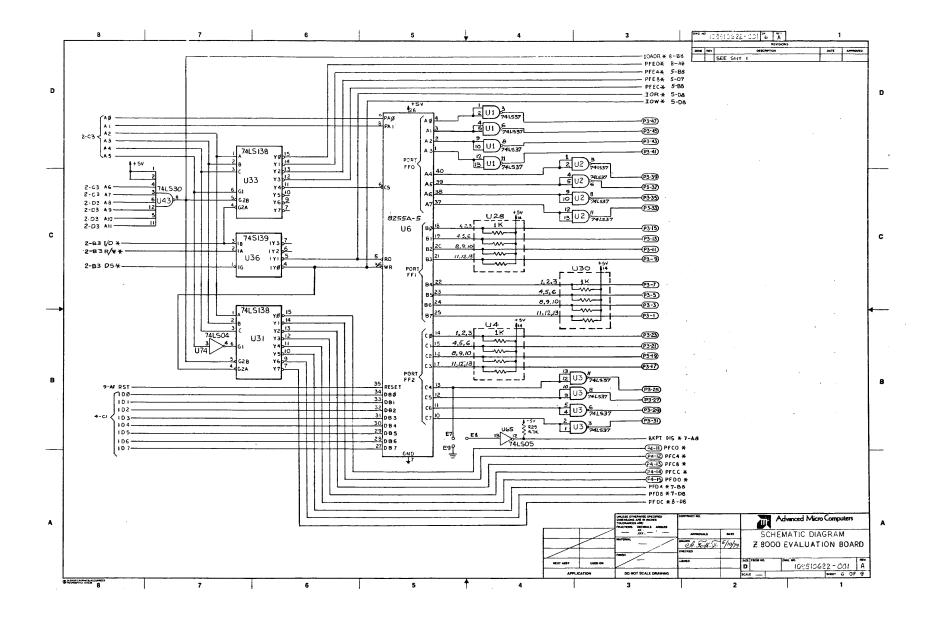

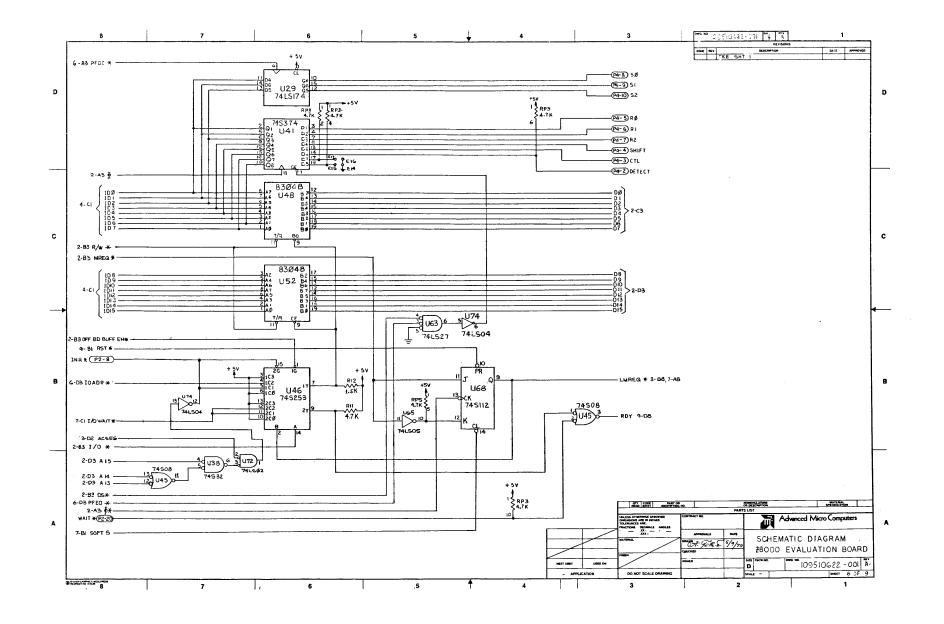

|      | Power-Up Sequence6-1             | C-2.         | Am96/4018 Schematic Diagram      |

|      | CPU Functions6-1                 |              | Sheet 1                          |

|      | Bus Structure6-3                 | C-3.         | Am96/4018 Schematic Diagram      |

|      | Memory6-3                        |              | Sheet 2                          |

|      | Peripheral Decoding6-5           | C-4.         | Am96/4018 Schematic Diagram      |

|      |                                  |              | Sheet 3                          |

|      |                                  | C-5.         | Am96/4018 Schematic Diagram      |

| APPE | ENDIX                            |              | Sheet 4                          |

|      |                                  | C-6.         | Am96/4018 Schematic Diagram      |

| Α.   | CPU BUS BUFFERING CHARACTER-     |              | Sheet 5                          |

|      | ISTICS AT P2A-1                  | C-7.         | Am96/4018 Schematic Diagram      |

|      |                                  |              | Sheet 6                          |

| В.   | ASCII CHARACTER SETB-1           | C-8.         | Am96/4018 Schematic Diagram      |

| _    |                                  |              | Sheet 7                          |

| С.   | SERVICE INFORMATION              | C-9.         | Am96/4018 Schematic Diagram      |

|      |                                  |              | Sheet 8                          |

|      | Introduction                     | C-10.        | Am96/4018 Schematic Diagram      |

|      | Service and Repair AssistanceC-l |              | Sheet 9                          |

|      | Service Diagrams                 |              |                                  |

|      |                                  | M V D T 12 ( | ,                                |

|      |                                  | TABLES       |                                  |

| FIGU | JRES                             | 1-1.         | Specifications1-5                |

|      |                                  | 2-1.         | ROM/E-PROM Sockets2-2            |

| 1-1. | Board Layout1-2                  | 2-2.         | Driver/Terminators For Paral-    |

| 1-2. |                                  |              | lel Port (P3)2-5                 |

| 1-3. |                                  | 2-3.         | Other Driver/Terminators Cir-    |

| 1-4. |                                  |              | cuits For P32-5                  |

| 2-1. |                                  | 2-4.         | Pl Connector Pins2-8             |

|      | Sockets2-2                       | 2-5.         | P2 Connector Pins2-8             |

| 2-2. | Connecting to the Develop-       | 2-6.         | P3 Connector Pins2-9             |

|      | ment System2-3                   | 2-7.         | P4 Connector Pins2-9             |

| 2-3. | Connecting the Keyboard/         | 2-8.         | P5 Connector Pins2-10            |

|      | Display Console2-4               | 2-9.         | P6 Connector Pins2-10            |

| 2-4. | 1 1                              | 3-1.         | Am8255A Addresses3-3             |

| 3-1. | Am8255A Operation Control        | 3-2.         | Am9551 Addresses3-6              |

|      | Word Format3-2                   | 3-3.         | Am8253 Addresses3-9              |

| 3-2. |                                  | 4-1.         | E-PROM Locations4-1              |

|      | Word Format3-2                   | 4-2.         | Monitor Command Summary4-4       |

| 4-3. | Monitor Console I/O Con-         | 5-7.  | Bit Manipulation Instruc-     |

|------|----------------------------------|-------|-------------------------------|

|      | trol Block4-16                   |       | tions5-19                     |

| 5-1. | Addressing Modes For SRC and     | 5-8.  | Rotate and Shift Instruc-     |

|      | DST Operands5-12                 |       | tions5-20                     |

| 5-2. | Condition Codes5-13              | 5-9.  | Block Transfer and String     |

|      |                                  |       | Manipulation Instructions5-21 |

| 5-3. | Load and Exchange Instruc-       | 5-10. | Input/Output Instructions5-24 |

|      | tions5-14                        | 5-11. | CPU Control Instructions5-26  |

| 5-4. | Arithmetic Instructions5-15      | 5-12. | Alphabetical Listing5-27      |

| 5-5. | Logical Instructions5-17         | 6-1.  | Peripheral Addresses6-6       |

|      | Program Control Instructions5-18 | B-1.  | ASCIIB-1                      |

|      |                                  |       |                               |

#### CHAPTER 1

# INTRODUCTION

#### DESCRIPTION

The Am96/4018 Evaluation Board is a complete single-board micro computer built around the new 16-bit AmZ8000 microprocessor. Used with a standard CRT or the low-cost keyboard/display console available as an option, it provides an excellent means of testing the advanced capabilities of this remarkably versatile CPU. Used with Advanced Micro Computer's 16-bit Development Systems, the entire AmZ8000 instruction set can be macroassembled to create very powerful programs for execution on the Evaluation Board.

The fully assembled and tested board has the following features:

#### Standard Features:

- AmZ8002 (non-segmented) CPU.

- 8K bytes of dynamic RAM, expandable off-board.

- Up to 16K bytes of ROM or E-PROM, expandable off-board.

- 8K byte ROM Monitor, with breakpoint, single-step and up/down-load commands.

- Buffered CPU bus available at edge of board.

- Two programmable serial I/O ports (RS232C and 20mA).

- A programmable counter/timer channel.

- 24 programmable parallel I/O lines (three 8-bit ports).

- Fits in Multibus<sup>†</sup> or iSBC<sup>†</sup> card cage.

#### Optional Features:

- AmZ8001 (segmented) CPU with 8K byte ROM monitor (Am96/4018/600).

- Keyboard/Display console (Am96/4018/100).

- CRT terminal.

- Universal prototyping board.

- 3-slot CPU-bus backplane (Am96/4018/400).

- Six-board card cage.

- 64-kilobyte memory expansion (up to 4 M bytes for AmZ8001).

- Complete 16-bit Development Systems, with diskette storage, interface utilities and macro-assembler for the AmZ8000 series.

- Line-by-line assembler in E-PROM (Am96/4018/200).

- Parallel I/O cable and diskette for use with Development System (Am96/4018/500).

Programs can be entered and executed in either the stand-alone or Development System configuration. Specialized circuits or external expansion boards can also be attached in either mode. The entire CPU bus is buffered and brought to the edge of the board for interconnection, as are extra I/O ports for serial and parallel transfers on the data bus.

<sup>&</sup>lt;sup>†</sup>Trademarks of Intel Corporation

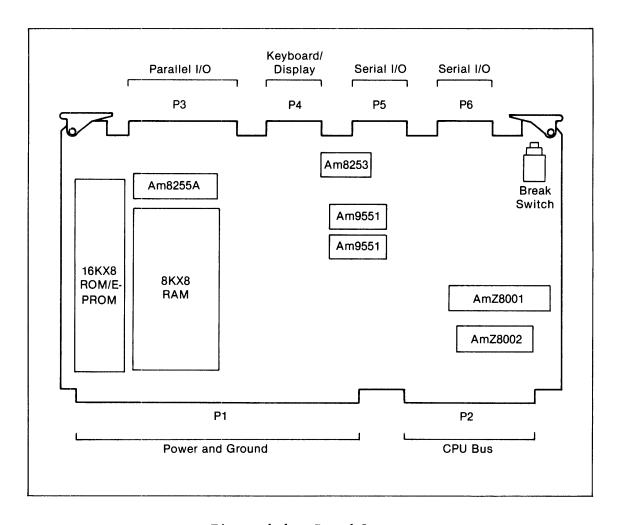

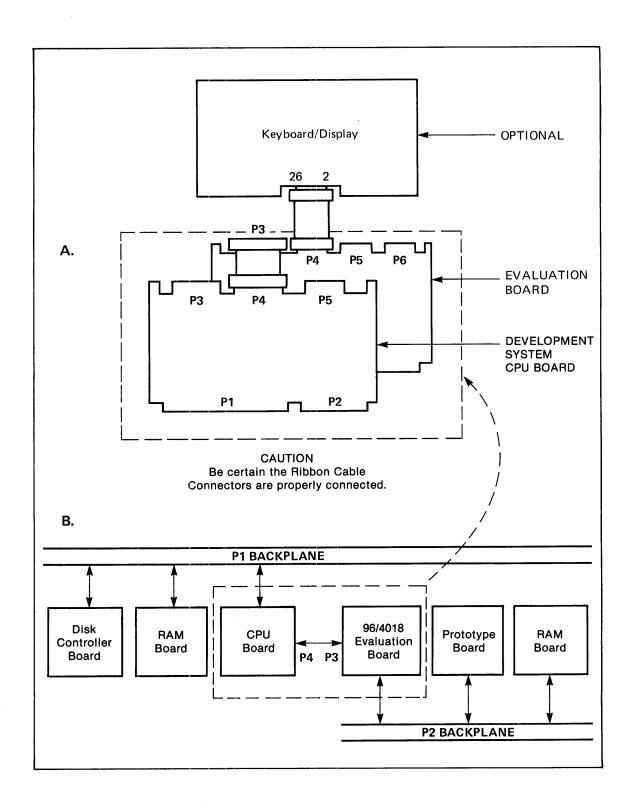

Figure 1-1 illustrates the board layout. The lower two edge connectors are physically compatible with the Multibus standard, although the Pl edge connector uses only power and ground in the standard Multibus card cage.

All four top edge connectors on the board are used for I/O. The P3 connector has 24 programmable lines, each with an associated ground, divided into three 8-bit ports for data and handshaking. The P4 connector is also parallel but designed specifically for the optional keyboard/display console that can be attached to the Evaluation Board. The P5 and P6 connectors both carry programmable lines for asynchronous or synchronous serial data. The P5 connector also carries control I/O for an on-board programmable counter/timer channel.

The CPUs are in the bottom right corner of the board. Near the top center is the Am8253 counter/timer and the two Am9551 serial I/O devices. The Am8255A parallel I/O device is in the upper left near P3 and the six driver/terminator sockets. The 8K bytes of user memory (RAM) and sockets for the 16K bytes of ROM are near the left edge of the board (the upper two sockets are reserved for 2732-type E-PROMS).

Figure 1-1. Board Layout

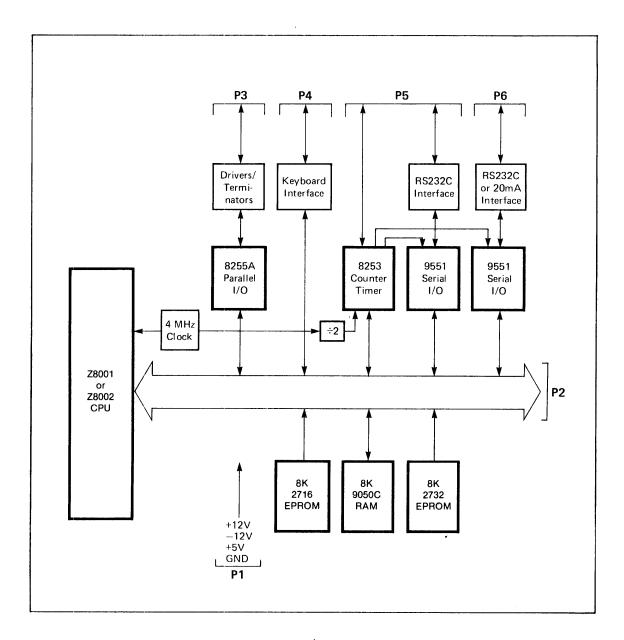

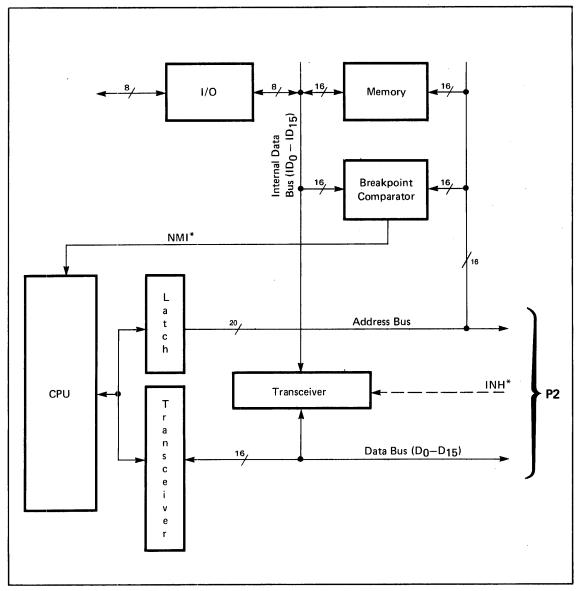

Figure 1-2 is a block diagram of the board. The system buses (address, data, and control) are buffered and available at connector P2. The multiplexed address/data is also available via the DATA pins on P2. The address and data buses, which are multiplexed in the CPU are separated into two separate 16-bit buses on the board. Figure 1-2 shows more clearly the difference between P5 and P6 serial I/O ports; one has a counter/timer available and the other can be either RS232C or 20mA current loop. Six of the seven AmZ8001 segment outputs are available at connector P2.

Memory-expansion boards and prototyping boards carrying any AmZ8000-compatible circuits (such as DMAs or even multiple CPUs) can be attached at P2. Specialized circuits can also be attached at P3, P5 and P6. P5 is useful for event-counting, process control circuits, or foreign host computers.

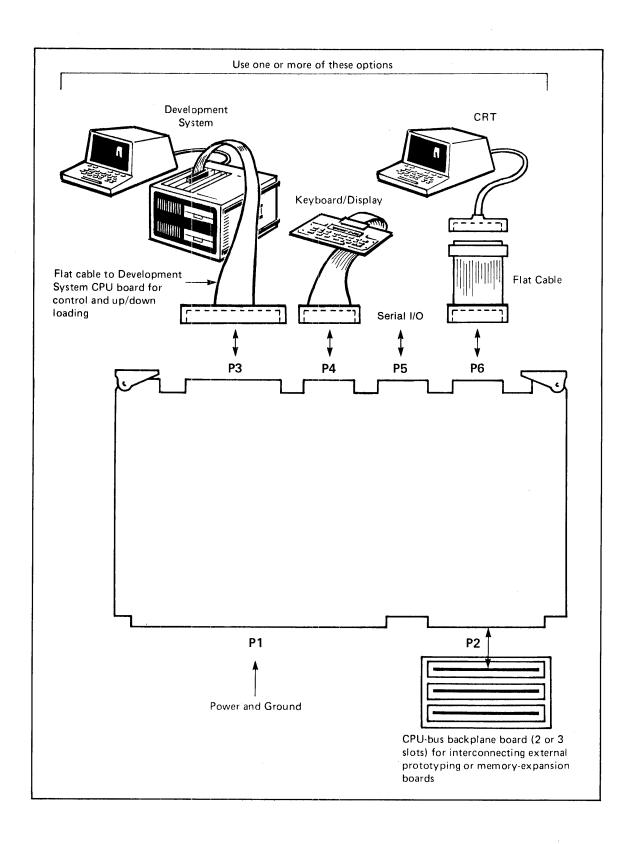

Figure 1-3 illustrates the range of standard plug-in configurations supported by the board's Monitor program. If attachments to the board are limited to any one or more of these three choices, application programming and execution can begin immediately without having to program the  $\rm I/O$  circuits.

When a Development System is connected for up/down loading of programs, the Development System's console can communicate with the Evaluation Board to control all functions.

The Development System contains a comprehensive set of hardware and software resources to fully utilize AmZ8000 capabilities. The system includes 64K bytes of RAM, serial and parallel ports, and a multimaster bus. Existing programming support includes a CP/M-compatible operating system with linking loader, editor and debugger and an AmZ8000 macroassembler, 8080 macro assembler and AmZ8000 translator.

Table 1-1 gives a summary list of specifications for the Evaluation Board

#### THE CPU

The AmZ8001 and the AmZ8002 microprocessors are register-oriented CPU's with minicomputer-like architecture. Sixteen general-purpose 16-bit registers, are available to the user. Over 100 instructions, and 400 combinations of instructions, can be used to manipulate data between the CPU registers, memory and I/O. Only one CPU can be used on-board, never both at the same time.

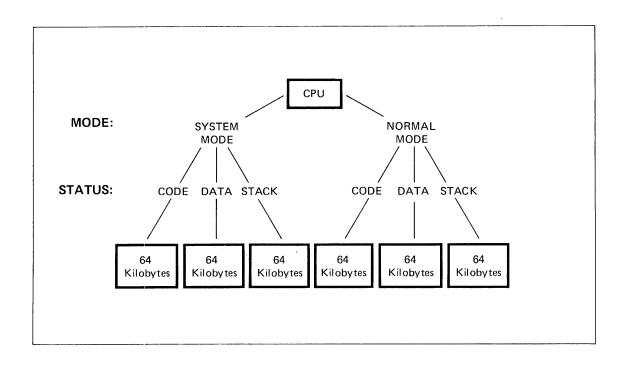

The CPU can operate in two modes, System and Normal, with separate relocatable stacks for each mode. This allows a distinction between privileged and protected instructions, as well as flexibility in allocating the system's use of memory. In either mode, 14 status conditions are continuously reported:

Internal operation Memory refresh I/O reference Special I/O reference Segment trap acknowledge Nonmaskable interrupt acknowledge Nonvectored interrupt acknowledge Vectored interrupt acknowledge Data memory request Stack memory request Data memory request (EPU) Stack memory request (EPU) Instruction space access Instruction fetch, first word Extension processor transfer Reserved

Only three of these status outputs (2, 6, and 7) are needed by the Evaluation Board's internal functions, but all are available, by decoding the status lines, at the P2 edge connector.

The interrupt and trap structure is particularly powerful, with very fast response to external devices and illegal conditions.

#### **MEMORY**

The Evaluation Board's dynamic RAM is refreshed by the CPU. Additional memory, either dynamic or static, can be added off-board through the P2 edge connector.

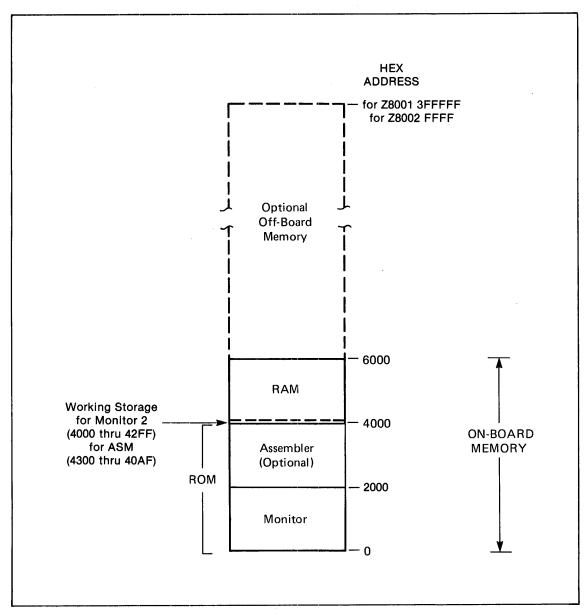

The AmZ8002 can directly address 64K bytes of memory using 16 address bits. The 23-bit address structure of the AmZ8001, is made up of 16 address bits and seven segment select outputs. Of the seven segment outputs available from the AmZ8001, only six are available on the Am96/4018, permitting memory addressing capability of 4 megabytes. If the distinctions between operating mode (System and Normal), and memory access status are used to differentiate memory resources, up to 384K bytes are available with the AmZ8002 and up to 24 Megabytes for the AmZ8001. Figure 1-4 illustrates the expanded memory capability for the AmZ8002.

#### INPUT/OUTPUT

Memory space and I/O space are differentiated by a memory-request line and other status outputs from the CPU. The CPU can use 16-bit I/O port addresses, although in the Evaluation board implementation the upper four address bits are not decoded. This gives 4K I/O ports for both on-board and off-board I/O.

#### TABLE 1-1. SPECIFICATIONS

| СРИ                        | AmZ8001 (segmented) or AmZ8002 (non-segmented)                                                                                                                                                                                                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time Base                  | 4MHz crystal oscillator                                                                                                                                                                                                                                                                                          |

| Serial I/O                 | Two RS232C serial ports with software-programmable baud rates. One port jumper- selectable for 20mA current-loop (TTY) operation.                                                                                                                                                                                |

| Parallel I/O               | 24 parallel I/O lines (three 8-bit ports). Also provides interconnection to 16-bit Development Systems.                                                                                                                                                                                                          |

| RAM Memory                 | 8K bytes of on-board dynamic memory; CPU refreshed (transparent).                                                                                                                                                                                                                                                |

| ROM Space                  | 16K bytes of ROM/EPROM space provided in six sockets; ROM monitor occupies four sockets.                                                                                                                                                                                                                         |

| Counter/Timer              | Three 16-bit programmable interval counter; two counters used for serial I/O baud rate control; third counter available to user.                                                                                                                                                                                 |

| Power                      | -12Vdc at 0.085A, +12Vdc at 0.06A, +5Vdc at 1.65A (without optional keyboard/display console), +5Vdc at 2.0A (with keyboard/ display console).                                                                                                                                                                   |

| Dimensions                 | 12.0" (305 mm) x 6.75" (172 mm); MULTIBUS form factor with six edge connectors (P1 through P6).                                                                                                                                                                                                                  |

| Memory                     | ROM space: 0-3FFFH Addressing RAM space: 4000-5FFFH                                                                                                                                                                                                                                                              |

| Environmental              | 0 to 55C ambient in free-air space with Conditions relative humidity to $90\%$ without condensation.                                                                                                                                                                                                             |

| Edge-of-Card<br>Connectors | P1: 86-Pin for power, ground, and initialize. P2: 60-Pin CPU bus P3: 50-Pin parallel I/O for up/down-load from 16-bit Development Systems. P4: 26-Pin interface for optional keyboard/display board. P5: 26-Pin RS232 and counter/timer interface. P6: 26-Pin RS232 or 20mA current loop for CRT or TTY console. |

| Monitor                    | 8K ROM monitor included at addresses 0-1FFFH                                                                                                                                                                                                                                                                     |

TABLE 1-1. SPECIFICATIONS (continued)

| Up/Down-Load                     | Can be plugged into 16-bit Development Systems to provide up-load and down-load capability. Can also by used with other host computer systems to execute AmZ8000 code.            |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Optional<br>Keyboard/<br>Display | 56-key keyboard with 20-character alphanumeric LED display. Same physical form as Am96/4016 Evaluation Board with attaching standoff connectors and interconnection ribbon cable. |

Figure 1-2. Am96/4018 Block Diagram

Figure 1-3. Standard Configurations

Figure 1-4. Memory Addressing Potential

The Evaluation Board implements only 8-bit I/O transfers on-board. These are the lower 8 bits on the data bus. Off-board I/O transfers can be 8 or 16 bits.

The 24 parallel I/O lines of the Am8255A circuit at P3 can be configured to transfer data in a variety of ways, with or without handshaking. In the standard configuration, this edge connector is used for up/down loading between the 16-bit Development Systems and the Evaluation Board. The Am8255A has a bit set/reset function that increases the efficiency of handshake software. The sockets provided for driver or terminator circuits allow further characterization of these ports for special applications. Ground lines are interleaved with signal lines for better noise immunity at this edge connector.

Two Am9551 Programmable Communications Interface devices can be programmed for a broad range of full-duplex, double-buffered serial communication protocols. The two serial ports are available at connectors P5(RS232C) and P6(RS232C or 20mA current loop). The data (baud) rate is controlled by two of three programmable counters in the Am8253 counter/timer device.

As mentioned above, no programming of I/O circuits is necessary when the Evaluation Board is used in one of the standard configurations illustrated in figure 1-3. The Monitor program will initialize these circuits.

#### SOFTWARE

The Evaluation Board's ROM-based Monitor program provides complete system initialization functions and over two dozen user commands for access to CPU registers and memory. It features breakpoint, single step and trace functions, as well as up-save (Am96/4018 to host) and down-load (host to Am96/4018) for use with the 16-bit Micro Computer Development Systems as the host computer. Any AmZ8000 instruction whether privileged (system mode) or protected (normal mode) can be entered in hex format using only the Monitor.

The full CPU instruction set can be used to create very powerful application programs. The 110 basic instructions have permutations around operand addressing modes, plus autoincrement and autodecrement facilities. Code written for the AmZ8002 is compatible with the AmZ8001 microprocessor.

Most instructions are between one and three 16-bit words in length. Instructions and hardware are available to operate on bits, 4-bit digits (BCD), 8-bit bytes, 16-bit words, 32-bit long words, 64-bit quad words, byte strings and word strings.

String instructions are auto-incrementing or auto-decrementing block transfers. The strings can be up to 64 kilobytes in length, the entire directly-addressable memory, and the transfers are interruptable.

# CHAPTER 2

# INSTALLATION AND INTERFACING

#### **UNPACKING AND INSPECTION**

Upon receipt of this equipment, inspect both the equipment and the shipping carton immediately for evidence of damage during transit. If the shipping carton is damaged or water-stained, request the carrier's agent to be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, save the carton and packing material for the agent's inspection. Shipping damages should be reported immediately to the carrier.

NOTE

Do not attempt to service the board yourself, as this will void the warranty.

#### **INSTALLATION OVERVIEW**

Figure 2-1 illustrates the hardware connectors and sockets that might require setup before the board can be used. These are the six edge connectors, Pl through P6, plus sockets for ROM or E-PROM and the sockets for parallel I/O driver or terminator circuits. Each of these groups is discussed individually below.

NOTE

When one of the standard configurations illustrated in figure 1-3 has been ordered from AMC, only the following installation connections need be considered.

| EDGE<br>CONNECTION | EXTERNAL CONNECTION                                                                                                    |

|--------------------|------------------------------------------------------------------------------------------------------------------------|

| Р3                 | 16-bit Development Systems CPU board (P3), as illustrated in figure 2-2, or a 8/8630 Communication Controller package. |

| P4                 | Keyboard/LED Display Board (Am96/4016-KBD), as illustrated in figure 2-3.                                              |

| P5                 | Serial I/O RS232C.                                                                                                     |

| P6                 | CRT or other RS232C terminal, or 20mA current loop.                                                                    |

Figure 2-1. Edge Connectors and IC Sockets

# **ROM/E-PROM SOCKETS**

The board contains six sockets for fixed-address ROM or E-PROM. All boards are shipped with at least four E-PROMs installed, which contain the 8-kilobyte Monitor program. Table 2-1 lists the memory space assigned to ROM and the device reference designators.

TABLE 2-1. ROM/E-PROM SOCKETS

| PROGRAM     | ADDRESSES (HEX)         | SOCKET AND DEVICE |

|-------------|-------------------------|-------------------|

| Monitor     | 000000 to 000FFE (Even) | U23 (2716)        |

| Monitor     | 000001 to 000FFF (odd)  | U20 (2716)        |

| Monitor     | 001000 to 001FFE (Even) | U17 (2716)        |

| Monitor     | 001001 to 001FFF (Odd)  | U12 (2716)        |

| User or ASM | 002000 to 003FFE (Even) | U7 (2732)         |

| User or ASM | 002001 to 003FFF (Odd)  | U5 (2732)         |

Figure 2-2. Connecting to the Development System

Figure 2-3. Connecting the Keyboard/Display Console

## PARALLEL I/O DRIVER/TERMINATORS

When the board is ordered, the driver and terminator circuits listed in table 2-2 are provided.

Various uses of the P3 edge connector may require different devices for the driver/terminator sockets. Some of the possible devices are listed in table 2-3. Alternatively, the sockets can be jumpered for direct connection to the Am8255A pins.

TABLE 2-2. DRIVER/TERMINATORS FOR PARALLEL PORT (P3)

| DEVICE  | FUNCTION   | SOCKET NO. |

|---------|------------|------------|

| 74LS37  | Driver     | IJ1        |

| 74LS37  | Driver     | U2         |

| 74LS37  | Driver     | บ3         |

| iSBC902 | Terminator | <b>U</b> 4 |

| iSBC902 | Terminator | U28        |

| iSBC902 | Terminator | บ30        |

|         |            |            |

TABLE 2-3. OTHER DRIVER/TERMINATOR CIRCUITS FOR P3

| DRIVERS                                                                                                 | TERMI                         | NATORS                                                |

|---------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------|

| 7438, 74LS38 7437, 74LS37 7432, 74LS32 7426, 74LS26 7409, 74LS09 7408, 74LS08 7403, 74LS03 7400, 74LS00 | Intel<br>National<br>National | 1SBC 901<br>1SBC 902<br>BLC 901<br>BLC 902<br>BLC 903 |

#### **EDGE CONNECTORS**

A minimum of two edge connectors must be used to operate the board. Power (+12V, -12V, +5V) and ground must be supplied through the P1 connector. A system console must also be connected on one of the remaining connectors: either P4 for the AMC-supplied keyboard/display console or P6 for a user-supplied terminal.

Many additions to these required connections are possible, as indicated in the list of edge-connector characteristics and applications below. The list is not needed if you are using the standard configuration illustrated in figure 1-3.

Note that connectors Pl and P2 have their odd-numbered pins on the component side of the board, whereas the remaining connectors have them on the solder side. The abbreviation N/C in the pin-connection lists means no connection.

- P1 an 86-pin connector physically (but not electrically) compatible to the Multibus and iSBC-80 formats. It is used only for power and ground, except that pin 14 can be used for external initializing (reset) when jumpered for this function (see figure 2-4). The pin connections are shown in table 2-4.

- P2 a 60-pin connector physically compatible with the Multibus and iSBC-80 formats. It carries buffered signals from all CPU lines except MREQ\*, uI\*, uO\*, and +5V, which is on the Pl connector, and DECOUPLE, which is not used on the AmZ8000. The multiplexed address/ data bus from the CPU is available on the data pins, and is also demultiplexed into separate address and data buses. The CPU's RESET\* line is connected directly to the RST\* line on P2, although RST\* also resets the Am9551 USARTs and the Am8255A PIO. One additional line, INH\* is used to inhibit addressing of off-board memory when on-board memory is addressed, (INH\* low will inhibit off-board memory).

The P2 connector is used to interface a prototyping board and/or external memory boards. An optional backplane is available for this purpose.

If the CPU is disabled via the BUSRQ\* input, an off-board device can take control over most of the signals on this connector to access memory and peripherals on the Evaluation Board. The pin connections are shown in table 2-5.

P3 - a 50-pin connector to the six driver/terminator sockets of the Am8255A parallel I/O circuit. The 24 active line are divided into three 8-bit ports (addresses FFO, FFI and FF2 hex where the upper four address bits are not decoded). Each port can be programmed independently for input or output to match the functions of the driver or terminator ICs that you insert in sockets U1 through U4, U28, and U30.

When the Development System is used, P3 of the Evaluation Board is connected to the Development System's CPU board for up/down loading and control from the Development System's console, or to the 8/8630. This is illustrated in figure 2-2a. The pin connections are shown in table 2-6.

#### NOTE

Be certain the connectors between the Evaluation Board and CPU are connected properly. Damage to the Evaluation Board may result if P3 is reversed.

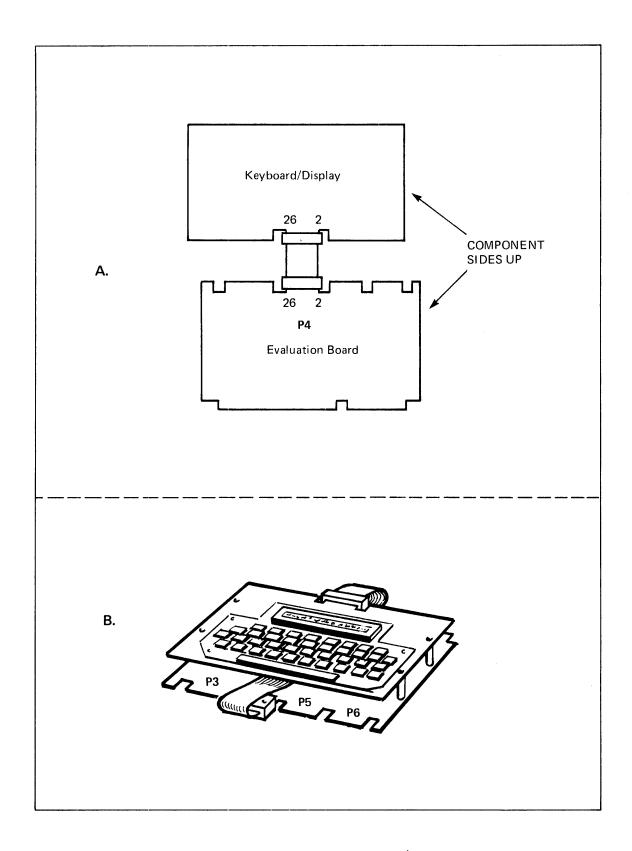

P4 - 26-pin connector used to attach the optional keyboard/display console.

The cable-connection method for the keyboard/display console is illustrated in figure 2-3.

The pin connections listed in table 2-7 include keyboard return and scan lines (R0-R2, S0-S2) and port addresses for LED characters (Ports FCO through FDO hex).

P5 - 26-pin connector providing access to the RS232C interface to one of the two Am9551 serial I/O circuits, plus three three pins connected to channel O of the Am8253 counter/timer circuit.

This connector can be used for time-controlled serial I/O (e.g., process controllers), a host computer other than the 16-bit Development Systems, or any other RS232C serial device.

The I/O port address for data through this connector is FEC hex.

The pin connections are given in table 2-8. Parenthesized numbers are the corresponding EIA pin numbers for RS232C. See the Am9551 and Am8253 Data Sheets for more details.

P6 - 26-pin connector providing access to the RS232C or 20mA interface to one of the two Am9551 serial I/O circuits.

Refer to figure C-6 for jumpering to change P6 from RS232 to 20mZ current loop.

This connector can be used for a system console (terminal) or any other serial I/O device.

The I/O port address for data through this connector is FE8 hex.

The pin connections are given in table 2-9. Parenthesized numbers are the corresponding EIA pin numbers for RS232C.

#### **KEYBOARD/DISPLAY INSTALLATION**

When using the optional keyboard/display console, the following installation method should be used.

Orient the Evaluation Board and the keyboard/display board so that their component sides are facing up and the P4 connector of the Evaluation Board faces the only edge connector of the keyboard/display board. Place the flat cable between the two connectors so that the even pins of the Evaluation Board connect to the even pins of the keyboard/display board, as shown in figure 2-3a. Fold the cable between the boards so that the board spacers lock into the holes on the boards, as shown in figure 2-3b. Both boards will then have their component sides facing down.

TABLE 2-4. P1 CONNECTOR PINS

| СОМР                       | ONENT SIDE                                            | SOLDER SIDE                                                         |  |

|----------------------------|-------------------------------------------------------|---------------------------------------------------------------------|--|

| COMP  1 3 5 7 9 11 13 15 . | GND<br>+5V<br>+5V<br>+12V<br>N/C<br>GND<br>N/C<br>N/C | SOLDER SIDE  2 GND 4 +5V 6 +5V 8 +12V 10 N/C 12 GND 14 INIT* 16 N/C |  |

| 73<br>75                   | N/C<br>GND                                            | 74 N/C<br>76 GND                                                    |  |

| 77<br>79                   | N/C<br>-12V                                           | 78 N/C<br>80 -12V                                                   |  |

| 81                         | +5V                                                   | 82 +5V                                                              |  |

TABLE 2-5. P2 CONNECTOR PINS

| PIN | SIGNAL | PIN | SIGNAL        | PIN  | SIGNAL |

|-----|--------|-----|---------------|------|--------|

|     | 45510  | ٥,  | DVT ( GT VI ) | ] ,, | 4.0    |

| 1   | ADR10  | 21  | PHI(CLK)      | 41   | AC     |

| 2   | ADR11  | 22  | STOP*         | 42   | AD     |

| 3   | ADR12  | 23  | NMI*          | 43   | AE     |

| 4   | ADR13  | 24  | VI*           | 44   | AF     |

| 5   | ADR14  | 25  | STO           | 45   | AO/DO  |

| 6   | ADR15  | 26  | ST1           | 46   | A1/D1  |

| 7   | NVI*   | 27  | ST2           | 47   | A2/D2  |

| 8   | INH*   | 28  | ST3           | 48   | A3/D3  |

| 9   | AS*    | 29  | A0            | 49   | A4/D4  |

| 10  | DS*    | 30  | A1            | 50   | A5/D5  |

| 11  | R/W*   | 31  | A2            | 51   | A6/D6  |

| 12  | SEGT*  | 32  | A3            | 52   | A7/D7  |

| 13  | N/S*   | 33  | A4            | 53   | A8/D8  |

| 14  | B/W*   | 34  | A5            | 54   | A9/D9  |

| 15  | BUSRQ* | 35  | A6            | 55   | AA/DA  |

| 16  | BUSAK* | 36  | A7            | 56   | AB/DB  |

| 17  | GND    | 37  | A8            | 57   | AC/DC  |

| 18  | GND    | 38  | A9            | 58   | AD/DD  |

| 19  | RST*   | 39  | AA            | 59   | AE/DE  |

| 20  | WAIT*  | 40  | AB            | 60   | AF/DF  |

TABLE 2-6. P3 CONNECTOR PINS

| SOL | DER 9 | SIDE  |      | СОМРО | NENT | SIDE |

|-----|-------|-------|------|-------|------|------|

| 1   | PB7   | (Port | FF1) | 2     | GND  |      |

| 3   | PB6   |       |      | 4     | GND  |      |

| 5   | PB5   |       |      | 6     | GND  |      |

| 7   | PB4   |       |      | 8     | GND  |      |

| 9   | PB3   |       |      | 10    | GND  |      |

| 11  | PB2   |       |      | 12    | GND  |      |

| 13  | PB1   |       |      | 14    | GND  |      |

| 15  | PB0   |       |      | 16    | GND  |      |

| 17  | PC3   | (Port | FF2) | 18    | GND  |      |

| 19  | PC2   |       |      | 20    | GND  |      |

| 21  | PC1   |       |      | 22    | GND  |      |

| 23  | PCO   |       |      | 24    | GND  |      |

| 25  | PC4   |       |      | 26    | GND  |      |

| 27  | PC5   |       |      | 28    | GND  |      |

| 29  | PC6   |       |      | 30    |      |      |

| 31  | PC7   |       |      | 32    | GND  |      |

| 33  | PA7   | (Port | FFO) | 34    | GND  |      |

| 35  | PA6   |       |      | 36    |      |      |

| 37  | PA5   |       |      | 38    | GND  |      |

| 39  | PA4   |       |      | 40    | GND  |      |

| 41  | PA3   |       |      | 42    | GND  |      |

| 43  | PA2   |       |      | 44    | GND  |      |

| 45  | PA1   |       |      | 46    | GND  |      |

| 47  | PA0   |       |      | 48    | GND  |      |

| 49  | N/C   |       |      | 50    | GND  |      |

TABLE 2-7. P4 CONNECTOR PINS

| SOLD | ER SIDE | COMPONENT SIDE |                 |  |

|------|---------|----------------|-----------------|--|

| _    | GND     | 2              | KEYBOARD DETECT |  |

| 3    | CTL     | 4              | SHIFT           |  |

| 5    | RO      | 6              | R1              |  |

| _    | R2      | 8              | SO              |  |

| 9    | S1      | 10             | S2              |  |

|      |         |                |                 |  |

| 11   | PFCO*   | 12             | PFC4*           |  |

| 13   | PFC8*   | 14             | PFCC*           |  |

| 15   | PFDO*   | 16             | Α0              |  |

| 17   | A1      | 18             | IDO             |  |

| 19   | ID1     | 20             | ID2             |  |

| 21   | I:D3    | 22             | ID4             |  |

| 23   | I.D5    | 24             | ID6             |  |

| 25   | GND     | 26             | <b>+</b> 5V     |  |

TABLE 2-8. P5 CONNECTOR PINS

|                                                                       | SOLDER SIDE                                                                                                                  | (RS232)                                | COMPONENT SIDE                                                                                            | (RS232) |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------|

| 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23<br>25 | CHASSIS GND TRANSMITTED DATA RECEIVED DATA REQUEST TO SEND CLEAR TO SEND DATA SET READY SIGNAL GND N/C N/C N/C N/C CLKO OUTO | (2)<br>(3)<br>(4)<br>(5)<br>(6)<br>(7) | 2 N/C 4 N/C 6 N/C 8 N/C 10 N/C 12 N/C 14 DATA TERM RDY 16 N/C 18 N/C 20 N/C 22 N/C 24 GATEO 26 SIGNAL GND | (20)    |

TABLE 2-9. P6 CONNECTOR PINS

|                       | SOLDER SIDE                                                                             | (RS232)                                      |                              | COMPONENT SIDE                                     | (RS232) |

|-----------------------|-----------------------------------------------------------------------------------------|----------------------------------------------|------------------------------|----------------------------------------------------|---------|

| 1<br>3<br>5<br>7<br>9 | CHASSIS GND TRANSMITTED DATA RECEIVED DATA REQUEST TO SEND CLEAR TO SEND DATA SET READY | ( 1)<br>( 2)<br>( 3)<br>( 4)<br>( 5)<br>( 6) | 2<br>4<br>6<br>8<br>10<br>12 | N/C<br>N/C<br>TTY RDR CONTROL<br>N/C<br>N/C<br>N/C | (16)    |

| 13                    | SIGNAL GND                                                                              | (7)                                          | 14                           | DATA TERM RDY                                      | (20)    |

| 15                    | DATA CARRIER RTN                                                                        | (8)                                          | 16                           | TTY RDR CONTROL RTN                                | (21)    |

| 17                    | N/C                                                                                     |                                              | 18                           | N/C                                                |         |

| 19                    | N/C                                                                                     |                                              | 2.0                          | N/C                                                |         |

| 21                    | N/C                                                                                     |                                              | 22                           | TTY RX TRN                                         | (24)    |

| 23                    | TTY RX                                                                                  | (12)                                         | 24                           | TTY TX RN                                          | (25)    |

| 25                    | TTY TX                                                                                  | (13)                                         | 26                           | SIGNAL GND                                         | ·       |

# PROTOTYPING AND MEMORY-EXPANSION BOARDS

Prototyping and memory-expansion boards can be connected to the CPU bus via P2. AMC offers the following optional products to accommodate these functions:

- Universal Prototyping Board for Multibus (Am96/9410)

- 64-kilobyte dynamic RAM board for standard Multibus and Evaluation Board with AmZ8002 (Am96/1064) or 128 kilobytes RAM (Am96/1128) for the AmZ8001.

- Three-board backplane for P2 edge connector (Am96/4016/400).

- Six-board Multibus-compatible card cage with cooling fan (Am95/6440). A card cage with power supplies is also available (Am95/6448)

Prototyping boards can contain any type of circuitry, including circuits that capture the system buses. The AmZ8002 bus is described further in the section entitled Principles of Operations.

Expansion memory can be of any type compatible with the available pins and the buffered electrical characteristics at P2 (see appendix A). Dynamic-memory refresh may be done on the external board or it may use the CPU refresh cycle, as does the on-board RAM. This is accomplished by decoding the AmZ8000 status lines, available on the P2 bus.

The 64K and 128K RAM board supplied by AMC are compatible with both the Evaluation Board (on P2), and with standard Multibus slave applications (on P1). Due to this dual use, dynamic refresh is handled on the memory board itself rather than relying on the AmZ8002. The P2 connector of the memory board supports 24 address bits whereas its P1 connector supports 20 bits.

# **DEVELOPMENT SYSTEM INTERCONNECTION**

When a 16-bit Development System is used, P3 of the Evaluation Board is connected to P4 of the Development System's CPU board as illustrated in figure 2-2. A cable (Am96/4016/500) for connecting P3 to P4 is available from AMC. Alternatively, a cable can be fabricated by using two Scotchflex card edge connectors (3M part #3415-0001) and one foot of Scotchflex flat cable (3M part #3306/50).

A diskette-based program named GHOST is supplied with the Development System for communication between the Development System and the Evaluation Board. Execution of this utility on the Development System allows Evaluation Board operations to be controlled through the Development-system console.

The Development System can be used for programming work simultaneously with execution of programs on the Evaluation Board. The Pl bus serves the Development System while the P2 bus serves the Evaluation Board. In this case, separate consoles may be needed. However, communication or transfers between the Evaluation Board and the Development System require the GHOST program to be in execution.

#### **JUMPER OPTIONS**

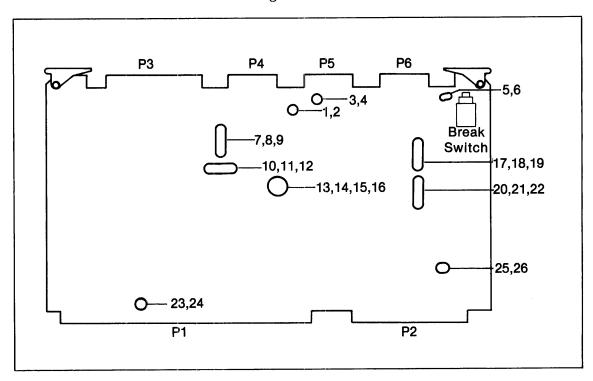

Several jumpers, illustrated in figure 2-4, can be connected to modify the standard functions of the Evaluation Board. There is a Break switch for regaining CPU control, two jumpers for grounding external I/O devices to the board, one for timing an external device, one for selecting RS232C or TTY serial interface, one for enabling an initialization line, one for enabling an inhibit line, and one for disabling the memory-cycle Wait state.

The jumper configuration when the board is shipped is as follows: 8-9, 11-12, 18-19, 21-22, and 23-24. Wire-wrapping between the jumper posts will affect the board's functions as described below.

BREAK SWITCH - When pressed, it asynchronously generates a non-maskable interrupt (NMI\*) to the CPU, which forces control back to the Monitor program. This circuit is connected via jumpers 18 and 19. If the NMI\* line on P2 is to be used, the Break switch must be disabled by removing jumper 18 and 19, and placing a jumper between 17 and 18.

- When jumpered, it connects the 2MHz clock (4MHz Jumper 1,2 divided by 2) to counter 0 of the Am8253 counter/ timer circuit, instead of using the external clock via P5.

- Jumper 3,4 - When jumpered, it connects the chassis ground of the external serial I/O device at P5 to the Evaluation-Board ground.

- Jumper 5,6 - When jumpered, it connects the chassis ground of the external serial I/O device at P6 to the Evaluation-Board ground.

- Jumper 8,9 - Must be jumpered for Z8002 CPU. For Z8001 CPU. jumper 7 and 8 instead.

- Jumper 11,12 - Must be jumpered for Z8002 CPU. For Z8001 CPU, jumper 10 and 11 instead.

- Jumper 14,15,16,17 Used by the Monitor to determine baud rate at P6 as follows:

9600 baud - all open

2400 baud - connect 14 to 17

300 baud - connect 15 to 16

110 baud - connect 14 to 17

and 15 to 16

- Jumper 18,19 - These jumpers enable the Break switch. If NMI\* is used, at P2, connect jumper between 17 and 18 instead.

- Must be jumpered for Z8002 CPU. Jumper 21,22 For Z8001 CPU, jumper 20 and 21 instead.

- Jumper 23,24 - When jumpered, it enables pin 14 on the Pl Multibus connector to be an INIT\* input. When the INIT\* line is low, it resets the CPU, USARTs, and parallel I/O circuit.

Jumper 25,26 - Wh

- When jumpered, it connects the OUTO/ output of the Am8253 at P5 to the NVI\* line, thereby generating periodic non-vectored interrupts.

RS232/20mA (P6)

The Evaluation Board is shipped with the local console I/O port configured for RS232C. To configure for use with a 20mA current-loop terminal, refer to figure C-6.

Figure 2-4. Jumper Option

# **CHAPTER 3**

## PERIPHERAL PROGRAMMING

#### PARALLEL I/O

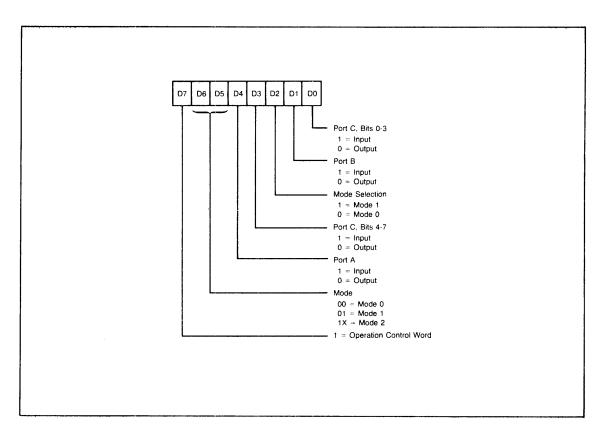

The Am8255A provides three 8-bit parallel I/O ports into or out of the lower eight lines of the internal data bus. In the standard Evaluation Board configuration, the three ports (A, B and C) are used for up/down program loading and remote console control from the 16-bit Development Systems. Port A is used for data output to the Development System, port B for data input, and port C for software-controlled handshaking (4 bits in, 4 bits out).

During power-up initialization, the Monitor writes an 8-bit Operation Control Word to the Am8255A control register for this purpose. In addition, a Bit Set/Reset handshaking byte is written to the same I/O address by the Monitor for each byte of data sent to port A. The port C lines are read for a response from AmSYS 8/8.

For non-standard uses of the P3 edge connector, the 8-bit Operation Control Word must be rewritten after initialization by the Monitor. There are three modes of operation possible:

- Mode 0 Basic input or output without strobed handshaking (but allowing software handshake routines). Ports A and B are 8 bits each and port C consists of two 4-bit ports. Any port can be input or output. Outputs are latched; inputs are not. In the standard Evaluation Board, the Am8255A is initialized in this mode.

- Mode l Input or output in conjunction with strobed handshaking signals. Port A consists of 8 data lines in conjunction with the upper four handshake lines of port C. Port B is similar but uses the lower four lines of port C for handshake. All data lines are latched, whether input or

- Mode 2 Bidirectional data transfers on the eight lines of port A, controlled by the upper five monodirectional lines of of port C. Port A is latched on both input and output. The lower three lines of port C and the eight eight lines of port B are monodirectional input or output data lines.

The form of the 8-bit Operation Control Word is shown in figure 3-1.

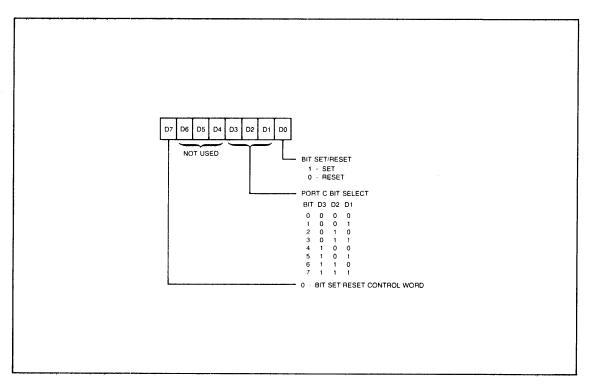

Port C contains an 8-bit output latch/buffer and an 8-bit input buffer (no latch). Any of the output bits can be set or reset with an output instruction to the same address according to the 8-bit Bit Set/Reset Control Word shown in figure 3-2.

After initialization, data or control bytes can be transferred at ports A, B and C using the I/O addresses shown in table 3-1.

Figure 3-1. Am8255A Operation Control Word Format

Figure 3-2. Am8255A Bit Set/Reset Control Word Format

TABLE 3-1. Am8255A ADDRESSES

| Port | Data | Control |

|------|------|---------|

| A    | FF0  | FF3     |

| В    | FF1  | FF3     |

| С    | FF2  | FF3     |

The six 14-pin sockets provided for drivers and terminators between the Am8255A and the P3 edge connector limit the use of all three ports to either input or output. Bi-directional capability, which is normally possible with port A in Mode 2 is not possible, with the drivers used with the Evaluation Board. However, if there is only a short distance between the P3 edge connector and the external device, the driver/terminator sockets can be shorted with headers and jumpers to use the bi-directional capability of port A.

#### SERIAL I/O

Two Am9551 USARTs provide full-duplex serial transmission between the lower eight lines of the internal data bus and the P5 and P6 edge connectors. Both the transmitter and receiver clock inputs to these circuits come from the Am8253 counter/timer.

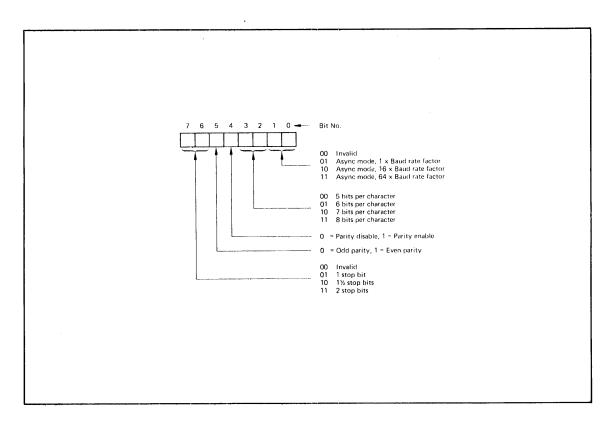

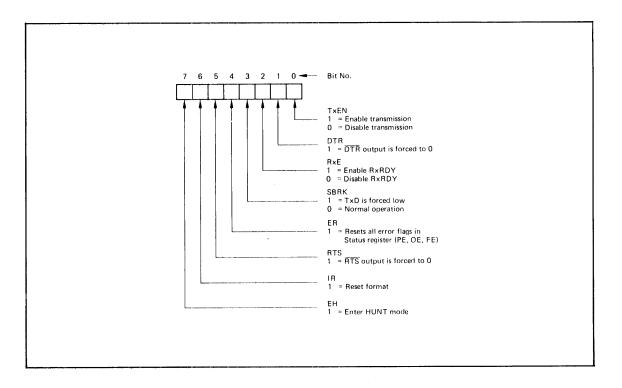

In the standard Evaluation Board configuration, the Am9551 at P6 (U42) is initialized by the Monitor with control bytes at power-up, independently of whether the ports are jumpered for RS232C or 20mA compatibility. The devices are configured for 8-bit asynchronous characters with two stop bits, parity disabled and 16x baud rate factor. They are also enabled for transmission and reception, with the Request-To-Send line forced active and without Hunt Mode. This is accomplished by first writing a hex CE Mode Control Code to I/O addresses FE9H and FEDH, followed by a hex 27 Control Command to the same address (11001110 followed by 00100111). The format for the Asynchronous Mode Control Code is shown in figure 3-3. The format for the Control Command that follows is shown in figure 3-4.

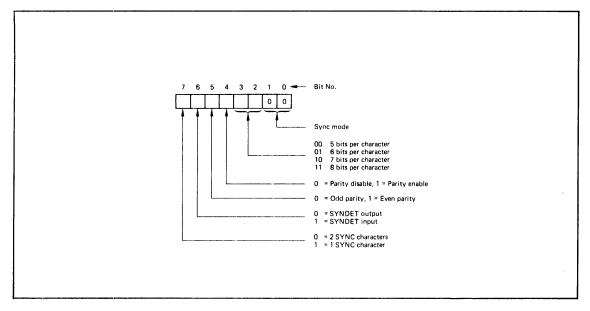

Synchronous transmission/reception is obtained by first writing a Synchronous Mode Control Code followed by one or two 8-bit sync characters, followed by the same Control Command format illustrated above. The format for the Synchronous Mode Control Code is shown in figure 3-5.

If you wish to change the Monitor's initialization of the P6 USART after power-up, or if you intend to use the P5 USART, the following steps are recommended:

- 1. Write three successive null bytes to the control port (FE9H for P6 or FEDH for P5).

- 2. Write a hex 40 to the port for a software reset.

- 3. Initialize the device by writing new control information as described above.

- 4. Execute a dummy Read to clear data in buffer and RxRDY line.

After initialization, data can be transferred using the I/O addresses shown in table 3-2.

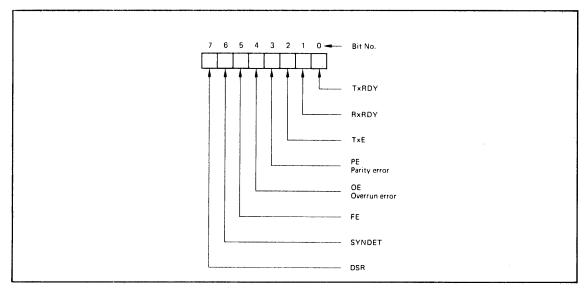

A readable status register maintains information on the current operational status of the device. Its format is shown in figure 3-6.

The definition of the status bits is as follows:

TxRDY Transmitter Ready indicates the Am9551 is ready to accept a data character or command.

RxRDY Receiver Ready indicates the Am9551 has received a character on its serial input and is ready to transfer it to the CPU.

TxE Transmitter Empty signals the processor that the transmit register is empty.

PE Parity Error indicates the character stored in the receiver character buffer was received with an incorrect number of binary 1 bits.

OE Overrun flag is set when a byte stored in the receiver character register is overwritten with a new byte before being transferred to the processor.

FE Framing Error indicates the asynchronous mode byte stored in the receiver character buffer was received with incorrect character bit format.

SYNDET When Sync Detect is set for internal sync detect, this bit indicates character sync has been achieved and the Am9551 is ready for data.

After initialization, always check the status of the TxRDY bit prior to writing data or a new command word to the Am9551. The TxRDY bit must be true to prevent overwriting and subsequent loss of commands or data. The TxRDY is inactive until initialization has been completed.

Figure 3-3. Am9551 Asynchronous Mode Control Code

Figure 3-4. Am9551 Control Command

TABLE 3-2. Am9551 ADDRESSES

| PORT | DATA        | CONTROL     |

|------|-------------|-------------|

| P5   | FEE#<br>FEC | FEF#<br>FED |

| Р6   | FEA<br>FE8  | FEB<br>FE9  |

Figure 3-5. Synchronous Mode Control Code

Figure 3-6. Am9551 Status Register

#### COUNTER/TIMER

The Am8253 provides three counter/timer channels using a 2MHz clock input derived from the 4MHz CPU clock. Two of the three counter outputs drive the transmit and receive clock inputs of the two Am9551 USARTs up to 9600 baud; counter 1 is attached to the USART at P6, and counter 2 is attached to the USART at P5. The third counter output, together with its associated gate and clock inputs, are available for external use on P5 together with the serial port.

A 16-bit binary counter in each channel counts down at the clock input rate and generates a signal when reaching zero. Alternatively, a 4-decade BCD counter can be used.

There are five modes associated with the manner in which signals are output:

#### Mode 0 - Interrupt on terminal count

The output will be initially low after the mode set operation. After the count is loaded into the selected count register, the output will remain low and the counter will count. When terminal count is reached, the output will go high and remain high until the selected count register is reloaded with the mode.

Reloading a counter register during counting results in the following:

- (1) Write 1st byte stops the current counting.

- (2) Write 2nd byte starts the new count.

The GATE input will enable the counting when high and inhibit counting when low.

#### Mode 1 - Programmable One-Shot

The output will go low on the count following the rising edge of the GATE input.

The output will go high on the terminal count. If a new count value is loaded while th output is low it will not affect the of the one shot pulse until the succeeding trigger. The current count can be read at any time without affecting the one-shot pulse.

The one-shot is retriggerable, hence the output will remain low for the full count after any rising edge of the gate input.

#### Mode 2 - Rate Generator

Divide by N counter. The output will be low for one period of the input clock. The period from one output pulse to the next equals the number of input counts in the count register. If the count register is reloaded between output pulses, the present period will not be affected, but the subsequent period will reflect the new value.

The GATE input, when low, will force the output high. When the GATE input goes high, the counter will start from the initial count. Thus, the GATE input can be used to synchronize the counter. When this mode is set, the output will remain high until after the count register is loaded. The output then can also be synchronized by software.

#### Mode 3 - Square Wave Rate Generator.

Similar to Mode 2 except that the output will remain high until one-half the count has been completed (for even numbers) and go low for the other half of the count. If the count is odd, the output will be high for (N+1)/2 counts and low for (N-1)/2 counts.

If the count register is reloaded with a new value during counting, this new value will be reflected immediately after the output transition of the current count.

#### Mode 4 - Software-triggered strobe.

After the mode is set, the output will be high. When the count is loaded, the counter will begin counting. On terminal count, the output will go low for one input clock period, then will go high again.

If the count register is reloaded between output pulses the present period will not be affected, but the subsequent period will reflect the new value. The count will be inhibited while the gate input is low. Reloading the counter register will restart counting beginning with the new number.

#### Mode 5 - Hardware-triggered strobe

The counter will start counting after the rising edge of the trigger input and will go low for one clock period when the terminal count is reached. The counter is retriggerable. The output will not go low until the full count after the rising edge of any trigger.

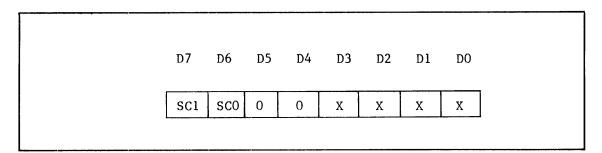

The format of the control byte is shown in figure 3-7; the various bits in the control byte are defined by figure 3-8. Counter 0 is not initialized by the Monitor during power-up. It is available for use at P5 and must be programmed, if used, in the same manner described

above. There are two inputs (clock and gate) and one output available. A jumper is provided on the Evaluation Board for tying the clock input to the same 2MHz clock used in channels 1 and 2.

The current counter values at each channel can be read while actively counting in the following manner: first, the control byte shown in figures 3-7, 3-8, and 3-9, is written to the control register (FE7H) in order to latch the current value. Then the counter is read by addressing it as shown in table 3-3.

| D7  | D6  | D5  | D4  | D3 | D2 | D1 | DO  |

|-----|-----|-----|-----|----|----|----|-----|

| SC1 | sc0 | RL1 | RLO | M2 | м1 | МО | BCD |

Figure 3-7. Am8253 Control Byte Format

TABLE 3-3. Am8253 ADDRESSES

| Counter | Status | Control |

|---------|--------|---------|

| 0       | FE4    | FE7     |

| 1       | FE5    | FE7     |

| 2       | FE6    | FE7     |

| SC1 | S  | CO      |                               |

|-----|----|---------|-------------------------------|

| 0   |    | 0       | Select Counter 0              |

| 0   |    | 1       | Select Counter 1              |

| 1   | (  | 0       | Select Counter 2              |

| 1   |    | 1       | Illegal                       |

|     |    |         |                               |

| RL1 | R  | L0      |                               |

| 0   | 1  | 0       | Counter Latching              |

| 1   |    | 0       | operation Read/Load most sig- |

| 1   | ,  | U       | nificant byte only.           |

| 0   |    | 1       | Read/Load least sig-          |

| Ü   |    | -       | nificant byte only.           |

| 1   |    | 1       | Read/Load least sig-          |

|     |    |         | nificant byte first,          |

|     |    |         | than most significant         |

|     |    |         | byte.                         |

|     |    |         |                               |

| М2  | M1 | МО      |                               |

| 0   | 0  | 0       | Mode 0                        |

| 0   | 0  | 1       | Mode 1                        |

| X   | 1  | 0       | Mode 2                        |

| X   | 1  | 1       | Mode 3                        |

| 1   | 0  | 0       | Mode 4                        |

| 1   | 0  | 1       | Mode 5                        |

|     | 0  | Binary  | Counter 16-bits               |

|     | 1  |         | Coded Decimal (BCD)           |

|     |    | Counter | c (4 Decades)                 |

|     |    |         |                               |

Figure 3-8. Am8253 Control Byte Definition

Figure 3-9. Am8253 Control Byte to Latch Count

# CHAPTER 4

# AmZ:8001 AND AmZ:8002 MONITORS

#### INTRODUCTION

The Monitors provide a basic program development tool for the Am96/4018 Evaluation Board. Two Monitors are available, one for the Am28001 segmented CPU, and one for the Am28002 non-segmented CPU. With the exception of the unique Am28001 modes, both monitors use the same command set. The Monitors provide the following capabilities:

- Memory inspection and modification.

- Display and alteration for all registers, program counter, and flag bits.

- Selection of System or Normal mode.

- Selection of segmented or non-segmented mode (AmZ8001).

- Trace facility and hardware or software breakpoint insertion.

- Saving and Loading programs using an 16-bit (System 8) Microcomputer Development System executing GHOST.

#### **INSTALLATION**

The Am96/4018 Monitors are supplied on four 2716-type E-PROMs. Two devices are for odd addresses, the other two for even address. Table 4-1 lists the part numbers and board locations for installing the E-PROMs.

TABLE 4-1. E-PROM LOCATIONS

| MONITOR | PART NO.      | BOARD LOCATION |

|---------|---------------|----------------|

| AmZ8001 | 002510682-001 | U23(Even)      |

| AmZ8001 | 002510682-002 | U20(Odd)       |

| AmZ8001 | 002510682-003 | U17(Even)      |

| AmZ8001 | 002510682-004 | U12(Odd)       |

| AmZ8002 | 002510683-001 | U23(Even)      |

| AmZ8002 | 002510683-002 | U20(Odd)       |

| AmZ8002 | 002510683-003 | U17(Even)      |

| AmZ8002 | 002510683-004 | U12(Odd)       |

Interface with the Monitor is through a standard RS232C or 20mA current loop terminal connected to connector P6. The Keyboard/Display console designed for the Evaluation Board connects to connector P4. An

Development System, executing GHOST, can also be used through either connector P3 (parallel) or P5 (serial). Figure 4-1 is a memory map of the evaluation board.

When power is supplied to the Am96/4018, the Monitor initializes all ports, and outputs ENTER ANY KEY to all I/O ports. The message is repeated every five seconds until the Monitor receives a response through one of the I/O ports. The port that receives the first character becomes the control port. An identification message and prompt is then output to the control port:

AMZ800x EVALUATION BOARD MONITOR V1.0 ->

Where AMZ800x can be either AMZ8002 or AMZ8001.

### **MONITOR COMMANDS**

Command mode directives are specified in the following manner:

- All commands are specified with alphabetic characters followed by arguments described in the following pages.

- The alphabetic command can be followed by a space or no space, and the arguments separated by commas only.

- Address parameters can be 1 to 4 hex digits for the AmZ8002 Monitor (FFFF hex), and 1 to 6 hex digits for the AmZ8001 Monitor (3FFFFF Hex). Data parameters for both Monitors can be 1 to 4 hex digits.

- Arguments enclosed in brackets [ ] are optional.

- A Carriage Return <CR>> must end each command input line.

When a command is not recognized by the Monitor, or the command parameters do not conform to the required format, the Monitor responds with a question mark (?). Table 4-2 is a summary of the Monitor commands.

The backspace character <CTRL-H> can be used to erase the current character on a line. Escape <ESC> can be used to erase entire current command line. In all examples of Monitor command usage, the user input is underlined, to distinguish it from Monitor response.

#### KEYBOARD/DISPLAY CONSOLE

Since the optional Keyboard/Display console has only a single 20-character display, certain of the commands produce a display different from that on a standard CRT console. In particular, the Help

Figure 4-1. Memory Address

command does not output a list of available commands. Also, the Save commands cannot display the entire address parameters as they are typed in, but will function properly if given the required data. The X (Register display) command outputs program counter address, and next instruction data only. The XF command is two displays, where <CR> is used to move from display to display and back to command mode. To clear Monitor displays, enter a <CR>. Entry of an <ESC> character will clear the Line-by-Line Assembler display. Entry of an <ESC> character always cancels the current command line.

TABLE 4-2. MONITOR COMMAND SUMMARY

| COMMAND FORMAT                                                                                        | FUNCTION                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASM                                                                                                   | Calls the Line-by-line Assembler                                                                                                                                |

| В                                                                                                     | Displays and permits setting or clear-<br>ing up to three software breakpoints.                                                                                 |

| D <start-addr>,<end-addr></end-addr></start-addr>                                                     | Displays the contents of memory from <start-addr> through <end-addr>.</end-addr></start-addr>                                                                   |

| E                                                                                                     | Displays and permits setting one hard-<br>ware breakpoint.                                                                                                      |

| F <start-addr>,<end-addr>, <data></data></end-addr></start-addr>                                      | Fills memory from <start-addr> through <end-addr> with 16-bit value of <data>.</data></end-addr></start-addr>                                                   |

| <pre>G [<execute-addr>] [,<stop-addr>]</stop-addr></execute-addr></pre>                               | Execute program beginning at <execute-addr>.</execute-addr>                                                                                                     |

| Н                                                                                                     | Help. Displays a list of commands available with Monitor.                                                                                                       |

| I [ <port-addr>]</port-addr>                                                                          | Input one word of data from I/O port at <port-addr>.</port-addr>                                                                                                |

| LOADP (n:)filename.typ                                                                                | Load a file from host computer using the parallel I/O port.                                                                                                     |

| LOADS (n:)filename.typ                                                                                | Load a file from host computer using the serial I/O port.                                                                                                       |

| M <start-addr>,<end-addr>, <new-addr></new-addr></end-addr></start-addr>                              | Move contents of memory from <start-addr> through <end-addr>, to new location at <new-addr>.</new-addr></end-addr></start-addr>                                 |

| NM                                                                                                    | Set CPU Normal Mode.                                                                                                                                            |

| 0 [ <port-addr>],<data></data></port-addr>                                                            | Output one word of <data> to I/O port at <port-addr>.</port-addr></data>                                                                                        |

| P                                                                                                     | Displays and permits setting the user Program Counter.                                                                                                          |

| R n (n=0 to 15 decimal)                                                                               | Displays and permits altering the contents of registers 0 through 15.                                                                                           |

| SAVEP (n:)filename[.BIN] <start-addr>,<end-addr> [,<entry-addr>]</entry-addr></end-addr></start-addr> | Save contents of memory from<br><start-addr> through <end-addr> as a<br/>file on host computer system, using the<br/>parallel I/O port.</end-addr></start-addr> |

TABLE 4-2. MONITOR COMMAND SUMMARY (continued)

| COMMAND FORMAT                                                                                        | FUNCTION                                                                                                 |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| SAVES (n:)filename[.BIN] <start-addr>,<end-addr> [,<entry-addr>]</entry-addr></end-addr></start-addr> | Same as SAVEP, except uses the serial I/O port.                                                          |

| S <address></address>                                                                                 | Displays and permits alteration of data at <address>.</address>                                          |

| SM                                                                                                    | Set CPU System Mode.                                                                                     |

| T n (n-1 to 65,535 decimal)                                                                           | Trace mode. Permits single-step execution of instructions, with a register display for each instruction. |

| U n (n=1 to 65,535 decima1)                                                                           | Untrace mode. Same as Trace, except n instructions are single-stepped before a register display.         |

| X                                                                                                     | Display of all CPU registers, Program Counter, Next Instruction, and flag bits.                          |

| XF                                                                                                    | Displays Flag and Control Word bits.                                                                     |