Advanced Micro Devices, Inc.

Am95/6120 Dual-Density Floppy Disk Controller

User's Manual

|                 | REVISION RECORD                                              |

|-----------------|--------------------------------------------------------------|

| REVISION        | DESCRIPTION                                                  |

| 01              | Preliminary Issue                                            |

| (7/1/80)        |                                                              |

| A               | Manual Release                                               |

| (8/15/80)       |                                                              |

| В               | Manual Updated To Incorporate Additional Jumper Information  |

| (3/20/81)       |                                                              |

| С               | Manual Updated To Clarify Information Added By Revision B    |

| (5/15/81)       |                                                              |

| D               | Manual Updated To Correct Documentation Errors And Reprinted |

| (9/30/81)       |                                                              |

| E               | Manual Updated to Reflect Parameter Changes and Reprinted.   |

| (11/1/82)       |                                                              |

|                 |                                                              |

|                 |                                                              |

|                 |                                                              |

|                 |                                                              |

|                 |                                                              |

|                 | •                                                            |

|                 |                                                              |

|                 |                                                              |

|                 |                                                              |

|                 |                                                              |

| Out tienting Na |                                                              |

| Publication No. | Address comments concerni                                    |

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1982 Advanced Micro Devices Printed in U.S.A.

059901341-001

Address comments concerning this manual to:

ADVANCED MICRO DEVICES Microcomputer Systems Publications Department P.O. Box 453 Sunnyvale, CA 94086

# PREFACE

This manual provides general information, an installation and interface guide, and programming information for the Advanced Micro Computer, Am95/6120 Flexible Disk Controller board. Additional information can be obtained from the following documents.

| Western Digital Corporation | FD1793 X-01 | Data Sheet       |

|-----------------------------|-------------|------------------|

|                             | FD1793 X-01 | Application Note |

|                             |             |                  |

| Advanced Micro Devices      | Am9517      | Data Sheet       |

|                             | Am9517      | Application Note |

|                             | Am9085      | Data Sheet       |

|                             |             |                  |

| Shugart Associates          | SA800/801   | OEM Manual       |

This manual is intended for use by systems engineering and programming personnel. A minimum of tutorial information is included. Standard abbreviations and acronyms are used in the text.

Both active-high (positive true) and active-low (negative true) signals are discussed. To eliminate confusion and simplify the notation, the following signal convention is used. Whenever a signal is active-low, its mnemonic is followed by an asterisk (\*). For example, MEMR\* denotes an active-low signal. Active-high signals are denoted without the asterisk.

Hexadecimal numbers are noted in this manual with a starting numeral and a final letter H. For example, OFF3H or 123H are hexadecimal numbers.

The information in this manual is believed to be accurate and complete at the time it was printed. However, AMC reserves the right to change specifications without notice. No responsibility is assumed for errors that might appear in this manual. No part of this manual may be copied or reproduced in any form without prior written permission from AMC.

# TABLE OF CONTENTS

| 1. | General Information1-1         | ·  | Track Zero*2-9                  |

|----|--------------------------------|----|---------------------------------|

|    | *                              |    | Index Pulse*2-9                 |

|    | Introduction1-1                |    | Ready*2-9                       |

|    | Functional Description1-2      |    | Write Gate*2-10                 |

|    | Data Transfer1-2               |    | Write Data*2-10                 |

|    | Communications1-3              |    | Direction (DIRC)2-10            |

|    | Disk Drive Compatibility1-3    |    | Step* (STEP*)2-11               |

|    | Bus Interface1-4               |    | Two Sided*2-11                  |

|    | Firmware1-4                    |    | Read Data*2-11                  |

|    | Automatic Boot From Disk1-5    |    | Drive Select* (DSO1* -          |

|    | Physical Description1-5        |    | DS04*)2-12                      |

|    | Specifications1-5              |    | Side One*2-12                   |

|    |                                |    | In Use/Motor ON*2-12            |

| _  |                                |    | Head Load*2-12                  |

| 2. | Installation and Interface2-1  |    | Floppy Disk Interface           |

|    |                                |    | Characteristics2-12             |

|    | Introduction2-1                |    |                                 |

|    | Unpacking and Inspection2-1    |    |                                 |

|    | Pre-Installation Option        | _  |                                 |

| ٠. | Selection2-1                   | 3. | Operation and Programming3-1    |

| ٠  | Board Select Switches2-1       |    |                                 |

|    | Interrupt Selection2-2         |    | Introduction3-1                 |

|    | Power Up Host Reset2-3         |    | Board Configuration3-1          |

|    | 16-Bit Board Select2-3         |    | Firmware Description3-1         |

|    | Autoboot ON Reset2-3           |    | Firmware Invocation3-2          |

|    | Memory Disable2-3              |    | Programming Information3-3      |

|    | Limited Master Mode2-4         |    | Mail Box Registers3-3           |

|    | Minifloppy Compatibility2-4    |    | Unit Code3-5                    |

|    | VCO Test2-4                    |    | Track Select Code3-7            |

|    | 9085 Not Ready2-4              |    | Sector Select Code3-8           |

|    | Head Stepping Rate2-4          |    | Memory Addressing3-8            |

|    | System Interrupt Selection2-4  |    | Command Code3-9                 |

|    | Installation2-5                |    | Status Byte3-9                  |

|    | System Interface2-5            |    | Command Descriptions3-9         |

|    | Bus Interface2-5               |    | Home Command3-10                |

|    | Address (ADRO* Through         |    | Set Parameters Command3-12      |

|    | ADR13*)2-5                     |    | INTERROGATE Status Command3-12  |

|    | Data (DATO* Through DATF*)2-7  |    | Clear Interrupt Command3-13     |

|    | Interrupt Request Lines        |    | Initialize Disk Command3-13     |

|    | (INTO* Through INT7*)2-7       |    | Sense Status 1 Command3-14      |

|    | Initialization (INIT*)2-7      |    | Sense Status 2 Command3-16      |

|    | Input/Output Read Command      |    | Board Reset Command3-20         |

|    | (IORC*)2-7                     |    | READ DISK Command3-20           |

|    | Memory Read Command (MRDC*)2-7 |    | WRITE DISK Command3-21          |

| •  | Memory Write Command           |    | SPECIAL EXECUTE Command3-22     |

|    | (MWTC*)2-8                     |    | Programming Applications3-22    |

|    | Transfer Acknowledge           |    | Power-ON/Reset3-23              |

|    | (XACK*)2-8                     |    | Limited Master Mode3-25         |

|    | Floppy Disk Drive Interface2-8 |    | Typical Command Sequence3-26    |

|    | Track Greater Than 432-8       |    | Component Level Programming3-27 |

|    | Write Protect*2-8              |    | Am9085A Microcomputer3-28       |

|   | Multimode Direct Memory                    | 5.           | 26     | ervice information5-1            |

|---|--------------------------------------------|--------------|--------|----------------------------------|

|   | Access (DMA) Controller                    |              |        |                                  |

|   | Am9517A3-28                                |              | Se     | ervice and Repair Assistance5-1  |

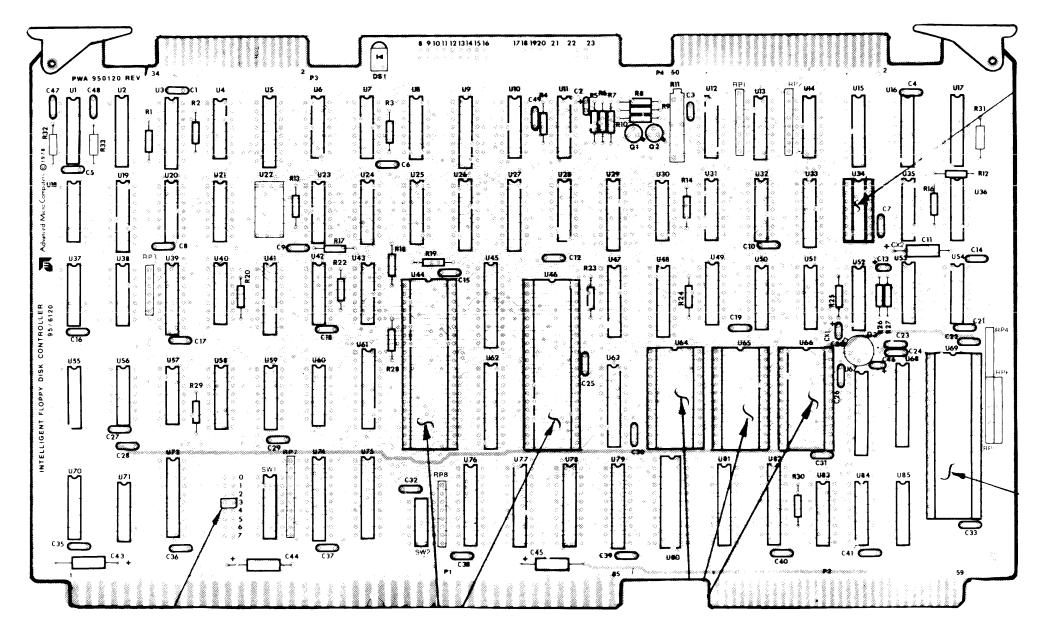

|   | Single Transfer Mode3-28                   |              | Co     | omponents Locations5-2           |

|   | Block Transfer Mode3-28                    |              | Ma     | aintenance5-2                    |

|   | Addressing3-28                             |              | Te     | est Points5-2                    |

|   | Pogistons 3-29                             |              | •      | Edge Connector Contact           |

|   | Registers3-29                              |              |        | Maintannes 5 2                   |

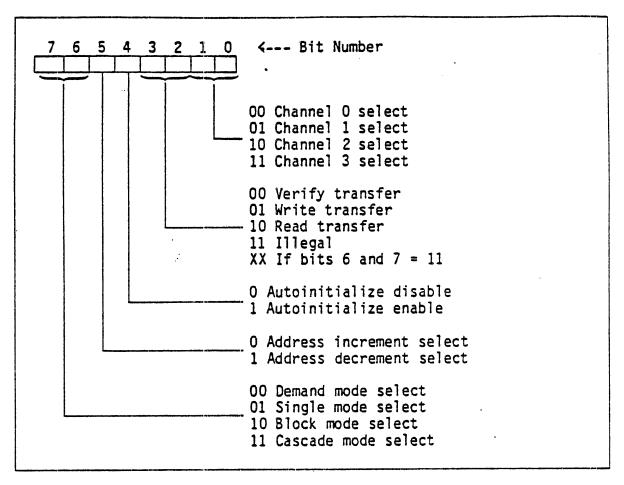

|   | Command Register3-29                       |              |        | Maintenance5-2                   |

|   | Mode Register3-29                          |              |        | VCO Adjustment5-2                |

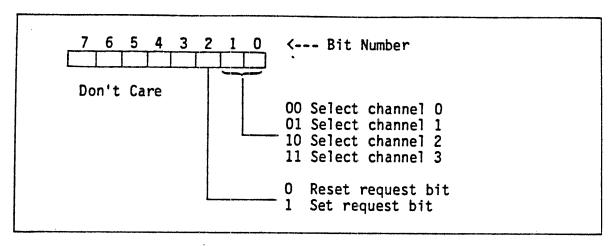

|   | Request Register3-30                       |              |        | Service Diagrams5-2              |

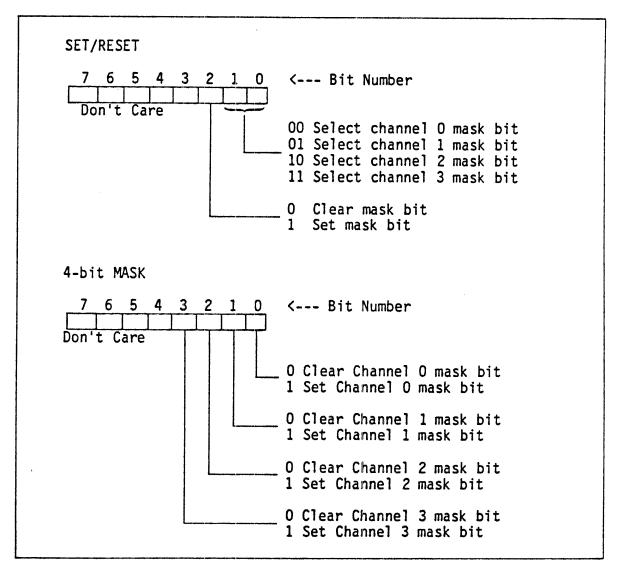

|   | Mask Register3-30                          |              |        |                                  |

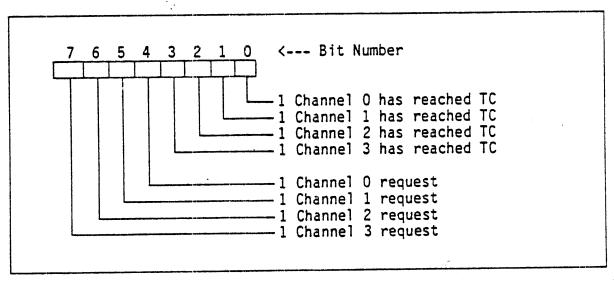

|   | Status Register3-33                        |              |        |                                  |

|   | Temporary Register3-33                     | FIG          | JRE    | ES                               |

|   | Software Commands3-33                      |              |        |                                  |

|   | Clear First/Last Flip-Flop3-34             | 1-1          | _      | Mailbox Registers1-3             |

|   | Master Clear3-34                           | 3-1          |        | Mailbox Registers3-4             |

|   |                                            | 3-1          |        | Unit Code3-5                     |

|   | Floppy Disk Formatter/                     |              |        |                                  |

|   | Controller FD17933-34                      | 3-3          |        | Track Select Code3-7             |

|   | Processor Interface3-35                    | 3-4          |        | Sector Select Code3-8            |

|   | Floppy Disk Interface3-35                  | 3-5          |        | Memory Addressing3-9             |

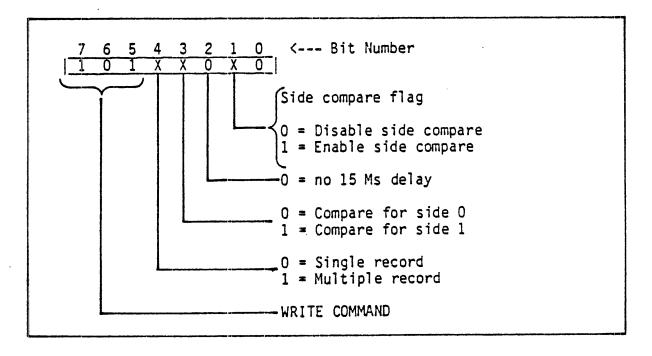

|   | Command Description3-36                    | 3 <b>-</b> 6 | •      |                                  |

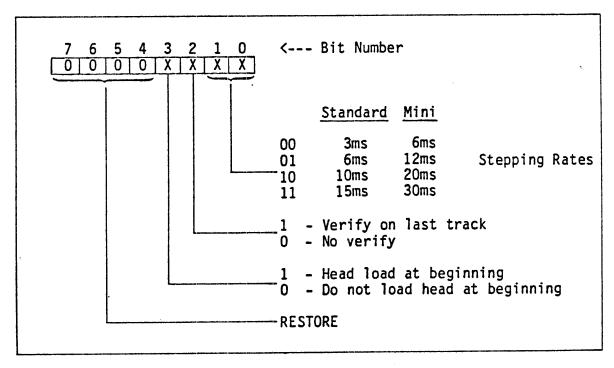

|   | Restore (SEEK Track 0)3-36                 | 3-7          | •      | Status Byte3-11                  |

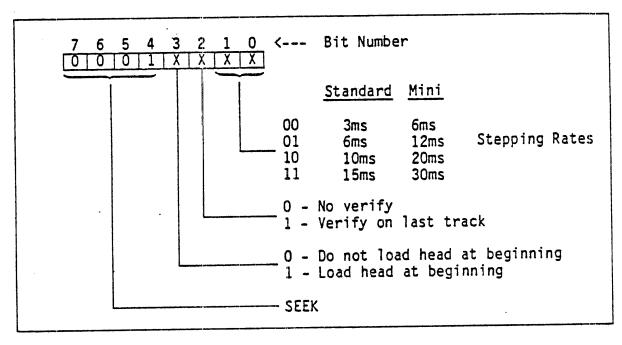

|   | SEEK3-37                                   | 3-8          |        |                                  |

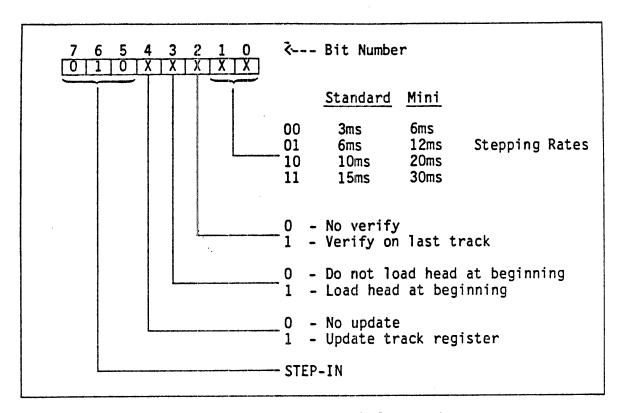

|   | Step-In3-37                                | 3-9          |        |                                  |

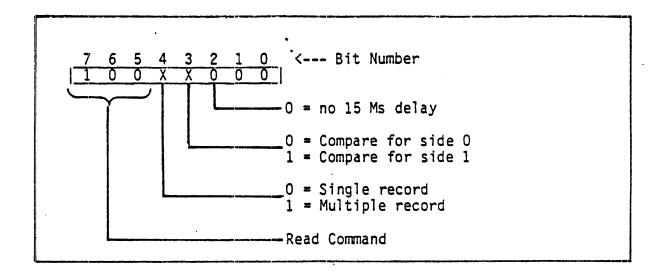

|   | Read3-37                                   |              |        | Am9517 Command Register3-30      |

|   | Write3-38                                  | 3_1          | 1      | Am9517 Mode Register Bit         |

|   | Willessessessessessessessessessessessesses | 3-1.         | ٠.     | Assignments3-31                  |

|   | Write Track3-40                            | 2 1          | ~      | #5519HHEHU5 2.22                 |

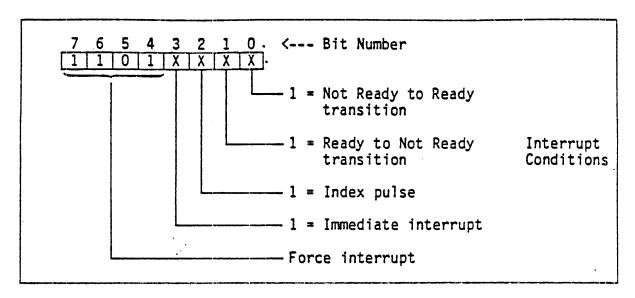

|   | Force Interrupt3-40                        | 3-14         | ۲.     | Am9517 Request Register3-32      |

|   | Status Register3-40                        | 3-1.         | ٥.     | Am9517 Mask Register3-32         |

|   |                                            | 3-1          | 4.     | Am9517 Status Register           |

|   |                                            |              |        | Configuration3-33                |

|   |                                            |              |        | FD1793 RESTORE Command3-36       |

|   |                                            | 3-1          | 5.     | FD1793 SEEK Command3-37          |

|   | Theory of Operation4-1                     |              |        | FD1793 STEP-IN Command3-38       |

| • | Theory of operational transfer a           |              |        | FD1793 Read Command3-39          |

|   | Introduction4-1                            | 3_1          | ٥.     | FD1793 WRITE Command3-39         |

|   | Pier Die Die num 4 1                       | 3 2          | ,<br>n | FD1793 FORCE INTERRUPT           |

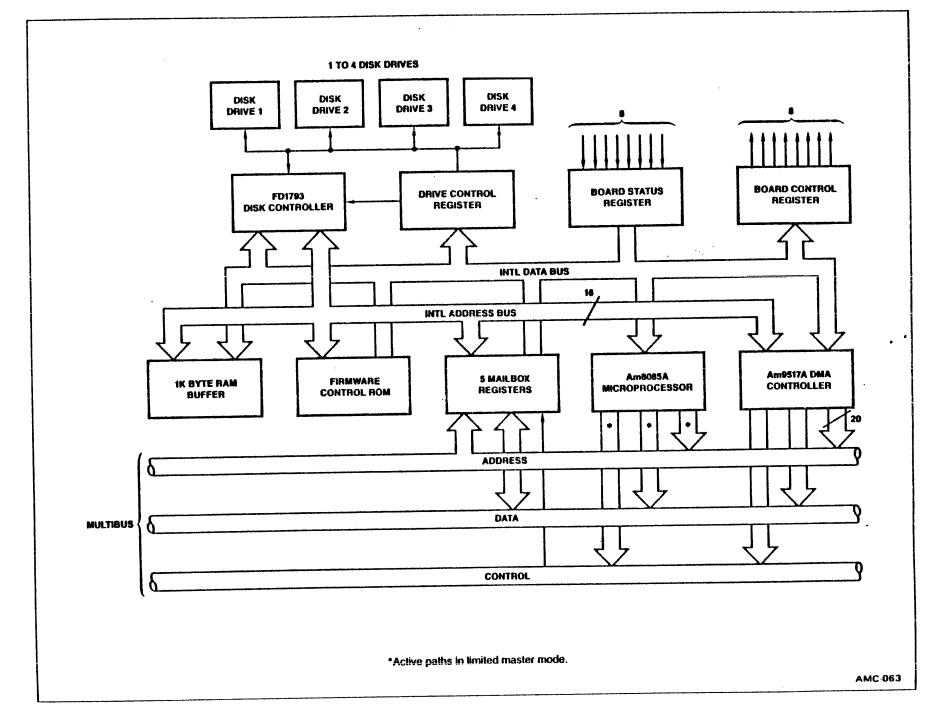

|   | Block Diagram4-1                           | 3-2          | •      | Compand 3-/1                     |

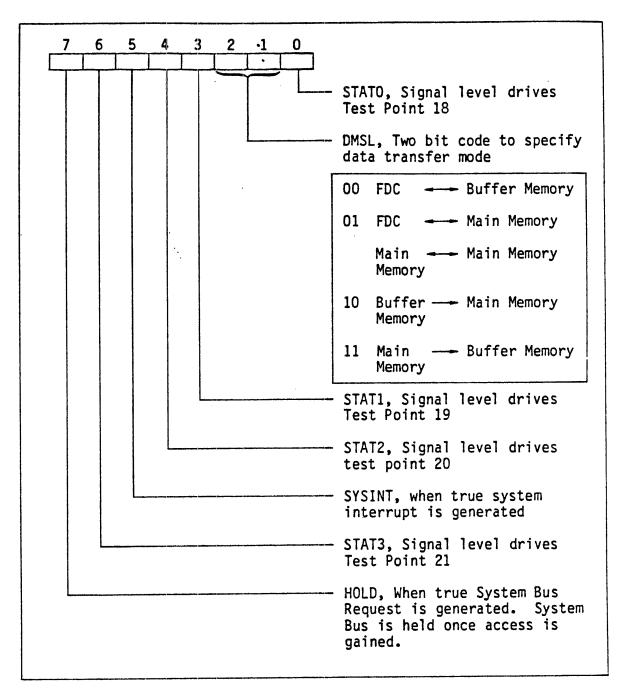

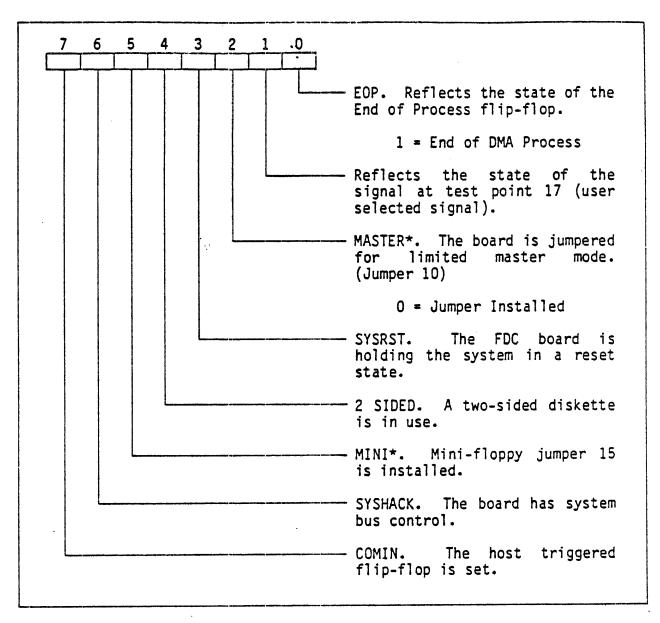

|   | Board Control Register4-1                  | 2.0          | •      | Command3-41                      |

|   | Board Status Register4-1                   |              |        | FD1793 Status Register3-41       |

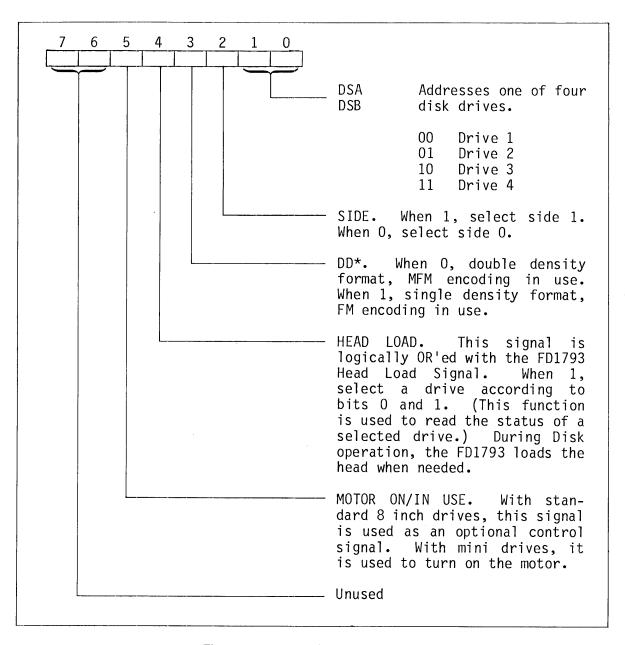

|   | Drive Control Register4-3                  | 4-1          |        | Block Diagram4-2                 |

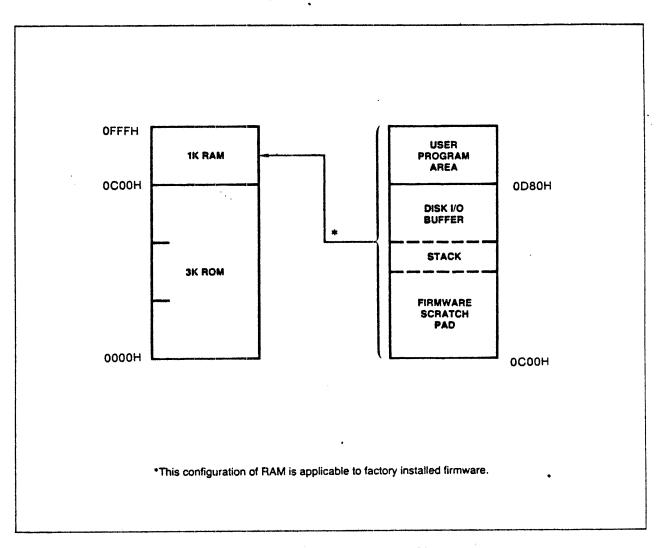

|   | On-Board Memory4-4                         | 4-2          |        | Board Control Register4-3        |

|   | RAM4-4                                     | 4-3          | •      | Board Status Register4-4         |

|   | Firmware ROM4-5                            | 4-4          | •      | Drive Control Register4-5        |

|   | Disk Controller4-5                         | 4-5          |        | On-Board Memory Map4-6           |

|   | FD1793 Floppy Disk                         | 4-6          |        | Phase Lock Loop Block            |

|   | Controller4-6                              | . •          | -      | Diagram (Standard Floppy         |

|   | Diek Drive Intenface                       |              |        | Only)4-7                         |

|   | Disk Drive Interface                       | A 7          |        | Phase Lock Loop Mode Timing. 4-8 |

|   | Circuits4-7                                | 4-7          |        | Company Logations                |

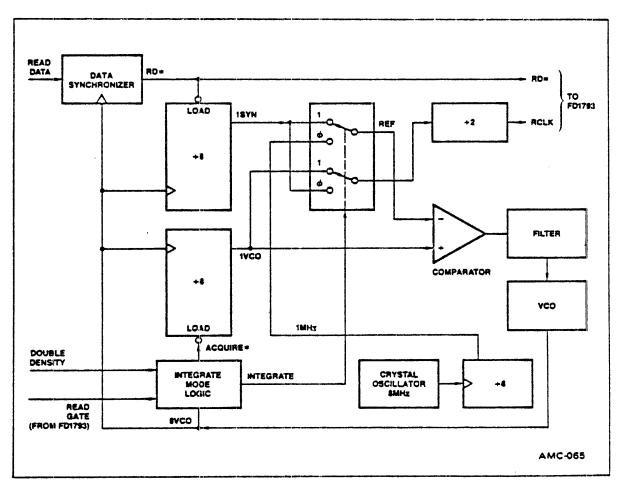

|   | Phase Lock Loop4-7                         | 5-1          |        | Component Locations5-3           |

|   | Mail Box Registers4-8                      | 5-2          | •      | AMC 950120-000 Schematic,        |

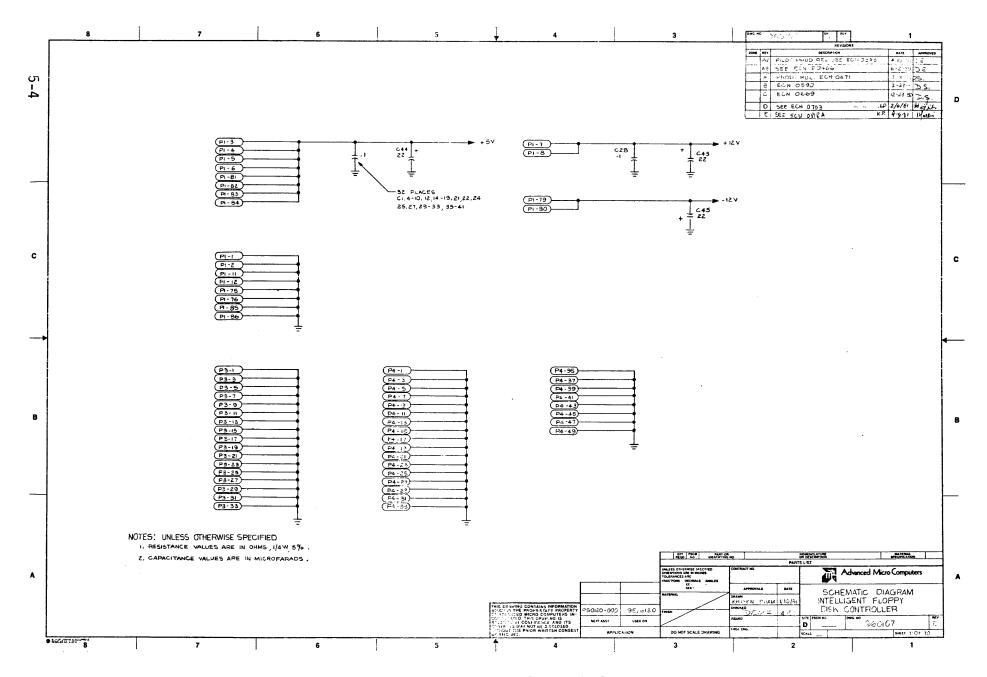

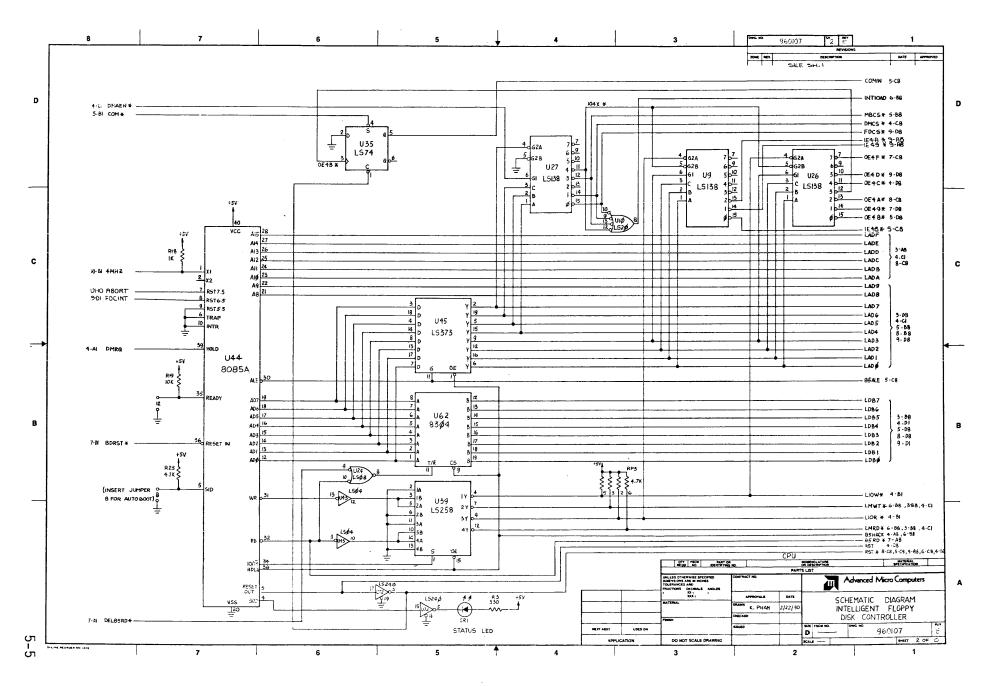

|   | LSI Circuits4-9                            |              |        | Sheet 15-4                       |

|   |                                            |              |        |                                  |

# TABLES

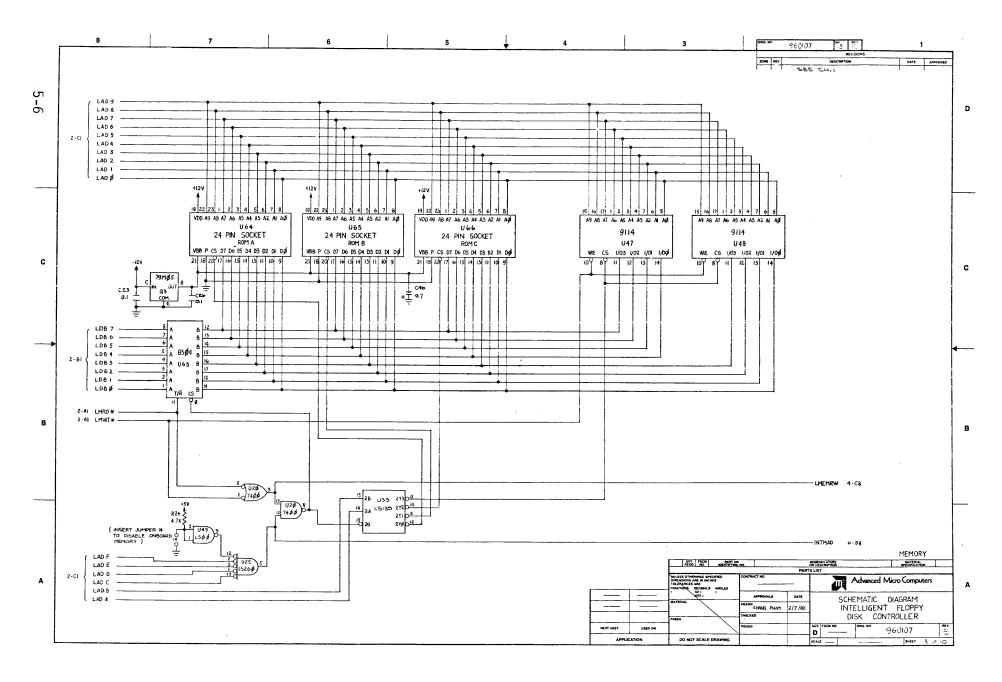

| 5-3.        | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | Drive Compatibility1-4                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------|

|             | Sheet 25-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-1. | Am95/6120 Specifications1-6 Board Select Switch |

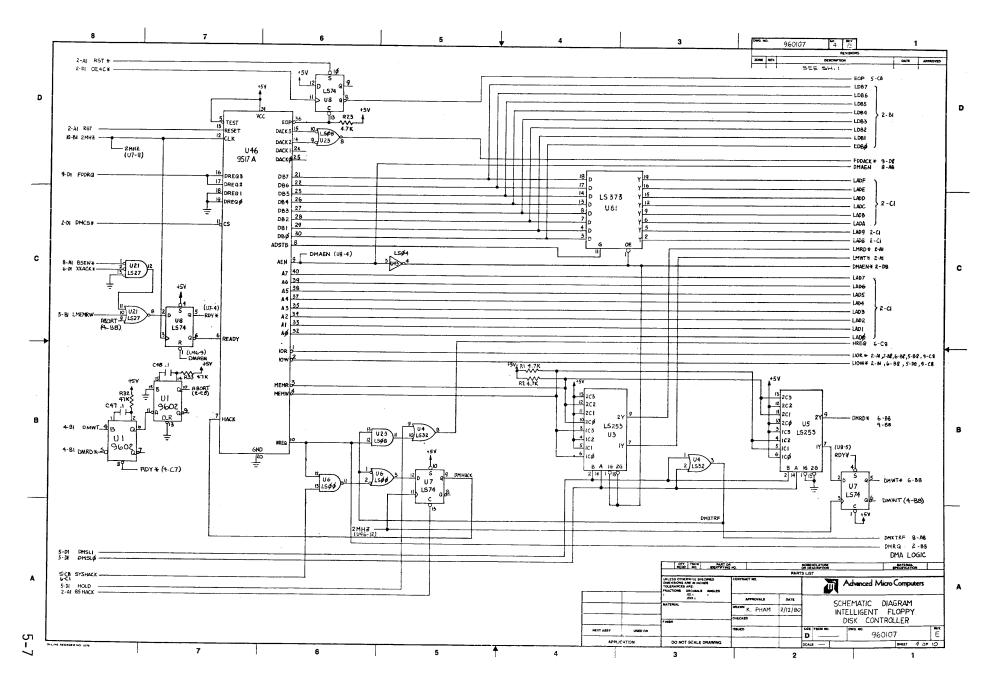

| 5-4.        | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | Settings2-2                                     |

| • 1•        | Sheet 35-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-2. | Interrupt Jumpers2-3                            |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-3. |                                                 |

|             | AMC 0E0120 000 Sahamatia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-0. | Assignments2-6                                  |

| <b>5-5.</b> | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.4  |                                                 |

|             | Sheet 45-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-4. | ——————————————————————————————————————          |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-5. |                                                 |

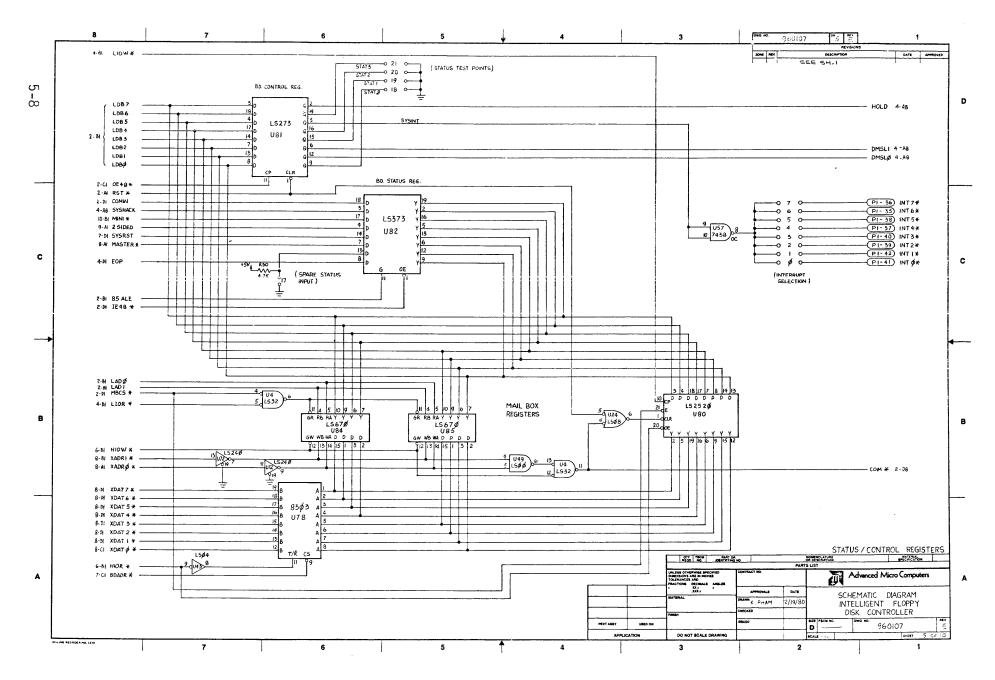

| 5-6.        | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | Assignment2-10                                  |

|             | Sheet 55-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-6. |                                                 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | Specification2-11                               |

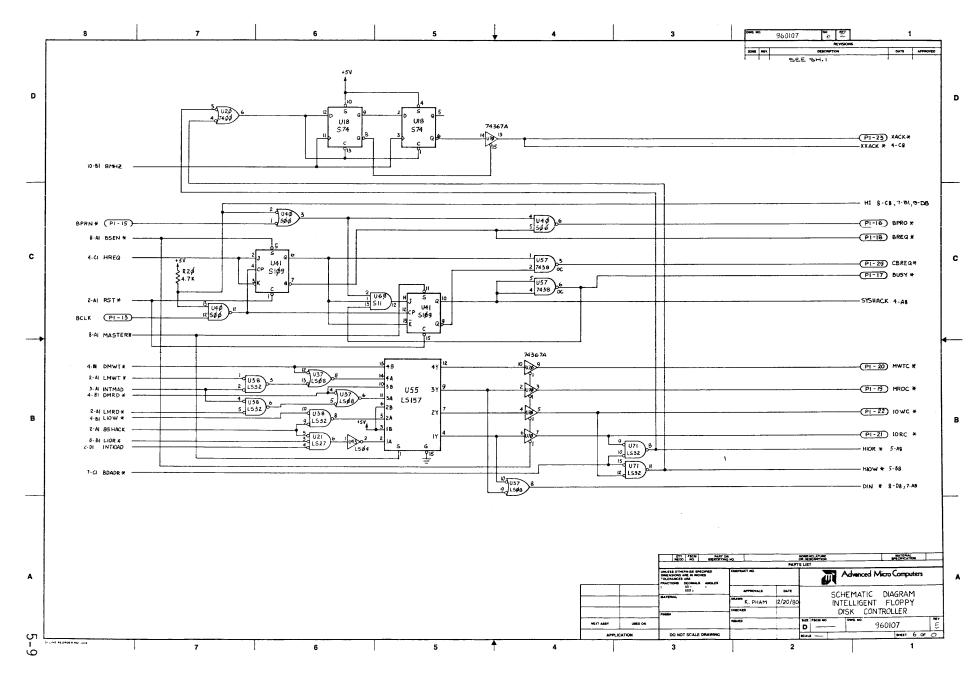

| 57          | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-1. |                                                 |

| J / .       | Sheet 65-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Functions3-4                                    |

|             | Jueec of the state | 3-2. |                                                 |

| E 0         | AMC DEDISO DOD Cohomotic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-2. |                                                 |

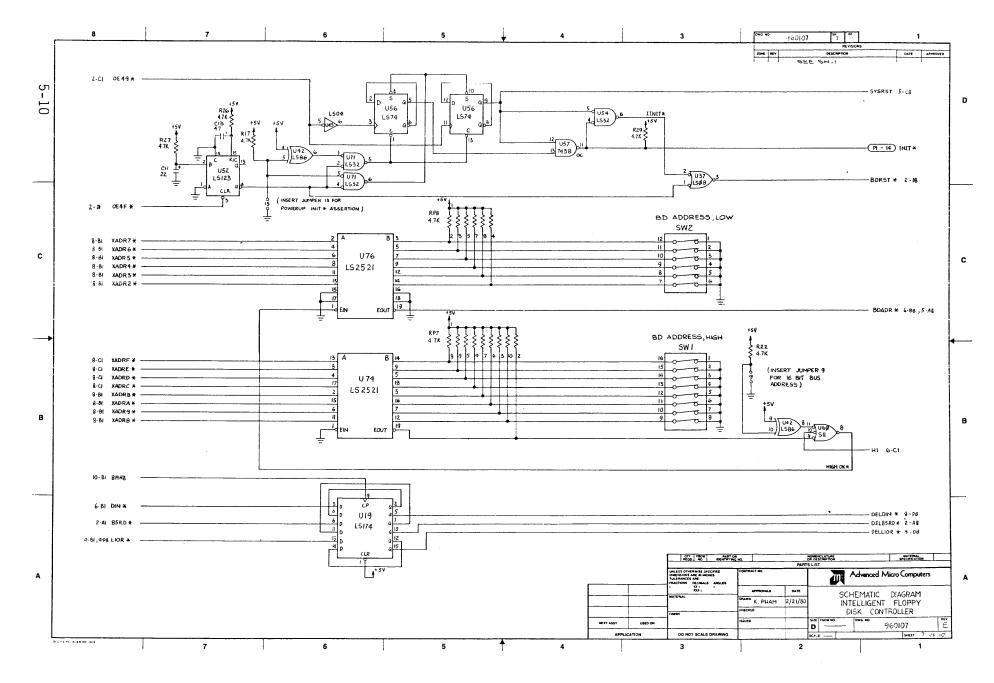

| 5-0.        | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-5. |                                                 |

|             | Sheet 75-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | Addresses3-29                                   |

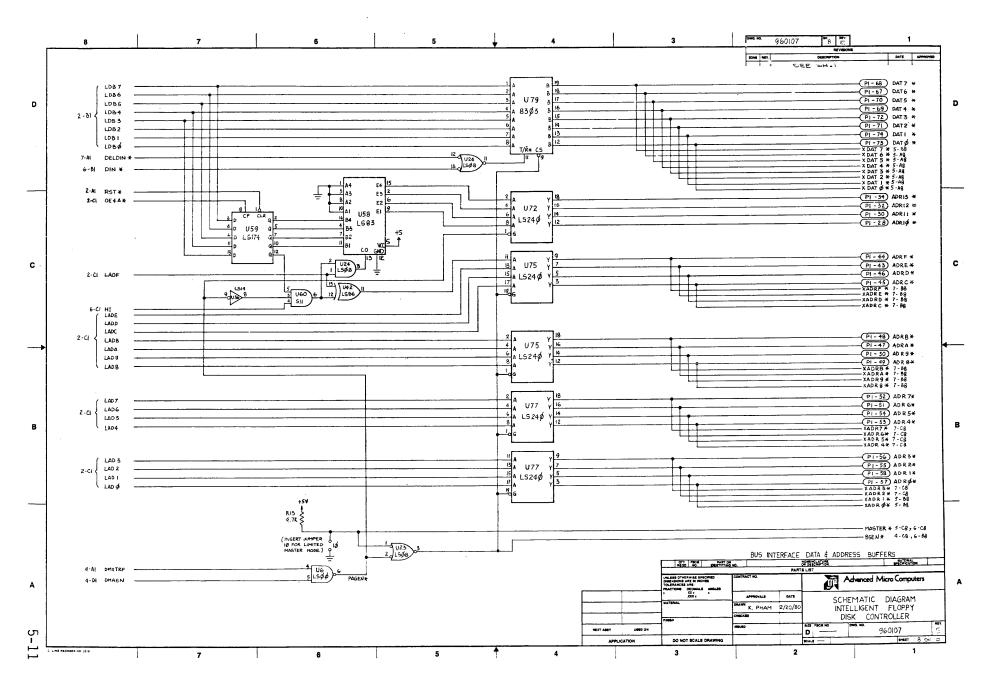

| 5-9.        | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-4. | Am9517 Internal Registers3-31                   |

|             | Sheet 85-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-5. | Software Command Codes3-34                      |

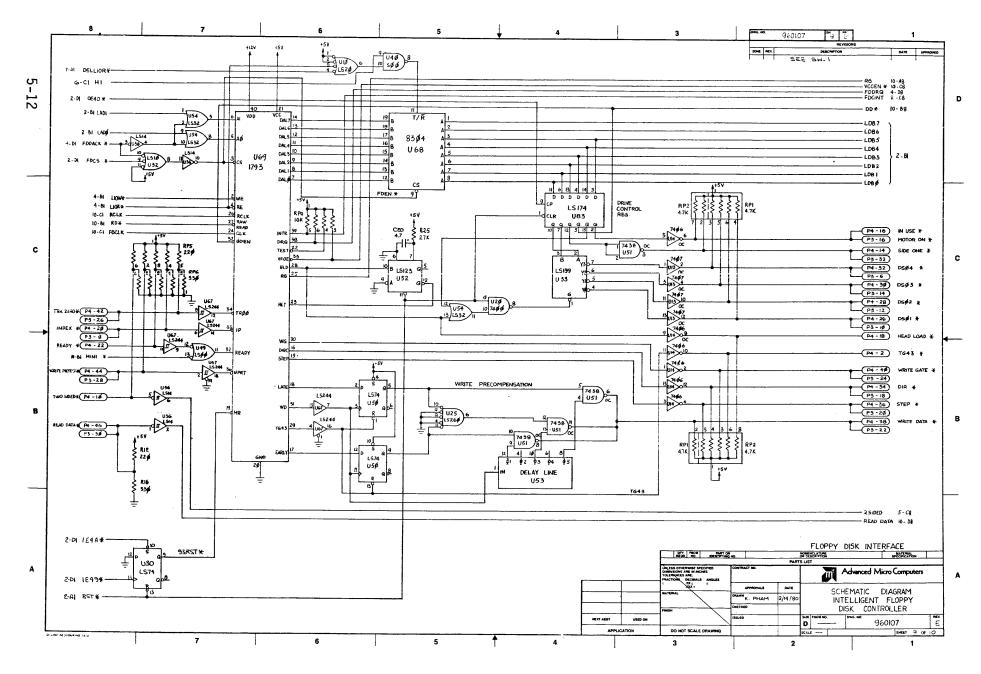

| 5-10.       | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-6. | FD1793 Address Port                             |

|             | Sheet 95-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | Assignment3-35                                  |

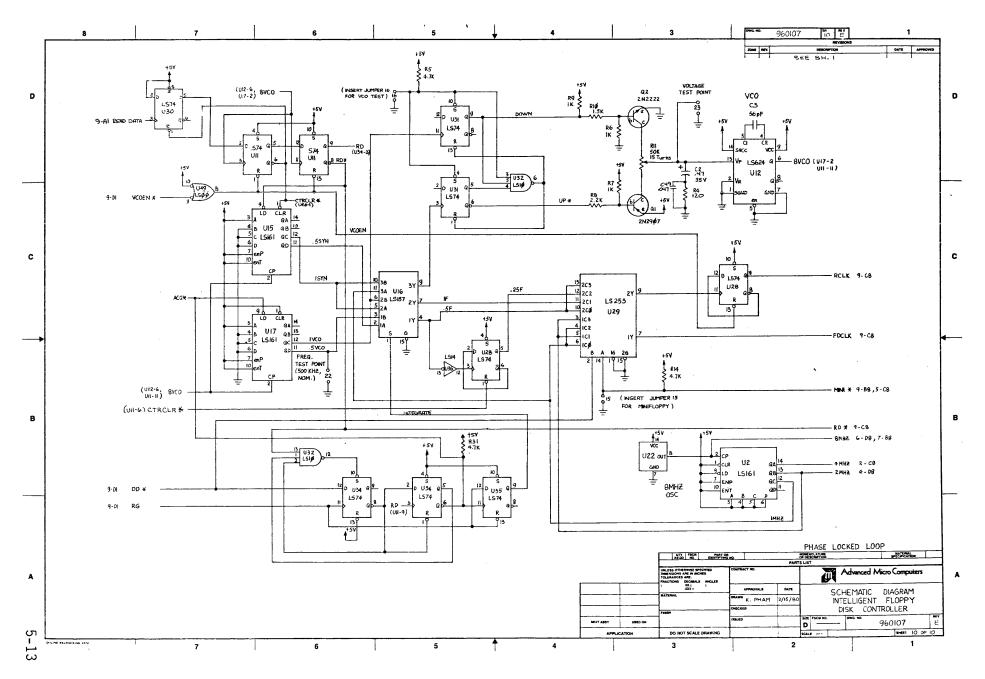

| 5_11        | AMC 950120-000 Schematic,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-7. |                                                 |

| 2-11.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | On-Board I/O Addresses4-9                       |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                                 |

# CHAPTER 1 GENERAL INFORMATION

#### 1-1. INTRODUCTION

The Am95/6120 Floppy Disk Controller is a high speed board providing the OEM with a powerful and easy-to-use means to interface industry standard 5.25 inch and 8 inch single or double density flexible disk drives to Multibus compatible OEM computers such as the Am95/4000 series MonoBoard and SBC-80 series single board computers.

The 6.75 x 12 inch board includes the Am9085 processor, the FD1793 Floppy Disk Controller, 1K-byte of high speed static RAM buffer, the Am9517A DMA Controller, 3K-byte of E-PROM with firmware, and five mailbox registers.

#### Am95/6120 features include:

• CONTROLS FOUR DRIVES, 5.25 inch or 8 inch Flexible Disk Drives, Single or Double-sided.

8 inch, single density: IBM 3740 (FM) Media Format Compatible

8 inch, double density: IBM System 34 (MFM) Media Format Compatible

5.25 inch single and double density: Shugart - Recommended Format Compatible

- DISTRIBUTED I/O PROCESSOR ARCHITECTURE. Performs all Disk I/O without host CPU intervention by means of its own dedicated processor, control firmware, and RAM buffer.

- CONTROL FIRMWARE. Provides program code for READ, WRITE, EXECUTE, and INITIALIZE plus several other commands for error checks and status words.

- HIGH THOUGHPUT by means of On-Board DMA Controller, programmable for either block or byte mode transfers. 20-bit addressing allows transfers up to 1M-byte.

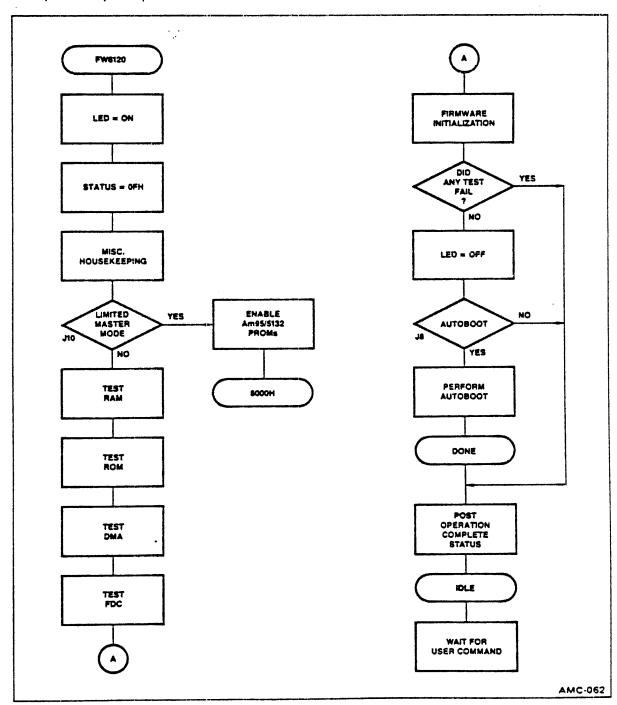

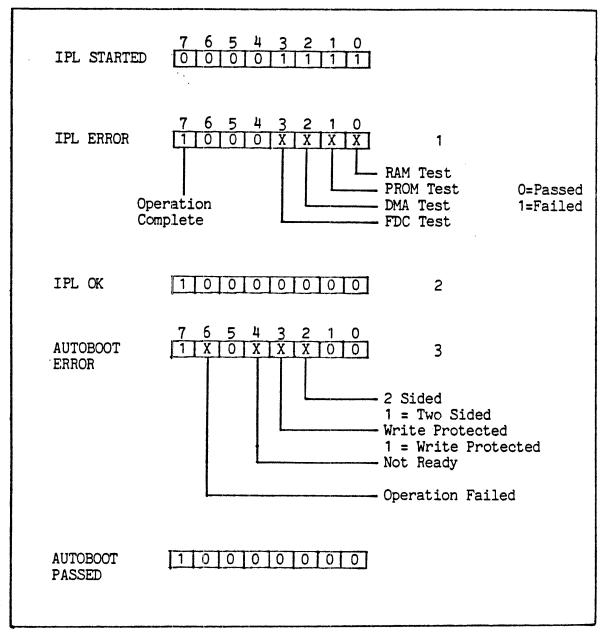

- CONFIDENCE CHECK. Automatically provides a diagnostic check on start-up of RAM, ROM, FDC, and DMA. Returns status word to CPU.

- AUTOMATIC SYSTEM BOOT. Provides a selectable system boot capability with the booting routine resident on disk and automatically read into memory on start-up, initialization, and reset.

- VERSATILE INTERFACE. SBC/Multibus<sup>†</sup> compatible, single or multimaster environment. Operates as an intelligent slave.

- AUTOMATIC CRC GENERATION AND CHECK.

- HEAD UNLOADING. Head unloaded after idle disk rotations to assure long diskette life.

#### 1-2. FUNCTIONAL DESCRIPTION

The Am95/6120 Floppy Disk Controller (FDC) is a microprocessor based disk controller that accepts commands from the host computer via the system bus. These commands are executed by the on-board CPU, allowing the host computer to perform other tasks while the disk controller is busy.

Two modes of operation are available. In polling mode, the Am95/6120 board status register can be read by the host computer at any time. In interrupt mode, up to eight jumper-selectable interrupts are available to signal the computer of the end of an operation.

# 1-3. DATA TRANSFER

Under control of the Am9085 processor and on-board operating firmware, the FD1793 controller chip selects a particular disk drive, accesses a specific location on that disk and writes onto or reads from that disk. Up to 64 disk sectors can be transferred with a single command. The head is automatically unloaded after 15 idle disk rotations. Automatic track-seek-verify, automatic CRC generation and check, and write protection verification are performed. The floppy disk controller frees the host CPU while it concurrently processes each disk I/O request.

Data transfers are performed in either full buffered mode, burst (buffered) mode or direct mode. In buffered mode, a block of 128 bytes (single density) or 256 bytes (double density) is transferred with a single bus request. Once it gains control of the bus for a full buffered mode data transfer, the controller holds the bus until all the bytes in the block are transferred. If more than one block is to be transferred, the controller generates multiple bus requests (one for each block). In burst mode, each block of data is transmitted in bursts of 64 bytes or 16 bytes, with a bus request for each burst. The controller releases the bus after each burst, and requests the bus for the next burst until the block is transferred. The facility to transfer multiple blocks in burst mode is provided. The firmware performs this operation.

†Multibus is a trademark of Intel Corporation.

A user can specify a data transfer of up to 64 blocks of data with a single user command. For a read operation in buffered mode, a sector of data is transferred from disk to on-board buffer RAM, and then, when the controller has control of the bus, from the buffer RAM to the host system. For a write operation the direction of data transfer is reversed and a block of data is transferred from the host system to the buffer RAM, and then to the disk.

In direct (byte) mode, the data is transferred directly between a disk drive and the host system. A bus request is necessary for each byte transfer. Transfer rates depend on the speed of the host system memory, up to a maximum rate of 30,000 bytes per second in direct mode single density or 60,000 bytes per second double density.

#### 1-4. COMMUNICATIONS

All communications between the host CPU and the Am95/6120 takes place independently through five mailbox registers. These consist of 8-bit registers which have dual access, either from the host system or the on-board CPU, and appear as I/O ports. These are described in figure 1-1.

#### 1-5. DISK DRIVE COMPATIBILITY

The Am95/6120 can drive up to four 5.25 inch or 8 inch flexible disk drives, with single or double sided capability. Compatible disk drives are listed in table 1-1.

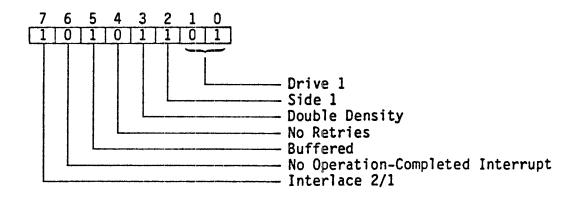

| CPU PORT#           | N                                                                                                                                                                              | N+1                                                                                                               | N+2                                                                                                                                          | N+3 (-10WC)                                                                                            | N+3 (+IOWC)                                                          |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 8-8it*<br>Registers | RO                                                                                                                                                                             | R1                                                                                                                | R2                                                                                                                                           | R3                                                                                                     | R4                                                                   |

| FDC Port#           | 30н                                                                                                                                                                            | 31H                                                                                                               | 3 <i>2</i> H                                                                                                                                 | 33H (+Read)                                                                                            | 33H (+Write)                                                         |

|                     | When referencing the FDC, this register is used to specify disk drive disk side, DMA mode, also selects options for 'retries' interrupt signal at EOP, and sector interlacing. | Used to specify starting track when referencing disk and high address byte (Ag-Ag) when referencing Global memory | Used to specify starting sector when referencing disk and low address byte (A <sub>7</sub> -A <sub>0</sub> ) when referencing Global memory. | Used to specify commands to floppy disk controller plus amount of data associated with each operation. | Used to report initial confidence test error check and status words. |

<sup>\*</sup> Switch Selectable Base Address (N)

Figure 1-1. Mailbox Registers

TABLE 1-1. DRIVE COMPATIBILITY

| Drive   | 1 Sided,<br>8 Inch Drive | 2 Sided,<br>8 Inch Drive | 1 Sided,<br>5.25 Inch Drive | 2 Sided,<br>5.25 Inch Drive |

|---------|--------------------------|--------------------------|-----------------------------|-----------------------------|

| SHUGART | SA800                    | SA850                    | SA400                       | SA450                       |

| SIEMENS | FDD100-8                 | FDD200-8                 | FDD100-5                    | FDD200-5                    |

| REMEX   | RFD2000                  | RFD4000                  |                             |                             |

| MEMOREX | 550                      | 552                      |                             |                             |

| PERTEC  | ******                   | FD650                    | FD200                       | FD250                       |

| MPI     |                          |                          | 51 <b>-</b> S               | 52 <b>-</b> S               |

| TEAC    | *****                    | **********               | FD50A                       |                             |

| - CDC   | ******                   | 9406-3                   |                             |                             |

| MFE     |                          | 700                      |                             |                             |

#### 1-6. BUS INTERFACE

The Am95/6120 is compatible with the SBC/Multibus bus standard. It can operate as one master in a multi-master environment. It can generate one of eight jumper-selectable interrupts at the end of each operation.

#### 1-7. FIRMWARE

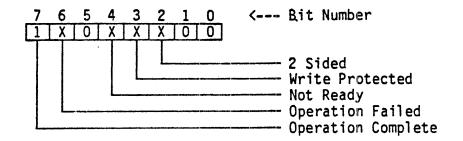

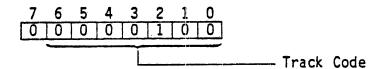

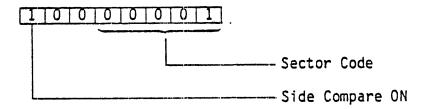

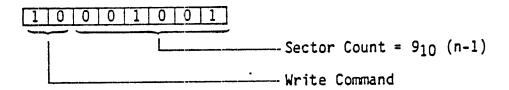

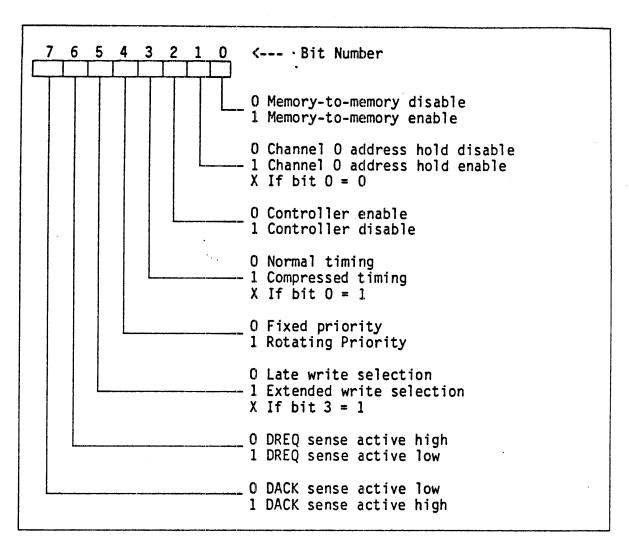

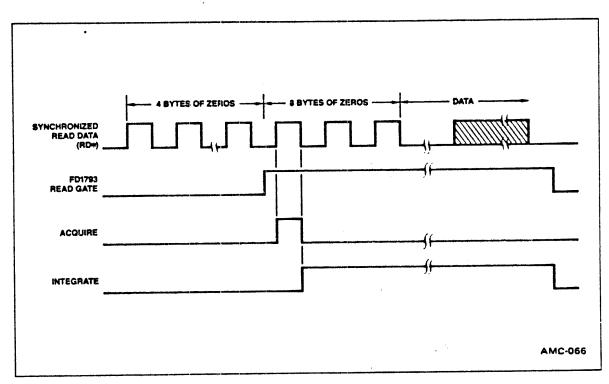

The 3K E-PROM based firmware controls all the major disk operations. Once a command is initiated by the host CPU, the Am95/6120 Floppy Disk Controller Board operates under its control. The factory-shipped firmware is present in three 2708 EPROMS.