# andahl

470 V/6 MACHINE REFERENCE MANUAL

## PREFACE

This manual describes the organization and functional characteristics of the Amdahl 470V/6, a very high-speed, large scale general purpose computing system. It provides machine reference data of fundamental interest and value to management, systems analysts, programmers and operations personnel.

Details on machine organization, performance and configuration are provided. Supplementary data on characteristics of machine check conditions, instruction timing formulas, specific channel characteristics and console operation is provided as appendices.

#### **SECOND EDITION:**

Amdahl Corporation Machine Reference Manual, Form MRM 1000-1.

This manual has been prepared by Amdahl Corporation Technical Publications.

The mark **annciaini** and the mark "amdahl 470" are trademarks of Amdahl Corporation.

Copyright Amdahl Corporation, 1976.

The Amdahl 470V/6 computing system provides extremely powerful, high-speed, general-purpose computing capabilities for sophisticated business and scientific applications. The high performance of the Amdahl 470V/6 results primarily from a newlydesigned high-speed circuitry with internal speeds measured in picoseconds, packing densities with up to 100 circuits on a central processor chip, a sophisticated architecture that incorporates the pipeline concept for a high concurrency of operations, efficient algorithms for high-speed internal functions, and a high-speed buffer coupled with monolithic main store for fast data access times. A highlyflexible input/output channel scheme is also provided for the Amdahl 470V/6. Sixteen inboard I/O channels are standard and may be configured in any combination of byte or block multiplexer or selector These inboard channels operate indechannels. pendently from the central processor.

The central processor and most of the channel unit are implemented with high-speed large scale integration (LSI) circuitry, which enables a six-to-eight times reduction in overall size and the number of external connections. The reduction in size and complexity becomes immediately obvious in that the central processor and the LSI portion of the channels occupy only 51 cards. Each card, or multichip carrier (MCC), is a ten-layer printed circuit board with 42 chip positions in a 7½" square area.

Reliability is greatly enhanced by the large reduction in components and connections. Further improvement is provided with hardware instruction retry of central processor instructions and channel command retry of I/O instructions. A significant fault recovery capability is thus provided without software assistance. An independent console processor is an integral part of the system console and provides formatted displays of any of approximately 16,000 internal latches, extended logouts to record error conditions, and the capability of configuring failing components out of the system. The high-speed buffer may thus be configured around most failures, and the system can continue running.

Main storage has error checking and correction (ECC) that corrects all single bit errors and detects all double and most multiple bit errors. If an uncorrectable error develops in a section of main storage (each megabyte is an independent section), that section may be configured out of the system.

| INTRC | DUCTION                                  |

|-------|------------------------------------------|

| SVSTE | M OVERVIEW                               |

| 51511 | Central Processor.                       |

|       |                                          |

|       | Main Storage                             |

|       | Channels                                 |

|       | System Console.                          |

|       | Power Distribution Unit                  |

|       | Optional Features                        |

| CPU   | MAIN STORAGE SYSTEM                      |

|       | Instruction Unit                         |

|       | Execution Unit                           |

|       |                                          |

|       | Storage Control Unit                     |

|       | High-Speed Buffer                        |

|       | Buffer Operation.                        |

|       | Virtual Address Operation                |

|       | TLB Operation                            |

|       | STO Stack Operation                      |

|       |                                          |

| CHAN  | NEL FACILITIES                           |

|       | Central LSI Channel                      |

|       | Modes of Channel Operation               |

|       | •                                        |

| SYSTE | CM CONSOLE                               |

|       | Usage Metering                           |

|       | Operator's Console Programming           |

|       |                                          |

| APPEN | IDIX A: MODEL-DEPENDENT FUNCTIONS        |

|       | Instruction Set Differences              |

|       | CPU Logout Areas                         |

|       | Fixed Logout Area                        |

|       | Extended CPU Logout                      |

|       | Machine Checks                           |

|       | Machine Check Conditions                 |

|       | Machine Check Interrupts                 |

|       | Hardware Diagnostic Mode                 |

|       |                                          |

| APPEN | IDIX B: INSTRUCTION TIMING ESTIMATES     |

|       | Early Condition Code Settings            |

|       | Retryable Instructions                   |

|       | Timing Formulas                          |

|       | Legend for Timing Formulas               |

|       | Special Timing Formulas.                 |

|       |                                          |

| APPEN | DIX C: MODEL-DEPENDENT CHANNEL FUNCTIONS |

|       | Subchannel Assignment                    |

|       | Extended Channel Locout                  |

|       | Extended Channel Logout                  |

| APPENDIX D: CONSOLE PROCESSOR SYSTEM          |    |

|-----------------------------------------------|----|

| Modes of Operation                            | 50 |

| Amdahl 470V/6 Power Up and Power Down         | 50 |

| Initialization                                |    |

| Initial Program Load                          | 51 |

| Status Display                                | 52 |

| Errors                                        |    |

| Control Mode Operation                        | 55 |

| Control Mode and Device Support Mode Commands |    |

| Strings                                       | 64 |

## SYSTEM OVERVIEW

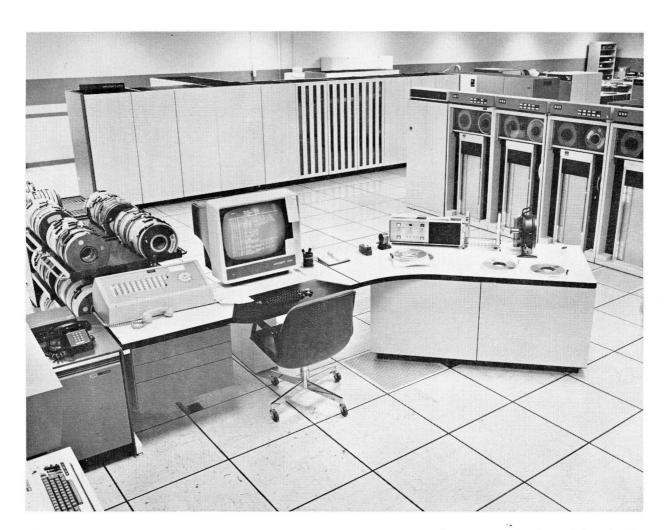

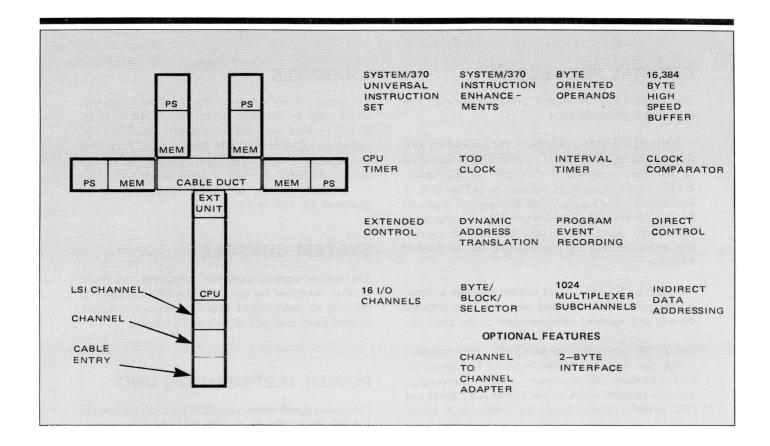

Major components of the Amdahl 470V/6 System are the central processing unit, main storage, channels, system console, and power distribution unit.

#### **CENTRAL PROCESSOR**

The Amdahl 470V/6 central processor includes the following standard features:

STANDARD ARCHITECTURE. The Amdahl 470V/6 follows the architecture of System/370 as specified in the *IBM System/370 Principles of Operation*, GA22-7000 (henceforth referred to as *Principles of Operation*). The standard full System/370 Universal Instruction Set with extended precision floating point operations, direct control and System/370 instruction enhancements are implemented on the Amdahl 470V/6.

DIRECT CONTROL. This facility provides a direct control path into the central processor from external devices and operates independently of the channels.

16K-BYTE HIGH-SPEED BUFFER. The standard buffer size provides 16,384 bytes of high-speed bipolar memory to maximize system throughput. Memory transfer width to the buffer is 32 bytes and CPU transfer width from the buffer is 4 bytes.

TRANSLATION LOOKASIDE BUFFER. To enhance virtual performance the Amdahl 470V/6 provides a 256-entry translation lookaside buffer (TLB). This TLB provides high-speed storage of most recently used virtual address translation information. Operation of the TLB is further enhanced with a 32-entry segment table origin stack to identify specific CPU states with TLB entries.

TIMING FACILITIES. Standard timing facilities of System/370 architecture are provided. These include an interval timer, time-of-day (TOD) clock (a 64-bit field with 52-bit resolution), a clock comparator (provides a 52-bit comparison field for the TOD clock) and CPU timer.

#### MAIN STORAGE

Main storage is available in one megabyte increments, up to eight megabytes. Interleaving is four-way for each two megabyte storage unit and two-way if one megabyte is installed in a storage unit. Thus, a three megabyte system is four-way interleaved for the first two megabytes and two-way interleaved for the last odd megabyte.

#### CHANNELS

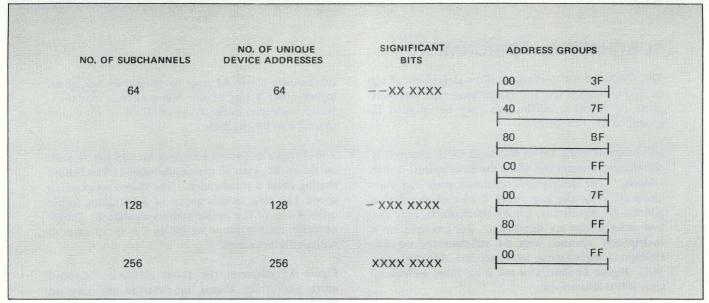

The Amdahl 470V/6 system has 16 inboard channels, which may be installed in any combination of selector, or byte or block multiplexer channels. The operation of these channels does not interfere with the operation of the CPU, except for possible storage access conflicts. A total of 1024 subchannels may be assigned to the multiplexer-type channels in groups of 64, 128, or 256.

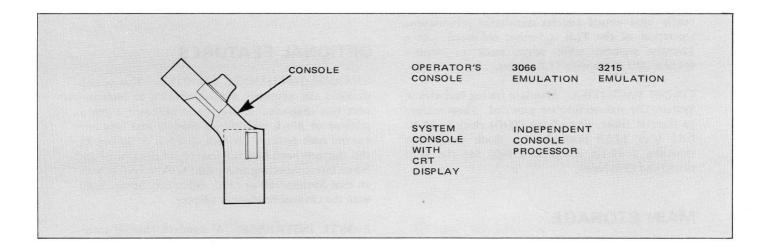

#### SYSTEM CONSOLE

The system console performs operations and maintenance functions for the Amdahl 470V/6 system. It includes an independent console processor, operator control panel and CRT display and keyboard.

#### POWER DISTRIBUTION UNIT

The power distribution unit (PDU) distributes 400 Hz and 60 Hz power to the Amdahl 470 V/6 system. Emergency power off and thermal monitoring facilities are also provided.

#### **OPTIONAL FEATURES**

CHANNEL-TO-CHANNEL ADAPTER. This option provides the necessary synchronization to interconnect two channels. It may be attached to either a selector or block multiplexer channel and uses one control unit position on each channel. Only one of the channels need have the feature installed, however. When interconnecting an Amdahl 470V/6 system with an IBM System/360 or /370, either may be equipped with the channel-to-channel adapter.

2-BYTE INTERFACE. A standard channel interface provides a one-byte wide data path between controllers and a channel. The addition of the twobyte interface effectively doubles bandwidth for control units that support this feature. The two-byte interface option is available on all selector and multiplexer channels.

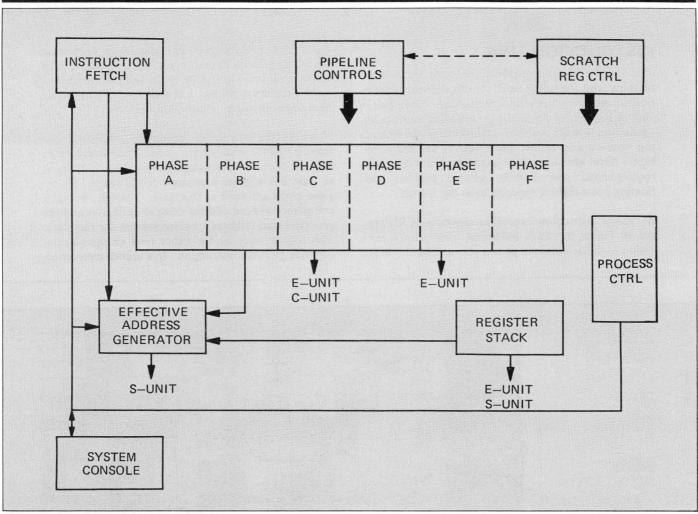

The Amdahl 470V/6 consists of four logical, independent units physically implemented in 51 MCCs. These four units are the instruction unit (I-Unit), which implements the pipeline; the execution unit (E-Unit), which performs arithmetic and logical instructions; the storage control unit (S-Unit), which controls the high-speed buffer and main storage requests; and the channel unit (C-Unit) which executes channel commands. Because of the distinct functional difference of the C-Unit, it is discussed separately in "Channel Facilities".

#### **INSTRUCTION UNIT**

The instruction unit pipeline performs instruction fetching and decoding and coordinates the execution of an operation with other units. Since the I-Unit is principally devoted to controlling instruction execution, it must interface with most of the rest of the machine and resolve priorities. It handles interrupts; status switching; CPU-channel control interface requirements; and scratch, general purpose and floating point register requests from the E-Unit.

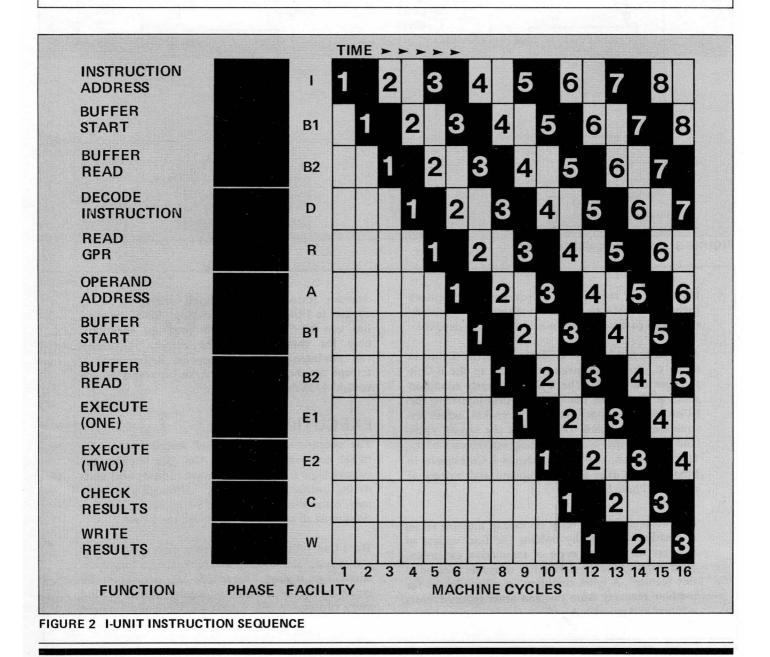

A typical instruction execution sequence is illustrated in Figure 2. Each individual instruction's execution is divided into six phases plus an I-fetch phase. The I-fetch phase begins with the I-Unit requesting the S-Unit priority in the I-cycle. A high-speed buffer access is initiated in the B1 cycle, and the instruction word becomes available in the B2 cycle. The I-Unit then begins instruction interpretation.

Phase A is the instruction decode and general purpose register (GPR) read cycle. Since most instructions have an operand address consisting of the contents of at least one register plus some modification, the register reads are done at this time. Phase B then generates the operand address using the effective address generator and initiates a buffer request for this data. This request may be for either four or eight bytes, depending on the instruction. In a branch instruction

FIGURE 3 I-UNIT ORGANIZATION

the target of the branch is requested so that both paths of the branch will be available. (The branchnot-taken path continues to be fetched and decoded).

After data has become available from the S-Unit in Phase C, the I-Unit passes this data to the E-Unit to begin execution. The E-Unit sets early condition codes at the end of the E1 cycle, thus informing the I-Unit of the proper path for branches before instruction completion. Phase D is the second cycle (and subsequent cycles for long operations) of E-Unit execution. The I-Unit checks E-Unit results in Phase E and does the final update and writing of results in Phase F.

Hardware instruction retry (in case of machine error) is greatly facilitated by holding the final update of registers to the last cycle of instruction execution. Most instructions are completely retryable because of this feature. A more complete list of conditions for machine recovery from this and other types of errors is found in Appendix A. Another feature of the delayed writing of results appears in I-Unit interrupt handling. Since the pipeline can be "backed up" an interrupt need wait only for completion of the current instruction (on noninterruptable instructions) before the interrupt can be taken; hence, all interrupts on the Amdahl 470V/6 are precise.

#### EXECUTION UNIT

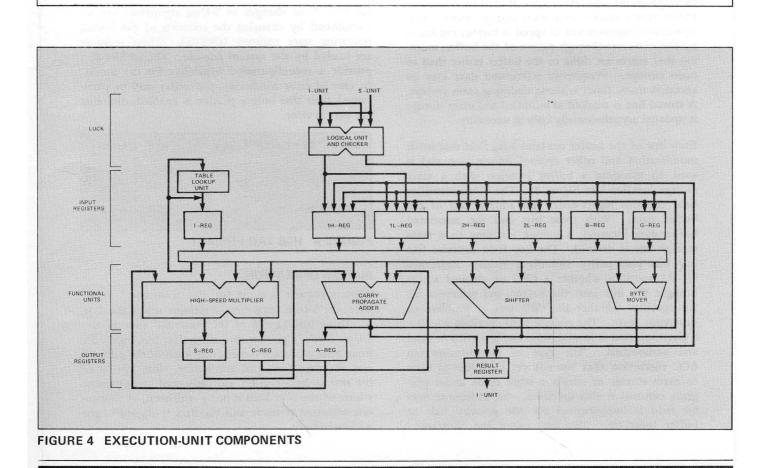

The execution unit consists of several major functional components, registers for data storage, and control logic for the coordination of functional units during instruction execution. Although some data may come directly from the S-Unit, actual instructions must all be presented through the I-Unit.

The I-Unit tells the E-Unit when to start an operation and supplies intermediate scratch space for long operations, e.g., Multiply Extended. Instructions can be presented to the E-Unit at a maximum rate of one every two cycles; the E-Unit is capable of generating results on single cycle boundaries thereafter.

Data is presented from the I-Unit to the E-Unit through the logical unit and checker (LUCK). The LUCK scans operands for any information that can be obtained before execution actually begins by performing the following functions:

- LOGICAL OPERATIONS AND, OR, Exclusive OR.

- OPERAND COMPARISON Magnitude of two operands is compared where possible.

- SETTING EARLY CONDITION CODES Condition code is returned after the first cycle on many operations.

- PARITY CHECK Input parity is checked and predicted.

- DECIMAL DIGIT CHECK Input data is checked for valid digits and sign.

- BIT COUNTER Several methods of counting leading zeros are performed for use in shifting and normalization.

The LUCK is placed first in the E-Unit data path to provide a "head-start" for the rest of the E-Unit. Data output from the LUCK is to several intermediate registers. These registers are each one word wide and are divided into higher and lower order words and first and second operands (hence, "1H" and "2L" in Figure 4). Data from each of these registers may then be sent to a functional unit.

The principal E-Unit functional units are multiplier, adder, shifter and byte mover. The multiplier is a carry-save adder used to multiply two operands to produce a 40-bit result; the adder performs a standard binary add or a decimal add, depending on which of several modes is requested; the shifter shifts input operands; the byte mover is used in manipulating single-byte fields for arithmetic or logical operations. Each functional unit performs its function in a single cycle. Error checking is done in all functional units. Output data is checked for good parity, and internal functional checks are made using residue arithmetic.

Output registers from the functional units store intermediate results. The S- and C-registers contain

the sum and carry outputs of the multiplier; the A-register contains output from the adder. The I-register is used in generation of 10-bit inverses, which are created by the table-lookup unit, or division operations. The B- and G-registers are used for intermediate storage of fields. When the E-Unit functions are complete, results are staged in the result register for transmission to the I-Unit.

#### STORAGE CONTROL UNIT

All storage requests from the CPU and channels are processed by the storage control unit. Priorities are resolved and facilities are provided based on the S-Unit's internal priority structure and the priority of the request from the I- or C-Unit. The S-Unit also determines whether requested data comes directly from the high-speed buffer or must be read in from main storage. All virtual-to-real address translations are performed by the S-Unit.

#### **HIGH-SPEED BUFFER**

The 470V/6 high-speed buffer (HSB) is organized as a 16,384-byte set-associative memory consisting of primary and alternate halves. Each half contains 256 32-byte lines that can be accessed on a double or single word basis. Because of the local nature of most programs, execution time should be related to buffer speed rather than main storage speed. This significant improvement in speed is further enhanced by the non-store-through nature of the buffer; meaning that stores are done to the buffer rather than to main storage. Frequently referenced data may be accessed many times without updating main storage. A stored line is marked as modified and main storage is updated asynchronously only as necessary.

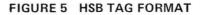

Each line of the buffer contains a tag field that holds modification and other control information and is used to associate a buffer location with a main storage location (see Figure 5). The block identifier field contains higher-order real address bits of the buffer data. With these bits and the associated buffer data location, a unique mapping to a main storage line is defined. The key field contains five key bits plus parity and check fields. Reference bit R1 specifies whether a CPU or channel access brought the line into the buffer, and reference bit R2 specifies whether the CPU was in problem or supervisor state. The control field specifies whether a given location is invalid, valid and modified or valid and unmodified. The type of modification (an ECC correction that has not yet been moved back to main storage or simply a store made under program control) is also specified. An additional onebit field is implemented for the primary half of buffer locations. This bit, called the "hot/cold"

bit, indicates that the primary location has been referenced more recently than the associated alternate location.

The above factors are variables used by the S-Unit to determine where to put new data in the buffer. If data is not present in the buffer when requested, it may be moved to either the primary or alternate half of the buffer from main storage. The S-Unit can check to see if either the associated primary or alternate location is invalid (and thus may be loaded immediately) or which was used more recently. A facility is also provided to distinguish between CPU and channel data and between supervisor and problem state. The ability to change buffer algorithms further enhances buffer tuning and provides for the most efficient operation under a wide variety of circumstances.

The S-Unit may also use a prefetch function to fetch data from main storage in advance of need. This prefetch may occur after either the first or second access to any quarter-line segment of the buffer. Prefetch may be selectively enabled for the channel, instruction fetch or operand fetch port. Prefetch and buffer change algorithms are preset by Amdahl to optimal values for most applications.

All the above changes to S-Unit algorithms are accomplished by changing the contents of the S-Unit operating state registers (OPSRs). These registers are loaded by the system console. The OPSRs also provide a reconfiguration capability for the buffer. In case of error conditions, the buffer may be partitioned such that only a portion is enabled, disabling the part in error.

| BLOCK IDENTIFIER    | KEY  | REF   | CNTRL |     |

|---------------------|------|-------|-------|-----|

|                     |      |       |       | H/C |

| (Real Address Bits) | 04PC | R1 R2 | 012   |     |

#### **BUFFER OPERATION**

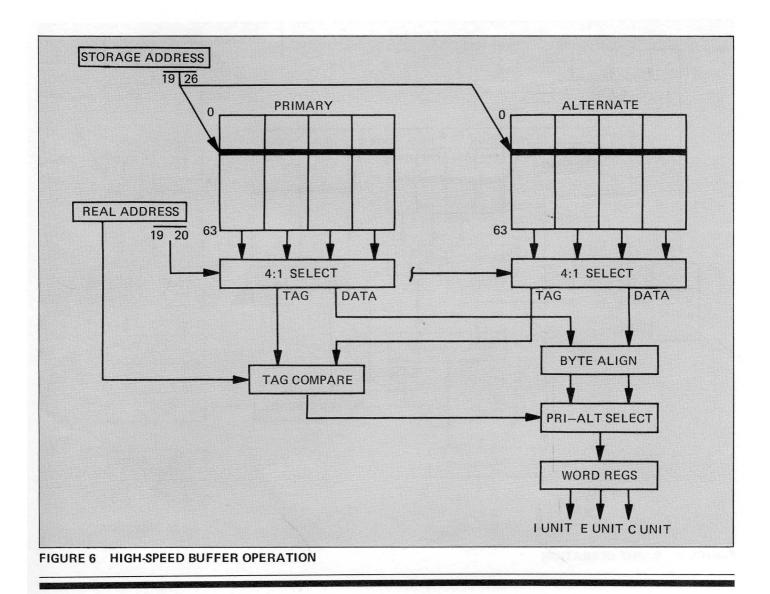

When a request is made for data from the I- or C-Unit, the S-Unit must first determine where the data is. Using bits 21-26 of the presented address, the S-Unit forms a pointer into the buffer (see Figure 6). Four lines of data are read from each of the primary and alternate halves of the buffer. Bits 19-20 of the real address register are then used to determine which of the four lines is being requested. A four-toone selection is made and the data is aligned to the addressed byte. With the associated tag information now available from both the primary and alternate lines, a tag comparison may be performed. The real address bits that correspond to tag information are compared to both of the tags from the primary and alternate reads, and a match is signaled for the appropriate half of the buffer. This match is then used to select which of the aligned words (byte alignment has already been accomplished) will be loaded into the output word register. This operation takes two cycles. Status information, such as protection exception, is available at the same time.

Requests to the S-Unit can be pipelined at the rate of one per cycle; data is returned at the end of two machine cycles. If data is not in the buffer a main storage request is generated. Main storage requests are four-way interleaved for each two megabytes of memory. Four requests, therefore, may be active simultaneously.

#### VIRTUAL ADDRESS OPERATION

To provide the advantages of virtual memory to users, the Amdahl 470V/6 system can perform dynamic address translation when in EC mode. The virtual address implementation in the 470V/6 follows the System/370 architecture. Performance is further enhanced with a translation lookaside buffer (TLB), which provides high-speed storage of most recently translated addresses, and a segment table origin (STO) stack, which identifies the environment of different TLB entries.

#### **TLB OPERATION**

The TLB provides a fast source of translation information to minimize virtual operation time and to allow overlap of translations and HSB accesses. The TLB is implemented very similarly to the HSB, but consists of 128 virtual-real address pairs in each of the primary and alternate halves. Thus, a correspondence is set up in the TLB between virtual and real address space whenever a translation is performed.

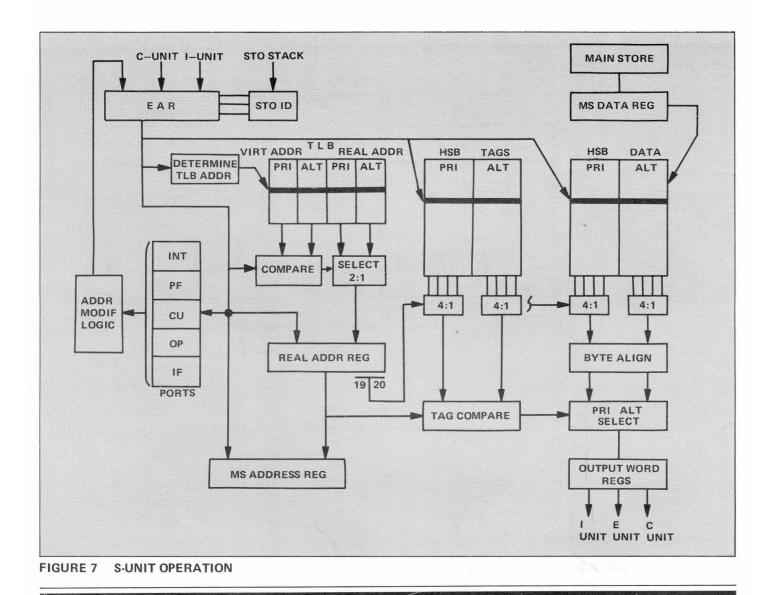

When a virtual address is presented to the S-Unit through the effective address register (EAR), a TLB and an HSB access are both started (see Figure 7). The virtual address maps to a given TLB location. When the associated real address is obtained from the TLB (assuming that an entry was there), a selection is performed based on matching the virtual address in the TLB with the virtual address presented. The real address register (RAR) is then loaded with the effective real line address, and bits 19–20 are used for buffer data selection as described above. If data is not present in the buffer, the real byte address is loaded in the main store address register (MSAR) to obtain data from main storage. S-Unit ports are provided for each of the possible requesting units (instruction fetch, operand, C-Unit, pre-fetch and internal ports) to allow the capability of having requests from the various units active simultaneously.

12

If the virtual-real address translation has been performed and information resides in the TLB, no overhead for the TLB access occurs since its access is overlapped with the buffer; thus, data is returned in two cycles for both real and virtual operations. If the virtual-real address pair is not currently valid in the TLB a full translation must be made, which requires two additional storage (either buffer or main store) references. The new translation is placed in the TLB using an algorithm similar to the buffer replacement algorithm. A hot/cold (H/C) bit feature similar to the feature of the HSB is implemented in the TLB.

TLB addresses may be made invalid by a system reset, a Purge TLB instruction, or by changing the state of control registers 0 and 1. To enhance performance, two sets of valid bits are kept in the TLB. When a Purge TLB instruction is executed, the S-Unit automatically switches the set of valid bits it is currently using to the other set, which are all marked "invalid". The S-Unit resets the older set of valid bits during spare cycles to be ready for the next Purge instruction; thus a single Purge TLB instruction may be executed, incurring only the minimum two cycle instruction overhead.

#### **STO STACK OPERATION**

The STO stack stores information about control registers 0 and 1 so that TLB entries can be reused if these control registers are reloaded with previous values. This is done by associating a STO identification field (ID) with translation information from control registers 0 and 1. The STO ID is then stored with the TLB and STO stack entries. Valid TLB entries must match the current STO stack entry (which matches current values in control registers 0 and 1).

When a translation is performed, control registers 0 and 1 determine segment table size and location in main storage. Thus, when these registers are changed, the current virtual-real address correspondence becomes invalid. Rather than invalidate all current TLB entries, the S-Unit assigns a new STO ID to be stored with all subsequent TLB entries and enters information from control registers 0 and 1 into the STO stack location associated with the new ID. If control registers 0 and 1 are changed to previous values, any entries remaining in the TLB from old translations need not be made again. The STO stack consists of 32 slots; when the 32nd entry is made, the S-Unit purges the oldest entry from the STO stack and all associated TLB entries during spare cycles. The system thus maintains up to 31 active address spaces. All STO stack entries are invalidated by a Purge instruction.

The Amdahl 470V/6 has 16 standard inboard channels. These channels are independent of the CPU and, with the possible exception of memory access conflicts, do not affect CPU performance. The channels may be configured in any combination of selector channels or byte or block multiplexer channels. A total of 1024 subchannels are available for allocation to multiplexer channels in groups of 64, 128 or 256.

The channel unit (C-Unit) is implemented in both LSI technology and non-LSI, third-generation technology. The LSI portion of the C-Unit provides interface sequencing, data movement to and communication with the S-Unit, and an operational interface to the CPU that obeys the System/370 architecture as defined in the Principles of Operation. The non-LSI portion (channel frame) performs buffering, translation from LSI logic levels to standard interface levels, and signal conditioning (driving and receiving interface signals).

#### **CENTRAL LSI CHANNEL**

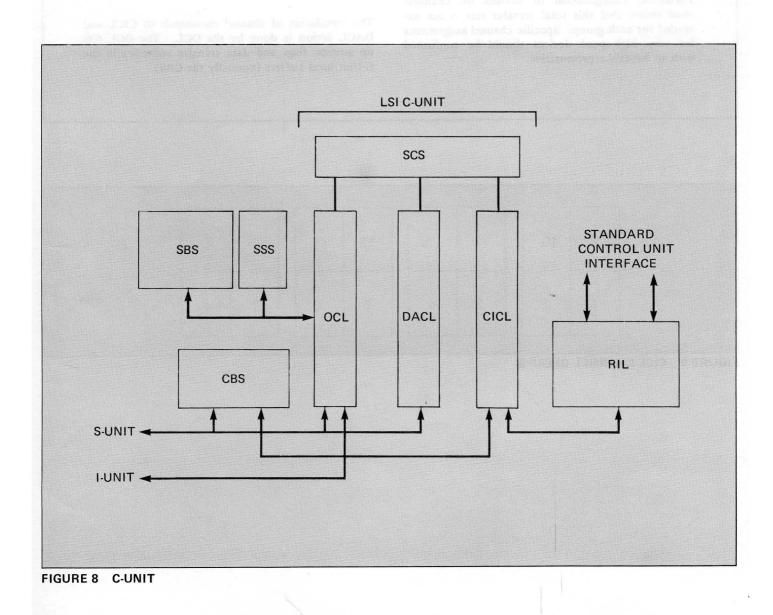

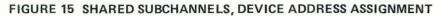

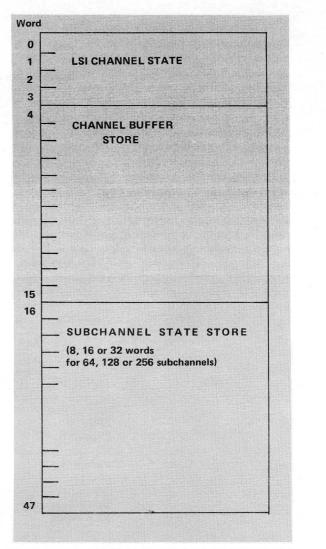

The LSI portion of the C-Unit is shown in Figure 8. It is functionally divided into three major parts. The central interface control logic (CICL) controls interface sequences and data buffering to and from the external devices; the data access control logic (DACL) updates buffer pointers and counts and moves data between the S-Unit and C-Unit buffers; the operations control logic (OCL) sets up channel transfer sequences and coordinates channel program execution with the operation of the rest of the C-Unit. The shifting channel state (SCS) is a communications area used by each of these major parts.

Data path information is also shown in Figure 8. On an output operation the DACL fetches data a word at a time from the S-Unit and stores it in the channel buffer store (CBS); the CICL moves it to the non-LSI remote interface logic (RIL) for transmission to the control unit. The above sequence is reversed for an input operation.

The CICL transfers data to or from the CBS on even cycles; the OCL and DACL share odd cycles. The CICL transfers one byte or two bytes at a time; the DACL and OCL transfer a word at a time. The CICL examines every channel in the SCS once every eight cycles for data transfer requests. Figure 9 illustrates how this property of the CICL may affect channel configuration. A group of four channels as illustrated shares certain resources of the C-Unit buffers. With a machine cycle time of 32.5 nanoseconds, the maximum bandwidth of each group is approximately 3.85 million bytes per second.

Therefore, configuration of devices on channels must insure that this total transfer rate is not exceeded for each group. Specific channel assignments for very high-speed devices should be confirmed with an Amdahl representative. The DACL is pipelined to optimize throughput. Each channel is examined every l6 cycles. Thus, while one section of the DACL may be fetching data from the S-Unit, another may be posting results to the SCS, and another may be examining the incoming SCS for channels that need service. Each channel is assigned a dynamic priority based on the amount of space it has remaining in the C-Unit buffers. If a channel has less than half of its buffer remaining, the DACL will change its S-Unit request from a low to a high priority. This change can occur even if a fetch or a store is in progress. The highest priority channel is marked from the SCS and serviced next by the DACL.

The translation of channel commands to CICL and DACL action is done by the OCL. The OCL sets up counts, flags and data transfer addresses in the C-Unit local buffers (normally the CBS).

| 9 | 10 | 11 | 12 | 13 | 14 | 15 | 0   |  |

|---|----|----|----|----|----|----|-----|--|

| 1 | 2  | 3  | 4  | 5  | 6  | 7  | 8 " |  |

To perform byte or block multiplexing, the OCL activates a subchannel (the portion of a channel that actually "executes" a channel program) when appropriate status information is received from the CICL. The OCL uses the subchannel buffer store (SBS) for temporary storage of inactive subchannel information. The OCL can monitor subchannel state and perform subsequent decisions with the information from the subchannel state store (SSS). The OCL obtains its control information directly from the I-Unit and S-Unit over an interface shared with the DACL.

Channel indirect data addressing as described in the *Principles of Operation* is fully implemented on the Amdahl 470V/6 by the OCL and DACL. Indirect data addressing (IDA) requires that a control program perform any necessary virtual-to-real address translations before a data transfer command is executed by the channel.

#### MODES OF CHANNEL OPERATION

Because of the relative independence of the OCL, DACL and CICL, any channel can be configured as a byte or block multiplexer or selector. Selector channels transfer only in burst mode and may address up to 256 I/O devices, one at a time. Selector channels contain a single implicit subchannel, which does not require allocation from that pool of 1024 subchannels. The total possible data rate per selector channel is the same as the rate for a block multiplexer.

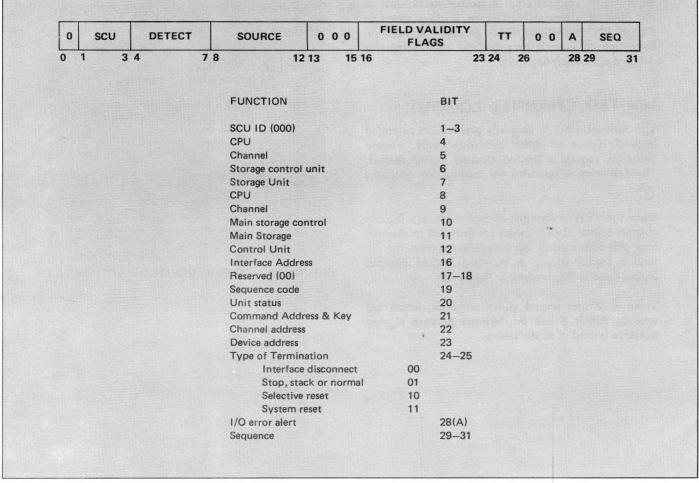

Multiplexer-type channels perform device multiplexing and execute several channel programs simultaneously. The level of concurrency is determined by the number of subchannels allocated to the multiplexer channel; one subchannel is necessary for each concurrent channel program execution. Subchannels are allocated in groups of 64, 128 or 256. With either 64 or 128 assigned subchannels, a channel may be configured for shared subchannel operation. Details on shared subchannel allocation and device address assignment are contained in Appendix C.

Block multiplexer channels perform the basic multiplexer function, but always transfer in burst mode. It is the more efficient type of multiplexer channel since a considerable amount of data is transferred each time a device logically connects to a channel. Maximum data rate on a standard singlebyte block multiplexer channel is the same as for any channel operating in burst mode, or approximately two million bytes per second. The optional two-byte bus doubles this available channel bandwidth.

Byte multiplexer channels usually multiplex a very few bytes at a time. The Amdahl 470V/6 allows a byte multiplex-mode bandwidth of approximately 110 kilobytes per second. The byte multiplexer bandwidth for single-byte bus devices running in burst mode is approximately two million bytes per second. Selector subchannels are not implemented in the Amdahl 470V/6 byte multiplexer channels.

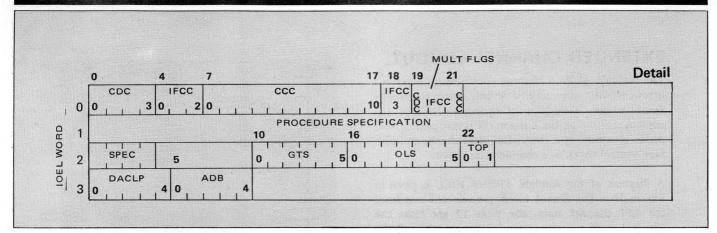

Extended channel logout is fully implemented on the Amdahl 470V/6. If control register 14 bit 2 is set, extended logouts will be made when certain errors occur. No logout will be made if this bit is off. More information on extended channel logout fields is found in Appendix C.

NOTE: Maximum burst mode data rates cited are maintainable with chaining only when the chaining occurs during device "gap time". The use of IDA flags in a virtual environment has a similar effect on data bandwidth. The possibility of overrun, therefore, greatly increases when chaining in a virtual environment.

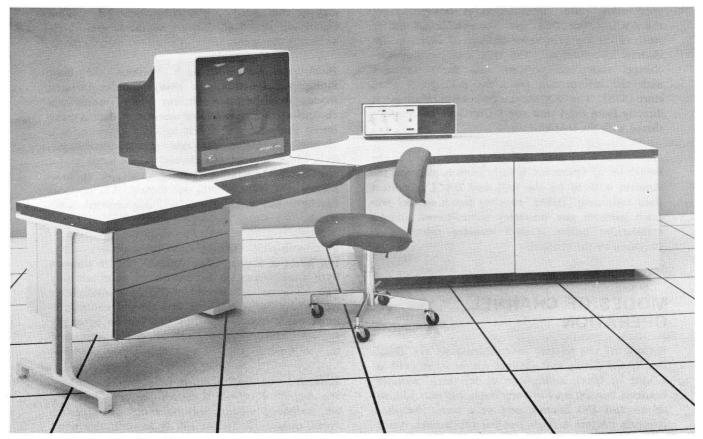

FIGURE 10 SYSTEM CONSOLE

The Amdahl 470V/6 system console serves as an operator's console and as a system maintenance console (Figure 10). It consists of a CRT and keyboard, an independent console processor, a disk for the console processor, a diskette unit to provide the Amdahl field engineer with a diagnostic test loading facility, and a modem to allow remote access to the Amdahl diagnostic facility. A standard channel interface allows the console processor to emulate a 3066 or 3215 operator's console. A standard operator's control panel is also provided (Figure 11).

The Amdahl 470V/6 system console can operate Device support mode provides in three modes. emulation of standard consoles for data transmission to and from the operator using the system console and a channel; hardware command mode allows display and storage of registers and memory, reset, clear, and other hardware functions; and maintenance mode allows operation of diagnostic programs and provides formatted displays of some 16,000 latches within the Amdahl 470V/6. Device support mode can emulate either a 3066 CRT display or a 3215 printer/keyboard using the CRT display instead of a printer. In device support mode the system console functions as a control unit on either a selector or a block multiplexer channel.

A direct computer-to-console interface is provided between the system console and the central processor. This separate path is independent of the channel and is used by hardware command and maintenance modes to permit static readout of system latches and setting of certain control and data registers. This provides the system console with increased diagnostic and maintenance flexibility.

Two functions of the Amdahl 470V/6 system console differentiate it from most other similar consoles presently available:

Most console input functions are performed using the keyboard rather than toggle or rotary switches.

Most scan-out and console output functions appear as formatted displays on the CRT rather than as panel lights.

To increase system availability and reliability, the system console can perform initial program loading using only the console processor and the diskette unit. For further information on functions, features and operations of the system console, see Appendix D.

#### **USAGE METERING**

System and maintenance meters are located in the system console next to the console processor. Which of these meters runs is a function of the maintenance key switch. Time is accumulated on the system meter when the switch is in the system position and the SYSTEM light is on. Time is accumulated on the maintenance meter when the switch is in the maintenance position. If there is no check condition in the CPU and the CPU is not in the STOP or WAIT state, or if the channels are active, then the SYSTEM light will be on.

FIGURE 11 OPERATOR'S CONTROL PANEL

#### OPERATOR'S CONSOLE PROGRAMMING

For 3066 emulation the system console CRT screen will display 35 lines of 80 characters each. Data may be read from or transmitted to any of these positions on the CRT under program control. Characters typed on the keyboard can be placed in any of these positions on the CRT, depending upon the location of the cursor. The screen is addressed by a two-byte buffer field and a two-byte cursor address field. The first byte in both address fields gives the line number (0 to 34); the second byte gives the position within the line (0 to 79). This form of address is used to control where information will be written on the screen from the program, which locations on the screen are to be transferred in response to a read from the program, and where the cursor will be placed for keyboard entry. A two-byte address is also returned to the program when the cursor position is requested.

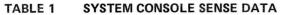

| SenseX'04'Reads two bytes of sense data (see Table 1).EraseX'07'Sets the entire screen to blanks, removes the cursor display,<br>resets CRT buffer address and cursor address to zeros.AlarmX'0B'Sounds a one-second tone and lights the alarm key.Set Buffer AddressX'27'Transfers a two-byte screen address to the console to designate<br>the starting byte position for a subsequent Read and Write<br>command.WriteX'01'Transmits EBCDIC data to be displayed, starting from the<br>current value of the CRT buffer address, and advances this<br>address by one for each byte transferred. The operation stops<br>when the CCW count is exhausted or when 2800 bytes are<br>written next.ReadX'06'Transfers data from the screen to the program, starting from<br>the current CRT buffer address, and continues until either<br>the CCW count is exhausted or the byte at the current cursor<br>position is transferred.Set CursorX'0F'Transfers a two-byte address to the console to indicate the<br>screen position is transferred.Read MIX'0E'Usually issued in response to an attention interruption caused<br>by either the "ENTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>by either the "ENTER" or the "CANCEL" (x80') for "ENTER"<br>and X'06' for "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>byte indicates which key was pressed (X'80') for "ENTER"<br>and X'06' for "CANCEL". |   | NOP                | X'03' | No operation.                                                                                                                                                                                                                                         |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AlarmX'0B'Sounds a one-second tone and lights the alarm key.Set Buffer AddressX'27'Transfers a two-byte screen address to the console to designate<br>the starting byte position for a subsequent Read and Write<br>command.WriteX'01'Transmits EBCDIC data to be displayed, starting from the<br>current value of the CRT buffer address, and advances this<br>address by one for each byte transferred. The operation stops<br>when the CCW count is exhausted or when 2800 bytes are<br>written next.ReadX'06'Transfers data from the screen to the program, starting from<br>the current CRT buffer address, and continues until either<br>the CCW count is exhausted or the byte at the current cursor<br>position is transferred.Set CursorX'0F'Transfers a two-byte address to the console to indicate the<br>screen position is transferred.Read MIX'0E'Usually issued in response to an attention interruption caused<br>by either the "ENTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address the tind<br>byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | Sense              | X'04' | Reads two bytes of sense data (see Table 1).                                                                                                                                                                                                          |  |

| Set Buffer AddressX'27'Transfers a two-byte screen address to the console to designate<br>the starting byte position for a subsequent Read and Write<br>command.WriteX'01'Transmits EBCDIC data to be displayed, starting from the<br>current value of the CRT buffer address, and advances this<br>address by one for each byte transferred. The operation stops<br>when the CCW count is exhausted or when 2800 bytes are<br>written. If position (34, 79) is reached, position (0, 0) is<br>written next.ReadX'06'Transfers data from the screen to the program, starting from<br>the current CRT buffer address, and continues until either<br>the CCW count is exhausted or the byte at the current cursor<br>position is transferred.Set CursorX'0F'Transfers a two-byte address to the console to indicate the<br>screen position at which the cursor should be displayed. If<br>the cursor was not previously displayed and the keyboard<br>was disabled, it can now be used to enter data onto the screen.Read MIX'0E'Usually issued in response to an attention interruption caused<br>by either the "ENTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                             |   | Erase              | X'07' |                                                                                                                                                                                                                                                       |  |

| WriteX'01'Transmits EBCDIC data to be displayed, starting from the<br>current value of the CRT buffer address, and advances this<br>address by one for each byte transferred. The operation stops<br>when the CCW count is exhausted or when 2800 bytes are<br>written. If position (34, 79) is reached, position (0, 0) is<br>written next.ReadX'06'Transfers data from the screen to the program, starting from<br>the current CRT buffer address, and continues until either<br>the CCW count is exhausted or the byte at the current cursor<br>position is transferred.Set CursorX'0F'Transfers a two-byte address to the console to indicate the<br>screen position at which the cursor should be displayed. If<br>the cursor was not previously displayed and the keyboard<br>was disabled, it can now be used to enter data onto the screen.Read MIX'0E'Usually issued in response to an attention interruption caused<br>by either the "CNTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | Alarm              | Х'0В' | Sounds a one-second tone and lights the alarm key.                                                                                                                                                                                                    |  |

| Current value of the CRT buffer address, and advances this<br>address by one for each byte transferred. The operation stops<br>when the CCW count is exhausted or when 2800 bytes are<br>written. If position (34, 79) is reached, position (0, 0) is<br>written next.ReadX'06'Transfers data from the screen to the program, starting from<br>the current CRT buffer address, and continues until either<br>the CCW count is exhausted or the byte at the current cursor<br>position is transferred.Set CursorX'0F'Transfers a two-byte address to the console to indicate the<br>screen position at which the cursor should be displayed. If<br>the cursor was not previously displayed and the keyboard<br>was disabled, it can now be used to enter data onto the screen.Read MIX'0E'Usually issued in response to an attention interruption caused<br>by either the "ENTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | Set Buffer Address | X'27' | the starting byte position for a subsequent Read and Write                                                                                                                                                                                            |  |

| Set CursorX'OF'Transfers a two-byte address to the console to indicate the<br>screen position at which the cursor should be displayed. If<br>the cursor was not previously displayed and the keyboard<br>was disabled, it can now be used to enter data onto the screen.Read MIX'OE'Usually issued in response to an attention interruption caused<br>by either the "ENTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • | Write              | X′01′ | current value of the CRT buffer address, and advances this<br>address by one for each byte transferred. The operation stops<br>when the CCW count is exhausted or when 2800 bytes are<br>written. If position (34, 79) is reached, position (0, 0) is |  |

| Read MIX'OE'Usually issued in response to an attention interruption caused<br>by either the "ENTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | Read               | X′06′ | the current CRT buffer address, and continues until either<br>the CCW count is exhausted or the byte at the current cursor                                                                                                                            |  |

| by either the "ENTER" or the "CANCEL" keys, this com-<br>mand returns three bytes of information to the program. The<br>first and second bytes are the current cursor address; the third<br>byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | Set Cursor         | X'0F' | screen position at which the cursor should be displayed. If the cursor was not previously displayed and the keyboard                                                                                                                                  |  |

| first and second bytes are the current cursor address; the third byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | Read MI            | X'0E' | by either the "ENTER" or the "CANCEL" keys, this com-                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                    |       | first and second bytes are the current cursor address; the third byte indicates which key was pressed (X'80') for "ENTER"                                                                                                                             |  |

| Sense Data: |       |                      |  |

|-------------|-------|----------------------|--|

|             |       |                      |  |

| Byte 0      | Bit 0 | Command reject       |  |

|             | Bit 1 | Reserved             |  |

|             | Bit 2 | Bus out check        |  |

|             | Bit 3 | Equipment check      |  |

|             | Bit 4 | Data check           |  |

|             | Bit 5 | Reserved             |  |

|             | Bit 6 | Buffer address check |  |

|             | Bit 7 | Reserved             |  |

| Byte 1      |       | Reserved             |  |

There are a few functional differences between the operation of the Amdahl 470V/6 system console in 3066 emulation as explained above and the operation of the 3066 system console. The following should be noted if exact compatibility is a requirement:

The 3066 keyboard has both upper and lower case alphabetic input even though the CRT displays only upper case. The Amdahl 470V/6 system console has only upper case alphabetic input.

The system console may respond to initial selection with a Control Unit Busy Sequence and Status =  $70_{16}$ . This sequence can occur if the selection was immediately preceded by a Halt I/O to the Console or if the console is selected while not in either 3066 or 3215 emulation mode.

## **MODEL-DEPENDENT FUNCTIONS**

The Amdahl 470V/6 System and the IBM System/370 are compatible within the constraints of System/370 architecture as specified in the *Principles of Operation*. This specification requires machine compatibility except in the following cases:

Programs relying on model-dependent data, such as the contents of logout areas

Time-dependent programs that rely on instruction or CCW execution times

Programs that cause deliberate machine checks

The Amdahl 470V/6 System has four areas of model dependence: the implementation of two instructions, the contents of CPU logout areas, machine check conditions, and channel logout. Only the first three are discussed here; channel logout is discussed in Appendix C.

#### **INSTRUCTION SET DIFFERENCES**

Two instructions have model-dependent results on the Amdahl 470V/6. They are:

STORE CPU ID (STIDP). This instruction causes certain model-dependent data to be stored at the double word addressed by the second operand address. In the Amdahl 470V/6 the version code field is reserved (bits 0-7). A unique serial number is stored in bits 8-31. The hexadecimal number 0470 is stored in the model number field (bits 32-47). Bits 48-63 are stored as zeros since the Amdahl 470V/6 performs the standard machine check extended logout to the memory of the console processor.

STORE CHANNEL ID (STIDC). Channel dependent data is to be stored at location 168. Since the 470V/6 channel type is implicit in the CPU model, zeros are stored in the channel model number field. The remaining fields (type and length) follow standard conventions.

#### **CPU LOGOUT AREAS**

Fixed CPU logout areas are assigned for storage of machine check logout information. Machine check logouts are the result of or associated with a machine error and result in storing model-dependent information.

#### FIXED LOGOUT AREA

The 104-byte area starting at location 248 is the fixed logout area. The Amdahl 470V/6 uses only the first 12 bytes of this area for fixed logout information. The failing storage address occupies the word starting at location 248; the region code is assigned to the two words starting at location 252. The remainder of the area, locations 260-351, is reserved.

The failing storage address (FSA) indicates the storage location or block that caused a correctable storage, an uncorrectable storage, or an uncorrectable key error. For a correctable storage error, bits 0-3 of the FSA contain the failing bit address; bits 8-31 contain the failing byte address. When an uncorrectable storage error is detected, bits 8-31 of the FSA may point anywhere within the failing 16-byte ECC block. When an uncorrectable key error is detected, bits 8-31 of the FSA may point anywhere within the failing 2048-byte protection block. In the case of multiple errors, the FSA may point to any one of the failing locations. In some cases an FSA cannot be stored. When this occurs, the FSA valid bit in the machine check interrupt code (MCIC) is set to zero. (The MCIC is discussed under machine checks).

Bytes 252–259 contain the region code that specifies where the error was detected. A summary of the region code bits is given in Table 2.

| Storage<br>Location | Bit | Source                                                               | Storage<br>Location | Bit | Source                                                                 |

|---------------------|-----|----------------------------------------------------------------------|---------------------|-----|------------------------------------------------------------------------|

| 252                 | 0   | I–Unit Pipeline Control Error                                        | 256                 | 0   | E–Unit Multiplier Byte Parity Error                                    |

|                     | 1   | E–Unit Condition Code Error                                          | 200                 | 1   | E–Unit Byte Adder Input 1 Parity Error                                 |

|                     | 2   | E–Unit LUCK1 Byte 0 Parity Error                                     |                     | 2   | E-Unit Byte Adder Input 2 Parity Error                                 |

|                     | 3   | E–Unit LUCK1 Byte 1 Parity Error                                     |                     | 3   | E-Unit Byte Adder Input 3 Parity Error                                 |

|                     | 4   | E–Unit LUCK1 Byte 2 Parity Error                                     |                     | 4   | S-Unit Bypass Error                                                    |

|                     | 5   | E–Unit LUCK1 Byte 3 Parity Error                                     |                     | 5   | S-Unit TLB Key Parity Error                                            |

|                     | 6   | E–Unit LUCK2 Byte 0 Parity Error                                     |                     | 6   | S-Unit TLB Logical Address Parity Error                                |

|                     | 7   | E-Unit LUCK2 Byte 1 Parity Error                                     | 10                  | 7   | S-Unit RAR Parity Érror                                                |

| 253                 | 0   | E Unit LUCK2 Pute 2 Parity Ever                                      | 257                 | 0   |                                                                        |

| 255                 | 1   | E–Unit LUCK2 Byte 2 Parity Error<br>E–Unit LUCK2 Byte 3 Parity Error | 257                 | 1   | I–Unit Result Byte 0 Parity Error                                      |

|                     | 2   | E-Unit Multiplicand Byte 0 Parity Error                              |                     | 2   | I-Unit Result Byte 1 Parity Error                                      |

|                     | 3   | E-Unit Multiplicand Byte 0 Parity Error                              |                     | 3   | I–Unit Result Byte 2 Parity Error<br>I–Unit Result Byte 3 Parity Error |

|                     | 4   | E–Unit Multiplicand Byte 2 Parity Error                              |                     | 4   | I–Unit EAG Parity Error (DA)                                           |

|                     | 5   | E–Unit Multiplicand Byte 3 Parity Error                              |                     | 5   | I–Unit EAG Parity Error (CI)                                           |

|                     | 6   | E–Unit Adder High-Input Phase Error                                  | 200                 | 6   | I–Unit Instruction Stream Entrance Parity Error                        |

|                     | 7   | E-Unit Adder Low-Input Phase Error                                   | Tresse<br>State     | 7   | I–Unit Store Data Parity Error                                         |

| 254                 | 0   | S–Unit Search Error                                                  | 258                 | 0   | S–Unit Address Translation Error                                       |

| 204                 | 1   | S-Unit Compare Register Parity Error                                 | 2.50                | 1   | S–Unit Channel Request                                                 |

|                     | 2   | S–Unit Tag Key Parity Error                                          |                     | 2   | C–Unit I/O Address Parity Error From I–Unit                            |

|                     | 3   | S-Unit Tag ID Parity Error                                           |                     | 3   | Reserved                                                               |

|                     | 4   | S–Unit Store Data Parity Error                                       |                     | 4   | C-Unit Error on CSW Store                                              |

|                     | 5   | Main Store Read Address Parity Error                                 |                     | 5   | Reserved                                                               |

|                     | 6   | Main Store Key Write Parity Error                                    |                     | 6   | Reserved                                                               |

|                     | 7   | Main Store Write Address Parity Error                                |                     | 7   | Reserved                                                               |

| 255                 | 0   | S–Unit Tag Control Parity Error                                      | 259                 | 0   | E–Unit Multiplier Residue Error                                        |

|                     | 1   | S-Unit Move Out Data Parity Error 0                                  |                     | 1   | E–Unit Adder Residue Error                                             |

|                     | 2   | S-Unit Move Out Data Parity Error 1                                  |                     | 2   | I-Unit Instruction Stream Exit Parity Error (DS)                       |

|                     | 3   | S-Unit Move Out Data Parity Error 2                                  |                     | 3   | S–Unit TLB Valid or ID Error                                           |

|                     | 4   | S–Unit Move Out Data Parity Error 3                                  |                     | 4   | I-Unit Control Register Bytes 0 - 1 Parity Error                       |

|                     | 5   | S–Unit Primary (1)/Alternate (0) Buffer                              |                     | 5   | I-Unit Control Register Bytes 2 - 3 Parity Error                       |

|                     | 6   | S-Unit Primary (1)/Alternate (0) TLB                                 |                     | 6   | I–Unit PSW Bytes 0 - 1 Parity Error                                    |

|                     | 7   | S-Unit Translation Register Segment/Page                             |                     | 7   | Reserved                                                               |

TABLE 2 REGION CODE

#### EXTENDED CPU LOGOUT

A machine check extended logout (MCEL) is performed by the console processor based on the setting of control register 14 bit 1, the synchronous MCEL mask. If the bit is on and a condition occurs that would normally cause an extended logout, the logout information is stored in the console processor.

The console processor detects the MCEL situation and performs a logout by scanning out all pertinent CPU latches to its own memory. This information can later be examined by a program in the main processor by issuing a special Diagnose instruction. After the console logout, the main processor is restarted to allow the CPU to continue its normal operation. If the console is not operational, the CPU is restarted by a time-out function and the MCEL is not performed. The CPU is informed of this action on the subsequent Diagnose.

Because MCEL data is saved in the console processor, the machine check extended logout area (location 512 and above) is not used by the Amdahl 470V/6. Control register 15, which normally contains the MCEL address, is not implemented and stores as all zeros.

The Diagnose instruction (operation code x'83') provides a means of communication between the CPU and the console processor for diagnostic and maintenance purposes. Because the operation of the Diagnose instruction may differ depending on the engineering change level of a particular system, documentation of this instruction is not provided in this manual.

#### **MACHINE CHECKS**

Extensive checking facilities are implemented in the Amdahl 470V/6. These include parity checking of instructions, registers and data, arithmetic checking of execution functions and effective address generation, and checking for certain illegal control sequences. When processing damage is detected, an attempt can usually be made to retry the instruction. (Details on which instructions are retryable are contained in Appendix B). If the retried instruction is successful, machine operation can continue and a system recovery condition is recognized. A similar retry facility is implemented in the 470V/6 channels. Additional correction facilities exist in the S-Unit for main storage error correction with automatic error checking and correction (ECC). The ECC field provides sufficient information to correct any single bit error for an associated group of 16 bytes. This type of correction is also recognized as a system recovery condition.

#### MACHINE CHECK CONDITIONS

A machine check condition is recognized for an uncorrectable error. A machine check condition is generated whenever an instruction or data with invalid parity is fetched, an arithmetic function is improperly performed, or invalid parity on the protection key makes it impossible to establish whether protection applies. Certain invalid control sequences can also cause a machine check condition. A machine check condition can be generated when instructions or data with invalid parity are fetched and before they are used.

If storage and registers contain valid information a machine check condition will be caused only by a machine malfunction, and never by an invalid instruction or data. If an unavailable component is specified the appropriate program, I/O interrupt or condition is set; a machine check condition is not generated.

A malfunction detected by the S-Unit during an I/O operation causes an external damage machine check condition. When the I/O operation is a fetch of a CCW or data, the malfunction is reported in the channel status word (CSW). When data is stored by the channel and a malfunction is detected in the S-Unit after status has been returned to the C-Unit, the CSW does not report the error. When the channel detects bad parity on an input operation, good parity is forced to the S-Unit and a channel data check is reported in the CSW.

An external I/O equipment malfunction detected in the channel is indicated in a CSW and not treated as a machine check condition. The error is reported as an I/O interrupt.

Machine malfunctions that cause machine check interrupts are grouped into two classifications, soft and hard machine checks. These correspond to repressible and exigent conditions defined in the *Principles of Operation*.

Soft machine checks comprise system recovery conditions, timer damage conditions, time-of-day clock damage, external damage and degradation conditions (associated with the S-Unit STO stack). Retryable errors and storage errors resulting from I/O or prefetch operations cause soft machine checks. These conditions do not terminate the current instruction or cause loss of interrupts.

Hard machine checks comprise instruction processing damage conditions (if retry is unsuccessful or impossible) and system damage conditions. Multiple bit storage errors, storage key parity errors, and internal CPU data transfer errors that are unretryable are considered hard machine checks. These conditions may result in termination of the current instruction or loss of interrupts.

#### MACHINE CHECK INTERRUPTS

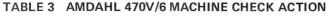

The machine check interrupt reports an equipment malfunction and supplies information about the location and nature of the malfunction. Actions taken by the Amdahl 470V/6 System in machine check condition are summarized in Table 3.

A soft machine check occurs after an instruction, including any associated SVC or program interruption, has completed. This is the same point at which an I/O interrupt occurs. Two classes of soft machine checks are retryable errors and corrected errors. A retryable error starts re-execution of the problem instruction; a corrected error is handled as a soft machine check (so far as point of interruption is concerned).

A hard machine check immediately inhibits further updating of machine state, including storage and registers, and points the instruction counter to the instruction farthest along in the pipeline. This action is taken immediately, before the end of an instruction, but still could have been caused by a part of the execution of any of the instructions in the pipeline (up to six).

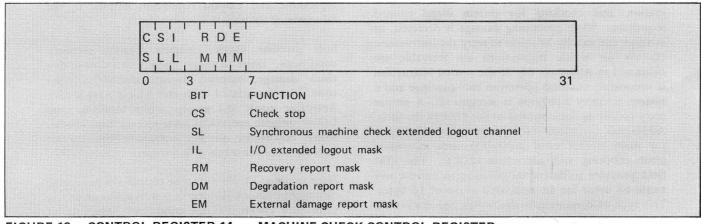

With the exception of processing of machine check extended logouts and the associated nonimplementation of control register 15, the Amdahl 470V/6 fully implements standard machine check handling as defined in the *Principles of Operation*. The significant bits of control register 14 and the machine check interrupt code (MCIC) for the Amdahl 470V/6 are detailed in Figures 12 and 13.

|                                                                | MCIC<br>STORED | SYS<br>DMG | PROC<br>DMG | SYS<br>REC | BACKUP | GPRs<br>STORED | FSA<br>STORED | REG<br>CODE<br>STORED |

|----------------------------------------------------------------|----------------|------------|-------------|------------|--------|----------------|---------------|-----------------------|

| SOFT MACHINE CHECK                                             |                |            |             |            |        |                |               |                       |

| CORRECTED                                                      | YES            | 0          | 0           | 1          | 0      | **             | **            | NO                    |

| RETRIED                                                        | YES            | 0          | 0           | 1          | 0      | **             | **            | **                    |

| HARD MACHINE CHECK                                             |                |            |             |            |        |                |               |                       |

| UNCORRECTED                                                    | YES            | 0          | 1           | 0          | †      | **             | **            | **                    |

| UNRETRYABLE                                                    | YES            | *          | *           | 0          | 0      | **             | **            | **                    |

| * = 1 AS APPROPRIAT<br>† = 1 IF NOT PAST RE<br>** IF AVAILABLE |                | DLD; ELSE  | = 0         |            |        |                |               |                       |

| PSTC | E D                       | SSK   | WMPIF FGC                       |    |

|------|---------------------------|-------|---------------------------------|----|

| DRDD | DG                        | BDECE | PSMAA PRR                       |    |

|      | 6 7 8                     | 14    | 20 24 27 28 29                  | 3  |

|      |                           |       | 111                             |    |

|      |                           |       | ТС                              |    |

|      |                           |       | RC                              |    |

|      |                           |       | 46 47                           | 63 |

| BIT  | FUNCTION                  | BIT   | FUNCTION                        |    |

| SD   | System damage             | KE    | Key in storage error corrected  |    |

| PD   | Processor damage          | WP    | PSW EMWP valid                  |    |

| SR   | System recovery           | MS    | PSW masks and key valid         |    |