## United States Patent [19]

## Milia et al.

[11] Patent Number:

4,979,099

[45] Date of Patent:

Dec. 18, 1990

| [54] | QUASI-FAIR ARBITRATION SCHEME<br>WITH DEFAULT OWNER SPEEDUP |                                                                     |  |

|------|-------------------------------------------------------------|---------------------------------------------------------------------|--|

| [75] | Inventors:                                                  | Andrew Milia, Burlington; Richard G. Bahr, Cambridge, both of Mass. |  |

| [73] | Assignee:                                                   | Apollo Computer Inc., Chelmsford, Mass.                             |  |

| [21] | Appl. No.:                                                  | 262,574                                                             |  |

| [22] | Filed:                                                      | Oct. 25, 1988                                                       |  |

| [51] | Int. Cl. <sup>5</sup>                                       | <b>G06F 13/14;</b> G06F 13/16;<br>G06F 13/18                        |  |

| [52] | U.S. Cl                                                     |                                                                     |  |

| [58] | Field of Sea                                                | 364/241.2<br>rch 364/200 MS File, 900 MS File                       |  |

| [56] |                                                             | References Cited                                                    |  |

|      | U.S. P                                                      | ATENT DOCUMENTS                                                     |  |

3,995,258

11/1976

Barlow

364/200

4,449,183

5/1984

Flahive et al.

364/200

4,536,839

8/1985

Shah et al.

364/200

| 4,554,628 | 11/1985 | Bell  | 364/200 |

|-----------|---------|-------|---------|

| 4,627,018 | 12/1986 | Trost | 364/900 |

Primary Examiner—David Y. Eng Attorney, Agent, or Firm—Weingarten, Schurgin, Gagnebin & Hayes

#### [57] ABSTRACT

A decentralized, pipelined, synchronous bus arbitration scheme which allows almost completely fair arbitration between multiple devices competing for the use of a communication bus while allowing the device that last used the bus faster access to the bus if no other device is competing for its use. The arbitration method and apparatus according to the present invention allows all competing devices equal access to the bus, with the exception that when bus requests are posted simultaneously, the device with the higher priority will always be granted use of the bus first.

8 Claims, 5 Drawing Sheets

4,979,099

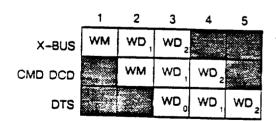

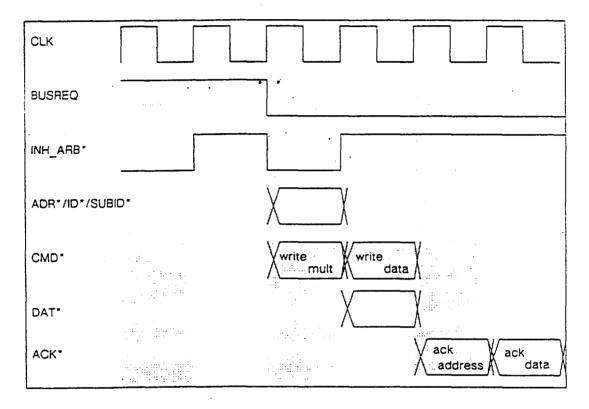

Fig. 2

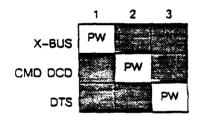

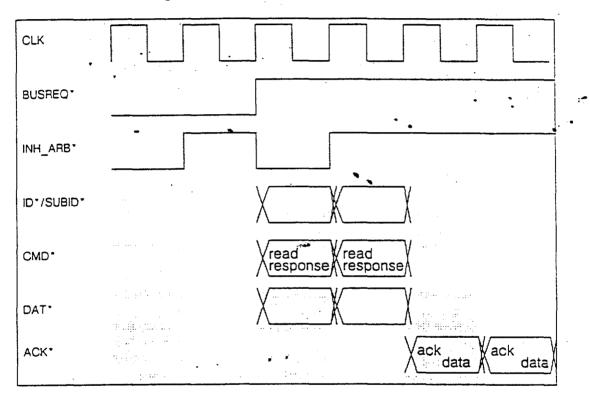

Fig. 3

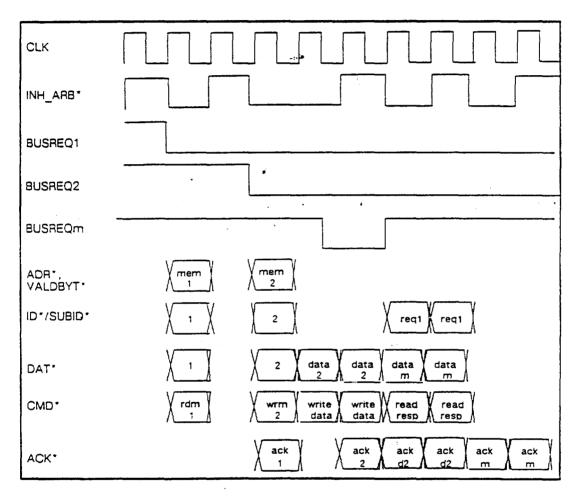

# SIMPLIFIED X-BUS LOCKING LOGIC IGNORES PIPELINED PROTOCOL EFFECTS

Fig. 4

Fig. 5

#### **OUASI-FAIR ARBITRATION SCHEME WITH** DEFAULT OWNER SPEEDUP

#### FIELD OF THE INVENTION

The present invention relates to computer system arbitration schemes, in particular, arbitration schemes providing a fair allocation of system resources.

#### BACKGROUND OF THE INVENTION

Computer systems include a variety of processing units, each seeking access to and control of system resources. Strict priority allocation schemes preclude lower priority units from obtaining necessary access. Thus, there is a need for a priority allocation scheme that avoids complete lock-out of, lower priority units.

#### BRIEF DESCRIPTION OF THE INVENTION

According to the present invention, when a device 20 'A' needs to use the bus to which it is connected, it asserts its request signal and, during the same cycle, looks for any other device's request signal. If no other device is requesting during the cycle, then device A becomes the bus owner during the following cycle. If 25 another device 'B', asserts its request signal during the same first cycle, then the requesting device with the highest priority is bus owner during the following cycle. The lower priority device will become bus owner immediately following the higher priority device's last 30 cycle as bus owner. The requesting device with the highest priority always wins bus ownership.

During the final cycle of bus ownership, the bus owner takes a "snapshot" of, i.e., ascertains and stores the state of all the request signals belonging to the lower 35 priority requesting devices, and will not reassert its request signal until all of the requests that were noted by the snapshot having been satisfied.

If during a device's last cycle as owner, or during subsequent cycles, device A requires another bus trans- 40 fer and no other device has requested the bus since it originally gained bus access, then the owner becomes the owner again by default and need not reassert its request signal, thus allowing it access to the bus one signal prior to renewing its ownership of the bus.

The arbitration scheme is implemented by providing identical arbitration apparatus disposed within each device. Thus, the apparatus employed to implement the and so the arbitration scheme is effectively decentralized.

This technique provides multiple devices with equitable access to a bus using a minimum of control signals, while minimizing the cycles used for arbitration.

#### BRIEF DESCRIPTION OF THE DRAWING

These and other features of the present invention will be better understood by reading the following detailed description of the invention, taken together with the 60 drawing wherein

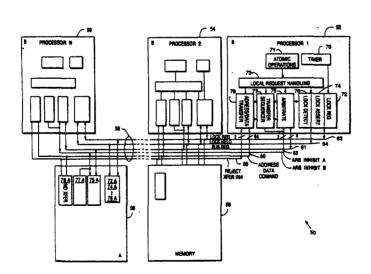

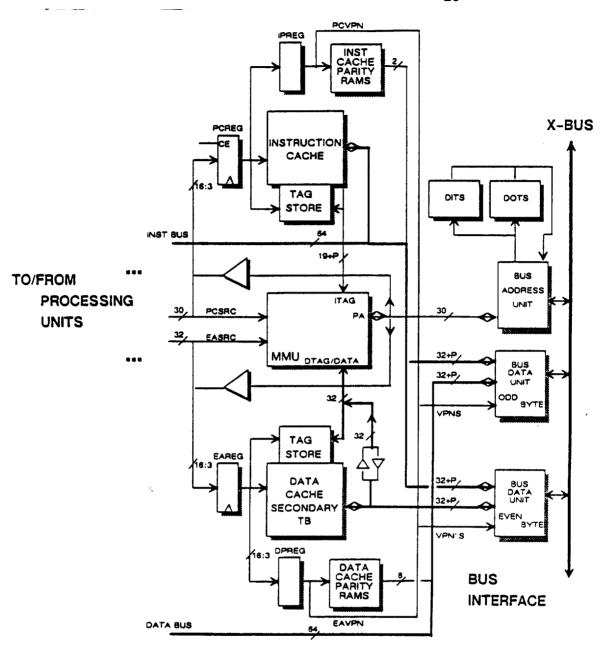

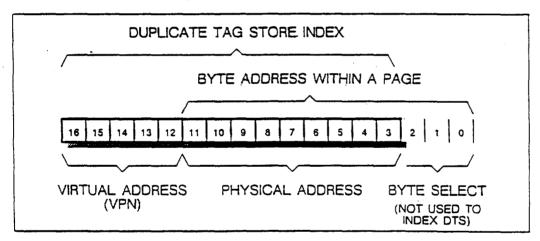

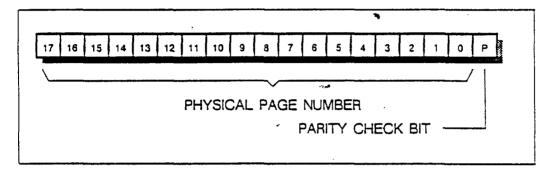

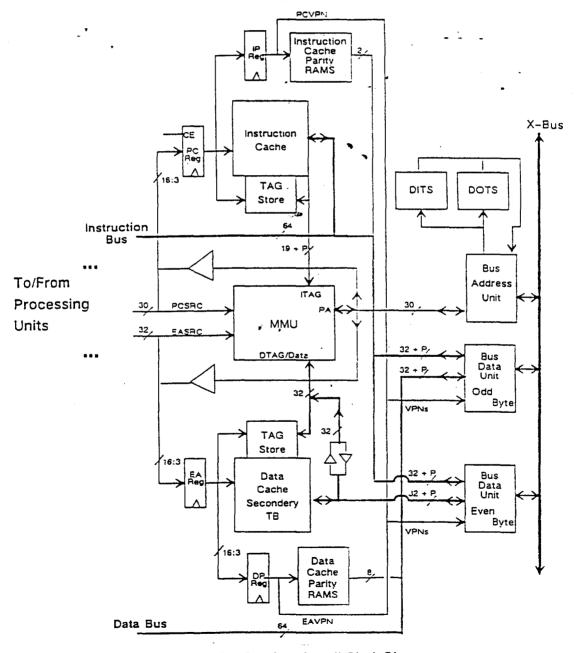

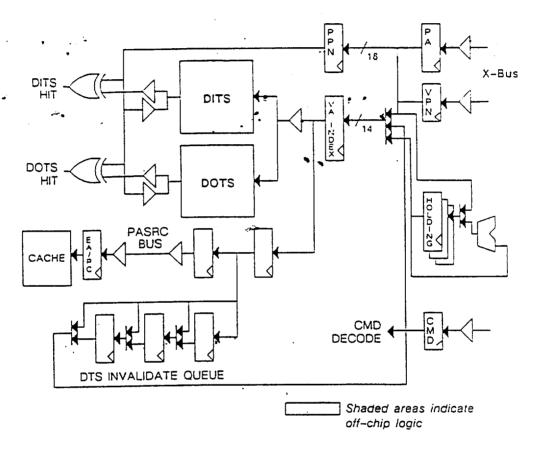

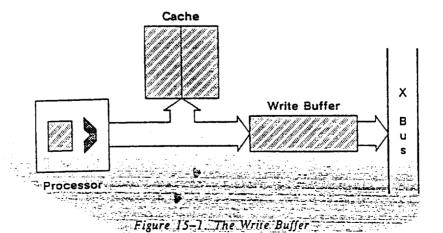

FIG. 1 is a block diagram of a computer system embodiment of the present invention;

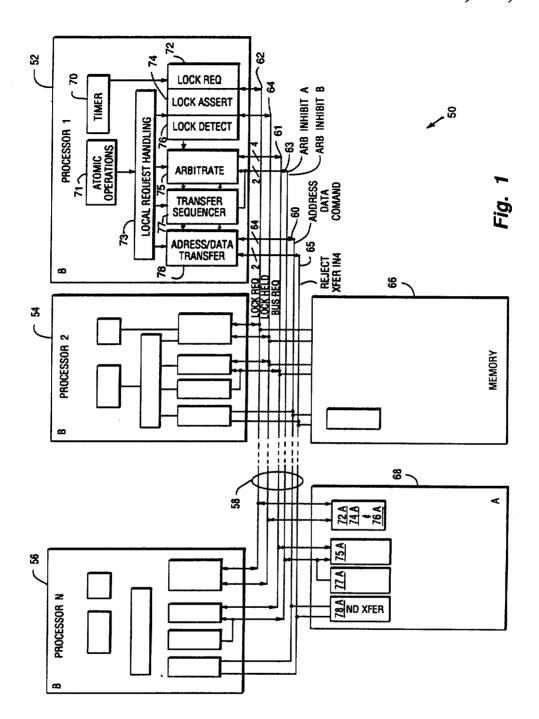

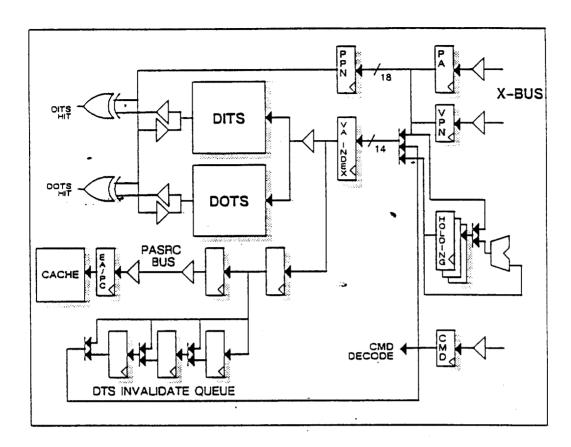

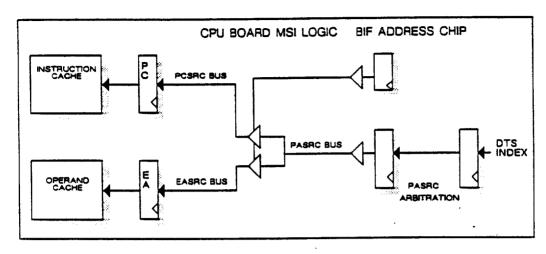

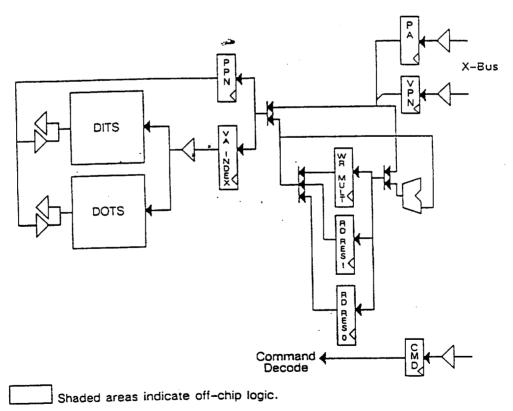

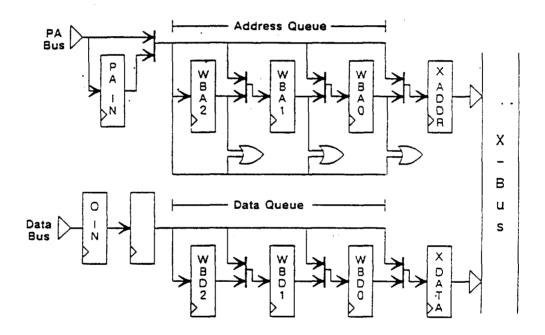

FIG. 2 is a block diagram of one embodiment of a bus interface unit:

65

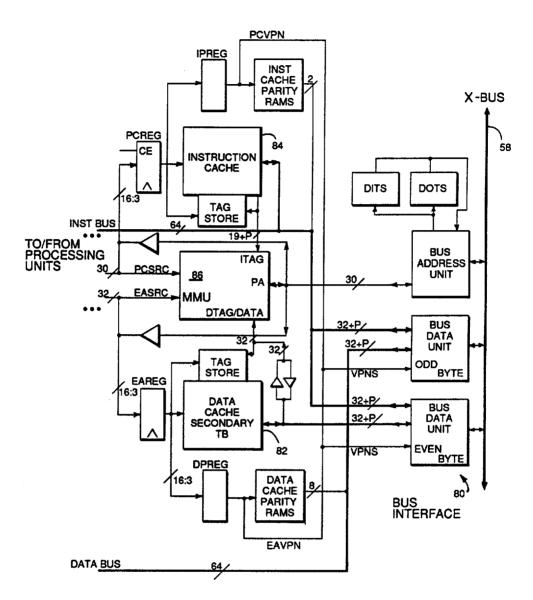

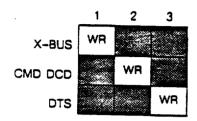

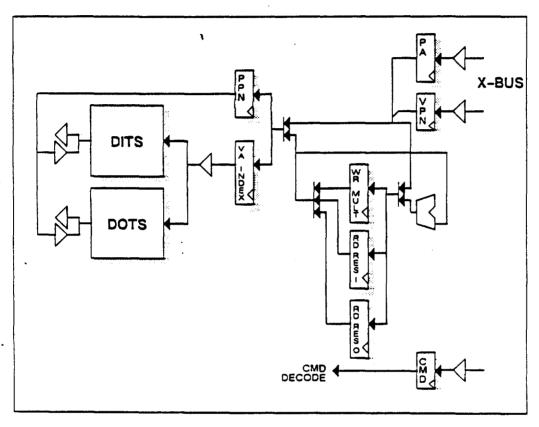

FIG. 3 is a block diagram of the interconnection of one embodiment of the lock acquisition and bus arbitration blocks of the bus interface;

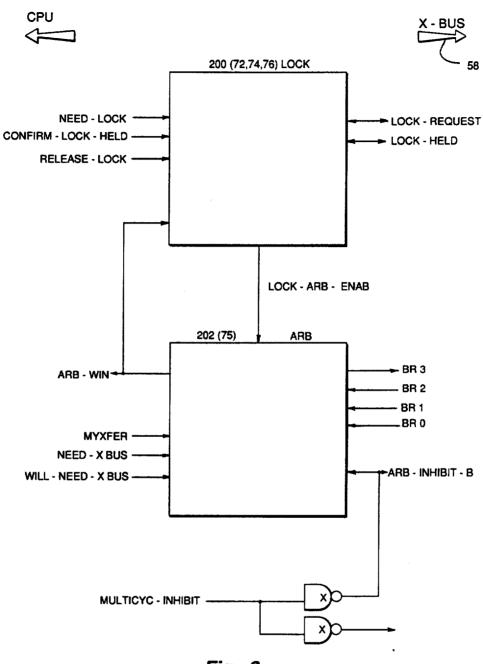

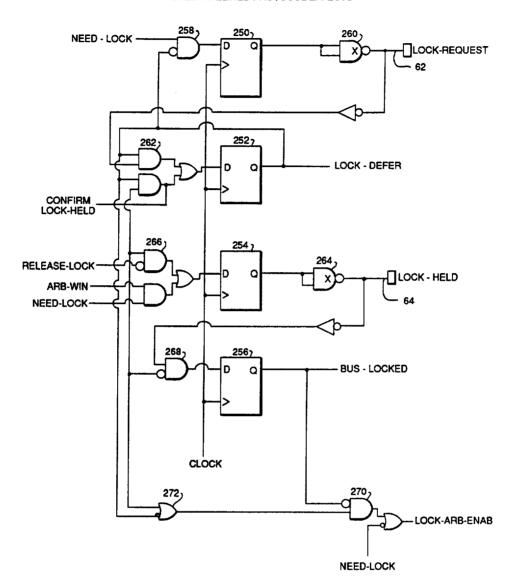

FIG. 4 is a schematic diagram having further detail of the lock.acquisition and requesting blocks 74 and 72 of the embodiment of FIGS. 1 and 2; and

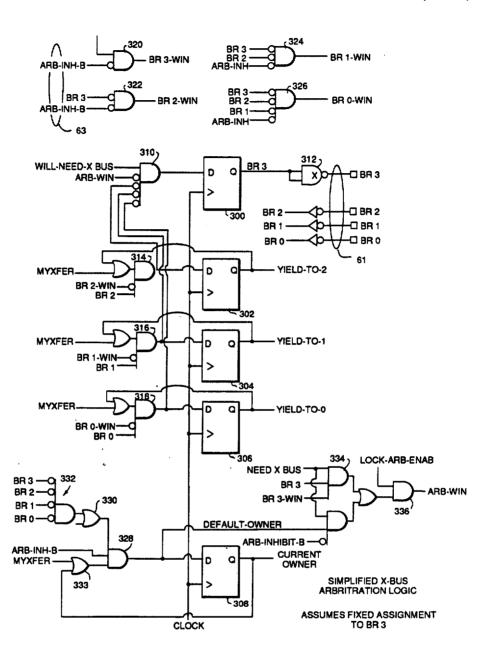

FIG. 5 is further detail of the bus arbitration block 75 5 of the bus interface of the embodiment of FIGS. 1 and

Further details of one embodiment of the present invention are provided in the appendix, wherein:

Appendix I provides a processor bus interface specifi-10 cation;

Appendix II provides a bus signal specification; and Appendix III provides further structural description of the processor-bus interface.

#### **DETAILED DESCRIPTION OF THE** INVENTION

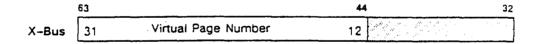

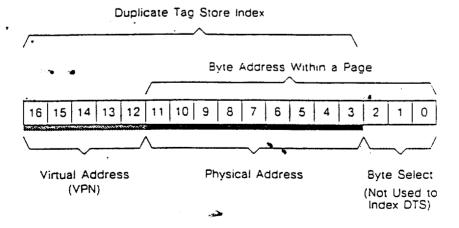

As shown in FIG. 1, the processors 52, 54, and 56 and memory units 66 and 68 are devices connected to a bus 58 via interface elements 70, 71, 72, 73, 74, 75, 76, 77, and 78 described in more detail with regard to bus signalling in APOLL-111XX, entitled MULTIPROCES-SOR INTERLOCK, filed concurrently herewith and incorporated by reference. Initially assume memory unit 68 is a sole default owner of the bus.

All device on the bus 58 except the default owner must request the bus prior to use. There is one bus request level on the backplane per device on the bus 58. Devices are grouped into two classes. Class A devices are awarded the bus in strict priority order i.e., the highest class A device gets access to the bus. Class B devices participate in fair arbitration and may also be default bus owners. Processors 52, 54 and 56 are class B devices.

Bus arbitration is decentralized arbitration is achieved by the collective action of interface elements 70, 72, 74, 75, 76 and 78 disposed in each device on the bus. Every device decides for itself whether it has won access to the bus 58. Bus arbitration can be inhibited by the assertion of an arb inhibit signal on leads 63. Only the current owner of the bus may assert an arb\_inhibit signal. The current owner will do so if the intended bus transfer requires multiple cycles.

If a class A device 68 requests the bus, it will assert cycle sooner than if it were required to assert its request 45 both its assigned request level 61 and the ARB\_IN-HIBIT\_B 63 line on the bus. When a class B device detects the assertion of ARB\_INHIBIT\_B in an active bus arbitration cycle, it will defer to the class A device.

The class B devices, e.g., processors 52, 54, and 56, arbitration scheme is distributed over all the devices, 50 are each assigned a fixed priority. Potential assignments are 0 through 3, with 3 being the highest priority. The assignment is used to determine which of the four class B request parallel backplane signals this particular processor is to use. The processor will drive its assigned 55 level, and defer to requesters at higher levels.

Fair arbitration is approximated whereby class B devices do not reassert their request lines unconditionally. Rather, a class B device will "snapshot", i.e., read and store all other lower priority class B request lines in the final cycle of its bus ownership. The class B device will then relinquish the bus and not reassert a request line until all the snapshotted requests are, or are about to be, satisfied. The class B device determines that the other requesters have been serviced by observing the current state of the other request lines. If a request line is deasserted, service is underway or completed. If a request line is still asserted, but arbitration is enabled and that requesters will win, service is presumed.

When the bus 58 is otherwise idle, the last successful bidder among the class B requesters is also established as the default bus owner. The default bus owner may use the bus at the end of any cycle in which no other request line was asserted. The default bus owner does not have to assert its assigned request line. The default status remains in effect until another class B device wins the bus.

A class B device's bus ownership may be suspended of the bus, the class B device that was the former owner waits for the bus to again become idle. The class B device then reclaims bus ownership; i.e., the class B device reassumes the ownership in the cycle following one in which arbitration was permitted, but no request 15 line was asserted. If another class B device wins the bus before the bus becomes idle, default bus ownership is transferred to the winning device.

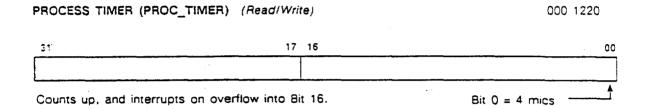

When a device first asserts a bus request line, it will start a timer 70. If the timer elapses before the bus is 20 acquired, a bus acquisition timeout occurs. The bus timeout duration is approximately 3.2 milliseconds. If a timeout occurs, the system is assumed broken and a clock (not shown) freeze request is made.

The timer 70 is not stopped until a request is con- 25 firmed to complete or fail, the timer will therefore expire if a device is continually busy. Broadcast transfers will stop the timer regardless of the acknowledge line state. The same timer 70 is reused for read data return monitoring.

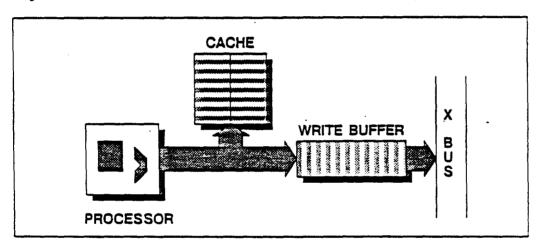

Shown in FIG. 2 are multiple competing local requesters: data cache 82 read, data cache write and instruction cache 84 read. Any number of data cache writes, up to the limit of the write queue size, may be read may be posted from each of the read request sources: the data cache read and the instruction cache read. In general, data cache read will be prioritized over instruction cache read. In turn, instruction cache read following exceptions exist:

if the write data queue is full, data cache write is prioritized over instruction cache miss;

if a data cache miss collides in address with a previover both data and instruction cache miss;

if a write and unlock is queued, data cache write is given priority over both data and instruction cache miss:

if a data cache miss from an unencacheable memory 50 location is posted, data cache write is given priority over both data and instruction cache miss:

if a data cache miss and lock is posted, data cache write is given priority over both data and instruction cache read:

if a data cache miss and unlock is posted, data cache write is given priority over both data and instruction cache read;

if a tb invalidate is queued in the write buffer, data data cache miss.

A fourth source of request for the return of read data, to itself, is given precedence over all other transmitters.

Subsequent requests from the data cache will be issued no more often than every other bus cycle. This is 65 required to assure write order between processors, and read-write order within one. Further details of system bus protocol relating to the reject signal is provided in

APOLL-113XX, entitled PIPELINE COMPUTER SYSTEM HAVING WRITE ORDER PRESERVA-TION, filed concurrently herewith and incorporated herein by reference. The instruction cache miss request is not restricted to every other cycle. In the cases of load and lock, load and unlock, and store and unlock, subsequent requests are not issued until a successful bus

acknowledge of the prior request is received. With reference to FIGS. 1 and 2, the address/data by a class A device. If a class A device assumes control 10 transfer unit 78 of a device 52, for example, accepts load lock, load unlock and store unlock command from the Memory Management Unit 86 (MMU) disposed within the local request handling unit 73. When load lock completes successfully, that device 52 can be assured of holding the bus lock until the device 52 explicitly releases the lock or an error arises. Only one device at a time may hold the bus lock and that, in turn, permits the construction of critical code sections in a multiple processor environment. Further details are provided in APOLL-111XX, incorporated herein by reference.

The bus lock will be secured only when a load lock data cache miss is successfully issued and acknowledged on the bus. In more detail, first the data cache miss which seeks the bus lock is posted. This request will push ahead of itself all previously queued up writes. When the lock request is next to be serviced, the current state of the LOCK\_HELD 64 and LOCK\_RE-QUEST 61 lines is examined. If LOCK\_HELD lock is already asserted by another device, the arbitration is 30 deferred. If the bus lock is available, arbitration is attempted. If the bus lock signal is subsequently asserted before the device gains access to the bus, the device will withdraw from further arbitration. When the bus is finally secured, and ARB\_INHIBIT\_A and ARposted and awaiting transfer on the bus. Only a single 35 B\_INHIBIT\_B and LOCK\_HELD signals are simultaneously asserted. ARB\_INHIBIT\_A and ARB\_IN-HIBIT\_B remain asserted for 3 cycles which is sufficient time for all other bus interfaces to see the LOCK-HELD signal asserted and to withdraw from arbitrawill be prioritized over data cache write. However, the 40 tion if they too plan to secure the bus lock. At the end of 3 cycles, the locking device will also examine the state of the acknowledge signals. If other than a successful acknowledge is detected, the bus lock is immediately released. If released, the LOCK\_HELD signal is deasously queued write, data cache write is given priority 45 serted at the end of the cycle following the acknowledge.

A device will release the bus lock when a load unlock or a store unlock is successfully issued and acknowledged. Alternatively, the lock is released upon an error in the local processor. A local processor error is assumed to result in a processor trap, and the signal trap dispatch, which so indicates, is therefore used to unconditionally release the bus lock. In more detail, first the data cache read or write which seeks to release the bus 55 lock is posted. This request will push ahead of itself all previously queued up writes. At the end of 3 cycles, the locking device will also examine the state of the acknowledge signals. If other than a successful acknowledge is detected, the bus LOCK\_HELD 64 is retained. cache write is given priority over both instruction and 60 Otherwise, the lock signal is deasserted at the end of the cycle following the acknowledge.

If a lock request is met with REJECT signal 65, the LOCK\_REQUEST signal 62 and ARB\_INHIBIT\_A and ARB\_INHIBIT\_B 63 are immediately released. Similarly, if an unlock request is met with a REJECT signal 65, the lock is retained if held.

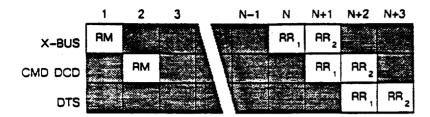

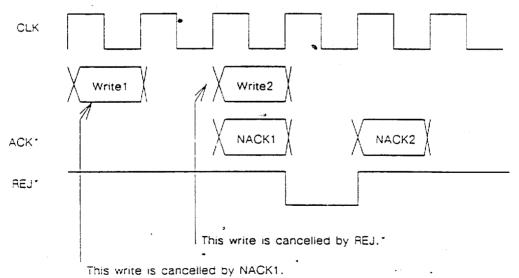

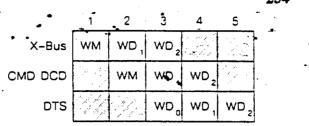

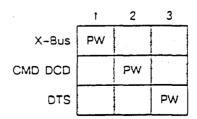

Two successive bus address transfers may be issued by a device in bus cycles spaced apart by only one NOP

or foreign cycle. If the first request receives a busy acknowledge, the acknowledge is received only after the second request has been sent. In this case, the bus REJECT signal on lead 65 is immediately asserted. The REJECT signal is interpreted by a slave as nullifying 5 the already accepted request. This use of REJECT assures that the order of transfers on the bus is retained. This is particularly important when the second request is a read for the same data that is being written by the first request. When REJECT is asserted, the acknowl- 10 edge for the second request is ignored. When REJECT is asserted, all transaction side effects, such as bus locking, do not take place.

It's possible for the MMU of a device to request the bus lock while the device is already in possession of the 15 bus lock. For this reason, a second load lock request will be accepted. If two bus lock requests have been accepted, two bus unlock requests will need to follow to one embodiment of the present invention, bus lock 20 tion protocol. A glossary follows: before the lock will really be released. Thus, according requests are nested by two levels.

A timer 70 starts running when the bus lock is first acquired. The timer 70 remains running so long as the device holds the bus lock. If the timer expires before the lock is released, a lock timeout trap is posted. The timer duration is approximately 200 microseconds. If a timeout trap occurs, a corresponding register (not shown) indicates so. If a second lock setting request is processed before a held lock is released, the timer is not reset. This results in a somewhat shorter timeout for the second request. If an unlock request is being transferred upon the bus, the device refrains from bidding for a new lock request for at least five cycles including the transferring one. This delay assures that there will always be two 35 cycles of delay between the release of a lock and its reacquisition by the same device.

A device will retry any request that receives a BUSY acknowledge. The retry will continue until the bus timeout expires. If an address transfer receives a BUSY 40 acknowledge, the request is marked as in retry. There can be as many as three requests in retry at any one

The use of REJECT in cooperation with the write order assurance of the write queue, guarantees that the 45 write order of one device is always preserved as seen by a second processor. This can permit alternate multiprocessor synchronization without the need for bus locking.

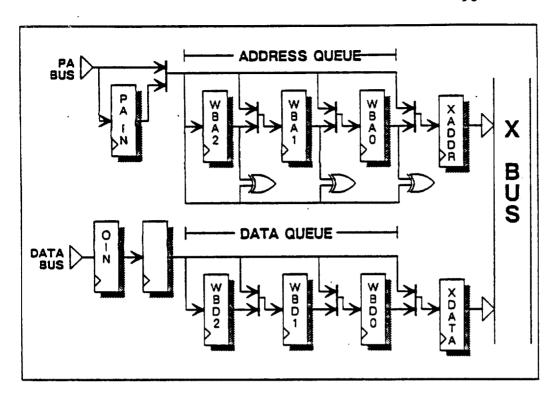

As shown in FIG. 3, the arbitration 75 and lock con- 50 trol blocks 72, 74, 76 of the bus interface 80 of the processor 52 attach to both the system's bus 58, and the processor's local request generation logic 73. A brief glossary of the signals generated or received by the local request generation logic follows:

NEED\_LOCK is asserted to identify that the next processor read to be serviced requires the acquisition of a bus lock.

CONFIRM\_LOCK\_HELD is asserted to identify that a processor "read and lock" which just took place 60 the bus as described in the next paragraph. This LOCKhas been properly acknowledged on the bus. This signal handles the situation that a bus operation may fail to complete successfully even though arbitration succeeds.

RELEASE\_LOCK is asserted when the processor wishes to abandon a bus lock. The processor chooses to 65 this processor of LOCK\_HELD by state element 254 do so when a "read and unlock" or "write and unlock" operation has been properly acknowledged on the bus. The processor may also choose to do so if there has

6 been a local error such as lock holding duration time-

ARB\_WIN is asserted by the bus arbitration logic 75 when the processor has been awarded the right to transfer on the bus 58.

MYXFER is asserted by the address/data transfer logic 78 when an address or data transfer is underway.

NEED\_BUS is asserted by the processor when there is a pending and unserviced processor read or write.

WILL\_NEED\_BUS is asserted by the processor when there "will be" a pending read and unserviced read or write in the next cycle. The advance warning of the need for service permits the early assertion of a bus\_request signal.

MULTICYC\_INHIBIT is asserted by the address-/data transfer logic 78 when a request is underway that requires the sustained and uninterrupted use of the bus.

Also as shown in FIG. 3, there are a number of bus control signals involved in the locking bus and arbitra-

LOCK\_REQUEST- (62) is asserted by a processor when it wishes access to a bus lock and is not blocked from acquiring the lock for fairness reasons.

LOCK\_HELD- (64) is asserted by a processor when 25 it holds the bus lock.

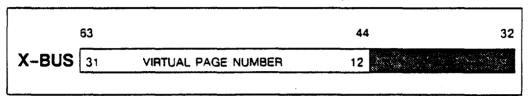

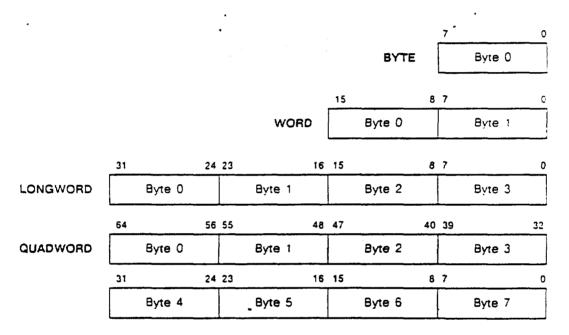

BR3-, BR2-, BR1- and BR0- (61) are the four bus request lines associated with four respective processors. (A number other than four may also be chosen.)

ARB\_INHIBIT\_B- (63B) is asserted when the "B" 30 level bus requesters are to be inhibited from bidding for the bus.

ARB\_INHIBIT\_A- (63A) is asserted when the "A" level bus requesters are to be inhibited from bidding for

The signal LOCK\_ARB\_ENAB is asserted and driven by the lock acquisition and request block 200 (72,74,76) to the bus arbitration block 200 (75) to indicate that a processor 52 request may proceed.

The lock arbitration and request block 200 is shown in more detail in FIG. 4. There are four state elements: 250, 252, 254 and 256, which drive and interpret the bus control signals LOCK\_REQUEST- 62 and LOCK-HELD- 64. When a processor, or other device on the bus requires a bus lock, it asserts the signal NEED... LOCK. NEED\_LOCK will cause the state element 250 to be set if not inhibited from doing so by state element 252 via gate 258. If element 250 is set, gate 260 will drive the open collector signal LOCK\_RE-QUEST- 62 on the backplane. NEED\_LOCK is assumed to be deasserted when the processor has been granted access to the bus so that the request is withdrawn at the correct time. State element 252 inhibits the assertion of LOCK\_REQUEST- if this processor had once held the bus lock during the duration of time when 55 LOCK\_REQUEST- had been uninterruptively asserted, providing the basis for the fairness in the acquisition of the bus lock. LOCK\_DEFER prevents this processor from asserting the LOCK\_REQUEST- signal, as well as preventing this processor from acquiring \_DEFER situation as recorded in element 252 is set when the CONFIRM\_LOCK\_HELD signal is presented to gate 262. Gate 262 also sustains the LOCK-DEFER situation for the duration of the assertion by or for the uninterrupted assertion of the external LOCK\_REQUEST- signal. The open collector signal LOCK\_HELD- 64 is driven by gate 264 whenever

state element 254 is set. The state element 254 is set when the processor is awarded the bus, i.e., ARB\_WIN is asserted, and the processor needs the bus lock, i.e., NEED\_LOCK is asserted. Gate 266 determines this. Gate 266 also sustains the lock holding until the 5 RELEASE\_LOCK signal is presented by the processor. State element 256 is set whenever the bus is locked for access by another processor. Gate 268 determines this situation by noting that the LOCK\_HELD- 64 ment 254 is not set. When element 256 is set, a lock requiring processor read cannot be allowed to proceed. This determination is made by the combination of the gates 270 and 272 and presented to the bus arbitration logic in the signal LOCK\_ARB\_ENAB. LOCK\_AR-B.ENAB is always set when the processor does not need the bus lock, i.e., NEED\_LOCK is deasserted. Alternatively, LOCK\_ARB\_ENAB is set when the bus is not locked, i.e., state element 256 is not set and either of two conditions prevail according to gate 272. The first condition is simply that this processor already holds the bus lock, i.e., state element 254 is set. The second condition is that there is no lock acquisition driven by state element 252 is not asserted.

The bus arbitration and request block is shown in more detail in FIG. 5. For purposes of simplicity, this block is drawn as if the processor was permanently fixed at bus request level 3. In the actual implementation, additional logic is present to permit the processor to request at any request level and can be provided according to the detail of FIG. 5. Also, the current implementation supports only 4 requesters, but there is or lesser number may be accommodated. In the discussion to follow, "B level requesters" and "processors (52, 54, 56)" are to be considered synonymous. However, in other implementation that need not be so.

In FIG. 5, there are five state elements: 300, 302, 304, 40 306 and 308, which drive and interpret the five bus request signals 61 BR3-, BR2-, BR1-, BR0 and AR-B\_INHIBIT\_B-. State element 300 is the bus request flipflop. State elements 302, 304 and 306 snapshot, i.e., sample the state of the other processor bus request sig- 45 nals to be used in the fairness deference algorithm of this processor. State element 308 reflects whether this processor is the default owner of the bus.

Gates 320, 322, 324 and 326 determine if one of the four processors may secure the bus in the next cycle. 50 BR0...WIN is asserted by gate 326 if all higher priority requests (BR3, BR2 and BR1) are not asserted, and B level request arbitration is not inhibited, i.e., ARB\_IN-HIBIT\_B is not asserted. Similarly, BR1\_WIN is as-WIN by gate 320. The processor associated with request level three can only fail to win the bus if AR-B\_INHIBIT\_B is asserted. ARB\_INHIBIT\_B- is asserted on the bus, by this processor or others, for one of two reasons. The first reason is that the current trans- 60 fer requires multiple uninterrupted bus cycles. In that both ARB\_INHIBIT\_B- and ARB\_IN-HIBIT\_A- are driven by the address/data transfer block 78 to suspend all new arbitration for the bus. The second reason is that an "A" level requester wishes 65 access to that bus. If any "A" level device requests the bus, that device must also drive the signal ARB\_IN-HIBIT\_B- to suspend all "B" level device arbitration.

In this manner, "A" level devices are assured total priority over "B" level devices.

The bus request flipflop 300 is set when the processor wishes to use the bus, i.e., WILL\_NEED\_BUS is asserted, and the processor has not just secured the use of the bus, i.e., ARB\_WIN is not asserted, and the processor is not deferring to any of the other three processors. This combination of events is determined by gate 310. Once flipflop 300 is set, gate 312 unconditionsignal is asserted, but the local lock holding state ele- 10 ally drives the bus signal BR3- so that other processors may decide arbitration as well. Bus request deference is in effect if any of the three signals driven by gates 314. 316 or 318 are asserted. Conceptually, these gates are asserted if the associated bus request signal is currently asserted and the requestor will not be serviced next, or if the associated bus request signal had been asserted when this processor had last transferred on the bus and there has been no service granted since that time. Specifically, gate 314, for example, will be asserted if BR2 20 is asserted and BR2 will not be granted the bus in the next cycle, i.e., BR2\_WIN is not asserted, and one of two conditions prevail. The first condition is that the current bus cycle is owned by this processor, i.e., fairness deference in effect, i.e., LOCK\_DEFER 25 ment 302 is set. The state element 302 is set if the condition of BR2 asserted and BR2\_WIN not asserted was true at the time of the last bus operation by this processor. This combination of conditions assures that a processor will not reacquire the bus twice in succession, 30 thereby providing other bus requesters an opportunity to acquire the bus.

State element 308, CURRENT\_OWNER, is set when this processor is the last one to transfer on the bus and the element remains set until another "B" level no fundamental restriction in this number and a greater 35 requester acquires the bus. Specifically, gate 328 will allow the element to be set if it is already set or the current transfer belongs to this processor (as decide by gate 333) and no other processor will acquire the bus in the next cycle. Other processors may not acquire the bus either because ARB\_INHIBIT\_B is asserted or because no other processor is requesting the bus. These events are combined in gate 330, with gate 332 detecting the absence of other "B" level requests.

Finally, ARB\_WIN is asserted if this processor is granted access to the bus in the next cycle. Gate 336 drives the signal if there is the lock acquisition and request blocks 74 and 72 drive the LOCK\_ARB\_ ENAB signal and the processor otherwise is awarded the bus. This condition assures that a processor will not get access to a locked bus if the processor also requires lock acquisition. Gate 334 decides whether the processor is otherwise awarded the bus. The processor may be so awarded for two reasons. In the first case, it is awarded the bus if the bus is needed (NEED\_BUS), the serted by gate 324, BR2\_WIN by gate 322, and BR3\_ 55 associated bus request line is asserted (BR3), and the bus prioritization logic says there is no higher priority requester (BR3\_WIN). The second situation is the one of default ownership. Again, the bus must be needed (NEED\_BUS), there must be no ARB\_INHIBIT\_B. In effect, and this processor is the default owner as already decided by gate 328. Gate 334 responds to all of these events.

Modifications and substitutions of the present invention by one of ordinary skill in the art are considered to be within the scope of the present invention, which not to be limited except by the claims which follow.

## APPENDIX I

# CPU - XBUS INTERFACE SPECIFICATION

Andrew Milia Rick Bahr

Revision: 1.1

This document contains confidential and proprietary information which is the sole property of Apollo Computer Inc. Its use is restricted to employees of Apollo Computer Inc.

11 4,979,099

# **CONTENTS**

| CHAPTER | 1 OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1     | Major Responsibilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.2     | BIF Overall Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3     | Bus Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CHAPTER | 2 XBUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1     | XBUS Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1.1   | Class A Request Override                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1.2   | Class B/CPU Requesting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1.3   | Default Ownership                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.1.4   | Acquisition Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1.5   | Local Request Prioritization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1.6   | Subsequent Request Arbitration Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.2     | XBUS Reads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2.1   | Read Initiating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2.1.  | 1 Read Initiation Bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2.2   | Read Data Return                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2.3   | Read Return Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| . 2.2.4 | Read Return Minimum Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2.5   | Read Return Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.3     | XBUS Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.3.1   | XBUS Write Multiple Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.2   | XBUS Initial Write Hold Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |