# Antares Rev. C

Instruction Set Reference Manual

1/15/1987

The material in this document is confidential and may not be copied for any purpose.

Do not show this material to anyone, inside or outside Apple.

| Copy | Assigned | to |  |

|------|----------|----|--|

|------|----------|----|--|

## **Table of Contents**

| List of Tables                             |                                         | <b>ji</b> i |

|--------------------------------------------|-----------------------------------------|-------------|

| Introc Programming Model Special Registers | duction                                 | 1           |

| Special Degisters                          | •••••••                                 | 1           |

| Traps and Interrupts                       | *************************************** | Ç           |

| Condition Codes.                           |                                         |             |

| Notation                                   |                                         |             |

| Quick-Reference                            |                                         | 18          |

|                                            |                                         |             |

| Instru                                     | uctions                                 | ***         |

| Add with Carry Partial (AdCP)              |                                         | 24          |

| Add (Add)                                  |                                         | 25          |

| Add Immediate (Add)                        |                                         | 26          |

| Add with Carry (AddC)                      |                                         | 27          |

| Add Partial (AddP)                         |                                         |             |

| Add Program Counter (AdPC)                 |                                         |             |

| And (And)                                  |                                         |             |

| And Complement (AndC)                      |                                         |             |

| Branch on Condition (Bcc)                  |                                         |             |

| Create Data Cache Line (CDC)               |                                         |             |

| Clear Field (ClrF)                         |                                         |             |

| Clear Mode (ClrM)                          |                                         |             |

| Count Leading Zeroes (CLZ)                 |                                         |             |

| Compare (Cmp)                              | *************************************** | 39          |

| Compare Immediate (Cmp)                    |                                         |             |

| Compare Partial (CmpP)                     |                                         |             |

| Deposit (Dep)                              |                                         |             |

| Divide (Div)                               |                                         |             |

| Double Shift (Dsh)                         |                                         |             |

| Extract Signed (ExtS)                      |                                         | 48          |

| Extract Unsigned (ExtU)                   |                                         | 0 |

|-------------------------------------------|-----------------------------------------|---|

| Flush Data Cache Line (FDC)               | 52                                      | 2 |

| Invalidate Data Cache Line (IDC)          | §                                       | 3 |

| Invalidate Instruction Cache Line (IIC)., |                                         | 4 |

| Invalidate Instruction Cache (IICa)       | *******5                                | 5 |

| Insert (Ins)                              |                                         |   |

| Interrupt (Int)                           |                                         |   |

| Invalidate Translation Lookaside Buffer   | (ITLB)59                                | 9 |

| Jump Relative (Jmp)                       |                                         | 0 |

| Jump Absolute (Jmp)                       | 6                                       | 1 |

| Jump and Link (JmpL)                      |                                         | 2 |

| Load Condition (Lcc)                      | 6                                       | 3 |

| Load Immediate (Ld)                       |                                         | 5 |

| Load Byte (LdB)                           |                                         | 6 |

| Load Carry Partial (LdCP)                 |                                         |   |

| Load Multiple (LdM)                       | 6                                       | 8 |

| Load Word (LdW)                           | 69                                      | 9 |

| Load Word Direct (LdW)                    |                                         |   |

| Load Word (LdW)                           | -00000000000000000000000000000000000000 |   |

| Load Word Extended (LdWE)                 |                                         | 3 |

| Move (Mov)                                |                                         |   |

| Move to Special (Mov)                     |                                         |   |

| Move from Special (Mov)                   | 2000s                                   |   |

| Mask Generate (Msk)                       | 4555456                                 |   |

| Mask Generate (Msk)                       | 5000000000                              |   |

| Multiply (Mul)                            | .00000000000000000000000000000000000000 |   |

| Multiply Partial (MulP)                   |                                         |   |

| Negate (Neg)                              |                                         |   |

| Not (Not)                                 | ,000,000,000,000,000,000                |   |

| Or (Or)                                   | .0000000000000000                       |   |

| Prefetch Data Cache Line (PDC)            |                                         |   |

| Prefetch Instruction Cache Line (PIC)     | 200020000000000                         |   |

| Prefetch Instruction Cache Line (PIC)     | 10000100000                             |   |

| Read Data Tag by Index (RDTX)             |                                         |   |

| Restart (Res)                             | 90                                      | 0 |

| Resume (Rsm)                              |                                         |   |

| Return from Interrupt (RtI)               |                                         |   |

| Subtract with CArry Partial (SbCP)        |                                         |   |

| Send (Send)                               |                                         |   |

| Set Field (SetF)                          |                                         |   |

| Set Mode (SetM)                           |                                         |   |

| Shift Left (ShL)            |                                         | • • • • • • • • • • • • • • • • • • • •    | 98  |

|-----------------------------|-----------------------------------------|--------------------------------------------|-----|

| Shift Right (ShR)           |                                         | ••••••                                     | 99  |

| Skip on Condition (Skcc)    |                                         | ***                                        | 100 |

| Store Byte (StB)            |                                         |                                            | 102 |

| Store Multiple (StM)        |                                         |                                            | 103 |

| Start (Strt)                |                                         |                                            |     |

| Store Word (StW)            |                                         |                                            | 105 |

| Store Word Direct (StW)     | ****                                    |                                            | 106 |

| Store Word (StW)            |                                         |                                            | 107 |

| Store Word Extended (StWI   | 3)                                      |                                            | 108 |

| Subtract (Sub)              | * • • • • • • • • • • • • • • •         |                                            | 109 |

| Subtract Immediate (Sub)    | *                                       |                                            | 110 |

| Subtract with Carry (SubC), |                                         | • • • • • • • • • • • • • • • • • • • •    | 111 |

| Subtract Partial (SubP)     | ••••••                                  | •••••                                      | 112 |

| Trap (Trap)                 |                                         | • • • • • • • • • • • • • • • • • • • •    | 113 |

| Test Field (TstF)           | • • • • • • • • • • • • • • •           | *****                                      | 114 |

| Test Mode (TstM)            |                                         |                                            | 115 |

| Update Data Cache Line (UI  | DC)                                     |                                            |     |

| Validate Data Cache Line (V | DC)                                     | • • • • • • • • • • • • • • • • • • • •    | 118 |

| Wait (Wait)                 |                                         | • • • • • • • • • • • • • • • • • • • •    | 119 |

| Exclusive Or (XOr)          | • • • • • • • • • • • • • • • • • • • • |                                            | 120 |

|                             |                                         |                                            |     |

|                             |                                         |                                            |     |

|                             | List of Ta                              | ıbles                                      |     |

|                             | B 11                                    |                                            | 1.1 |

| Table 1. Trap and Interrupt |                                         |                                            |     |

| Table 2. Traps and Interrup |                                         |                                            |     |

| Table 3. Operands           |                                         |                                            | 16  |

| Table 4. Operators and Syn  | 0000000                                 | 000000000000000000000000000000000000000    |     |

| Table 5. Alphabetic Summa   |                                         |                                            |     |

| Table 6. Functional Summa   |                                         |                                            |     |

| Table 7. CC Field Encoding  |                                         |                                            |     |

| Table 8. CC Field Encoding  | 1 10000000                              | 50V                                        |     |

| Table 9. CC Field Encoding  | gs (Skcc)                               | 9<br>• • • • • • • • • • • • • • • • • • • | 100 |

## Introduction

Antares is a new 32-bit CPU being developed by the Advanced Computer Development group. The CPU features a unique design, containing four individual processing units, or PUs, and on-board instruction and data caches. The Antares chip uses a compact instruction set: operations performed the most frequently can be executed with a single instruction, while less frequently used operations are synthesized by instruction sequences.

This manual describes the Antares instruction set. This introduction describes the Antares programming model and defines the special registers used by the chip. This section also covers the trap/interrupt mechanism and lists the traps and interrupts, as well as describing the notation used in the manual. Quick-reference tables list the instructions functionally and alphabetically.

Following the introduction, the manual presents each instruction separately. Each description includes an operation statement, a description of the instruction's operation, a list of affected condition codes, exceptions, restrictions, timing, and format. Where appropriate examples are included.

A companion volume, *The Antares CPU: An Overview*, contains information about Antares architecture.

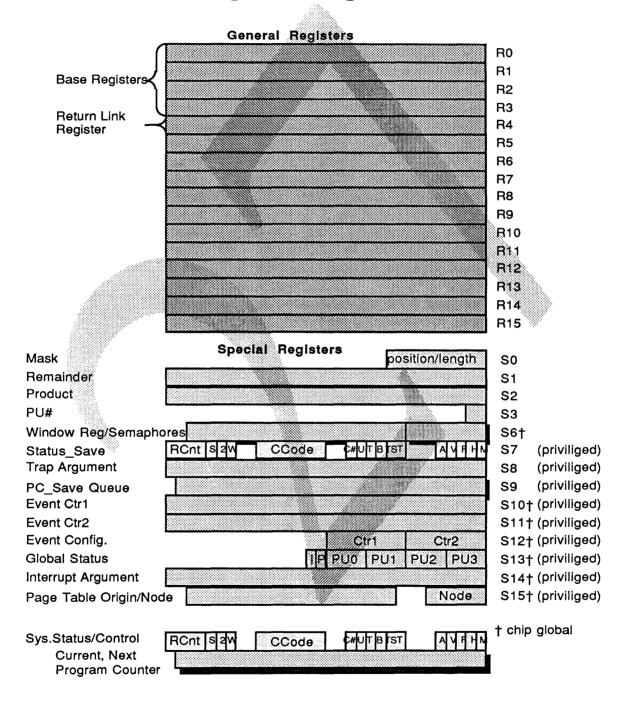

## **Programming Model**

The drawing on the following page provides a programming model for the Antares CPU. It shows the general and special registers used by the chip. Of the 16 general registers, the first four (R0 through R3) are used as base registers for most instructions; however, all 16 general registers can be used for the extended instructions (LdWE and StWE). The fifth register (R4) serves as the return link register (used by the JmpL instruction).

## **Programming Model**

#### **Special Registers**

The Antares CPU uses a number of special registers to execute its instructions. Registers S0, S1, S2, S3, S7, S8, and S9 apply to a specific PU, while S4, S6, S10, S11, S12, S13, S14, and S15 are chip global registers used by all four PUs. Registers S4 and S7 through S15 are privileged. Each special register has a specific purpose, as defined below.

Mask (S0)

S0 holds the definition of a field defined by the Mask Generate (Msk) instructions. The Mask register contains 15 bits in this implementation. The Mask and Move instructions set the Mask register.

Remainder (S1)

S1, used by the Divide (Div) instruction, fulfills two purposes: it allows formation of 64-bit dividends and stores the remainder from a division operation. When the MDfull bit in the System Status/Control register is set, the Divide (Div) instruction uses the contents of the Remainder register as the upper 32 bits of the dividend. The Remainder register contains 32 bits and is filled as a result of a divide operation or by a Move to Special (Mov) instruction.

Product (\$2)

Used by the Multiply (Mul) and Multiply Paritial (MulP) instructions, the Product register allows formation of 64-bit products. When two 32-bit numbers are multiplied, the upper 32 bits of the product get stored in the Product register. In addition, if the MDfull bit in the System Status/Control register is set, a Mul or MulP instruction adds the contents of the Product register to the product. The Product register contains 32 bits and is filled as a result of a multiplication or it can be filled by a Move to Special (Mov) instruction.

PU# (S3)

S3 holds the PU# for the PU with which the register is associated. This 2-bit register is a read-only register.

Test (S4)

S4 is used for system diagnostics. It is a global, privileged register.

Window/Semaphores (S6)

The two S6 registers contain two parts: a window register and semaphores. Which of the two S6 registers used depends on the setting of the Cluster# bit in the System Status/Control register.

The 20-bit window registers are used by the Load Word (LdW) and Store Word (StW) Direct instructions to determine the address of a Memory word. One Window register is a read-only register that holds the constant 0x3FF00000. The other Window register can be modified using the Move to Special (Mov) instruction when the Cluster# bit in the System Status/Control register equals 1.

The Semaphore registers facilitate inter-PU communications. They are set by executing a Store Word (StW) Direct to addresses 0 through 7. Load Word (LdW) Direct from addresses 0 through 7 clears the Semaphore register. They are read and written along with the Window registers.

When traps are disabled, the PU's status is saved from the System Status Control register to the Status\_Save register on each clock cycle. Enabling traps invalidates the contents of the Status\_Save register. S7 is a privileged register.

S8 holds the data address that caused the trap. Its contents can be read using the Mov from Special (Mov) instruction and are not valid unless traps are disabled. S8 is a privileged register.

Saves the PC and next PC when the processor executes a Trap instruction. Reading S9 returns PC; writing to S9 moves Next PC to PC and writes into Next PC. The privileged register's contents are valid only when traps are disabled. S9 contains 30 bits.

S10 and S11 count the events specified by the Event Counter Configuration register (S12). The Event Counter registers aid performance analysis by counting specific events. If enabled, an interrupt occurs when the counter overflows. The two 32-bit privileged registers can be read using a Move from Special (Mov) instruction.

Status\_Save (S7)

Trap Argument (S8)

PC\_Save Queue (S9)

Event Counter 1 (S10) Event Counter 2 (S11)

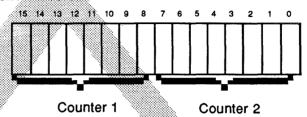

#### Event Configuration (S12)

Specifies which events will be counted into the S10 and S11 registers. S12 contains 16 bits, eight of which are allocated to each Event Counter register, as shown below.

- 15 7

- Interrupt enable. If set, it allows an interrupt when the Event Counter overflows.

- 14 6

- If set, indicates that the Event Counter has overflowed. Cannot be written with a 1; always resets if written.

- 13 5

- If set, counts system mode events.

- 12 4

- If set, counts user mode events.

- 11 3

- If set, indicates that the next three bits (0..2 and 8..10) encode a Memory Mangement Unit (MMU) event to be counted:

- Data out. If set, counts moveouts from the data cache.

- 9 1 Data in. If set, counts moveins to the data cache.

- 8 0 Instructions in. If set, counts moveins to the instruction cache.

If bits 8..10 and/or 0..2 are all clear, counts TLB misses.

- 11 3 If clear, indicates that the next three bits encode a Processing Unit (PU) event to be counted:

- 10 2 If set, counts each cycle that the selected PU is not halted. If clear, counts each instruction that the selected PU finishes.

- 8.9 0,1 Selects PU (2 bits).

If the System and User bits are both clear, the Event Counter counts all cycles if the MMU/PU bit is set. If the MMU/PU bit is clear, the Event Counter does not count any cycles.

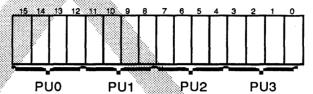

#### Global Status (S13)

S13 facilitates deadlock detection. The Global Status register contains 16 bits, four for each PU. The four bits for each PU enable the PUs to determine the state of other PUs according to how the bits are set. S13 is a read-only, privileged register. The diagram below shows the bits used.

0, 4, 8, 12

User. If this bit is set for a particular PU, it indicates that the PU is in user mode.

1, 5, 9, 13

Trap enabled. If this bit is set, the PU is enabled for traps.

2, 6, 10, 14

Semaphore wait. If this bit is set, the PU is waiting for a semaphore to be modified.

3, 7, 11, 15

Halted. If this bit is set, the PU is halted because it has executed a Wait instruction.

#### Interrupt Argument (S14)

S14 contains the address that caused the IPB interrupt as well as the external interrupt pending and external interrupt enable bits. S14 is a chip global, privileged register that can be read using the Move from Special (Mov) instruction. Only the external interrupt pending and enable bits can be written with the Move to Special (Mov) instruction. The external interrupt enable bit can be set or cleared; the interrupt pending bit can be cleared only. The contents of bits 0 through 29 are valid only when interrupts are disabled.

| 31 | 30 | 29                 | 0 |

|----|----|--------------------|---|

| Р  | ١  | Interrupt Argument |   |

30

External interrupt pending. If this bit is set, it indicates that an external interrupt is waiting for processing.

31

External interrupt enable. If this bit is set, it indicates that the CPU can be interrupted.

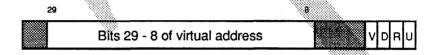

Page Table Origin/Node (S15) Bits 8 through 30 contain the page address of the base of the page table, which the TLB miss logic uses. Bits 0 through 5 contain the PU node number used by the IPB logic. The powerup logic normally

sets the node number.

**Current, Next Program Counters**

The Current and Next Program Counters hold the addresses of the currently executing instruction and the next instruction.

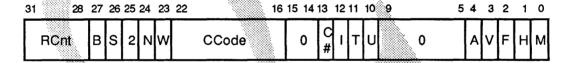

System Status/Control

The System Status/Control register holds the status and control information that the processor uses. The register contains the 10 mode bits and the condition codes, as well as other status information.

The 10 mode bits are set and cleared by the Set Mode (SetM) and Clear Mode (ClrM) instructions. Bits 0 through 7 can be set in user or system mode, bits 8 through 15 are restricted to system mode only. Both interrupts and traps clear bits 0 through 15.

The drawing below shows the contents of the System Status/Control register.

| Bits  | Field | Meaning                  | Bits  | Fleid | Meaning         |

|-------|-------|--------------------------|-------|-------|-----------------|

| 0     | М     | MD control               | 16-22 | CCode | Condition codes |

| 1     | Н     | Halfword/byte            | 16    | Z     | Zero            |

| 2     | F     | MD full                  | 17    | N     | Negative        |

| 3     | V     | Overflow trap enable     | 18    | V     | Overflow        |

| 4     | Α     | Registers available      | 19    | C0    | Carry           |

| 5-7   |       | Reserved                 | 20    | C1    | Carry           |

| 8-9   |       | Reserved                 | 21    | C2    | Carry           |

| 10    | В     | Branch taken trap enable | 22    | СЗ    | Carry           |

| 11    | T     | Trap enable              |       |       | -               |

| 12    | U     | User/system              | 23-23 |       | Reserved        |

| 13    | C#    | Cluster number           | 25    | W     | Halted          |

| 14-15 |       | Reserved                 | 26    | 2     | Second half     |

|       |       |                          | 27    | S     | Skipped         |

|       |       |                          | 28-31 | RCnt  | Register count  |

MD control (M) will be defined later.

Halfword/byte (H) indicates whether the partial word instructions (AddP, AdCP, SubP, SbCP, CmpP, and MulP) execute in halfword or byte mode.

MD full (F) indicates whether or not the MD special register contains data to be used by a Multiply or Divide instruction. The MD full bit is cleared by Multiply and Divide instructions.

Overflow trap enable (V) allows a trap to occur when the V condition code bit is set by an Add, Add Immediate, Add with Carry, Negate, Subtract, Subtract Immediate, or Subtract with Carry instruction. (Divide--maybe.)

Registers available (A) is used by the interrupt/trap handler to indicate which PU was idle when trapped or interrupted. Executing a Resume or Start instruction clears the A bit for the target PU.

Branch taken trap enable (B) can be modified in system mode only. If set, it enables a trap when a branch is taken; clearing the bit disables traps on a taken branch. If set when a branch is taken, the processor branches and then traps before the shadow of the branch.

Trap Enable/Disable (T) can be modified in system mode only to enable traps. It is cleared to disable traps.

User/System (U) can be modified in system mode only. It is set to indicate user mode and cleared to indicate system mode.

Cluster number (C#) can be modified in system mode only to indicate which window register should be used to determine addresses for the Load and Store Word Direct instructions. If the bit is clear, the instruction uses the read-only window register containing the constant 0x3FF00000; if the bit is set, the instruction uses the modifiable window register.

The Condition Codes (CCode) are modified by the integer instructions or by the Load Condition (Lcc) instruction, which writes directly to the System Status/Control register. They can be tested by the Branch and Skip on Condition (Bcc, Skcc) instructions.

Halted (W) indicates that the PU is halted. Other PUs use this status bit while executing Resume, Start, and Send instructions. Interrupt selection logic also uses the Halted bit.

Second half (2) indicates an instruction page fault on the second half of an extended operation when set. The page fault handler uses the Second half bit to restore state or to determine which part of the instruction faulted.

**Skipped** (S), when set, indicates that the instruction that the head of the PC\_Save Queue points to will not be executed upon return from a trap.

Register count (RCnt) counts the number of registers stored or loaded for the Load and Store Multiple instructions (LdM, StM). The trap handler uses the count to correctly restore state when a page fault trap occurs.

#### Traps and Interrupts

The Antares CPU uses several different types of traps and interrupts which have specific characteristics. These characteristics include whether the exception is a *trap* or *interrupt*, whether it is a *directed* or *nondirected interrupt*, and whether it is *nonmaskable*, *maskable*, or *individually enabled*.

The interrupt handler distinguishes traps from interrupts by the source of the interrupt or trap. *Traps* are synchronous (i.e. caused by a particular instruction), while most *interrupts* are asynchronous (originate externally) and global in origin, except for the Inter-PU interrupt.

The externally originating interrupts are usually *nondirected*, which means that any PU can process the interrupt. The one type of interrupt that is *directed* is the Inter-PU interrupt (1B), which originates on the chip and is directed at particular PUs. The interrupt handler directs all traps to the PU that caused the trap.

When a nondirected interrupt occurs, the interrupt handler uses a priority system to select the PU to process the interrupt. It first looks for a PU with the Available bit set in the Status\_Save register. If no PUs are "available," the interrupt handler looks for a "halted" PU. Running PUs have the lowest priority. If none of the PUs can accept an interrupt (i.e., trap enable bit in the Status\_Save register is cleared), the handler holds the interrupt until a PU can accept it. Interrupts that can be held have a pending status bit in the Global Status register that indicates that the interrupt is waiting for processing.

If none of the PUs to which an Inter-PU interrupt is directed to can accept the interrupt, the instruction is held until the interrupt can be processed.

Several bits in the special registers enable traps and interrupts. Each PU has a master trap enable bit in its local Status\_Save register (bit 11, T). The Status\_Save register also contains two individual trap enables: the overflow trap enable (bit 3, V) and the taken branch trap enable (bit 10, B). The master CPU interrupt enable resides in the Global Status register (bit 18, I), and the event counter interrrupt enables occupy bits 7 and 15 of the Event Configuration register.

Nonmaskable interrupts can override the state of the local trap enables. Interrupts and traps that have individual enabling bits are called *individually enabled*, and the rest fall into the category termed *maskable*.

The table below shows the possible states of the PU master trap enable bit and the individual enables. The individual enables include the overflow and taken branch trap enables and the master CPU and event counter interrupt enables.

Master PU Individual Enable Enable Meaning 1 1 PU can be interrupted or trap 1 0 PU can trap, individual trap/interrupt is disabled 0 0 PU has trapped or been interrupted. no others will be accepted 0 PU has trapped or been interrupted, another PU can be interrupted

Table 1. Trap and Interrupt Enables

The following events occur when a trap or interrupt occurs.  $(A \rightarrow B \rightarrow C \text{ means } B \text{ is stored in } C$ , then A is stored in B)

```

0 → System Status/Control → Status_Save register

0 → individual enable (if any)

Trap #*8 → PC_Queue → PC_Save Queue

Address → Trap Argument/Interrupt Argument

```

When a PU traps or interrupts, the System Status/Control register resets, including the master PU trap enable bit. If the trap or interrupt is individually enabled, the individual enable resets.

If a maskable or individually enabled trap or interrupt occurs on a PU when traps or interrupts are disabled for that PU, but enabled for the individual trap, a machine check (1E) interrupt occurs.

If multiple interrupts occur simultaneously, only the one with the highest number is reported; all other interrupts are held until interrupts are re-enabled.

When the trap enable bit in the System Status/Control register is set, each cycle moves the contents of System Status/Control into the Status\_Save register and the contents of the Current and Next Program Counter registers into the PC\_Save Queue. The transfer does not occur when the trap enable bit is cleared.

The following table lists the interrupt/trap causes. The table shows the interrupt and trap names, numbers, and other information, and lists some implications of the existence of the interrupt or trap.

Table 2. Traps and Interrupts

| Name               | Codes    | Trap<br>No. | Other                                                                                                                                                                                                                                                        |

|--------------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset              | I, N, B  | 1F          | Occurs on powerup reset (ND), reset pushbutton (ND), or Res instruction (D).                                                                                                                                                                                 |

| Machine Check      | I, N, B  | 1E          | Occurs on bus error, internal detectable hardware failure (might be used with a redundant 'shadow' mode, where it indicates a mismatch between what was put on the bus, and what should have been on the bus), and when trap occurs when traps are disabled. |

| Restart            | I, N, B  | 1D          | Caused by hardware deadlock detection (ND) or results from one PU interrupting another with the Restart (Res) instruction.                                                                                                                                   |

| PowerFail/OverTemp | I, N, ND | 1C          |                                                                                                                                                                                                                                                              |

| Inter-PU           | I, M, D  | 1B          | Results from one PU interrupting another with the Interrupt (Int) instruction.                                                                                                                                                                               |

| Inter-chip         | I, M, ND | 1A*         | Results from access of an address mapped in another node with the page table 'message' bit set .                                                                                                                                                             |

Codes: I = Interrupt, T = Trap, N = Nonmaskable, M = Maskable, E = Individually enabled, D = Directed, ND = Nondirected, B = Both

<sup>\*</sup>Will set an address into the Interrupt Argument (S14)register.

Table 2. Interrupts (continued)

|                          |          |             | <u> </u>                                                                                                                                                                                                                            |

|--------------------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                     | Codes    | Trap<br>No. | Other                                                                                                                                                                                                                               |

| Event Counter            | I, E, ND | 19          | Individual enables in Event Counter<br>Configuration (S12) register. Results from<br>overflow of one of the event counters (S10<br>and S11). Check bit in configuration<br>register (S12) to determine which counter<br>overflowed. |

| External                 | I, E, ND | 18          | I/O interrupt                                                                                                                                                                                                                       |

| Overflow/Divide by 0     | T, E, D  | 17          | Individual enable. Check opcode to distinguish an overflow from a divide by 0.                                                                                                                                                      |

| Illegal or Privileged Op | Ŧ, M, D  | 16          | Check opcode to distinguish an illegal operation from a privileged operation or a taken branch.                                                                                                                                     |

| Taken Branch             | T, E, D  | 16          | Check opcode to distinguish an illegal operation from a privileged operation or a taken branch.                                                                                                                                     |

| Data access fault        | T, M, D  | 15†         | Results from user attempt to access system pageor from user or system attempt to access data on execute-only page or to write to a read-only page.                                                                                  |

| Instruction access fault | T, M, D  | 14          |                                                                                                                                                                                                                                     |

| Data Page Fault          | T, M, D  | 13†         |                                                                                                                                                                                                                                     |

| Inst Page Fault          | T, M, D  | 12          |                                                                                                                                                                                                                                     |

| Node Busy                | T, M, D  | 11†         | Results from failed access to an address mapped in another node with the page table 'message' bit set                                                                                                                               |

| Software Trap            | T, M, D  | F0          | Opcodes F0                                                                                                                                                                                                                          |

Codes: I = Interrupt, T = Trap, N = Nonmaskable, M = Maskable, E = Individually enabled, D = Directed, ND = Nondirected, B = Both

<sup>†</sup>Will set an address into the Trap Argument (S8) register.

#### **Condition Codes**

The System Status and Control register for the Antares CPU contains seven condition code bits. The processor sets them as described below for all instructions except partial word instructions.

- N Negative condition code bit. This bit gets set if the true result is less than zero. The N condition code bit may be different from the most significant bit of the result if an arithmetic overflow occurs.

- Z Zero condition code bit. This bit gets set if the result equals zero.

- V Overflow condition code bit. This bit gets set if an arithmetic overflow occurs.

- C Carry condition code bits. The highest of these four bits is set if a carry is generated out of the most significant bit of the operand for all instructions except the partial word instructions. The lower three bits are cleared. The indication not carry means that all four Carry bits are cleared.

The Carry bit gets set for the Add instructions under the following conditions:

$$S \cdot D + [(S + D) \cdot \neg R]$$

If the source and destination registers both have their sign bits set, then the Carry bit is set. If either the source or destination register has its sign bit set and the result does not have its sign bit set, the Carry bit is set.

The Carry bit gets set for the Subtract and Compare instructions under the following conditions:

$$(-S) \cdot D + [((-S) + D) \cdot R]$$

If the source register does not have its sign bit set and the destination register does have its sign bit set, the Carry bit is set. If the source register does not have its sign bit set or the destination register does have its sign bit set and the result does not have its sign bit set, the Carry bit is set.

#### Partial Word Condition Codes

The condition codes for partial word instructions (Add with Carry Partial, Add Partial, Compare Partial, Load Partial Carry, Subtract with Carry Partial, and Subtract Partial) function differently.

- N Negative condition code bit. This bit gets set if any halfword/byte result is negative.

- Z Zero condition code bit. This bit gets set if any halfword/byte result equals zero.

- V Overflow condition code bit. This bit is always cleared; no overflow can occur in partial word operations.

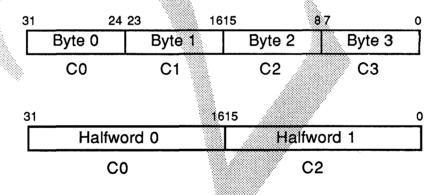

- C Carry condition code bits. A Carry bit gets set if a carry is generated out of the most significant bit of the halfword or byte corresponding to that specific Carry bit. The four Carry bits (C0 through C3) are set individually if the halfword/byte bit in the System Status/Control register is cleared. If the halfword/byte bit is set, Carry bits C0 and C2 are set and C1 and C3 are cleared.

The individual Carry bits correspond to the following bytes and halfwords:

## **Notation**

The following tables show the notation used in this manual.

Table 3. Operands

| Operand            | Meaning                                                                                            |

|--------------------|----------------------------------------------------------------------------------------------------|

| RegA               | Source register A<br>Instruction <3:0>                                                             |

| RegB               | Source register B<br>Instruction <7:4>                                                             |

| Base               | Base register<br>Instruction <1:0> or <3:0> if extended                                            |

| Mask               | Mask register                                                                                      |

| PC                 | Program counter                                                                                    |

| Next PC            | Halfword address of next instruction to be executed                                                |

| Imm, Pos, Len, Amt | Immediate operands: Immediate,<br>Position, Length, Amount<br>Constants encoded in the instruction |

| Displacement       | Displacement/direct address                                                                        |

| Sp                 | Special register                                                                                   |

| @R                 | Contents of memory location addressed by register                                                  |

| R0, R1R15          | General-purpose registers                                                                          |

| R0R3               | Base registers for normal instructions                                                             |

| R-0R16             | Base registers for extended instructions                                                           |

| R4                 | Return link register                                                                               |

| R <b></b>          | Bit b of R                                                                                         |

| Reg <m:n></m:n>    | bits m through n, inclusive, of specified register                                                 |

Table 4. Operators and Symbols

| Operator        | Meaning                                                                   |

|-----------------|---------------------------------------------------------------------------|

| $\rightarrow$   | Move left operand to right operand                                        |

| +               | Add operands                                                              |

| -               | Subtract right operand from left operand                                  |

| *               | Multiply operands                                                         |

| 1               | Divide left operand by right operand                                      |

| ,               | Concatenate                                                               |

| ~               | Ones complement the operand                                               |

| &               | Bitwise logically AND the operands                                        |

| ۸               | Bitwise exclusive OR the operands                                         |

| 1               | Bitwise logically OR the operands                                         |

| <b>&lt;&lt;</b> | Shift the left operand left by the amount specified by the right operand  |

| >>              | Shift the left operand right by the amount specified by the right operand |

| @               | Contents of memory location                                               |

## **Quick Reference**

The tables in this section provide quick reference to Antares instructions. Table 5 contains an alphabetic summary, while Table 6 groups the instructions functionally.

Table 5. Alphabetic Summary of Instructions

| Mnemonic                           | Instruction                                                                                   | Operation                                                                                                                                  | Page                       |

|------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| AdCP<br>Add<br>Add<br>AddC<br>AddP | Add with Carry Partial<br>Add<br>Add Immediate<br>Add with Carry<br>Add Partial               | AdCP RegB(H/B) + RegA → RegB<br>Add RegB + RegA → RegB<br>Add RegB + Imm → RegB<br>AddC RegB + RegA → RegB<br>AddP RegB(H/B) + RegA → RegB | 24<br>25<br>26<br>27<br>28 |

| AdPC<br>And<br>AndC<br>Bcc<br>CDC  | Add Program Counter<br>And<br>And Complement<br>Branch on Condition<br>Create Data Cache Line | AdPC PC + 1 + RegA → RegA<br>And RegB & RegA → RegB<br>AndC RegB & ~RegA → RegB<br>Bcc PC + Displacement<br>CDC @RegA                      | 29<br>30<br>31<br>32<br>34 |

| ClrF<br>ClrM<br>CLZ<br>Cmp<br>Cmp  | Clear Field<br>Clear Mode<br>Count Leading Zeros<br>Compare<br>Compare Immediate              | CIrF 0 → RegA <mask> CIrM BitNumber CLZ RegA → RegB Cmp RegB - RegA Cmp RegB - Imm</mask>                                                  | 35<br>36<br>38<br>39<br>40 |

| CmpP<br>Dep<br>Div                 | Compare Partial<br>Deposit<br>Divide                                                          | CmpP RegB(H/B) - RegA<br>Dep RegB → RegA <mask><br/>Div (MDfull &amp; (Remainder&lt;&lt;32) , RegB) /</mask>                               | 41<br>42                   |

| DSh<br>ExtS                        | Double Shift<br>Extract Signed                                                                | RegA → {RegB, Remainder}<br>DSh (RegB, RegA) >> Mask → RegA<br>ExtS RegA <mask> → RegB</mask>                                              | 44<br>46<br>48             |

| ExtU<br>FDC<br>IDC                 | Extract Unsigned<br>Flush Data Cache Line<br>Invalidate Data Cache<br>Line                    | ExtU RegA <mask> → RegB<br/>FDC @RegA<br/>IDC @RegA</mask>                                                                                 | 50<br>52<br>53             |

| IIC                                | Invalidate Instruction                                                                        | IIC @RegA                                                                                                                                  | 54                         |

| llCa                               | Cache Line<br>Invalidate Instruction<br>Cache                                                 | IICa                                                                                                                                       | 55                         |

| Ins<br>Int<br>ITLB                 | Insert<br>Interrupt<br>Invalidate Translation<br>Buffer                                       | Ins RegB → RegA <mask><br/>Int PuMask<br/>ITLB</mask>                                                                                      | 56<br>58<br>59             |

| Jmp<br>Jmp                         | Jump Relative<br>Jump Absolute                                                                | Jmp PC + Displacement<br>Jmp @RegA                                                                                                         | 60<br>61                   |

Table 5. Alphabetic Summary of Instructions (continued)

| Mnemonic                | Instruction                        | Operation                                               | Page     |

|-------------------------|------------------------------------|---------------------------------------------------------|----------|

| JmpL                    | Jump and Link                      | JmpL next PC + 1 → R4, Jmp @RegA                        | 62       |

| Lcc                     | Load Condition                     | Lcc → RegB                                              | 63       |

| Ld                      | Load Immediate                     | Ld Imm → RegB                                           | 65       |

| LdB                     | Load Byte                          | LdB @Base → RegA                                        | 66       |

| LdCP                    | Load with Carry Partial            | LdCP Extend ~(C0C3) → RegA                              | 67       |

| LdM                     | Load Multiple                      | LdM @RegA → RegBReg1                                    | 68       |

| LdW                     | Load Word                          | LdW @Base + Displacement → RegB                         | 69       |

| LdW                     | Load Word Direct                   | LdW @Displacement → RegB                                | 70       |

| LdW                     | Load Word                          | LdW @RegA → RegB                                        | 72       |

| LdWE                    | Load Word Extended                 | LdWE @RegA + Displacement → RegB                        | 73       |

| Mov                     | Move                               | Mov RegA → RegB                                         | 74       |

| Mov                     | Move to Special                    | Mov RegB → Sp                                           | 75       |

| Mov                     | Move from Special                  | Mov Sp → RegB                                           | 77       |

| Msk                     | Mask Generate                      | Msk Pos for Len                                         | 79       |

| Msk <sup>*</sup><br>Mul | Mask Generate<br>Multiply          | Msk RegA for Len Mul RegB * RegA + (MDfull & Product) → | 80       |

| IVIUI                   | мапру                              | {Product, RegB}                                         | 81       |

| MulP                    | Multiply Partial                   | MulP RegB(H/B) * RegA → RegB                            | 82       |

| Neg                     | Negate                             | Neg - RegA → RegB                                       | 83       |

| Not                     | Not                                | Not ~RegA → RegB                                        | 84       |

| Or                      | Or                                 | Or RegA   RegB → RegB                                   | 85       |

| PDC                     | Prefetch Data Cache<br>Line        | PDC @RegA                                               | 86       |

| PIC                     | Prefetch Instruction               | PIC @RegA                                               | 87       |

| PIC                     | Cache Line<br>Prefetch Instruction | PIC PC + Displacement                                   | 88       |

| DDTV                    | Cache Line                         | DDTV GENA DOOD                                          | 00       |

| RDTX                    | Read Data Tag by Index             | RDTX @RegA → RegB<br>Res PuMask                         | 89<br>90 |

| Res                     | Restart                            | Rsm PuMask                                              | 91       |

| Rsm                     | Resume                             | Hall Edwigan                                            | _        |

| RtI                     | Return from Interrupt              | RtI                                                     | 92       |

| SbCP                    |                                    | SbCP RegB(H/B) - RegA → RegB                            | 93       |

| Send                    | Send                               | Send RegB → Destination Register <pumask></pumask>      | 94       |

| SetF                    | Set Field                          | SetF 1 → RegA <mask></mask>                             | 95       |

Table 5. Alphabetic Summary of Instructions (continued)

| Mnemonic | Instruction           | Operation                            | Page |

|----------|-----------------------|--------------------------------------|------|

| SetM     | Set Mode              | SetM BitNumber                       | 96   |

| ShL      | Shift Left            | ShL RegB << Amt → RegB               | 98   |

| ShR      | Shift Right           | ShR RegA >> Amt → RegA               | 99   |

| Skcc     | Skip on Condition     | \$kcc                                | 100  |

| StB      | Store Byte            | StB RegB → @RegB                     | 102  |

| StM      | Store Multiple        | StM RegBR1 → @RegA                   | 103  |

| Strt     | Start                 | Strt RegB, PuMask                    | 104  |

| StW      | Store Word            | StW RegB → @Base + Displacement      | 105  |

| StW      | Store Word Direct     | StW RegB → @Displacement             | 106  |

| StW      | Store Word            | StW RegB → @Base                     | 107  |

| StWE     | Store Word Extended   | StWE RegB → @Base + Displacement     | 108  |

| Sub      | Subtract              | Sub RegB - RegA → RegB               | 109  |

| Sub      | Subtract in the       | Sub RegB - Imm → RegB                | 110  |

| SubC     | Subtract with _arry   | SubC RegB - RegA + (Carry -1) → RegB | 111  |

| SubP     | Subtract Partial      | SubP RegB(H/B) - RegA → RegB         | 112  |

| Trap     | Trap                  | Trap Trapnum                         | 113  |

| TstF     | Test Field            | TstF RegA <mask></mask>              | 114  |

| TstM     | Test Mode             | TstM BitNumber                       | 115  |

| UDC      | Update Data Cache     | UDC @RegA                            | 117  |

| VDC      | Line<br>Validate Data | VDC @RegA                            | 118  |

| ,,,,     | Cache Line            |                                      |      |

| Wait     | Wait                  | Wait PuMask                          | 119  |

| XOr      | Exclusive Or          | XOr RegA ^ RegB → RegB               | 120  |

Table 6. Functional Summary of Instructions

| Mnemonic | Instruction             | Operation                               | Page |

|----------|-------------------------|-----------------------------------------|------|

|          | Register Load, S        | itore, and Move Instructions            |      |

| Lcc      | Load Condition          | Lcc RegB                                | 63   |

| Ld       | Load Immediate          | Ld Imm → RegB                           | 65   |

| LdB      | Load Byte               | LdB @Base → RegB                        | 66   |

| LdCP     | Load with Carry Partial | LdCP Extend ~(C0C3) → RegA              | 67   |

| LdM      | Load Multiple           | LdM @RegA → RegB. R1                    | 68   |

| LdW      | Load Word               | LdW @Base + Displacement → RegB         | 69   |

| LdW      | Load Word Direct        | LdW @Displacement → RegB                | 70   |

| LdW      | Load Word               | LdW @RegA → RegB                        | 72   |

| LdWE     | Load Word Extended      | LdWE @RegA + Displacement → RegB        | 73   |

| Mov      | Move                    | Mov RegA → RegB                         | 74   |

| Mov      | Move to Special         | Mov RegB → Sp                           | 75   |

| Mov      | Move from Special       | Mov Sp → RegB                           | 77   |

| StB      | Store Byte              | StB RegB → @Base                        | 102  |

| StM      | Store Multiple          | StM RegB → @RegB                        | 103  |

| StW      | Store Word              | StW RegB → @Base + Displacement         | 105  |

| StW      | Store Word Direct       | StW RegB → @Displacement                | 106  |

| StW      | Store Word              | StW RegB → @Base                        | 107  |

| StWE     | Store Word Extended     | StWE RegB → @Base + Displacement        | 108  |

|          |                         | -                                       |      |

|          | Arithr                  | netic instructions                      |      |

| AdCP     | Add with Carry Partial  | AdCP RegB(H/B) + RegA → RegB            | 24   |

| Add      | Add                     | Add RegB + RegA → RegB                  | 25   |

| Add      | Add Immediate           | Add RegB + Imm → RegA                   | 26   |

| AddC     | Add with Carry          | AddC RegB + RegA → RegB                 | 27   |

| AddP     | Add Partial             | AddP RegB(H/B) + RegA → RegB            | 28   |

| CLZ      | Count Leading Zeros     | CLZ RegA → RegB                         | 38   |

| Div      | Divide                  | Div (MDfull & (Remainder<<32) + RegB) / | 44   |

|          |                         | RegA → { RegB, Remainder}               |      |

| Mul      | Multiply                | RegB * RegA + (MDfull & Product) →      | 81   |

|          |                         | {Product, RegB}                         |      |

| MulP     | Multiply Partial        | MulP RegB(H/B) * RegA → RegB            | 82   |

| Neg      | Negate                  | Neg - RegA → RegB                       | 83   |

| SbCP     |                         | SbCP RegB(H/B) - RegA → RegB            | 93   |

| Sub      | Subtract                | Sub RegB - RegA → RegB                  | 109  |

| Sub      | Subtract Immediate      | Sub RegB - Imm → RegB                   | 110  |

| SubC     | Subtract with Carry     | SubC RegB - RegA + (Carry -1) → RegB    | 111  |

| SubP     | Subtract Partial        | SubP RegB(H/B) - RegA → RegB            | 112  |

Table 6. Functional Summary of Instructions (continued)

| Mnemonic | Instruction         | Operation                         | Page     |

|----------|---------------------|-----------------------------------|----------|

|          | Compare, Test, Bra  | inch, Jump, and Skip Instructions |          |

| AdPC     | Add Program Counter | AdPC PC + 1 + RegA → RegA         | 29       |

| Bcc      | Branch on Condition | Bcc PC + Displacement             | 32       |

| Cmp      | Compare             | Cmp RegB - RegA                   | 39       |

| Cmp      | Compare Immediate   | Cmp RegB - Imm                    | 40       |

| CmpP     | Compare Partial     | RegB (H/B) - RegA                 | 41       |

| Jmp      | Jump Relative       | Jmp PC + Displacement             | 60       |

| Jmp      | Jump Absolute       | Jmp @RegA                         | 61       |

| JmpL     | Jump and Link       | JmpL next PC + 1 → R4, Jmp @RegA  | 62       |

| Skcc     | Skip on Condition   | Skcc                              | 100      |

| TstF     | Test Field          | TstF RegA                         | 114      |

| TstM     | Test Mode           | TstM BitNumber                    | 115      |

|          |                     |                                   |          |

|          | Shift, Logical, and | d Field Manipulation Instructions | <b>.</b> |

| And      | And                 | And RegB & RegA → RegB            | 30       |

| AndC     | And Complement      | AndC RegB & ~RegA → RegB          | 31       |

| ClrF     | Clear Field         | CIrF RegA                         | 35       |

| Dep      | Deposit             | Dep RegB → RegA <mask></mask>     | 42       |

| DSh      | Double Shift        | DSh (RegB, RegA) >> Mask → RegA   | 46       |

| ExtS     | Extract Signed      | ExtS RegA <mask>⇒ RegB</mask>     | 48       |

| ExtU     | Extract Unsigned    | ExtU RegA <mask> → RegB</mask>    | 50       |

| Ins      | Insert              | Ins RegB → RegA <mask></mask>     | 56       |

| Msk      | Mask Generate       | Msk Pos for Len                   | 79       |

| Msk      | Mask Generate       | Msk RegA for Len                  | 80       |

| Not      | Not                 | Not ~RegA → RegB                  | 84       |

| Or       | Or                  | Or RegA   RegB → RegB             | 85       |

| SetF     | Set Field           | SetF1 → RegA <mask></mask>        | 95       |

| ShL      | Shift Left          | ShL RegB << Amt → RegB            | 98       |

| ShR      | Shift Right         | ShR RegA >> Amt → RegA            | 99       |

| XOr      | Exclusive Or        | XOr RegA ^ RegB → RegB            | 120      |

Table 6. Functional Summary of Instructions (continued)

| Mnemonic    | Instruction                                            | Operation                              | Page     |

|-------------|--------------------------------------------------------|----------------------------------------|----------|

|             | Cache                                                  | Control Instructions                   |          |

| CDC         | Create Data Cache Line                                 | CDC @RegA                              | 34       |

| FDC<br>IDC  | Flush Data Cache Line<br>Invalidate Data Cache<br>Line | FDC @RegA<br>IDC @RegA                 | 52<br>53 |

| IIC         | Invalidate Instruction Cache Line                      | IIC @RegA                              | 54       |

| IICa        | Invalidate Instruction<br>Cache                        | IICa                                   | 55       |

| PDC         | Prefetch Data Cache<br>Line                            | PDC @RegA                              | 86       |

| PIC         | Prefetch Instruction<br>Cache Line                     | PIC @RegA                              | 87       |

| PIC         | Prefetch Instruction<br>Cache Line                     | PIC PC + Displacement                  | 88       |

| UDC         | Update Data Cache<br>Line                              | UDC @RegA                              | 117      |

| VDC         | Validate Data<br>Cache Line                            | VDC @RegA                              | 118      |

|             | Cos                                                    | ntrol Instructions                     |          |

|             |                                                        |                                        |          |

| ClrM        | Clear Mode                                             | ClrM BitNumber                         | 36       |

| Int<br>ITLB | Interrupt Invalidate Translation Lookaside Buffer      | Int PuMask<br>ITLB                     | 58<br>59 |

| RDTX        | Read Data Tag by Index                                 | RDTX @RegA → RegB                      | 89       |

| Res         | Restart                                                | Res PuMask                             | 90       |

| Rsm         | Resume                                                 | Rsm PuMask                             | 91<br>92 |

| RtI<br>Send | Return from Interrupt<br>Send                          | RtI<br>Send RegB → Destination Registe |          |

| SetM        | Set Mode                                               | SetM BitNumber                         | 96       |

| Strt        | Start                                                  | Strt RegB, PuMask                      | 104      |

| Trap        | Trap                                                   | Trap Trapnum                           | 113      |

| Wait        | Wait                                                   | Wait PuMask                            | 119      |

**AdCP**

## Add with Carry Partial

**AdCP**

Operation:

AdCP  $RegB(H/B) + RegA \rightarrow RegB$

Description:

If H/B is clear, add RegB to RegA using carry bits C0, C1, C2, and C3 as carries into bytes. Set the C0, C, C2, and C3 carry bits from the carryout of the corresponding bytes.

If H/B is set, add RegB to RegA using carry bits C0 and C2 as carries into halfwords. Set the C0 and C2 carry bits from the carryout of the corresponding halfwords. Clear bits C1 and C3.

Condition codes:

H/B = 0

N -- Set if any byte is negative, cleared otherwise.

Z -- Set if any byte is equal to zero, cleared otherwise.

V -- The V bit is cleared.

C -- Set if any byte carries, cleared otherwise.

H/B = 1

N -- Set if any halfword is negative, cleared otherwise.

Z -- Set if any halfword is equal to zero, cleared otherwise.

V -- The V bit is cleared.

C -- Set if any halfword carries, cleared otherwise.

**Exceptions:**

None.

**Restrictions:**

None.

Timing:

This instruction takes one cycle.

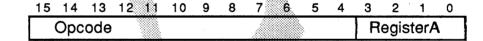

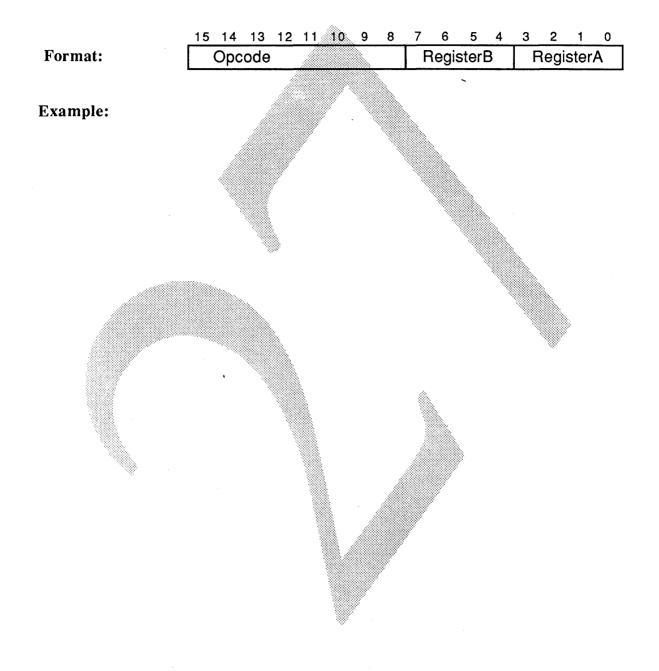

Format:

| 15 | 14  | 13  | 12 | 11 | 10 | 9 | 8 |   | 6     | 5     | 4 | 3 | 2    | 1    | _0 |

|----|-----|-----|----|----|----|---|---|---|-------|-------|---|---|------|------|----|

|    | Орс | ode |    |    |    |   |   | F | Regis | steri | 3 | F | Regi | ster | Α  |

Add

Add

Add

Operation:

Add RegB + RegA → RegB

Description:

Add the contents of RegA to the contents of RegB. Store the

result in RegB. Clear carry bits C1, C2, and C3.

Condition codes:

N -- Set if result is negative, cleared otherwise.

Z -- Set if result is equal to zero, cleared otherwise.

V -- Set if an overflow is generated, cleared otherwise.

C -- Set if a carry is generated, cleared otherwise.

**Exceptions:**

A trap occurs if the operation sets the V condition code bit and

Trap\_on\_Overflow is enabled.

**Restrictions:**

None.

Timing:

This instruction takes one cycle.

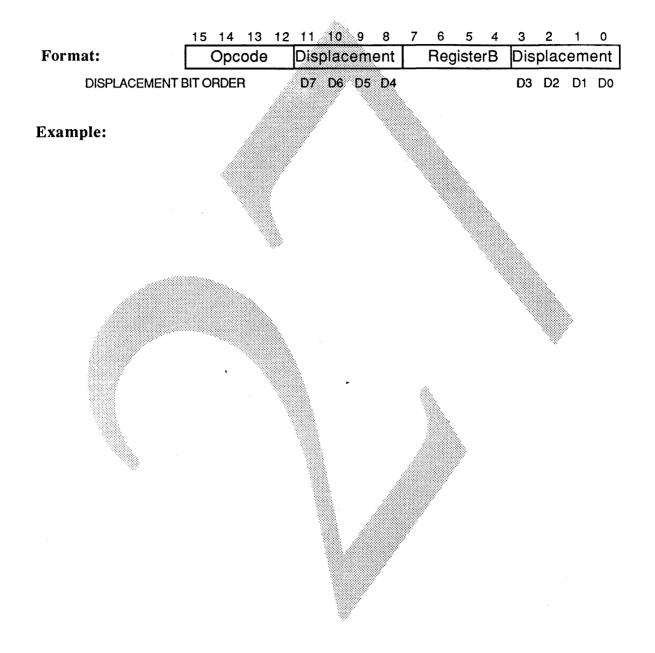

Add

#### Add Immediate

Add

Operation:

Add RegB + Imm → RegB

**Description:**

Add the contents of RegB to the immediate value Imm. Store the result in RegB and clear carry bits C1, C2, and C3. The range for

the value Imm is 1 through 256; the encoding is (Imm -1).

Condition codes:

N -- Set if the result is negative, cleared otherwise. Z -- Set if the result equals zero, cleared otherwise. V -- Set if an overflow is generated, cleared otherwise. C -- Set if a carry is generated, cleared otherwise.

**Exceptions:**

A trap occurs if the operation sets the V condition code bit and

Trap\_on\_Overflow is enabled.

Restrictions:

None.

Timing:

This instruction takes one cycle.

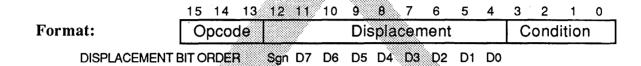

|                | 15    | 14  | 13  | 12 11 | 10  | 9    | 8  | 7 6    | 5    | 4 | 3  | 2   | 1    | 0  |   |

|----------------|-------|-----|-----|-------|-----|------|----|--------|------|---|----|-----|------|----|---|

| Format:        |       | Орс | ode | lr    | nme | diat | е  | Regist | terE | } | In | ıme | diat | te |   |

| DISPLACEMENT E | BIT O | RDE | ₹   | B7    | B6  | B5   | B4 |        |      |   | В3 | B2  | B1   | B0 | • |

AddC

Add with Carry

AddC

**Operation:**

AddC

RegB + RegA → RegB

Description:

Add the contents of the C0 carry status bit and the contents of RegA to the contents of RegB. Store the result in RegB and clear carry

bits C1, C2, and C3.

Condition codes:

N -- Set if the result is negative, cleared otherwise.

Z -- Set if the result equals zero, cleared otherwise. V -- Set if an overflow is generated, cleared otherwise.

C -- Set if a carry is generated, cleared otherwise.

**Exceptions:**

A trap occurs if the operation sets the V condition code bit and

Trap\_on\_Overflow is enabled.

Timing:

This instruction takes one cycle.

Format: Opcode RegisterB RegisterA

AddP

#### Add Partial

AddP

**Operation:**

AddP

$RegB(H/B) + RegA \rightarrow RegB$

**Description:**

If H/B is clear, add RegB to RegA, inhibiting carries between bytes. Set the CO, C1, C2, and C3 carry bits from the carryout of

the corresponding bytes.

If H/B is set, add RegB to RegA, inhibiting carries between halfwords. Set the C0 and C2 carry bits from the carryout of the corresponding halfwords. Clear the C1 and C3 carry bits.

Condition codes:

H/B = 0

N -- Set if any byte is negative, cleared otherwise.

Z -- Set if any byte is equal to zero, cleared otherwise.

V -- The V bit is cleared.

C -- Set if any byte carries, cleared otherwise.

H/B = 1

N -- Set if any halfword is negative, cleared otherwise.

Z -- Set if any halfword is equal to zero, cleared otherwise.

V -- The V bit is cleared.

C -- Set if any halfword carries, cleared otherwise.

**Exceptions:**

None.

**Restrictions:**

None.

Timing:

This instruction takes one cycle.

Format:

| 15 | 14  | 13  | 12 | 11 | 10 | 9 | 8 | 7 | 6     | 5     | 4 | 3 | 2    | 1_   | 0 |  |

|----|-----|-----|----|----|----|---|---|---|-------|-------|---|---|------|------|---|--|

|    | Орс | ode |    |    |    |   |   | F | ?egis | sterl | 3 | F | Regi | ster | Ą |  |

**AdPC**

## Add Program Counter

**AdPC**

**Operation:**

AdPC PC + 1 RegA → RegA

**Description:**

Add the halfword address of the Current PC+ 1 to the contents of

RegA and store the result in RegA.

Condition codes:

N -- Not affected.

Z -- Not affected.

V -- Not affected. C -- Not affected.

**Exceptions:**

None.

Restrictions:

None.

Timing:

This instruction takes one cycle.

Format:

And And And

RegB & RegA → RegB Operation: And

Logically AND the contents of RegB with the contents of RegA. **Description:**

Store the result in RegB.

Condition codes: N -- Set if the result is negative, cleared otherwise.

Z -- Set if the result equals zero, cleared otherwise.V -- The V bit is cleared.

C -- Not affected.

**Exceptions:** None.

Restrictions: None.

Timing: This instruction takes one cycle.

15 14 13 12 11 10 9 2 Format: Opcode RegisterB RegisterA

AndC

## And Complement

AndC

**Operation:**

**AndC**

RegB & ~RegA → RegB

**Description:**

Logically AND the contents of RegB with the ones complement of

the contents of RegA. Store the result in RegB.

Condition codes:

N -- Set if the result is negative, cleared otherwise.

Z -- Set if the result equals zero, cleared otherwise. V -- The V bit is cleared.

C -- Not affected.

**Exceptions:**

None.

Restrictions:

None.

Timing:

This instruction takes one cycle.

Format:

| 15 | 14  | 13  | 12 11 | 10 | 9 | 8 | 7 6   | 5     | 4 | 3 | 2    | 1    | 0 |

|----|-----|-----|-------|----|---|---|-------|-------|---|---|------|------|---|

| (  | Орс | ode |       |    |   |   | Regis | sterl | 3 | F | Regi | ster | Α |

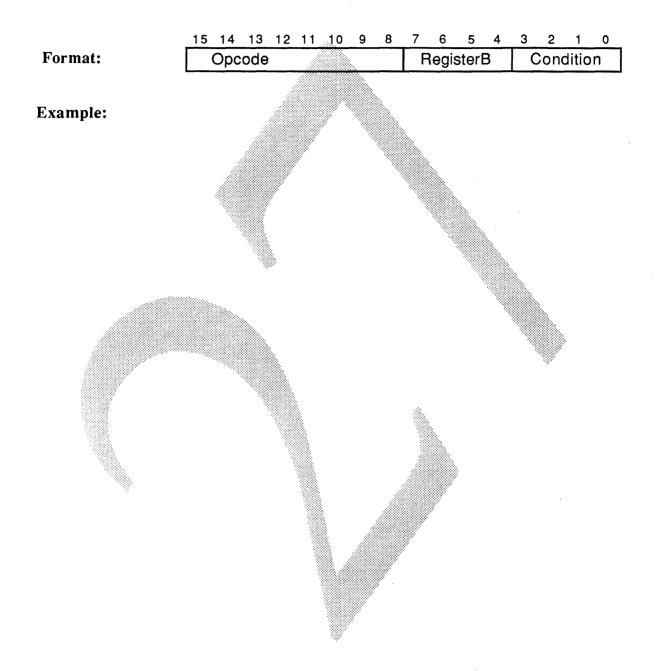

Bcc

Branch on Condition

Bcc

Operation:

Bcc

PC + Displacement

**Description:**

If the condition cc specified by the instruction is met, continue execution at the instruction whose halfword address is PC + Displacement. Otherwise, continue execution. In all cases, execute the instruction whose address is in Next PC. **Displacement** is a 9-bit quantity (8 bits + sign bit).

The encodings and meanings of the ce field are shown in the table below.

Table 7. CC Field Encodings

| va.                  |                |                                        |                                               |

|----------------------|----------------|----------------------------------------|-----------------------------------------------|

| Encoding             | cc             | Condition                              | Meaning                                       |

| 0<br>1<br>2<br>3     | EQ<br>LT<br>LE | reserved<br>Z=1<br>N=1<br>N=1 or Z=1   | equal<br>less than<br>less or equal           |

| 4<br>5<br>6<br>7     | LO<br>LS<br>OV | C=0<br>C=0 or Z=1<br>V=1<br>reserved   | lower<br>less or same<br>overflow             |

| 8<br>9<br>10<br>11   | NE<br>GE<br>GT | reserved<br>Z=0<br>N=0<br>N=0 and Z =0 | not equal<br>greater or equal<br>greater than |

| 12<br>13<br>14<br>15 | HS<br>HI<br>NV | C=1<br>C=1 and Z=0<br>V=0<br>reserved  | higher or same<br>higher<br>no overflow       |

Condition codes: N -- Not affected.

Z -- Not affected.

V -- Not affected.

C -- Not affected.

**Exceptions:**

None.

**Restrictions:**

None.

Timing:

This instruction takes one cycle.

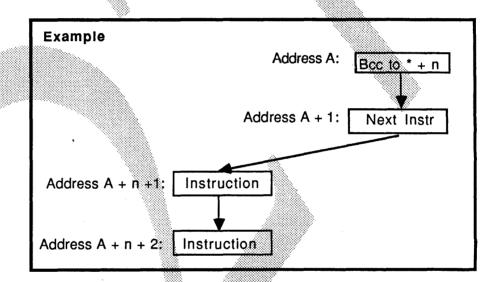

Example:

The example below illustrates the order in which the processor executes instructions following the Bcc instruction.

**CDC**

Create Data Cache Line

**CDC**

**Operation:**

**CDC**

@RegA

**Description:**

If the LRU cache line in the set addressed by RegA is modified, write the data back to Main Memory. Set the tag for the LRU line to

valid and unmodified, with the address in RegA.

Condition codes:

N -- Not affected.

Z -- Not affected. V -- Not affected. C -- Not affected.

**Exceptions:**

A privileged access fault may occur if executed in user mode.

**Restrictions:**

None.

Timing:

This instruction takes one cycle.

Format:

| 15 | 14  | 13  | 12 11 | 10 | 9 | 8 | 7 6 | 5 | 4 | 3 | 2    | 1    | 0 |

|----|-----|-----|-------|----|---|---|-----|---|---|---|------|------|---|

|    | Opc | ode |       |    |   |   |     |   |   | R | egis | ter/ | 1 |

ClrF

Clear Field

ClrF

**Operation:**

0 → RegA<Mask> ClrF

**Description:**

Clear the bits of the field defined by the Mask register in RegA to zeroes. Store the result in RegA. This instruction does not affect

bits outside the field.

Condition codes:

N -- Not affected.

Z -- Not affected. V -- Not affected. C -- Not affected.

Exceptions:

None.

Restrictions:

The result is undefined if an illegal field definition has been moved into the Mask register with a Move to Special (Mov) instruction.

Timing:

This instruction takes one cycle.

Format:

|   | 15 | 14  | 13  | 12 | 11 | 10 | 9 | 8 | 76 | 5 | 4 | 3 | 2    | 1    | 0   |

|---|----|-----|-----|----|----|----|---|---|----|---|---|---|------|------|-----|

| 1 |    | Орс | ode |    |    | :  |   |   |    |   |   | R | egis | ter/ | ١ . |

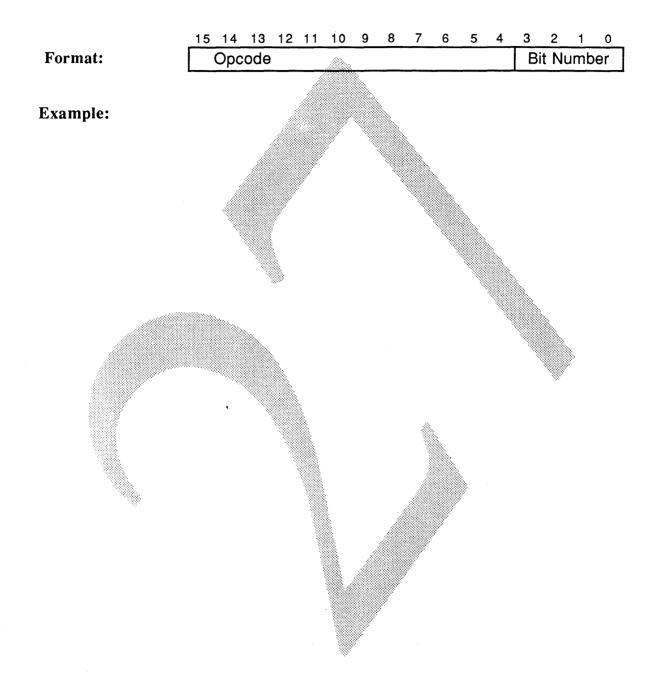

ClrM Clear Mode ClrM

**Operation:**

ClrM

BitNumber

**Description:**

Clear the specified Mode bit in the System Status/Control

register. The mode bits are:

- 0 MD control

- 1 Halfword/byte

- 2 MD full

- 3 Overflow trap enable

- 4 Register available

- 5 reserved

- 6 reserved

- 7 reserved

- 8-9 reserved

- 10 Branch taken trap enable†

- 11 PU trap enable/disable†

- 12 User/system<sup>†</sup>

- 13. Cluster number<sup>†</sup>

- 14 reserved

- 15 reserved

Condition codes:

N -- No ected.

Z -- Not affected.

V -- Not affected.

C -- Not affected.

**Exceptions:**

A privileged operation trap occurs if the instruction is executed when in user mode and any one of mode bits 8 through 15 is specified. An illegal operation trap occurs if mode bit 5, 6, 7, 8, 9, 14, or 15 is

specified in the instruction.

**Restrictions:**

None.

Timing:

This instruction takes one cycle.

<sup>†</sup>Indicates privileged.

**CLZ**

Count Leading Zeros

**CLZ**

**Operation:**

**CLZ** RegA → RegB

**Description:**

Count the number of leading zeros in RegA. Store the number in

RegB.

Condition codes:

N -- Set if RegA is less than zero, cleared otherwise.

Z -- Set if RegA equals zero, cleared otherwise.

V -- The V bit is cleared.

C -- Not affected.

**Exceptions:**

Note.

Restrictions:

None.

Timing:

This instruction takes one cycle.

Format:

| 15 14 13 1 | 2 11 | 10 | 9 | 8 | 7 6   | 5    | 4 | 3 | 2    | 1    | 0 |

|------------|------|----|---|---|-------|------|---|---|------|------|---|

| Opcode     |      |    |   |   | Regis | ster | 3 | F | Regi | ster | 4 |

Cmp

Compare

Cmp

**Operation:**

Cmp RegB - RegA

**Description:**

Subtract the contents of RegA from the contents of RegB and set

the condition codes.

Condition codes:

N -- Set if RegB is arithmetically less than RegA, cleared

otherwise.

Z -- Set if the result equals zero, cleared otherwise.

V -- The V bit is cleared.

C -- Set if unsigned RegB is greater than or equal to RegA.

(C = not borrow), cleared otherwise

**Exceptions:**

None.

**Restrictions:**

None.

Timing:

This instruction takes one cycle.

Format:

| 15 | 14  | 13  | 12 | 11 | 10 | 9 | 8 | 7 6    | 5   | 4 | 3 | 2    | _1   | 0 |

|----|-----|-----|----|----|----|---|---|--------|-----|---|---|------|------|---|

| (  | Орс | ode |    |    |    |   |   | Regist | erE | 3 | F | Regi | ster | Α |

Cmp

Compare Immediate

**Cmp**

**Operation:**

Cmp

RegB - Imm

**Description:**

Subtract the immediate value Imm from the contents of RegB and

set the condition codes. The value Imm must be in the range 1

through 256. Encoding for Imm is (Imm - 1).

Condition codes:

N -- Set if RegB is arithmetically less than Imm, cleared

otherwise

Z -- Set if the a sult equals zero, cleared otherwise.

V -- The V bit ared.

C -- Set if unsigned **RegB** is greater than or equal to **Imm**, cleared otherwise (C = not borrow).

**Exceptions:**

None.

Restrictions:

None.

Timing: