# What the Hell is this?

#### What this was

This was a document called "The Lisa Theory of Operations Manual" from Apple Computer, Inc dated June 3, 1983. It consisted of photocopied pages (some a little fuzzy) describing the hardware of the Lisa 1 and was written using the editor of the Lisa Pascal Workshop. The drawings were hand-drawn and still had editing marks on them. There were no schematics, although they were referenced in the manual.

At the time I got this, Apple was also sending a document called "Macintosh XL Hardware Information" which had additions/corrections for the Manual although it didn't include the major hardware differences between the Lisa 1 and Lisa 2.

#### What this is

I didn't really like the state that the Manual was in. First off, it described only the Lisa 1. Secondly, the schematics were missing. Thirdly, the copy was poor and wouldn't copy any better if I wanted to send this to another of my fellow Lisaphiles. Fourthly, some of the drawings would cause severe eye strain if you really needed to look at them. Fifthly, since the editor used to write the original used strictly ascii characters, some of the notation is a bit strange.

So I began the project of entering the Manual into Macwrite. This set of documents is the original manual with the original wording, right or wrong. I have added my own corrections and comments surrounded by square brackets for use in making the final version. I have corrected misspellings. By the way, I have NOT incorporated the changes/additions specified in the XL Corrections paper. I figure I'll get this Manual up to Lisa 2 standards, then put them in.

I am also replacing the clumsy hand-drawn diagrams with my own clumsy Macpaint pictures. I may not win any art awards with them, but I think they're an improvement. I have also replaced the notation of an active low signal from SIGNAL to SIGNAL with a modified Geneva-12 font which is included on this disk. I have also modified my Geneva to have the 0 with a slash through it so you can tell it from an O more easily.

#### What this will be

Eventually, this Manual will describe not only the Lisa 1, but the Lisa 2 series of computers also: Lisa 2, 2/5, 2/10, and Mac XL. I hope to have or make schematics of these versions too. The Glossary, Table of Contents, and Index will be more fully worked out when the Manual has been completed.

6:01:41 AM 10/12/85

Gary M. Kato 2346 Sutter Ave. #11 Santa Clara, CA 95050 (408) 249-1101 Compuserve 76074,1020

# **Lisa Theory of Operations**

[Let's use the Lisa script here! - gk]

WARNING: This equipment has been certified to comply with the limits for a Class B computing device, pursuant to Subpart J of Part 15 of FCC rules. Only peripherals (computer input/output devices, terminal, printers, and the like) certified to comply with the Class B limits may be attached to this computer. Operation with noncertified peripherals is likely to result in interference to radio and TV reception.

© Apple Computer Inc., 1985 20525 Mariani Ave. Cupertino, CA 95014

# PREFACE (condensed version)

The Lisa Hardware Manual provides information on the functional performance and general specifications of the Lisa. Chapter 1 provides a general introduction to the Lisa and gives a brief description of the architecture.

Chapter 2 is of interest to programmers who need to know the address and interrupt structure, as well as the operation of the memory mapping unit. Chapter 3 provides dimensions, environmental requirements, and interfaces that are useful to design engineers wishing to interface to the Lisa.

Following are other manuals that relate to the Lisa.

- Lisa Owner's Guide

- · Lisa Theory of Operations

- Profile Owner's Manual

- · Operating System Reference Manual for the Lisa.

# PREFACE [expanded version]

The Lisa Theory of Operations Manual provides a detailed description of the functional operation of the Lisa hardware. Chapter 1 provides a general introduction to the Lisa and gives a brief description of the architecture.

Chapter 2 is of interest to programmers who need to know the address and interrupt structure, and the operation of the memory mapping unit. Chapter 3 provides dimensions, environmental requirements, and interfaces that are useful to design engineers wishing to interface to the Lisa.

Chapter 4 through 11 contain complete functional descriptions and theory of operation for each module in the Lisa. These chapters will not be of interest to the general reader; they are intended for use only by design and service personnel. Included is information on the:

- Processor board

- Memory board

- I/O board

- · Video board

- User Interface

- Floppy-disk drives

- Power supply

- Assembly.

Schematics for all modules are located in the appendixes. Other relevant documents include the:

- Lisa Owner's Guide

- Operating System Reference Manual for the Lisa.

- Profile Owner's Manual

- Motorola 68000 User's Manual

- Motorola 6504 User's Manual [Does Motorola make this?-qk]

- Motorola 6522 User's Manual [Does Motorola make this?-qk]

- [National Semicondutor gk] COPS421 User's Manual

- [Zilog gk] 8530 SCC User's Manual

- AMD 9512 Data Sheet.

[Include 9512 only if this was a real option - gk] [There should be addresses where the user can contact the manufacturers and part numbers of the documents. There should also be a listing of books from other publishers like Osborne, Addison-Wesley, Prentice-Hall, etc. - gk]

# Chapter 1. Architecture

The Lisa is a powerful, compact personal computer. It features an integral screen, disk storage, and a large amount of memory. In addition, you can add an extensive mix of input and/or output (I/O) devices. Perhaps the most striking hardware feature is the mouse, which the operator uses to communicate with the Lisa software.

Details of the operation and use of the Lisa can be found elsewhere; see the Preface for a list of related documents. This manual provides an exhaustive description of the internal workings of the Lisa for those who need to diagnose, repair, or expand one.

### 1.1 LAYOUT

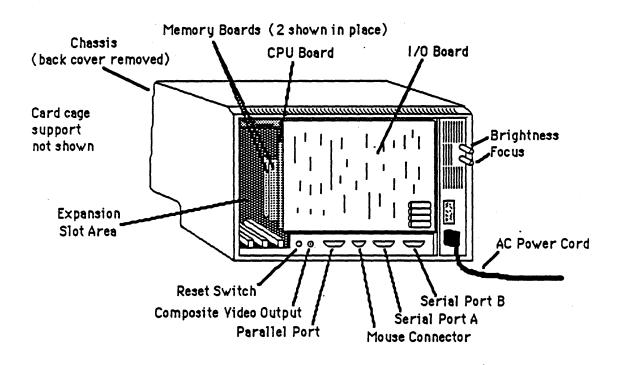

The Lisa consists of a cabinet that houses the screen, removable hardware modules, and two floppy-disk drives, and a detachable keyboard and mouse that plug into the front and back of the cabinet, respectively.

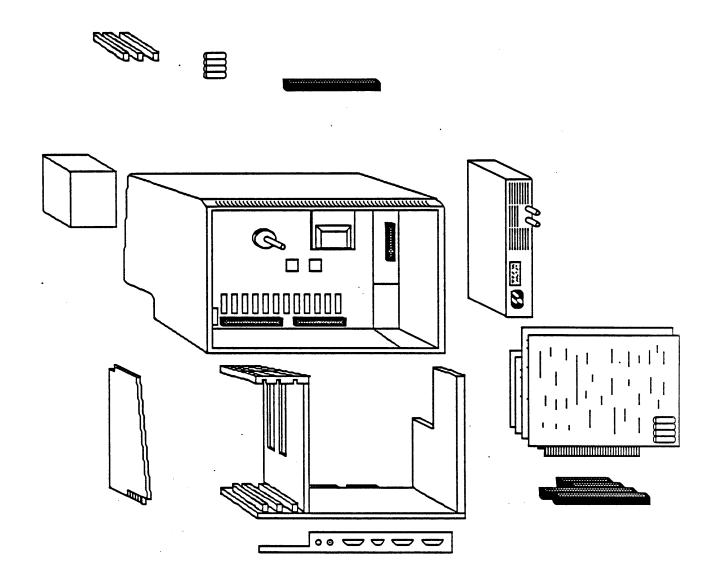

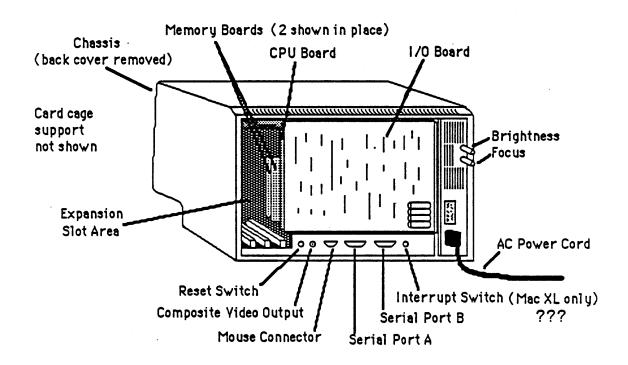

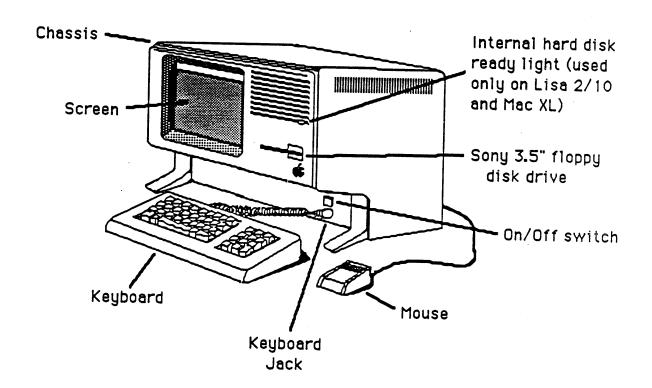

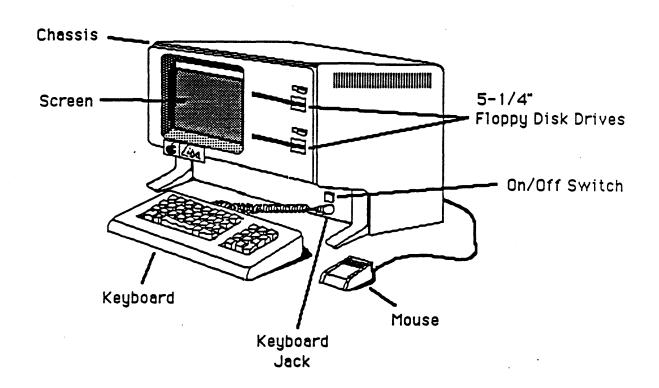

Figure 1-1 presents a front view of the Lisa. Figure 1-2 shows the connectors and controls on the back of the Lisa.

[Differences between various models should be pointed out or have a separate diagram. There should be two front views: Lisa 1 and Lisa 2. The Lisa 2 diagram should point out the internal hard disk ready light and mention that it is used only for those Lisas with the internal 10MB hard disk. There should be two back views: one for both the Lisa 1 and the Lisa 2/5, and another for the Lisa 2/10 and Mac XL. The interrupt button should be pointed out in the latter and mention that it is found only on the Mac XL.-gk]

The hardware modules inside the cabinet are accessed by removing the front and back panels. Note that removing these panels causes the Lisa to turn off due to the panel safety interlocks. Also note that this does not remove power from the Lisa; to remove power, unplug the line cord.

Chapter 3 describes the assembly of removable hardware modules in detail. Assembly and disassembly procedures are available in other Lisa documents; see the Preface for a list of related documents.

# Figure 1-1. Front View

Figure 1-2. Back View with Panel Removed.

### 1.2 HARDWARE STRUCTURE

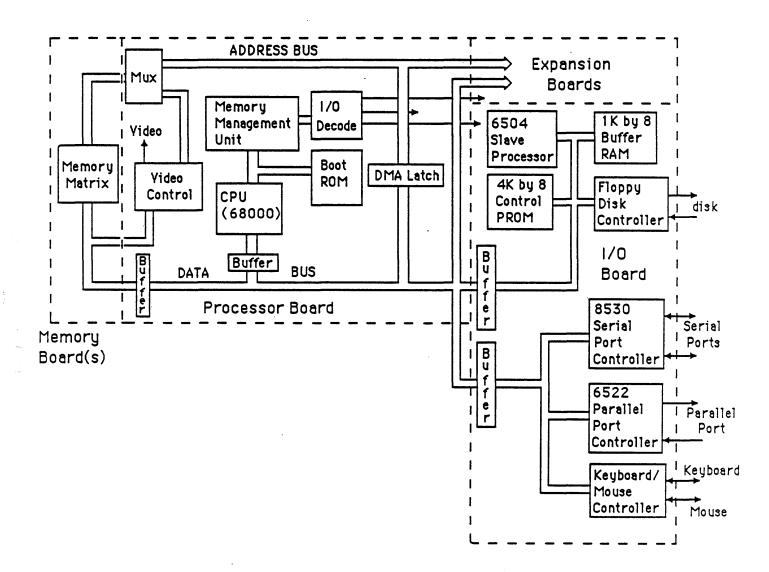

The logic components of the Lisa are interconnected by several buses, as shown in Figure 1-3. The main bus connects the processor board with the I/O board and the expansion slots.

# Figure 1-3. Block Diagram

The heart of the Lisa is the processor board; it contains the central processing unit (CPU), timing, memory management unit (MMU), video generation logic, I/O decode and interrupt logic. It also provides the necessary control and timing signals for the memory boards. The memory boards can be in several possible configurations, depending on the size and type of memory installed. The memory board contains the main random access memory (RAM) matrix, plus parity generation and checking, and some address decoding logic.

The Lisa communicates with the outside world principally through the I/O board. This board provides controllers and interfaces for:

- \* Two serial I/O ports,

- \* A parallel port for peripherals, such as a hard disk or printer,

- \* Keyboard,

- \* Mouse.

- \* Speaker, and

- \* Floppy-disk drives.

Video contrast is also controlled by this board. In addition, the CPU may have use of an optional arithmetic processing unit, located on the I/O board. [Was this ever a real option?-gk]

The video board is controlled both by the logic present on the processor board and by the contrast latch on the I/O board. It provides the analog logic necessary to drive the video monitor. The video memory is used to display an image organized as a bit map in main memory.

The expansion slots on the motherboard provide locations for additional logic modules. A description of the bus interface itself can be found in Chapter 3 of this manual.

[This paragraph is for Lisa 1 only. - gk]

The disk drives accept standard Fileware diskettes. The diskettes are described in a separate manual; see the Preface for a list of related documents. An overview of the disk drives is given in Chapter 9. Details of the disk drives can be found in the relevant disk drive manual; see the Preface. [There should be another paragraph talking about the Sony drive of the Lisa 2s and possibly of the hard disk for the 2/10 and XL. - gk]

The monitor is a high-resolution twelve-inch diagonal monochrome cathode-ray tube (CRT) that uses a 60 hertz (Hz) refresh rate. It displays individual pixels as black or white only. There is no gray scale as such; grays are displayed by intermixing black and white pixels in the same area.

### 1.3 THE CENTRAL PROCESSING UNIT

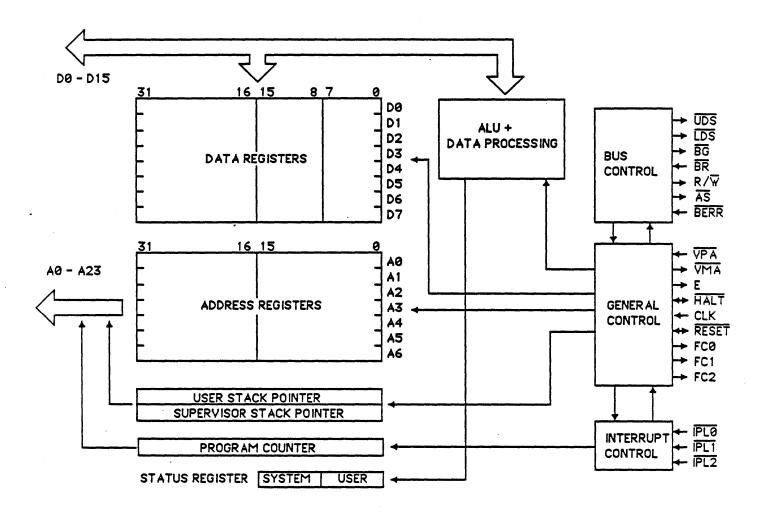

The Lisa's central processor is based on the Motorola 68000 processor chip. A block diagram of the 68000 is shown in Figure 1-4. The 68000 provides:

- \* 32-bit data and address registers

- \* 16 megabyte (Mbyte) addressing range

- \* Memory-mapped I/O

- \* 14 addressing modes.

In addition to the seventeen 32-bit registers, a 32-bit program counter, and a 16-bit status register, there exists the possibility of configuring the general purpose registers to allow for the width of the data actually being used.

In the Lisa, the 68000 is driven by a 5 megahertz (MHz) clock with a period of 200 nanoseconds (ns). The processor memory access time is 800 ns. The CPU and the video logic interleave memory accesses. Instruction execution times must be a multiple of 800 ns. All instructions that are longer than 800 ns have wait states inserted if required, so that all instructions execute in multiples of 800 ns.

Figure 1-4. Processor Block Diagram

### 1.4 MEMORY

The 68000 CPU generates 24-bit logical addresses to access data in the Lisa. These are considered logical addresses and the set of all possible addresses is the 16 Mbyte logical address space of the Lisa. The logical address space is used to access all random access memory, ROM or RAM, and I/O present in the Lisa.

In order to access one of these physical locations, each logical address must be translated into a physical address. A physical address can point to one of the three possible physical address spaces in the Lisa.

#### These are:

- \* Main memory, 2 Mbytes of RAM,

- \* I/O space, I/O devices and latches,

- \* Special I/O, MMU registers and boot ROM.

The translation is performed by a method known as relocation. It is implemented by a section of logic on the processor board known as the MMU.

The main memory is where programs and data are stored while

in use by the Lisa. The MMU provides both the translation of the address and flags that provide further information on the type and accessibility of the data. This is described in section 2.3.

The I/O space is used to access peripheral controllers and status and control registers. The special I/O space is used to access bootstrap routines stored in non-volatile ROM and also to access the registers internal to the MMU where translation data is stored. The MMU internal registers permit the operating system to control the entire relocation process.

Within the MMU there are four identical sets of translation registers, each representing a different mapping of logical addresses into the three physical address spaces. Each set is called a context.

Context 0 is reserved for use by the operating system, while 1, 2 and 3 are available for the operator, who is also referred to as the "user", programs. Only one context is current at any given time. By switching contexts, rapid switching between processes can be affected under user control.

User programs only need to be aware which segments of logical space are available to them and which of these point to RAM and to valid I/O addresses. The MMU performs checks and classifies the type of storage that they point to, such as stack memory, ROM, and I/O space.

The maximum configuration of RAM storage that can be present in the main memory is 2 Mbytes. Each physical memory space within the Lisa is divided as shown in Figure 1-5.

Special I/O space is not invoked during normal operation. It is used during startup, and when the registers that configure the MMU are being modified. During normal operation, only the operating system has access to special I/O space. Note that the operating system is capable of providing this ability to any program, although it would not be an advisable practice to do so.

Since logical addresses make no distinction among the three possible address spaces, each can be operated on by the full 68000 command set. Each physical address space shown in Figure 1-5 is distinguished by signals generated within the MMU. There is, therefore, no physical overlap of memory space and no masking of any memory area.

| Hexadecimal<br>Address Range | Physical<br>Address Space | Function             |

|------------------------------|---------------------------|----------------------|

| 000000-1FFFF                 | Main Memory               | RAM Storage          |

| 000000-001FFF                | 1/0                       | Slot 1 low decode    |

| 002000-003FFF                | 1/0                       | Slot 1 high decode   |

| 004000-005FFF                | 1/0                       | Slot 2 low decode    |

| 006000-007FFF                | 1/0                       | Slot 2 high decode   |

| 008000-009FFF                | 1/0                       | Slot 3 low decode    |

| 00B000-00BFFF                | 1/0                       | Slot 3 high decode   |

| 00C000-00CFFF                | 1/0                       | FD Controller memory |

| 00D000-00DFFF                | 1/0                       | I/O board devices    |

| 00E000-00EFFF                | 1/0                       | CPU board devices    |

| xx0000-xx3FFF                | Special I/O               | Boot & self-test ROM |

Figure 1-5. Physical Memory Map

### 1.5 INTERNAL BUSES

The Lisa uses two bus structures to communicate between hardware modules, such as the processor board, I/O board, etc. Most boards communicate through the system bus, which interconnects the processor board with the I/O board and the expansion slots.

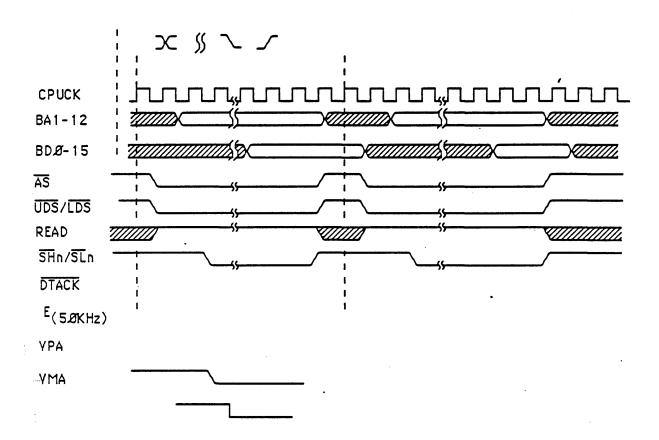

The system bus is based on the interface signals of the 68000 CPU. Operations and timing on the bus follow those of the 68000 closely, although not identically. Refer to Chapter 4 for a discussion of the system bus and its operation.

The second bus, the memory bus, is a specialized set of signals

that are used by the processor board to provide timing and control signals to the memory board(s).

### 1.6 DATA STORAGE MEDIA

The Lisa[1 - gk] contains two high-density mini-floppy disk drives. Disks from non-Lisa computers may not be freely interchanged with those used in the Lisa, due to the special encoding of disks format and media type. Details of the disk drives can be found in Chapter 9 or from the relevant disk drive manual; see the Preface for a list of related documents.

In addition, a compatible hard-disk drive, such as Apple's Profile, can be connected to the parallel port to provide enhanced data storage capacity and access time. Details of this interface can be found in Chapter 3. Format and storage capacity of this drive are a function of the actual unit used. Details are beyond the scope of this document.

### 1.7 USER INTERFACES

The user communicates with the Lisa by way of the keyboard, as on a conventional computer, and by using the mouse. In fact, most tasks can be completed without typing.

You can roll the mouse around a small area beside the Lisa to move a [the - gk] cursor around the CRT. Press the button on top of the mouse to select among the available functions displayed on the CRT.

### 1.8 ADDITIONAL FEATURES

A real-time clock has been incorporated into the I/O board. The clock keeps the correct time, and is available to the programmer for use in a number of applications where measurement of elapsed time or the current date and time is important.

The Lisa is also equipped with a battery-backup unit. This enables the real-time clock to function while the Lisa is

entirely disconnected from a power source. It also preserves the contents of the parameter memory.

[ Lisa 2 Notes -gk. There are a number of differences between the original Lisa (aka Lisa 1) described in this document and the various models of the Lisa 2 and Mac XL. Here are the various models of Lisa:

Lisa 1: 2 Twiggy drives. Battery backup for clock. Space for AMD 9512 arithmetic processor.

Lisa 2: As Lisa 1 except for 1 3.5 inch floppy drive in place of both Twiggy drives.

Lisa 2/5: As Lisa 2, but with a 5MB Profile connected to the parallel port connector in the back.

Lisa 2/10 or Mac XL: Different System I/O board. No longer has a parallel connector in the back. An internal 10MB hard disk drive is connected internally to the parallel port. AMD 9512 capability deleted. No battery backup for clock. (Note: there may also be a difference between Mac XL and Lisa 2/10. I suspect that the Lisa 2/10 back panel is much the same as on the other Lisas (except for the parallel connector). The back panel of the XL has an extra push-button on the back labeled "Interrupt", presumably to make the XL Macintosh-compatible.) ]

# CHAPTER 2. PROGRAMMING

This chapter describes the interface that the Lisa hardware provides to the software. It is not intended as an exhaustive description of the operating system, nor should it be regarded as a specification of required parameters for an operating system on the Lisa. Refer to the Preface for the names of manuals that contain programming details.

## 2.1 THE INSTRUCTION SET

The instruction set of the Lisa is essentially that of the 68000 processor. Differences occur only in the details of addressing the memory and I/O in the Lisa. Instructions can be categorized into four possible modes of logical addressing.

- \* Data: When an effective address mode refers to data operands, it is considered as a data address mode.

- \* Memory: When an effective address mode refers to memory operands, it is considered a memory address mode.

- \* Alterable: When an effective address mode is used to refer to writeable operands, it is considered an alterable address mode.

- \* Control: When an effective address mode is used to refer to memory operands without an associated size, it is considered a control address mode.

It is possible to combine these categories within the instruction set, resulting in more specialized categories. For example, data alterable refers to address modes that are both data and alterable.

Note that the status register addressing mode is not permitted unless it is explicitly mentioned as a legal addressing mode.

The full instruction set is not discussed here. Details are

available in the 68000 User's Manual.

### 2.2 CPU REGISTERS AND THEIR USE

There is a 16-bit status register, which consists of a user byte and a system byte. In addition, there are a number of 32-bit registers in the CPU that are available to the user. These are:

- \* 8 Data registers

- \* 7 Address registers

- \* 1 User stack pointer

- \* 1 Supervisor stack pointer

- \* 1 Program Counter.

The status register contains a number of coded bits, divided into a user byte and a supervisor byte. The supervisor byte contains the trace and supervisor flags, plus a three-bit code showing the current interrupt mask. The user byte contains the condition codes. Refer to the 68000 user manual for a full discussion.

The data registers can be used for bit, byte, word, or long-word operations. The address registers can be used as word or long-word registers. Both the address registers and the stack pointer can be used as software stack pointers and base-address registers. All data, address, and stack pointer registers can be used as index registers.

Where a data register is used to store less than the full 32-bit capacity, the bit, byte, or word is stored in the low-order part of the register. The least significant bit (LSB) is bit zero and the most significant bit (MSB) is bit 31.

Address registers provide either the low-order word, or the full 32-bit long-word, as the source operand, depending on the operation. When used as a destination, the entire register is affected, regardless of the size of the operand required in the operation.

### 2.3 MEMORY MANAGEMENT SCHEME

The MMU is a hardware device that translates logical addresses emitted by the CPU into physical addresses for objects in main memory or I/O space. At the same time, it provides access controls that are preset by the operating system. These prevent a particular program from accessing areas of memory outside of the portion assigned to it.

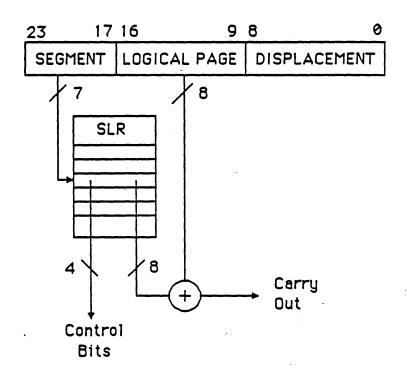

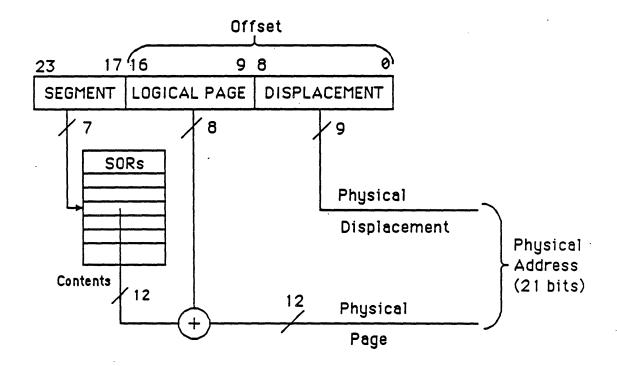

The logical address provided by the CPU consists of 24 bits. These are interpreted by the MMU in three sections. The first section consists of bits 23 through 17 and is the logical segment number. The second section consists of bits 16 through 9 and provides the logical page displacement. The third section consists of bits 8 through 0 and gives the displacement, both logical and physical, within the page. This can be seen in Figure 2-1.

# Figure 2-1. Address Word Decode

Logical addresses can point to any part of the 16 Mbyte addressing space. The MMU interprets these logical addresses on the basis of parameters loaded into its registers by the operating system.

The Lisa's memory physically occupies 2 Mbytes of physical address space. This would imply that only 16 segments, each of 128 kilobytes (Kbytes) can be used meaningfully. However, each segment's physical address space does not necessarily occupy the full 128 Kbytes allotted to it in logical address space. Each segment can be mapped into as little as one 512-byte page of physical memory. Therefore many more than 16 logical segments can map into the 2 Mbyte memory space.

Each segment within the MMU has two registers associated with it. The first is known as the Segment Origin Register (SOR). It describes the physical origin of the segment, which is a page boundary within the memory. The second is the Segment Limit Register (SLR). It describes both the size in terms of 512-byte pages and the type of space being addressed.

Each context in the MMU consists of a table of 128 segment descriptors consisting of the SOR and SLR. The segment number, bits 23-17 of the logical address, is used to index into the table and retrieve the value stored in the SOR and SLR.

### 2.3.1 Address Transformation

Logical address space is divided into 128 logical segments. Each segment consists of up to 256 pages of 512 bytes per page. Therefore, the maximum segment size is 128 Kbytes and the minimum is 512 bytes.

The SOR register [the "register" is redundant - gk] contains the 12-bit page address in physical space where the corresponding physical segment begins. The entire segment is located in physical space with respect to this origin. The logical page displacement given by the second section of the logical address, bits 16-9, is added to the contents of SOR to produce the physical page address being accessed. The logical operation is shown in Figure 2-1. The least significant nine bits of the logical address translate directly into the physical displacement.

The SLR contains the size limit of the physical segment, given as a number of pages, plus control bits that define the type of the segment. This indicates which of the three physical address spaces the segment is contained in: memory, I/O, or special I/O. It can also indicate the memory use, such as read-only or stack.

Once the SOR contents and logical page displacement have been added, the MMU performs a limit check to see whether the resulting physical page lies within the limits given by the SLR. The logical operation performed is shown in Figure 2-2.

The SLR contains control and limit data. The four high-order bits of the register contain control information. The eight low-order bits contain the number of pages in the segment, which is compared with the page offset in the logical address. If the address is within the physical segment, the access

proceeds. If the address lies outside the segment, the access is terminated and an error condition is presented to the CPU.

The physical address word consists of 21 bits. These 21 bits are sufficient to address a space of 2 Mbytes.

Figure 2-2. Segment Limit Check

# 2.3.2 The MMU Registers

)

The MMU registers are physically a matrix of 1024 12-bit registers. These are divided into four sets of 128 pairs of registers, one for each of the four contexts in which the Lisa may operate. The technique of switching contexts is used to reconfigure the Lisa rapidly when switching between processes.

All MMU registers are addressed in special I/O space; refer to Figure 1-5. The contents of the SOR are modified or read by accessing an address in special I/O space, as shown in Figure 2-3.

$000200_{16}$  would have its corresponding SOR set to  $0001_{16}$ . The SOR contains the origin in terms of multiples of 512-byte pages in the physical space.

The segment length is interpreted by the 68000 IN TWO'S COMPLEMENT FORM. Care should therefore be taken in loading the limit to be used. A length of 00 implies a segment of maximum length, 128 Kbytes. A length of  $FF_{16}$  implies the minimal segment length of 512 bytes, one page.

An exception to the above occurs in the case of a stack segment, which is flagged as such by the control bits. In the case of a stack, usage of the segment begins at the top of the segment and decrements. Thus  $00_{16}$  implies one page, 512 bytes, and  $FF_{16}$  implies 128 Kbytes for a stack segment only.

The access control bits are used to restrict program

manipulation of the data pointed to in the area of memory. The bit significance is shown in Figure 2-4.

To set up the MMU registers, the SOR and SLR registers must be set up by the operating system for each of the 128 possible segments. [Instead of "SOR and SLR registers, I suggest "SORs and SLRs" - gk]

|    |    |   | Bit |                                      |

|----|----|---|-----|--------------------------------------|

| 11 | 10 | 9 | 8   | Address space and access limitation  |

| 0  | 1  | 0 | 0   | Main memory read only from stack     |

| 0  | 1  | 0 | 1   | Main memory read only                |

| 0  | 1  | 1 | 0   | Main memory read/write from stack    |

| 0  | 1  | 1 | 1   | Main memory read/write               |

| 1  | 0  | 0 | 1   | I/O space                            |

| 1  | 1  | 0 | 0   | Page invalid (segment not present)   |

| 1  | 1  | 1 | 1   | Special I/O space                    |

| 0  | 0  | 0 | 0   | )                                    |

| 0  | 0  | 0 | 1   | ) Invalid Codes                      |

| 0  | 0  | 1 | 0   | )                                    |

| 1  | 0  | 0 | 0   | )                                    |

| 1  | 0  | 1 | 0   | ) (Unpredictable results will occur) |

| 1  | 0  | 1 | 1   | )                                    |

| 1  | 1  | 0 | 1   | )                                    |

| 1  | 1  | 1 | 0   | )                                    |

Figure 2-4. MMU Access Control Bits

### 2.3.3 MMU Initialization

When the Lisa performs a Power-On Reset (POR), the MMU registers are in an unknown state. In order to write to the MMU registers, the START bit must be set. This is satisfied automatically at power-on time, or by the software accessing I/O address  $00E010_{16}$ .

When the START bit is set, bit 14 of the address acts as a switch between special I/O space and other address spaces. During initialization, bit 14 must be 0 to execute from ROM in

special I/O space. A 1111<sub>2</sub> code output for the access bits of the SLR registers [Instead of "SLR registers", I suggest "SLRs" - gk] is provided by hardware in setup mode. The MMU is not needed to address the boot ROM, so the boot program does not require the MMU to be initialized.

The boot ROM initializes the MMU so that physical memory is contiguous and starts at address 0. Accesses higher than the top of physical memory are not allowed except for segment 126 (addresses of the form FCxxxx<sub>16</sub>) addresses I/O space, and segment 127 (addresses of the form FExxxx<sub>16</sub>) addresses special I/O.

To set the MMU registers, the MMU is disabled. This is done by setting the START bit. This bit is set automatically at power-up when the MMU registers are uninitialized. It must be set whenever the MMU registers are being loaded.

In order that a program in RAM may continue to execute when the START bit is set, a hardware switch is incorporated which permits execution via the MMU. This avoids the need to invoke a subroutine in ROM, which would otherwise be necessary. Address bit 14 controls the switch and the program executing in RAM must execute with address bit 14 set. [Deleted a "1" here. I figured it was a type - gk]

RAM continues to be accessible via the MMU whenever address bit 14 is high while the START bit is set. Thus, any access to a location whose address has bit 14 set results in the MMU performing an address translation, just as in normal processing. By using this feature, it is possible to access both normal mapped address space, and non-mapped special I/O space under control of program addressing.

A program that alters any of the MMU register contents is typically run only in supervisor mode.

### 2.3.4 Contexts

To permit fast switching among program environments, the MMU provides four contexts in which programs can run. The context in which the Lisa is currently running is selected by two control bits, SEG1 and SEG2. The operating system typically runs in context 0. User programs execute in one of the other three contexts. When transfer of control to the Lisa and back is required, such as might happen for interrupt handling, the SEG bits are configured to select the new context. Since the MMU has completely independent sets of SOR and SLR registers [I suggest using "SORs and SLRs" - gk] for each context, context maps are independent of each other.

These bits are located on the processor board and modified as described in subsection 2.5.5. Context is selected by configuring the SEG1 and SEG2 bits to give the required context as shown below:

| SEG2 | SEG1 | Context |  |

|------|------|---------|--|

| 0    | 0    | 0       |  |

| 0    | 1    | 1       |  |

| 1    | 0    | 2       |  |

| 1    | 1    | 3       |  |

Context 0 is intended for exclusive use of the operating system, while contexts 1, 2, and 3 are intended for general purpose use. The Lisa automatically selects context 0 whenever an access is made in supervisor mode. Thus a TRAP instruction can be used to generate a call from a user process to the operating system.

Normally, the context is changed while executing in supervisor mode. Execution in the new context begins when user mode is entered.

The context is loaded by a read or write to certain addresses in I/O space, as follows:

00E00A<sub>16</sub> set SEG1

00E008<sub>16</sub>

reset SEG1

[Let's make sure the above isn't 00E00B - gk]

00E00E<sub>16</sub>

set SEG2

00E00C16

reset SEG2

# 2.4 ADDRESSING IN SPECIAL I/O SPACE

In special I/O space, it is misleading to talk in terms of address translation as used in normal memory space. The address in special I/O space has several meanings, depending on the state of bits 14 and 15.

The address is divided into a number of fields. Either the segment number used to address an MMU register will be present in bits 17 thru 23 or a ROM address will be present in bits 1 thru 13, but not both.

The exact significance of the bits is shown in Figure 2-3 above. The format of a word used to alter an MMU register is:

### SSSSSS010xxxxxxxxxxxBxxx

The "S" designates the bits that select the segment for which the registers are to be altered. The "x" indicates a "don't care" condition. The "B" is a 1 to write to the SOR and a 0 to write to the SLR.

When the ROM is to be addressed, the word has the format:

OR

SSSSSS000RRRRRRRRRRRRRR (via the MMU)

Each "x" bit is ignored. The "S" bits are the address of the segment that points to special I/O space. The "R" bits are used as an address for the boot ROM directly. That is, they are not translated by the MMU.

A program that alters any of the MMU registers should only be

run in supervisor mode.

### 2.5 I/O MAP

A -1 -1 -- - - -

As outlined in Chapter 1, the Lisa contains memory-mapped I/O and a special I/O space. The special I/O space is invoked at power-up time and during accesses to the MMU registers.

A full list of the I/O addresses within the Lisa is given here, along with the bit significance of the data written to and read from each address. An overview of the full I/O space map is given in Figure 2-5. Note that the best (should this be boot? -gk) ROM assigns segment 126 to the 110 space, so all accesses to I/O space using the default MMU setup have a logical address of FCxxxx<sub>16</sub>.

| Address<br>(hexadecimal) | Function                           |

|--------------------------|------------------------------------|

| 000000-001FFF            | Expansion slot #1 Low Decode       |

| 002000-003FFF            | Expansion slot #1 High Decode      |

| 004000-005FFF            | Expansion slot #2 Low Decode       |

| 006000-007FFF            | Expansion slot #2 High Decode      |

| 008000-009FFF            | Expansion slot #3 Low Decode       |

| 00A000-00BFFF            | Expansion slot #3 High Decode      |

| 00C001-00C7FF            | Floppy Disk Control (see 2.5.1)    |

| 00D000-00D3FF            | Serial Ports Control (see 2.5.2)   |

| 00D800-00DBFF            | Parallel Port Control (see 2.5.3)  |

| 00DC00-00DFFF            | Keyboard/Mouse Control (see 2.5.4) |

| 00E000-00E01E            | CPU board Control (see 2.5.5)      |

| 00E01F-00E7FF            | (not used)                         |

| 00E8xx                   | Video Address Latch                |

| 00F0xx                   | Memory Error Address Latch         |

| 00F8xx                   | Status Register                    |

Figure 2-5. I/O Space Overview

# 2.5.1 Floppy Disk Control

The floppy disk controller is located on the I/O board and is

controlled by addressing the portion of physical I/O space in the range 00C001<sub>16</sub>-00C7FF<sub>16</sub>. This area contains command and status data as described below.

The floppy-disk controller consists of a 6504 based microcomputer, which has 4 Kbytes of program ROM for its own exclusive use and 1 Kbyte of buffer RAM that is shared with the main CPU. This RAM is provided with power backup by a battery. Parameters stored in the floppy-disk controller RAM are therefore not lost during power down. [There is no battery backup in the Mac XL. There may not be any in the pre-XL Lisa 2/10. - gk]

The low 16 words of the 6504 address space are treated as a command block. The first byte is used for communication between the CPU and the 6504. The others are used to pass parameters for use in defining command data and status.

Controller commands are written to 00C001<sub>16</sub> and have the significance shown in Figure 2-6.

| Code          | Operation |

|---------------|-----------|

| (hexadecimal) |           |

| 81 | Execute the RWTS routine (parameters are given by |

|----|---------------------------------------------------|

|    | FCC003-FCC00F <sub>16</sub> )                     |

| 82 | Not used                                          |

| 83 | Seek to side/track                                |

| 84 | JSR to routine pointed to by 00C003-5             |

| 85 | Clear Interrupt Status                            |

| 86 | Set Interrupt Mask                                |

| 87 | Clear Interrupt Mask                              |

| 88 | Wait in ROM until called to do cold start         |

| 89 | Loop in ROM                                       |

Figure 2-6. Floppy-disk Commands

The main part of the 6504 code consists of a Read/Write/Track/Sector (RWTS) routine. This utilizes a

command block in the 8 bytes of memory that should be configured by the CPU in accordance with Figure 2-7.

| Address<br>(hexadecimal) | Operation (hexadecimal)                                                                                                                                             |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCC003                   | Command Code  00 Read  01 Write  02 Unclamp  03 Format  04 Verify  05 Format Track  06 Verify Track  07 Read (without checksum verify)  08 Write (without checksum) |

| FCC005                   | Drive Select<br>00 Drive 2 (lower)<br>80 Drive 1 (upper)                                                                                                            |

| FCC007                   | Side Select<br>0x Side 1 (upper)<br>1x Side 2 (lower)                                                                                                               |

| FCC009                   | Sector Number (0 to 22) [decimal? - gk]                                                                                                                             |

| FCC00B                   | Track Number (0 to 44) [decimal? - gk]                                                                                                                              |

| FCC00D                   | Speed Byte                                                                                                                                                          |

| FCC00F                   | Format Confirmation Byte                                                                                                                                            |

| FCC011                   | Error Status                                                                                                                                                        |

| FCC013                   | Disk ID Value                                                                                                                                                       |

Figure 2-7. Floppy-disk Command Block

The disk drives generate an interrupt to the CPU whenever a

diskette is inserted or a diskette eject button is pressed. An interrupt is also generated upon completion of an  $81_{16}$  command. The status of the controller can be found by examining location  $00C05F_{16}$ , as shown in Figure 2-8.

| Error Codes (hexadecimal) | Significance                |

|---------------------------|-----------------------------|

| 01                        | Invalid Command             |

| 02                        | Invalid Drive               |

| 03                        | Invalid Sector              |

| 04                        | Invalid Side                |

| 05                        | Invalid Track               |

| 06                        | Invalid Clear Mask          |

| 07                        | No Disk                     |

| 08                        | Drive Not Enabled           |

| 09                        | Interrupts Pending          |

| 0A                        | Invalid Format Confirmation |

| 0B                        | ROM Selftest Failure        |

| 0C                        | Unexpected IRQ or NMI       |

| 14                        | Write Protect Error         |

| 15                        | Unable to Verify            |

| 16                        | Unable to Clamp             |

| 17                        | Unable to Read              |

| 18                        | Unable to Write             |

| 19                        | Unable to Unclamp           |

| 1A                        | Unable to Find Calibration  |

| 1B                        | Unable to Adjust Speed      |

| 1C                        | Unable to Write Calibration |

Figure 2-8. Floppy-disk Controller Error Codes

Note that the interrupt flag must first be enabled or a bus error will occur. The enable bit must be high in order to be able to access the floppy RAM that is shared by the floppy-disk controller and the processor board. The interrupt source is identified by this status byte, the bit interpretation being coded according to Figure 2-9.

The disk controller has an area of memory that can be used for CPU storage of parameters. It is located between  $00C181_{16}$  and  $00C1FF_{16}$ .

The memory area used for information transfer to and from the disk controller is shared by the CPU and the 6504 and is located between  $00C501_{16}$  and  $00C7FF_{16}$ .

| Bit | Significance                              |

|-----|-------------------------------------------|

| 7   | Set if bits 5, 4, or 6 set                |

| 6   | Set if RWTS complete for Drive 2          |

| 5   | Set when button on Drive 2 is pushed      |

| 4   | Set when disk in place on Drive 2         |

| 3   | Set if bits 0, 1, or 2 set                |

| 2   | Set if RWTS complete for Drive 1          |

| 1   | Set when button on Drive 1 is pushed      |

| 0   | Set when disk in place on Drive 1         |

| ·   | Figure 2-9. Floppy-disk Interrupt Sources |

2.5.2 Serial Port Control

The serial logic interface is implemented by a serial communication controller (SCC) dual channel device. Refer to the 8530 serial communication controller manual for details.

The two serial interfaces in the Lisa are accessed via the peripheral control device by accessing four distinct addresses in I/O space, as shown below.

| Channel A | Data:    | 00D247 <sub>16</sub> |

|-----------|----------|----------------------|

|           | Control: | 00D243 <sub>16</sub> |

| Channel B | Data:    | 00D245 <sub>16</sub> |

|           | Control: | 00D241 <sub>16</sub> |

The baud rate for each of the two channels is defined in terms

of two time constants, which must be loaded into the SCC. The time constants are governed by the formulas:

TC(A) = 4,000,000/(2 \* BaudRate) - 2

TC(B) = 3,686,400/(2 \* BaudRate) - 2

This results in a table of baud rate values shown in Figure 2-10. The serial ports use autovectoring, which eliminates the need for the SCC to supply interrupt vectors to indicate the source of the interrupt to the CPU.

| Baud Rate                          | Clock<br>Multiplier | TC(A) | Error<br>(%) | TC(B) | Error<br>(%) |

|------------------------------------|---------------------|-------|--------------|-------|--------------|

| 19200                              | 16                  |       |              | 4     | 0            |

| 9600                               | 16                  | 11 .  | -0.16        | 10    | 0            |

| 4800                               | 16                  | 24    | -0.16        | 22    | 0            |

| 2400                               | 16                  | 50    | -0.16        | 46    | 0            |

| 1200                               | 16                  | 102   | -0.16        | 94    | 0            |

| 300                                | 16                  | 414   | -0.16        | 382   | 0            |

| 110                                | 16                  | 1134  | -0.03        | 1045  | 0            |

| 19200                              | 1                   | 102   | -0.16        | 94    | 0            |

| 9600                               | 1                   | 206   | -0.16        | 190   | 0            |

| 4800                               | 1                   | 414   | -0.16        | 382   | 0            |

| 2400                               | 1                   | 831   | -0.04        | 766   | 0            |

| 1200                               | 1                   | 1664  | -0.04        | 1534  | 0            |

| 300                                | 1                   | 6664  | -0.01        | 6142  | 0            |

| 224000 <sup>*</sup><br>*(Applebus) | 1                   | • •   |              | 6     | 0            |

Figure 2-10. Serial Port Baud Rates

### 2.5.3 Parallel Port Control

The parallel port is controlled by a 6522 versatile interface adapter (VIA). There is a direct correspondence between hardware lines on the physical connector and the assigned line within the 6522's two-byte ports. Refer to subsection 3.5.2 for a discussion of the signal lines on the interface. The

relationship between the 6522 port bits and the interface signals is shown in Figure 2-11.

| 6522 Contr | oller Line        | Parallel Port Line |                   |      |

|------------|-------------------|--------------------|-------------------|------|

| PA0-PA7    | Peripheral A port | DD0-DD7            | Data lines        |      |

| CA2        | Control Line 2 A  | PSTRB              | Processor Strobe  | 15   |

| CA1        | Control Line 1 A  | BSY                | Busy              | 16   |

| PB0        | Periph. B Port 0  | OCD                | Open Cable Detec  | t 19 |

| PB1        | Periph. B Port 1  | BSY                | Busy              | 16   |

| PB2 .      | Periph. B Port 2  | DEN                | Disk Enable       | -    |

| PB3        | Periph. B Port 3  | DRW                | Read/Write        | 3    |

| PB4        | Periph. B Port 4  | CMD                | Command           | 17   |

| PB5        | Periph. B Port 5  | DIAGPAR            | Diagnostic Parity | -    |

| CB2        | Control Line 2 B  | PARITY             | Interface Parity  | 18   |

| (PB5)      | Keyboard B Port 5 | PRES               | Parity Reset      | -    |

| (PB7)      | Keyboard B Port 7 | CRES               | Controller Reset  | 21   |

| •          | See note          | CHK                | Check             | 25   |

Notes: The last three signals are connected to the keyboard 6522.

The BSY signal connects to both the CA1 and PB1 lines.

The check line is encoded by the keyboard interface and produces an independent interrupt and key code D000<sub>2</sub> 0101<sub>2</sub>, where D is a 1 on a rising edge and a 0 on a falling edge.

Figure 2-11. Parallel Port Bit Correspondence

Note that some bits on this 6522 are used for signals other than those for the parallel port. Also note that two bits for the parallel port are controlled via the keyboard 6522. The programming of the 6522 is described in the 6522 data sheet. The addressing scheme is given in Figure 2-12.

| Address<br>(hexadecim | Register #<br>al) | Function                          |

|-----------------------|-------------------|-----------------------------------|

| 00D901                | 0                 | ORB/IRB (Input/Output Register)   |

| 00D909                | 1                 | ORA/IRA (Input/Output Register)   |

| 00D911                | 2                 | DDRB (Data Direction Register)    |

| 00D919                | 3                 | DDRA (Data Direction Register)    |

| 00D921                | 4                 | T1C-L (Low-order latch/counter)   |

| 00D929                | 5                 | T1C-H (High-order counter)        |

| 00D931                | 6                 | T1C-L (Low-order latches)         |

| 00D939                | 7                 | T1C-H (High-order latches)        |

| 00D941                | 8                 | T2C-L (Low-order latch/counter)   |

| 00D949                | 9                 | T2C-H (High-order counter)        |

| 00D951                | 10                | SR (Shift Register)               |

| 00D959                | 11 -              | ACR (Auxiliary Control Register)  |

| 00D961                | 12                | PCR (Peripheral Control Register) |

| 00D969                | 13                | IFR (Interrupt Flag Register)     |

| 00D971                | 14                | IER (Interrupt Enable Register)   |

| 00D979                | 15                | ORA/IRA (as for 1 w/o handshake)  |

Figure 2-12. Parallel Port Addressing

If CA1 is in pulse handshake mode and the DEN bit is low, the CA1 line pulses to transfer data to or from the parallel port each time that data is read from or written to the A port. CA1 is fed directly to CA2 to allow latch mode to be used on the A port while data is being read.

The  $\overline{CR}$  signal is generated by manipulation of the B port on the keyboard interface. Refer to subsection 2.5.4 for details.

# 2.5.4 Keyboard/Mouse Control

Keyboard and mouse control are performed by a dedicated slave processor, known as a control-oriented processor system (COPS). It provides communication with four peripheral devices via the A port of the keyboard 6522 VIA port controller. These devices are the:

<sup>\*</sup> Keyboard

- \* Mouse

- \* Real-time clock

- \* Software power-off.

Commands to these peripherals are written to the A port of the 6522 and data is fetched from the same location. The keyboard and mouse are addressed using the 6522 registers as shown in Figure 2-13.

| Address<br>(hexadecir | Register #<br>nal) | Function                                               |

|-----------------------|--------------------|--------------------------------------------------------|

| 00DD81                | 0                  | ORB/IRB (Input/Output Register)                        |

| 00DD83                | 1 .                | ORA/IRA (Input/Output Register)                        |

| 00DD85                | · <b>2</b>         | DDRB (Data Direction Register)                         |

| 00DD87                | 3                  | DDRA (Data Direction Register)                         |

| 00DD89                | 4                  | T1C-L (Low-order latch/counter)                        |

| 00DD8B                | 5                  | T1C-H (High-order counter)                             |

| 00DD8D                | 6                  | T1C-L (Low-order latches)                              |

| 00DD8F                | 7                  | T1C-H (High-order latches)                             |

| 00DD91                | 8                  | T2C-L (Low-order latch/counter)                        |

| 00DD93                | 9                  | T2C-H (High-order counter)                             |

| 00DD95                | 10                 | SR (Shift Register)                                    |

| 00DD97                | 11                 | ACR (Auxiliary Control Register)                       |

| 00DD99                | 12                 | PCR (Peripheral Control Register)                      |

| 00DD9B                | 13                 | IFR (Interrupt Flag Register)                          |

| 00DD9D                | 14                 | IER (Interrupt Enable Register)                        |

| 00DD9F                | 15                 | ORA/IRA (Same as in register 1, but without handshake) |

Refer to 6522 Data Sheet for details.

Figure 2-13. Keyboard/Mouse Addressing

The command format to the COPS is shown in Figure 2-14.

| Keyboard     |            |

|--------------|------------|

| 6522 PA Port | Function ` |

| 7654 3210    |            |

|              |            |

| 0000 | 0000 | Turn I/O port on                           |

|------|------|--------------------------------------------|

| 0000 | 0001 | Turn I/O port off                          |

| 0000 | 0010 | Read Clock Data                            |

| 0001 | nnnn | Write nnnn to clock                        |

| 0010 | spmm | Set Clock Modes, where:                    |

|      |      | s=enable (1) or disable (0) clock set mode |

|      |      | p=power on (1) or power off (0)            |

|      |      | mm = 00 Clock/Timer Disable                |

|      |      | 01 Timer Disable                           |

|      |      | 10 Timer Underflow Interrupt               |

|      |      | 11 Timer Underflow Power-on                |

| 0101 | nnnn | Set NMI character high nibble to nnnn      |

| 0110 | nnnn | Set NMI character low nibble to nnnn       |

| 1xxx | xxxx | No operation                               |

|      |      |                                            |

Figure 2-14. Keyboard COPS Commands

Note that, in addition to the keyboard and the mouse, several other peripherals are interfaced to the Lisa via the keyboard 6522. These are:

- \* Two parallel-port lines

- \* Three volume-control lines

- \* Speaker tone line

- \* Floppy-disk interrupt.

The COPS receives power from the backup supply. This voltage is available at all times, whether the Lisa is powered down or even unplugged. The only time the COPS ceases functioning is if the battery is allowed to run down by having the Lisa unplugged over a long period.

This means that the COPS is always operational. It keeps the time of day and provides software control of the power on and off functions.

## Keyboard

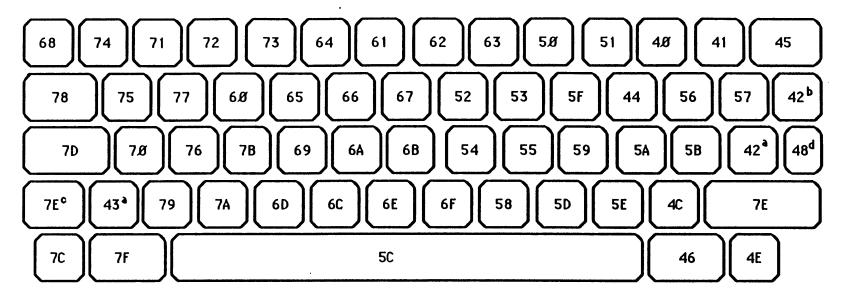

The keyboard on the Lisa is a true N-key rollover design. An arbitrary number of keys can be depressed without causing phantom key problems. The key codes returned by the interface

are in the form:

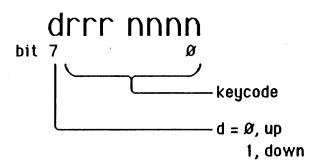

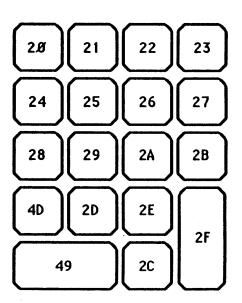

# $drrr_2 nnnn_2$

where "d" indicates direction of keystroke (down=1, up=0), and "rrr" and "nnnn" are given in Figure 2-15.

Figure 2-15. Lisa Keyboard Codes

Software must interpret such functions as shift and auto-repeat. Any key can be programmed to generate a non-maskable interrupt.

In addition to key information, a number of two-byte sequences that are known as reset codes are produced. Each sequence consists of a reset character,  $80_{16}$ , followed by a code number. The significance of the code numbers is shown in Figure 2-16.

| Reset Code<br>(hexadecimal) | Significance                                                                                                                          |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FF                          | Keyboard COPS failure detected                                                                                                        |  |  |

| FE                          | I/O board COPS failure detected                                                                                                       |  |  |

| FD                          | Keyboard unplugged. The reset code of the keyboard identification follows when the keyboard is plugged back in.                       |  |  |

| FC                          | Clock timer interrupt                                                                                                                 |  |  |

| FB                          | "Soft power off" switch has been depressed                                                                                            |  |  |

| FA )                        | •                                                                                                                                     |  |  |

| . )                         |                                                                                                                                       |  |  |

| . )                         | Reserved for future use                                                                                                               |  |  |

| . )                         |                                                                                                                                       |  |  |

| F0 )                        |                                                                                                                                       |  |  |

| Еу                          | Clock data follows. Five bytes are transferred after this. "y" is the year, coded in the reset byte. The other bytes have the format: |  |  |

|                             | (80 Ey) dd dh hm ms st                                                                                                                |  |  |

|                             | Where ddd is the day, hh the hour, mm the                                                                                             |  |  |

|            | minute, ss the second. | second, and t the tenths of |

|------------|------------------------|-----------------------------|

| DF )       |                        |                             |

| . )        | Keyboard ID nu         | mber. This code is produced |

| . )        | whenever the ke        | eyboard COPS is reset. At   |

| . )        | present, the val       | id codes are:               |

| 00 )       |                        |                             |

|            | HEX                    | LAYOUT                      |

| KEYTRONICS | APD                    |                             |

| \$AD       | \$2D                   | French                      |

| \$AE       | \$2E                   | German                      |

| \$AF       | \$2F                   | UK                          |

| \$BF       | \$2F                   | US                          |

Figure 2-16. Keyboard COPS Reset Codes

### Mouse

The mouse connects to the COPS. Mouse commands have the format:

# 0111<sub>2</sub> ennn<sub>2</sub>

If "e" is set, mouse interrupts are enabled. The "n" bits define the time interval that separate mouse interrupts. The time interval is the binary value of "nnn" times 4 milliseconds. Whenever you move the mouse, it interrupts the processor with this period.

Mouse data are transferred to the CPU in three bytes. These are polled from the keyboard 6522 A port. The significance of the bytes is as follows:

| 00 | Mouse  | data | follows   |        |    |      |

|----|--------|------|-----------|--------|----|------|

| dx | Change | in   | direction | (-127  | to | 127) |

| dy | Change | in y | direction | (-127) | to | 127) |

Each time the value is accepted by the CPU, the bytes are reset. Should the CPU not respond immediately, the data are updated to show a cumulative value. The mouse button is returned as

keycode  $d000_2$   $0110_2$ . The "d" bit defines whether the button is pressed (1) or not (0).

If the mouse is plugged in, a code of  $1000_2$   $0111_2$  is returned. If the mouse is unplugged, the code is  $0000_2$   $0111_2$ .

### Real-time Clock

The real-time clock (RTC) is capable of resolution to 1/10th of a second and need be reset only every 16 years. An alarm can be programmed via the RTC to generate an interrupt and/or turn the Lisa on after a timeout of up to FFFFF<sub>16</sub> seconds, or about 12 days.

The clock commands are coded as shown in Figure 2-14. The "p" bit in Figure 2-14 is used to power the Lisa on or off under software control. A "0" turns power off. The "s" bit enables and disables Clock Set Mode.

In Clock Set Mode, only as many nibbles as are required need be sent. Once the "s" bit is cleared, the peripheral assumes that the data was complete. The clock and timer must be stopped while the clock is being set. The clock can be left running while setting up the timer.

Time information is entered as a series of nibbles in the form:

### aaaaa y ddd hh mm ss t

The "a" nibbles are the timer delay value in seconds  $(0\text{-}\text{FFFF}_{16})$ , "y" is the year (0-15), "ddd" is the day (1-366), "hh" is the hour (0-23), "mm" is the minute (00-59), "ss" is the second (0-59), and "t" is the 1/10th of a second value (0-9).

All nibbles are maintained in binary coded decimal (BCD) format, except for the timer and year nibbles, which are binary. When reading the clock, the data are returned as a series of reset codes in the form:

# 80 Ey dd dh hm ms st

## Software On-Off

Software controls the on and off states in the Lisa. When the power switch on the lower-front cabinet is pressed during operation, a reset code is presented to the CPU. This allows software to finish operations in progress and store work files before turning off the Lisa. Note that pressing the on-off switch does not remove power from the Lisa; power can only be removed by unplugging the line cord.

### 2.5.5 Processor Board Control

The processor board has a number of control bits that are set and reset by access to a particular address in I/O space. A summary of these is shown in Figure 2-17.

| Address<br>(hexadecimal) | Function                              |

|--------------------------|---------------------------------------|

| 00E000                   | Memory Diagnostic DIAG1 Reset         |

| 00E002                   | Memory Diagnostic DIAG1 Set           |

| 00E004                   | Memory Diagnostic DIAG2 Reset         |

| 00E006                   | Memory Diagnostic DIAG2 Set           |

| 00E008                   | Context Selection SEG1 Reset          |

| 00E00A                   | Context Selection SEG1 Set            |

| 00E00C                   | Context Selection SEG2 Reset          |

| 00E00E                   | Context Selection SEG2 Set            |

| 00E010                   | SETUP Register Reset                  |

| 00E012                   | SETUP Register Set                    |

| 00E014                   | Enable Soft Memory Error Detect Reset |

| 00E016                   | Enable Soft Memory Error Detect Set   |

| 00E018                   | Enable Vertical Trace Interrupt Reset |

| 00E01A                   | Enable Vertical Trace Interrupt Set   |

| 00E01C                   | Enable Hard Memory Error Detect Reset |

| 00E01E                   | Enable Hard Memory Error Detect Set   |

| 00E800                   | Video Address Latch                   |

| 00F000                   | Memory Error Address Latch            |

| 00F800                   | Status Register                       |

Figure 2-17. Processor Board Control Addressing

Context selection is discussed in subsection 2.3.4. Memory errors are discussed in section 2.7. The status register is discussed in section 2.8.

The video address latch is used to point to the physical address of the 32 Kbyte video page in main memory. The memory error address latch saves the accessed address when a memory error occurs. This may then be interrogated by software for statistical analysis of memory errors.

#### 2.6 INTERRUPT HANDLING

Upon detection of an interrupt, the CPU enters supervisor mode automatically. It then uses a table in memory, known as the Exception Vector Table, to point to the location at which the routine to handle the interrupt can be found. The priority level of the source of the interrupt can be used as an index into the table, or the interrupt level itself can be used directly as the exception vector.

The fixed priority interrupts are:

| Level | Туре                                         |

|-------|----------------------------------------------|

| 7     | Non-maskable interrupt (highest)             |

| 6     | Serial I/O ports                             |

| 5     | Expansion slot #1                            |

| 4     | Expansion slot #2                            |

| 3     | Expansion slot #3                            |

| 2     | Keyboard/Mouse/Real-time Clock/on-off switch |

| 1     | All others (lowest)                          |

Figure 2-18 shows the Exception Vector Table assignment for the Lisa. All addresses are logical addresses. This means that their physical location is a function of the MMU setup.

Exception

Vector Address

# (hexadecimal)

| Reset: Initial SSP                   | 000000               |

|--------------------------------------|----------------------|

| Reset: Initial PC                    | 000004               |

| Bus Error                            | 800000               |

| Address Error                        | 00000C               |

| Illegal Instruction                  | 000010               |

| Zero Divide                          | 000014               |

| CHK Instruction                      | 000018               |

| TRAP Instruction                     | 00001C               |

| Privilege Violation                  | 000020               |

| Trace                                | 000024               |

| Unimplemented Instruction 1010       | 000028               |

| Unimplemented Instruction 1111       | 00002C               |

| Reserved, unassigned                 | 000030 - 00005F      |

| Spurious Interrupt                   | 000060               |

| Other Internal Interrupt             | 000064               |

| Keyboard Interrupt                   | 000068               |

| Slot 2 Autovector                    | 00006C               |

| Slot 1 Autovector                    | 000070               |

| Slot 0 Autovector                    | 000074               |

| [For consistency shouldn't the above | be Slot 3,2,1? - gk] |

| RS232 Interrupt                      | 000078               |

| Non-maskable Interrupt               | 00007C               |

| TRAP Instruction Vectors             | 000080 - 0000BF      |

| Reserved, unassigned                 | 0000C0 - 0000FF      |

| User Interrupt Vectors               | 000100 - 0003FF      |

Figure 2-18. Exception Vector Table

A non-maskable interrupt can come from one of four sources:

- \* Power Failure

- \* Hard memory error

- \* Soft memory error

- \* Keyboard reset.

Level-1 Interrupts can be generated by one of three sources:

- \* Hard disk interface, the parallel port,

- \* Floppy-disk controller

- \* Video circuit controller.

The power reset vector is not shown here because it is located in ROM, which is not accessed except in special I/O space during powerup processing.

### 2.7 ERROR PROCESSING

The Lisa operates with a flexible system of handshaking on the bus. When a device is addressed, the CPU will wait 30-300 microseconds for some response from the addressed device before timing out. Upon timeout, a bus error is produced.

The Lisa can experience two kinds of memory errors: hard or soft. A hard memory error is the result of a parity error during memory access on a parity memory board or an uncorrectable error on an Error Correction Code (ECC) memory board. [Was there ever an ECC board by Apple or a third-party? - gk]

A soft memory error is the result of detection of a correctable error on an ECC memory board. In either case, the appropriate status bit is set, see section 2.8, and a non-maskable interrupt is generated to the CPU. A latch contains the address at which the error was detected. The MMU can be used to map out bad pages in memory, should this become necessary.

The address of the word that caused the error can be read from the Memory Error Address Latch at 00F000<sub>16</sub> in I/O space. Detection of either a hard or soft memory error can be disabled, as described in Figure 2-17.

|    |    |    |    |    |    | ٨ | /lem | ory | er | ror | add | dres | s la | atch |   |   |  |

|----|----|----|----|----|----|---|------|-----|----|-----|-----|------|------|------|---|---|--|

| 15 |    |    |    |    | 1  | 0 | 9    | )   |    |     |     |      |      |      |   | 0 |  |

|    |    |    |    |    |    |   |      |     |    |     |     |      |      |      |   |   |  |

| 20 | 19 | 18 | 17 | 16 | 15 |   | 14   | 13  | 12 | 11  | 10  | 9    | 8    | 7    | 6 | V |  |

bit 0: 0- error on CPU access D1-D15 contain A6-A20 of failing address

1 - error on Video access D10-D15 contain A15-A20 of failing address. D1 - D9 invalid.

#### 2.8 STATUS REGISTER

The status register is located at 00F800<sub>16</sub> in I/O space and is a read-only 16-bit register. A bus error exception routine can use the status register to determine the cause of bus errors. A breakdown of the significance of the bits in the status register is shown in Figure 2-19.

| Bit  | Name                     | Significance                                                                                                                                                                                                                                            |

|------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Soft Error<br>Hard Error | A soft memory error has occurred.  A hard memory error has occurred.                                                                                                                                                                                    |

| 2    | Vertical Retrace         | The video circuit has begun a vertical retrace and an interrupt has been generated. The video circuit continues to set this bit for 90 microseconds after the start of the retrace. Enable Vertical Retrace Interrupt can be reset to inhibit this bit. |

| 3    | Bus Timeout              | A timer attached to Address Strobe $(\overline{AS})$ waits for 30-300 microseconds before generating a Bus Error condition.                                                                                                                             |

| 4    | Video Bit                | Available to the CPU for diagnostic purposes, this bit corresponds to the output of the video circuit.                                                                                                                                                  |

| 5    | Horiz. Sync              | Reflects the state of the horizontal sync signal. It is available to the CPU for diagnostic purposes.                                                                                                                                                   |

| 6    | Video Mode               | Reserved for future use.                                                                                                                                                                                                                                |

| 7-15 |                          | Not used.                                                                                                                                                                                                                                               |

Figure 2-19. Status Register

•

#### CHAPTER 3. INTERNAL SPECIFICATIONS

This chapter describes specifications for the Lisa and the manner in which it interfaces with the outside world.

#### 3.1 PACKAGING

The configuration of hardware modules within the cabinet was discussed briefly in Chapter 1. The following parts are removable for inspection or replacement:

- \* Front panel

- \* Floppy-disk drives

- \* Back panel

- \* Power supply

- \* Motherboard

- \* CPU board

- \* I/O board

- \* Memory boards

- \* Keyboard

- \* Mouse

- \* Expansion boards.

Disassembly procedures for user-serviceable parts are described in the Lisa Owner's Guide. Access to other subassemblies is described in Chapter 11.

The top front of the cabinet is taken up by the CRT and the two floppy-disk drives. You can access these devices by removing the front panel of the cabinet. The drives are held in place by a finger-nut below the lower drive, and both drives are slid out once this is undone. Care must be taken not to snag or overextend the drive cables before they are disconnected from the drives.

Removing the back panel from the cabinet gives you access to the power supply and the motherboard assembly. The motherboard carries all the logic boards and conceptually consists of two parts. The first part carries the main logic boards, including the processor board, the I/O board, and either one or two memory boards, parallel to the back of the cabinet. Not all the boards are immediately visible when the back panel is removed, because they are arranged one behind the other.

The second part carries the boards at right angles to the back of the cabinet, and is known as the expansion bus section. This is where additional boards, such as interface or controller boards, are inserted. The entire motherboard slides out from the cabinet by gently pulling to the rear, which disengages the two edge connectors through which the motherboard connects into the cabinet.

However, it is not necessary to remove the entire card cage to remove one of the boards from the expansion slots. These are held in place by special card-edge connectors that allow the boards to slide out towards the back of the cabinet.

The power supply is the rectangular enclosure occupying the right side of the cabinet; it can be removed separately. To do this, unfasten the finger-nut beneath the cabinet. Then, slide the entire power supply backwards out of the cabinet.

Electrical connections between modules and the rest of the Lisa are made by means of tongue and socket connectors. These connections are made automatically when the boards are inserted and push home.

Only the disk drives require that their connecting cable be carefully disconnected before the drive can be fully removed from the cabinet. Figure 3-1 shows an exploded view of modules inside the cabinet.

### Figure 3-1. Modules in Cabinet

No module should be removed from the cabinet while the Lisa is turned on. Interlock switches on both the front and back panels turn the Lisa off when either panel is removed. However, the line plug should be unplugged before the Lisa is serviced.

|   | · |  |  |  |  |

|---|---|--|--|--|--|

|   |   |  |  |  |  |

| i |   |  |  |  |  |

| · |   |  |  |  |  |

Following dimensions apply to the Lisa only.

Main Assembly Dimensions: 13.9" (354 mm) High

18.6" (474 mm) Wide 15.6" (396 mm) Deep

Keyboard dimensions: 3.1" (79 mm) High

18.8" (479 mm) Wide 6.5" (166 mm) Deep

Mouse operating space: 2.1" by 6.3" (55 mm by 160 mm)

Keyboard cable extension: 4 ft. (1.2 m) maximum

Main assembly weight: 44.8 lbs (20.4 kg)

[the above is for a Lisa 1. - gk]

Keyboard weight: 4.13 lbs. (1.88 kg)

Power cord length: 7.5 ft. (2.26 m)

The Lisa should be used with an acceptable operating space around it. Under no circumstances should the air flow through the cabinet vents, particularly those on the bottom, be restricted.

The mouse operating space should be approximately 6 inches on from either side of the keyboard. When you move the mouse around a 6 inch area on any flat surface, you can reach any point on the CRT with the cursor.

#### 3.2.3 Electrical

AC power requirements 150 VA @ 115 VAC

(single phase)

Acceptable input voltages 90 to 130 VAC

Input AC frequency 60 +/- 2Hz

Maximum power dissipation 150 watts @ 70 Deg.F

[For Lisa 1. - gk]

Voltages available on bus +5V, -5V, +12V, -12V,

+5V VSTBY DC

The currents available on these voltages is a function of the Lisa configuration. Refer to subsection 3.3.2 for the total power capacity of the power supply.

#### 3.3 MODULES

Each module can be easily dismounted from the cabinet for test or replacement. In addition, the keyboard and mouse detach for easy inspection or replacement. The Lisa consists of the following assemblies: