Date: March 15, 1983

To:

Wavne Rosina Bruce Daniels

Ken Okin Wendell Henry Rick Meyers

Jon Fitch Paul Baker Rich Page

∨Mike Urguhart Art Benjamin Ann Nunziata

Ron Hochsprung Wolfgang Dirks 200

From: Gary Marten

Subj: v1.75

Here is what is hopefully close to the final definition of 1.75. As you recall, 1.75 is the current Lisa with a new logic cage assembly and a new disk drive assembly.

#### System Configuration

10 MHz 68010 processor

720 x 364 video display

10 MB built-in hard disk Built in floppy disk

MMU with 512 byte pages

896 Kbytes RAM

128/256 Kbytes ROM Dual serial ports

Onhat about substitutes in state for 6522 timers? Uno 6522 These are used extensively.

(2) A 10ps/6522 By Keyboard mouse?

Then O which functions (on the 16 board)

are different? Keyboard/mouse

Parallel port (1f needed) of course, or expected to use expansion state? You

### The MMU and Memory Address Space

The 512 byte page size will remain. This makes the use of 256K RAMS a little more difficult, but doable. To compensate for the 2 megabyte limitation of the 512 byte page scheme, another 2 megabyte address space has been added, for a total of 4 megabytes of address space. The standard memory cycle time will be 500ns, including time through the MMU.

#### Parity Errors

It was earlier thought that Motorola had corrected the problem that inhibits us from generating bus errors due to memory parity errors. This is not the case however. Therefore the current scheme of generating an NMI on a parity error will have to remain.

#### Disk Drives

The design of 1.75 has relied on controlling the floppy disk with the 68000. This does not appear to be a problem.

The hard disk will probably also be controlled directly by the 68000, this elminates the problems of missing interleves due to excessive recopying of data at slow rates.

#### Revieu

There will be a review of 1.75 on Tuesday, March 22nd at 3:30 in The Big Apple. Those interested are welcome.

# 1.75 Memory Configurations

With 2-2 Megabyte mapped address spaces with 512 byte resolution

## 3/4 Megabyte memory board

|                   | . 0  | On Board RAM                            |

|-------------------|------|-----------------------------------------|

| First 2 Megabyte  | 3/41 | 3/4 MB                                  |

| address space     |      | 1////////////////////////////////////// |

|                   | 271  | V <i>I.[.].[.].[.]</i>                  |

|                   | 0    |                                         |

| Second 2 Megabyte |      | Slot 4 - 1 MB                           |

| address space     | 14   |                                         |

| enimess share     |      | Slot 5 - 1 MB                           |

|                   | 271  |                                         |

## 1 1/2 Megabyte memory board

| First 2 Megabyte                | 0       | On Board RAM  |

|---------------------------------|---------|---------------|

| address space                   | 1 1/2H. | 1 1/2 MB      |

| Second 2 Megabyte address space | 0<br>1H | Slot 4 - 1 MB |

|                                 | 2H      | Slot 5 - 1 MB |

## 3 Megabyte memory board

| First 2 Megabyte address space | 0   | On Board RAM                  |

|--------------------------------|-----|-------------------------------|

| 4                              | 211 | 3 MB                          |

|                                | 0   |                               |

| Second 2 Megabyte              |     |                               |

| address space                  | 111 | Slot 485 - 1 MB               |

|                                | 211 | (Slot selected by status bit) |

## 1.75 Memory Allocation

| ual Address Space   |     | Hain Hemory    | •   | "Special" Address Space |

|---------------------|-----|----------------|-----|-------------------------|

| ent 0,32,64,96      |     |                |     | 32K ROH                 |

| egment 1,33,65,97   | ·   |                |     | 32K ROH                 |

| gment 2,34,66,98    |     | •              |     | 32K ROM                 |

| gment 3,35,67,99    | .   | •              |     | 32K ROM                 |

| gment 4,36,68,100   |     |                | ·x° | 32K ROM                 |

| gment 5,37,69,101   | }   | -              |     | 32K RO1                 |

| gment 6,38,70,102   |     |                |     | / 32K RON               |

| gment 7,39,71,103   | -[  |                |     | 32K ROH                 |

| ment 8,40,72,104    |     |                | 4.  | , a                     |

| gment 9,41,73,105   |     |                |     | Future Expansion        |

| ment 10,42,74,106   |     |                |     | Do not use              |

| grient 11,43,75,107 |     | Any            |     |                         |

| gment 12,44,76,108  |     |                |     | Internal I/O            |

| gment 13,45,77,109  | 1   | •              |     | Slot 1                  |

| ment 14,46,78,110   |     | and the second |     | Slot 2                  |

| ment 15,47,79,111   |     |                |     | Slot 3                  |

| ment 16,48,80,112   | _   | Mapped         | or  |                         |

| ent 17,49,81,113    | -   | 1-1appeu       | O1  |                         |

| ment 18,50,82,114   | 1   |                | , 1 |                         |

| ment 19,51,83,115   | . [ | •              |     |                         |

| ent 20,52,84,116    | Ì   | •              |     |                         |

| ment 21,53,85,117   | . 1 | Mamoru         |     |                         |

| ment 22,54,86,118   |     | Memory         |     | Future Expansion        |

| ment 23,55,87,119   |     |                |     | LACATA CYNGISTON        |

| ent 24,56,88,120    |     |                |     |                         |

| tent 25,57,89,121   |     |                |     | Do not use              |

| ent 26,58,90,122    | 1   |                |     |                         |

|                     |     |                |     |                         |

| ent 27,59,91,123    |     |                |     | *                       |

| ment 28,60,92,124   |     |                |     |                         |

| ent 29,61,93,125    | l   |                |     | 114.4 14 4-             |

| ment 30,62,94,126   |     | te e           | ·   | Video Henory            |

| pment 31,63,95,127  | ı   |                | 1   | Future Expansion        |

In "Set-up" mode (MMU Registers are accessed by a program in the "special" address space):

## For MMU register access:

| 1   |         |   |     |     | - |     |       |        | <del></del> | <del></del> |

|-----|---------|---|-----|-----|---|-----|-------|--------|-------------|-------------|

|     | Coomont | 4 | 8.  | ,   |   | 100 | k lat | I look |             | į.          |

| - } | Segment | 1 | 101 | 1 . |   |     | Not   | Used   |             |             |

|     |         |   |     |     |   |     |       |        |             | <del></del> |

|     |         |   |     |     |   |     |       |        |             |             |

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

### For ROM/Video RAM access:

| - 1 |    |         |      | _ |                 |

|-----|----|---------|------|---|-----------------|

|     | хх | Special | Addr | 0 | Special Address |

|     |    |         |      |   |                 |

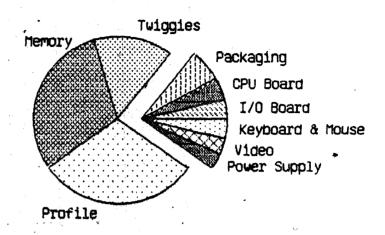

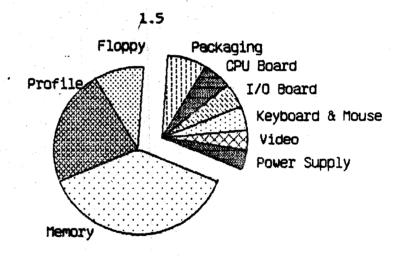

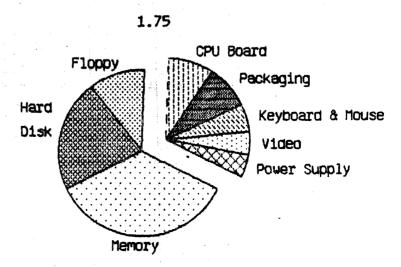

## Cost Breakdown

Lisa.

One interesting way

of looking at the

cost breakdown is

to look at each

system component

as part of the total

system cost.

The components can

then be broken into

two major classifications,

program/data storage,

and "stuff" to manipulate

that propram and data.

In defining 1.75 it is important to note that the major area that is being changed (CPU & . I/O) is a relatively small portion of the total system cost. In fact, the major cost saving over 1.5 comes from reducing total RAM by 128K and eliminating the cost of two (bare) PC boards by moving the floppy controller to the 68000 and moving memory onto the old CPU board.