TO: DISTRIBUTION

FROM: P. MICHIENZI

DATE: JANUARY 23, 1986

SUBJ: SPECIFICATION FOR 1/4" TAPE DRIVE CONTROLLER

Attached is a preliminary 1/4" tape drive controller specification. Please review and return any comments to me by February 6, 1986.

Thanks,

Pete

DISTRIBUTION: Fred Hayes

Phil Goldman Ric Plummer Jenny Ryan John Cameron Jim Stair

Phil Schreibman

Bob Angelini

Lary Gravett

Kim Cabot

Mike Feldstein

Don Carson

Bob Houde

| 1 / | AND SE | HALL NO | T BE RI | EPRODUCED          | OR CO | PIED OR U | JSED IN | PERTY OF APOLLO COMPUT<br>WHOLE OR PART AS THE BA<br>EN PERMISSION. | ER INC.<br>ASIS FOR |

|-----|--------|---------|---------|--------------------|-------|-----------|---------|---------------------------------------------------------------------|---------------------|

|     |        |         |         |                    |       |           |         |                                                                     |                     |

| -   |        |         |         |                    |       |           |         |                                                                     |                     |

|     | -      |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     |        |         |         |                    |       |           |         |                                                                     |                     |

|     | - 1    |         |         |                    |       |           |         |                                                                     |                     |

|     | RE     | VISIONS | T T     | DRAW               |       |           | APO     | OLLO COMPUTER INC.                                                  |                     |

| REV | ECO    | APP.BY  | DATE    | P. MICHII<br>CHECK |       |           |         | TITLE                                                               |                     |

|     |        |         |         | J. RYA<br>ENGINE   |       |           | CONTROL | LER - QIC-36, 1/4" TAPE                                             |                     |

|     |        |         |         | P. MICHI           |       |           |         |                                                                     |                     |

|     |        |         |         | FIRST USI          | ED ON | SIZE      | CODE    | DRAWING NUMBER                                                      | REV.                |

|     |        |         |         |                    |       | A         |         | 008845                                                              | E0                  |

SHEET 1 OF 44

#### TABLE OF CONTENTS

#### 1.0 INTRODUCTION

#### 2.0 REFERENCE DOCUMENTS

- 2.1 Industry Standards and Vendor Documents

- 2.2 Apollo Documents

## 3.0 ENVIRONMENTAL SPECIFICATIONS

- 3.1 Operational Environment

- 3.2 Non-Operating Environment

- 3.3 Packaging

- 3.3.1 Electrostatic Protection

- 3.3.2 Physical Stability

- 3.3.3 Mechanical Shock

#### 4.0 POWER SPECIFICATIONS

## 5.0 MECHANICAL SPECIFICATIONS

- 5.1 Dimensions

- 5.2 I/O Bus Slot Location

- 5.3 Controller Jumper Configurations

## 6.0 FUNCTIONAL SPECIFICATIONS

- 6.1 General

- 6.2 Command Set

- 6.3 Performance

- 6.4 Diagnostics/Led's

## 7.0 HOST INTERFACE SPECIFICATIONS

- 7.1 Host Interface Signal Level

- 7.2 Signal Loading

- 7.3 I/O Connector

- 7.4 I/O Pin Assignments

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

#### 8.0 TAPE DRIVE INTERFACE SPECIFICATIONS

- 8.1 General

- 8.2 Interface Signal Levels

- 8.3 Signal Loading

- 8.4 Signal Terminations

- 8.5 Pin Assignments

## 9.0 AGENCY COMPLIANCE

- 9.1 Safety

- 9.2 Emissions

## 10.0 RELIABILITY AND LIFE

- 10.1 MTBF

- 10.2 Life

- 10.3 Error Rates

#### 11.0 THEORY OF OPERATION

- 11.1 Block Diagram Descriptions

- 11.2 I/O Signal Descriptions

- 11.3 I/O Port Assignments (Base Address)

- 11.4 Control/Status Register Descriptions

- 11.5 DMA Channel

- 11.6 Interrupt Priority Level

- 11.7 Resets

#### 12.0 PROGRAMMING INFORMATION

- 12.1 Command Set Descriptions

- 12.2 Command Flow Charts

- 12.3 QIC-02 Command Maximum Timings

## 13.0 SYSTEMS SOFTWARE INFORMATION

- 13.1 Diagnostic Level Test

- 13.2 Operating Systems Software (AEGIS)

## APPENDIX A COMMAND FLOW CHARTS

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

#### 1.0 INTRODUCTION

< 1

This document specifies the functional, electrical, physical, reliability and certification requirements for a 1/4" tape controller which interfaces a QIC-36, 1/4" cartridge tape drive (basic interface) to an IBM PC -XT/AT, QIC-02 I/O structured compatible system. The tape controller will be used in Apollo's Domain Series DN3000 System.

The Apollo part number for the DN3000 1/4" Tape controller is 008845-001.

This document is both a purchase specification which the vendor must adhere to and a product or functional specification used as a reference for systems integrators and programming engineers. Sections 11.0 through 13.0 of this document designate the theory of operation, programming and systems software information which are to be used for reference and general knowledge only.

#### 2.0 REFERENCE DOCUMENTS

- 2.1 Industry Standards and Vendor Documents

- 2.1.1 "1/4 Inch Cartridge Tape Drive Basic Interface Quarter -Inch Compatibility Committee, QIC-36 revision C, 9/14/84.

- 2.1.2 "Proposed Standard for Data Interchange on the Streaming 1/4" Magnetic Tape Cartridge using Group Code Recording at 10,000 FRCI". QIC-24, Revision D, April 22, 1983.

- 2.1.3 Specification Archive Corp. SC-499 Tape controller information guide. (Preliminary)

- 2.1.4 "Specification 1/4" Cartridge Tape Drive Interface Standard," QIC-02, Rev. D, Sept. 23, 1982.

- 2.1.5 Theory of Operation Intelligent 1/4" Tape Drive, Archive Corp. #20100-001, Rev. C, August 16, 1982.

### 2.2 Apollo Documents

- 2.2.1 Specification 1/4" Cartridge Tape Drive with QIC-36 (basic) Interface APN 008850.

- 2.2.2 Specification Apollo DN3000 System I/O Bus. (Preliminary) Sept. 13, 1985.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

#### 3.0 **ENVIRONMENTAL SPECIFICATIONS**

#### Operational Environment 3.1

The 1/4" Tape controller shall be capable of operating under any combination of the following conditions without failure to meet all of the requirements of this document.

Ambient Temperature:

5 Degrees C. to 60 Degrees C. (41 Degrees F. to 140 Degrees F.)

Relative Humidity:

0% to 99% (Non-Condensing)

Wet Bulb Temperature:

26 Degrees C. Maximum (78.8 Degrees F. Max.)

Temperature Gradient:

1 Degree C. Per minute maximum (33.8 Degree F. per minute Max.)

20 Degrees C. per hour Max. without condensation (68 Degrees F. per hour Max.)

Altitude:

-1000 to 15,000 feet above sea level

Vibration:

0 - 63 Hz, 0.0005 inches max. Peak to Peak displacement.

(Apollo DN3000 system mounting configuration)

63 - 500Hz, 1.0G Peak Maximum

Acceleration.

Shock:

2.5G Peak Max. (1/2 Sine Wave, 11 msec duration on any axis)

(Apollo DN3000 system mounting configuration)

> SIZE CODE DRAWING NUMBER REV. Α 008845 E0

#### 3.2 Non-Operating (Unpackaged) Environment

The 1/4" Tape controller shall be capable of withstanding any combination of the following conditions in a powered off state without damage or degradation of life expectancy.

Ambient Temperature:

-30 Degrees C. to 60 Degrees C) (-22 Degrees F to 140 Degrees F)

Relative Humidity:

0% to 99% (Non-Condensing)

Wet Bulb Temperature:

26 Degrees C. Maximum

(78.8 Degrees F. Max.)

Temperature Gradient:

30 Degrees C. Per hour max. without condensation (86 Degrees F. Per hour max.)

Altitude:

-1000 to 15,000 feet above sea level

1 hour min. exposure unpackaged.

Vibration:

0 - 17 Hz. 0.1 inches max.

(Apollo DN3000 system

Peak to Peak displacement.

17 - 500 Hz, 1.5G Peak Max. mounting configuration)

Acceleration

Shock:

(Apollo DN3000 system

mounting configuration)

2.5G Peak Max. (1/2 Sine Wave, 11 msec duration on any axis)

> SIZE CODE DRAWING NUMBER REV. Α 008845 E0

#### 3.3 PACKAGING

#### 3.3.1 Electro-Static Protection (ESP)

The controller shall be packaged in anti-static material to prevent damage from electrostatic discharge.

#### 3.3.2 Physical Stability

If the packaged controllers are shipped in a stacked configuration, the stack must be stable so as to permit safe transportation or movement of the packaged controllers by sliding in the intended direction of travel. The controllers in their shipping packages, will not be subject to tipping over when placed with any of the four base edges downward on a surface inclined at a 20 Degree angle. This applies to controllers packaged on a skid or pallet.

#### 3.3.3 Mechanical Shock

The 1/4" Tape controller packaged as shipped in its cushioned shipping container must be able to resist damage resulting from random shock or impact for non-operating conditions.

This packaged controller shall be designed to withstand impacts resulting from flat drop free fall onto a concrete or equivalent floor as follows:

## FREE FALL FLAT DROP TESTS

| TOTAL PACKAGE WEIGHT               | DROP HEIGHT |

|------------------------------------|-------------|

| 20 lbs or less (single controller) | 36 inches   |

| 21 lbs to 40 lbs                   | 30 inches   |

| 41 lbs to 80 lbs **                | 24 inches   |

Each of the six package surfaces must withstand a minimum of one such impact, and the surface judged most vulnerable to shock input will experience three (3) impacts.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

### 4.0 POWER SPECIFICATIONS

The voltages and currents required to operate the controller board, along with the applicable pin numbers of the J1 I/O connector are shown in Table 1.0.

| J1 I/O<br>PIN NUMBER | VOLTAGE                       | CURRENT                        | MAXIMUM<br>RIPPLE                        |

|----------------------|-------------------------------|--------------------------------|------------------------------------------|

| B03, B29             | +5VDC +/-5% including ripple  | 1.0A Typical<br>1.25A Maximum  | 100 mv                                   |

| B01, B10, B31        | +5VDC/+12VDC<br>Return        |                                |                                          |

| В09                  | +12VDC +/-5% including ripple | .065A Typical<br>.125A Maximum | 500 mv to 10 KHz<br>200 mv beyond 10 KHz |

Table 1.0

#### 5.0 MECHANICAL SPECIFICATIONS

### 5.1 Dimensions

Width:

13.5 in (34.29CM)

Height:

4.2 in (10.67CM)

Weight:

0.6 lbs

#### 5.2 I/O Bus Slot Location

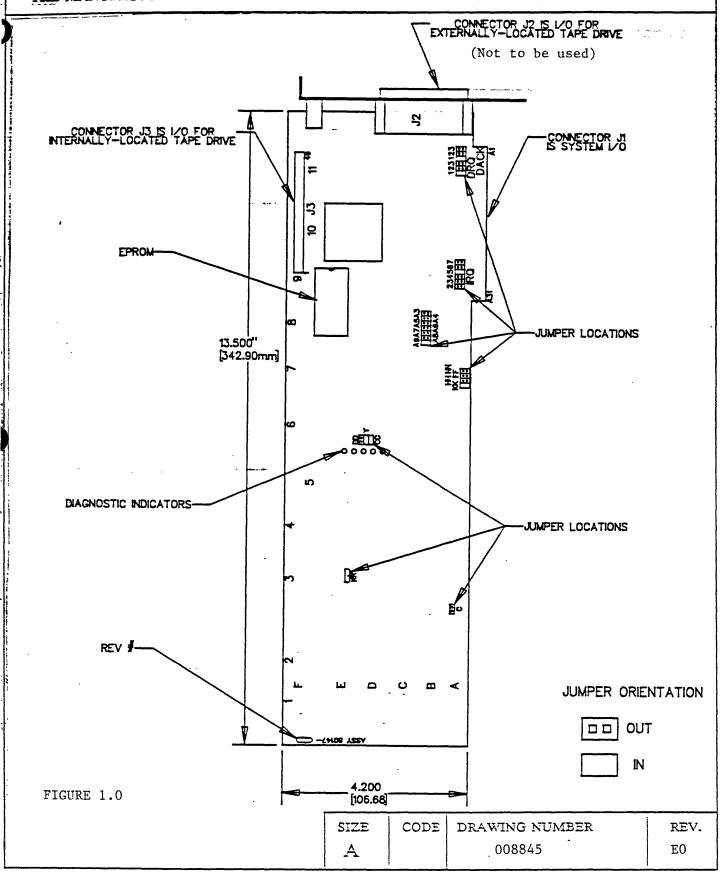

The 1/4" Tape controller, consisting of a single printed circuit board, plugs directly into any I/O expansion slot of an Apollo DN3000 system. See Figure 1.0 for Controller I/O connector J1 location.

## 5.3 Controller Jumper Configurations

To avoid bus contention between the 1/4" tape controller and any other controller utilizing the I/O backplane in the DN3000 system. The tape controller must be configured as follows:

5.3.1 Device Address (Base Address)

-0200 (HEX)

5.3.2 DMA Channel

- 1

5.3.3 Interrupt Request Level

- 5

Table 2.0 describes all jumper options and their functions along with the Apollo configurations designated by an asterik (\*) and the configuration received from the vendor designated by a dot ( $\bullet$ ).

See Figure 1.0 for jumper locations.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

TABLE 2.0 CONTROLLER JUMPER CONFIGURATION

| DESCRIPTION                                              | JUMPER LOCATION                              | OPTION                                                                                                                                          |

|----------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| TAPE FORMAT                                              | сс                                           | IN = QIC-24 * ●<br>OUT = QIC-11                                                                                                                 |

| TAPE SPEED                                               | DD                                           | OUT (90IPS)* ● FOR VENDOR USE ONLY                                                                                                              |

| NUMBER OF TRACKS                                         | Y                                            | IN = 9 TRACKS * ● OUT = 4 TRACKS                                                                                                                |

| POWER-ON CONFIDENCE<br>TEST                              | KK                                           | IN = TEST AT POWER-ON* ● OR RESET                                                                                                               |

| I/O REGISTER BASE<br>ADDRESS                             | A3 THRU A9 A3 THRU A8 = OUT* • A9 = IN* •    | OUT = TEST DISABLED  IN = ADDRESS BIT TRUE  OUT = ADDRESS BIT FALSE  NOTE: BASE ADDRESS IS  SELECTABLE FROM 0 TO 3F8  HEX ON 8-BYTE BOUNDARIES. |

| DMA PRIORITY LEVEL<br>(SELECT ONE PAIR)                  | DRQ1, DACK1<br>DRQ2, DACK2<br>DRQ3, DACK3    | BOTH IN = PRIORITY LEVEL 1* • BOTH IN = PRIORITY LEVEL 2 BOTH IN = PRIORITY LEVEL 3                                                             |

| INTERRUPT PRIORITY                                       | IRQ2<br>IRQ3<br>IRQ4<br>IRQ5<br>IRQ6<br>IRQ7 | IN = PRIORITY LEVEL 2 • IN = PRIORITY LEVEL 3 IN = PRIORITY LEVEL 4 IN = PRIORITY LEVEL 5* IN = PRIORITY LEVEL 6 IN = PRIORITY LEVEL 7          |

| LOOP ON ERROR<br>MAINTENANCE                             | FF<br>C                                      | OUT* • (FOR VENDOR USE ONLY) OUT* • (FOR VENDOR USE ONLY)                                                                                       |

| TEST CONFIGURATION NO DESCRIPTION READY INTERRUPT DISABL | HH<br>NN<br>E RR<br>RR                       | OUT* • (FOR VENDOR USE ONLY) OUT • (FOR VENDOR USE ONLY) OUT • (PARTIE A MARKED - WAT ON INT.                                                   |

<sup>•</sup> As-Shipped Configuration from vendor

\* Apollo Configuration

REMOTENA - WHEN DONE INT

DIJABLAD

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

#### 6.0 FUNCTIONAL SPECIFICATIONS

#### 6.1 General

. 1

- 6.1.1 The appropriate manufacturer's specifications contain information which must be used in conjunction with the specifications covered in this document. In case of conflict, Apollo specifications shall be in force.

- 6.1.2 The 1/4" Tape controller shall meet all of the requirements of this document while utilizing 1/4" tape drives which comply with the specifications for Apollo part number 008850, and will electrically interface to a QIC-02 command set compatible Apollo DN3000 system I/O bus.

#### 6.2 Command Set

The controller shall utilize the QIC-02 standard command set as follows:

| Select, Soft Lock Off | H'01' |

|-----------------------|-------|

| Select, Soft Lock On  | H'11' |

| BOT                   | H'21' |

| Erase                 | H'22' |

| Retension             | H'24' |

| Select Q11 Format     | H'26' |

| Select Q24 Format     | H'27' |

| Write                 | H'40' |

| Write File Mark (WFM) | H'60  |

| Read                  | H'80' |

| Read File Mark (RFM)  | H'A0' |

| Read Status           | H'C0' |

### 6.3 Performance

Tape drives controlled Transfer rate Recording tracks Recording Code Data Buffering

Write/Read re-tries Error detection 90KB/sec

9 track serpentine

(0,2) Run length limited, GCR 3 x 512 Byte blocks minimum

16 maximum CRC (standard)

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

## 6.4 Diagnostics/Led's

## 6.4.1 Power-On Confidence test (POC)

The controller level diagnostics are located physically on the board in PROM. They are activated when power is applied or when a reset command is issued from the host.

A POC test or controller initialization occurs automatically when power is applied or when a reset command is issued. This test includes sub-tests of the following:

- \*Microprocessor Internal Ram and Basic Instructions

- \*LSI controller operation

- \*16K Ram Ic

- \*Data Separator Logic (discrete)

Successful completion of the above tests are reported to the host by the assertion of EXC-(from status register) within five secs. If EXC-is not asserted within this time a failure is indicated.

Each logic group except the microprocessor has an associated Led diagnostic indicator as follows:

- \*DS1-LS1 Controller chip

- \*DS2-16K Ram bufffer logic

- \*DS3-Data Separator logic

- \*DS4,DS5 Not Used

Successful completion of all tests is indicated by a single blink of all five Led's following the off period during which the tests are performed. Each time a test fails the associated Led blinks and the test is repeated; hence, a blinking indicator is a visual indication of the area of failure. If the microprocessor fails the results are unpredictable.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

#### 7.0 HOST INTERFACE SPECIFICATIONS

. 2

The 1/4" tape controller will be electrically and mechanically compatible with the IBM PC XT/AT I/O structured DN3000 system, use DMA for data transfer and respond to the standard QIC-02 command set.

In general the controller will meet all of the requirements of the specifications referenced in Sections -2.1.4 and 2.1.5 of this document.

## 7.1 Host Interface Signal Level

All signals to the host are standard tri-state TTL levels as follows:

False = High = 2.4 to 5.25 VDC

True = Low = 0 to 0.8 VDC

Off = High Impedance State

Voltages shall be measured at the controller connector - J1

#### 7.2 Signal Loading

Signal from the host to the controller are loaded by not more than 2.0MA. Command, address, DMA and Interrupt request lines drive into not more than PAL1628A or equivalent inputs. The data lines drive into a single low power schottky (LS) input.

#### 7.3 I/O Connector

The controller interfaces to the DN3000 system via card edge connector J1. The connector has 62-pins and mates to the 62-pins host system I/O bus connector with 100-MIL card tab spacing.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

## 7.4 I/O Pin Assignments

٠.,

Table 3.0 summarizes Pin Assignments for the I/O bus connector - J1.

TABLE 3.0 - I/O CONNECTOR J1 SIGNAL DESCRIPTIONS

| PIN                                                                                                                                                                                                | NAME                                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A02<br>A03<br>A04<br>A05<br>A06<br>A07<br>A08<br>A09<br>A11<br>A12 THRU A31<br>B02<br>B18<br>B06<br>B16<br>B17<br>B26<br>B15<br>B13<br>B14<br>B04<br>B25<br>B24<br>B23<br>B22<br>B21<br>B27<br>B30 | DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 AEN A19 THRU A00 RESET DRV DRQ1 DRQ2 DRQ3 //DACK1 //DACK2 //DACK3 //IOW //IOR IRQ2 IRQ3 IRQ4 IRQ5 IRQ6 IRQ7 T//C OSC | DATA BUS BIT 7 DATA BUS BIT 6 DATA BUS BIT 5 DATA BUS BIT 4 DATA BUS BIT 3 DATA BUS BIT 2 DATA BUS BIT 1 DATA BUS BIT 1 DATA BUS BIT 0 ADDRESS ENABLE SYSTEM ADDRESS BUS RESET DRIVE DMA REQUEST PRIORITY LEVEL 1 DMA REQUEST PRIORITY LEVEL 2 DMA REQUEST PRIORITY LEVEL 3 DMA ACKNOWLEDGE PRIORITY LEVEL 1 DMA ACKNOWLEDGE PRIORITY LEVEL 2 DMA ACKNOWLEDGE PRIORITY LEVEL 3 I/O WRITE I/O READ INTERRUPT REQUEST PRIORITY LEVEL 2 INTERRUPT REQUEST PRIORITY LEVEL 3 INTERRUPT REQUEST PRIORITY LEVEL 4 INTERRUPT REQUEST PRIORITY LEVEL 5 INTERRUPT REQUEST PRIORITY LEVEL 6 INTERRUPT REQUEST PRIORITY LEVEL 6 INTERRUPT REQUEST PRIORITY LEVEL 7 TERMINAL COUNT OSCILLATOR (14.31818 MHZ CLOCK) |

NOTE: Refer to Section 11.0 for I/O Signal Descriptions

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

#### 8.0 TAPE DRIVE INTERFACE SPECIFICATIONS

#### 8.1 General

The 1/4" Tape controller must allow interfacing to a QIC-36 (basic interface) compatible 1/4" cartridge tape drive which is internally mounted with the controller in the DN3000 system.

Interconnections from drive to controller are made via a card-edge connector on the drive.

The drive to controller interface cable is a 3M-3365, 50-wire flat cable with CA-50, IDS socket.

Maximum interface cable length is 10 ft. See figure 1.0 for location of drive interface connector J2.

The 1/4" tape drive which interfaces to the 1/4" tape controller must meet the requirements of specifications referenced in Sections 2.1.1 and 2.2.1 of this document to operate correctly in the Apollo DN3000 system.

## 8.2 Interface Signal Levels

All Interface signals between the basic tape drive and the controller are TTL logic levels as defined below:

Signal True = Logic 1 (Low) 0.00 to 0.55 VDC

Signal False = Logic 0 (High) 2.40 to 5.25 VDC

#### 8.3 Signal Loading

All Signals from the tape drive to the controller are capable of driving one standard TTL load in addition (1.6mA) in addition to the 23mA required by the tape drive interface terminations. Refer to the specifications in sections 2.1.1 and 2.1.5 of this document.

#### 8.4 Signal Terminations

All Signals between the controller and the tape drive must be terminated with 330 ohms  $\pm -5\%$  to ground and 220 ohms  $\pm -5\%$  to 5VDC.

Signal inputs to the controller must be terminated at the controller. Signal outputs from the controller are terminated in the tape drive. Figure 2.0 shows the signal termination scheme.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

#### 8.5 Pin Assignments

Table 4.0 identifies the tape drive/controller interface signals. This signal interface is pin and plug compatible with the QIC-36 interface standard (See Section 2.1.1) except as noted.

CONNECTOR J3 PIN ASSIGNMENTS/SIGNAL DESCRIPTIONS

TABLE 4.0

| PIN                              | NAME                                                | то*                   | DESCRIPTION                                                                                                                                                                                                                                       |

|----------------------------------|-----------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                                     | ****                  |                                                                                                                                                                                                                                                   |

| 02<br>04<br>06<br>08<br>10<br>12 | GO-<br>REV-<br>TR3-<br>TR2-<br>TR1-<br>TR0-<br>RST- | D<br>D<br>D<br>D<br>D | GO. MOTION CONTROL FOR CAPSTAN SERVO. REVERSE. DIRECTION CONTROL FOR CAPSTAN SERVO TRACK SELECT BIT 3 (MSB). TRACK SELECT BIT 2 TRACK SELECT BIT 1. TRACK SELECT BIT 0 (LSB). RESET. CAUSE DRIVE TO PERFORM INITIALIZATION AND HEAD RECALIBRATION |

| 22 24                            | DS0-<br>HC-                                         | D<br>D                | DRIVE SELECT. HIGH CURRENT. ENABLES OPERATION WITH ALTERNATE TAPE TYPE. (DC600A).                                                                                                                                                                 |

| 26                               | RDP-                                                | С                     | READ DATA PULSE. READ DATA IS PRESENT AT THE DRIVE INTERFACE.                                                                                                                                                                                     |

| 28<br>30<br>32<br>34<br>36       | UTH-<br>LTH-<br>• SLD-<br>CIN-<br>USF-              | CCCCC                 | UPPER TAPE HOLE. LOWER TAPE HOLE. RESPONSE FROM DRIVE WHEN SELECTED. CARTRIDGE IN. TAPE CARTRIDGE IN PLACE. UNSAFE. SAFE PLUG ON CARTRIDGE IS IN THE UNSAFE POSITION, I.E. WRITING IS ENABLED.                                                    |

| 38<br>40<br>42<br>44             | TCH-<br>WDA-<br>WDA+<br>• THD-                      | C<br>D<br>D           | TACHOMETER. CAPSTAN TACHOMETER PULSES. WRITE DATA. INVERSE OF WRITE DATA SIGNAL. THRESHOLD - INVOKES A PERCENTAGE QUALIFYING AMPLITUDE FOR THE READ SIGNAL OFF TAPE.                                                                              |

| 46<br>48<br>50                   | HSD-<br>WEN-<br>EEN-                                | D<br>D<br>D           | HIGH SPEED DRIVE. TAPE SPEED = 90 IPS.<br>WRITE ENABLE.<br>ERASE ENABLE.                                                                                                                                                                          |

\*C = CONTROLLER

D = DRIVE

- The controller shall discriminate between DC300XL and DC600A cartridges by measurement of BOT to load distance and shall select the appropriate basic drive write current.

- These signals are not present on the controller drive interface connector J3.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

#### 9.0 AGENCY COMPLIANCE

The 1/4" tape controller shall conform to the following certification requirements.

#### 9.1 Safety

U.L. - recognized by U.L. and meet 94 V-0 flammability rating.

CSA - certified by Canadian Standards Association (CSA) as a component.

#### 9.2 Emissions

FCC - Tested for compliance with FCC Class B, Part 15, Subchapter J and VDE Standard 0871 for radio frequency emissions, when installed in an Apollo system.

#### 10.0 RELIABILITY AND LIFE

#### 10.1 MTBF

The calculated MTBF for the 1/4" Tape controller shall be a minimum of 400,000 power on hours, using accepted calculation methods for a benign environment.

#### 10.2 Life

The minimum life expectancy of the controller shall be 5-years.

#### 10.3 Error Rates

The controller is expected to have a read data reliability rate: When connected to Apollo 1/4" Tape drive #008850 and utilizing Apollo 1/4" tape cartridge 004634 as follows:

Recoverable (Soft) error rate - No more than 1 in 10E8 bits

Non-Recoverable (Hard) error rate - No more than 1 in 10E10 bits.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

#### 11.0 THEORY OF OPERATIONS

This section is for reference only. It describes the major functions of the controller including a block diagram, I/O signal descriptions, I/O port assignments, control/status registers, DMA channel, interrupt priority level and resets.

For more information describing the controller and QIC-02 based I/O registers refer to the specifications listed in sections 2.1.4 and 2.1.5 of this document.

### 11.1 Block Diagram Descriptions

The microprocessor based 1/4" tape controller performs the function of an intelligent streaming tape controller. In the write mode, it accepts data from the host, formats it into blocks, appends CRC, GCR encodes the data and writes it to tape. The controller performs a read after write data check using the appended CRC to insure data integrity. In the read mode, the controller reads data from tape, GCR decodes the data, checks the CRC and sends the data to the host.

See Figure 3.0 for block diagram of the controller circuitry.

Following is a functional description of the controller:

(To be supplied)

| 11.1.1  | Register Base Address | Decoder |      |                |      |

|---------|-----------------------|---------|------|----------------|------|

| 11.1.2  | Register Select       |         |      |                |      |

| 11.1.3  | DMA Control           |         |      |                |      |

| 11.1.4  | Interrupt Control     |         |      |                |      |

| 11.1.5  | Control Status        |         |      |                |      |

| 11.1.6  | Data Register         |         |      |                |      |

| 11.1.7  | Microprocessor        |         |      |                |      |

| 11.1.8  | Host Data Sequencer   |         |      |                |      |

| 11.1.9  | Buffer Memory Control |         |      |                |      |

| 11.1.10 | Data Buffers          |         |      |                |      |

| 11.1.11 | Write Data Sequencer  |         |      |                |      |

| 11.1.12 | Read Data Sequencer   |         |      |                |      |

| 11.1.13 | PLL                   |         |      |                | ·    |

|         |                       | SIZE    | CODE | DRAWING NUMBER | REV. |

|         |                       | A       |      | 008845         | E0   |

## 11.2 I/O Signal Descriptions

Following is a description of the I/O channel signals present on the controller I/O bus connector – J1.

| SIGNAL    | I/O  |      | DESCRIPTION                                                                                                                                                                                                                                                                                            |                                                         |

|-----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| OSC       | O    |      | Oscillator: High-Speed clock v 70-NS period (14.31818 MHz has a 50% duty cycle.                                                                                                                                                                                                                        | vith a<br>). It                                         |

| Reset Drv | Ο    |      | This line is used to reset or insystem logic upon power-up of a low line voltage outage. This is synchronized to the falling eclock and is active high.                                                                                                                                                | during s signal                                         |

| A0-A19    | Ο    |      | Address bits 0 to 19: These linused to address memory and I within the system. The 20 addines allow access of up to 1 m of memory. A0 is the least significant bit (LSB) and A19 most significant bit (MSB). The lines are generated by either the processor or DMA controller. active high.           | /O devices dress negabyte is the lese ne                |

| D0-D7     | 0    |      | Data bits 0 to 7: These lines p<br>data bus bits 0 to 7 for the pr<br>memory and I/O devices. D0 i<br>least significant bit (MSB). Th<br>are active high.                                                                                                                                              | ocessor,<br>is the                                      |

| IRQ2-IRQ7 | I    |      | Interrupt request 2 to 7: These used to signal the processor the device requires attention. The prioritized with IRQ2 as the hipriority and IRQ7 as the lowest interrupt request is generated an IRQ line (low to high) and it high until it is acknowledged processor. (Interrupt service researched) | at an I/O ey are ghest st. An ey raising holding by the |

|           | SIZE | CODE | DRAWING NUMBER                                                                                                                                                                                                                                                                                         | REV.                                                    |

|           | A    |      | 008845                                                                                                                                                                                                                                                                                                 | E0                                                      |

|               | - |                               |                                                                       |                                                                                                                                                                                                             |                                       |

|---------------|---|-------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| IOR           | 0 | i<br>t                        | nstructs ar<br>he data bu                                             | command: This command line in I/O device to drive its data on its. It may be driven by the property A controller. This signal is active.                                                                    | cessor                                |

| IOW           | 0 | iı<br>C                       | nstructs ar<br>lata bus.                                              | command: This command line in I/O device to read the data or It may be driven by the process controller. This signal is active                                                                              | n the<br>sor or                       |

| DRQ1-DRQ3     | I | a<br>d<br>. w<br>ti<br>a<br>n | synchrono<br>levices to<br>vith DRQ3<br>he highest<br>DRQ line        | est 1 to 3: These lines are sus channel requests used by pergain DMA service. They are probeing the lowest and DRQ1 between to an active level (High). A Deld high until the corresponding ctive.           | rioritized<br>ing<br>nging<br>RQ line |

| DACK0 - DACK3 | 0 | t.<br>a                       | o acknowl<br>nd to refr                                               | enowledge 0 to 3: These lines are edge DMA requests (DRQ1-DR esh system dynamic memory (Ective low.                                                                                                         | RQ3)                                  |

| AEN           | 0 | p<br>ti<br>li<br>c            | orocessor a<br>o allow Di<br>ine is active<br>control of<br>ines (mem | nable: This line is used to De-gund other devices from the I/O MA transfers to take place. Where (high), the DMA controller has address bus, data bus, read tory and I/O), and the write conterpy and I/O). | channel<br>en this<br>nas<br>command  |

| T/C / * **    | 0 | ť                             | he termina                                                            | Count: This line provides a pulse al count for any DMA channel is active high.                                                                                                                              | e when<br>is reached.                 |

| -             |   |                               |                                                                       |                                                                                                                                                                                                             |                                       |

|               |   | SIZE                          | CODE                                                                  | DRAWING NUMBER                                                                                                                                                                                              | REV.                                  |

|               |   | A                             |                                                                       | 008845                                                                                                                                                                                                      | E0                                    |

## 11.3 I/O Port Assignments (Base Address)

The I/O Registers occupy eight adjacent locations in the systems I/O address map. Only four of the address locations are used by the 1/4" tape controller.

Note: The jumper-selectable base address is factory-set at 200 HEX.

See Table 2.0 for details

- 11.3.1 Data/Command Register: Base Address +0 (Read or Write)

- 11.3.2 Control Register (Write Only): Base Address +1 Status Register (Read Only).

- 11.3.3 Start DMA (DMAGO): Base Address +2. Any Write to this Register will cause DMAGO to be active.

- 11.3.4 Reset DMA (RSTDMA): Base Address +3. Any Write to this Register will cause RSTDMA to be active.

SIZE CODE DRAWING NUMBER REV.

A 008845 E0

## 11.4 Control/Status Register Descriptions

## 11.4.1 Control Register (Write)

DNIEN = 0, Masks done interrupt.

(Bits 0-3 Not Used)

## 11.4.2 Status Register (Read)

| Bit 7 | 0 = IRQF | Interrupt request flag, ORING of RDY and EXC, and done if DNIEN is set. |

|-------|----------|-------------------------------------------------------------------------|

| Bit 6 | 0 = RDY  | Ready, From LSI Chip.                                                   |

| Bit 5 | 0 = EXC  | Exception, from LSI Chip                                                |

| Bit 4 | 1 = DONE | Done, From DMA logic                                                    |

| Bit 3 | 1 = DIRC | Direction, indicates direction of bus is from controller to I/O bus.    |

(Bits 0-2 Not Used)

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

#### 11.5 DMA Channel

The tape controller uses the systems I/O bus DMA controller to transfer data to and from the system main memory. The DMA channel is also jumper-selectable (See Table 2.0).

The tape-controller DMA logic can be initialized by writing to address location base +3 (RSTDMA). RSTDMA initializes the DMA sequencer, clears all control register bits to 0, and sets done to 1 (Power-on reset from the system performs the same functions). The following sequence may be used to start DMA transfer:

Sequese)

1. Issue a transfer command to the tape controller.

3 2. Set up the DMA controller's register (But leave the mast bit set).

2 3. Write (any value) to the tape controller register at base address +2 (DMAGO)

4. Clear the mask bit in the 8237 DMA controller.

5. Repeat above from Step 2 for each subsequent block.

## 11.6 Interrupt Priority Level

Market S

The controller interrupt priority level is jumper-selectable (See Table 2.0) each interrupt source bit, RDY, EXC, and DONE (See Status Register – Section 11.4.2), can be read through the status register regardless of the state of the interrupt masks: IEN = 0, DNIEN = 0, (See Control Register – Section 11.4.1). The IRQ line is tri-stated when IEN is cleared. This allows other systems I/O bus options the use of that interrupt line when the tape controller is not using it. Therefore, the systems I/O bus interrupt controller should be programmed to respond to the tape controller's IRQF only after IRQ has been enabled by setting IEN.

Interrupts to the host will be caused for the following reasons:

- 1. After completion of any command when status is valid and ready to be checked.

- 2. A soft reset has been issued.

- 3. An exception condition occurs such as illegal command or an erroneous condition occurs during the operation of the tape drive while doing a command.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

#### 11.7 Resets

Four reset signals (Two DMA resets, and two microprocessor/tape drive resets) are available on the controller.

### 11.7.1 DMA Resets:

- \* RSTDMA. (RSTDMA is discussed in Section 11.5)

- \* Reset DRV. This is the power-on reset from the systems power supply, and performs the same functions as RSTDMA.

## 11.7.2 Microprocessor and Tape Drive Resets:

- \* Microprocessor reset. Reset the controller microprocessor when any of the following conditions occur:

- A. The +5V Supply drops below 4.6V.

- B. The +12V Supply drops below 9V.

- C. RSTSAC is set.

Note: Microprocessor reset will also cause a tape drive reset.

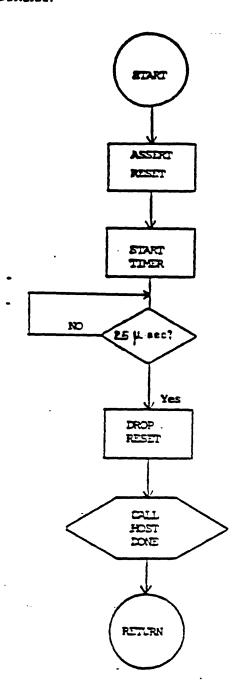

\*RSTSAC. Activated by writing a 1 to control register bit 7. RSTSAC must be set, held for more than 25 usec, then cleared by either writing a 0 to control register bit 7 or by a RSTDMA.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

#### 12.0 PROGRAMMING INFORMATION

This section is for reference only. It describes the QIC-02 command set, programming flow charts, and maximum command timings. Refer to specifications listed in sections 2.1.4 and 2.1.5 of this document for additional information on command sequencing, status register sense bytes, QIC-24 tape format and command timing diagram descriptions.

#### 12.1 Command Set Descriptions

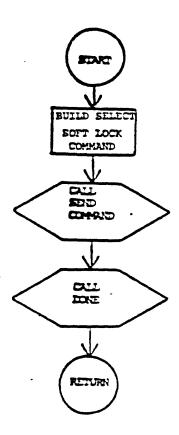

## 12.1.1 Select, Soft Lock Off (0000 0001)

The select command selects the tape drive. The drive shall remain until changed by another select command or reset.

#### 12.1.2 Select, Soft Lock On\* (0001 0001)

This command is identical in function to the select, soft lock off command and additionally provides a soft lock on the cartridge. Execution of the select command or reset unlocks the cartridge.

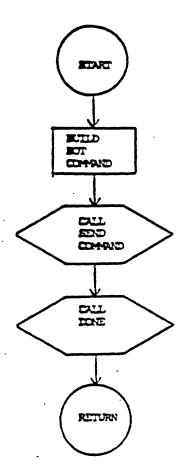

## 12.1.3 Bot Command (0010 0001)

The BOT command positions the tape in the cartridge in the selected device to BOT (beginning of tape).

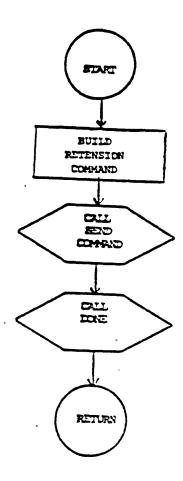

#### 12.1.4 Retension Command (0010 0100)

The retension command shall be used in accordance with cartridge tape manufacturer's instructions. The retension command moves the tape in the device to BOT, then to EOT and then back to BOT.

#### 12.1.5 Erase Command (0010 0010)

The erase command completely erases the tape in the selected drive. The erase command moves the tape in the device to BOT, activates the erase head and moves to EOT, deactivates the erase head and moves the tape back to BOT. The erase command also fulfills the requirements of initialization.

\*Note: Softlock "On" enables the "Selected" LED of the tape drive and issues an exception status if the cartridge is removed during next command issued.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

12.1.6 Write Command (0100 0000)

When the write command is issued the device requests and transfers data. The Ready line is activated when the device is ready for a data block transfer. When the ready line is active, the host terminates transfer of write data by issuing a write-file-mark command. Note: A write command following cartridge insertion or reset shall commence recording at BOT. Otherwise recording shall commence at the current tape postern. NOTE: If the host starts transfer between blocks before ready is asserted, ready may not be asserted when the early warning hole of the last track is detected by the device, thus the device ceases to transfer additional data blocks from the host. The device terminates the write command and reports end of media by means of an exception and read status.

12.1.7 Read Command (1000 0000)

We use here

When the read command is issued the device transfer data. The ready line is activated when the device is ready for a data block transfer. The read command shall be terminated by the device if a file mark is detected. The host is informed by means of an exception and a read status sequence. When ready is true, the host may alternatively terminate the read command by issuing a read-file-mark command. If a read command is issued, the command is accepted and the drive continues reading. Note: A read command following cartridge insertion or reset shall commence at BOT, otherwise the read command commences from the current tape position. Note: If the host starts transfer between blocks before ready is asserted, ready may not be

12.1.8 Write-File-Mark Command (0110 0000)

The Write-File-Mark (WFM) command causes a file mark to be written on the tape in the selected drive. Note: A WFM command following cartridge insertion or reset shall commence recording at BOT, otherwise recording shall commence at the current tape position.

12.1.9 Read-File-Mark Command (1010 0000)

The Read-File-Mark (RFM) command causes the tape in the selected drive to be moved to the next file mark. Note: A RFM command following cartridge insertion or reset shall commence reading at the BOT, otherwise, reading shall commence at the current tape position.

SIZE CODE DRAWING NUMBER REV.

008845 E0

SHEET 25 OF 44

6

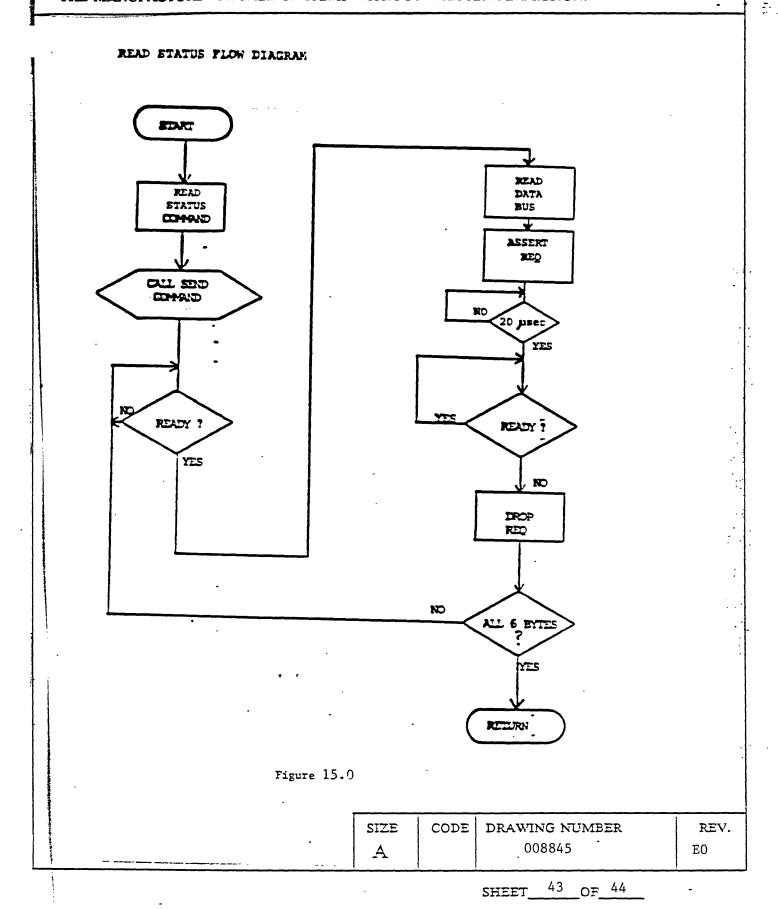

## 12.1.10 Read Status Command (1100 0000)

The Read Status command provides the host with information about the selected device. The host issues the read status command. The device transfers the standard six bytes to the host.

## 12.1.11 Select Q11 Format Command (0010 0110)

The Select Q11 format command selects the QIC-11 format as the current format.

### 12.1.12 Select Q24 Format Command (0010 0111)

The Select Q24 format command selects the QIC-24 format as the current format.

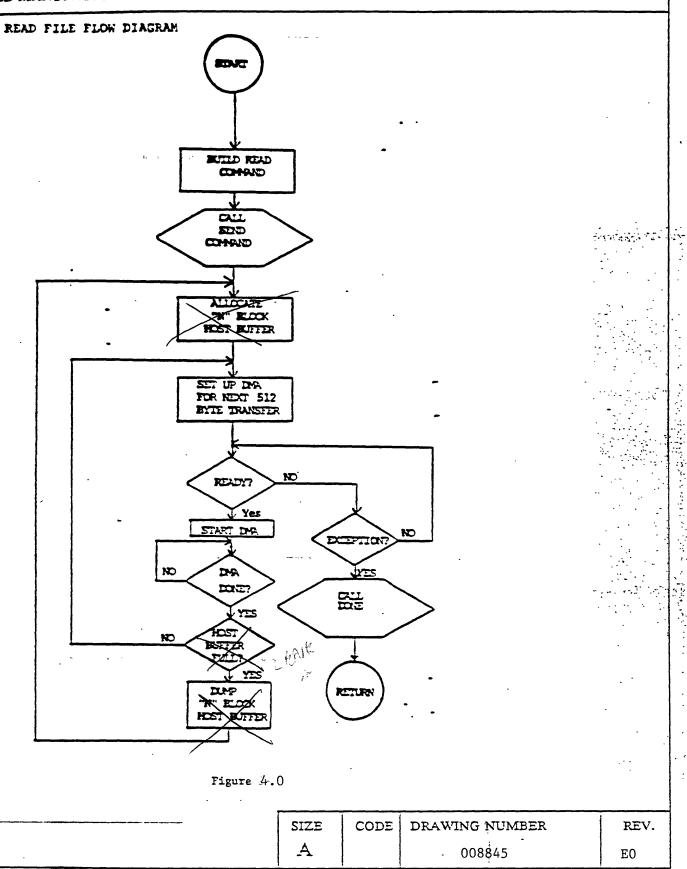

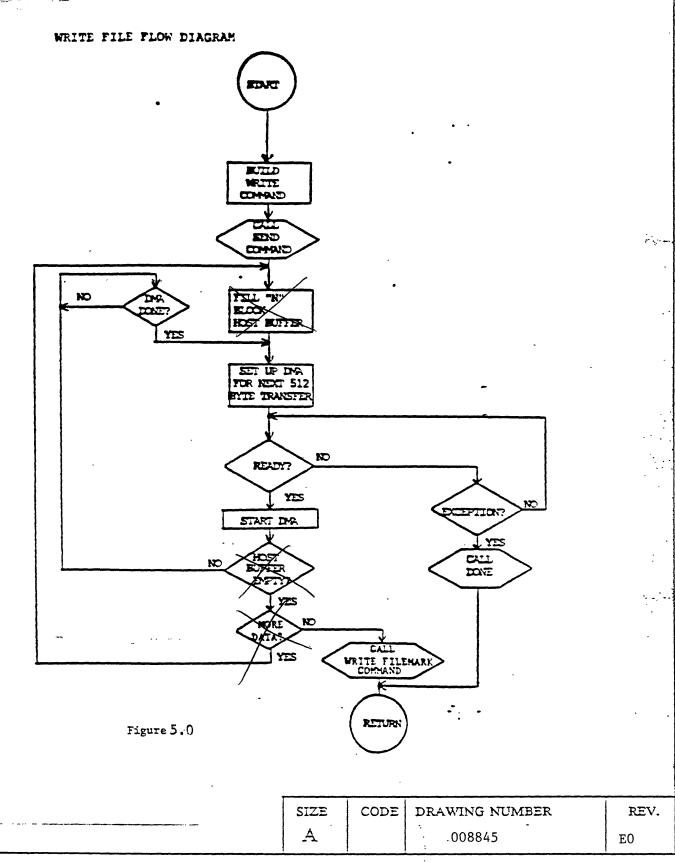

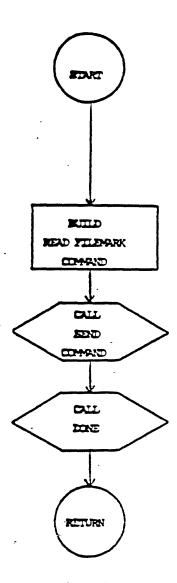

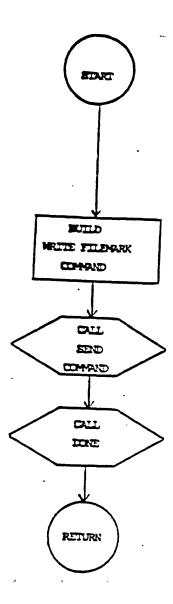

## 12!2 Command Flow Charts

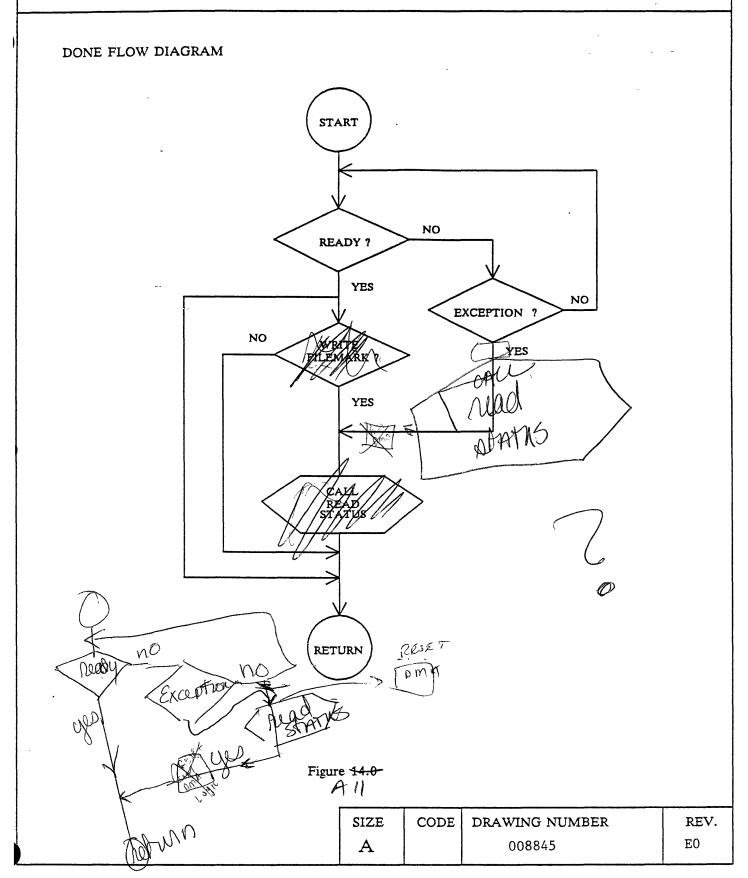

The Diagrams in Appendix A specify the flow of the command structures.

These flow charts are helpful for any software engineer who is designing a software driver. The flow charts in Appendix A are listed as follows:

| DESCRIPTION |                                            |            |           |         | FIGURE   |      |

|-------------|--------------------------------------------|------------|-----------|---------|----------|------|

| 12.2.1      | Read File Flow                             | Diagram    |           |         | 4.0      |      |

| 12.2.2      | Write File Flow                            | Diagram    |           |         | 5.0      |      |

| 12.2.3      | Read File Mark                             | Flow Diag  | ram       |         | 6.0      |      |

| 12.2.4      | Write File Mark                            | Flow Diag  | gram      |         | 7.0      |      |

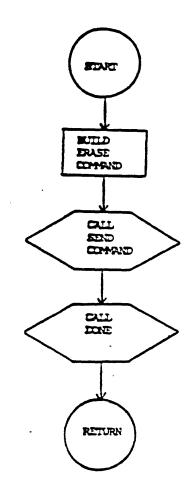

| 12.2.5      | Erase Command                              | l Flow Dia | gram      |         | 8.0      |      |

| 12.2.6      | Initialize Cartraidge Command Flow Diagram |            |           | Diagram | 9.0      |      |

| 12.2.7      | BOT Command Flow Diagram                   |            |           |         | 10.0     |      |

| 12.2.8      | Select Softlock                            | Command    | Flow Diag | gram    | 11.0     |      |

| 12.2.9      | Select Format C                            | command I  | Flow Diag | ram     | 12.0     |      |

| 12.2.10     | Reset Flow Diag                            | ram        |           |         | 13.0     |      |

| 12.2.11     | Done Flow Diag                             | ram        |           |         | 14.0     |      |

| 12.2.12     | Read Status Flo                            | w Diagram  |           |         | 15.0     |      |

| 12.2.13     | Send Command                               | Flow Diag  | gram      |         | 16.0     |      |

|             | i                                          | SIZE       | CODE      | DRAWIN  | G NUMBER | REV. |

|             |                                            | A          | CODE      |         | 8845     | E0   |

## 12.3 QIC-02 Command Maximum Timings

The maximum QIC-02 Command Set Timings before time-out conditions are generated are as follows:

12.3.1 Retension Command

450ft tape - 180 seconds

600ft tape - 241 seconds (Worst Case)

12.3.2 BOT Command

600ft tape - 1 min 20 sec.

12.3.3 Reset Command

5 Sec

12.3.4 Erase Command

4 Min

#### 13.0 SYSTEMS SOFTWARE INFORMATION

This section is for referenced only. It describes the minimum revision levels for diagnostic tests and operating systems software support.

#### 13.1 Diagnostic Level Test

The systems or device level diagnostic test is called CTAPE.DEX and is located in the SAU8 Directory on the DN3000 system disk. The minimum diagnostic revision level required is 1.0. The minimum required O.S. Level of AEGIS containing SAU8 Directory is SR9.2.1.

## 13.2 Operating Systems Software (AEGIS)

The 1/4" Cartridge tape controller will operate only in an Apollo DN3000 system backplane which utilizes QIC-02 command compatible I/O bus.

The DN3000 operating systems software which supports the 1/4" Tape controller functionality is located in the SAU8 directory on the systems disk. The minimum O.S. Revision level required is SR9.2.1.

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| Α    |      | 008845         | E0   |

| THIS DRAWING AND SPECIFICATION HERE AND SHALL NOT BE REPRODUCED OR CONTHE MANUFACTURE OR SALE OF ITEMS | PIED OR U | SED IN | WHOLE OR PART AS THE BA | ER INC.<br>ASIS FOR |

|--------------------------------------------------------------------------------------------------------|-----------|--------|-------------------------|---------------------|

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

| Append                                                                                                 |           |        |                         |                     |

| - Command Fl                                                                                           | ow Cha    | rts –  |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         | -                   |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         | :                   |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        |           |        |                         |                     |

|                                                                                                        | SIZE      | CODE   | DRAWING NUMBER          | REV.                |

|                                                                                                        | A         |        | 008845                  | E0                  |

|                                                                                                        |           |        | SHEET 28 OF 44          |                     |

SHEET 29 OF 44

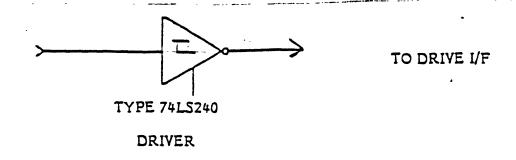

220 } 330 } GRND

FROM DRIVE I/F

Figure 2.0 Interface Signal Termination

TYPE 74LS14

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | E0   |

THE DRAWING AND SPECIFICATION HEREIN ARE THE PROPERTY OF APOLLO COMPUTER INC.

AND SHALL NOT BE REPRODUCED OR COPIED OR USED IN WHOLE OR PART AS THE BASIS FOR

THE MANUFACTURE OR SALE OF ITEMS WITHOUT WRITTEN PERMISSION. CONTROLLER · HICRO Q ١ COMPUTER o ۷ ٠. ٠ 3 6 В IBH/QIC 02 HOST а QIC 02 ADAPTOR . INTERFACE S CIRCUITRY 1 WRITE C DATA SEQUENCER BUFFER v: HOST HEHORY D 8 R SEQUENCER CONTROL READ DATA SEQUENCER v I E В M I N Т 5 E m DATA C ۴ BUFFERS PLL A T c B FUNCTIONAL BLOCK DIAGRAM FIGURE 3.9 SIZE REV. CODE DRAWING NUMBER A 008845 E0

SHEET 31 OF 44

ا الراب المرابع المرابع المستوافق المرابع المرابع المرابع المرابع المرابع المرابع المرابع المرابع المرابع المر المرابع المرابع

SHEET 33 OF 44

READ FILE MARK FLOW DIAGRAM

Figure 6.0

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | . 008845       | EO   |

# WRITE FILE MARK FLOW DIAGRAM

يرب درونه يعربي بوقي بتعريبه مراتهم ومداها

Figure 7.0

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | . 008845       | ΕO   |

## ERASE COMMAND FLOW DIAGRAM

Figure 8.0

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | EO   |

SHEET 36 OF 44

# INITIALIZE CARTRIDGE COMMAND FLOW DIAGRAM

Figure 9.0

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    | ,    | . 008845       | EO   |

## BOT COMMAND FLOW DIAGRAM

Figure 10.0

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | . 008845       | EO   |

145

BELECT, BOFT LOCK COMMAND FLOW DIAGRAM

Figure 11.0

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | 008845         | EO   |

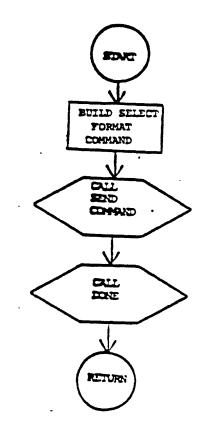

# SELECT FORMAT COMMAND FLOW DIAGRAM

Figure 12.0

| - | SIZE | CODE | DRAWING NUMBER | REV. |

|---|------|------|----------------|------|

|   | A    |      | · 008845       | EO   |

SHEET 40 OF 44

e in entagen a la light

### RESET FLOW DIAGRAM

Figure 13.0

| SIZE | CODE | DRAWING NUMBER | REV. |

|------|------|----------------|------|

| A    |      | . 008845       | EO   |

SHEET 41 OF 44

: .

\*