# TECHNICAL MANUAL for MODEL 1200 CENTRAL PROCESSING UNIT

September 1, 1972

Revised: August 10, 1973

# PROPRIETARY INFORMATION

The information contained herein is proprietary to and considered a trade secret of Basic/Four Corporation and shall not be reproduced in whole or part without the written authorization of Basic/Four Corporation.

basic/four and

are registered trademarks of BASIC/FOUR CORPORATION

# List of Effective Pages

|                                                  | Revision           |

|--------------------------------------------------|--------------------|

| Page                                             | Date               |

|                                                  |                    |

| iii thru xii                                     | Original           |

| xiii, xiv                                        | August 10, 1973    |

| χv                                               | February 1, 1973   |

| xvi                                              | August 10, 1973    |

| 1-1 thru 1-54                                    | Original           |

| 2-1 thru 2-46                                    | Original           |

| 2-47                                             | February 1, 1973   |

| 2-48 thru 2-54                                   | Original           |

| 2-55                                             | February 1, 1973   |

| 2-56 thru 2-115                                  | Original           |

| 3-1 thru 3-25                                    | Original           |

| 4-1 thru 4-9                                     | Original           |

| 5-1                                              | February 1, 1973   |

| 5-2 thru 5-4                                     | Original           |

| 5-5                                              | February 1, 1973   |

| 5-6 thru 5-10                                    | Original           |

| 5-11                                             | February 1, 1973   |

| 5-12 thru 5-19                                   | Original           |

| 5-19.1 thru 5-19.3                               | August 10, 1973    |

| 5-20                                             | August 10, 1973    |

| 5-21                                             | Original           |

| 5-22                                             | August 10, 1973    |

| 5-23                                             | Original           |

| \$4/4/,/\$4/44///////////////////////////        | // Otilginal       |

| \$1/1/th#p/\$1/13/////                           | / Driginal         |

| Ş2-i                                             | February 1, 1973   |

| S2-1 thru S2-6                                   | February 1, 1973   |

| S3-i                                             | Original           |

| S3-1 thru S3-13                                  | Origina1           |

| S4-i                                             | Origina1           |

| S4-1 thru S4-4                                   | Original           |

| <i>\$</i> ፮/ሕ/////////////////////////////////// | /Febthaty/1/,/1973 |

| <i>\$\$\1\t\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\</i> | /Febthaty/1/,/1973 |

| S6-i, S6-ii                                      | August 10, 1973    |

| S6-1 thru S6-26                                  | August 10, 1973    |

| S7-i, S7-ii                                      | February 1, 1973   |

| S7-1 thru S7-32                                  | February 1, 1973   |

|                                                  |                    |

# TABLE OF CONTENTS

|            |                                    | Page  |

|------------|------------------------------------|-------|

| SECTION 1. | INTRODUCTION                       |       |

| 1.1        | Scope                              | 1-1   |

| 1.2        | Manual Organization                | 1-1   |

| 1.3        | Equipment Purpose and Capabilities | 1-2   |

| 1.4        | Reference Data                     | 1-4   |

| 1.5        | Physical Description               | 1-6   |

| 1.5.1      | Enclosures                         | 1-6   |

| 1.5.2      | Backplane                          | 1-6   |

| 1.5.3      | Interconnections                   | 1-7   |

| 1.5.4      | CPU Printed Circuit Boards         | 1-9   |

| 1.5.4.1    | Front Panel Assembly               | 1-9   |

| 1.5.4.2    | Interface Board                    | 1-12  |

| 1.5.4.3    | Control Board                      | 1-13  |

| 1.5.4.4    | Data Board                         | 1-13  |

| 1.5.5      | Power Supply                       | 1-14  |

| 1.6        | Functional Organization            | 1-14  |

| 1.6.1      | Registers                          | 1-16  |

| 1.6.1.1    | T Register                         | 1-16  |

| 1.6.1.2    | M and N Registers                  | 1-16  |

| 1.6.1.3    | U Register                         | 1-16  |

| 1.6.1.4    | File Registers                     | 1-16  |

| 1.6.1.5    | L Register                         | 1-17  |

| 1.6.1.6    | L Save Register                    | 1-17  |

| 1.6.1.7    | R Register                         | ,1-17 |

| 1.6.1.8    | Link Register                      | 1-18  |

| 1.6.1.9    | MD Register                        | 1-18  |

| 1.6.1.10   | IC Register                        | 1-18  |

| 1.6.1.11   | OD Register                        | 1-19  |

| 1.6.2      | Main Data Buses                    | 1-19  |

| 1.6.2.1    | Memory Data Bus                    | 1-19  |

| 1.6.2.2    | Input Data Bus                     | 1-19  |

| 1.6.2.3    | Output Data Bus                    | 1-19  |

|             |                                                                               | Page |

|-------------|-------------------------------------------------------------------------------|------|

| SECTION 1.  | INTRODUCTION (continued)                                                      |      |

| 1.6.2.4     | B Bus                                                                         | 1-19 |

| 1.6.2.5     | A Bus                                                                         | 1-20 |

| 1.6.2.6     | RS Bus                                                                        | 1-20 |

| 1.6.3       | Arithmetic/Logic Unit (ALU)                                                   | 1-20 |

| 1.6.4       | Control Memory                                                                | 1-21 |

| 1.6.5       | Core Memory                                                                   | 1-22 |

| 1.6.6       | Real Time Clock                                                               | 1-23 |

| 1.6.7       | Power Fail and Restart Feature                                                | 1-23 |

| 1.6.8       | File Zero Flags                                                               | 1-23 |

| 1.6.9       | Internal Status Byte                                                          | 1-24 |

| 1.7         | Microcommand Descriptions                                                     | 1-25 |

| 1.7.1       | Command Modification Class                                                    | 1-27 |

| 1.7.1.1     | Execute, Literal Type (ELT)                                                   | 1-27 |

| 1.7.1.2     | Execute, Operate Type (EOT)                                                   | 1-28 |

| 1.7.1.3     | Modify High-Order Bits of Op Codes 8 Through F                                | 1-28 |

| 1.7.1.4     | Modify Lower Command (MLC)                                                    | 1-29 |

| 1.7.1.5     | Enter Console Switches (ECS)                                                  | 1-30 |

| 1.7.1.6     | Formation of Effective Microcommand From ${\tt U}$ and ${\tt OD}$ Registers . | 1-30 |

| 1.7.1.7     | Formation of Effective Microcommand From U Register and                       |      |

|             | Data Switches                                                                 | 1-31 |

| 1.7.2       | Jump and Return Jump Class                                                    | 1-31 |

| 1.7.2.1     | Jump Extended (JE)                                                            | 1-31 |

| 1.7.2.2     | Jump In 1K (JP)                                                               | 1-32 |

| 1.7.2.3     | Jump In 1/2K                                                                  | 1-33 |

| 1.7.2.4     | Return (RTN)                                                                  | 1-33 |

| 1.7.2.5     | Return, Load T (RLT)                                                          | 1-34 |

| 1.7.3       | Literal Class                                                                 | 1-34 |

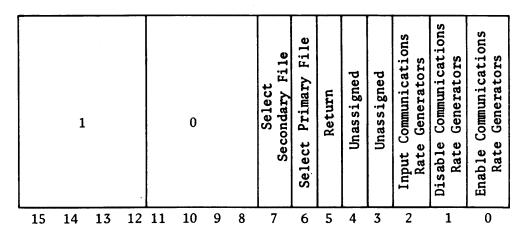

| 1.7.3.1     | Discrete-Function Literals                                                    | 1-34 |

| 1.7.3.1.1   | Load Zero (LZ)                                                                | 1-34 |

| 1.7.3.1.1.1 | Primary/Secondary File Selection (SPF and SSF)                                | 1-35 |

| 1.7.3.1.1.2 | Return Jump (RTN)                                                             | 1-35 |

| 1.7.3.1.1.3 | Input Communication Rate Generators (ICR)                                     | 1-35 |

| 1.7.3.1.1.4 | Enable/Disable Communication Rate Generators (ECR                             |      |

|             | and DCR)                                                                      | 1-36 |

|             |                                                     | Page |

|-------------|-----------------------------------------------------|------|

| SECTION 1.  | INTRODUCTION (continued)                            |      |

| 1.7.3.1.1.5 | No Operation (NOP)                                  | 1-36 |

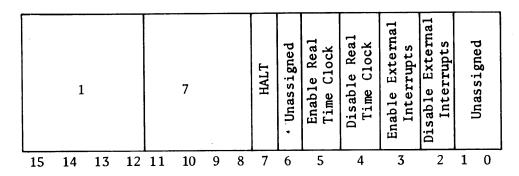

| 1.7.3.1.2   | Load Seven (LS)                                     | 1-36 |

| 1.7.3.1.2.1 | Processor Halt (HLT)                                | 1-36 |

| 1.7.3.1.2.2 | Enable/Disable Real Time Clock (ERT and DRT)        | 1-37 |

| 1.7.3.1.2.3 | Enable/Disable External Interrupts (EEI and DEI)    | 1-37 |

| 1.7.3.1.2.4 |                                                     | 1-37 |

| 1.7.3.1.3   | Load Eight (LE)                                     | 1-37 |

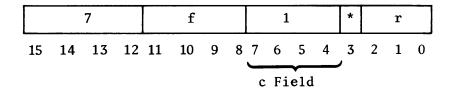

| 1.7.3.2     | Load Literal In Selected Register                   | 1-37 |

| 1.7.3.2.1   | Load T (LT)                                         | 1-38 |

| 1.7.3.2.2   | Load M (LM)                                         | 1-38 |

| 1.7.3.2.3   | Load N (LN)                                         | 1-38 |

| 1.7.3.2.4   | Load U (LU)                                         | 1-38 |

| 1.7.3.2.5   | Load File (LF)                                      | 1-39 |

| 1.7.3.2.6   | Add To File Register (AF)                           | 1-39 |

| 1.7.3.3     | Skip-Type Commands                                  | 1-39 |

| 1.7.3.3.1   | Test If Zero (TZ)                                   | 1-39 |

| 1.7.3.3.2   | Test If Not Zero (TN)                               | 1-40 |

| 1.7.3.3.3   | Compare File (CP)                                   | 1-40 |

| 1.7.4       | Operate Class                                       | 1-41 |

| 1.7.4.1     | Input/Output Operations                             | 1-41 |

| 1.7.4.1.1   | Enter Sense Switches (ESS)                          | 1-42 |

| 1.7.4.1.2   | Enter Internal Status (EIS)                         | 1-42 |

| 1.7.4.1.3   | External I/O (EXIO)                                 | 1-42 |

| 1.7.4.1.4   | File and Register Storage Actions for EXIO Commands | 1-43 |

| 1.7.4.2     | Arithmetic Operations                               | 1-44 |

| 1.7.4.2.1   | Add                                                 | 1-44 |

| 1.7.4.2.2   | Subtract (SBT or SBO)                               | 1-45 |

| 1.7.4.2.3   | Copy (CPY)                                          | 1-46 |

| 1.7.4.2.4   | Add Link To File (ALF)                              | 1-47 |

| 1.7.4.2.5   | Increment (INC)                                     | 1-47 |

| 1.7.4.2.6   | Decrement (DEC)                                     | 1-48 |

| 1.7.4.2.7   | Zero File (ZOF)                                     | 1-48 |

| 1.7.4.2.8   | Plus One To File (POF)                              | 1-48 |

| 1.7.4.2.9   | Copy Link To Register (CLN)                         | 1-49 |

|            |                                                      | Page |

|------------|------------------------------------------------------|------|

| SECTION 1. | INTRODUCTION (continued)                             |      |

| 1.7.4.2.10 | Move File (MOV)                                      | 1-49 |

| 1.7.4.2.11 | Enter 255 Into Register (255)                        | 1-49 |

| 1.7.4.2.12 | Complement File (CF)                                 | 1-50 |

| 1.7.4.2.13 | Shift File Right Four (SRF)                          | 1-50 |

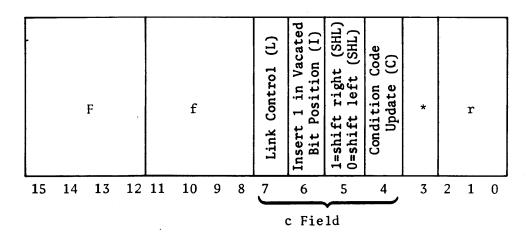

| 1.7.4.2.14 | Shift Left or Right (SFL, SLI, SFR, SRI)             | 1-50 |

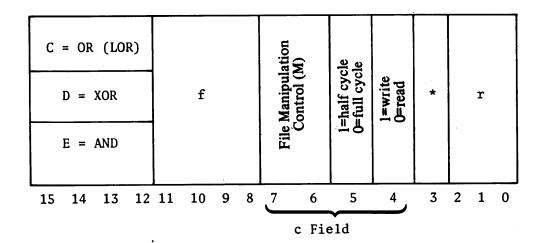

| 1.7.4.3    | Logical Operations                                   | 1-51 |

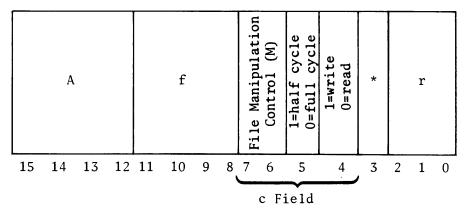

| 1.7.4.4    | Core Memory Operations                               | 1-52 |

| SECTION 2. | CPU THEORY OF OPERATION                              |      |

| 2.1        | Introduction                                         | 2-1  |

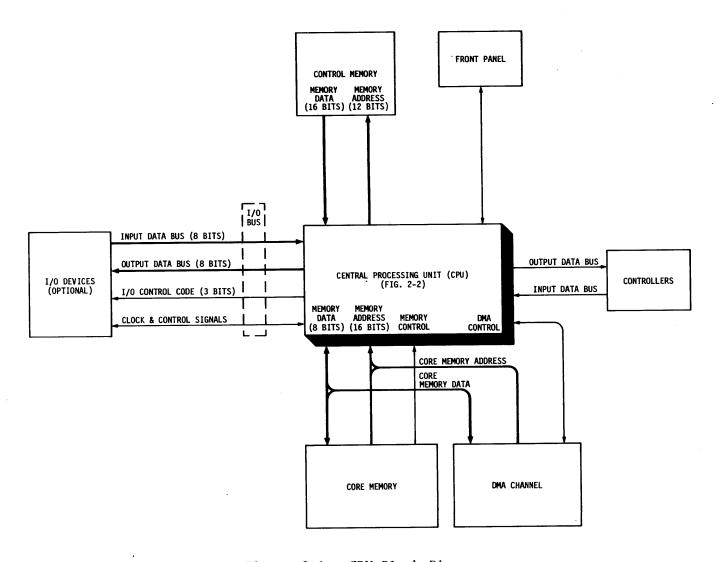

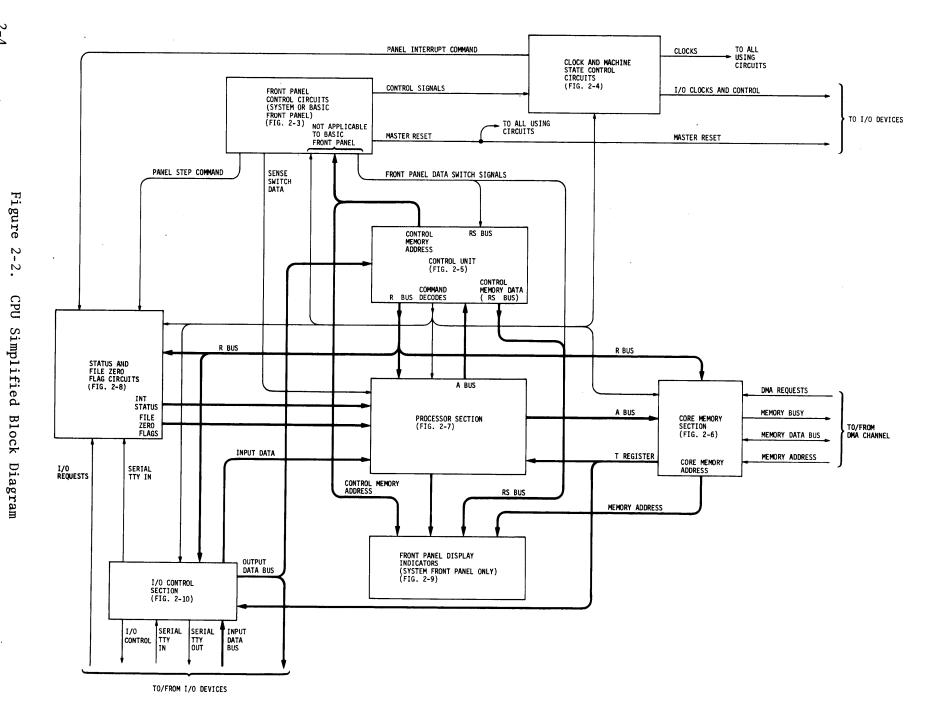

| 2.2        | System Block Diagram Description                     | 2-1  |

| 2.3        | CPU Block Diagram Descriptions                       | 2-2  |

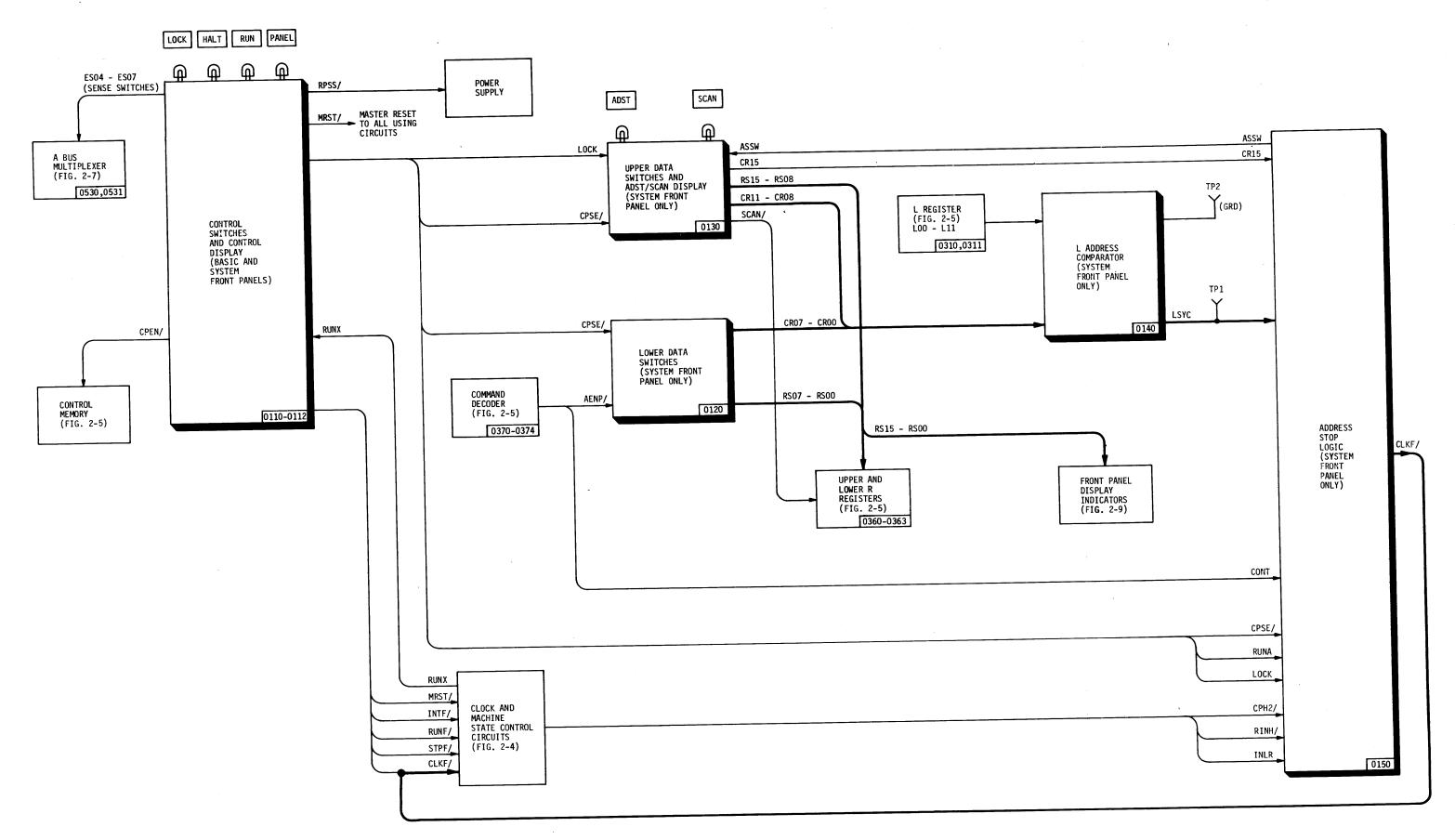

| 2.3.1      | Front Panel Control Circuits                         | 2-6  |

| 2.3.1.1    | Control Switches and Control Display                 | 2-6  |

| 2.3.1.2    | Upper and Lower Data Switche's and ADST/SCAN Display | 2-6  |

| 2.3.1.3    | L Address Comparator                                 | 2-7  |

| 2.3.1.4    | Address Stop Logic                                   | 2-7  |

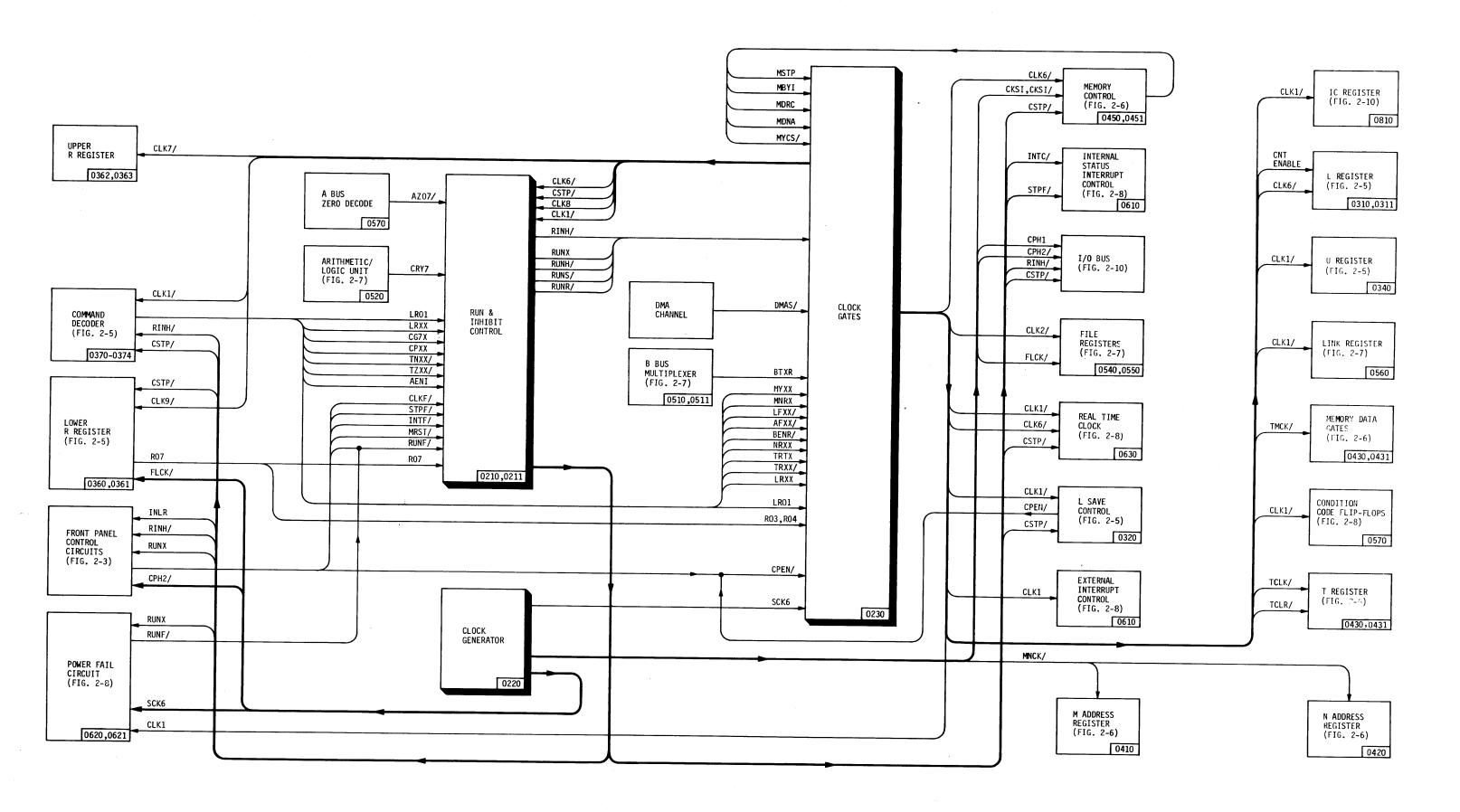

| 2.3.2      | Machine State Control and Clock Circuits             | 2-8  |

| 2.3.2.1    | Run and Inhibit Control                              | 2-8  |

| 2.3.2.2    | Clock Generator                                      | 2-8  |

| 2.3.2.3    | Clock Gates                                          | 2-8  |

| 2.3.3      | Control Unit                                         | 2-11 |

| 2.3.3.1    | Control Memory                                       | 2-11 |

| 2.3.3.2    | L Register                                           | 2-11 |

| 2.3.3.3    | L Save Register                                      | 2-11 |

| 2.3.3.4    | Upper and Lower R Registers                          | 2-11 |

| 2.3.3.5    | U Register                                           | 2-12 |

| 2.3.3.6    | Command Decoder                                      | 2-12 |

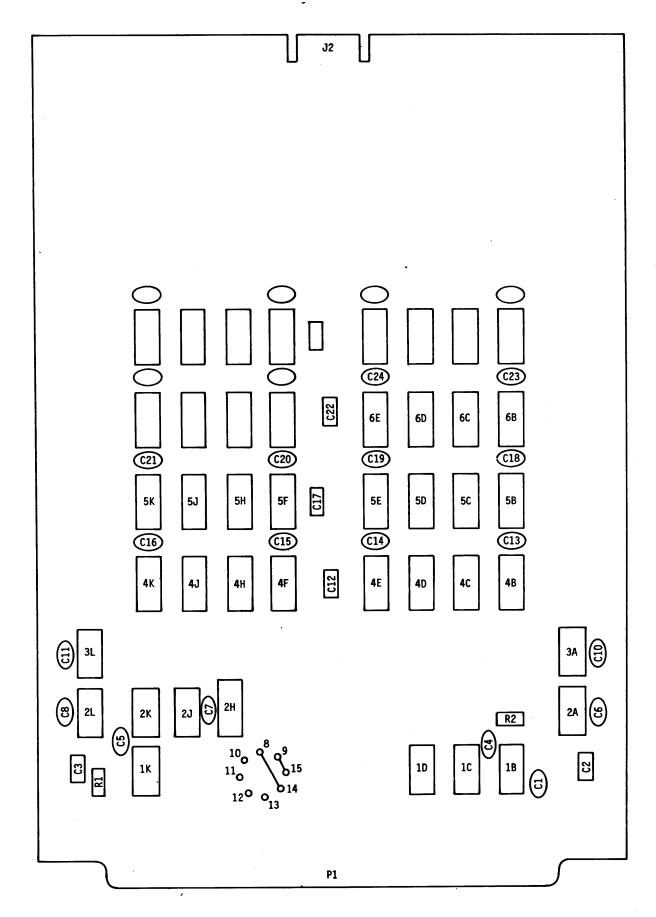

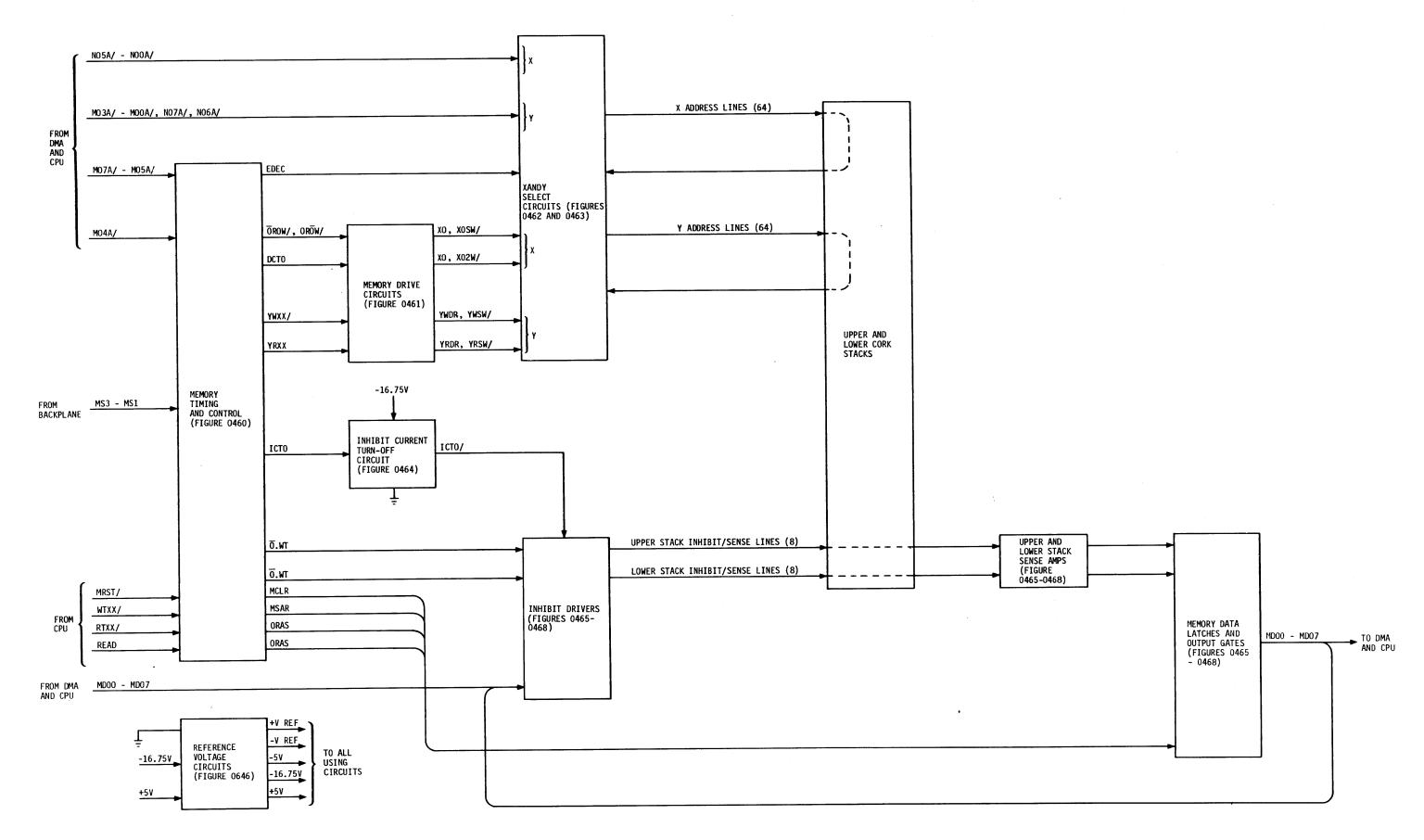

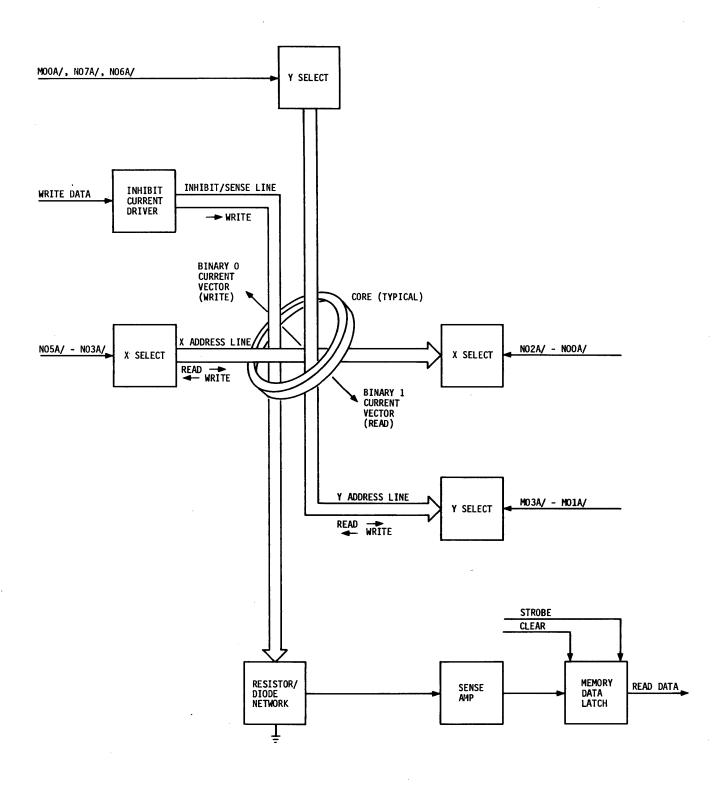

| 2.3.4      | Core Memory Section                                  | 2-12 |

| 2.3.4.1    | Core Memory                                          | 2-15 |

| 2.3.4.2    | Memory Control                                       | 2-15 |

| 2.3.4.3    | M and N Address Registers                            | 2-15 |

| 2.3.4.4    | Memory Data Gates                                    | 2-16 |

|            |                                     | Page   |

|------------|-------------------------------------|--------|

| SECTION 2. | CPU THEORY OF OPERATION (continued) |        |

| 2.3.4.5    | T Register                          | . 2-16 |

| 2.3.4.6    | Memory Data (MD) Register           |        |

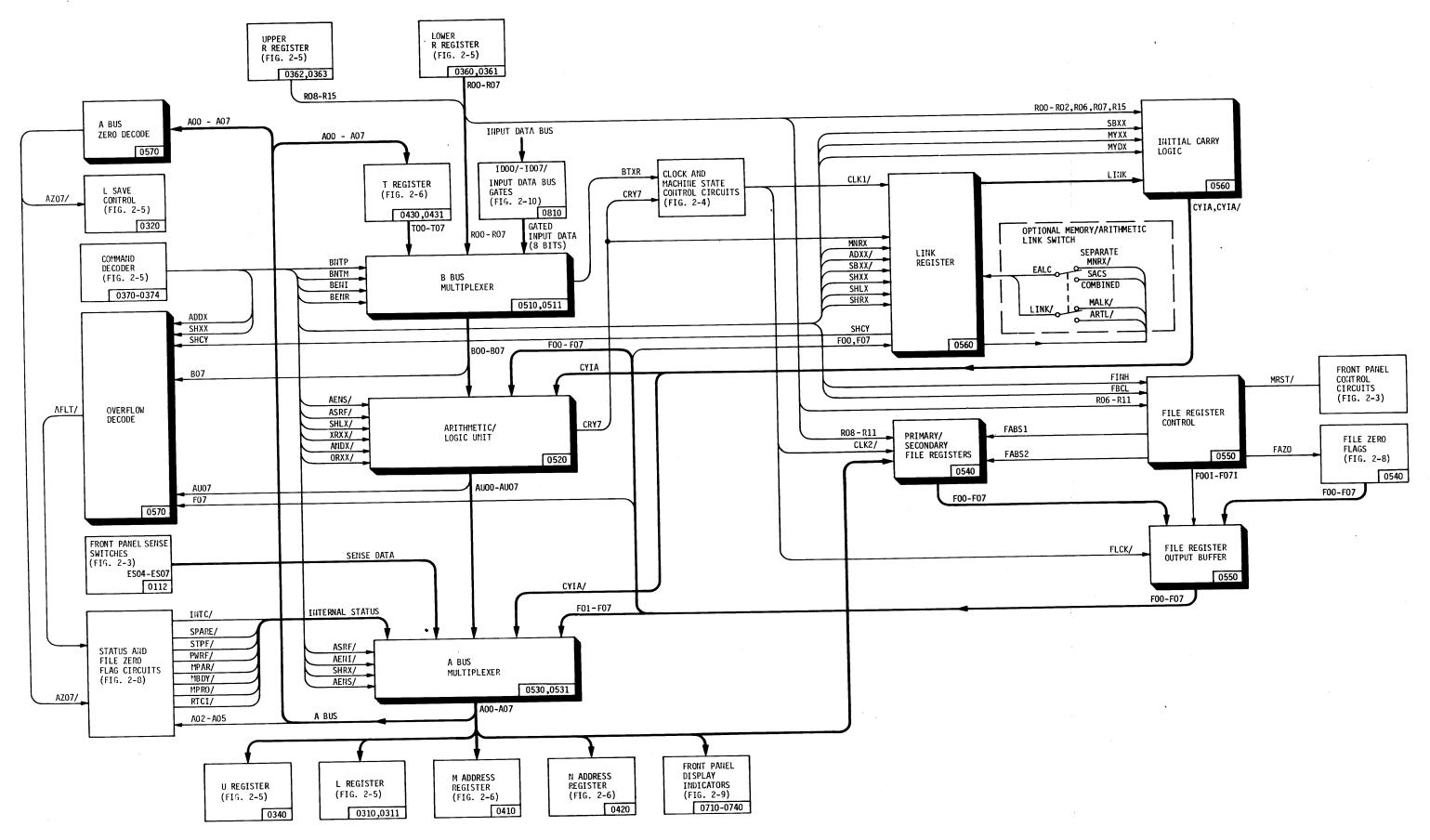

| 2.3.5      | Processor Section                   |        |

| 2.3.5.1    | B Bus Multiplexer                   |        |

| 2.3.5.2    | Arithmetic/Logic Circuits           |        |

| 2.3.5.3    | File Registers                      |        |

| 2.3.5.4    | A Bus Multiplexer                   |        |

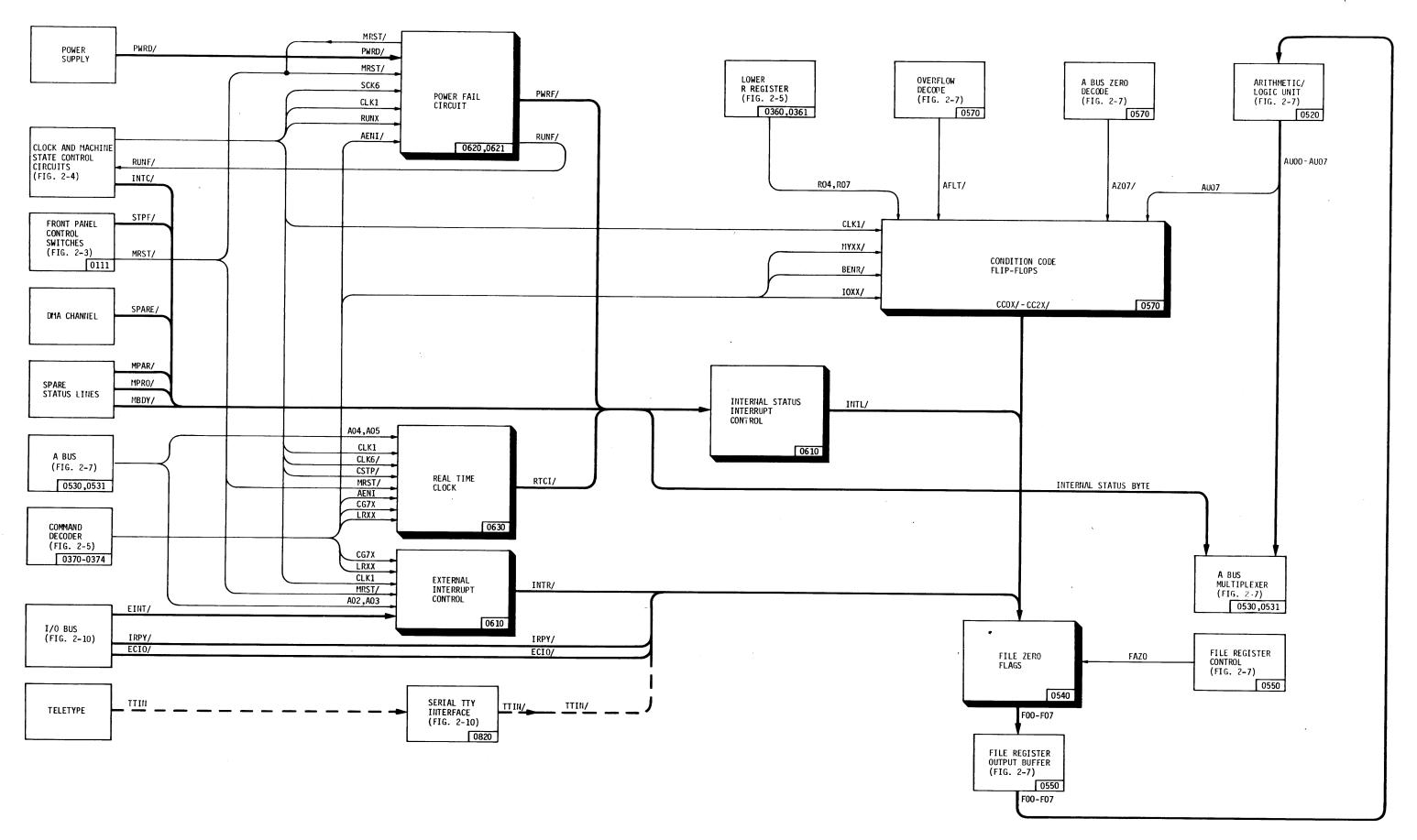

| 2.3.6      | Status and File Zero Flag Circuits  |        |

| 2.3.6.1    | Power-Fail Circuit                  |        |

| 2.3.6.2    | Real Time Clock                     |        |

| 2.3.6.3    | External Interrupt Control          |        |

| 2.3.6.4    | Internal Status Interrupt Control   |        |

| 2.3.6.5    | Condition Code Flip-Flops           |        |

| 2.3.6.6    | File Zero Flags                     |        |

| 2.3.7      | Front Panel Display Indicators      |        |

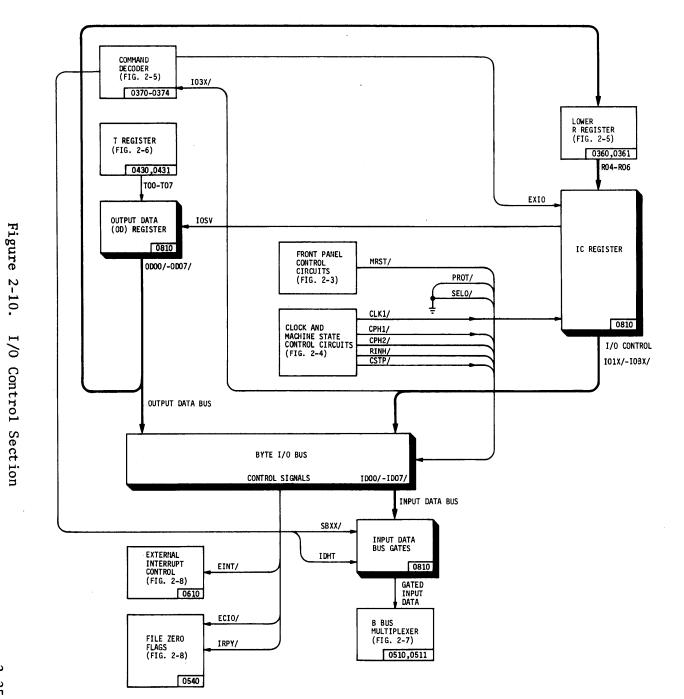

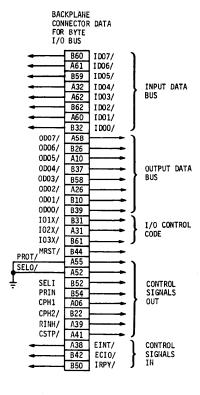

| 2.3.8      | I/O Control Section                 |        |

| 2.3.8.1    | Output Data (OD) Register           |        |

| 2.3.8.2    | I/O Control (IC) Register           |        |

| 2.3.8.3    | Input Data Bus                      |        |

| 2.4        | Data Flow Descriptions              |        |

| 2.4.1      | Control Unit Data Flow              |        |

| 2.4.2      | Core Memory Section Data Flow       |        |

| 2.4.3      | Processor Section                   |        |

| 2.4.4      | Status and File Zero Flag Data Flow |        |

| 2.4.4.1    | Internal Status Signal Data Flow    |        |

| 2.4.4.2    | File Zero Flag Data Flow            |        |

| 2.4.5      | Data Display Indicator Data Flow    |        |

| 2.4.6      | Byte I/O Bus Data Flow              |        |

| 2.5        | Command Decoding                    |        |

| 2.6        | CPU Timing Considerations           |        |

| 2.6.1      | Fetch/Execute Cycles                |        |

| 2.6.1.1    | Cycle Type I                        |        |

| 2.6.1.2    | Cycle Type II                       |        |

|            |                                                           | Page |

|------------|-----------------------------------------------------------|------|

| SECTION 2. | CPU THEORY OF OPERATION (continued)                       |      |

| 2.6.1.3    | Cycle Type III                                            | 2-45 |

| 2.6.1.4    | Cycle Type IV                                             | 2-45 |

| 2.6.1.5    | Cycle Type V                                              | 2-46 |

| 2.6.1.6    | Fetch/Execute Cycle for Operate-Type Commands That Select |      |

|            | the L Register                                            | 2-47 |

| 2.6.1.7    | Cycle Type VI                                             | 2-47 |

| 2.6.2      | Basic Clock Timing                                        | 2-48 |

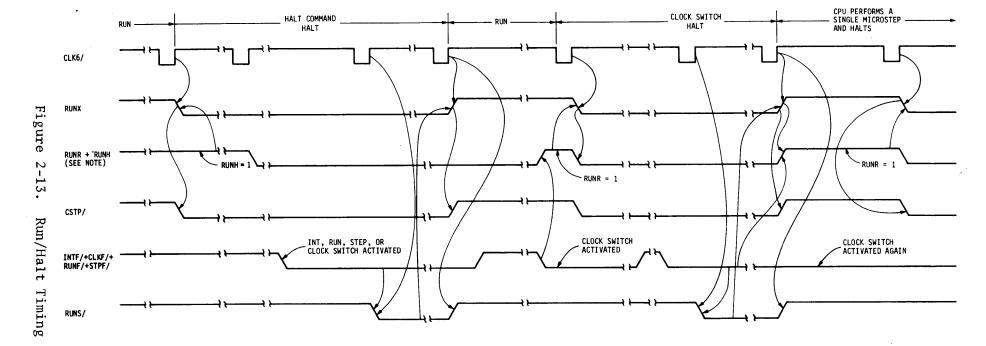

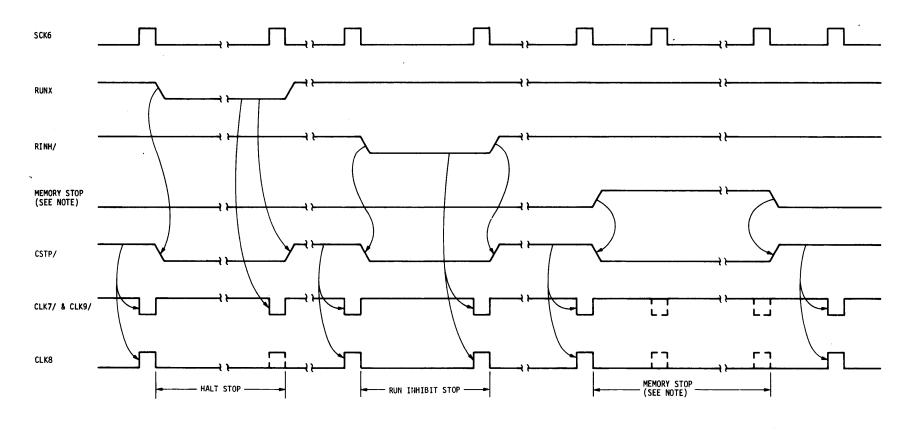

| 2.6.3      | Run/Halt Timing                                           | 2-49 |

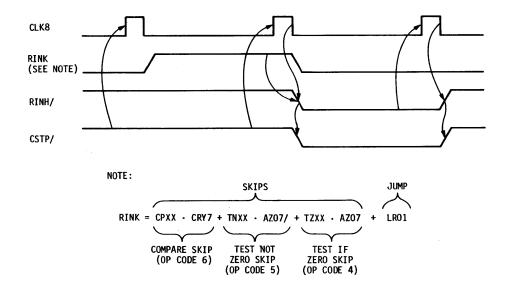

| 2.6.4      | Run Inhibit Timing                                        | 2-49 |

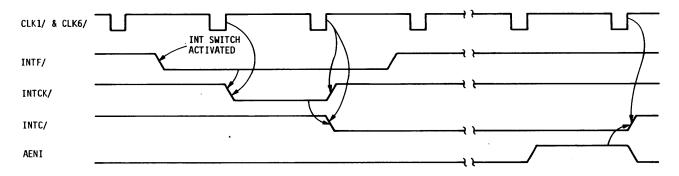

| 2.6.5      | Panel Interrupt Timing                                    | 2-49 |

| 2.6.6      | Clock Stop and Clock 7, 8, and 9 Timing                   | 2-49 |

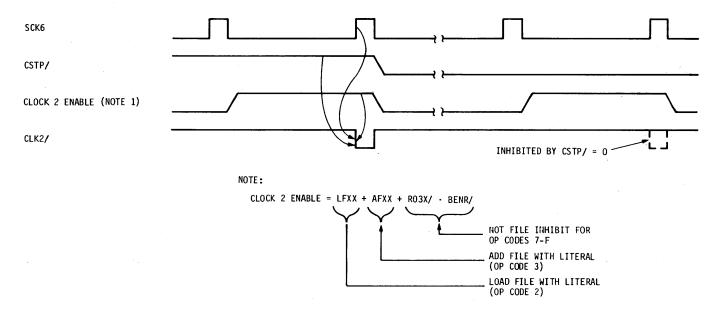

| 2.6.7      | Clock 2 Timing                                            | 2-53 |

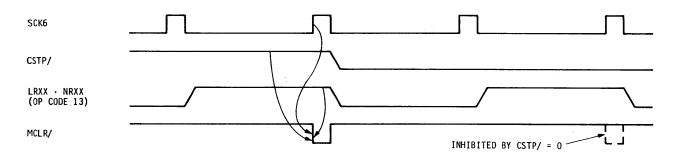

| 2.6.8      | M Register Clear Clock Timing                             | 2-53 |

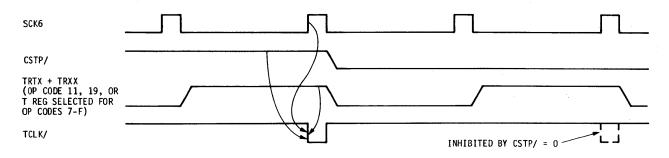

| 2.6.9      | T Register Load Clock Timing                              | 2-53 |

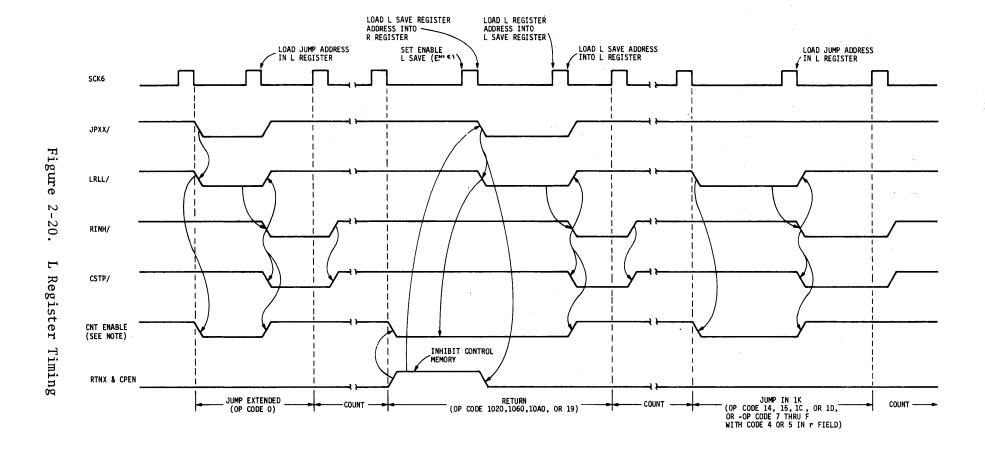

| 2.6.10     | L Register Timing                                         | 2-55 |

| 2.6.11     | Core Memory Read/Write Timing                             |      |

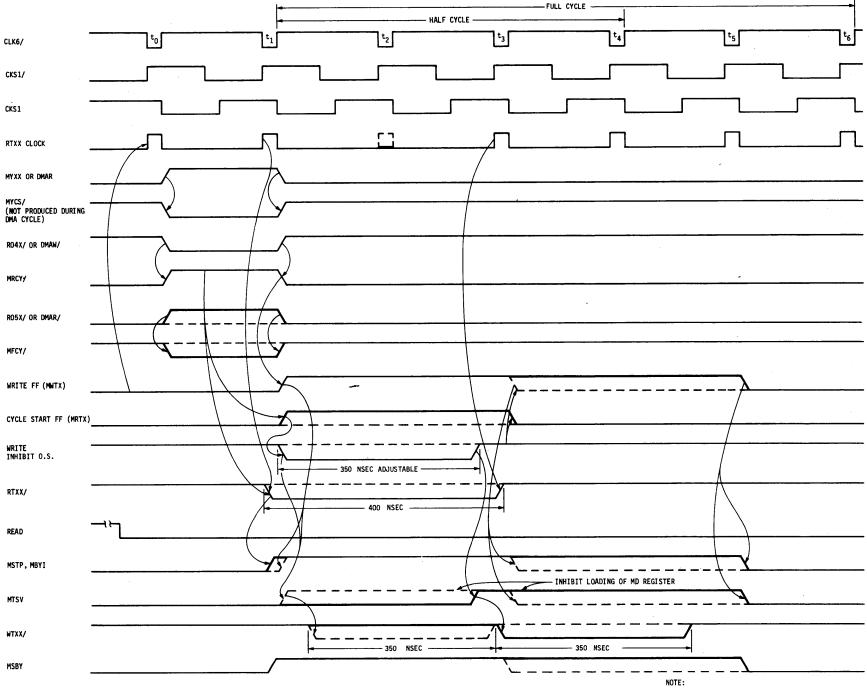

| 2.6.11.1   | Memory Write Cycle Timing                                 | 2-57 |

| 2.6.11.1.1 | Half-Cycle Memory Write                                   |      |

| 2.6.11.1.2 | Full-Cycle Memory Write                                   | 2-59 |

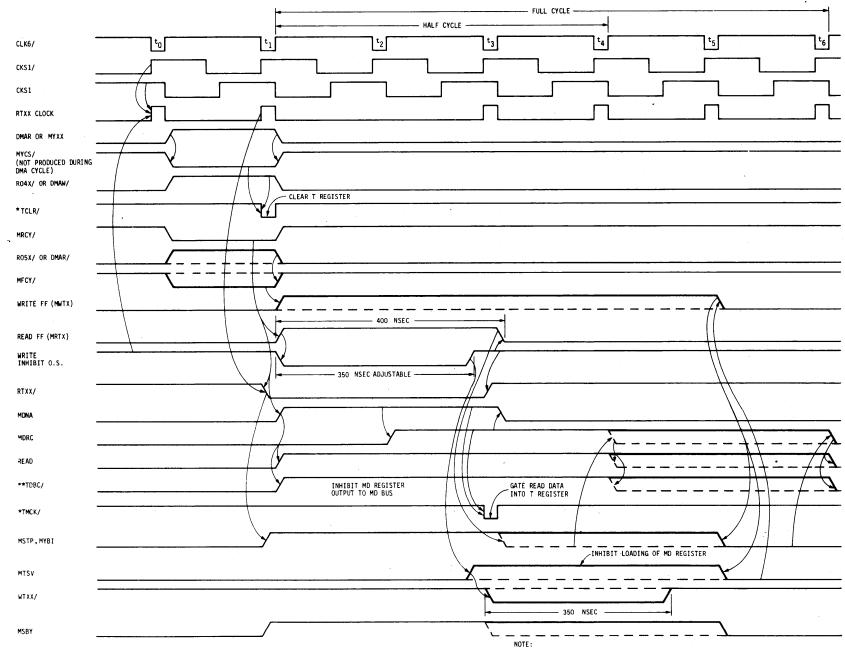

| 2.6.11.2   | Memory Read Cycle Timing                                  | 2-59 |

| 2.6.11.2.1 | Half-Cycle Memory Read                                    | 2-59 |

| 2.6.11.2.2 | Full-Cycle Memory Read                                    | 2-61 |

| 2.6.11.3   | Modified Timing for DMA Memory Cycles                     | 2-61 |

| 2.6.12     | Master Reset                                              | 2-62 |

| 2.7        | Logic Descriptions                                        | 2-63 |

| 2.7.1      | Front Panel Control Circuits                              | 2-63 |

| 2.7.1.1    | Control Switches and Control Display                      | 2-63 |

| 2.7.1.2    | Upper Data Switches and ADST/SCAN Display                 | 2-64 |

| 2.7.1.3    | Lower Data Switches                                       | 2-64 |

| 2.7.1.4    | L Address Comparator                                      | 2-64 |

| 2.7.1.5    | Address Stop Logic                                        | 2-64 |

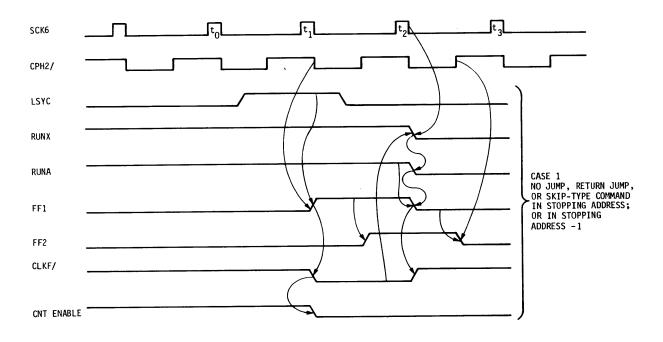

| 2.7.1.5.1  | Case 1                                                    | 2-65 |

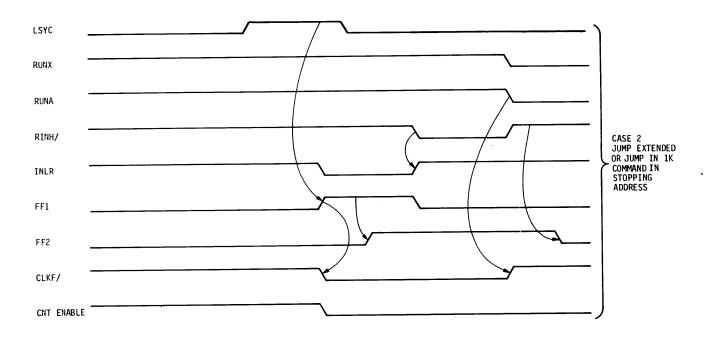

| 2.7.1.5.2  | Case 2                                                    | 2-67 |

|            |                                                           |      |

|            |                                          | Page |

|------------|------------------------------------------|------|

| SECTION 2. | CPU THEORY OF OPERATION (continued)      |      |

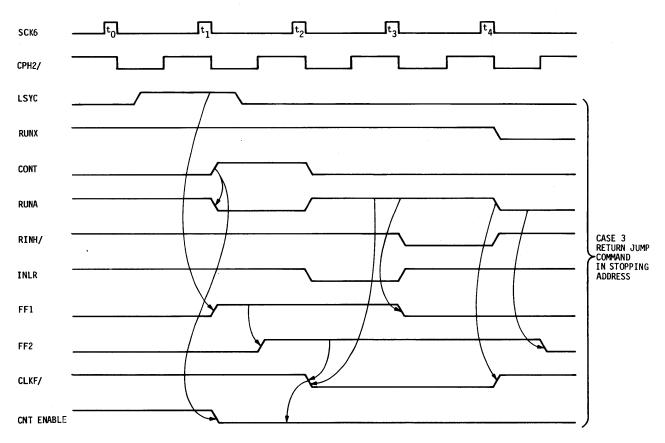

| 2.7.1.5.3  | Case 3                                   | 2-67 |

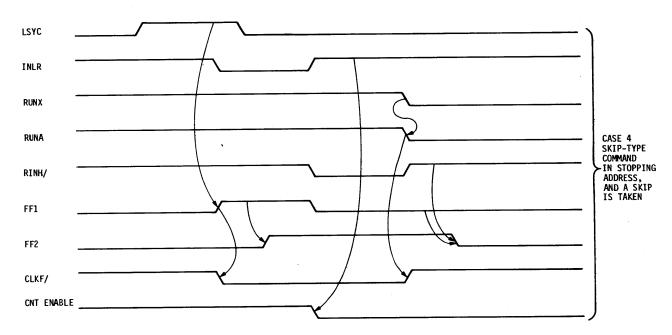

| 2.7.1.5.4  | Case 4                                   | 2-68 |

| 2.7.2      | Machine State Control and Clock Circuits | 2-68 |

| 2.7.2.1    | Run and Inhibit Control                  | 2-68 |

| 2.7.2.2    | Clock Generator                          | 2-69 |

| 2.7.2.3    | Clock Gates                              | 2-70 |

| 2.7.3      | Control Unit                             | 2-70 |

| 2.7.3.1    | L Register                               | 2-70 |

| 2.7.3.2    | L Save Register and L Save Control       | 2-71 |

| 2.7.3.3    | U Register                               | 2-71 |

| 2.7.3.4    | Lower R Register                         | 2-72 |

| 2.7.3.5    | Upper R Register and U Register Enable   | 2-72 |

| 2.7.3.6    | Command Decoder                          | 2-73 |

| 2.7.4      | Core Memory Section                      | 2-73 |

| 2.7.4.1    | M Register                               | 2-73 |

| 2.7.4.2    | N Register                               | 2-74 |

| 2.7.4.3    | Memory Control                           | 2-74 |

| 2.7.4.4    | Memory Data Gates                        | 2-74 |

| 2.7.4.5    | T Register                               | 2-74 |

| 2.7.4.6    | Memory Data (MD) Register                | 2-74 |

| 2.7.5      | Processor Section                        | 2-75 |

| 2.7.5.1    | B Bus Multiplexer                        | 2-75 |

| 2.7.5.2    | Arithmetic/Logic Unit                    | 2-75 |

| 2.7.5.3    | A Bus Multiplexer                        | 2-77 |

| 2.7.5.4    | File Register Control                    | 2-77 |

| 2.7.5.5    | Primary and Secondary File Registers     | 2-78 |

| 2.7.5.6    | File Register Output Buffer              | 2-78 |

| 2.7.5.7    | Link Register                            | 2-78 |

| 2.7.5.8    | Initial Carry Logic                      | 2-79 |

| 2.7.5.9    | A Bus Zero Decode                        | 2-80 |

| 2.7.5.10   | Overflow Decode                          | 2-80 |

| 2.7.6      | Status and File Zero Flag Circuits       | 2-80 |

| 2.7.6.1    | Power Fail Circuits                      | 2-80 |

| 2.7.6.2    | Real Time Clock                          | 2-82 |

|            |                                                   | Page |

|------------|---------------------------------------------------|------|

| SECTION 2. | CPU THEORY OF OPERATION (continued)               |      |

| 2.7.6.3    | Internal Status Interrupt Control                 | 2-83 |

| 2.7.6.4    | External Interrupt Control                        | 2-83 |

| 2.7.6.5    | Condition Code Flip-Flops                         | 2-83 |

| 2.7.6.6    | File Zero Flags                                   | 2-84 |

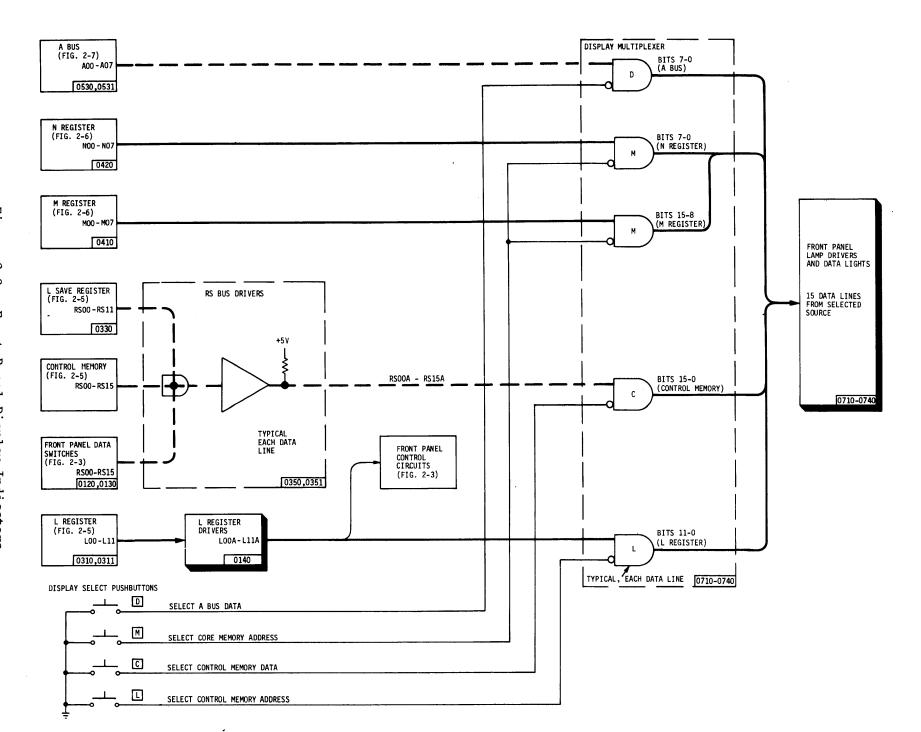

| 2.7.7      | Front Panel Display Indicators                    | 2-84 |

| 2.7.7.1    | RS Bus Drivers                                    | 2-84 |

| 2.7.7.2    | L Register Drivers                                | 2-84 |

| 2.7.7.3    | Display Multiplexer                               | 2-84 |

| 2.7.7.4    | Lamp Drivers and Data Lights                      | 2-84 |

| 2.7.8      | I/O Control Section                               | 2-85 |

| 2.7.8.1    | I/O Control (IC) Register                         | 2-85 |

| 2.7.8.2    | Output Data (OD) Register                         | 2-85 |

| 2.7.8.3    | Input Data Bus Gates                              | 2-85 |

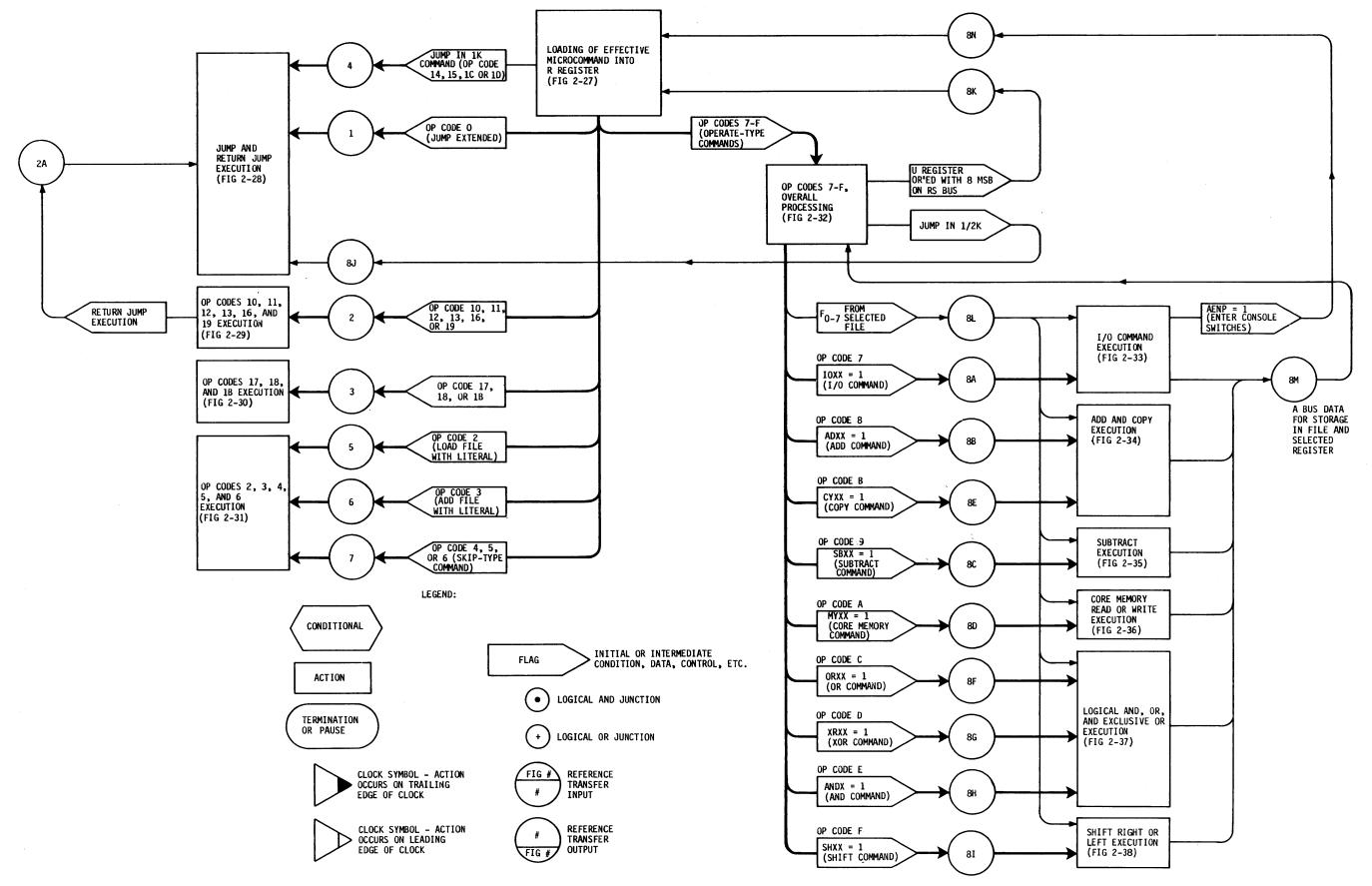

| 2.8        | Flow Diagram Descriptions                         | 2-86 |

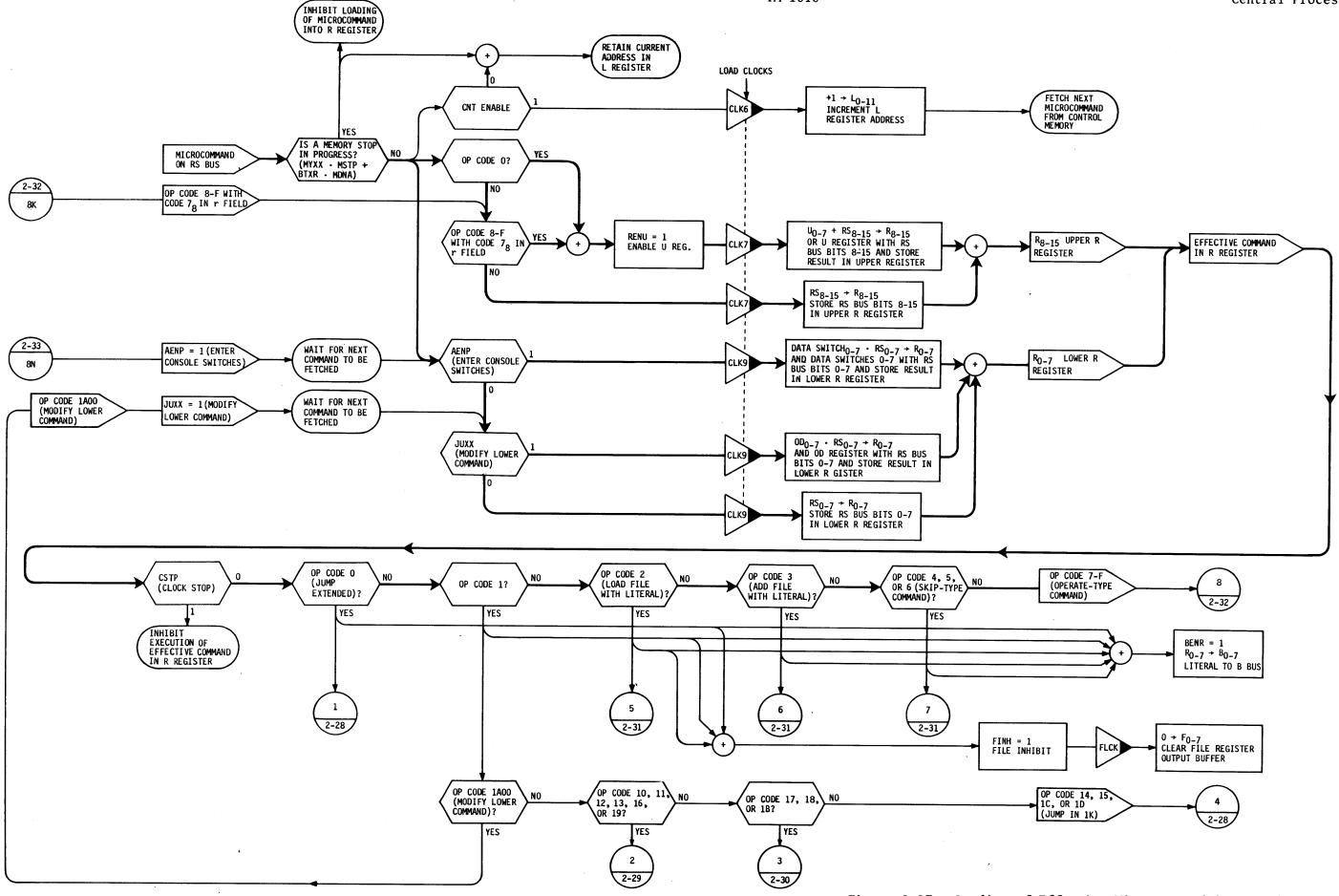

| 2.8.1      | Loading of Effective Microcommand Into R Register | 2-89 |

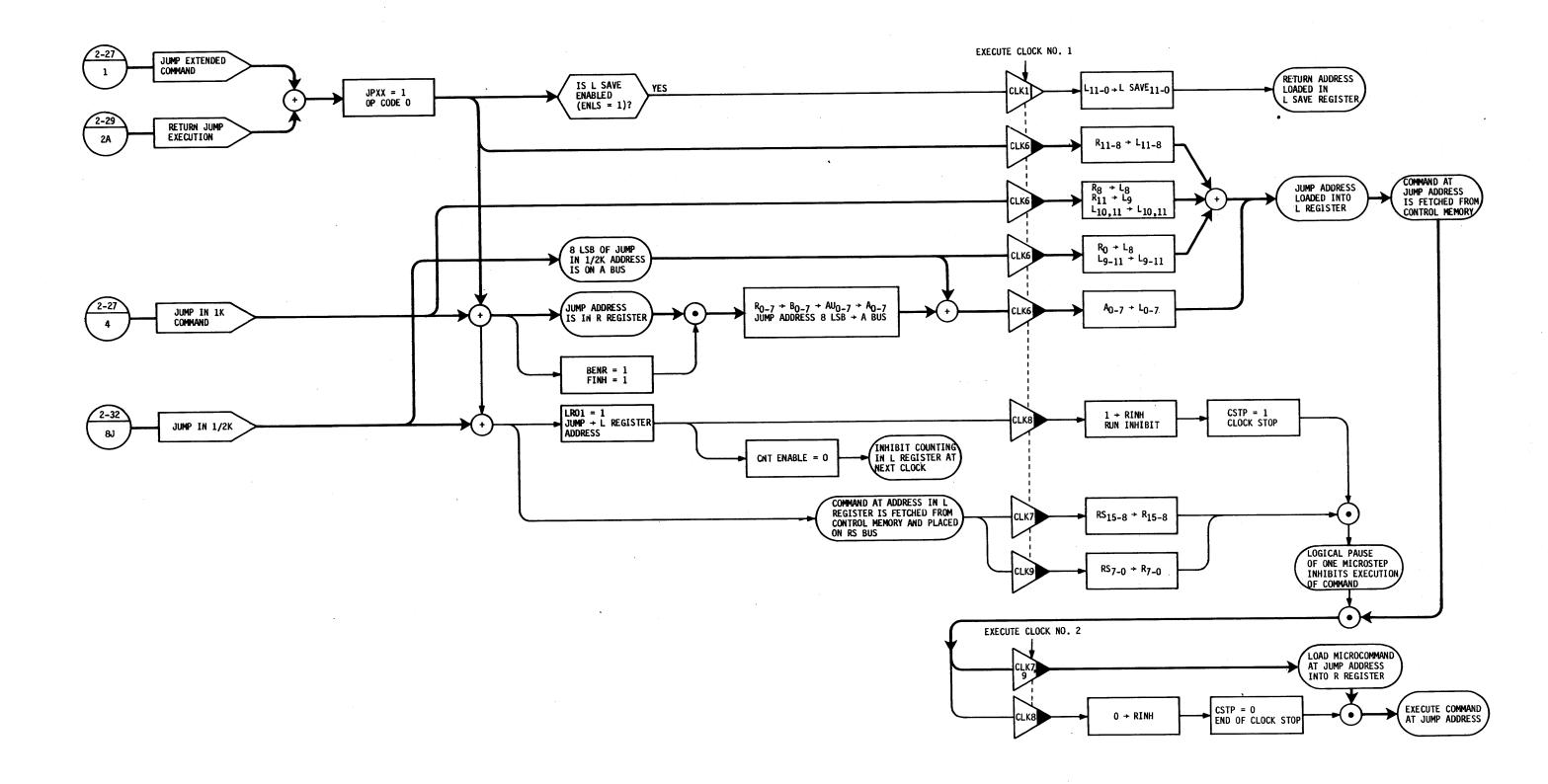

| 2.8.2      | Jump and Return Jump Execution                    | 2-90 |

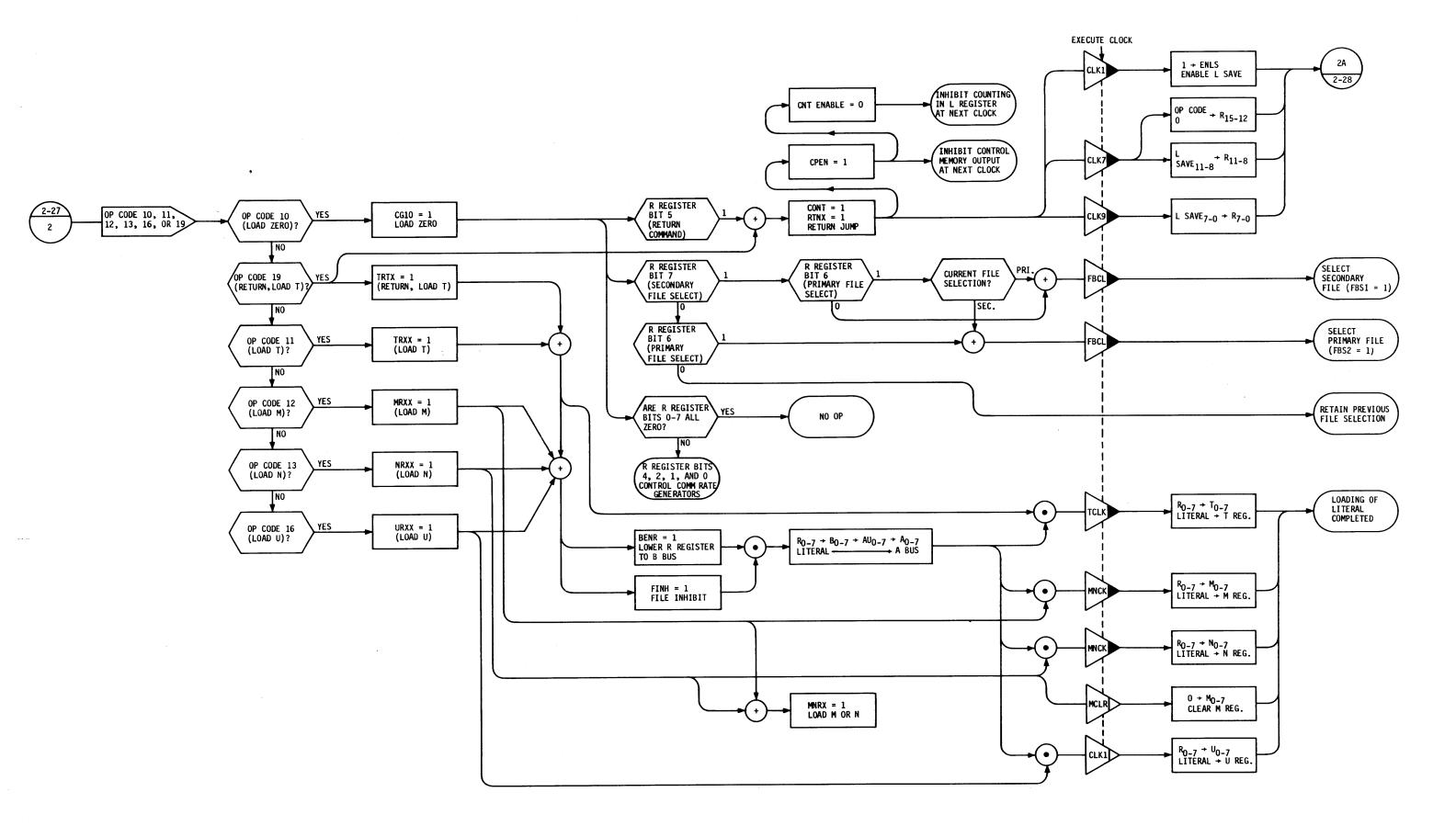

| 2.8.3      | Op Code 10, 11, 12, 13, 16 and 19 Execution       | 2-93 |

| 2.8.3.1    | Load Zero Command                                 | 2-93 |

| 2.8.3.2    | Return, Load T Command                            | 2-94 |

| 2.8.3.3    | Load T Command                                    | 2-94 |

| 2.8.3.4    | Load M Command                                    | 2-94 |

| 2.8.3.5    | Load N Command                                    | 2-94 |

| 2.8.3.6    | Load U Command                                    | 2-94 |

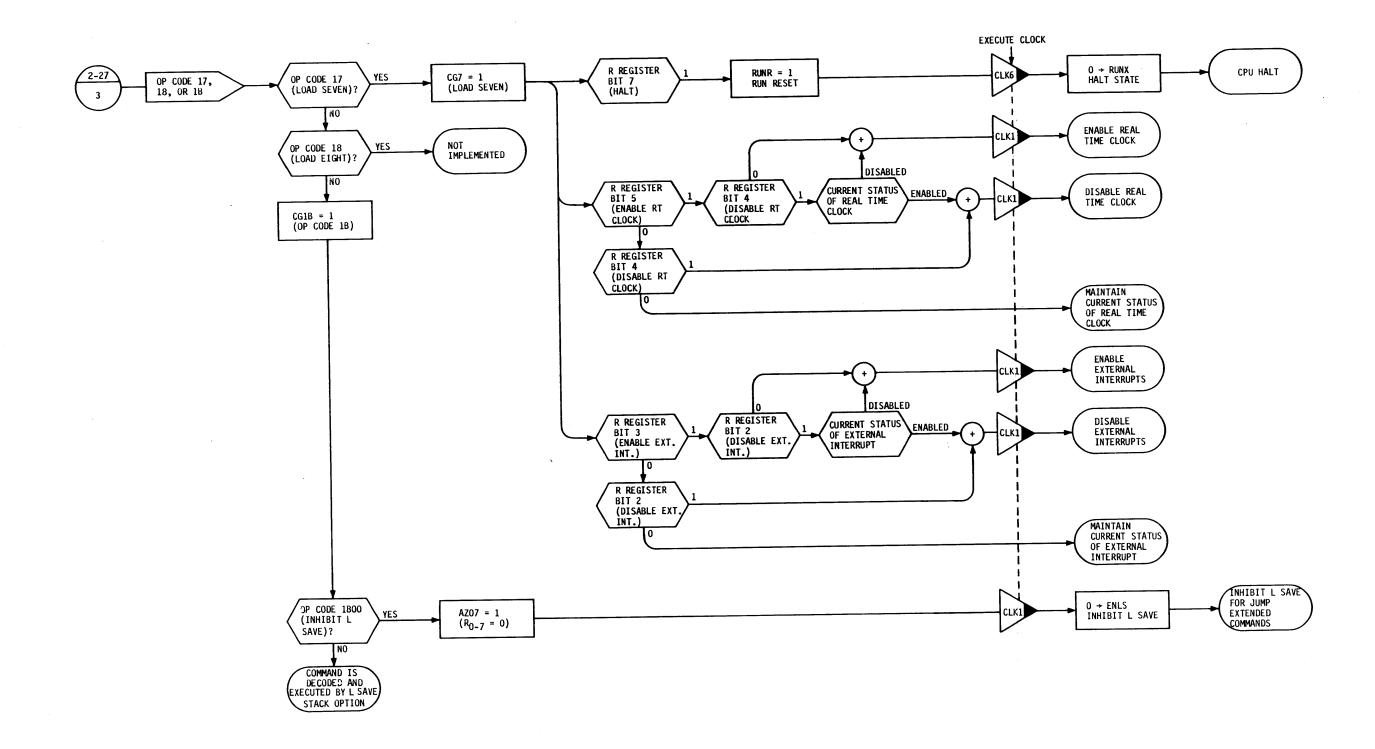

| 2.8.4      | Op Code 17, 18, and 1B Execution                  | 2-94 |

| 2.8.4.1    | Load Seven Command                                | 2-94 |

| 2.8.4.2    | Load Eight Command                                | 2-95 |

| 2.8.4.3    | L Save Commands                                   | 2-95 |

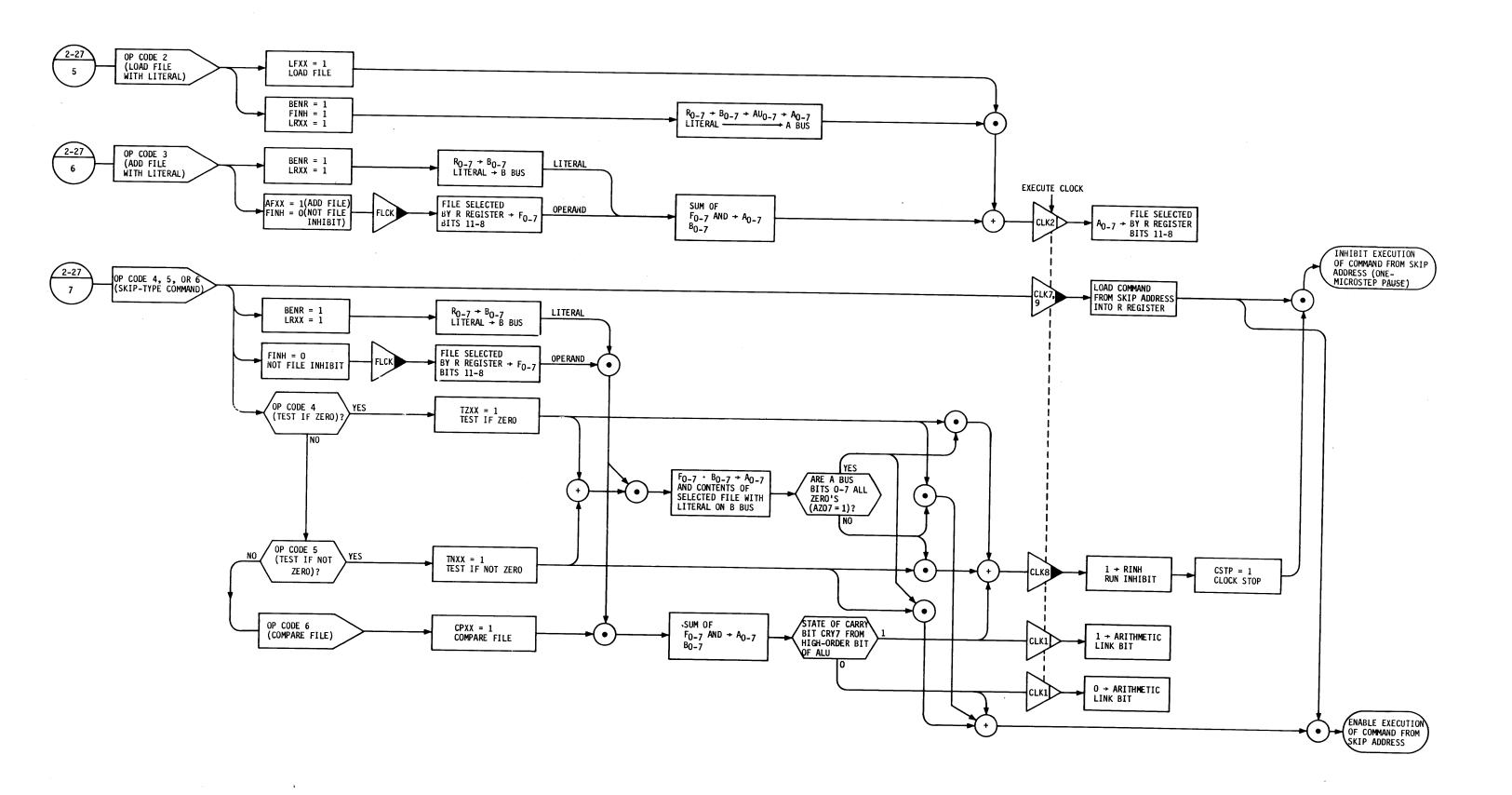

| 2.8.5      | Op Code 2, 3, 4, 5 and 6 Execution                | 2-95 |

| 2.8.5.1    | Load File Command                                 | 2-95 |

| 2.8.5.2    | Add File Command                                  | 2-96 |

| 2.8.5.3    | Test If Zero Command                              | 2-96 |

| 2.8.5.4    | Test If Not Zero Command                          | 2-96 |

| 2.8.5.5    | Compare File Command                              | 2-99 |

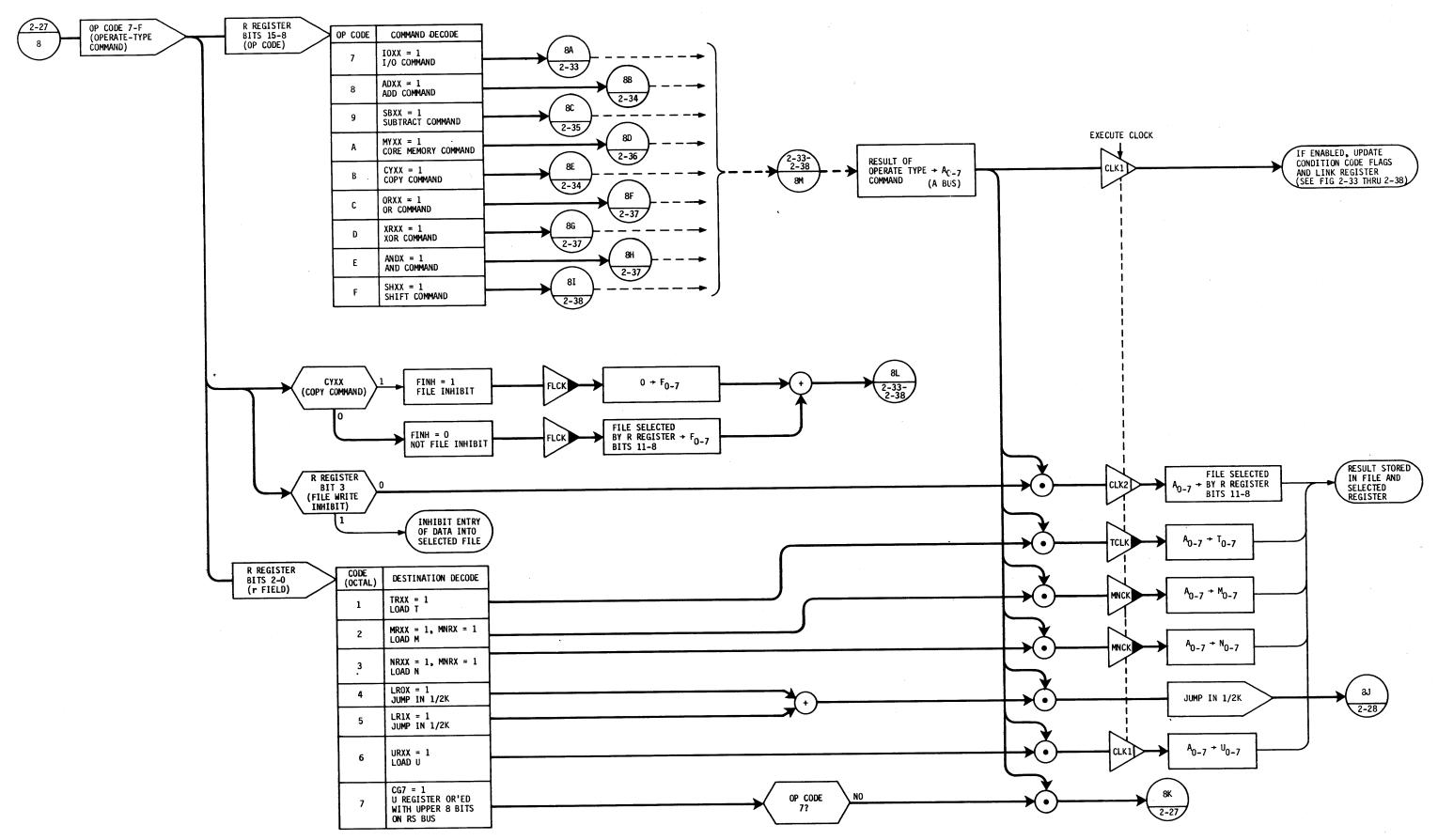

| 2.8.6      | Op Code 7 Through F Overall Processing            | 2-99 |

|            |                                                             | Page  |

|------------|-------------------------------------------------------------|-------|

| SECTION 2. | CPU THEORY OF OPERATION (continued)                         |       |

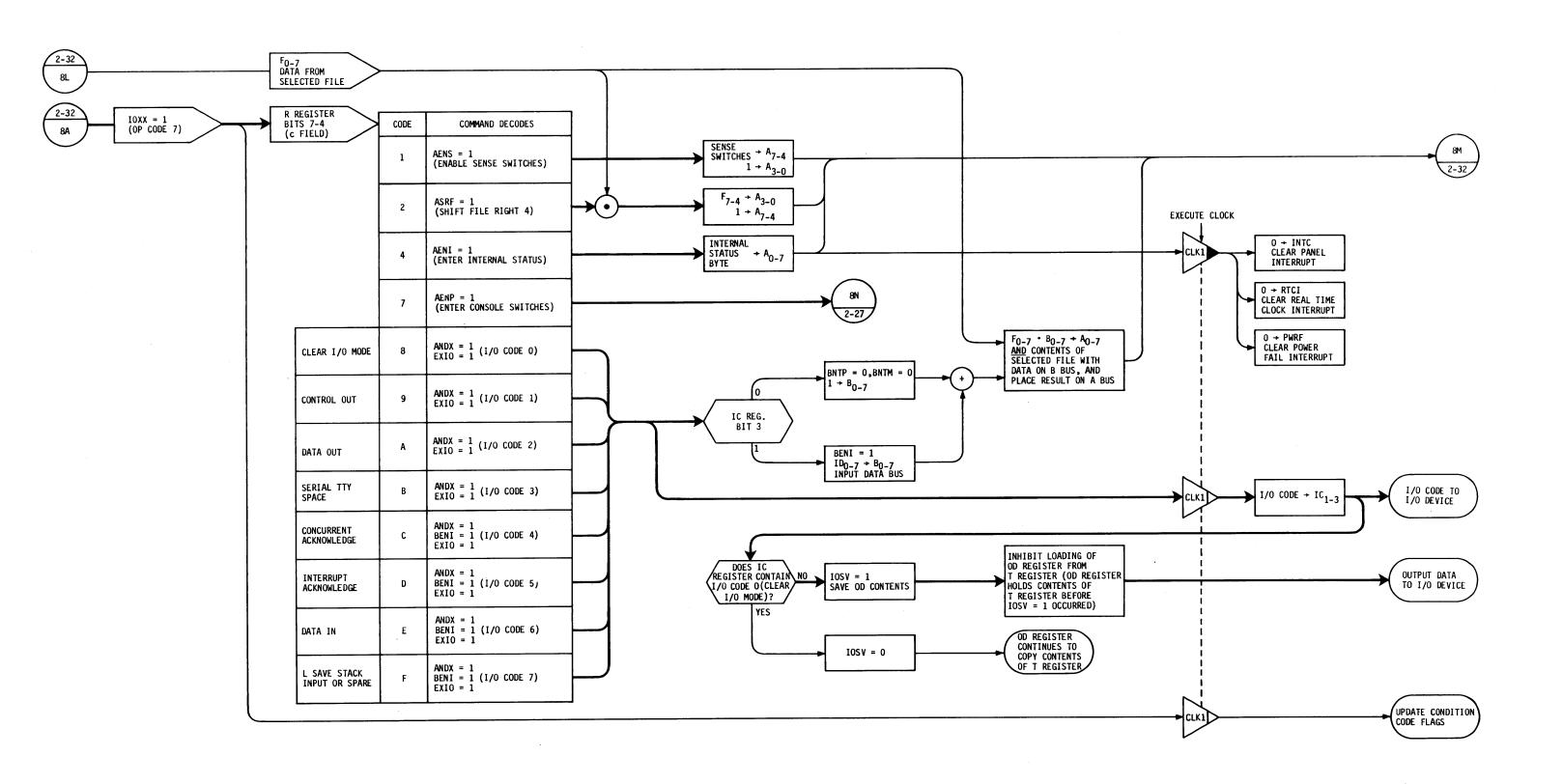

| 2.8.7      | I/O Command Execution                                       | 2-100 |

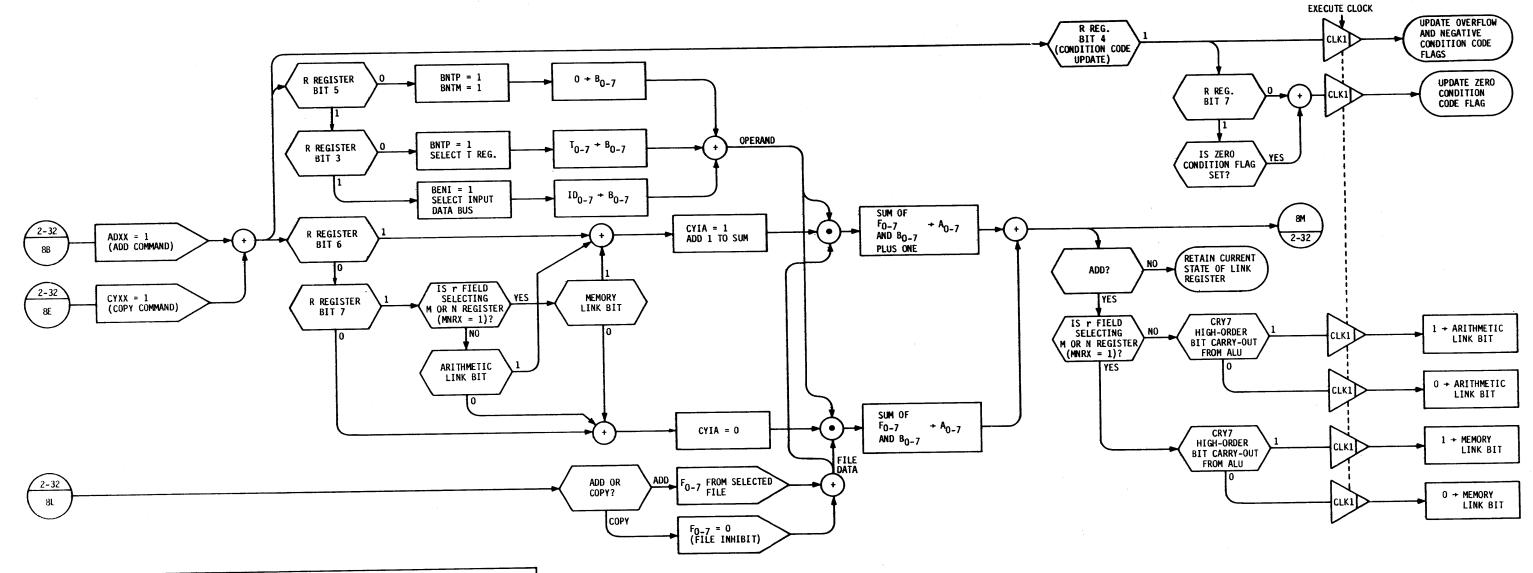

| 2.8.8      | Add and Copy Command Execution                              | 2-103 |

| 2.8.8.1    | Initial Carry                                               | 2-104 |

| 2.8.8.2    | Selection of B Bus Operand                                  | 2-104 |

| 2.8.8.3    | Condition Code Updating                                     | 2-104 |

| 2.8.8.4    | Link Register Updating                                      | 2-104 |

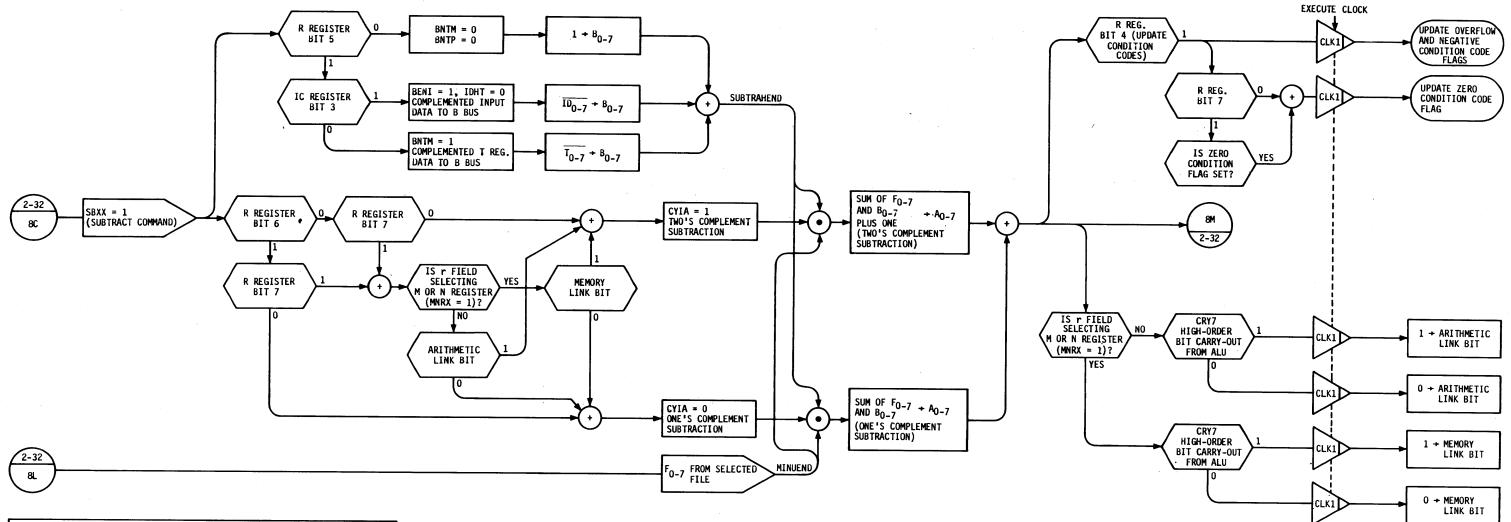

| 2.8.9      | Subtract Command Execution                                  | 2-107 |

| 2.8.9.1    | Initial Carry                                               | 2-107 |

| 2.8.9.2    | Selection of Operand on B Bus                               | 2-107 |

| 2.8.9.3    | Condition Code Updating                                     | 2-107 |

| 2.8.9.4    | Link Register Updating                                      | 2-107 |

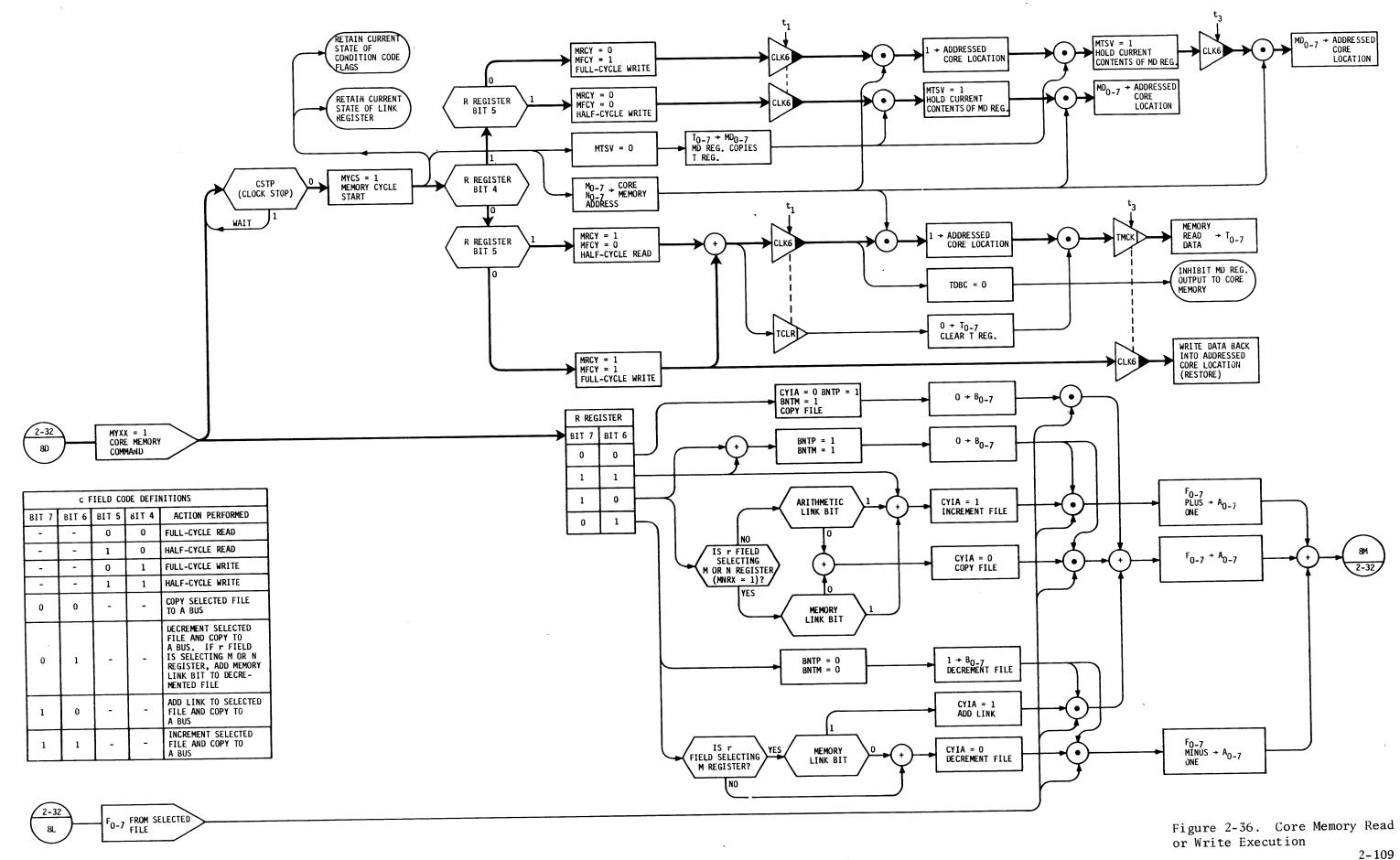

| 2.8.10     | Core Memory Read or Write Execution                         | 2-108 |

| 2.8.10.1   | Half-Cycle Memory Write                                     | 2-108 |

| 2.8.10.2   | Full-Cycle Memory Write                                     | 2-108 |

| 2.8.10.3   | Half-Cycle Memory Read                                      | 2-108 |

| 2.8.10.4   | Full-Cycle Memory Read                                      | 2-108 |

| 2.8.10.5   | Operations on Selected File                                 | 2-111 |

| 2.8.10.6   | Updating of Condition Codes and Link Register               | 2-111 |

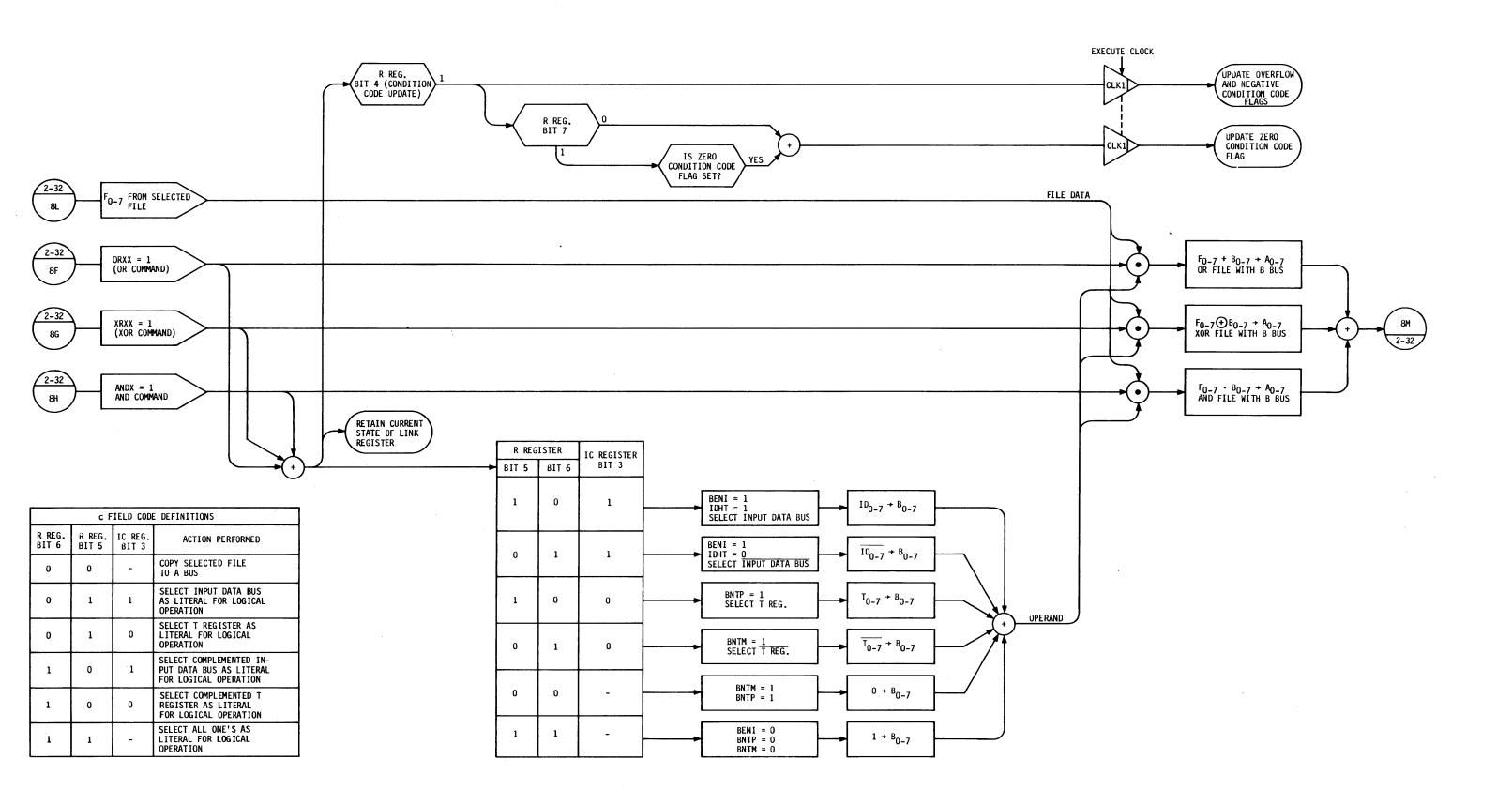

| 2.8.11     | Logical AND, OR, and Exclusive OR Command Execution         | 2-111 |

| 2.8.11.1   | Selection of Operand on B Bus                               | 2-111 |

| 2.8.11.2   | Updating of Condition Codes                                 | 2-112 |

| 2.8.11.3   | Updating of Link Register                                   | 2-112 |

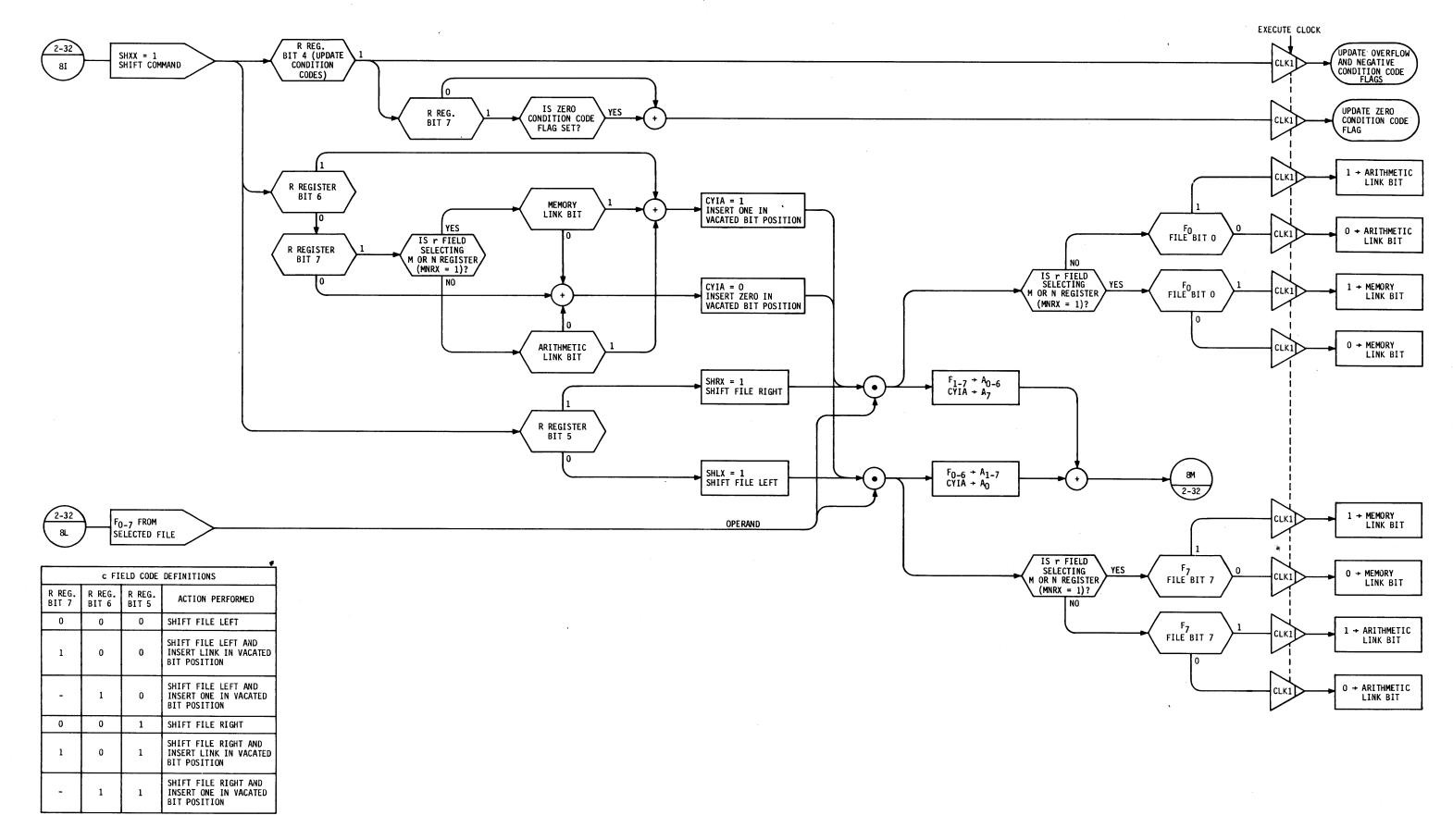

| 2.8.12     | Shift Right or Left Command Execution                       | 2-112 |

| 2.8.12.1   | Initial Carry                                               | 2-112 |

| 2.8.12.2   | Condition Code Updating                                     | 2-112 |

| 2.8.12.3   | Link Register Updating                                      | 2-115 |

|            |                                                             |       |

| SECTION 3. | OPERATION                                                   |       |

| 3.1        | Introduction                                                | 3-1   |

| 3.2        | Front Panel Controls and Indicators                         | 3-1   |

| 3.3        | Purposes and Capabilities of Front Panel Modes of Operation | 3-1   |

| 3.3.1      | Panel Mode                                                  | 3-1   |

| 3.3.2      | Scan Mode                                                   | 3-4   |

|            |                                                            | Page |

|------------|------------------------------------------------------------|------|

| SECTION 3. | OPERATION (continued)                                      |      |

| 3.3.3      | Address Stop Mode                                          | 3-5  |

| 3.3.4      | Combined Scan and Address Stop Mode                        | 3-6  |

| 3.3.5      | Step Mode                                                  | 3-7  |

| 3.3.6      | Panel Interrupt Mode                                       | 3-7  |

| 3.3.7      | Panel Locked-Out Mode                                      | 3-8  |

| 3.4        | Data Entry and Display Capabilities                        | 3-8  |

| 3.4.1      | Enter and Display M Register Data                          | 3-9  |

| 3.4.2      | Enter and Display N Register Data                          | 3-10 |

| 3.4.3      | Enter and Display L Register Data                          | 3-10 |

| 3.4.4      | Enter and Display U Register Data                          | 3-11 |

| 3.4.5      | Enter and Display T Register Data                          | 3-11 |

| 3.4.6      | Enter and Display File Register Data                       | 3-12 |

| 3.4.7      | Enter and Display Output Data (OD) Register Data           | 3-13 |

| 3.4.8      | Enter and Display Internal Status Data                     | 3-13 |

| 3.4.9      | Enter and Display File Zero Flag Data                      | 3-14 |

| 3.4.10     | Enter and Display Sense Switch Data                        | 3-15 |

| 3.4.11     | Enter and Display Memory Link Bit                          | 3-15 |

| 3.4.12     | Enter and Display Arithmetic Link Bit                      | 3-16 |

| 3.4.13     | Enter and Display Core Memory Data (Single Location)       | 3-17 |

| 3.4.14     | Accessing Consecutive Core Memory Locations for Data Entry |      |

|            | and Display                                                | 3-18 |

| 3.4.15     | Enter and Display L Save Register Data                     | 3-20 |

| 3.4.16     | Enter and Display Lower R Register Data                    | 3-21 |

| 3.5        | Execution and Display of Literal-Type Arithmetic and Logic |      |

|            | Operations                                                 | 3-21 |

| 3.6        | Execution and Display of Operate-Type Arithmetic and Logic |      |

|            | Operations                                                 | 3-23 |

| 3.7        | Entry of Microcommands via the U and OD Registers          | 3-24 |

| SECTION 4. | MAINTENANCE                                                |      |

| 4.1        | Introduction                                               | 4-1  |

| 4.2        | Checking Command Decodes                                   | 4-1  |

| 4.3        | Checking Core Memory Timing                                | 4-2  |

|            |                                                            |      |

|                    |                                             | Page            |

|--------------------|---------------------------------------------|-----------------|

| SECTION 4.         | MAINTENANCE (continued)                     |                 |

| 4.4                | Dynamic Checks of Command Execution         | .4-2            |

| 4.5                | Clock Checks                                | .4-3            |

| 4.6                | L Register Timing Checks                    | .4-3            |

| 4.7                | Machine State Control Timing Checks         | .4-3            |

| 4.8                | Data Checks                                 | .4-3            |

| 4.9                | Control Memory Checks                       | .4-3            |

| 4.10               | Register Checks                             | .4-4            |

| 4.11               | Checking Arithmetic and Logic Operations    | .4-4            |

| 4.12               | Checking I/O Devices and Controllers        | .4-4            |

| 4.13               | Troubleshooting                             | .4-4            |

| 4.14               | Preventive Maintenance                      | .4-5            |

| 4.15               | Marginal Voltage Checking                   | .4-5            |

| 4.16               | Adjustments                                 | .4-7            |

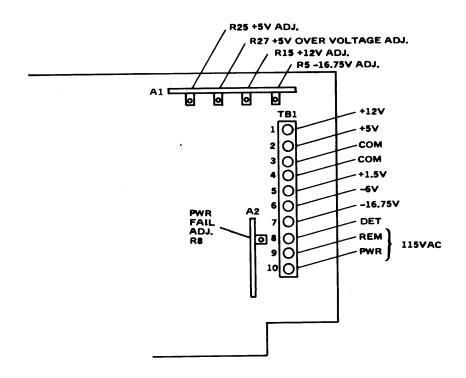

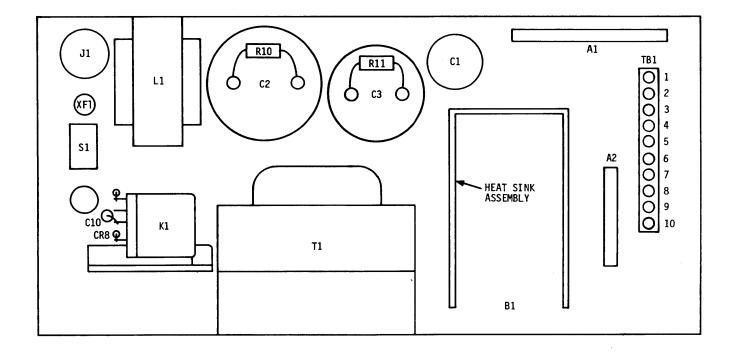

| 4.16.1             | Power Supply Adjustments                    | .4-7            |

| 4.16.2             | Write Inhibit One-Shot Adjustment           | .4-8            |

| SECTION 5.         | PARTS LIST                                  |                 |

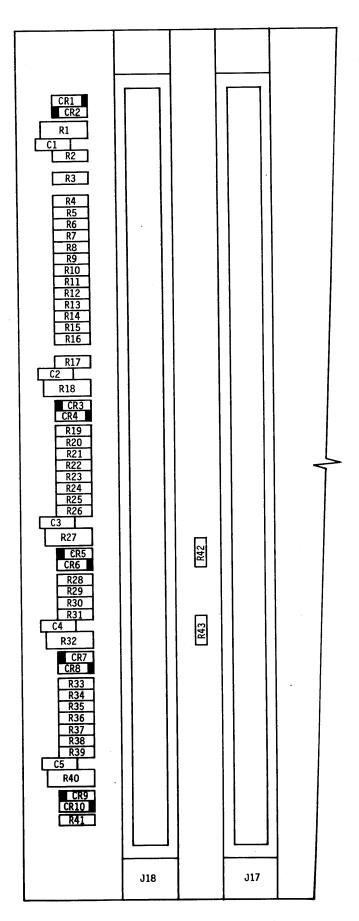

| 5.1                | General                                     | 5-1             |

| 5.2                | System Panel P. C. Card Parts List          | 5-2             |

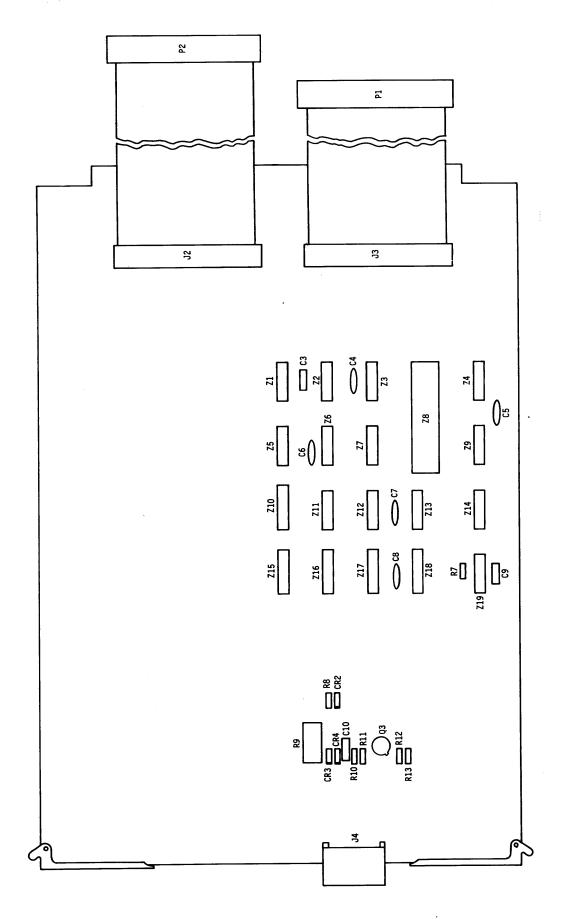

| 5.3                | Backplane Assembly Parts List               | 5-4             |

| 5.4                | Interface Card With Integral TTY Parts List | 5-6             |

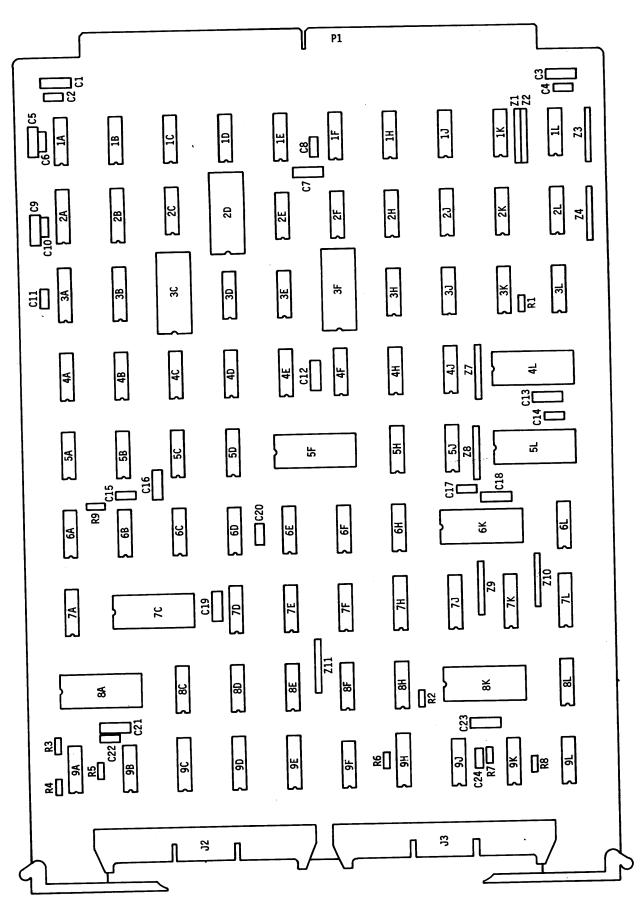

| 5.5                | Data Card Parts List                        | 5-8             |

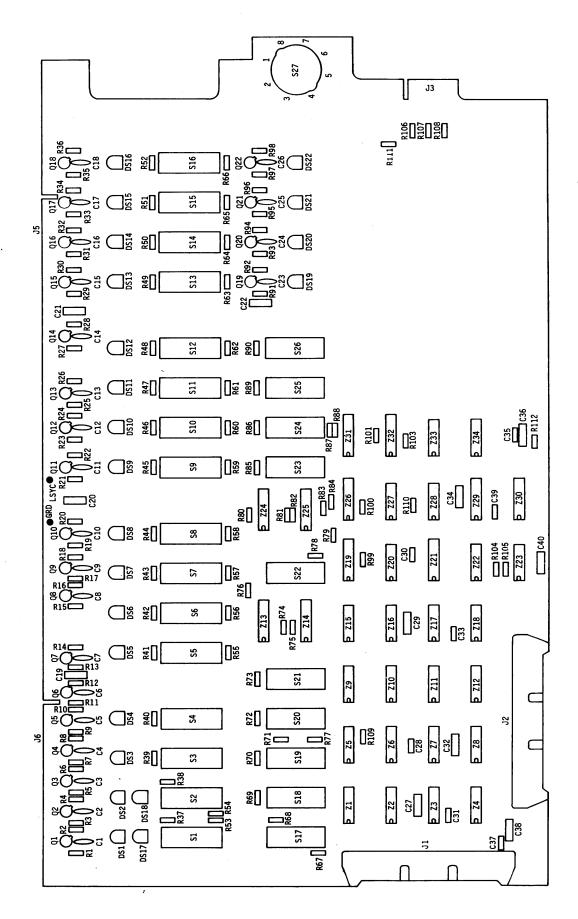

| 5.6                | Read Only Memory Card Parts List            | 5-10            |

| 5.7                | Control Card Parts List                     | 5-12            |

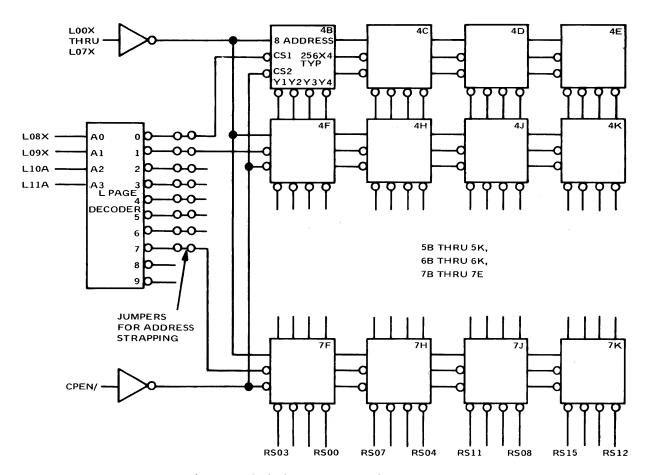

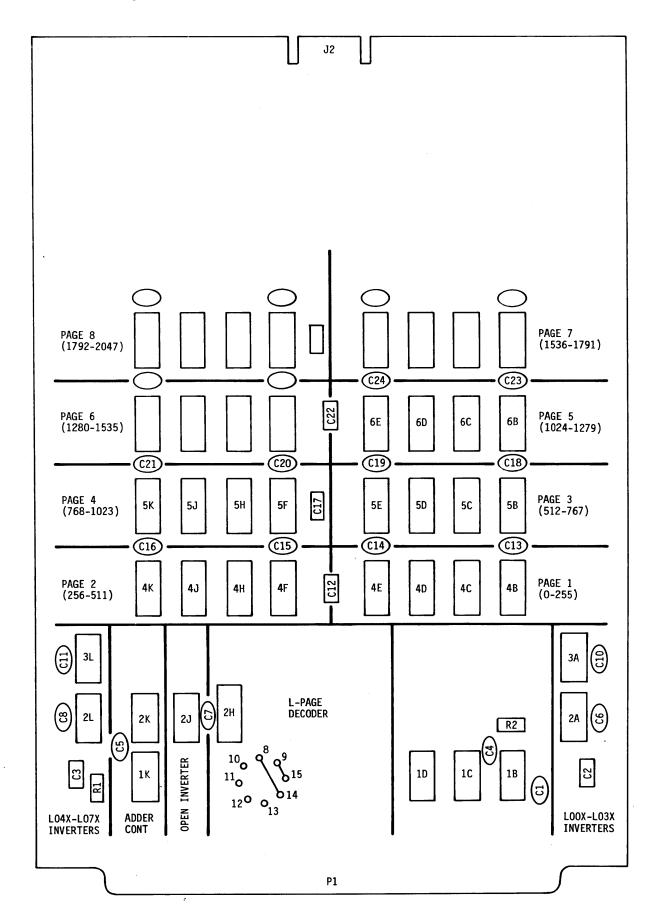

| 5.8                | 8K Memory Card Parts List                   | 5-15            |

| 5.9                | Power Supply (Later Model) Parts List       | 5-18            |

| 5.9.1              | Power Supply (Later Model) Parts List       | 5-19.1          |

| 5.10               | Regulator Board Parts List                  | 5-20            |

| 5.11               | Failure Detection Board Parts List          | 5-22            |

| <b>ZÁBAKÉWÉW</b> Á | \#\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\      | /\$¥ <i>+</i> ¥ |

| SUPPLEMENT         | 2. READ ONLY MEMORY                         | S2-i            |

| CHIDDI EMENIT      | Z QV MEMODY MODILLE                         | S3-i            |

|            | Page                                                                      |

|------------|---------------------------------------------------------------------------|

| SUPPLEMENT | 4. REMOTE POWER SUPPLY                                                    |

| SAAAKKWKWA | 3                                                                         |

| SUPPLEMENT | 6. LOCAL/REMOTE SINGLE CHANNEL CONTROLLER                                 |

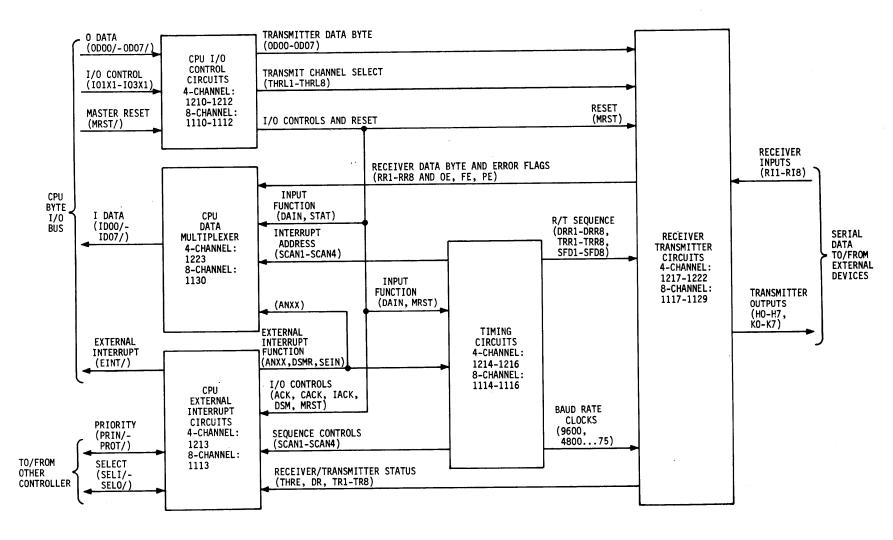

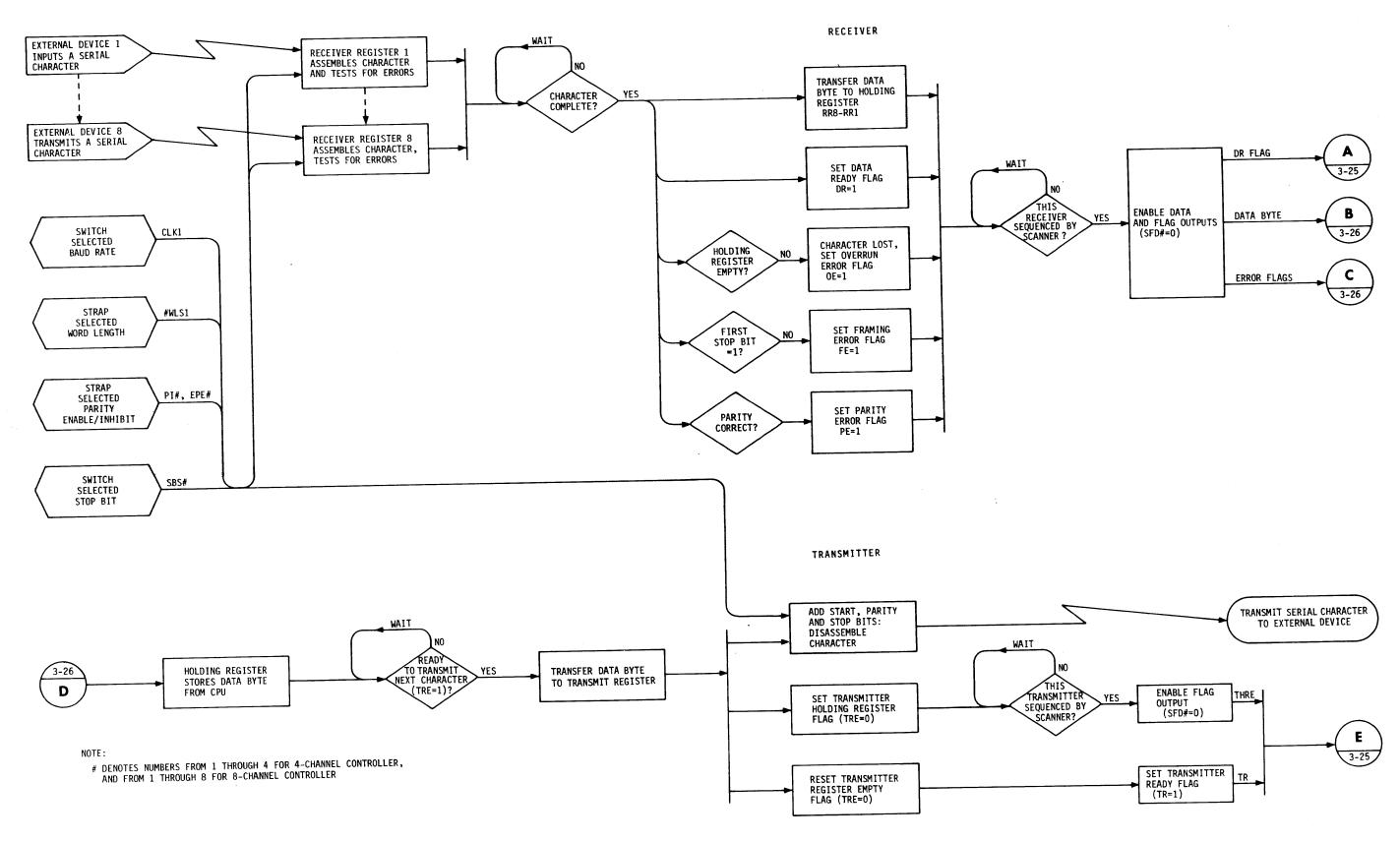

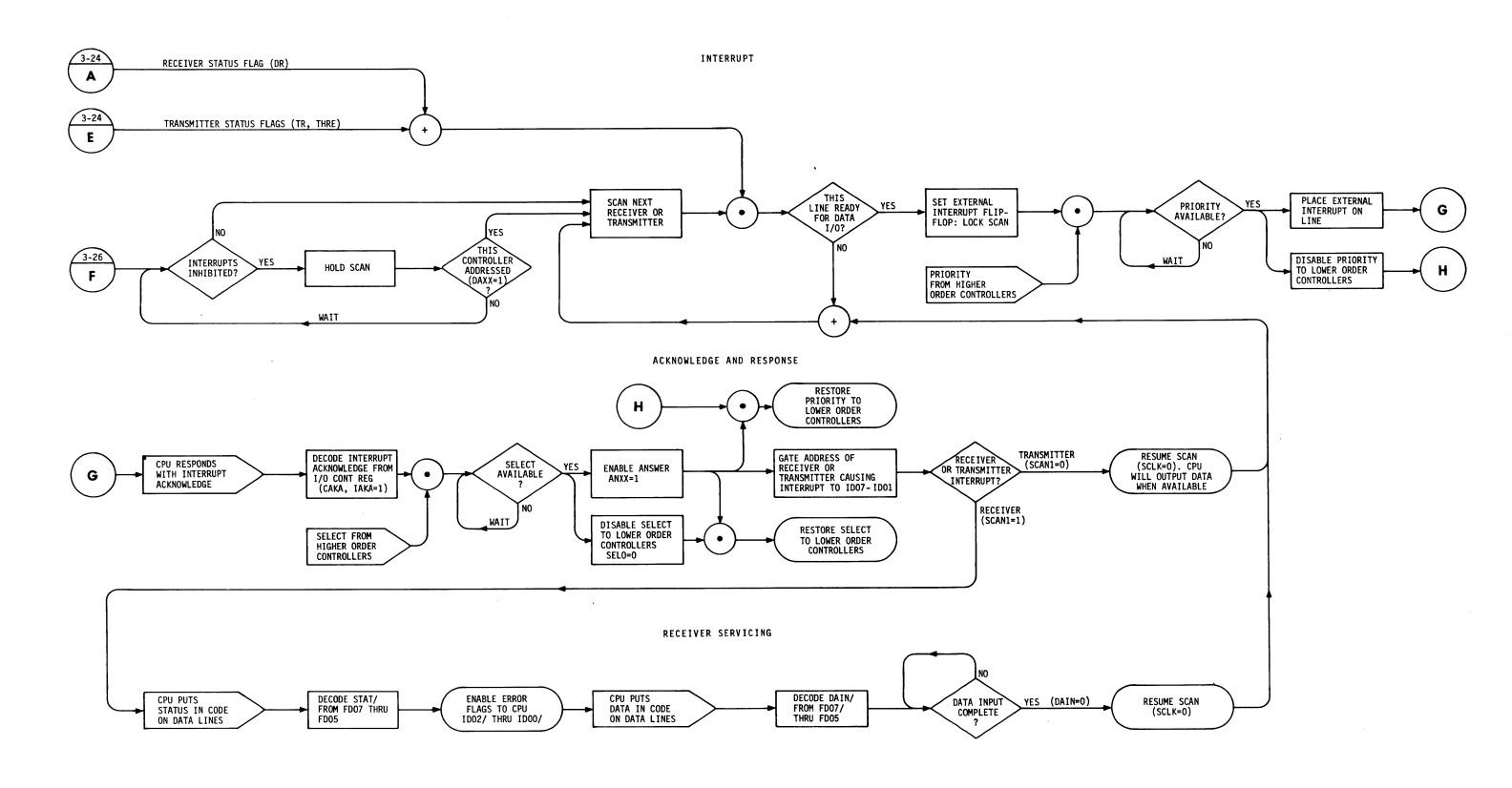

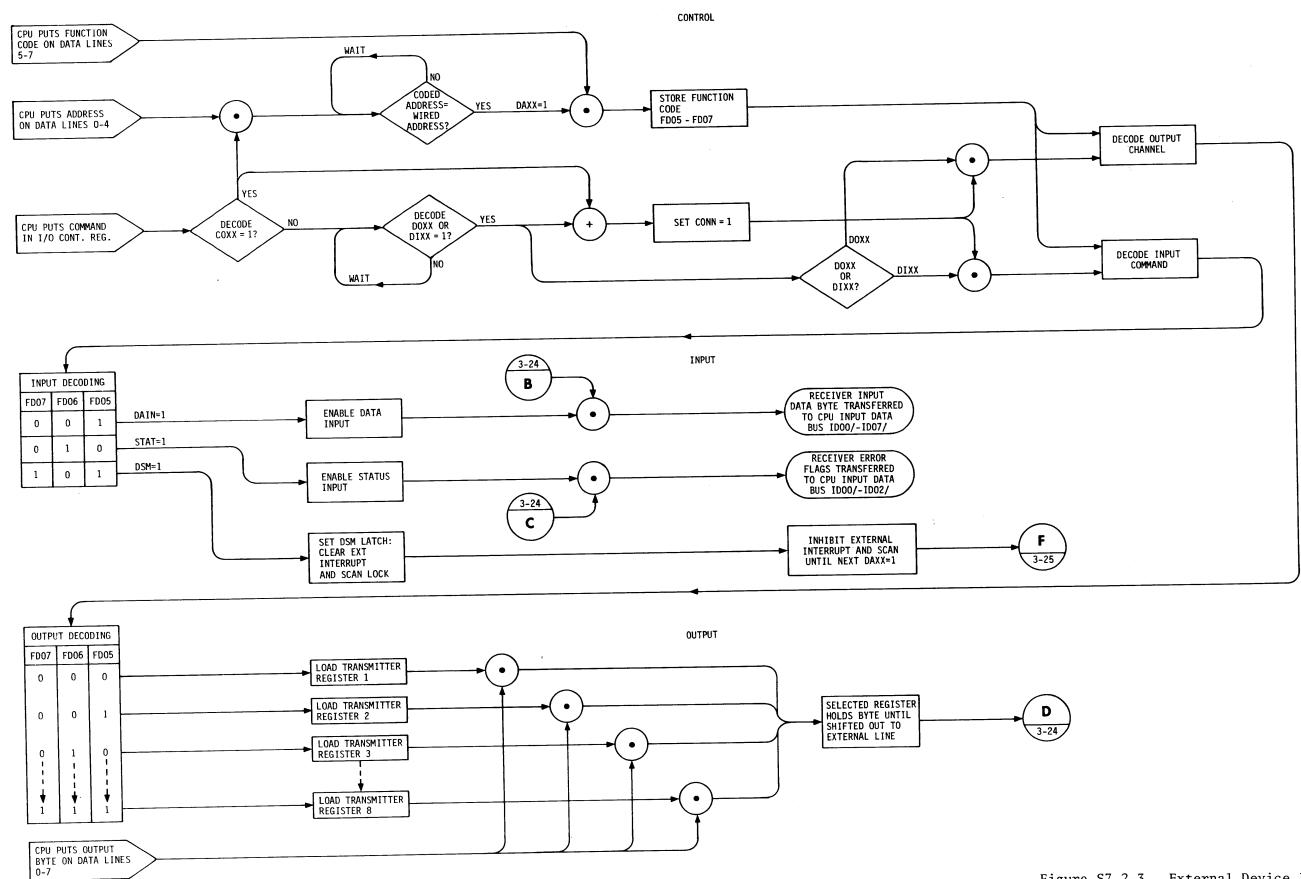

| SUPPLEMENT | 7. SWITCH SELECTABLE BAUD RATE FOUR-CHANNEL AND EIGHT-CHANNEL CONTROLLERS |

|            | LIST OF TABLES                                                            |

|            | Page                                                                      |

| 1-1        | System Specifications                                                     |

| 1-2        | File Zero Flag Byte                                                       |

| 1-3        | Internal Status                                                           |

| 1-4        | Microcommand Repertoire                                                   |

| 2-1        | Command Decode Signal Glossary                                            |

| 2-2        | Op Codes 0 through 6 Command Decodes                                      |

| 2-3        | Op Code 7 Command Decodes                                                 |

| 2-4        | Op Codes 8 through F Command Decodes                                      |

| 2-5        | B Bus Data Selection                                                      |

| 2-6        | Arithmetic/Logic Unit Operations                                          |

| 2-7        | A Bus Data Selection                                                      |

| 2-8        | Display Multiplexer Data Selection 2-85                                   |

| 3-1        | Data Entry Display Capabilities                                           |

| 4-1        | Marginal Voltage Tests                                                    |

| 4-2        | Power Supply Adjustments                                                  |

# LIST OF ILLUSTRATIONS

|      |                                                 | Page |

|------|-------------------------------------------------|------|

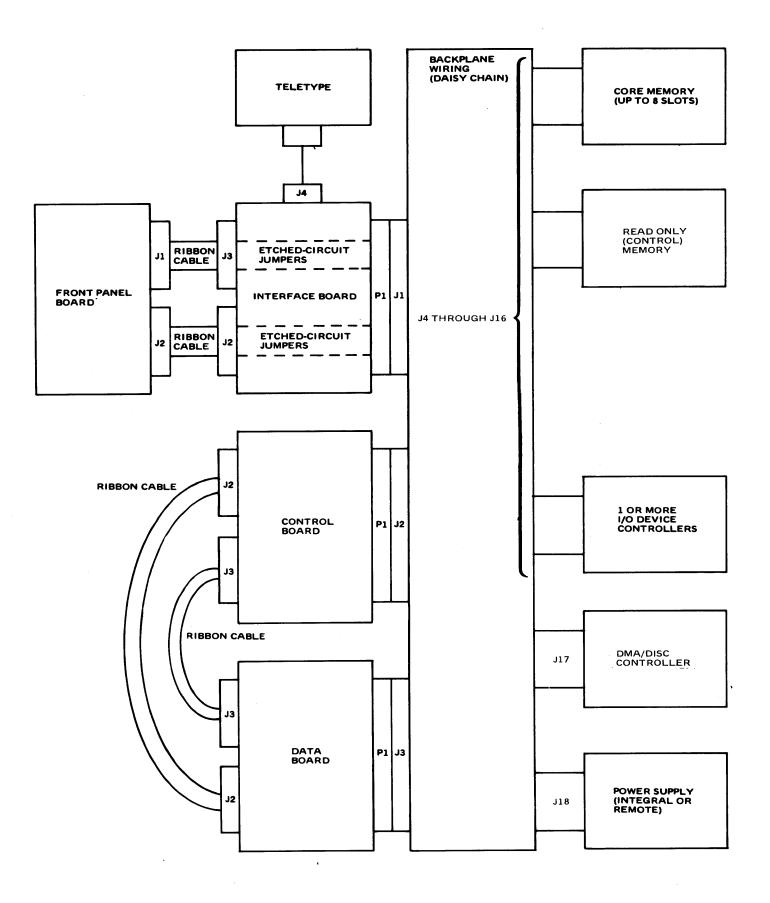

| 1-1  | CPU Interconnections                            | 1-8  |

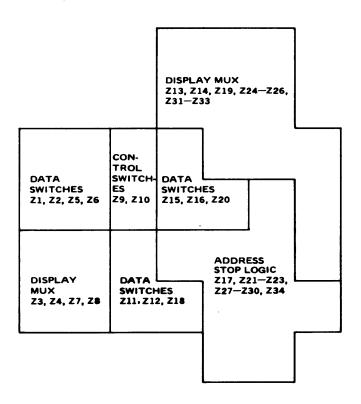

| 1-2  | Front Panel Board Circuit Functions             | 1-9  |

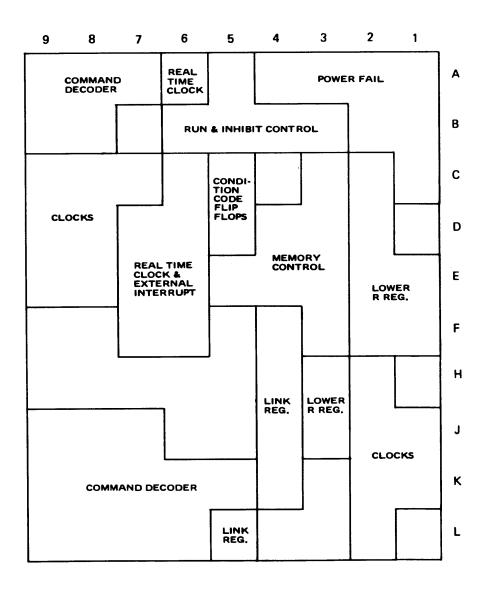

| 1-3  | Control Board Circuit Functions                 | 1-10 |

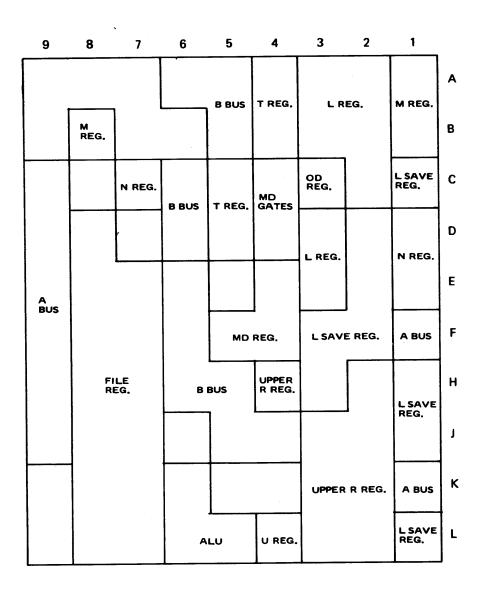

| 1-4  | Data Board Circuit Functions                    | 1-11 |

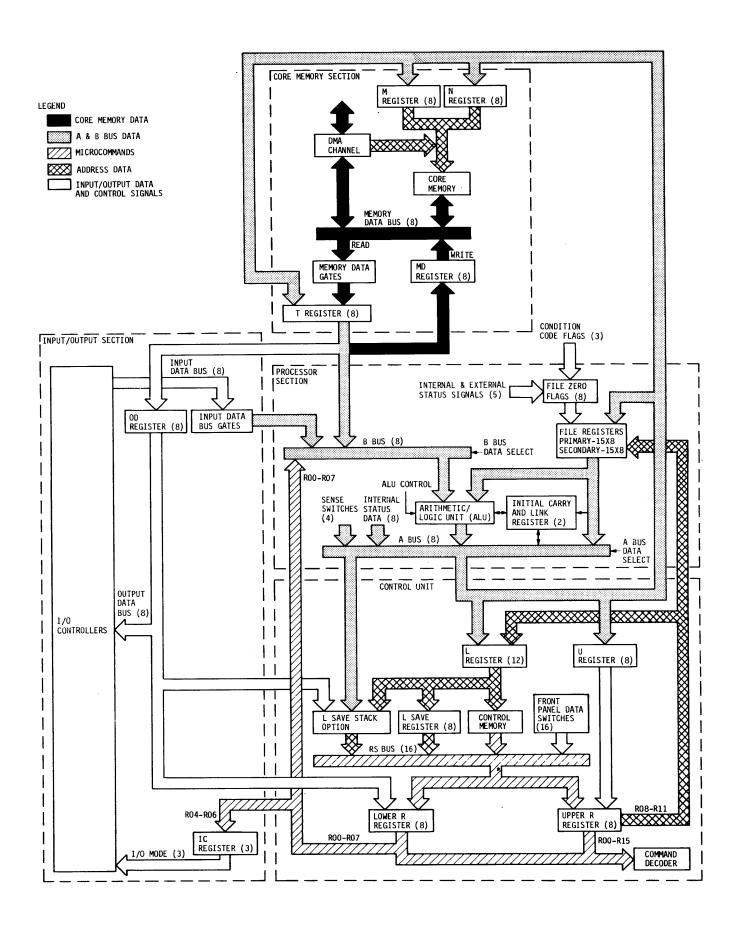

| 1-5  | CPU Functional Block Diagram                    | 1-15 |

| 2-1  | CPU Block Diagram                               | 2-3  |

| 2-2  | CPU Simplified Block Diagram                    | 2-4  |

| 2-3  | Front Panel Control Circuits                    | 2-9  |

| 2-4  | Clock and Machine State Control Circuits        | 2-10 |

| 2-5  | Control Unit                                    | 2-13 |

| 2-6  | Core Memory Section                             | 2-14 |

| 2-7  | Processor Section                               | 2-17 |

| 2-8  | Status and File Zero Flag Circuits              | 2-18 |

| 2-9  | Front Panel Display Indicators                  | 2-24 |

| 2-10 | I/O Control Section                             | 2-25 |

| 2-11 | Types of Fetch/Execute Cycles                   | 2-43 |

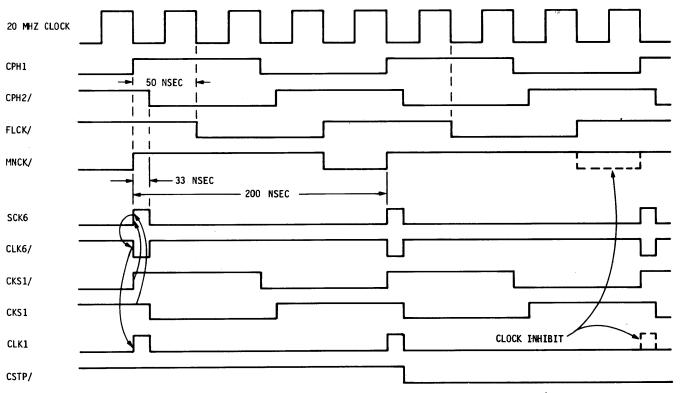

| 2-12 | Basic Clock Timing                              | 2-48 |

| 2-13 | Run/Halt Timing                                 | 2-50 |

| 2-14 | Run Inhibit Timing                              | 2-51 |

| 2-15 | Panel Interrupt Timing                          | 2-51 |

| 2-16 | Timing for Clock Stop and Clocks 7, 8, and 9    | 2-52 |

| 2-17 | Clock 2 (File Register Write Clock) Timing      | 2-54 |

| 2-18 | MCLR/ (M Register Clear) Timing                 | 2-54 |

| 2-19 | TCLK/ (T Register Load) Timing                  | 2-54 |

| 2-20 | L Register Timing                               | 2-56 |

| 2-21 | Memory Write Cycle Timing                       | 2-58 |

| 2-22 | Memory Read Cycle Timing                        | 2-60 |

| 2-23 | Address Stop Timing, Case 1 and Case 2          | 2-66 |

| 2-24 | Address Stop Timing, Case 3                     | 2-68 |

| 2-25 | Address Stop Timing, Case 4                     | 2-69 |

| 2-26 | Command Execution, Flow Block Diagram           | 2-87 |

| 2-27 | Loading of Effective Microcommand in R Register | 2-88 |

Revised: February 1, 1973

# LIST OF ILLUSTRATIONS (continued)

|       |                                                         | Page    |

|-------|---------------------------------------------------------|---------|

| 2-28  | Jump and Return Jump Execution                          | .2-91   |

|       | Op Codes 10, 11, 12, 13, 16 and 19 Execution            | .2-92   |

| 2-29  | Op Codes 17, 18 and 18 Execution                        | .2-97   |

| 2-30  | Op Codes 2, 3, 4, 5, and 6 Execution                    | .2-98   |

| 2-31  | Op Codes 7 through F Overall Processing                 | .2-101  |

| 2-32  | Op Codes / through r Overall Placessing                 | .2-102  |

| 2-33  | I/O Command Execution                                   | 2-105   |

| 2-34  | Add and Copy Execution                                  | 2_106   |

| 2-35  | Subtract Execution                                      |         |

| 2-36  | Core Memory Read or Write Execution                     | .2-109  |

| 2-37  | Logical AND, OR, and Exclusive OR Execution             | .2-110  |

| 2-38  | Shift Right or Left Execution                           | .2-113  |

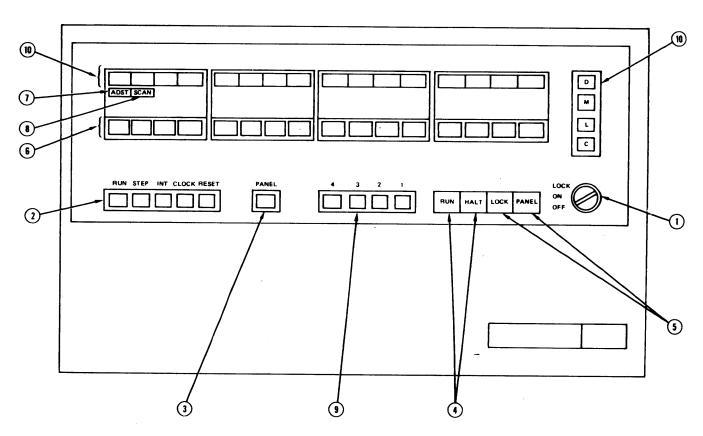

| 3-1   | Front Panel Controls and Indicators (2 Sheets)          | .3-2    |

| 4-1   | Remote Power Supply Voltage Adjustments and Test Points | .4-6    |

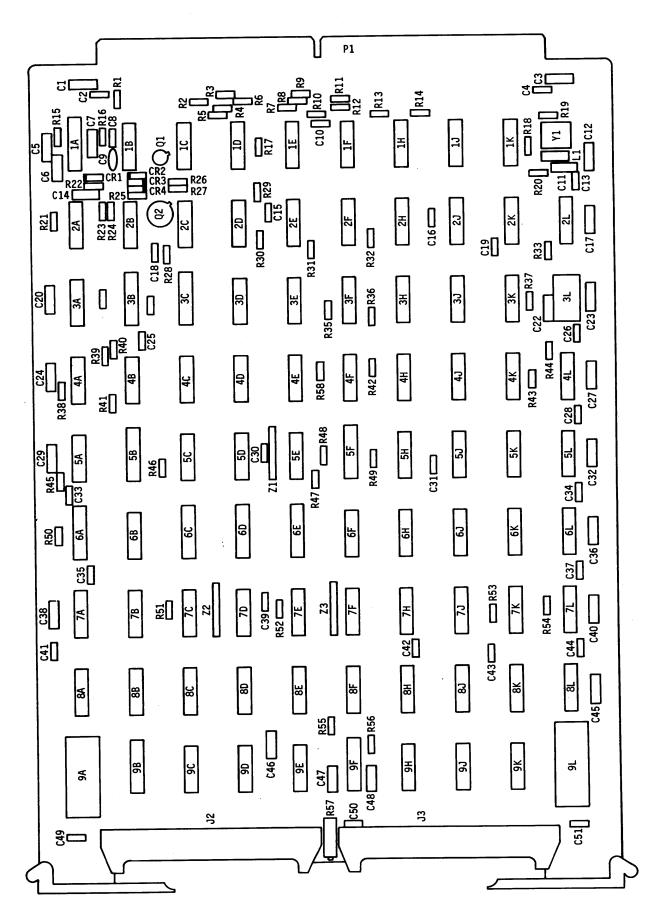

| 5-1   | System Panel P. C. Card                                 | .5-3    |

| 5-2   | Backplane Assembly                                      | .5-5    |

| 5-3   | Interface Card With Integral TTY                        | .5-7    |

| 5-4   | Data Card                                               | .5-9    |

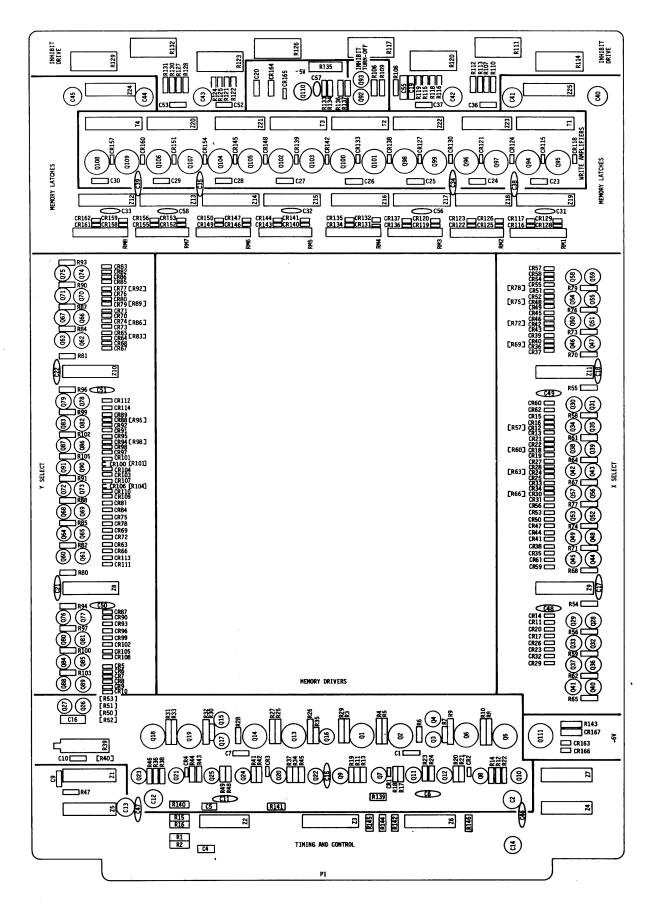

| 5-5   | Read Only Memory Card                                   | .5-11   |

| 5-6   | Control Card                                            | .5-13   |

| 5-7   | 8K Memory Card                                          | .5-17   |

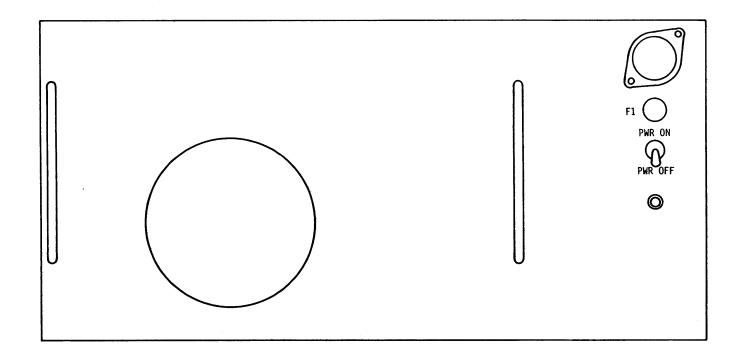

| 5-8   | Power Supply (Front)                                    | .5-19   |

| 5-8.1 | Power Supply (Later Model) (Front)                      | .5-19.3 |

| 5-9   | Power Supply (Back)                                     | .5-19   |

| 5-9.1 | Power Supply (Later Model) (Back)                       | .5-19.3 |

| 5-10  | Regulator Board                                         | .5-21   |

| 5-11  | Failure Detection Board                                 | .5-23   |

|       |                                                         |         |

Revised: August 10, 1973

#### SECTION 1

### GENERAL DESCRIPTION

# 1.1 SCOPE

This manual contains the general description, installation procedures, operation, theory of operation, and maintenance data for the Model 1200 Central Processing Unit (CPU), Part Number 400100, manufactured by the Basic/Four Corporation, 18552 MacArthur Boulevard, Santa Ana, California 92707. The CPU is an integral part of the Basic/Four data processing systems. The logic diagrams for the CPU are in LD 1010.

# 1.2 MANUAL ORGANIZATION

Sections 1 through 5 of this manual cover the CPU portion of the computer system. The CPU includes the following basic elements:

- a. Control Board

- b. Data Board

- c. Front Panel Board

- d. Interface Board

The basic elements are common to all Basic/Four Model 1200 Central Processing Units. Sections 1 through 5 provide detailed descriptions and instructions for these elements, together with interface descriptions that relate the CPU to other elements of a computer system. These other elements, including core memory, control memory, power supply, and I/O device controllers are either optional or variable, depending on the requirements of each application. Supplements, following Section 5, describe these elements in a specific application.

Sections 1 through 5 contain the following information:

- a. <u>Section 1 General Information</u>. This section contains physical and functional descriptions of the CPU. Also included are detailed descriptions of the microcommand repertoire, and reference data.

- b. Section 2 Theory of Operation. This section contains block diagrams and data flow descriptions, detailed logic descriptions, timing descriptions, and instruction flow diagram descriptions for the CPU. Overall and detailed block diagrams support the block diagram and data flow descriptions. Timing

diagrams support the timing descriptions. The instruction flow diagrams and descriptions describe the sequence of actions performed by the CPU for each microcommand in the CPU repertoire. Interfaces between the CPU and the other elements of a computer system are also described.

- c. Section 3 Operation. This section describes the operator controls and indicators that are included on the system front panel (part of the front panel board). The various front panel modes of operation are described, and detailed procedures are provided for using the front panel controls and indicators to exercise the CPU.

- d. <u>Section 4 Maintenance</u>. This section describes the use of the procedures in Section 3 for checkout and troubleshooting of the CPU. Adjustment procedures are also included in this section.

- e. <u>Section 5 Parts Lists</u>. This section contains assembly drawings and parts lists for the major elements of the CPU.

# 1.3 EQUIPMENT PURPOSE AND CAPABILITIES

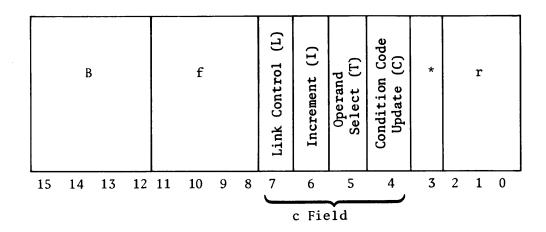

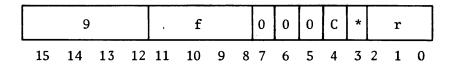

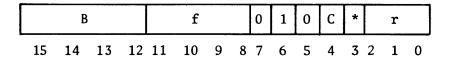

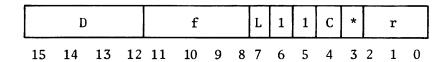

The CPU is a microprogrammed digital data processor. Microprogramming is a technique for obtaining maximum utilization of computer capabilities by efficient use of the machine subcommands. These hardware-implemented subcommands cause the CPU to execute specific storage, retrieval, arithmetic, or logical operations. A sequence of subcommands are employed to perform specific data processing routines or subroutines. These subcommand sequences (microprograms) are translated into a sequence of 16-bit microcommands that are stored in control memory. The microcommands stored in control memory constitute the firmware for a specific data processing application. A firmware routine or subroutine is executed by the CPU as follows:

- a. The 16-bit microcommands that compose a particular firmware routine, or subroutine, are stored in consecutive locations in control memory.

- b. The CPU sequentially accesses each microcommand storage location in control memory.

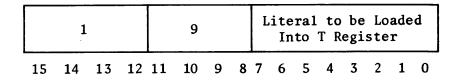

- c. Each 16-bit microcommand read from control memory is stored, decoded and executed by the CPU. In some cases, the microcommand includes an 8-bit literal for storage or computation purposes. In other cases, the microcommand contains a core memory address for a core memory read or write operation.

- d. At the end of a firmware routine, or subroutine, a jump microcommand may be utilized to proceed to the next firmware routine or subroutine. The jump microcommand causes the CPU to access the first location of the next firmware routine, or subroutine, to be executed.

The flexibility of the CPU is enhanced by the jump capability, plus the capability to modify microcommands received from control memory with software instructions read

from core memory. The jump capability makes more efficient use of the firmware in control memory. For example, a firmware routine can be made up of a number of multipurpose firmware subroutines, each stored in different segments of control memory. In this case, the microcommands in the firmware routine include jump instructions that direct the CPU to jump to the start of each firmware subroutine in control memory.

At the end of each subroutine, a return jump instruction causes the CPU to return to the next instruction in the firmware routine. The capability to modify microcommands with instructions received from the core memory permits data processing operations to be performed under the combined control of firmware and software. In this case, the firmware-to-software transition is achieved by inserting a firmware subroutine that typically performs the following actions:

- a. The next software instruction (two 8-bit words) is read from core memory and stored in the CPU.

- b. A Modify Lower Command (MLC) microcommand is issued, notifying the CPU to modify the low-order bits of the next microcommand.

- c. An Execute, Literal Type (ELT) microcommand is issued. This microcommand would typically contain all zeros in the eight high-order bits, and all ones in the eight low-order bits. The resulting effective microcommand stored in the instruction (R) register would then be identical to the two 8-bit words read from core memory. The CPU then executes the software-derived instruction in the R Register. Typically, this instruction causes the CPU to jump to the beginning of a firmware routine, or subroutine, specified by the address in the effective microcommand.

The described capabilities permit the CPU to be applied directly to problem solutions by full programming at the micro level, by emulating the operation of a macro level computer in which software instructions are stored in core memory, or by a combination of micro- and macro-level programming. Options are available that permit the user to modify the microprograms stored in control memory, permitting greater flexibility in the application of the system.

The arithmetic/logic unit (ALU) of the CPU typically performs arithmetic and logic operations on a selected 8-bit operand and the 8-bit contents of a selected file register. The CPU contains 30 eight-bit general-purpose file registers for storage of user's data. The selected operand may be an 8-bit word from the I/O bus or the core memory, a literal from control memory, or the result of a previous arithmetic,

logical or storage operation. A typical microcommand for an arithmetic or logical operation designates the file register, the source of the operand, and the type of computation to be performed by the ALU. The result produced by the ALU is then stored in a file register or in one of the other CPU registers.

# 1.4 REFERENCE DATA

Table 1-1 provides complete reference data for the CPU. Included in Table 1-1 are power requirements, environmental conditions, dimensions, and circuit characteristics.

TABLE 1-1. SYSTEM SPECIFICATIONS

| PARAMETER                       | CHARACTERISTICS                                                                                                                       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Input Power Requirements        | 115/230 Vrms ±10%, single-phase, 47-63 Hz, 350 watts maximum                                                                          |

| Power Supply:                   |                                                                                                                                       |

| Туре                            | Series regulator power supply with three regulated dc outputs.                                                                        |

| DC Outputs                      | +12 Vdc, 1.2A, ±5% adjustable; +5 Vdc, 20A, ±5% adjustable; -16.75 Vdc, 3.5A, ±2% adjustable                                          |

| Overload/Overvoltage Protection | +7 Vdc limit on +5 Vdc output; overload current limiting with automatic recovery                                                      |

| Power Fail Detect               | Power failure is detected two milliseconds before loss of dc regulation; automatic recovery after ac is restored.                     |

| Line Filtering                  | Integral line filter for ac line transient protection                                                                                 |

| Circuit Types                   | Hermetically sealed semiconductors and ceramic integrated circuits used throughout                                                    |

| Environmental:                  |                                                                                                                                       |

| Operating Temperature           | 0-50 degrees C (32-122 degrees F)                                                                                                     |

| Relative Humidity               | 10-90% without condensation                                                                                                           |

| CPU Circuit Types               | Integrated LSI, MSI, and SSI circuit design throughout. TTL logic is used internally, and DTL logic is used for input/output drivers. |

TABLE 1-1. SYSTEM SPECIFICATIONS (cont)

| PARAMETER                          | CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dimensions:                        |                                                                                                                                                                                                                                                                                                                                                      |

| Rack-Mounted Enclosure             | 10.5-inch height by 20-inch depth by 19-inch width                                                                                                                                                                                                                                                                                                   |

| Internal Logic Levels              | Logical 1 = +5 V (nominal); logical $0 = 0$ V                                                                                                                                                                                                                                                                                                        |

| External Logic Levels              | Logical 1 = 0 V (nominal); logical 0 = +3 V (nominal)                                                                                                                                                                                                                                                                                                |

| Remote Power Supply (rack-mounted) | 8-3/4-inch height by 10.5-inch depth by 19-inch width                                                                                                                                                                                                                                                                                                |

| Clock Rate                         | 5-MHz clock rate (crystal-controlled)                                                                                                                                                                                                                                                                                                                |

| Command Repertoire                 | See Table 1-4                                                                                                                                                                                                                                                                                                                                        |

| Command Execution Times            | See Table 1-4                                                                                                                                                                                                                                                                                                                                        |

| Arithmetic/Logic Unit              | 8-bit parallel, binary, fixed point. One's and two's complement for negative numbers.                                                                                                                                                                                                                                                                |

| File Registers                     | 30 general-purpose 8-bit file registers plus one 8-bit flag register                                                                                                                                                                                                                                                                                 |

| Control Memory                     | Up to 2048 words (16 bits) of control memory. Control memory is implemented with bipolar read only memory (ROM) devices. Minimum system has 1280 words of control memory.                                                                                                                                                                            |

| Core Memory                        | Core memory containing up to 65,536 eight-bit bytes can be accommodated in basic enclosure. Core memory is implemented with 8192-byte modules. Wide-temperature-range lithium cores are utilized. Either full- or half-cycle memory read or write operations can be performed. Full-cycle time is 1 microsecond; half-cycle time is 600 nanoseconds. |

| Power Fail and Restart             | Automatic shut-down in the event of a power failure; automatic restart when power is restored.                                                                                                                                                                                                                                                       |

| Input/Output Interface             | Separate 8-bit parallel input and output data buses for communication with I/O device controllers in either programmed or concurrent (block transfer) modes.                                                                                                                                                                                         |

| Real Time Clock                    | Real Time Clock produces an interrupt once every millisecond.                                                                                                                                                                                                                                                                                        |

| •                                  |                                                                                                                                                                                                                                                                                                                                                      |

TABLE 1-1. SYSTEM SPECIFICATIONS (cont)

| PARAMETER                               | CHARACTERISTICS                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Direct Memory Access/Disc<br>Controller | DMA channel allows the disc memory to communicate directly with the core memory at data transfer rates up to 1-million bytes per second.                                                                                                                                                                                |

| TTY controller                          | An optional parallel TTY controller is available.                                                                                                                                                                                                                                                                       |

| Miscellaneous Controllers               | Magnetic tape controller, card reader controller, paper tape controller, multi-channel TTY controllers, line printer controller, and 2400 baud controller are available.                                                                                                                                                |

| Software                                | A variety of supporting standard software, including special firmware development packages, are available. These packages include assemblers, simulators, generators for direct conversion of language assembler outputs into control memory bit patterns, diagnostics, and alterable control memory operating systems. |

### 1.5 PHYSICAL DESCRIPTION

# 1.5.1 ENCLOSURES

The CPU is enclosed in an 18-slot card-cage enclosure with removable front panel and power supply. The entire assembly is mounted, along with a Disc Drive Unit and power supply in a Basic/Four system cabinet. Controllers are inserted into slots in the CPU enclosure and interface with external equipment.

# 1.5.2 BACKPLANE

The backplane contains connector slots for all computer system elements except the front panel board. The backplane can be supplied with 18-connector slots.

Printed circuit (PC) boards installed in the backplane connector slots are accessible from the rear of the enclosure. The connector pins of the backplane are accessible with the front panel removed. All PC boards are equipped with handles for convenient extraction, insertion, and lock-down. The boards may be installed on extender boards for troubleshooting and checkout. All PC boards have dimensions of 8.575 inches by 12.5 inches. PC boards that serve as controllers for I/O devices include connectors which provide connection by ribbon cables to the devices.

The first three slots of the backplane are dedicated to the CPU.

| Slot No. | Dedicated Use   |

|----------|-----------------|

| J1       | Interface Board |

| J2       | Control Board   |

| J3       | Data Board      |

A typical CPU card cage for a system with maximum core memory would have this configuration: J1 - interface with integral TTY controller, J2 - control, J3 - data, J4 through J11 - 8K core memory, J12 - control memory, J13 through J16 - priority selected controllers, J17 - DMA/disc controller, and J18 - power supply extender board. The normal priority sequence for the seven available types of controllers is (from highest to lowest priority): eight channel, four channel, 2400 baud, magnetic tape, paper tape, card reader, and line printer. The magnetic tape controller requires two slots; all other controllers require only one slot. The eight channel, four channel, and 2400 baud controllers provide the interface for video display terminals and/or accounting machine terminals.

Slots J4 through J17 are used for core memory, control memory, the DMA channel, I/O device controllers, and other options. Slot J18 is reserved for the power supply extender board. The DMA/disc controller is installed in slot J17. The PC boards for the core memory are installed in the slots immediately following slot J3, and the PC board for the control memory is installed immediately following the last core memory board. Optional I/O and device controllers are installed in the slots that follow the last control memory board. The order of installation in these slots is usually dependent on the order of device priority, such that the highest-priority device or I/O controller is installed in the first slot following the control memory, and the lowest-priority controller is installed in the slot with the highest number. Controllers must not be separated by empty slots.

#### 1.5.3 INTERCONNECTIONS

The elements of the CPU are interconnected as shown in Figure 1-1. The front panel board is connected to the other elements of the CPU by means of two ribbon cables attached to the interface board in backplane slot J1. The signals to and from the front panel board are distributed via the backplane between slot J1 (interface board) and slots J2 (control board) and J3 (data board). Interconnections between the

Figure 1-1. CPU Interconnections

control and data boards are made by means of two ribbon cables. Interconnections between the control and data boards and other elements mounted in the backplane are made via the backplane wiring. Power distribution is from the power supply (slot J14 or J18) to all elements connected in the backplane.

# 1.5.4 CPU PRINTED CIRCUIT BOARDS (Figures 1-2 through 1-4)

With the exception of transistor lamp drivers on the front panel board, all circuits are implemented by LSI, MSI, and SSI integrated circuits (IC). TTL logic is used internally, and DTL logic is used for input/output drivers.

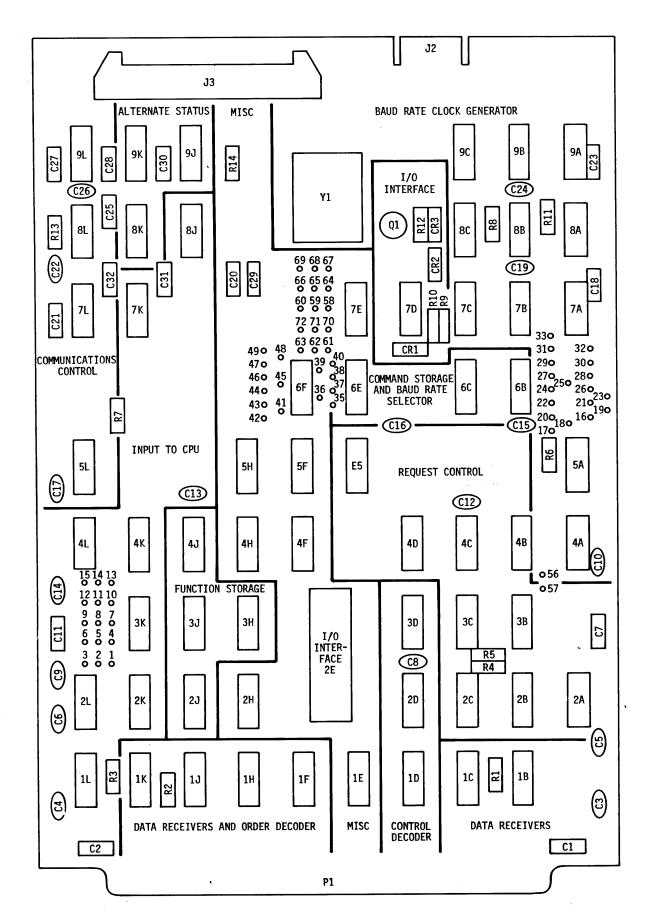

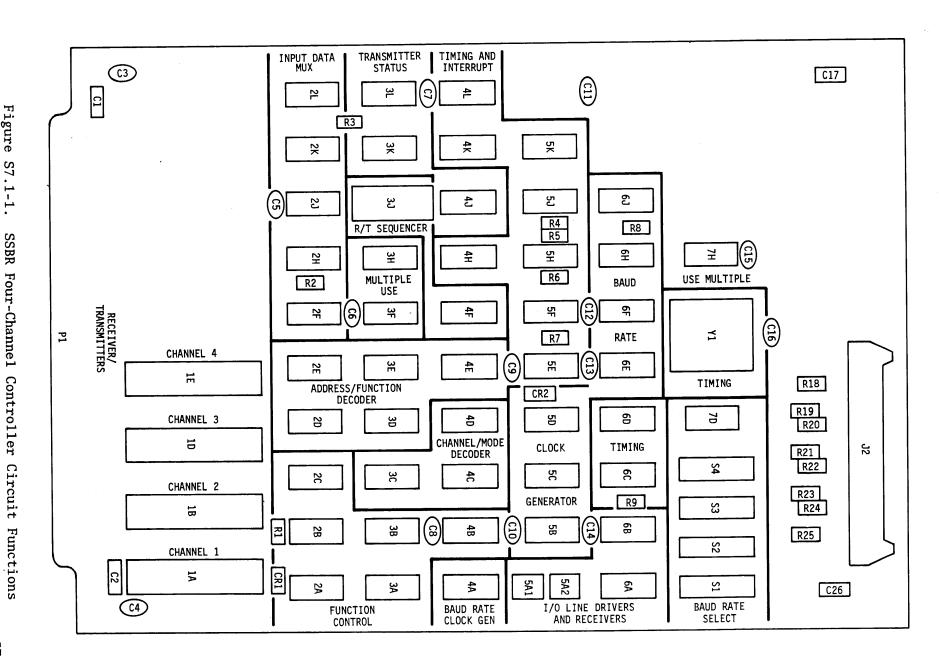

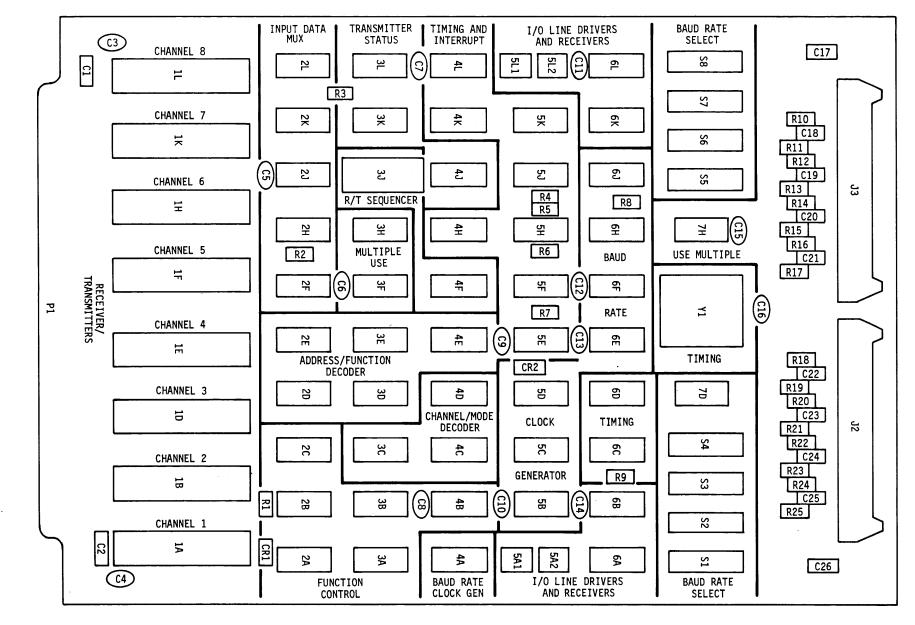

Physical organization of the PC boards in the CPU are shown in Figures 1-2 through 1-4. In these figures a grid system is used to identify the integrated circuit elements. An integrated circuit reference designation consists of the column number followed by the row letter. Example: 5C is the integrated circuit in column 5, row C.

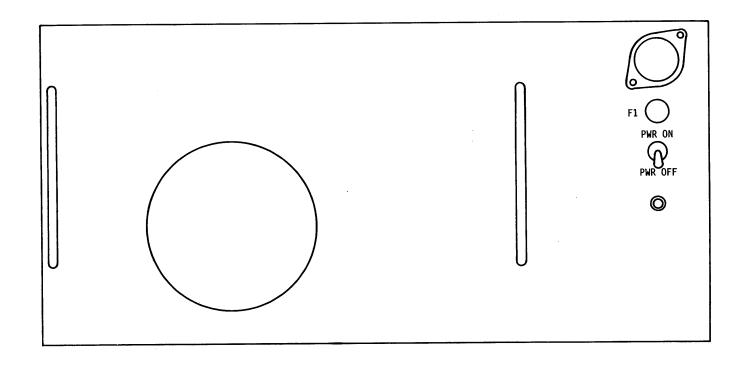

1.5.4.1 FRONT PANEL ASSEMBLY. The front panel assembly (Figure 1-2) consists of a front panel circuit board mounted to a panel that contains the labels for switches and indicators. All switches and indicators are physically mounted to the front panel board, and protrude through holes in the front panel. Four pins in the front

Figure 1-2. Front Panel Board Circuit Functions

Figure 1-3. Control Board Circuit Functions

Figure 1-4. Data Board Circuit Functions

panel assembly provide the means for mounting the assembly in the enclosure. These pins mate with spring-loaded fasteners in the enclosure. The ribbon cables that connect the front panel board to the interface board are of sufficient length to permit removal or installation of the front panel board without stressing the cable connectors.

Two versions of the front panel assembly are available. The basic front panel contains a key-lock power switch, five machine state control switches, two machine state control indicators, and four sense switches. The system front panel contains identical switches and indicators to those located on the basic front panel. In addition, the system front panel contains a panel mode selector switch (with associated indicators), 16 data switches, 16 data display indicators, address stop and scan features, and associated display control pushbutton switches. The basic front panel is included in the unit, and provides all controls for normal operation. The basic front panel is removed and replaced by the system front panel for CPU maintenance.

Figure 1-2 illustrates the CPU front panel board, and identifies the integrated circuit elements associated with the various functional sections of the front panel.

These functional elements include the following:

- a. Front Panel Control Switches

- b. Sense Switches

- c. Upper and Lower Data Switches

- d. L Address Drivers and Comparator

- e. Address Stop Logic

- f. RS Bus Drivers

- g. Front Panel Display Indicators

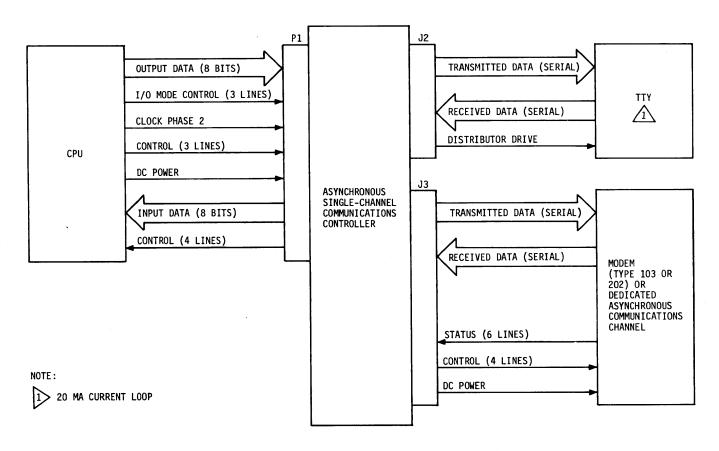

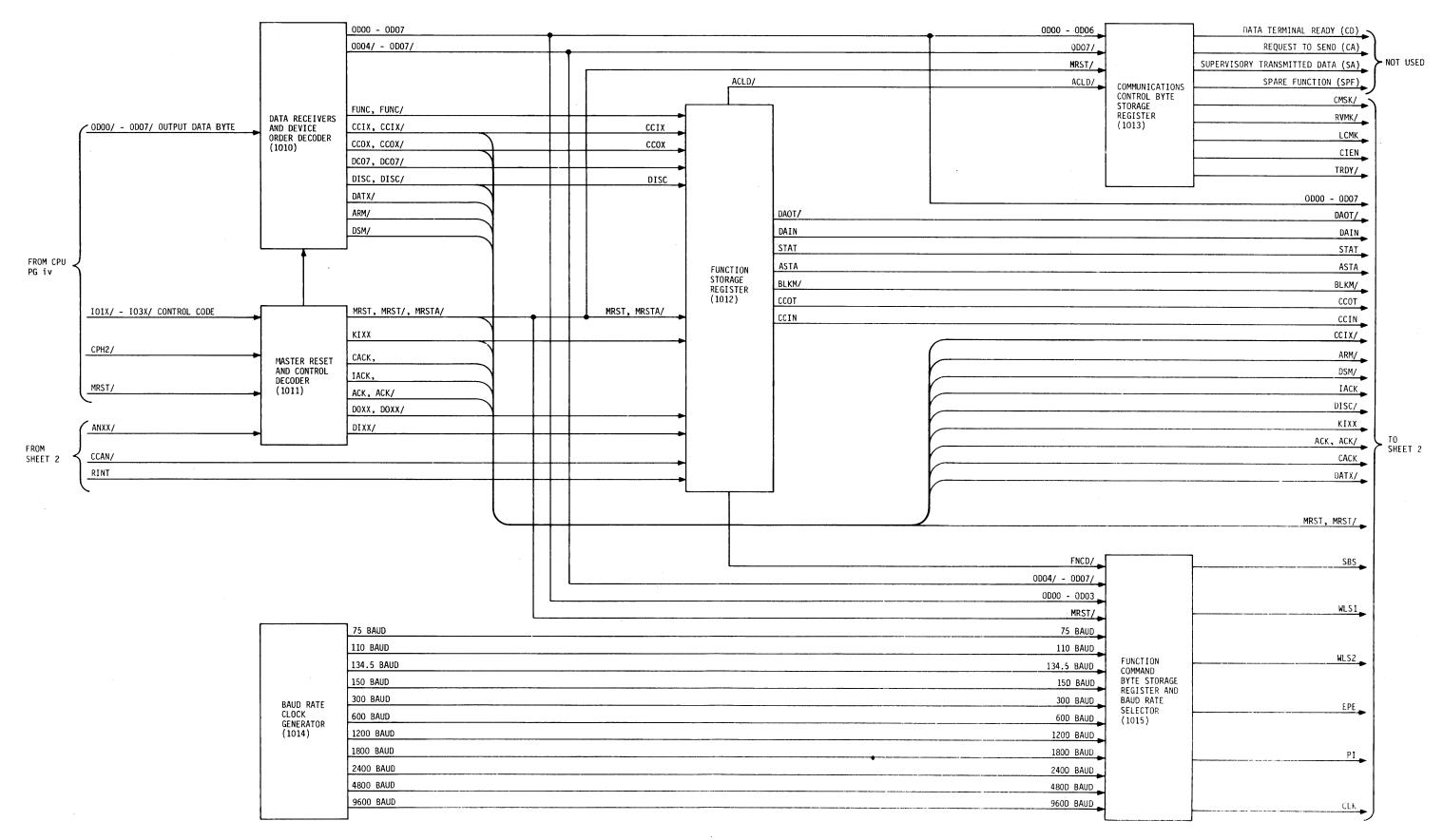

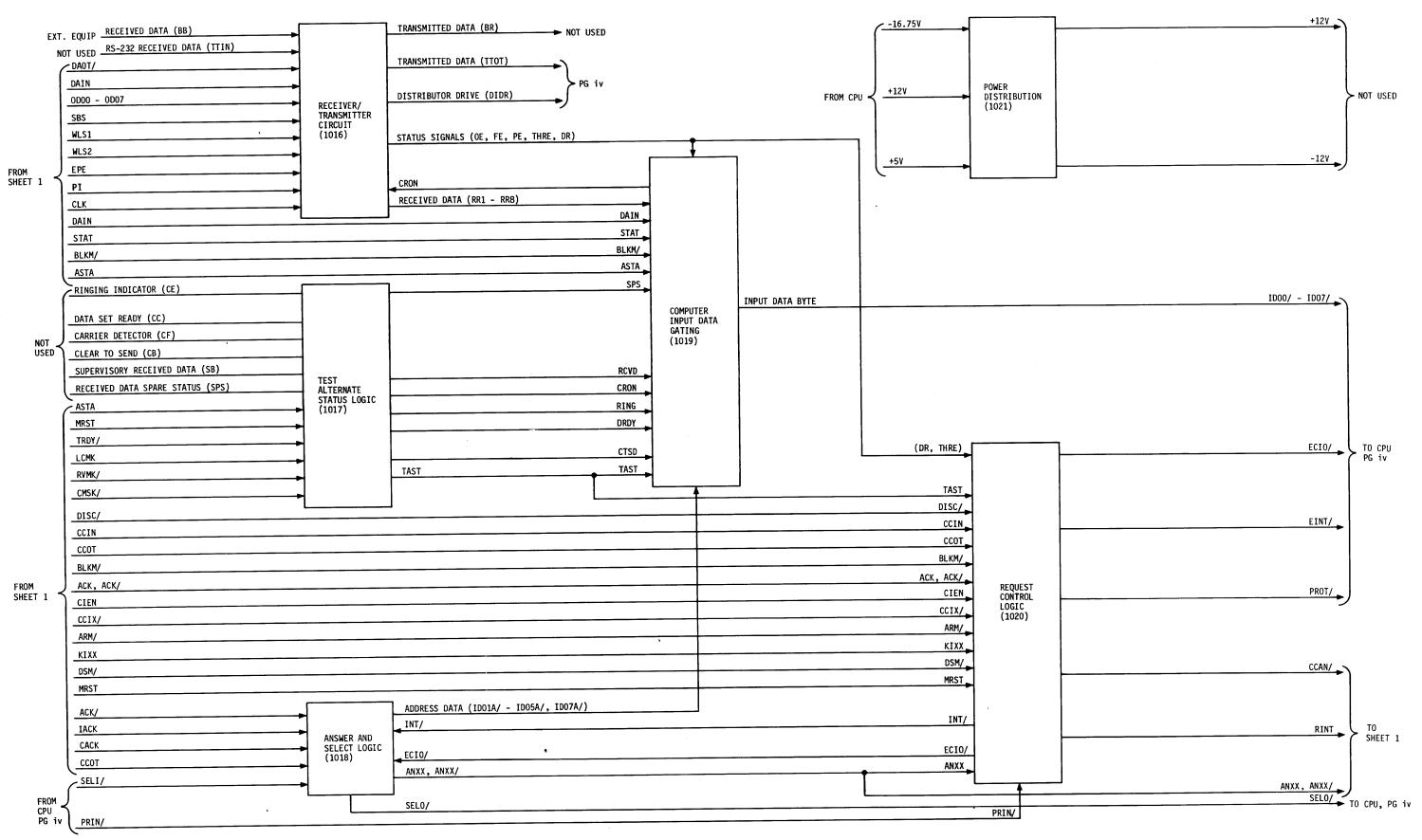

- 1.5.4.2 INTERFACE BOARD. The interface board serves both as the interface for the front panel, and as the controller for a Teletype. The front panel interface section consists of printed circuit jumpers between the backplane and the ribbon cables that connect to the front panel. The integral TTY controller receives 8-bit parallel data from the CPU, and converts this data to a serial form for transmittal via connector J4 to the Teletype. Serial data from the Teletype is converted by the TTY controller to an 8-bit parallel form for transmittal via the backplane to the CPU.

The front panel interface section of the interface board is described in Section 2.

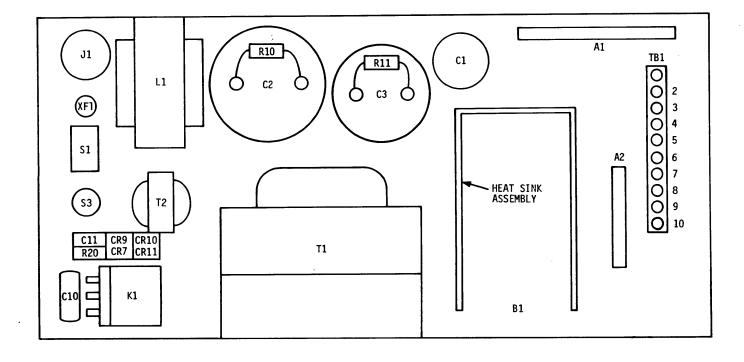

- 1.5.4.3 <u>CONTROL BOARD</u>. Figure 1-3 identifies the integrated circuits associated with the various CPU elements contained on the control board. These functional elements include the following:

- a. Clock Generator and Clock Gating

- b. Run and Inhibit Control

- c. Lower R Register

- d. Command Decoder

- e. Memory Control

- f. Link Register

- g. Initial Carry Logic

- h. Condition Code Flip-Flops

- i. External Interrupt Control

- j. Power Fail Circuits

- k. Real Time Clock

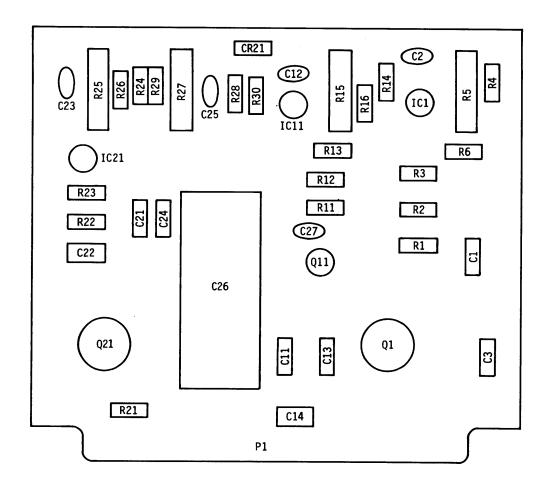

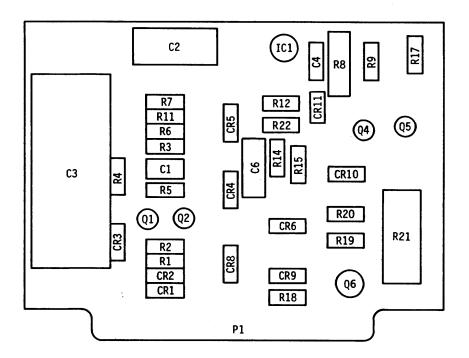

- 1.5.4.4 <u>DATA BOARD</u>. Figure 1-4 identifies the integrated circuits associated with the various CPU elements contained on the data board. These functional elements include the following:

- a. L Register

- b. L Save Register

- c. U Register

- d. Upper R Register

- e. M Register

- f. N Register

- g. Memory Data Gates

- h. T Register

- i. MD Register

- j. B Bus Multiplexer

- k. A Bus Multiplexer

- 1. Arithmetic/Logic Unit (ALU)

- m. File Registers

- n. Internal Status Interrupt Control

- o. Input Data Bus Gates

- p. IC Register

- q. OD Register

### 1.5.5 POWER SUPPLY

The power supply is mounted remotely. An extension cable connects between the remote power supply and a printed circuit board that is installed in power supply slot J18 of the backplane. The printed circuit board contains etched-circuit jumpers to the appropriate pins of the backplane. Usually a single power supply is used for both the CPU and the Disc Drive Unit.

The power supply has ample capacity to power all system configurations. A basic system consisting of the following elements would require +5 V current:

| Item                                                | Current (amps)  |

|-----------------------------------------------------|-----------------|

| Basic CPU (control board and data board)            | 5.0             |

| System front panel assembly                         | 0.9             |

| ROM                                                 | 1.5             |

| Four core memory modules containing 8192 words each | 2.4             |

|                                                     | 9.8 amps total. |

The basic system would occupy eight slots in the backplane. Each additional core memory requires 0.5 amps at +5 V. Since the power supply is capable of delivering 20 amps at +5 V, the basic system allows 10 amps for expansion in the remaining backplane slots. This leaves more than 1.5 amps for each I/O device controller.

## 1.6 FUNCTIONAL ORGANIZATION

As shown in Figure 1-5, the CPU is divided into four major functional sections. The functional sections are: Control Unit, Core Memory, Processor, and Input/Output Section.

a. Control Unit. This section consists of the control memory and its associated address and instruction storage registers, plus the command decoder that decodes the microcommands. The basic control memory may contain up to 2048 16-bit words.

Figure 1-5. CPU Functional Block Diagram

- b. Core Memory Section. This section consists of the variable-sized core memory and associated memory control logic, address and data registers, and an direct memory access (DMA) channel.

- c. Processor Section. The processor section is organized around the arithmetic logic unit (ALU), with two buses (A and B) provided for data transfers. The T Register (indicated as part of the core memory section) is also part of the processor section, and serves as a buffer for transient data. Also included are general-purpose file registers and file zero flags.

- d. <u>Input/Output Section</u>. This section provides the communications interface with the I/O device controllers connected to the byte I/O interface. Included are data gates associated with the input data bus, an OD (output data) Register associated with the output data bus, and an IC Register that produces the 3-bit I/O mode control used to control the I/O controllers.

### 1.6.1 REGISTERS

- 1.6.1.1 TREGISTER. The 8-bit T Register serves as the operand register for most operate-type commands, and as a buffer for data being written into, or read from, core memory. Data to be supplied over the output data bus is also entered into the T Register and supplied to the OD Register.

- 1.6.1.2 M AND N REGISTERS. The 8-bit M and N Registers hold the current address of the location being accessed in core memory. The M Register holds the eight high-order bits of the address, and the N Register holds the eight low-order bits.

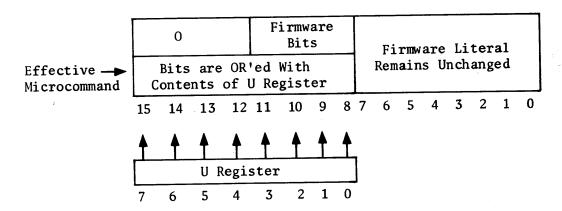

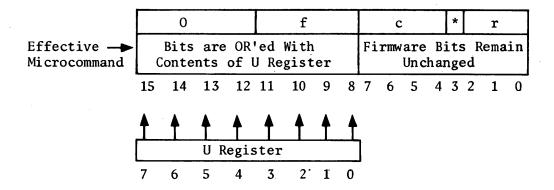

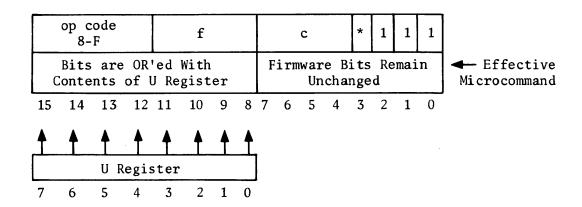

- 1.6.1.3 <u>U REGISTER</u>. The 8-bit U Register stores data to be used in modifying the eight high-order bits of execute-type microcommands received from control memory. The contents of the U Register are OR'ed with the eight high-order bits from control memory, and the result is stored in the upper R Register.

- 1.6.1.4 FILE REGISTERS. The File Registers include the file zero flags (File 0), a primary file containing fifteen 8-bit registers, and a secondary file that also contains fifteen 8-bit registers. Either the primary or secondary file is selected by microcommand. Then, each microcommand that involves a manipulation of data in the selected file, specifies which of the 15 registers is to be accessed for a file read and/or write operation. File 0 cannot be written into, but is used as a source of data. Data written into the File Registers is from the A bus and data read from a File Register is supplied to the ALU and to the A bus.

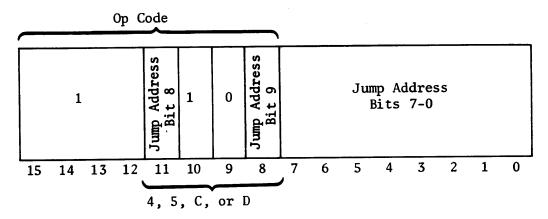

- 1.6.1.5 <u>L REGISTER</u>. The 12-bit L Register holds the address of the next microcommand to be read from control memory, permitting direct addressing of any location in a 2048-word control memory bank. While sequencing through a firmware routine, or subroutine, the L Register is incremented by one as each instruction is executed, unless it is loaded with a jump or return jump-type microcommand. In this case, the L Register is parallel-loaded with the jump address. The following types of jump addresses can be loaded into the L Register:

- a. <u>Jump Extended</u>. The jump extended (JE) microcommand contains a 12-bit jump address, permitting a jump to any location within a 2048-word bank of control memory.

- b. Return Jump. When a return jump microcommand is executed, the contents of the 12-bit L Save Register are loaded into the L Register, permitting a return to any location within a 2048-word bank of control memory.

- c.  $\frac{\text{Jump in 1K}}{\text{permitting a jump to any location within a 1024-word sector of control memory.}$

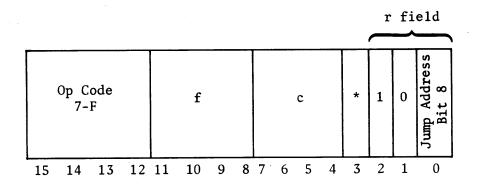

- d. Jump in 1/2K. The jump in 1/2K microcommand is an operate-type command that contains the most significant bit (MSB) of a 9-bit jump address. The 8 least significant bits (LSB) of the jump address are placed on the A bus as the result of the operate-type command execution. The 9-bit jump address is loaded into the L Register, permitting a jump to any location within a 512-word sector of control memory.

- 1.6.1.6 L SAVE REGISTER. When a jump extended or return jump microcommand is executed, the incremented contents of the L Register (before the jump address is loaded) are stored in the L Save Register unless storage was inhibited by a previously executed Inhibit L Save (ILS) microcommand. Subsequent execution of a return jump microcommand causes the L Save contents to be transferred back to the L Register. In this manner, the L Save Register acts as a linkage register for a single level subroutine.

When the L Save Stack Option is included in the system, the L Save Register is disabled, and is replaced by an L Save Stack containing 16 registers that perform the same function as the L Save Register. In this case, however, multi-level subroutines are permitted.

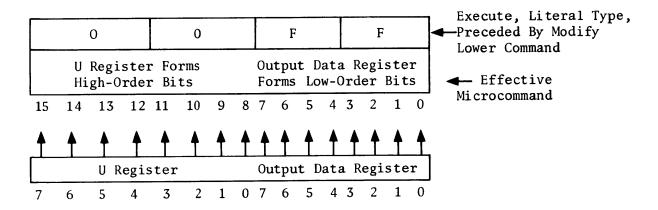

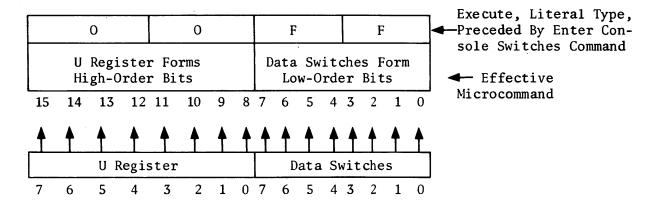

1.6.1.7 R REGISTER. The 16-bit R Register is divided into an upper R Register and a lower R Register. Each microcommand from control memory is supplied via the RS bus and stored in the R Register. For execute-type microcommands, the eight

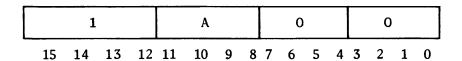

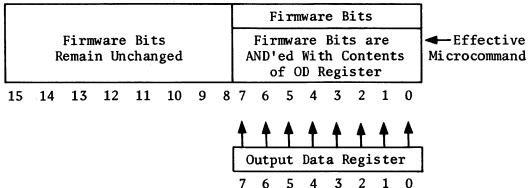

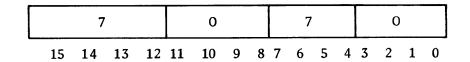

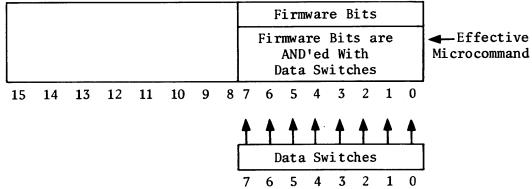

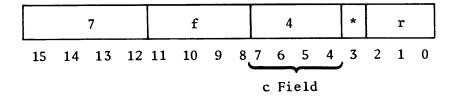

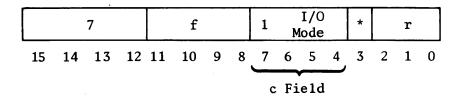

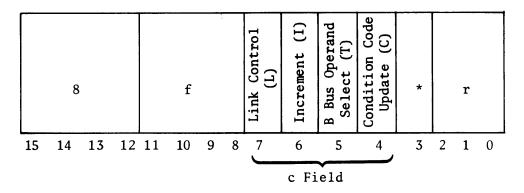

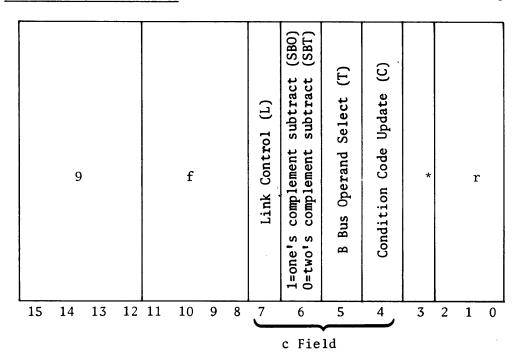

high-order bits from control memory are OR'ed with the contents of the U Register before storage in the R Register. Following execution of a Modify Lower Command (MLC) microcommand, the eight low-order bits of the next microcommand from control memory are AND'ed with the contents of the OD Register before storage in the R Register. Following execution of an Enter Console Switches (ECS) microcommand, the eight low-order bits of the next microcommand from control memory are AND'ed with the states of the eight low-order data switches (on the front panel) before storage in the R Register.