# for DISC STORAGE UNIT CONTROLLER Part No. 900280

**November 1, 1974**

## PROPRIETARY INFORMATION

The information contained herein is proprietary to and considered a trade secret of Basic/Four Corporation and shall not be reproduced in whole or part without the written authorization of Basic/Four Corporation.

basic/four and

are registered trademarks of BASIC/FOUR CORPORATION

# List of Effective Pages

| Pages         | Revision<br>Date |

|---------------|------------------|

| iii/vi        | Original         |

| 1-1 thru 1-17 | Original         |

| 2-1           | Original         |

| 3-1 thru 3-43 | Original         |

| 4-1 thru 4-15 | Original         |

| 5-1 thru 5-4  | Original         |

# TABLE OF CONTENTS

|                                                                                                                                                            |                                                                                                                                                                                                                                                | Page                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| SECTION 1.                                                                                                                                                 | GENERAL DESCRIPTION                                                                                                                                                                                                                            |                                                                                                            |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.5.1<br>1.5.1.1<br>1.5.1.2<br>1.5.1.3<br>1.5.1.4<br>1.5.1.5<br>1.5.1.6<br>1.5.2<br>1.5.3<br>1.5.4<br>1.6<br>1.7<br>1.8 | Scope                                                                                                                                                                                                                                          | 1-1<br>1-3<br>1-4<br>1-6<br>1-6<br>1-7<br>1-8<br>1-9<br>1-9<br>1-10<br>-10<br>1-10<br>1-12<br>1-14<br>1-16 |

| SECTION 2.                                                                                                                                                 | INSTALLATION                                                                                                                                                                                                                                   |                                                                                                            |

| 2.1<br>2.2<br>2.3                                                                                                                                          | Scope                                                                                                                                                                                                                                          | 2-1                                                                                                        |

| SECTION 3.                                                                                                                                                 | THEORY OF OPERATION                                                                                                                                                                                                                            |                                                                                                            |

| 3.1<br>3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2<br>3.2.1.3<br>3.2.2<br>3.2.2.1<br>3.2.2.2<br>3.2.2.3<br>3.2.2.4<br>3.2.2.5<br>3.2.2.6                            | General Overall Block Diagram Description  DMA Channel Logic Interface Logic Control Logic Address Logic Disc Drive Controller CPU/DMA Interface Logic Read/Write Control Logic Data Registers Address Logic Write Logic Read Logic Read Logic | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4<br>3-5<br>3-5                                  |

| SECTION 3. | THEORY OF OPERATION (continued)                  | Page |

|------------|--------------------------------------------------|------|

| 3.3        | Data Flow Description                            | 3-5  |

| 3.3.1      | write Data Path                                  | 3-5  |

| 3.3.2      | Function/Address Data Path                       | 3-6  |

| 3.3.3      | Read Data Path                                   | 3-7  |

| 3.3.4      | Status Data Path                                 | 3-7  |

| 3.4        | DMA Sequences                                    | 3-8  |

| 3.4.1      | Initialization Sequence                          | 3-8  |

| 3.4.1.1    | Major Activity Sequence State 1                  | 3-9  |

| 3.4.1.2    | Major Activity Sequence State 2                  | 3-9  |

| 3.4.1.3    | Major Activity Sequence State 3                  | 3-9  |

| 3.4.1.4    | Major Activity Sequence State 4                  | 3-9  |

| 3.4.2      | Data Transfer Sequence                           | 3-10 |

| 3.4.3      | Status Transfer Sequence                         | 3-11 |

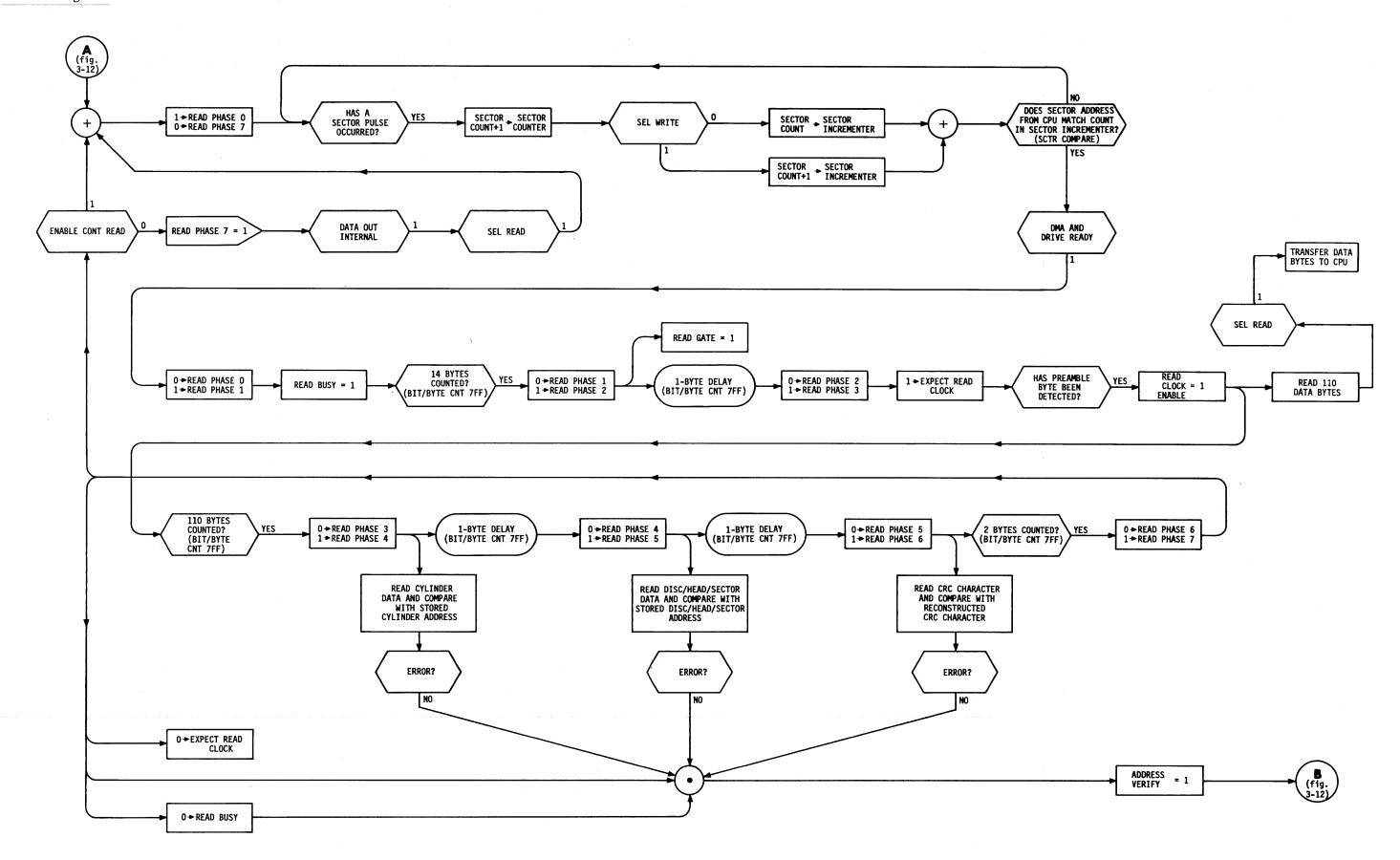

| 3.5        | Disc Drive Controller Sequences                  | 3-11 |

| 3.5.1      | Write Sequence                                   | 3-12 |

| 3.5.2      | Read Sequence                                    | 3-13 |

| 3.6        | DMA Channel Logic Detailed Logic Description     | 3-14 |

| 3.6.1      | Data Receivers                                   | 3-14 |

| 3.6.2      | I/O Control Decoder                              | 3_15 |

| 3.6.3      | Clock and Master Reset Circuits                  | 3-15 |

| 3.6.4      | Device Address Decoder                           | 3-15 |

| 3.6.5      | Sequence Logic                                   | 3-15 |

| 3.6.5.1    | Major Activity Sequencer                         | 3-15 |

| 3.6.5.2    | Memory Cycle Sequencer                           | 3-16 |

| 3.6.5.3    | Address Byte Counter                             | 3-17 |

| 3.6.5.4    | Address Logic Control                            | 3-17 |

| 3.6.5.5    | Memory Cycle Control                             | 3-18 |

| 3.6.6      | Status Control                                   | 3-18 |

| 3.6.7      | End of Block Interrupt Control                   | 3-19 |

| 3.6.8      | Current Address Logic                            | 3-19 |

| 3.6.9      | End Address Logic                                | 3-20 |

| 3.7        | Disc Drive Controller Detailed Logic Description | 3-20 |

| 3.7.1      | CPU Interface Logic                              | 3-20 |

| 3.7.1.1    | Error Logic                                      | 3-20 |

| 3.7.1.2    | Disc Drive Status Receivers                      | 3-21 |

| 3.7.1.3    | Output Data Logic                                | 3-21 |

| 3.7.1.4    | Control Logic                                    | 3-21 |

| 3.7.1.5    | Request Logic                                    | 3-22 |

| 3.7.2      | Read/Write Control Logic                         | 3-23 |

| 3.7.2.1    | Function Decoder                                 | 3-23 |

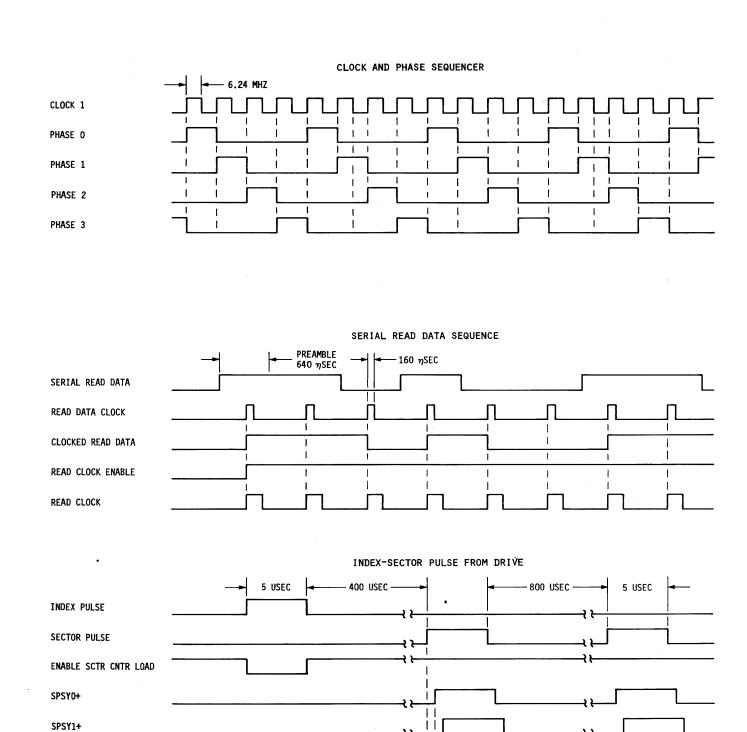

| 3.7.2.2    | Clock Generator and Phase Sequencer              | 3-23 |

| 3.7.2.3    | Sector Logic                                     | 3-24 |

| 3.7.2.4    | Bit/Byte Counters                                | 3-25 |

| 3.7.2.5    | CRC Generator                                    | 3-25 |

| 3.7.3      | Data Registers                                   | 3-26 |

| 3.7.3.1    | Data Register Operation During a Read Sequence   | 3-26 |

| 3.7.3.2    | Data Register Operation During a Write Sequence  | 3-26 |

| 3.7.4      | Address Logic                                    | 3-27 |

| 3.7.4.1    | Cylinder Address Register                        | 3-27 |

| SECTION 3.                                                 | THEORY OF OPERATION (continued) | Page                                                 |

|------------------------------------------------------------|---------------------------------|------------------------------------------------------|

| 3.7.4.2<br>3.7.4.3<br>3.7.5<br>3.7.5.1<br>3.7.5.2<br>3.7.6 | Unit/Disc/Head Select Logic     | 3-27<br>3-27<br>3-28<br>3-28<br>3-28<br>3-29<br>3-29 |

| 3.7.6.2<br>SECTION 4.                                      | Read Data Logic                 | 3-29                                                 |

| 4.1<br>4.2<br>4.3                                          | General                         | 4-1                                                  |

| SECTION 5.                                                 | PARTS LIST                      | 5-1                                                  |

# LIST OF TABLES

| Table |                                                 | Page |

|-------|-------------------------------------------------|------|

| 1-1   | Electrical Characteristics and Performance Data | 1-3  |

| 1-2   | Device Order Codes                              |      |

| 1-3   | Drive Status Byte Format                        |      |

| 1-4   | Controller Status Byte Format                   |      |

| 3-1   | Memory Cycle Sequence States                    | 3-17 |

| 3-2   | Function Command Outputs                        |      |

| 3-3   | Address Bit Multiplexer Bit Selection           |      |

| 4-1   | Logic Glossary                                  |      |

# LIST OF ILLUSTRATIONS

| Figure |                                                                               | Page |

|--------|-------------------------------------------------------------------------------|------|

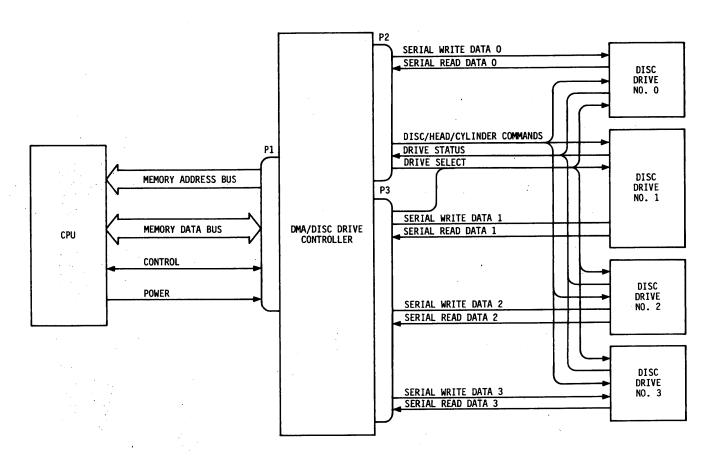

| 1-1    | DMA/Disc Drive Controller, Simplified Block Diagram                           | 1-2  |

| 1-2    | Location of Parts                                                             | 1-5  |

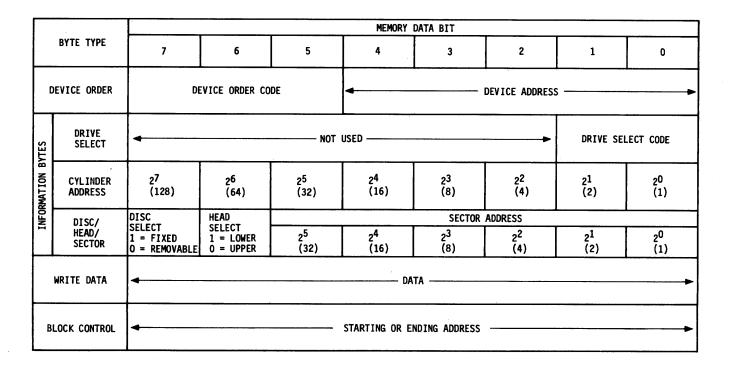

| 1-3    | CPU Output Data Formats                                                       |      |

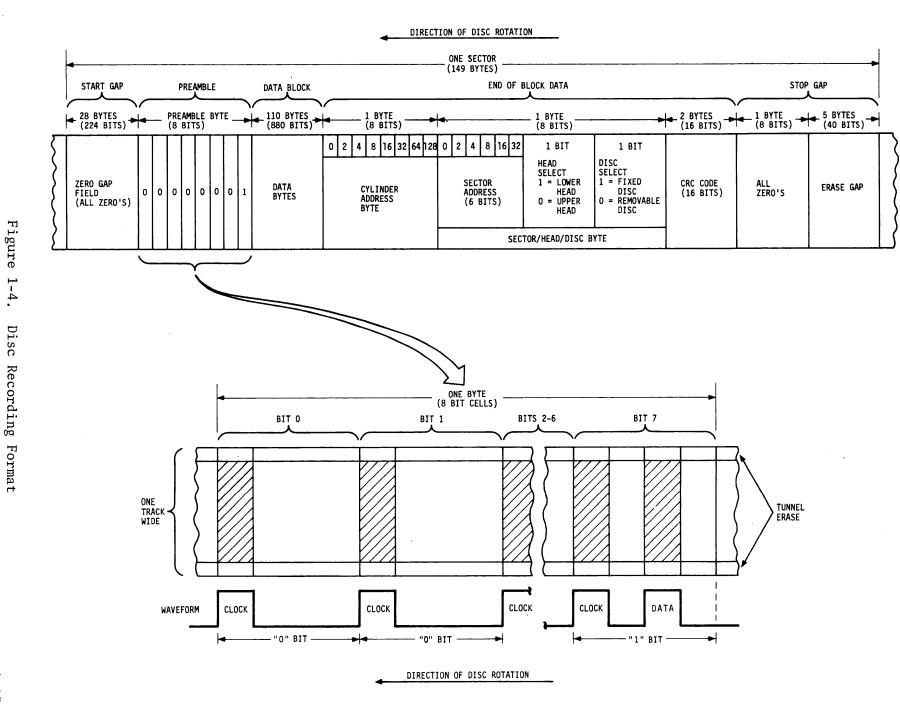

| 1-4    | Disc Recording Format                                                         | 1-6  |

| 2-1    | Interface Diagram                                                             | 1-13 |

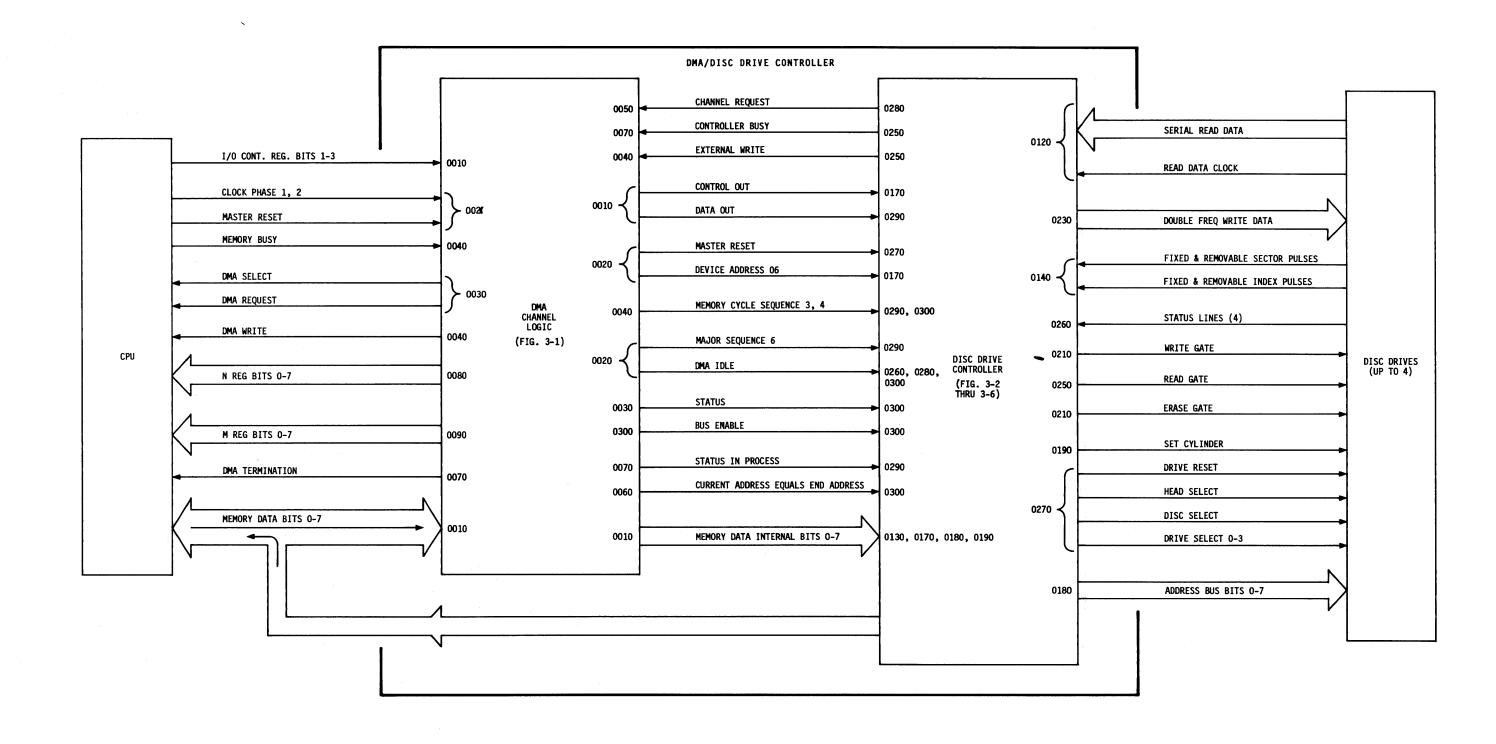

| 3-1    | Overall Block Diagram                                                         | 2-3  |

| 3-2    | Overall Block Diagram .                                                       | 3-31 |

| 3-3    | DMA Channel Logic, Block Diagram  Disc Prive Controller Overall Block Diagram | 3-33 |

| 3-3    | Disc Drive Controller Overall Block Diagram, Sheet 1 of 2                     | 3-35 |

| 3-4    | Disc Drive Controller Overall Block Diagram, Sheet 2 of 2                     | 3-37 |

| 3-4    | DPU/DMA Interface Logic, Block Diagram                                        | 3-39 |

|        | Read/write Control Logic, Block Diagram                                       | 3-41 |

| 3-6    | Address Logic, Block Diagram                                                  | 3-43 |

| 3-7    | mile Logic, block Diagram                                                     | 3-45 |

| 3-8    | Read Logic, block Diagram                                                     | 3-47 |

| 3-9    | Cro-co-bise brive bata Flow                                                   | 3-49 |

| 3-10   | Disc Drive-to-CPU Data Flow                                                   | 3-49 |

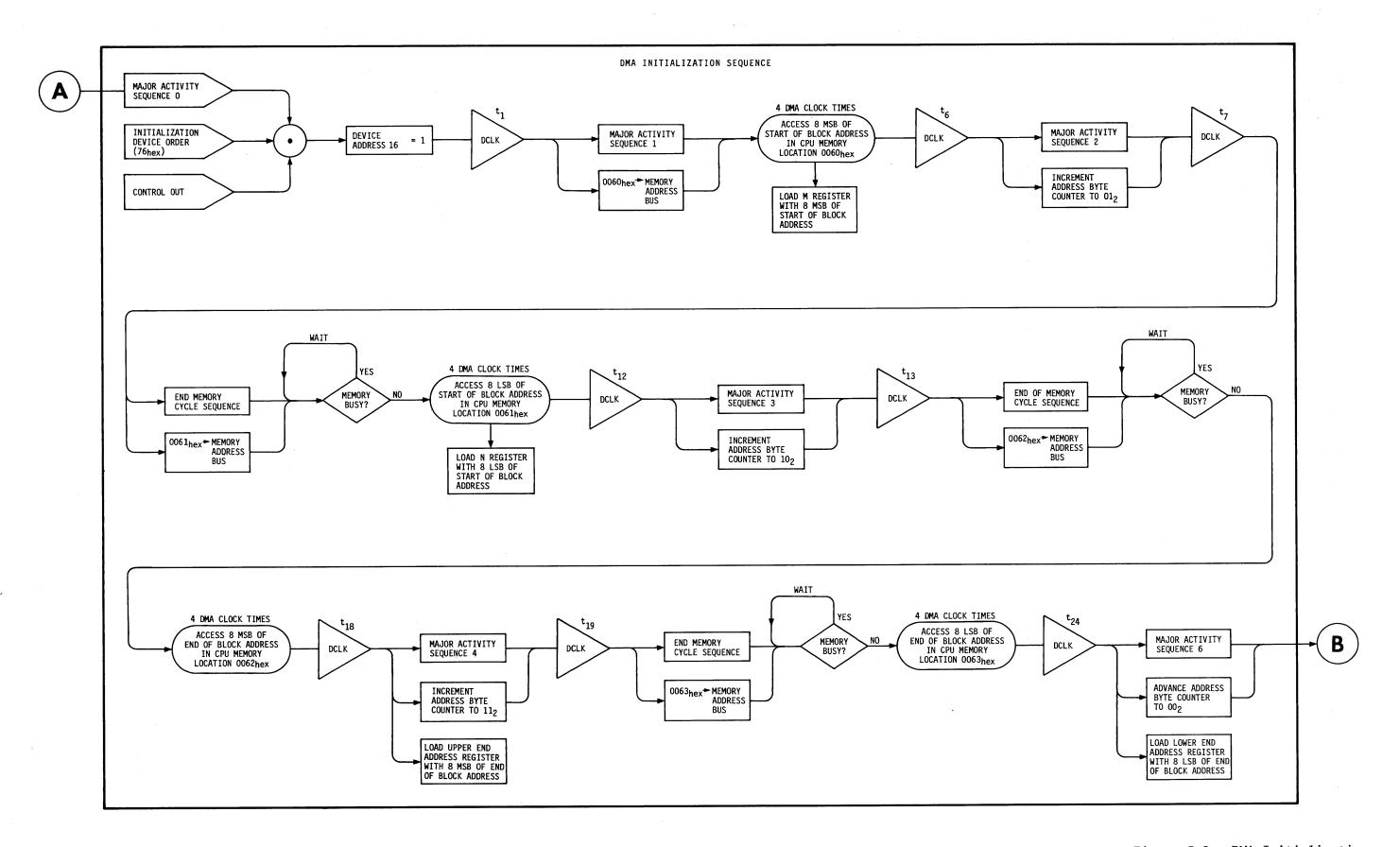

| 3-11   | DMA Sequence Diagram, Sheet 1 of 2                                            |      |

| 3-11   | DMA Sequence Diagram, Sheet 2 of 2                                            | 3-53 |

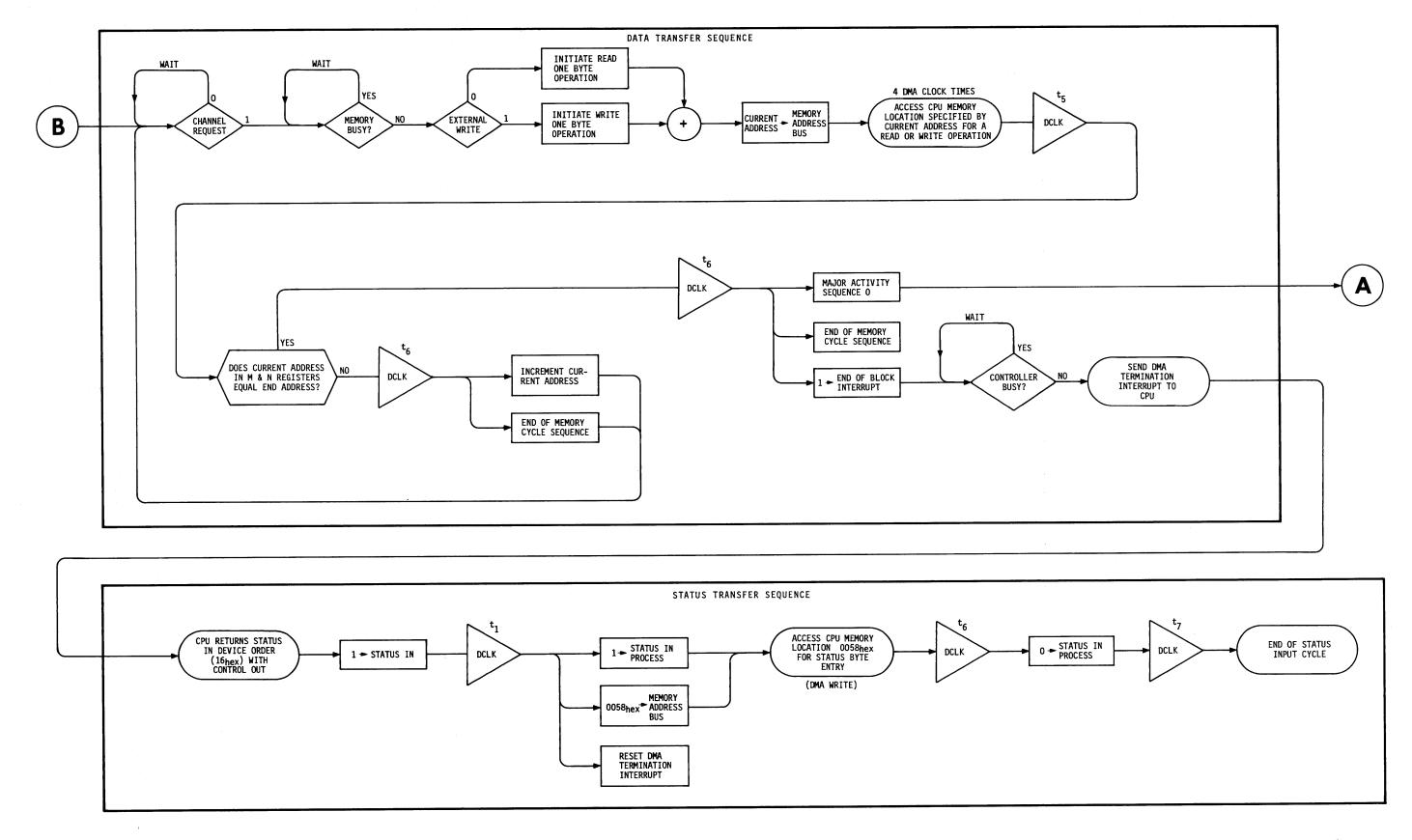

| 3-12   | Write Sequence Flow Diagram                                                   | 3-55 |

| 3-13   | Write Sequence, Flow Diagram                                                  | 3-57 |

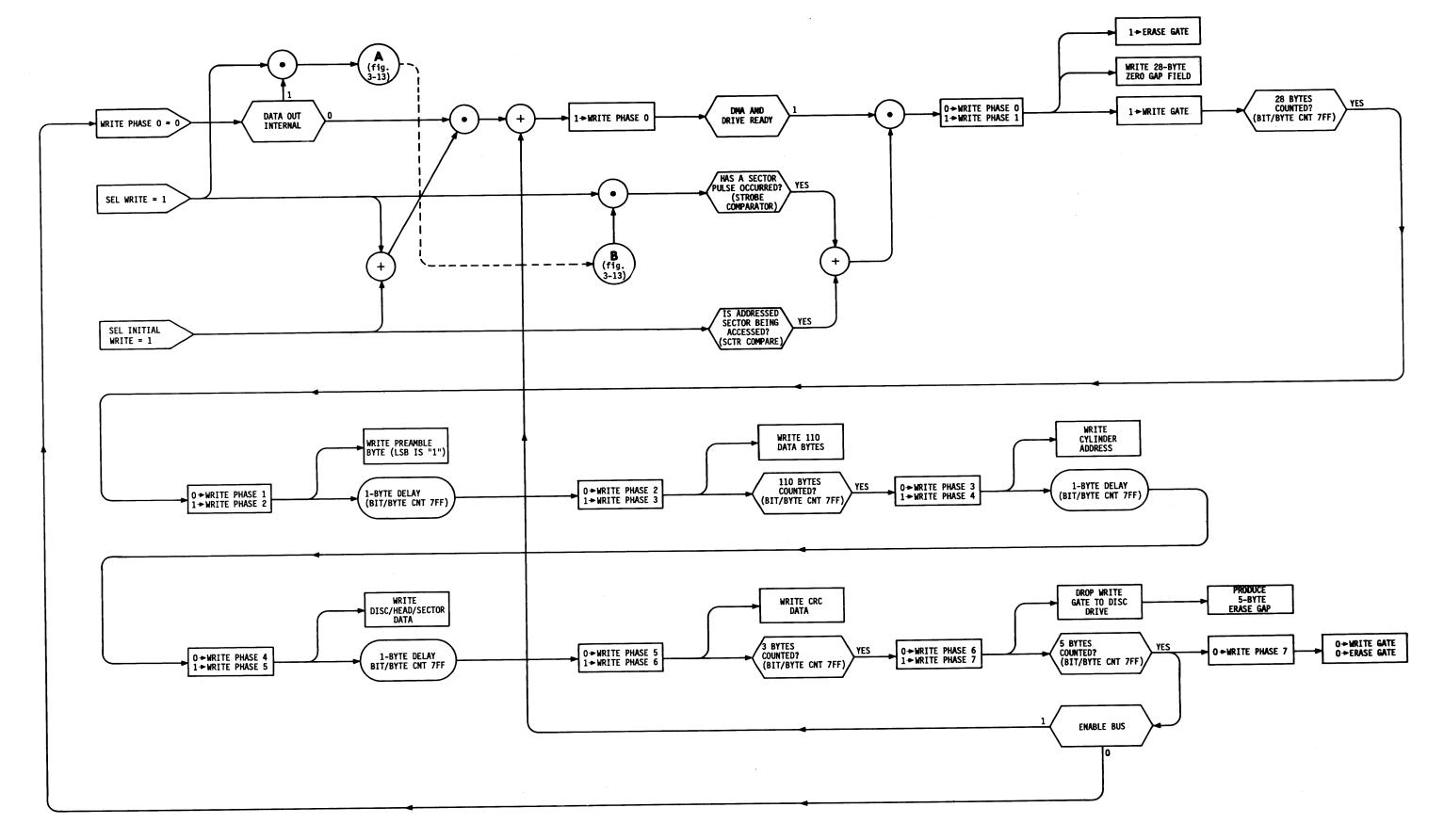

| 3-14   | Read Sequence, Flow Diagram                                                   | 3-59 |

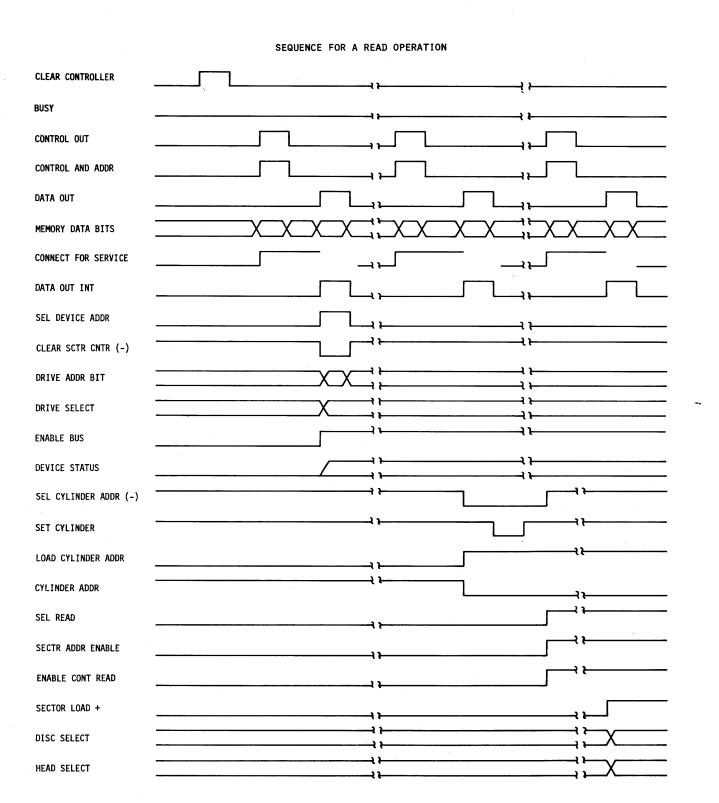

| U 17   | Timing Diagram                                                                | 3-61 |

|        |                                                                               |      |

# Section 1 GENERAL DESCRIPTION

# 1.1 SCOPE

This manual contains general description, installation procedures, theory of operation, and maintenance data for the DMA Disc Storage Unit Controller, Part Number 900280, manufactured by the Basic/Four Corporation, 18552 Mac Arthur Boulevard, Santa Ana, California 92707. The DMA/Disc Storage Unit Controller (called the DMA/disc drive controller) is an integral part of the BASIC/FOUR® data processing systems. The logic diagrams for the DMA/Disc Storage Unit Controller are in LD 2002.

# 1.2 PURPOSE AND FUNCTIONAL DESCRIPTION (figures 1-1 and 1-2)

The DMA/disc drive controller serves as the communications link between the Central Processing Unit (CPU) and up to four Disc Storage Units. Each of the Disc Storage Units (called disc drives) connected to a controller must be functionally identical. The direct memory access (DMA) channel included in the controller is used for communicating with the CPU. The DMA channel is a high-speed port that connects the core memory of the CPU to the disc drive controller, permitting transfer of a block of data bytes between memory and the disc drives. The DMA channel requires minimum attention from the CPU program during a data transfer. Program instructions are used to set up the channel for a block transfer, but, thereafter, all data transfers occur automatically without program intervention.

During a single block transfer operation (to or from the CPU), up to 5,280 eight-bit data bytes can be transferred. To initiate a block transfer, the CPU first initializes the DMA channel, and issues the appropriate device orders to the DMA/disc drive controller, followed by information bytes specifying the disc drive unit and cylinder (track) number address involved in the data transfer. The controller returns disc drive status information to the CPU. After checking status, the CPU issues a read or write device order, followed by a sector address information byte that specifies the disc (fixed or removable), and disc head (upper or lower) to be used for the read or write operation, and also specifying the starting sector of the previously designated cylinder. The controller again returns status information.

Figure 1-1. DMA/Disc Drive Controller, Simplified Block Diagram

If status is correct, the controller executes the data transfer operation, during which data is transferred from memory to the controller for writing on the disc, or data is read from the disc and supplied to the controller for transfer to CPU memory. At the completion of the data transfer, the controller issues an interrupt to the CPU, and the CPU program responds by again checking status. After status is checked, the CPU issues a reset status command to the controller, resetting the disc drive controller and the disc drive.

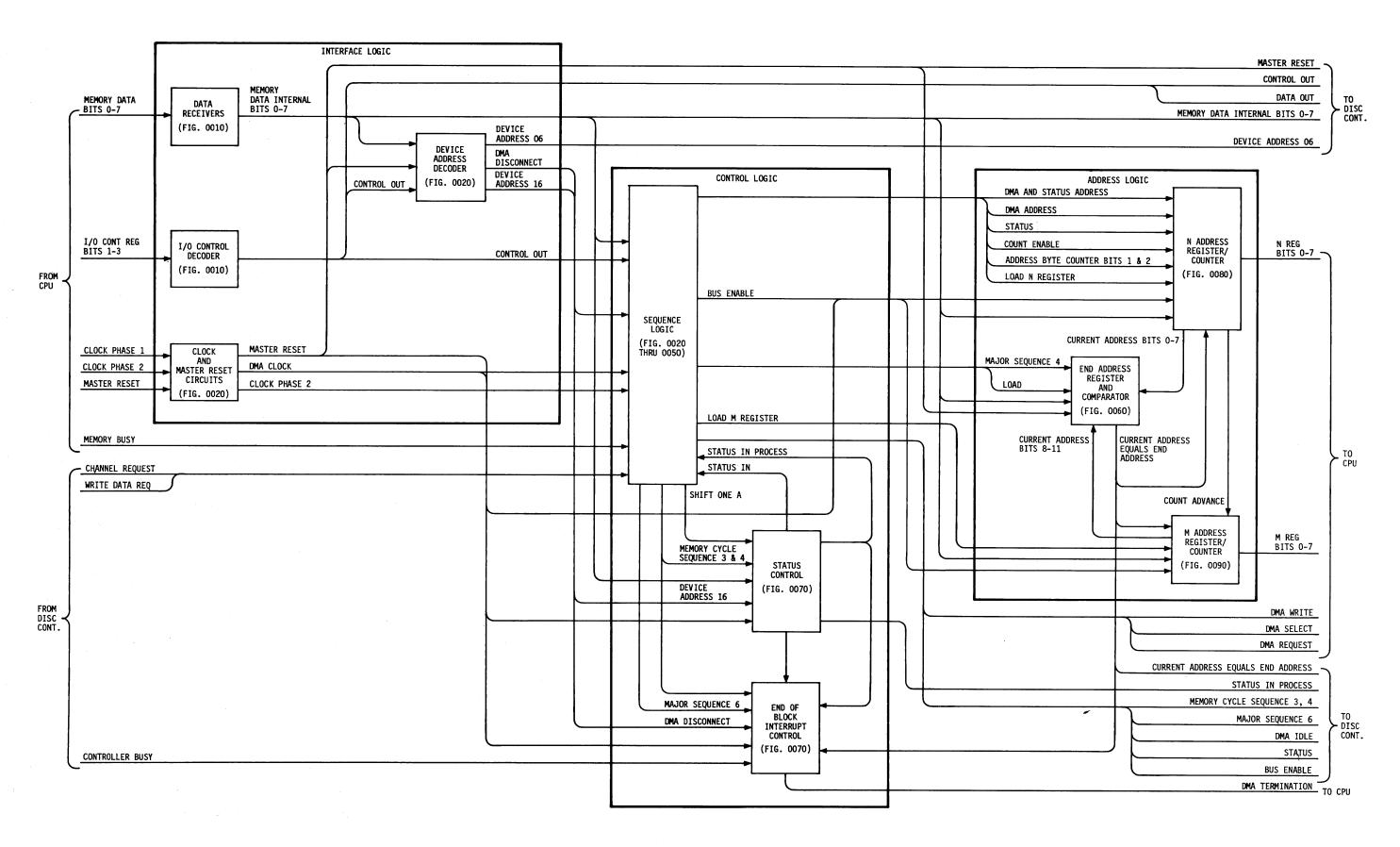

Figure 1-2 shows the relationship to the two prime functions of the DMA/Disc Drive Controller. The DMA channel contains all of the logic interface circuits for communication with the CPU except for output from the Disc Drive Controller to the CPU memory. The Disc Drive Controller contains all of the logic interface circuits for communication with the disc drive units. The four digit numbers on the signal flow lines indicate the page number of the logic diagram in LD 2002 where the signal is shown as an input/output. The blocks representing the DMA channel and the Disc Drive Controller reference block diagrams in Section 3 that expand signal flow in greater detail.

Figure 1-2. Overall Block Diagram

# 1.3 ELECTRICAL CHARACTERISTICS AND PERFORMANCE DATA

Table 1-1 lists the pertinent electrical characteristics and performance data for the DMA/disc drive controller.

Table 1-1. Electrical Characteristics and Performance Data

| Parameter                                         | Characteristic                                                                                  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Input Power Requirements                          | +5vdc, 3 amperes from CPU (supplied via connector P1 on circuit board)                          |

| Environmental:                                    |                                                                                                 |

| Ambient Temperature Range                         | 0 to 50° C.                                                                                     |

| Relative Humidity                                 | Up to 90% without condensation                                                                  |

| Circuit Types                                     | TTL and DTL integrated circuits (IC) used throughout                                            |

| Internal Logic Levels                             | Logical 1 = +5vdc (nominal) logical 0 = 0vdc (nominal)                                          |

| Logic Levels for CPU and<br>Disc Drive Interfaces | Logical 1 = 0vdc (nominal)<br>logical 0 = +3 to 5 vdc                                           |

| Number of Types of Disc Drives                    | Up to four Model 2100 or Model 2200 Disc<br>Storage Units can be handled by one<br>controller.  |

| Disc Recording Technology:                        |                                                                                                 |

| Recording Format                                  | Double-frequency write data (manchester coding)                                                 |

| Data Clock Frequency                              | 6.24 MHz                                                                                        |

| Bit Density                                       | 2200 bits per inch                                                                              |

| Bit Cell Time (nominal)                           | 640 nanoseconds                                                                                 |

| Byte Size                                         | 8 bits                                                                                          |

| Data Transfer Rate                                | 195 kilobytes/second                                                                            |

| Disc Rotational Speed                             | 1500 rpm                                                                                        |

| Number of Discs per Disc Drive                    | Two - one fixed disc and one removable disc, either of which can be accessed by the controller. |

| Track Density                                     | 100 tracks per inch or 200 tracks per inch.                                                     |

| Number of Tracks per Disc<br>(both sides)         | 200, 400, or 800 depending on Model number.                                                     |

Table 1-1. Electrical Characteristics and Performance Data (continued)

| Parameter                                       | Characteristic                                                                                             |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Disc Recording Technology (continued)           | ·                                                                                                          |

| Number of Bit Cells per Track (nominal)         | 72,000                                                                                                     |

| Number of Sectors per Track                     | 48                                                                                                         |

| Number of Data Bytes per Sector                 | 110                                                                                                        |

| Number of Data Bytes per Track                  | 5,280                                                                                                      |

| Number of Data Bytes per Disc                   | 1,056,000 (200 tracks per disc),<br>2,112,000 (400 tracks per disc), or<br>4,224,000 (800 tracks per disc) |

| Number of Data Bytes per Disc Drive (two discs) | 2,112,000 (200 tracks per disc),<br>4,224,000 (400 tracks per disc), or<br>8,448,000 (800 tracks per disc) |

| Access Times:                                   |                                                                                                            |

| Average Random Move                             | 35 to 150 milliseconds                                                                                     |

| Average Rotational Delay                        | 20 milliseconds                                                                                            |

| Average Latency Time                            | 20 milliseconds                                                                                            |

## 1.4 PHYSICAL DESCRIPTION

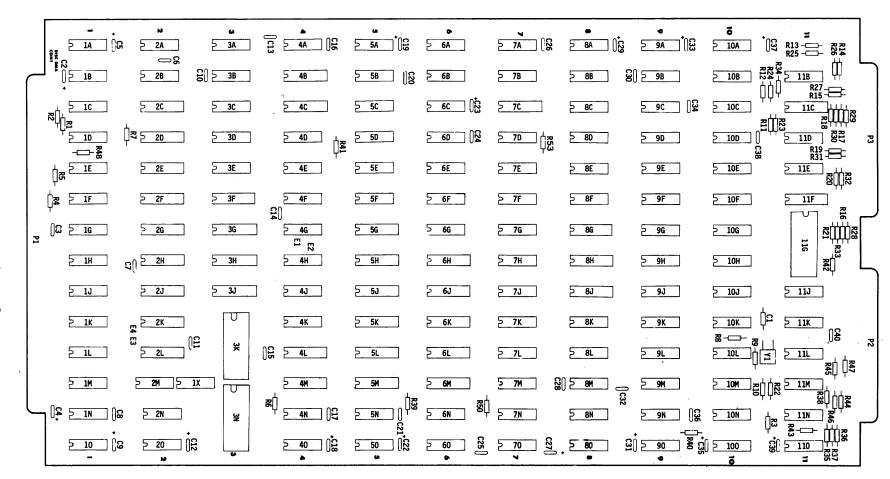

The DMA/disc drive controller is an 8.575 X 16.5-inch printed circuit board assembly containing integrated circuit (IC) elements. Each IC element is soldered into the board. The reference designation for each IC element consists of the row-column grid coordinates shown in figure 5-1. The reference designation consists of a combination of the column letter and the row number; for example, reference designator 4B is the fourth row location in column B. The numbers in each element box shown in figure 5-1 are the reference designation and the IC type number.

External connections are made to three connectors that are an integral part of the circuit board. Connector P1, which is installed in a mating receptacle in the CPU mainframe, connects the controller to the CPU. A cable assembly from the disc drive units is connected to connectors P2 and P3.

# 1.5 DATA FORMATS

This paragraph describes the data formats for the various types of data exchanged between the CPU and the controller, and also describes the format of the data written on the magnetic discs.

# 1.5.1 CPU OUTPUT DATA FORMATS (figure 1-3)

Figure 1-3 shows the various types of output data formats that can be present on the bi-directional MEMORY DATA bus from the CPU to the controller. Bit MEMORY DATA BIT 7 is the most significant bit (MSB), and bit MEMORY DATA BIT 0 is the least significant bit (LSB). As shown in figure 1-3, six types of output data bytes are sent to the controller.

The device order byte is accompanied by the CONTROL OUT code (001<sub>2</sub>) in I/O CONTROL REG BITS 3-1 from the CPU. The presence of the CONTROL OUT code notifies the controller that a device order byte is on the MEMORY DATA lines. Although the device order byte is placed on the MEMORY DATA lines, it does not originate in the CPU memory, and a memory cycle is not performed to place the byte on the lines.

Figure 1-3. CPU Output Data Formats

The three types of information bytes (Drive Select, Cylinder Address, and Disc/Head/Sector) also originate outside of CPU memory. An information byte is accompanied by the DATA OUT code  $(010_2)$  in I/O CONTROL REG BITS 1-3 from the CPU. The presence of DATA OUT notifies the controller that an information byte is on the MEMORY DATA lines.

The Write Data and Block Control bytes are contained in CPU memory. The DMA channel must specify the memory address location of the byte to be accessed by sending a 16-bit memory address to the CPU. Then the DMA channel issues a memory cycle request to the CPU. The CPU responds (if the memory is not otherwise busy) by executing a memory read cycle, during which the byte in the addressed memory location is placed on the MEMORY DATA lines to the controller.

The succeeding subparagraphs describe each of the six output data byte types from the CPU.

1.5.1.1 <u>Device Order Byte.</u> This byte contains a device address in MEMORY DATA BITS 4 through 0, and contains a device order in MEMORY DATA BITS 7 through 5. Device orders for the DMA channel section contain device address 16 hex. Device orders for disc drive controller section contain device address 06 hex. The device order codes are explained in table 1-2.

Table 1-2. Device Order Codes

| Device            | Memory Data Bit |   |   |                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------------------|-----------------|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Address*          | 7               | 6 | 5 | Definition                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 16 <sub>hex</sub> | 0               | 0 | 0 | Status In. This device order causes the DMA channel section to place memory address 0058hex on the memory address bus to the CPU, and causes the controller to place a status byte on the MEMORY DATA lines to the CPU. The DMA channel executes a status transfer sequence that causes the CPU to perform a memory write cycle, during which the status byte is stored in the addressed memory location. |  |

| 06 <sub>hex</sub> | 0               | 0 | 0 | <u>Drive Select</u> . Notifies the controller that a drive select information byte is coming.                                                                                                                                                                                                                                                                                                             |  |

| <sup>06</sup> hex | 0               | 0 | 1 | Cylinder Select. Notifies the controller that a cylinder address information byte is coming.                                                                                                                                                                                                                                                                                                              |  |

| Device            | Memo | ry Dat | a Bit | D. Cimitai                                                                                                                                                                                                                                         |

|-------------------|------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address*          | 7    | 6      | 5     | Definition                                                                                                                                                                                                                                         |

| 06 <sub>hex</sub> | 0    | 1      | 0     | Select Read. Sets up the controller for a read operation.                                                                                                                                                                                          |

| 06<br>hex         | 0    | 1      | 1     | Select Write. Sets up the controller for a normal write operation.                                                                                                                                                                                 |

| 16 <sub>hex</sub> | 0    | 1      | 1     | Initialize Channel. Commands the DMA channel to execute an initialization sequence during which start of block and end of block addresses are fetched from CPU memory and stored in the DMA channel in preparation for a block transfer operation. |

| 16 <sub>hex</sub> | 1    | 0      | 0     | DMA Disconnect. Unconditionally disconnects the DMA channel from the CPU, and resets the DMA channel.                                                                                                                                              |

| 06 <sub>hex</sub> | 1    | 0      | 0     | Select Initial Write. Used to write positional information on a new disc. Identical to the normal write operation, with the exception that positional checking is not performed, and the write operation is limited to a single sector.            |

| 06 <sub>hex</sub> | 1    | 0      | 1     | Reset Status. Initiates reset action in the disc drive controller and the disc drives.                                                                                                                                                             |

| 06 <sub>hex</sub> | 1    | 1      | 0     | Alternate Status Function. Commands the controller to return controller status information, rather than drive status information, to the CPU.                                                                                                      |

| 06 <sub>hex</sub> | 1    | 1      | 1     | Not used.                                                                                                                                                                                                                                          |

Table 1-2. Device Order Codes (continued)

1.5.1.2 <u>Drive Select Byte</u>. Following the occurrence of a drive select device order, a DATA OUT control code from the CPU notifies the controller that a drive select byte is on the output bus. The drive select byte contains a two-bit code in bits MEMORY DATA BIT 1 through 0 that selects one of the four disc drive units connected to the controller. The section codes are as follows:

<sup>\*</sup> Device address  $16_{\rm hex}$  is the DMA channel section; device address  $06_{\rm hex}$  is the disc drive controller section.

| MEMORY 1 | DATA BIT<br>0 | Selected Disc Drive |

|----------|---------------|---------------------|

| 0        | 0             |                     |

| U        | Ü             | . 0                 |

| 0        | 1             | 1                   |

| 1        | 0             | 2                   |

| 1        | 1             | 3                   |

1.5.1.3 Cylinder Address Byte. Following the occurrence of a cylinder select device order, a DATA OUT control code from the CPU notifies the controller that a cylinder address byte is on the output bus. The cylinder address byte contains an eight-bit binary code designating one of the 203 cylinders on each side of the disc.

1.5.1.4 <u>Disc/Head/Sector Byte</u>. Following the occurrence of a select read, select write, or select initial write device order, a DATA OUT control code from the CPU notifies the controller that a disc/head/sector byte is on the output bus. Bit MEMORY DATA BIT 7 contains the disc select code; a 1 in bit 7 selects the fixed disc and a 0 in bit 7 selects the removable disc.

Bit MEMORY DATA BIT 6 contains the head select code that designates the side of the disc on which the operation is to be performed; a 1 in this bit selects the lower head and a 0 in bit 6 selects the upper head.

Bits MEMORY DATA BIT 5 through 0 contain a six-bit binary code designating one of the 48 sectors on the cylinder selected by the cylinder address byte.

1.5.1.5 Write Data Byte. When the controller and disc drive are ready to execute a block data transfer to write data on the disc, the controller issues a CHANNEL REQUEST to the DMA channel for each byte to be written on the disc. The DMA channel responds by issuing low DMA SELECT and DMA REQUEST signals, and a high DMA WRITE signal to the CPU. Also, the next address is placed on the memory address lines to the CPU. The CPU responds by executing a memory read cycle, during which the byte in the addressed location is read from memory and placed on the MEMORY DATA lines. The controller accepts the byte and serially transmits it to the disc drive for writing on the disc in the selected sector of the addressed cylinder.

1.5.1.6 <u>Block Control Byte</u>. During initialization of the DMA channel, the DMA channel requests four 8-bit block control bytes from the CPU. To request each byte, the DMA channel issues low DMA SELECT and DMA REQUEST signals, and a high DMA WRITE signal to the CPU. Also, the address (0060<sub>hex</sub>, 0061<sub>hex</sub>, 0062<sub>hex</sub>, or 0063<sub>hex</sub>) of the block control byte is placed on the memory address bus to the CPU. Address locations 0060 and 0061 contain the start of block memory address, and locations 0062 and 0063 contain the end of block memory address. During the initialization sequence, these four bytes are fetched from CPU memory and stored in the DMA channel.

#### 1.5.2 CPU READ DATA

Eight-bit data bytes read from the disc are presented to the CPU on the MEMORY DATA bus. For each byte to be transferred to the CPU, the controller issues a CHANNEL REQUEST to the DMA channel. The DMA channel responds by issuing low DMA REQUEST, DMA SELECT, and DMA WRITE signals to the CPU. Also, the next address is placed on the memory address bus to the CPU. The CPU responds by executing a memory write cycle, during which the byte on the MEMORY DATA bus is written into the addressed memory location.

# 1.5.3 STATUS BYTE FORMATS (tables 1-3 and 1-4)

A status byte is placed on the MEMORY DATA bus to the CPU in response to a Status In device order (see table 1-2). The content of the status byte depends on whether or not an Alternate Status Function device order (see table 1-3) preceded the Status In device order. When no Alternate Status Function device order was received, the status byte contains drive status information, as described in table 1-3. When an Alternate Status Function device order was received, the status byte contains controller status information, as described in table 1-4. The DMA channel responds to the Status In device order by placing code 0058hex on the memory address lines. Then the DMA channel issues low DMA REQUEST, DMA SELECT, and DMA WRITE signals to the CPU. The CPU responds by performing a memory write cycle, during which the status byte on the MEMORY DATA bus is written into memory location 0058hex.

Table 1-3. Drive Status Byte Format

| Device Status<br>Bit No. | Description                                                                                                                                                                                                                                                                                                           |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                        | DMA Idle. This bit is a 1 when the DMA channel logic is in major activity sequence state 0.                                                                                                                                                                                                                           |

| 1                        | Ready to Seek, Read or Write. This bit is a 1 when all of the following status conditions exist:                                                                                                                                                                                                                      |

|                          | <ul> <li>a. The controller is not busy.</li> <li>b. The DRIVE READY status signal from the disc drive is active.</li> <li>c. The ACCESS READY status signal from the disc drive is active.</li> <li>d. The SEEK INCOMPLETE and WRITE UNSAFE status signals from the disc drive are both inactive.</li> </ul>          |

| 2                        | Read Error. This bit is a 1 when a CRC or address error is detected at the end of a read operation. During a write operation, a 1 in this bit indicates that a read error was detected in the sector preceding the sector in which data is to be written. This bit is also a 1 when an overrun condition is detected. |

| 3                        | Access Not Ready. This bit is a 1 when the ACCESS READY status signal from the disc drive is inactive, indicating that a command to move the heads to another cylinder is being executed.                                                                                                                             |

| 4                        | Seek Incomplete. This bit is a 1 when the SEEK INCOMPLETE status signal from the disc drive is active, indicating that a seek operation was not completed due to a malfunction.                                                                                                                                       |

| 5                        | Write Unsafe. This bit is a 1 when the WRITE UNSAFE status signal from the disc drive is active, indicating that an abnormal condition exists in the disc drive or the external power supplies, and writing of records may not be possible.                                                                           |

| 6                        | Disc Drive Ready. This bit is a 1 when the DRIVE READY status signal from the disc drive is active, indicating that:                                                                                                                                                                                                  |

|                          | <ul> <li>a. The drive is properly supplied with power.</li> <li>b. The drive is loaded with a disc cartridge.</li> <li>c. The load/unload switch is in the load position.</li> <li>d. The green ready light is not on.</li> </ul>                                                                                     |

| 7                        | End of Block. This bit is a 1 when the DMA detects an end of block condition.                                                                                                                                                                                                                                         |

7

Device Status Description Bit No. 0 DMA Idle. This bit is a 1 when the DMA channel logic is in major activity sequence state 0. 1 Ready to Seek, Read or Write. Same as bit 1 of drive status byte. 2 \*Read Error. Same as bit 2 of drive status byte. 3 Access Not Ready. Same as bit 3 of drive status byte. 4 \*CRC Error. This bit is a 1 when a CRC error is detected during a read operation. 5 \*Cylinder Address Error. This bit is a 1 when a discrepancy exists between the cylinder address read from the disc and the cylinder address received from the CPU. 6 \*Sector Address Error. This bit is a 1 when a discrepancy

exists between the disc/head/sector data read from the disc

End of Block. This bit is a 1 when the DMA channel logic

and the disc/head/sector data received from the CPU.

Table 1-4. Controller Status Byte Format

detects an end of block condition.

## 1.5.4 DISC RECORDING FORMAT (figure 1-4)

Bits are recorded serially on the disc in a manchester coding form. A binary 0 bit is represented by a clock at the beginning of a bit cell, with no subsequent flux reversals in the remainder of the bit cell. A binary 1 bit contains a clock at the beginning of the bit cell, followed by a second flux reversal (data clock) in the center of the bit cell. One recording byte contains eight serial bit cells, written on one of the 406 tracks of the disc. Each track is divided into 48 sectors containing 1,200 bit cells (150 bytes). Of these 150 bytes, one is spare, and the other 149 are shown in figure 1-4. Each sector contains all of the elements shown, broken down as follows, starting at the beginning of the sector:

<sup>\*</sup> For a write operation, these bits indicate error status for the sector preceding the sector in which a write operation is to be performed.

- a. Start Gap. This portion contains 28 bytes in which all 0's are written (zero gap field).

- b. Preamble Byte. This byte contains a 1 in the least significant bit position, and 0's in the remaining seven bit positions.

- c. Data Bytes. This section contains 110 data bytes received from the CPU.

- d. End of Block Data. This section contains four bytes. The first byte contains the eight-bit cylinder address code (the number of the cylinder in which the sector is located). The second byte contains the six-bit sector address code (the number of the sector), followed by one-bit codes indicating the selected head (upper or lower) and selected disc (fixed or removable). The final two bytes contain the 16-bit cyclic redundancy check (CRC) character used to check for the presence of data errors during a read operation.

- e. Stop Gap. Following the CRC character, all 0's are written for one byte. Then for the next five bytes, an erase gap is written (no flux reversals).

# 1.6 TYPICAL SEQUENCE OF OPERATION

This paragraph describes a typical sequence of events for performing a read or write operation on a single sector (110 data bytes). Interface signals between the CPU and the controller that are mentioned in this discussion are shown in figure 2-1. As noted in the discussion that follows, all of these events are not necessarily required for each read or write operation. The sequence of events is as follows:

- a. DMA Initialization. The CPU issues the initialize channel device order to the DMA channel, which responds by fetching and storing the memory addresses for the start and end of the data block to be transferred. At the end of the initialization sequence, the DMA channel is ready for a block data transfer. When a single sector is being read or written, the end of block address is equal to the start of block address plus 109.

- b. Drive Select. This operation is only required immediately after power on, or when the previous operation was on a different disc drive. After initializing the DMA channel, the CPU issues CONTROL OUT and places the drive select device order on the MEMORY DATA bus. The controller accepts and stores the device order. Next, the CPU places the drive select byte on the MEMORY DATA bus, and issues DATA OUT. The controller accepts, stores, and decodes the drive select code, and activates the DRIVE SELECT line to the designated disc drive. Status signals from the selected disc drive are returned to the controller, which supplies a drive status byte to the CPU in response to a status in device order. Bit 1 of the status byte (ready to seek, read or write) must be a 1 for the sequence to continue.

- c. Cylinder Select. This operation is required only when the previous operation was on a different cylinder. The CPU issues CONTROL OUT and places the cylinder select device order on the MEMORY DATA bus. The controller accepts and stores the device order. Then the CPU places the cylinder address byte on the MEMORY DATA bus, and issues DATA OUT. The controller accepts and stores the cylinder address byte, and supplies the code and a SET CYLINDER command to the previously selected disc drive. The disc drive responds by slewing the head/arm assembly to the designated cylinder of the disc. Bit 3 (access not ready) of the status byte must be a 0 for the sequence to continued.

- d. Initiate Read or Write. The CPU issues CONTROL OUT and places the select read, select write, or select initial write device order on the MEMORY DATA bus. The controller accepts and stores the device order. Then the CPU places the disc/head/sector byte on the MEMORY DATA bus, and issues DATA OUT. The controller accepts and stores the disc/head/sector byte, and sends disc and head select commands to the previously selected disc drive. If a select write device order was issued, the controller initiates a read operation in the sector preceding the sector in which the write operation is to be performed. The end of block data (positional information) in this sector is checked. The status byte indicates whether a positional (read) error was detected. If the positional information is correct, a write operation is initiated in the next sector. If the device order was select read or select initial write, no positional checking is performed and the operation commences when the heads are at the beginning of the designated sector.

- e. Transfer Data. During this operation, 110 data bytes are transferred from the CPU to the controller for writing on the disc (write operation), or 110 data bytes are read from the disc and transferred (via the controller) to the CPU (read operation). A CHANNEL REQUEST to the DMA channel precedes each byte transfer. The state of the DMA WRITE line to the CPU indicates whether the transfer is to (DMA WRITE low) or from (DMA WRITE high) the CPU. The CPU returns the write data bytes (write operation), or accepts the read data bytes (read operation).

- f. Process End of Block Data. Following the transfer of the 110 data bytes, the end of block data is processed. In a write operation, the end of block data (see figure 1-4) is written on the disc. In a read operation, the end of block data is read from the disc and checked for the presence of errors. If errors are detected, the appropriate error latches in the controller are set.

- g. End of Block Interrupt. When the DMA channel detects that the current memory address equals the end of block address, the DMA termination line to the CPU goes low, indicating that the operation is completed.

- h. Alternate Status Function. The CPU responds to the DMA termination interrupt by issuing CONTROL OUT and placing the alternate status function device order on the output bus. The controller accepts and stores the device order, and returns the controller status byte to the CPU, in response to a status in device order.

i. <u>Disconnect</u>. After status is checked, the CPU issues CONTROL OUT and places the reset status device order on the output bus. The controller accepts and stores the device order. Then the CPU issues DATA OUT. After a fixed delay, the controller and disc drive are both reset.

# 1.7 DISC FILE ACCESSING TECHNIQUES

As mentioned previously, each disc has either 200 (Model 2100) or 400 (Model 2200) tracks, each divided into 48 sectors. Each sector is capable of storing 110 eight-bit data bytes. Mechanical pickups on the rotating disc turntable produce index and sector pulses as the disc rotates. An index pulse occurs once every disc revolution to indicate the starting (0) sector. At the beginning of each sector, a sector pulse is produced.

The sector and index pulses from the disc drive are supplied to the disc drive controller, where they control the operation of sector counters. Each time the index pulse occurs, the sector counters are reset to 0. Then, as the disc rotates, the sector counters tally the sector pulses to provide an indication of the positional location (sector number) of the disc head.

The CPU specifies the disc (fixed or removable), and the side of the disc (upper or lower) for each read or write operation, by issuing appropriate select codes (disc and head select) to the controller for transmittal to the disc drive. To access a particular data block on the designated side of the selected disc, the CPU issues cylinder and sector address codes to the controller. The cylinder address code is transmitted to the disc drive, and the disc drive responds by slewing the head/arm assembly to the cylinder specified by the address. Once the cylinder is accessed, the sector address from the CPU (stored in the controller) is compared with the sector count from the sector counters until the sector count matches the stored sector address. At this time, the heads are in the correct position for reading or writing the data block, and the data transfer commences.

# 1.8 ERROR CHECKING (figure 1-4)

During a read operation (performed in response to a select read device order, and also performed on the sector preceding the sector to be written when a select write device order is received), the DMA/disc drive controller checks the end of block data for the presence of errors. The presence of errors is indicated in the status bytes.

Each time a write operation is performed in response to a select write or select initial write device order, end of block data (see paragraph 1.5.4) is written in each sector of the disc. Included in the end of block data is positional information (cylinder and sector addresses and disc and head select codes) and a 16-bit cyclic redundancy check (CRC) character. The positional information is derived from the cylinder address, head select, and disc select codes received from the CPU, and from the sector count contained in the sector counters. The CRC character is derived by shifting each bit written in the sector (all data preceding the CRC character) into a CRC generator in the controller. The CRC generator produces a 16-bit character whose bit pattern is a unique function of the states of all of the data bits written in the sector.

An overrun error may occur if the trailer of a sector is magnetically destroyed. When this coniditon exists it is detected by the controller and the CPU is notified that there has been a read error.

During a read operation, the positional information in the end of block data is read from the disc and compared with the cylinder, disc, head, and sector information currently contained in the controller. A compare mismatch indicates a positional error. Starting at the beginning of the sector, each data bit read from the disc is shifted into the CRC generator. At the time that the CRC character is read from the disc, the reconstructed CRC character in the CRC generator should be identical to the CRC character read from the disc. A compare mismatch indicates that a data error occurred. The data error can be the result of any of the following:

- a. The record was incorrectly written on the disc.

- b. The record was incorrectly read from the disc.

- c. A data error occurred in the controller.

#### Section 2

#### INSTALLATION

# 2.1 SCOPE

This section contains instructions and data required for installing the DMA/Disc Storage Unit Controller in the CPU, and making connections to the disc storage units.

# 2.2 INSTALLATION IN THE CPU

The DMA/Disc Storage Unit Controller is installed in the last slot in the CPU (slot 17). Connector P1 of the circuit board inserts into the slot in the CPU mainframe. The signal interface between the circuit and the CPU are shown in the figure on page iv of LD 2002.

The DMA/Disc Storage Unit Controller has a pre-wired address of  $16_{

m hex}$  for the DMA and an address of  $06_{

m hex}$  for the disc storage unit controller. If another address is assigned, wiring changes must be made.

# 2.3 CONNECTIONS TO THE DISC STORAGE UNITS

As shown on page iv of LD 2002, up to four disc storage units are connected by a cable to connectors P2 and P3 of the circuit board. Connector P3 is used only when more than one disc storage unit is connected to the controller. With the exception of the DRIVE SELECT, SERIAL READ DATA, READ DATA CLOCK and DOUBLE FREQ WRITE DATA lines, all signals between the controller and the disc storage units are on a common bus to each disc storage unit. Each of the four DRIVE SELECT lines must be connected so that the assigned number of each disc storage unit corresponds to the function assigned in the CPU program.

# Section 3

#### THEORY OF OPERATION

# 3.1 GENERAL

This section contains detailed theory of operation for the DMA/Disc Storage Unit Control (DMA disc drive controller). Logic signal names (all capital letters) mentioned in the descriptions that follow are as they appear on the logic diagrams in Logic Diagrams Manual LD 2002. Following the logic signal name, a negation symbol (-) is added if the signal is a logical 0 (false) when the active state of the signal exists (indicated by a minus sign suffixed to the mnemonic in LD 2002). If no negation symbol is indicated, the signal is a logical 1 (true) when the active state of the signal exists (indicated by a plus sign suffixed to the mnemonic in LD 2002). Unless otherwise specified, a true (1) logic level is +5v, and a false (0) level is 0v.

# 3.2 BLOCK DIAGRAM DESCRIPTIONS

The following paragraphs describe the functioning of the DMA/Disc Drive Controller. Each description references a block diagram which illustrates signal flow and references specific pages in LD 2002. The descriptions are divided into the two groups illustrated in figre 1-2; DMA channel and Disc Drive Controller.

#### 3.2.1 DMA CHANNEL LOGIC (figure 3-1)

The DMA channel logic communicates with the CPU to initiate and control block data transfers between the CPU and the disc drive controller. In response to a channel initialization device order from the CPU, start of block and end of block addresses are fetched from the CPU memory and stored in address registers in the DMA channel logic. After initialization, the DMA channel logic is ready to service the disc drive controller for a read or write block transfer operation. Starting with the start of block address, data bytes are written into, or fetched from, the CPU memory.

Each time a data byte transfer is completed, a current address register in the DMA channel logic is incremented. The data transfers continue until the current address equals the end of block address that was stored in the DMA channel logic during the initialization sequence. When the end of block condition is detected, the DMA channel logic initiates a DMA termination interrupt to the CPU.

Normally, the CPU responds to a DMA termination interrupt by issuing a status input device order addressed to the DMA channel logic. The DMA channel logic responds by placing a status byte memory address code (0058 hex) on the memory address lines to the CPU, and commanding the disc drive controller to place a device status byte on the MEMORY DATA lines to the CPU. The CPU responds by storing the status byte in the memory address location specified by the DMA channel logic.

Included in the DMA channel logic are the MEMORY DATA line receivers, which distribute the MEMORY DATA bits (from the CPU) throughout the DMA/disc drive controller. The MEMORY DATA bus between the CPU and the DMA disc drive controller is bidirectional. That is, write data block control words, information bytes, or device orders are supplied over the MEMORY DATA bus to the DMA/disc drive controller, and read data or status bytes from the DMA/disc drive controller are supplied over the bus to the CPU. The direction of data flow depends upon the operation being performed.

- 3.2.1.1 Interface Logic. The interface logic includes the data receivers for the MEMORY DATA inputs from the CPU, the I/O control decoder that decodes the three-bit I/O control codes from the CPU, the receivers for the clock and master reset signals received from the CPU, and the device address decoder that detects the presence of device address code  $06_{\rm hex}$  (disc drive controller address) or  $16_{\rm hex}$  (DMA address) in device orders received from the CPU.

- 3.2.1.2 Control Logic. The control logic controls the initialization, data transfer, and status transfer sequences performed by the DMA channel logic. The initialization sequence is performed in response to an initialization device order addressed to the DMA. The data transfer sequence is performed following initialization in response to channel requests from the disc drive controller, and continues until either an end of block condition is detected (DMA termination interrupt), or until a DMA disconnect device order is received from the CPU. The status transfer sequence is performed in response to a status input device order from the CPU.

Figure 3-1. DMA Channel Logic, Block Diagram

3.2.1.3 Address Logic. The address logic includes an end address register and comparator, and a current address register/counter (M and N registers). Gating included as part of the M and N registers permits either the contents of the M and N registers or a fixed address  $(0058_{\rm hex},\ 0060_{\rm hex},\ 0061_{\rm hex},\ 0062_{\rm hex},\ or\ 0063_{\rm hex})$  to be gated onto the memory address bus to the CPU. The fixed addresses are used during initialization (addresses 0060 through 0063), or during a status transfer (address 0058).

During initialization, the end address register is loaded with the end of block addresses, and the M and N registers are loaded with the start of block address. During a data transfer sequence, the M and N registers are incremented one count each time a data transfer is completed, setting up the memory address for the next data transfer. The end address comparator compares the contents of the end address register with the contents of the M and N registers. When a match exists, an end of block condition is detected and the data transfer sequence is terminated.

#### 3.2.2 DISC DRIVE CONTROLLER

The disc drive controller is divided into six functional sections. Each of the functional sections is described in the following paragraphs and the signal flow illustrated by block diagrams. All of the four digit numbers are page references to LD 2002. In general, the data flow in the disc drive controller is from the DMA channel to CPU/DMA interface logic and the read/write control logic and then to the read, write, and address logic. Communication between the controller and the disc drive units is also through the read, write, and address logic sections. The data registers provide temporary storage for the disc drive controller.

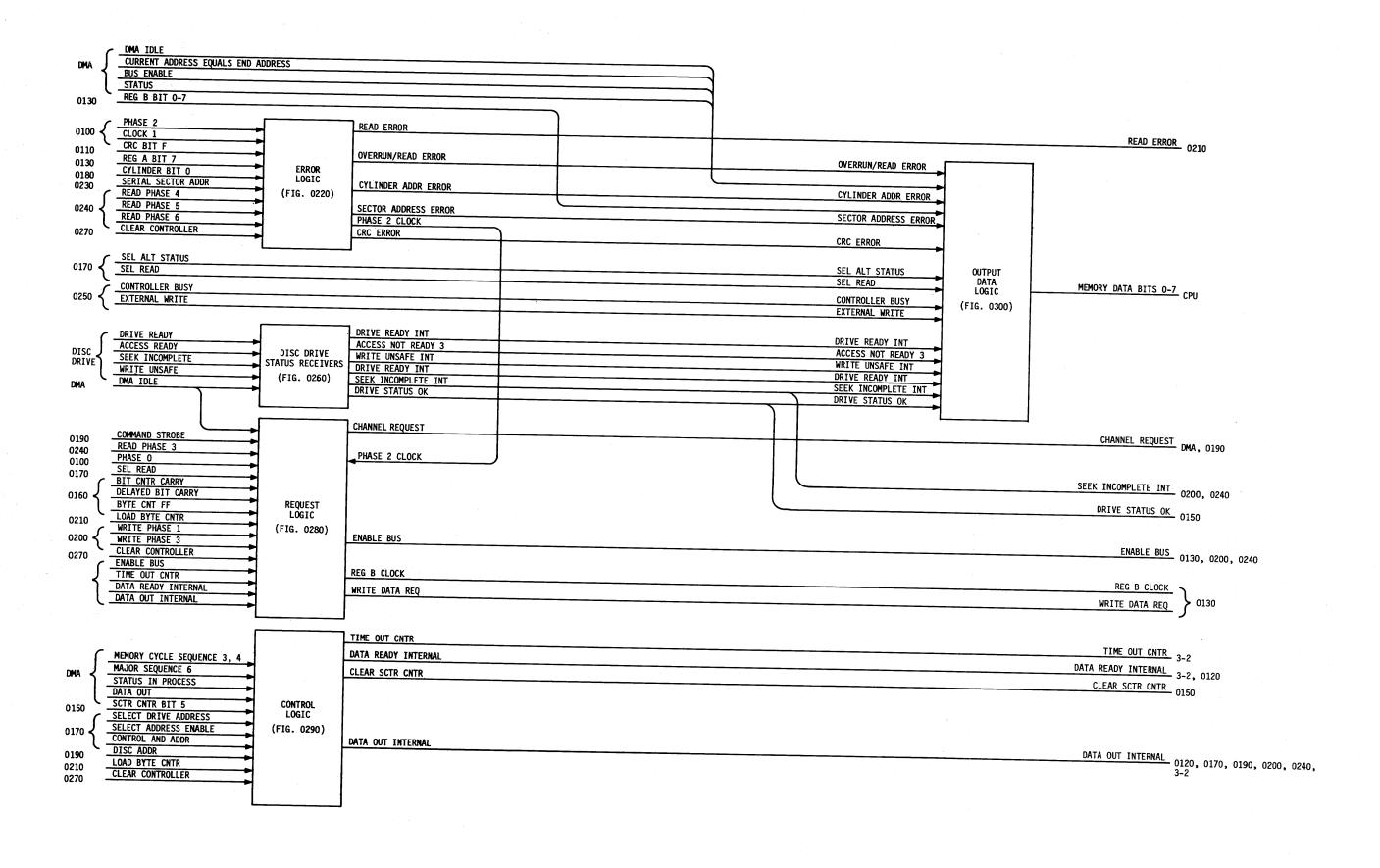

3.2.2.1 <u>CPU/DMA Interface Logic</u> (figure 3-2). This functional section includes the logic circuits that interface with the DMA channel logic and the CPU. Included is the status logic, the interface control logic, the error logic, the output data logic, the disc drive status receivers, and the request logic. The figure numbers referenced within each block and on all input and output signals refer to the appropriate logic diagrams.

The output data logic produces the read data byte output to the CPU (read operation), or the status byte that is supplied to the CPU in response to a status in device order. The output data logic formulates the appropriate eight-bit byte for transmittal to the CPU.

Figure 3-2. CPU/DMA Interface Logic, Block Diagram

The control and request logic processes control signals received from the DMA channel logic.

The error logic circuits develop the four error signals: read error, cylinder address error, sector address error, and CRC error.

The disc drive status receivers receive the status information from the disc drives.

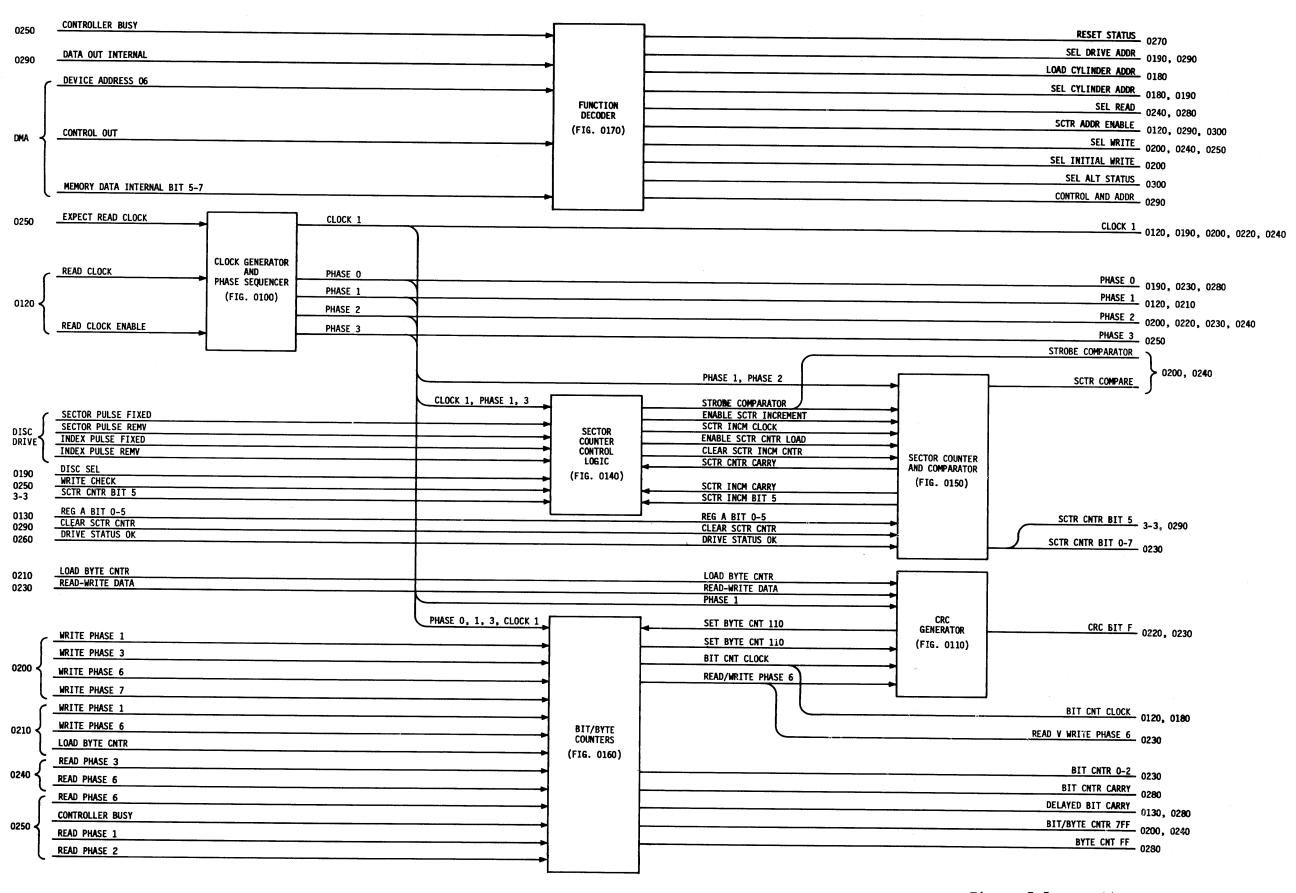

3.2.2.2 Read/Write Control Logic (figure 3-3). This functional section includes logic associated with both the read and write operations of the controller. Included are the function decoder, the clock generator and phase sequencer, the CRC generator, the sector logic, and the bit and byte counters. The figure numbers referenced within each block and on all input and output signals refer to the appropriate logic diagrams.

The function decoder processes device order bytes from the CPU (via the DMA channel logic) to produce function commands used throughout the controller.

The clock generator and phase sequencer generates the basic timing signals used to control the sequence of read/write operations.

The CRC generator is used during the write operation to generate the CRC character written at the end of each sector. During a read operation, the CRC generator reconstructs the CRC character that was previously written on the disc.

The sector logic processes the index and sector pulses received from the disc drive in order to produce a count identifying the disc sector being accessed. By comparing the sector count with the sector address received from the CPU (via the DMA channel logic), the sector logic determines when a read or write operation in a designated sector is ready to be commenced.

The bit and byte counters tally the bits and bytes respectively that have been read or written within a sector, thereby determining the positional location of the disc heads within the sector.

3.2.2.3 <u>Data Registers</u> (figure 0130). The data registers serve as the temporary storage location for all data and sector address bytes received from, or sent to, the CPU. During a write operation, each eight-bit data byte received from the CPU (via the DMA channel logic) is stored in the data registers and converted to serial

Figure 3-3. Read/Write Control Logic, Block Diagram

form for writing on the disc. During a read operation, the serial read data from the disc is shifted into the data registers, and a serial-to-parallel conversion produces the eight-bit data input bytes supplied to the CPU.

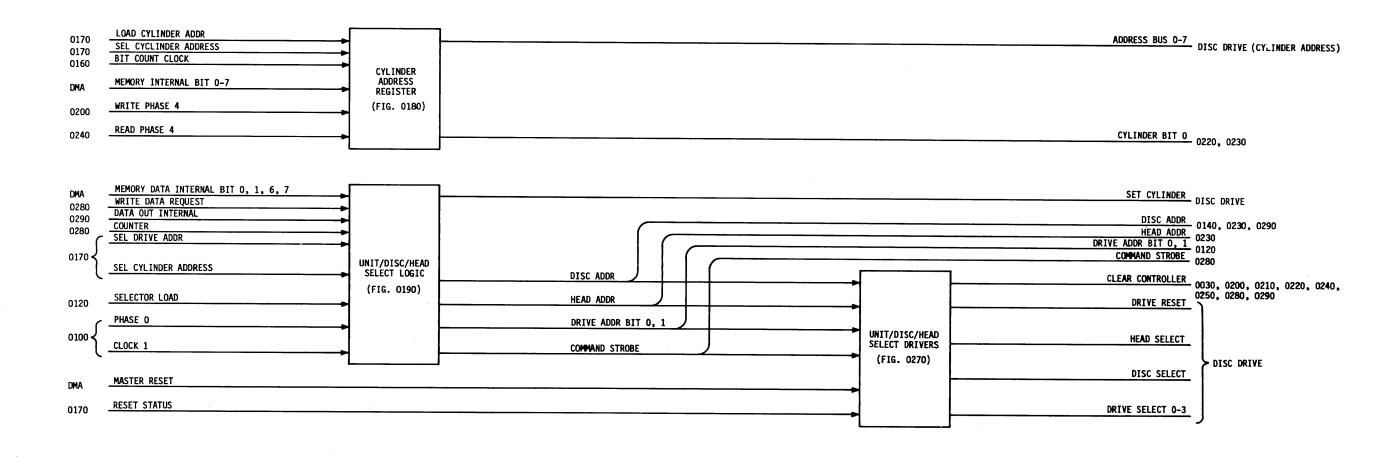

- 3.2.2.4 Address Logic (figure 3-4). The address logic receives and stores the cylinder address, drive select, disc select, and head select codes from the CPU (via the DMA channel logic). This data is used to form cylinder select, drive select, disc select, and head select commands for the disc drive.

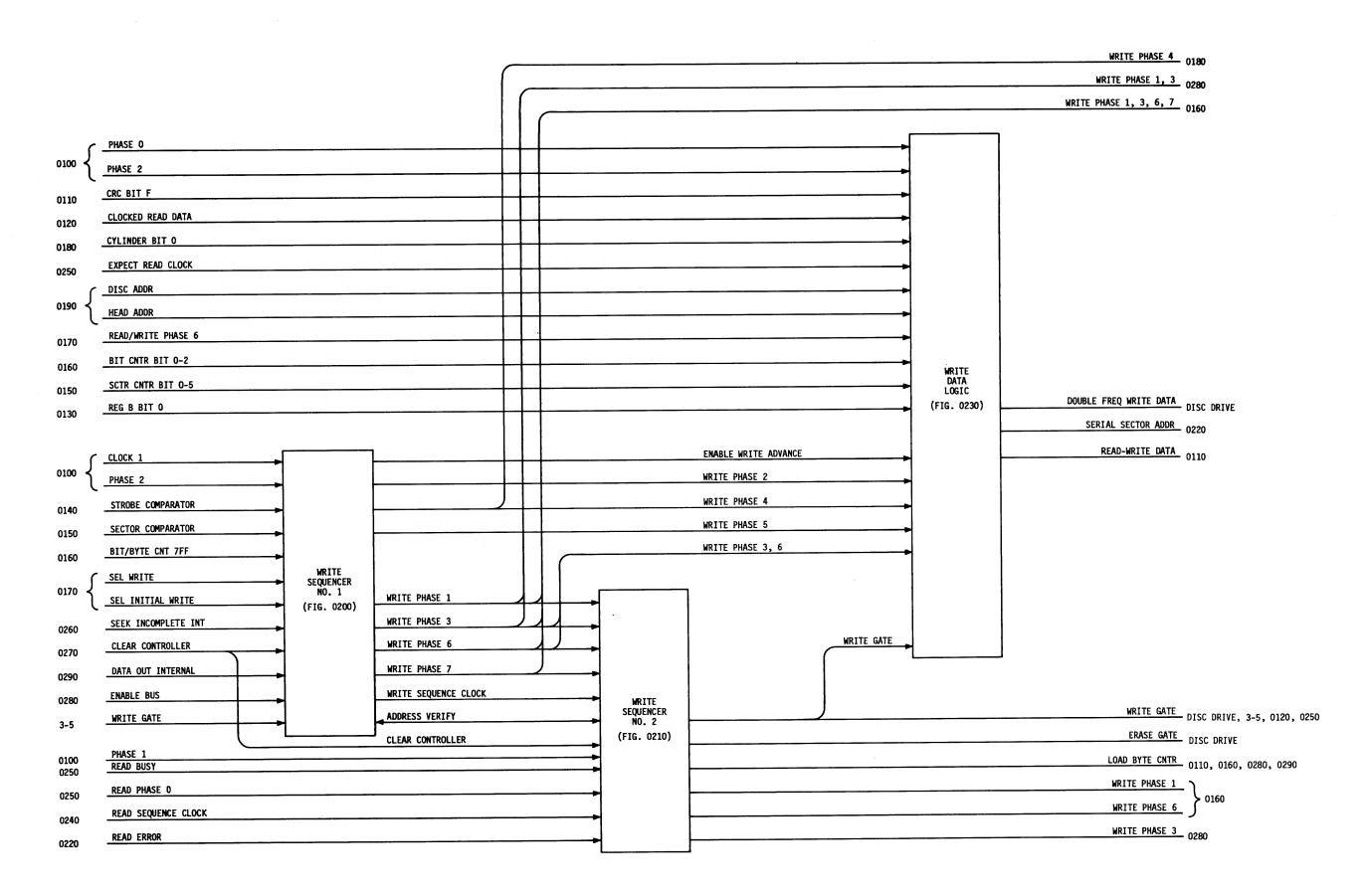

- 3.2.2.5 <u>Write Logic</u> (figure 3-5). The write logic includes the write sequencer and the write data logic. The write sequencer controls the sequence of actions during a write operation. The write data logic produces the serial write data stream supplied to the disc drive for writing on the disc.

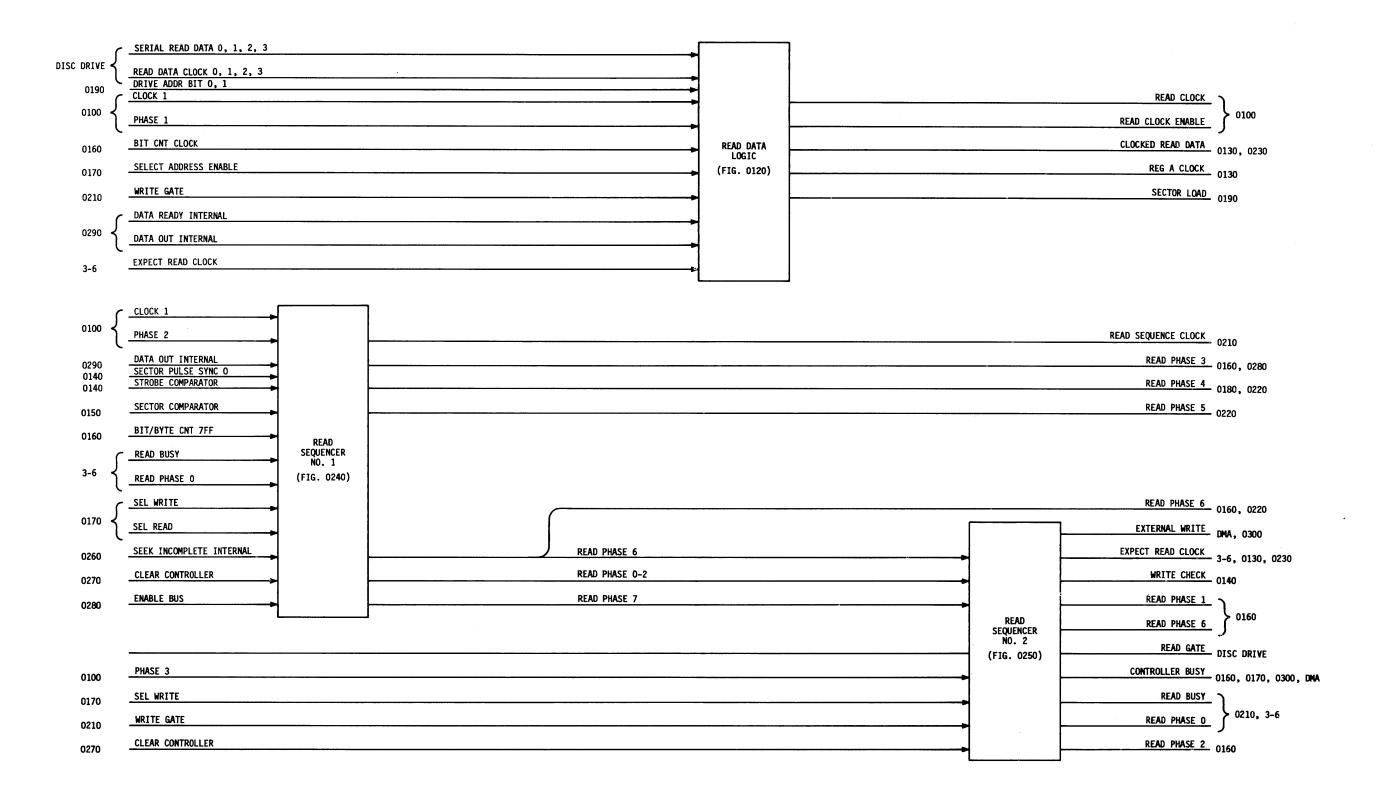

- 3.2.2.6 Read Logic (figure 3-6). The read logic includes the read sequencer and the read data logic. The read sequencer controls the sequence of actions during a read operation. The read data logic processes the serial read data and read clock received from the disc drive.

# 3.3 DATA FLOW DESCRIPTION

The following paragraphs describe the data flow for each of the controller functions. The functions are represented by four major data paths: the write data path, the function/address data path, the read data path, and the status data path. The supporting illustrations are block diagrams arranged in data flow sequence. The illustrations reference pages in LD 2002.

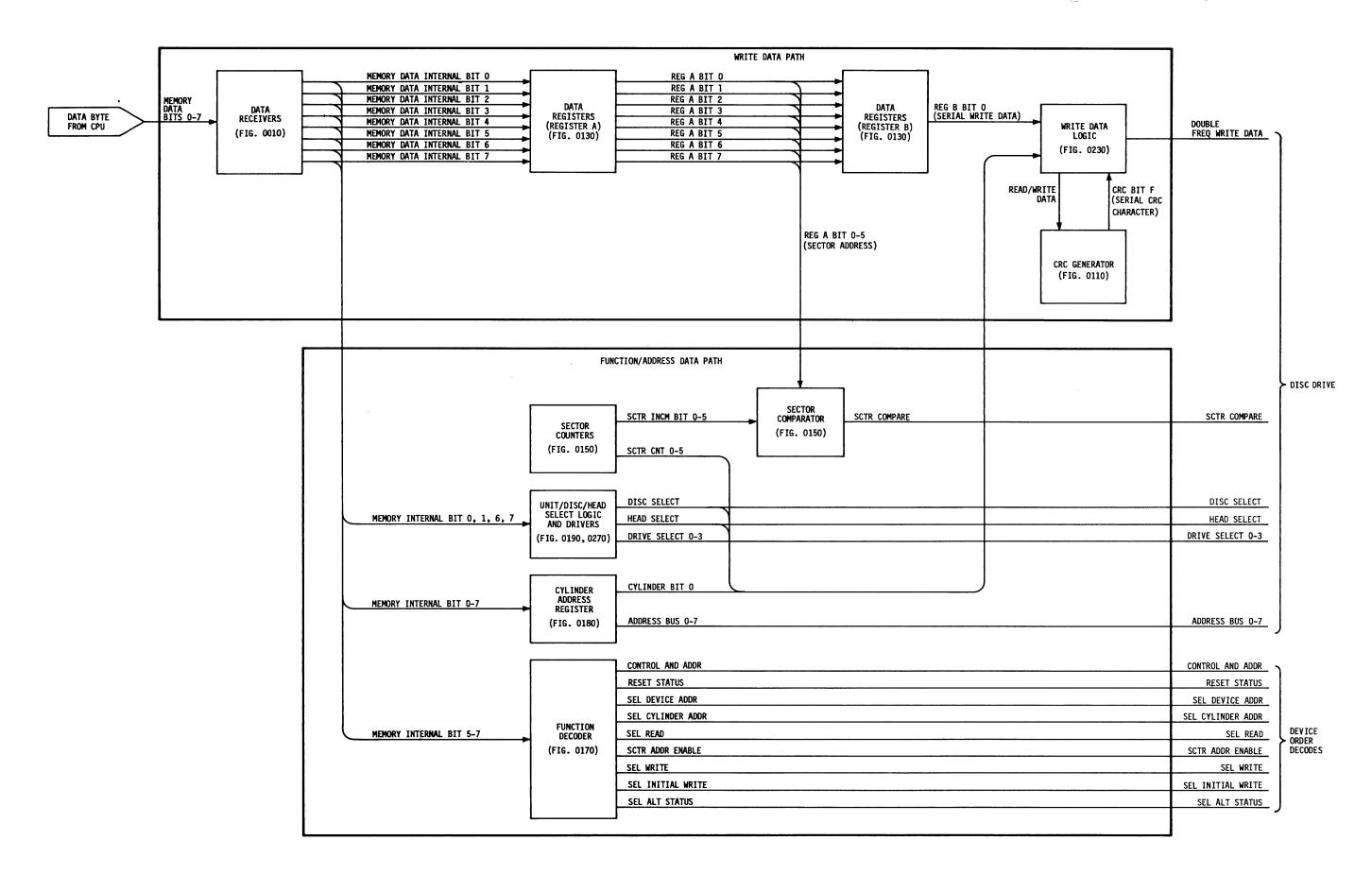

#### 3.3.1 WRITE DATA PATH (figure 3-7)

The serial DOUBLE FREQ WRITE DATA to the disc drive is produced by the write data logic. During the initial portion of a write operation, the write data logic produces the 28-byte zero gap field, followed by the preamble byte. Then the CPU transfers 110 consecutive data bytes to the DMA/disc drive controller. Each byte from the CPU is supplied (via the data receivers in the DMA channel logic) to register A, and is then parallel-loaded into register B. Register B operates in the serial shift mode to shift out the bits of each byte to the write data logic

Figure 3-4. Address Logic, Block Diagram

Figure 3-5. Write Logic, Block Diagram

Figure 3-6. Read Logic, Block Diagram

Figure 3-7. CPU-to-Disc Drive Data Flow

is also supplied as READ-WRITE DATA to the CRC generator. During each bit time, the state of the bit shifted into the CRC generator is determined by the state of the READ-WRITE DATA line, in conjunction with the CRC pattern already stored in the generator.

After the 110 data bytes have been transferred to the disc drive, the stored cylinder address (8 bits) is serially shifted (CYLINDER BIT 0) into the write data logic and out to the disc drive. Next, the sector count (SCTR CNT 0-5), head select code (HEAD ADDR), and disc select code (DISC ADDR) are supplied to the write data logic, where a multiplexer converts this data to serial form for output to the disc drive. Finally the contents (16 bits) of the CRC generator are shifted out serially (CRC BIT F) to the write data logic and supplied to the disc drive.

# 3.3.2 FUNCTION/ADDRESS DATA PATH (figure 3-7)

This path processes the following types of information bytes from the CPU:

- a. Device Order Byte. Device order bytes are supplied via the data receivers in the DMA channel logic to the function decoder. If the address section of the device order byte contains the address (06hex) of the disc drive controller, DEVICE ADDRESS 06 = 1 exists, and the function decoder decodes the device order section (bits 5 through 7) to produce a function command that sets up the controller for the specified response.

- b. Disc/Head/Sector Address Byte. This byte is supplied via the data receivers to register A, and to the unit/head/disc select logic. The stored sector address portion (REG A BIT 0-5) is supplied to the sector comparator, where it is compared with the sector count (SCTR INCM BIT 0-5) from the sector counters. When the code in REG A BIT 0-5 matches the code in SCTR INCM BIT 0-5, the SCTR COMPARE signal is made true, indicating that the disc heads are positioned at the beginning of the designated sector. The disc and head select data (bits 6 and 7) is supplied (via the data receivers) to the unit/disc/head select logic. Here, the select codes are decoded to produce the HEAD SELECT and DISC SELECT commands to the disc drive.

- c. Cylinder Address Byte. Cylinder address bytes are supplied via the data receivers to the cylinder address register. The stored cylinder address code is supplied to the disc drive as bits ADDRESS BUS 0-7.

- d. <u>Unit Select Byte</u>. This byte is supplied (via the data receivers) to the <u>unit/disc/head</u> select logic. Here, the code in bits 0 and 1 is decoded to produce the DRIVE SELECT 0-3 commands to the disc drives.

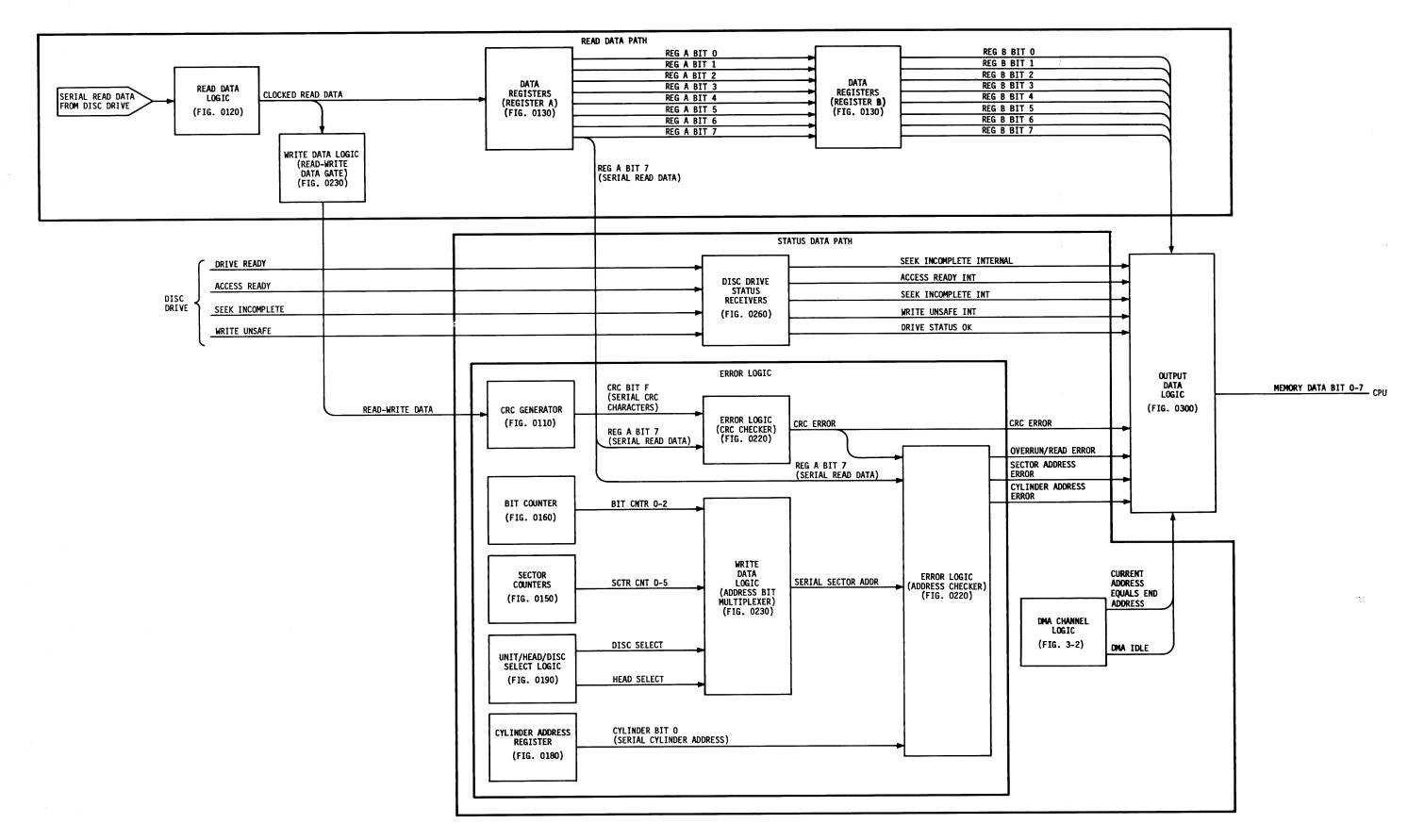

### 3.3.3 READ DATA PATH (figure 3-8)

Serial read data from the disc drive is supplied to the read data latch. The CLOCKED READ DATA output of the read data latch is supplied to register A, which operates in the shift mode. When eight bits have been shifted into register A, the contents of register A are parallel-loaded into register B, which supplies the recovered read byte to the CPU via the output data logic.

The CLOCKED READ DATA is also supplied via the read-write data gate to the CRC generator. During each bit time, the state of the bit shifted into the CRC generator is determined by the state of the READ-WRITE DATA line, in conjunction with the CRC pattern already stored in the generator.

# 3.3.4 STATUS DATA PATH (figure 3-8)

Status data supplied to the CPU is derived from the DMA channel logic, the error logic, and disc drive status signals received via disc drive status receivers. The format of the status byte is determined by whether or not an alternate status function command is decoded by the function decoder.

The error logic is used to check the end of block data in each sector to verify that no CRC error is present, and that the disc, head, cylinder, and sector information received from the CPU matches the disc, head, cylinder, and sector information read from the disc. During error checking, the serial read data shifted into register A of the read path is supplied as REG A BIT 7 to the CRC and address checkers. When the address portion of the end of block data is being read, the address checker compares the state of REG A BIT 7 in each bit time with the serial cylinder address (CYLINDER BIT 0) from the cylinder address register, or the SERIAL SECTOR ADDR bit from the address bit multiplexer. The address bit multiplexer, controlled by the bit count from the bit counter, selects one bit from the sector counter or the unit/head/disc select logic while this portion of the end of block data is being read from the disc. When the address checker detects a mismatch between the state of REG A BIT 7 and the selected address data bit, the appropriate error signal is made true.

When the CRC portion of the end of block data is being read, the CRC checker compares the state of REG A BIT 7 in each bit time with the serially shifted output (CRC BIT F) of the CRC generator. When the CRC checker detects a mismatch between the state of REG A BIT 7 and CRC BIT F, the CRC ERROR signal is made true.

Figure 3-8. Disc Drive-to-CPU Data Flow

The output data logic processes the error and disc drive status signals to formulate the appropriate status byte for the CPU. The status byte is made available to the CPU each time STATUS is true.

# 3.4 DMA SEQUENCES

Figures 3-9 and 3-10 depict the three sequences performed by the DMA channel logic. In a typical block operation, these three sequences are performed in the following order:

- a. Initialization Sequence

- b. Data Transfer Sequence

- c. Status Transfer Sequence.

These sequences are always performed to completion unless a DMA disconnect device order  $(96_{hex})$  is received from the CPU. When the DMA disconnect device order is received, all sequences are terminated, and the DMA channel logic is reset, as follows:

- a. The INHIBIT COUNT ENABLE flip-flop (figure 0020) is reset.

- b. The DMA SELECT flip-flop (figure 0030) is reset.

- c. The major activity sequencer (figure 0050) is reset.

- d. The REQUEST flip-flop (figure 0050) is reset.

- e. The DMA termination interrupt flip-flop (figure 0070) is reset.

- f. The STATUS IN flip-flop (figure 0070) is reset.

The succeeding paragraphs describe the three sequences shown in figures 3-9 and 3-10.

### 3.4.1 INITIALIZATION SEQUENCE (figure 3-9)

Upon receipt of an initialization device order (76<sub>hex</sub>) while the DMA is in major activity sequence state 0 (idle), the DMA advances to major activity sequence states 1, 2, 3, 4 and 6. Sequence states 1, 2, 3 and 4 each exist for 1.2 microseconds if the CPU memory is not otherwise busy. Memory read cycles are performed in sequence states 1, 2, 3 and 4 to fetch the start of block and end of block addresses from the CPU memory. The memory read cycles are initiated by the CPU in response to the issuance of DMA REQUEST = 1, DMA SELECT = 1, and DMA WRITE = 0 from the DMA channel logic. As soon as the memory read cycle commences, DMA REQUEST = 0 occurs. Signal DMA SELECT = 1 continues for an additional 0.8 microseconds, and returns to the 0 state during the final 0.2 microseconds of each memory read cycle.

Figure 3-9. DMA Initialization Sequence Diagram

The actions performed during each major activity sequence state are as follows:

- 3.4.1.1 Major Activity Sequence State 1. Memory address  $0060_{\rm hex}$  is placed on the address bus to the CPU. During the memory read cycle, the byte contained in this location (8 MSB of start of block address) is read from memory. At DMA clock time  $t_6$ , the following actions occur:

- a. The address byte read from memory is stored in the M register of the DMA channel logic.

- b. The address byte counter is advanced to count  $01_2$ , setting up memory address  $0061_{\rm hex}$  for major activity sequence state 2.

- c. The DMA channel logic advances to major activity sequence state 2.

- 3.4.1.2 Major Activity Sequence State 2. Memory address  $0061_{hex}$  is placed on the address bus to the CPU. During the memory read cycle, the byte contained in this location (8 LSB of start of block address) is read from memory. At DMA clock time  $t_{12}$ , the following actions occur:

- a. The address byte read from memory is stored in the N register of the DMA channel logic.

- b. The address byte counter is advanced to count  $10_2$ , setting up memory address  $0062_{\rm hex}$  for major activity sequence state 3.

- c. The DMA channel logic advances to major activity sequence state 3.

- 3.4.1.3 Major Activity Sequence State 3. Memory address  $0062_{hex}$  is placed on the address bus to the CPU. During the memory read cycle, the byte contained in this location (8 MSB of end of block address) is read from memory. At DMA clock time  $t_{18}$ , the following actions occur:

- a. The address byte read from memory is stored in the 8 MSB positions of the end address register of the DMA channel logic.

- b. The address byte counter is advanced to  $11_2$ , setting up memory address  $0063_{\rm hex}$  for major activity sequence state 4.

- c. The DMA channel logic advances to major activity sequence state 4.

- 3.4.1.4 Major Activity Sequence State 4. Memory address  $0063_{hex}$  is placed on the address bus to the CPU. During the memory read cycle, the byte contained in this location (8 LSB of end of block address) is read from memory. At DMA clock time  $t_{24}$ , the following actions occur:

- a. The address byte read from memory is stored in the 8 LSB positions of the end address register of the DMA channel logic.

- b. The address byte counter is advanced to  $00_2$ .

- c. The DMA channel logic advances to major activity sequence state 6, enabling the data transfer sequence.

## 3.4.2 DATA TRANSFER SEQUENCE (figure 3-10)

At the completion of the initialization sequence, the DMA channel logic is in major activity sequence state 6, and remains in this state until either a DMA disconnect device order is received, or until an end of block condition is detected. If the memory is not busy, the DMA channel logic initiates a memory read or write cycle each time CHANNEL REQUEST = 1 is received from the disc drive controller. When CHANNEL REQUEST = 1 occurs, either a memory read cycle or a memory write cycle is initiated by the occurrence of DMA SELECT = 1, DMA REQUEST = 1, and either DMA WRITE = 1 (memory write cycle) or DMA WRITE = 0 (memory read cycle). As soon as the memory cycle sequence commences, DMA REQUEST = 0 occurs. Signal DMA SELECT = 1 continues for an additional 0.8 microsecond, and returns to the 0 state during the final 0.2 microsecond of the memory cycle sequence. The memory location accessed during the memory read or write cycle is determined by the contents (current address) of the M and N registers in the DMA channel logic. If a memory write cycle is being performed, an 8-bit data byte is read from the disc drive and supplied from the disc drive controller to the CPU for entry into the addressed memory If a memory read operation is being performed, the 8-bit data or block control byte read from the addressed memory location is supplied (via the data receivers in the DMA channel logic) to the disc drive controller.

The actions occurring at clock time  $t_6$  of the data transfer sequence depend upon whether an end of block condition exists. If the current address in the M and N registers matches the end address in the end address register, an end of block condition exists, and the following actions occur at clock time  $t_6$ :

- a. The end of block interrupt is set. If the disc drive controller is not busy, a DMA termination interrupt is sent to the CPU.

- b. The DMA channel logic returns to major activity sequence state 0 to await another initialization device order from the CPU.

If an end of block condition is not present at clock time  $t_6$ , the current address (in the M and N registers) is incremented one count, and the DMA channel logic

remains in major activity sequence state 6 to await the next occurrent of CHANNEL REQUEST = 1 from the disc drive controller. When CHANNEL REQUEST = 1 occurs, the data transfer sequence is repeated.

# 3.4.3 STATUS TRANSFER SEQUENCE (figure 3-10)

The CPU may initiate a status transfer sequence at any time, but the sequence is also normally performed immediately following the receipt of a DMA termination interrupt. The sequence is initiated upon receipt of a status in device order  $(16_{\rm hex})$  from the CPU. Upon receipt of this command (accompanied by CONTROL OUT), STATUS IN = 1 occurs, and, at clock time  $t_1$ , the following actions are produced:

- a. The STATUS IN PROCESS flip-flop is set.

- b. Code  $0058_{\mbox{hex}}$  is placed on the memory address bus to the CPU.

- c. The end of block interrupt is reset.

- d. The status byte from the disc drive controller is placed on the MEMORY DATA lines to the CPU.

- e. DMA SELECT = 1, DMA REQUEST = 1, and DMA WRITE = 1 all occur, initiating a memory write cycle during which the status byte on the MEMORY DATA lines is written into CPU memory location 0058 hex.