# ATL-008 MAINTENANCE MANUAL

### © 1984 by Beehive

This equipment complies with the requirements in Part 15 of FCC Rules for a Class A computing device. Operation of this equipment in a residential area may cause unacceptable interference to radio and TV reception requiring the operator to take whatever steps are necessary to correct the interference.

Notice: This document has been prepared by Beehive International and is furnished on the condition that it will be used by the customer solely for the purpose of supporting operation, service, and maintenance of Beehive products. Beehive believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this manual or this material. Revisions may be issued to advise of such changes and/or additions. This document shall not be duplicated by the customer nor released, disclosed or used, in full or in part, for any purpose other than as stated herein, without the express written permission of Beehive International.

All specifications contained in this manual are subject to change at any time without notice.

DOCUMENT TM0283-T1-2

REV. 7/84

**VERSION 1.0**

HARDWARE OVERVIEW

ON-SITE MAINTENANCE AND REPAIR

ATL POWER SUPPLY FUNCTIONAL DESCRIPTION

ATL-008 MONITOR FUNCTIONAL DESCRIPTION

**S**KEYBOARD

FUNCTIONAL

DESCRIPTION

6 LOGIC BOARD FUNCTIONAL DESCRIPTION

APPENDICES

ASCII CODE CHART

MEMORY MAP

PAL EQUATIONS & STATE TABLES

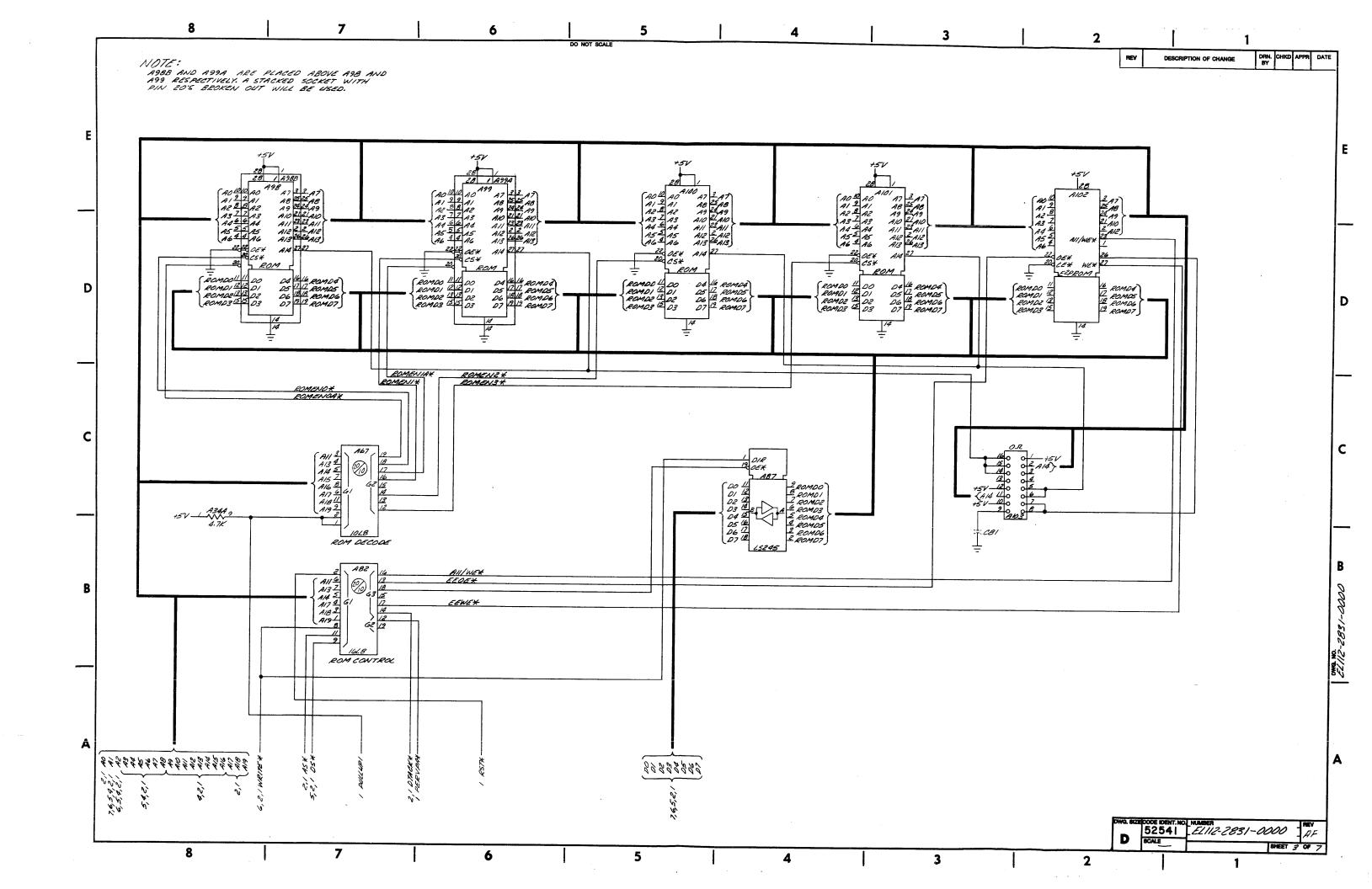

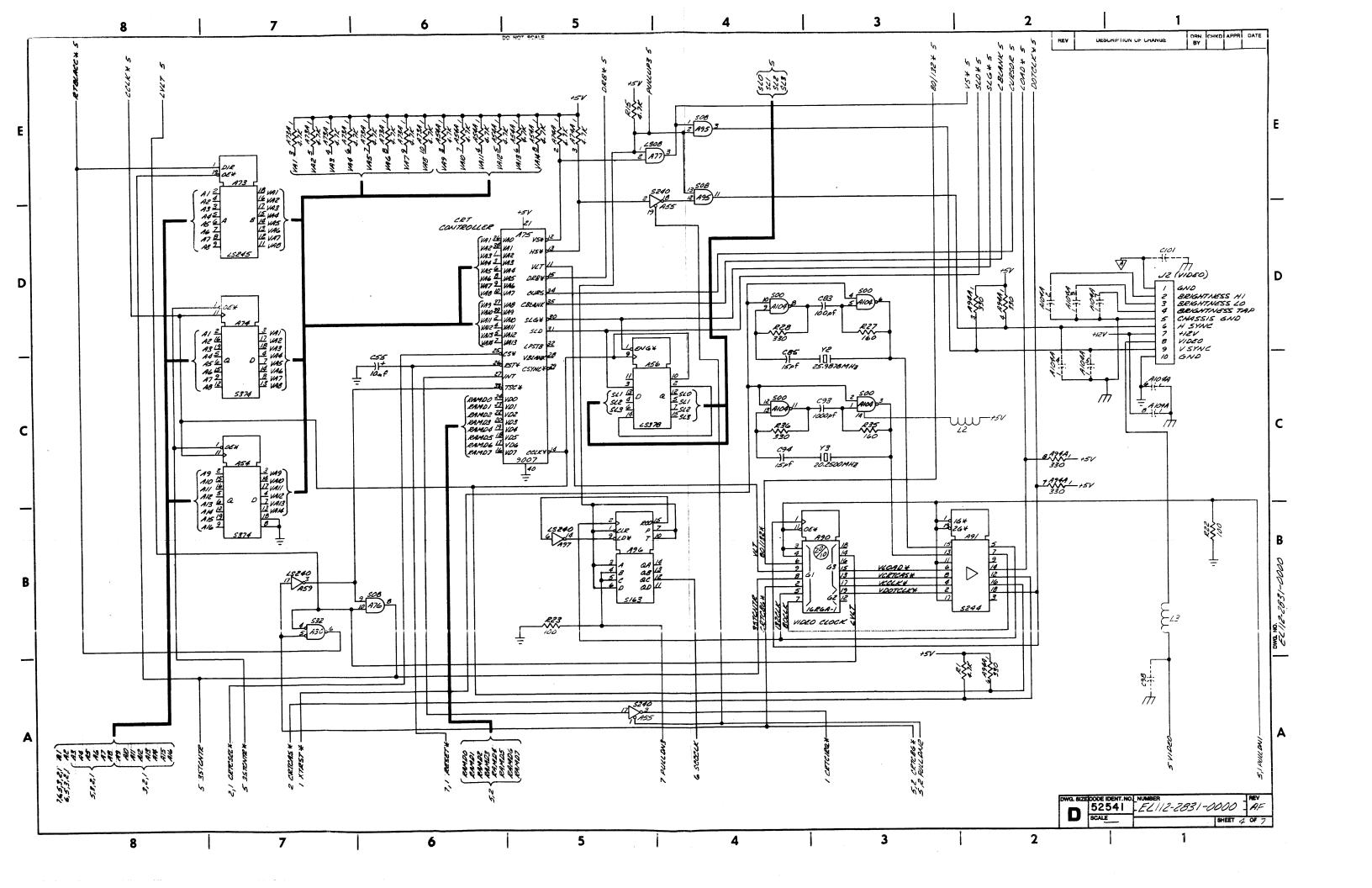

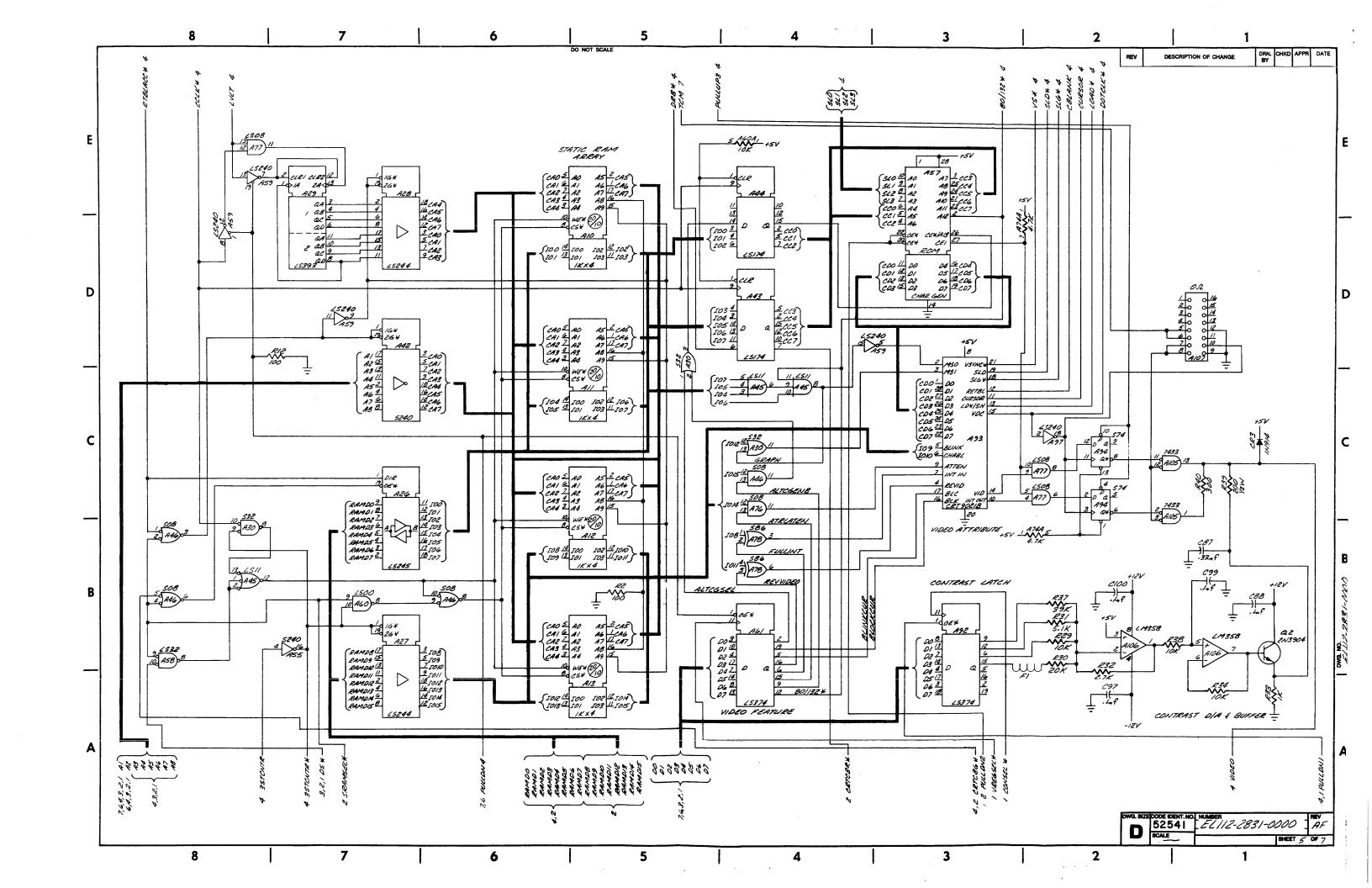

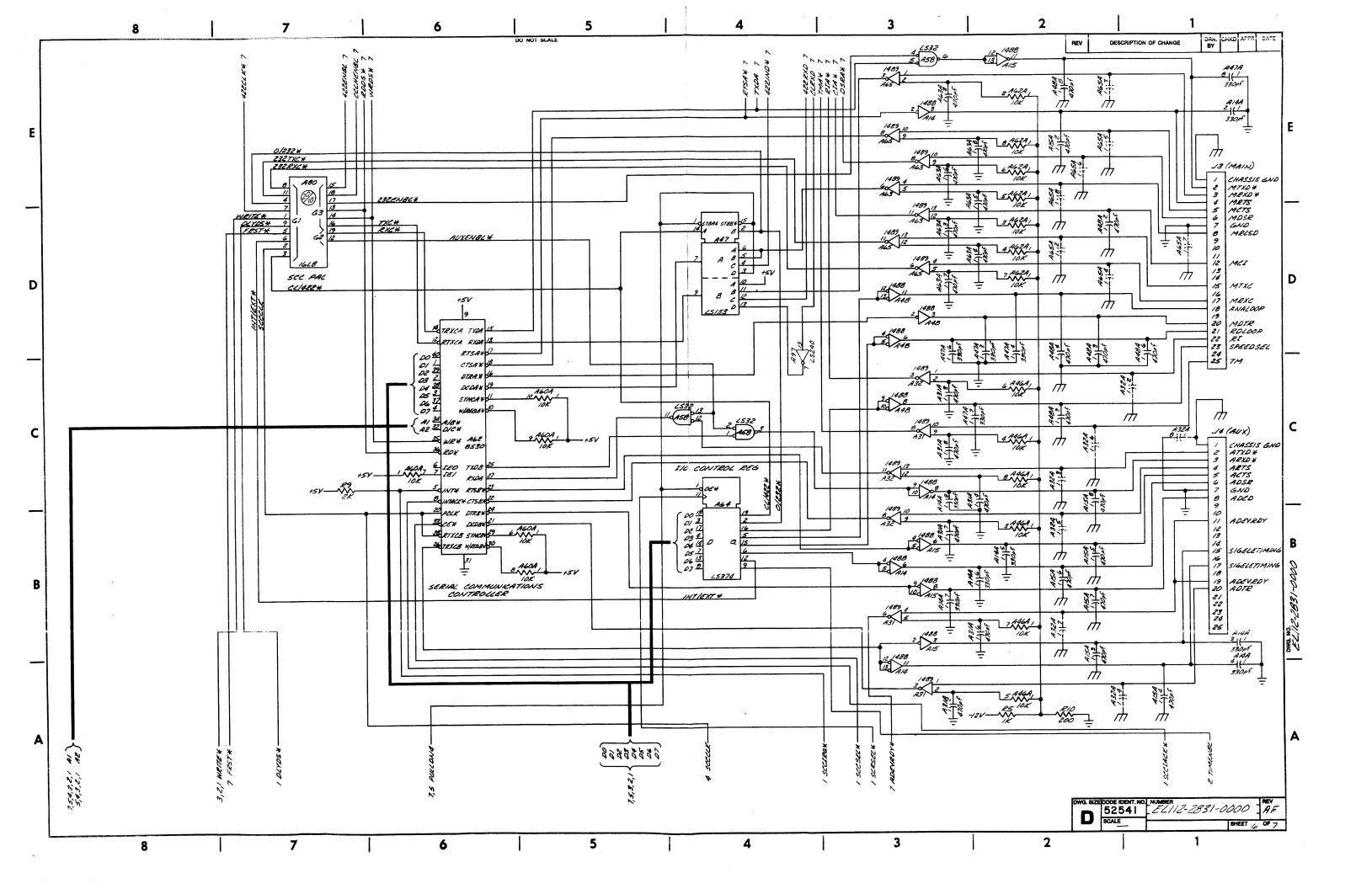

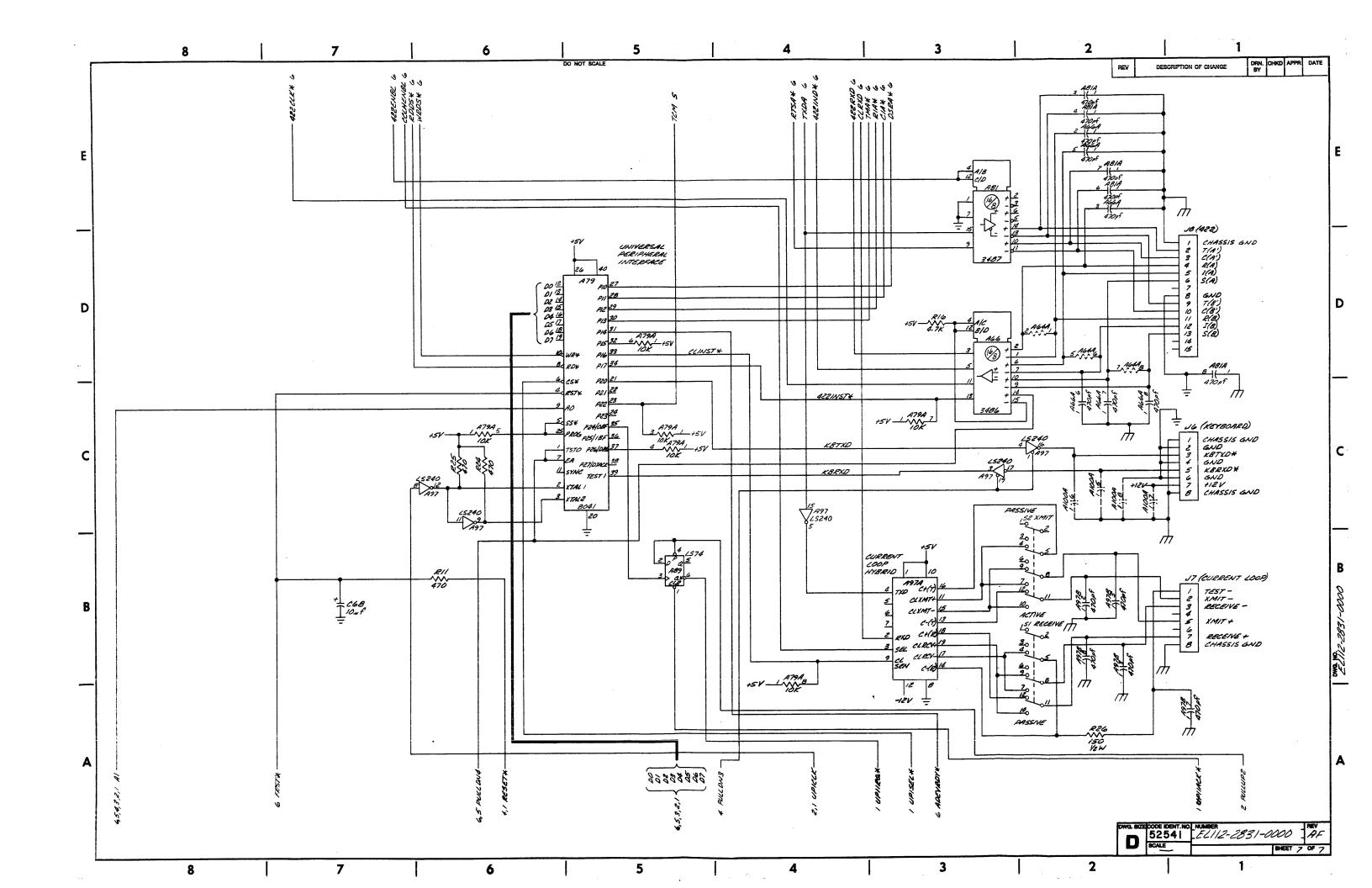

SCHEMATIC DRAWINGS

# TABLE OF CONTENTS

**HARDWARE OVERVIEW**

| INTRODUCTION                                             |                  |        |           |

|----------------------------------------------------------|------------------|--------|-----------|

| CONTROLS AND INDICATORS                                  |                  |        | <b>1-</b> |

| Power Switch                                             |                  |        |           |

| Status Lines                                             |                  |        | 1-:       |

| Audio Alarms                                             |                  |        |           |

| FUSE                                                     |                  |        |           |

| CONNECTORS                                               |                  |        | 1-:       |

| VENTILATION                                              |                  |        | 1-4       |

| HARDWARE DESCRIPTION .                                   |                  |        | 1-:       |

| Identification of Optional Co                            |                  |        |           |

| Internal Cabling                                         |                  |        |           |

| Power Supply                                             |                  |        |           |

| Monitor                                                  |                  |        |           |

| Keyboard                                                 |                  |        | 1-4       |

| Logic Board                                              |                  |        | 1-4       |

|                                                          |                  |        |           |

| ON-SITE MAINTENA                                         |                  |        |           |

| GENERAL INFORMATION                                      |                  |        | 2-        |

| Warranty Provisions                                      |                  |        |           |

| Operating Environment                                    |                  |        | 2-        |

| Ventilation and Contaminan                               | s                |        | 2-        |

| AC Power                                                 |                  |        |           |

| Potential Hazards                                        |                  |        |           |

| Tools and Test Equipment                                 |                  |        |           |

| PROBLEM DIAGANOSIS                                       |                  |        | 2-3       |

| General                                                  |                  |        |           |

| Functional Failures                                      |                  |        | 2-4       |

| Video Failures                                           |                  |        |           |

| Communications Failures                                  |                  |        |           |

| KEYBOARD FAILURES                                        |                  |        |           |

| SUBASSEMBLY REPLACEMENT                                  | Γ                |        | 2-9       |

| Tools and Tips                                           |                  |        | 2-9       |

| Removing and Replacing the                               | Cover            |        | 2-10      |

|                                                          | Logic Board      |        |           |

| Removing and Replacing the                               |                  |        | 2-15      |

|                                                          | rower ouppry     |        |           |

| Removing and Replacing the                               |                  |        |           |

| Removing and Replacing the<br>Removing and Replacing the | Monitor Board an | d Yoke |           |

### TABLE OF CONTENTS (cont.)

| 3          | ATL POWER SUPPLY FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | GENERAL       3-1         FUNCTION       3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4          | ATL-008 MONITOR FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            | GENERAL       4-1         PRINTED CIRCUIT BOARD ASSEMBLY       4-1         Video Amplifier       4-2         Horizontal Deflection       4-2         Vertical Deflection Processor       4-3         Dynamic Focus       4-4                                                                                                                                                                                                                                                                                        |

|            | CATHODE RAY TUBE ASSEMBLY 4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5          | KEYBOARD FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | GENERAL       5-1         8039 MICROCOMPUTER       5-1         CRYSTAL FREQUENCY       5-1         INTERFACE TO TERMINAL       5-1         Keyboard Receive Data       5-2         Keyboard Transmit Data       5-2         POWER SUPPLY       5-2         GROUNDING       5-2         MATRIX SCANNING       5-2         Byte-Wide Interface       5-2         Scanning Levels       5-5         Keyboard Encoding       5-5         MEMORY       5-5         AUDIO ALARM       5-5         RESET CIRCUIT       5-6 |

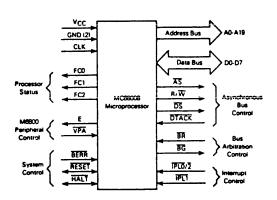

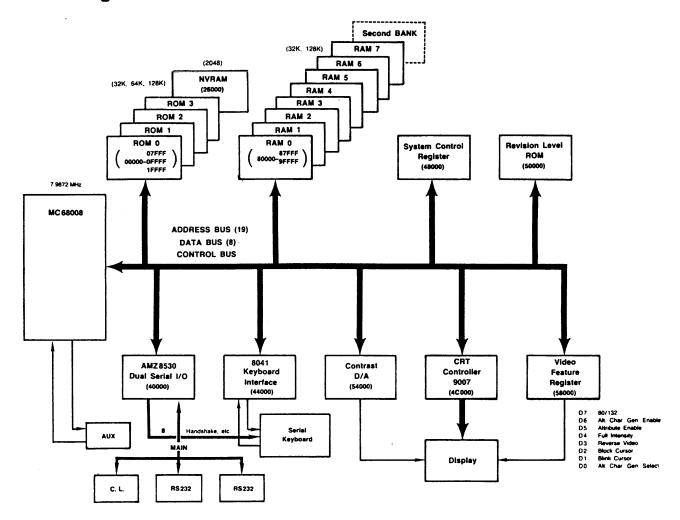

| <b>6</b> . | ATL-OOS LOGIC BOARD FUNCTIONAL DESCRIPTION         GENERAL       6-1         68008 MICROPROCESSOR       6-1         Address Bus (A0 – A19)       6-2         Data Bus (D0 – D7)       6-2         Clock Generator       6-3         Reset       6-3         Halt       6-3         Bus Error       6-3         Control Pure       6-3                                                                                                                                                                               |

|            | Control Bus         6-4           PERIPHERALS         6-6           Serial Communications Controller         6-6           Universal Peripheral Interface         6-7           CRT Controller         6-9           Board Revision Level         6-9           Contrast Control         6-9                                                                                                                                                                                                                        |

|            | Video Features Register 6-9 System Control Register 6-10                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### TABLE OF CONTENTS (cont.)

**APPENDIX**

**APPENDIX**

**APPENDIX**

FIGURES

Figure 1-1

Figure 2-1

Figure 2-2

Figure 2-3

Figure 2-4 Figure 2-5

Figure 2-6

Figure 2-7

Figure 2-8

Figure 2-9

Figure 2-10 Figure 2-11

Figure 4-1

Figure 5-1

Figure 5-2

Figure 6-1

Figure 6-2

Figure 6-3

Figure 6-4

Figure 6-5

Figure 6-6

Figure 6-7

Figure 6-8

Figure 6-9

TABLES

Table 1-1

Table 2-1

Table 2-2

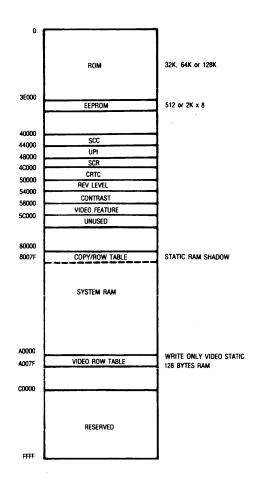

| MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

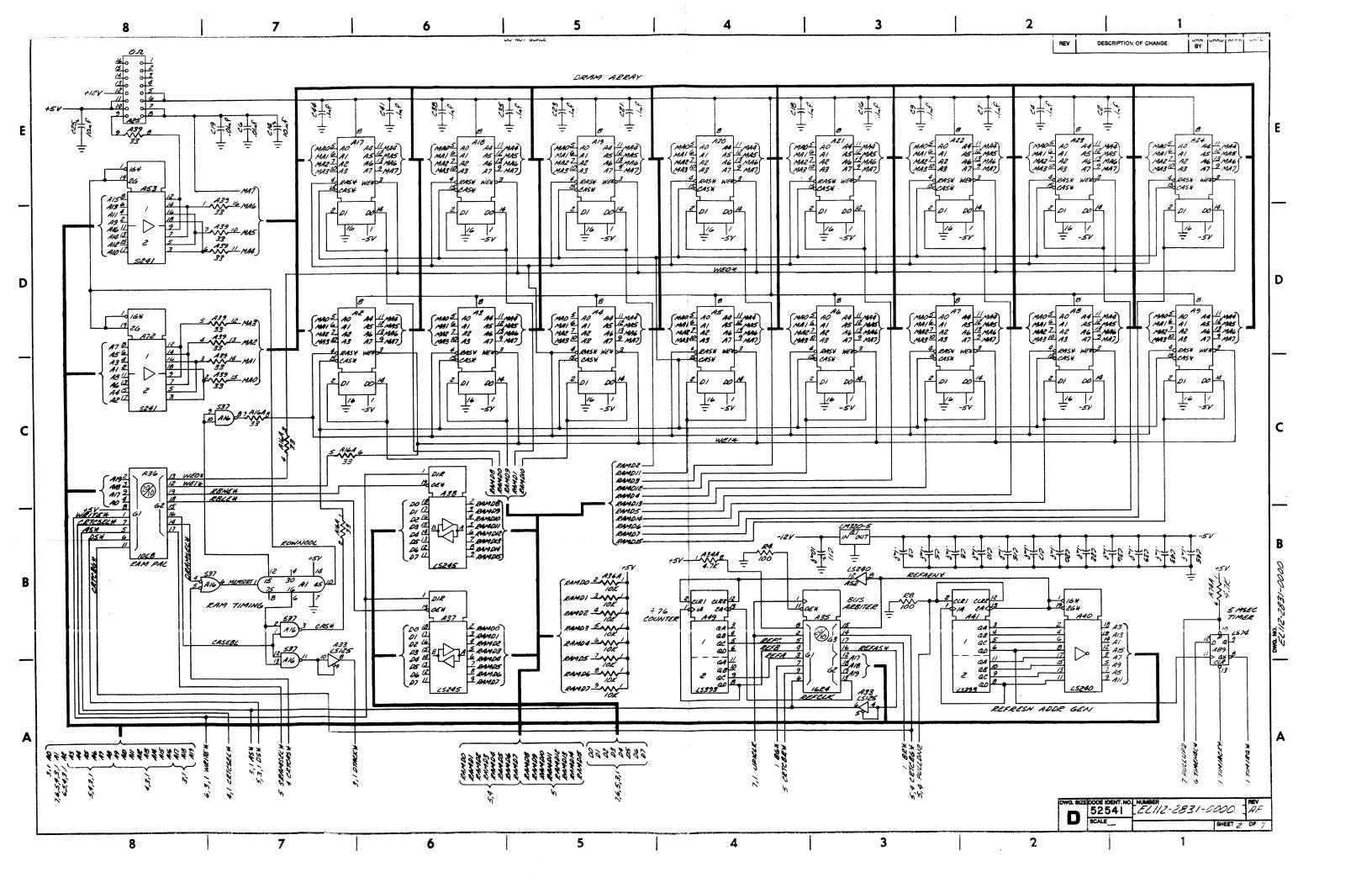

| Dynamic RAM Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-10                                                                                                       |

| Static RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-14                                                                                                       |

| Read Only Memory Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-14                                                                                                       |

| VIDEO SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-16                                                                                                       |

| 9007 CRT Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

| 9021 Video Attributes Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-18                                                                                                       |

| 1K × 4 Static RAMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-20                                                                                                       |

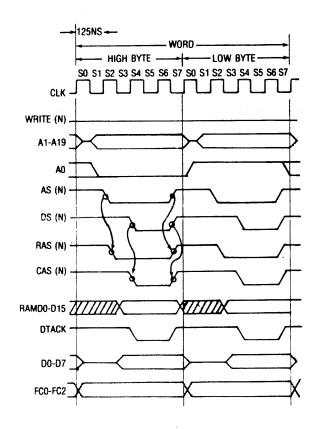

| BUS ARBITER/REFRESH CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-21                                                                                                       |

| Bus Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |

| Dynamic RAM Refresher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0-22                                                                                                       |

| ASCII CODE CHART ATL-008 MEMORY MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

| ATL-008 PAL EQUATIONS & STATE TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                            |

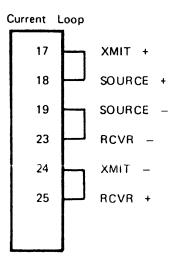

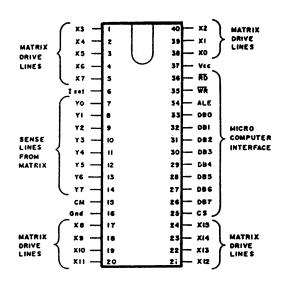

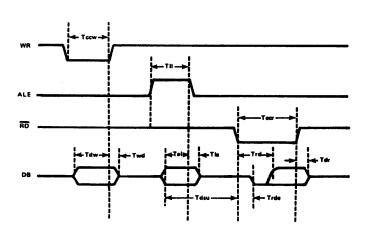

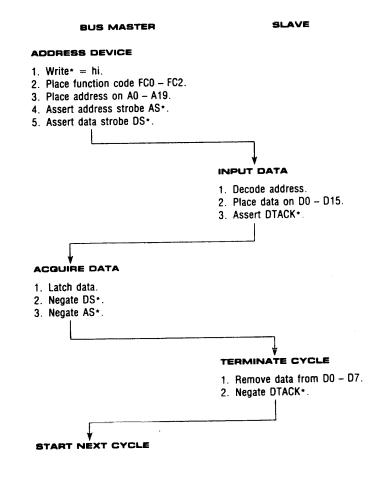

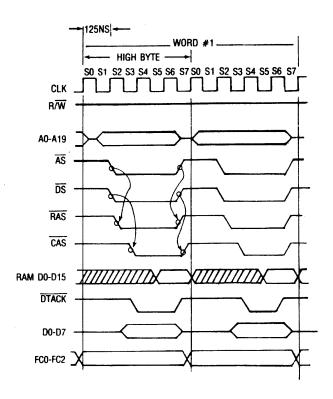

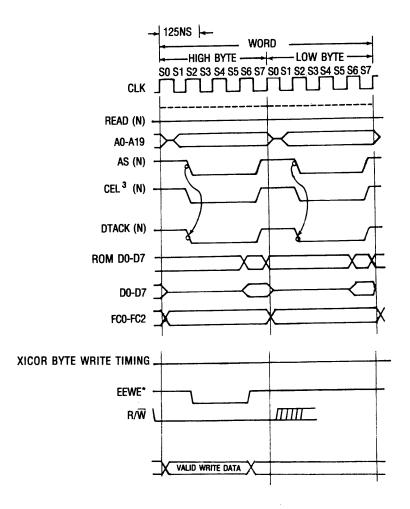

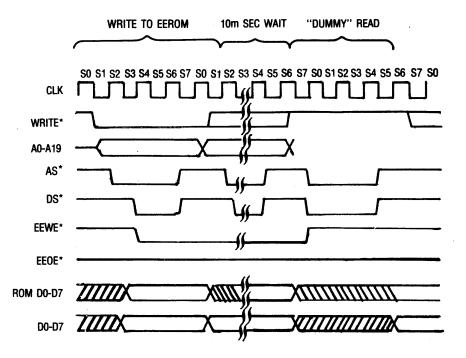

| ATL Terminal  Electrified Electronic Technician  Voltage Hazards  Power Supply Output Voltage Locations  +5 VDC Adjustment Pot  Logic Card Ribbon Cable Connector to Monitor Card  Video Output from Logic Card (Pin 1)  Horizontal Sync Output from Logic Card (Pin 6)  Vertical Sync Output from Logic Card (Pin 9)  RS232 Loopback Test Connector  Main Port RS422 Loopback Test Connector  20 mA Current Loop Loopback Test Connector  Monitor Board Block Diagram  Byte-Wide Pinouts  Byte-Wide Pinouts  Byte-Wide Timing Diagram  68008 Input/Output Signal Configuration 68008 System Block Diagram  ATL-008 Memory Map  DRAM Byte Write Cycle Flow Chart  DRAM Write Word Timing Diagram  DRAM Byte Read Cycle Flow Chart  DRAM Read Word Timing Diagram  ROM/EEPROM Read Word Timing Diagram  EEPROM Write Word Timing Diagram | 2-2<br>2-4<br>2-5<br>2-6<br>2-6<br>2-7<br>2-8<br>2-8<br>4-1<br>5-4<br>6-12<br>6-12<br>6-13<br>6-14<br>6-15 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                            |

| ATL-008 Optional Component Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-3                                                                                                        |

| Power Supply Output Voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-4                                                                                                        |

| Logic Board Video Output Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-5                                                                                                        |

### TABLE OF CONTENTS (cont.)

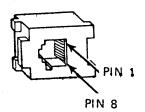

| Table 5-1 | J1 Data Jack Pin Assignments                | 5-2 |

|-----------|---------------------------------------------|-----|

| Table 5-2 | Byte-Wide AC Characteristics                | 5-4 |

| Table 5-3 | Keyboard Internal/External Memory Strapping | 5-5 |

| Table 6-1 | Data Strobe Control of Data Bus             | 6-4 |

| Table 6-2 | Function Code Outputs                       | 6-5 |

| Table 6-3 | Main/Auxiliary Port Selection               | 6-7 |

## HARDWARE OVERVIEW

### INTRODUCTION

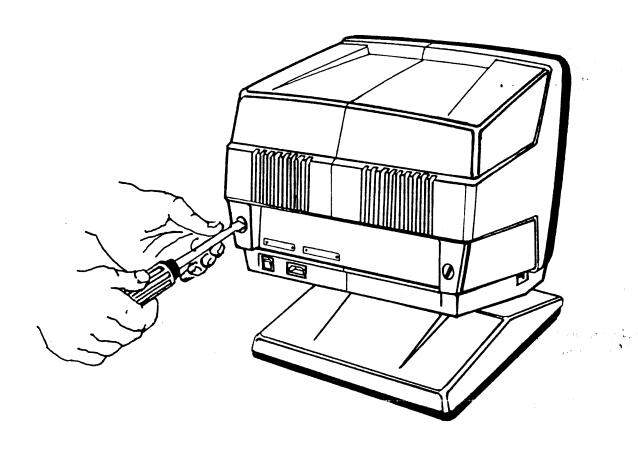

embers of the Beehive ATL family of terminals consist of a display screen with integral logic, video control, and communications circuitry and a detachable keyboard. The screen housing may be rotated and tilted. See Figure 1-1.

Figure 1-1

ATL Terminal

### CONTROLS AND INDICATORS

Power Switch

rocker switch on the rear panel controls power to the terminal. It is located so it may be easily reached with the right hand while using the terminal. Pressing the lower half of the switch turns the terminal on; pressing the top half turns the terminal off. Aside from the keys on the keyboard, this is the only external control on ATL terminals.

#### Status Lines

Line 25 divides the ATL screen into two areas: lines 1 to 24 are the data display area, lines 26 and 27 are the status lines. Line 26 indicates terminal status. Line 27 displays the status of the softkeys. These status lines are the only external indicators for ATL terminals.

Other terminal functions (contrast, intensity, error reporting, etc.) are handled by the Terminal Configuration Manager (TCM). See the appropriate Technical User's Manual for a description of TCM controls and indicators.

### **Audio Alarms**

The keyboard is capable of generating two beeps, a ring, warble and a click. The beeps produce a 600 Hz tone or a 1200 Hz tone. A ring is a signal alternating between 600 Hz and 1200 Hz. A warble is the same as a ring but with a different rate of alternation. A keyswitch click is a DC pulse with a duration of 5 msec. A two-level volume control is also provided by the microprocessor. All of these audio sounds and the volume control are under program control.

### **FUSE**

here is no external fuse on ATL terminals. In the event of an overload, a crowbar circuit in the power supply interrupts the AC current. If this happens, it is essential that the power switch be turned off as soon as possible to prevent burning out the crowbar circuit. Remedy the cause of the overload and turn the terminal on again.

There is an internal fuse in the power supply. This fuse is used to protect the unit in the event that the crowbar circuit has engaged and the terminal has not been powered off at the switch for some time. If this fuse blows, the entire power supply must be replaced. See the power supply functional description for more details.

### CONNECTORS

TL terminals have two types of connectors on the rear panel: the power cord connector and the communications cable connectors. The number, type and purpose of the communications cable connectors depend on the type of terminal and the communications options selected. See the corresponding logic board communications section for more information.

### **VENTILATION**

TL terminals are cooled by convection. This means that air enters through the bottom, side and rear vents to cool the circuitry, and leaves through the top vents. There is no fan. Care must be taken not to cover the vents in the top, back, sides and bottom of the terminal. Even a sheet of paper inadvertently placed on top of the terminal will impede air flow and result in overheating and failure.

### HARDWARE DESCRIPTION

TL terminals consist of a display screen and a detachable keyboard. The screen housing may be rotated and tilted. The screen enclosure contains the power supply, monitor circuitry, and logic board. The logic board contains the CPU, memory, communications controller, and video controller. The keyboard is connected to the screen enclosure by a coiled cable. The keyboard enclosure contains a printed circuit card with the keyboard CPU, clock, ROM, and keyswitches.

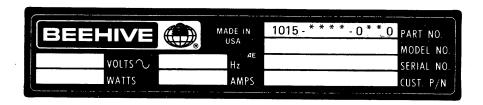

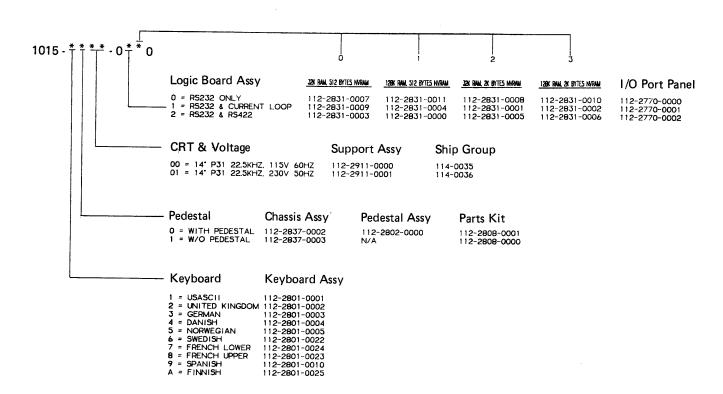

# Identification of Optional Components

There are several options available for ATL-008 terminals. The logic board offers three communications options and four memory options. The monitor offers a choice of voltage and display phosphor (B/W or green). The screen

enclosure may be ordered with or without the pedestal. The keyboard may be ordered for eleven different national character sets. The part number on the rear panel is the key to determining which of these options were chosen when a terminal was delivered.

The part number consists of three groups of four digits each. The digits of the last two groups are significant for identifying optional components. See Table 1-1.

Table 1-1

ATL-008 Optional

Component

Identification

### Internal Cabling

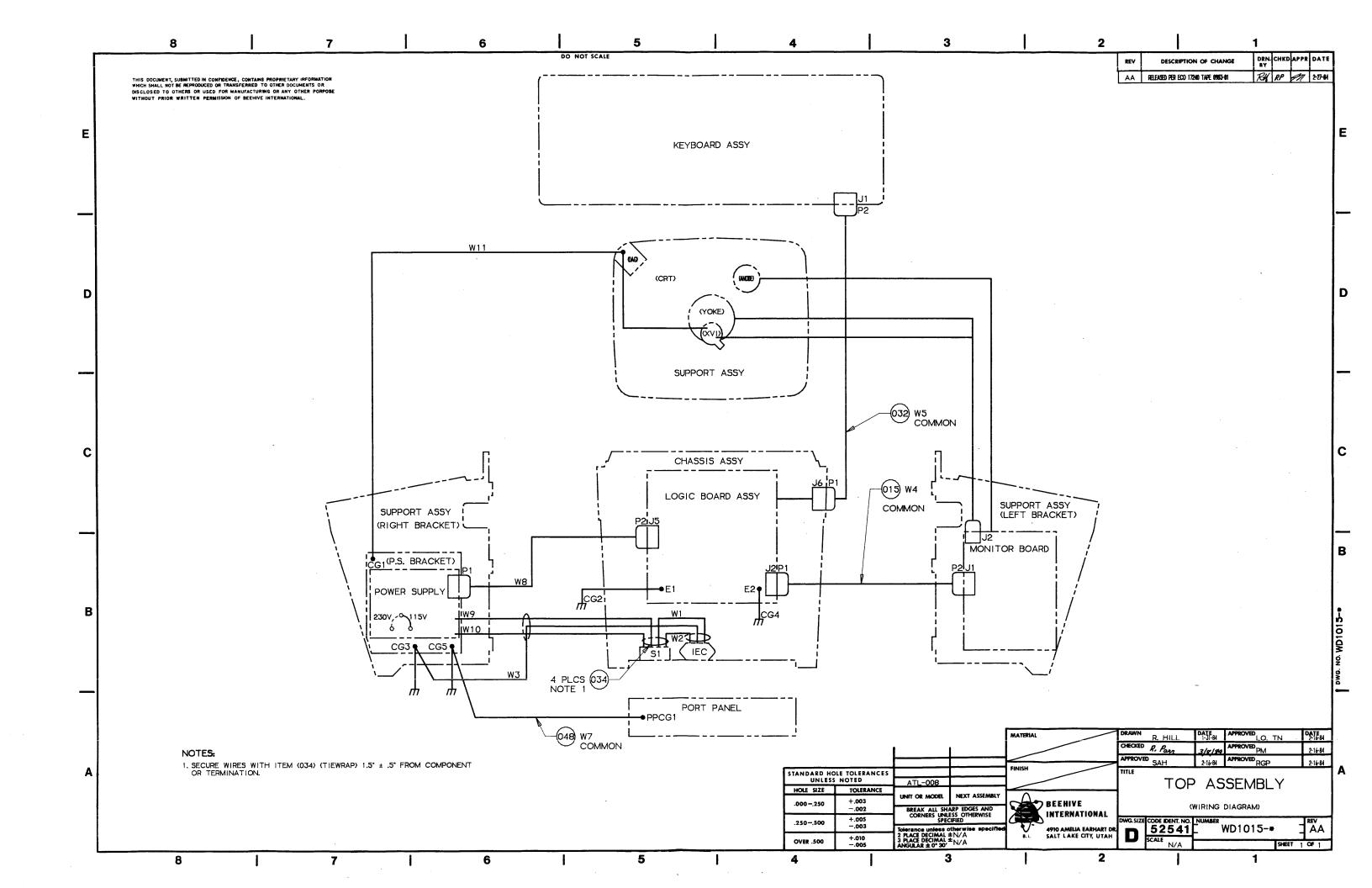

ATL terminals use three types of internal cables. Ribbon cables connect the logic board to the power supply and to the monitor board. The keyboard cable jack is connected to the logic board by eight small wires. A wire harness connects the monitor board to the CRT yoke; another harness connects the CRT neck socket to the monitor board. Several wires are used to ground the various subassemblies.

The ribbon cable from the power supply to the logic board carries the three voltages needed on the logic board,  $+5\,\text{V}$ ,  $\pm$  12 V. The ribbon cable from the logic board to the monitor board provides the signals needed to drive the monitor board. The wires to the keyboard jack carry power, ground, and character information between the logic board and the keyboard. The wires between the monitor board and the CRT neck are color-coded with the corresponding color written on the monitor board. See the ATL-008 schematic in the drawings section.

### **Power Supply**

The 40W ATL power supply is an offline flyback converter that provides three DC outputs: +5V at 2.5 amps, +12V at 2.0 amps, and -12V at 0.25 amps, from a single 115V/230V AC line. The power supply is constructed on a single PC board measuring 6.0 in.  $\times$  3.7 in.  $\times$  1.7 in. It is designed to be cooled by convection in an operating range of  $0^{\circ}$ C to  $60^{\circ}$ C.

### Monitor

The ATL-008 terminal uses a  $90^{\circ}/20$  MM, TTL-compatible display requiring separate video, horizontal sync and vertical sync inputs. The +12 V monitor operating voltage is supplied through the input signal connector. There is also a provision to connect an external brightness control through the same input signal connector. ATL terminals utilize this feature to provide a contrast control in TCM. The monitor consists of a Printed Circuit Board (PCB) assembly and a Cathode Ray Tube (CRT) assembly. The monitor screen is covered by a nylon mesh anti-glare screen.

### Keyboard

The ATL terminal keyboard is a low-profile, detachable, intelligent serial unit. It complies with the DIN specification that the home row keys be 30mm above the work surface and that the keyboard be inclined at an angle between 7 and 11 degrees.

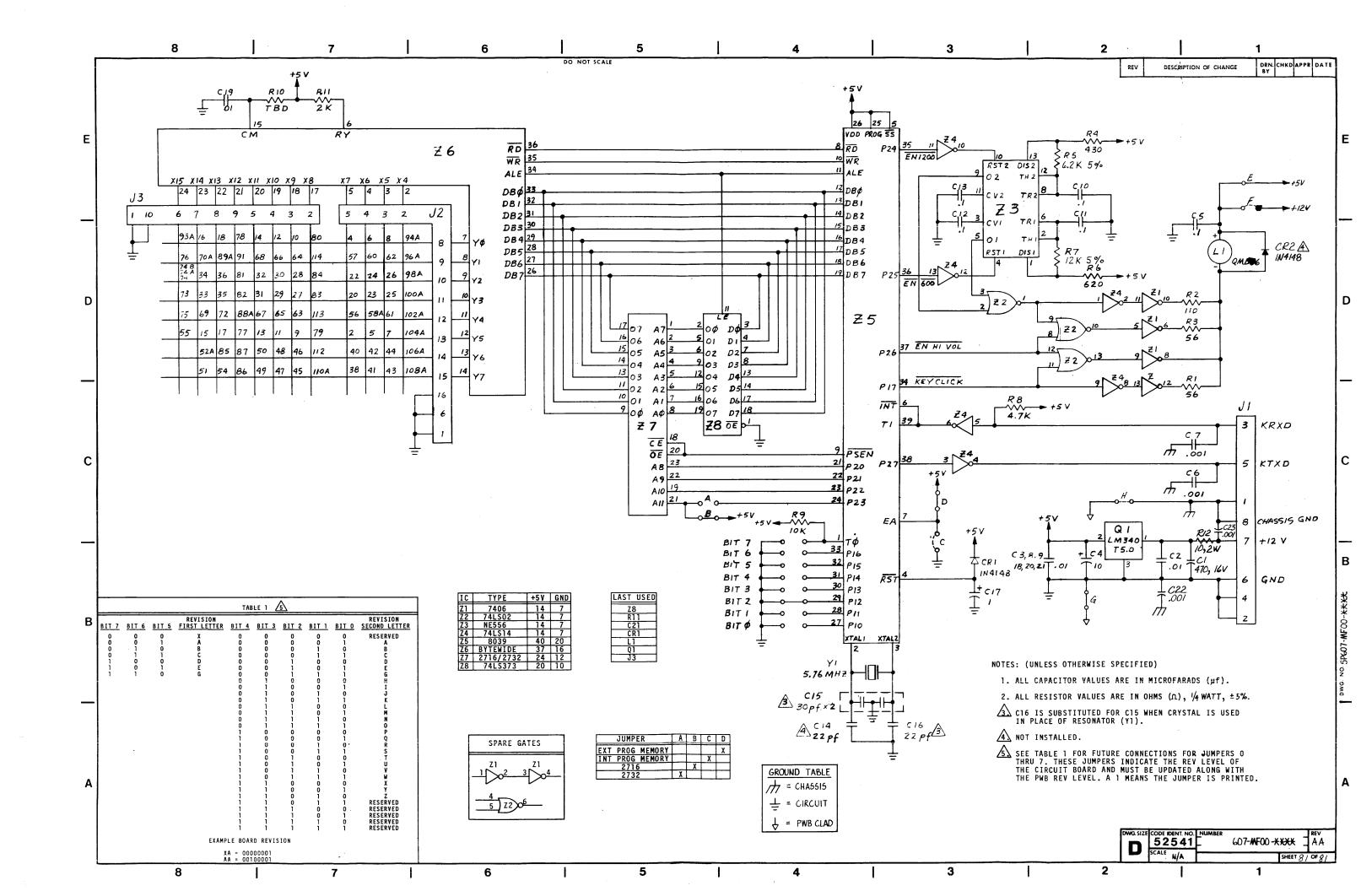

Scanning circuitry is based on the P8039-6 microprocessor and an external 2716 ROM. The microprocessor communicates data between the 94 keystation matrix and the main terminal processor over a 9600 baud bidirectional, full duplex serial link.

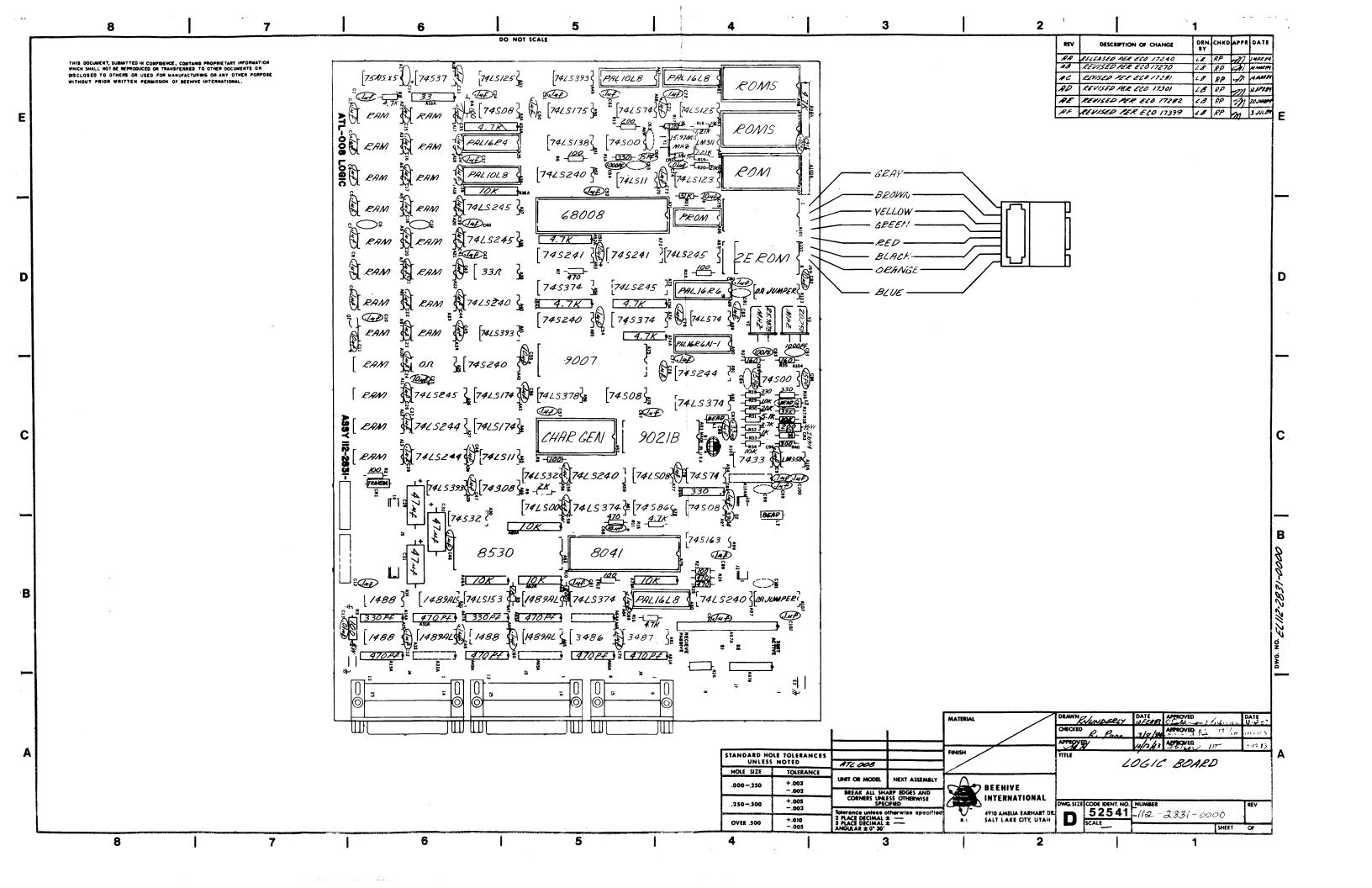

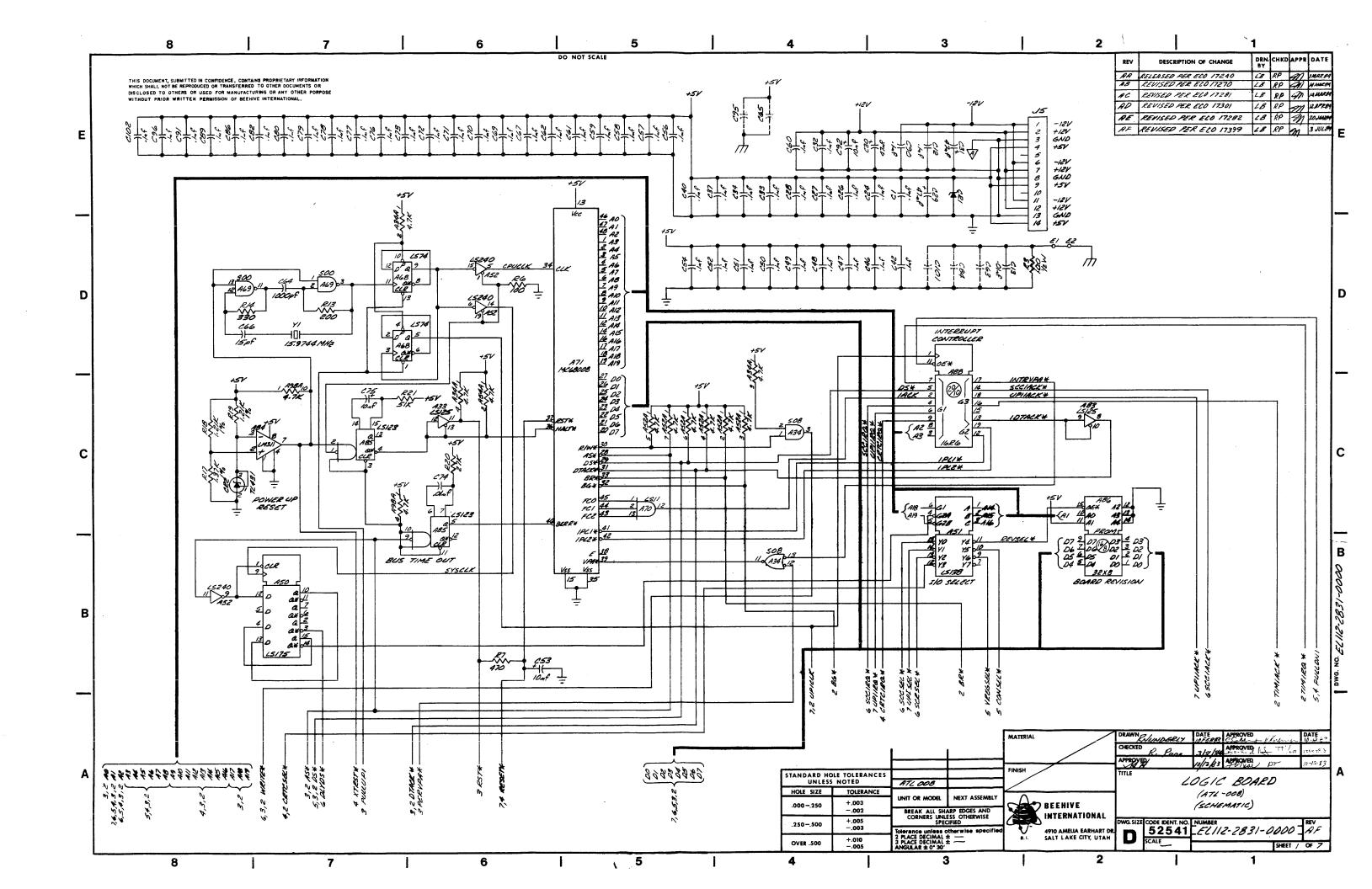

### Logic Board

The ATL-008 terminal logic board contains the terminal microprocessor, communications circuitry, memory, and video control circuitry. The 68008 microprocessor allows the use of an 8-bit data bus. It controls the system operation by executing instructions read from the program memory. The 8530 Serial Communications Controller (SCC) is a dual channel, full duplex, multiprotocol data communications peripheral which functions as a serial-to-parallel, parallel-to-serial converter/controller. The 8041/8741 is a Universal Peripheral Interface (UPI), designed as a general purpose programmable interface device compatible with a variety of microprocessor systems. It functions basically as an intelligent UART to reduce overhead for the 8039 microprocessor on the keyboard and to provide certain status information about the main and aux ports.

The ATL-008 memory consists of dynamic RAM, static RAM, ROM, and EEPROM. The standard ATL-008 has 32K bytes of DRAM, which is upgradable to 128K bytes. The video section is comprised of a CRT controller, a video attribute controller, four 1K  $\times$  4 bit static RAMs, and a clock generation circuit.

### ON-SITE MAINTENANCE AND REPAIR

### GENERAL INFORMATION

ection two contains information concerning the maintenance and repair of ATL terminals. It begins with some information on warranty provisions, then discusses the operating environment (ventilation considerations, power, etc.). It also illustrates potential shock hazards and lists the tools and test equipment required for board-level troubleshooting and repair. Finally, this section details the failures that can occur and gives illustrated instructions for removing and replacing subassemblies.

Warranty Provisions Limited warranty information is provided in the appropriate ATL technical user's manual. Warranties can vary considerably in accordance with specific purchase or lease agreements, so check your contract or contact your distributor for details.

### Operating Environment

**Terminal Placement** - ATL terminals are designed to function in a wide variety of office settings, and will provide good service if given the care normally afforded a valued office machine. Position the terminal (including the keyboard) so that it is not in danger of being dropped or otherwise harmed. Be sure to provide adequate room for ventilation—position the terminal so that it has a minimum of 3.5 inches of clearance on all sides.

Temperature and Humidity - Extremes in temperature or humidity can shorten the life of almost any electronic component. They can lead to malfunction or damage of solid state devices, changes in value in passive components, and many other reliability problems. ATL terminals may be operated when the temperature and humidity do not exceed the ranges specified in the appropriate technical user's manual. If the operating environment exceeds these ranges, the terminal should be shut off until the situation is corrected.

### Ventilation and Contaminants

ATL terminals are cooled by convection. This means that most of the ATL terminal's case consists of cooling vents. Great care must be taken to avoid spilling liquids into the terminal. Common substances such as coffee, soft drinks, cigarette ash and dust can cause problems with proper heat dissipation if they are spilled onto the circuit components. In extreme cases, such substances can cause short circuits resulting in erratic operation or damage to the terminal.

Preventing contamination is much easier than correcting it. Keep food, drink and smoking materials away from the terminal. Wipe off any spilled substances with a soft, dry cloth.

In areas where airborne dust or other contaminants are unavoidable, it is a good idea to cover the terminal when it is not in use. Be sure to remove the cover each time the terminal is turned on or overheating can occur. Remember, there is no fan and the cooling vents must be unobstructed.

#### **AC Power**

The AC power line voltage may vary  $\pm$  15% from the 115V or 230V that is specified for the terminal. The AC line frequency, however, must not vary more than  $\pm$  5% from the required 50 or 60 Hz. AC supplied to the terminal should be as free as possible from spikes, noise, and other transient problems.

### **Potential Hazards**

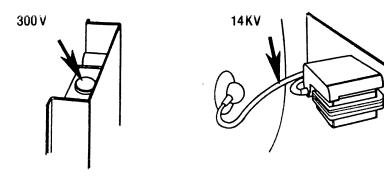

**Electric Shock** — Potentially *LETHAL* voltages are present at several points in the terminal. See Figure 2-1.

Figure 2-1 Electrified Electronic Technician

Take great care to become familiar with these areas and exercise caution. The power supply power transistor produces a 300 V signal. The monitor flyback (CRT anode) voltage is approximately 14 KV. See Figure 2-2.

Figure 2-2 Voltage Hazards

### Tools and Test Equipment

ATL terminals have been designed to be easily and rapidly seviced in the field. Disassembly, board-level troubleshooting, and reassembly require a few hand tools and test devices. The following tools are needed:

### Test Equipment

- Digital multimeter

- Tektronics 465 oscilloscope (or equivalent)

#### Tools

- Antistatic mat with wrist strap

- Medium flat-bladed screwdriver

- Long flat-bladed screwdriver with grounding jumper

- Phillips screwdriver

- Nut driver set

- Adjustable wrench

- Pliers

- Safety goggles

### PROBLEM DIAGNOSIS

his section describes procedures for determining the cause of a problem at the board level. A complete set of illustrated instructions for disassembly and replacement of each of the major subassemblies is contained in the next section. Use this section to determine the cause of the problem, then refer to the disassembly instructions to see how to replace the faulty board. This section assumes that the cover has been removed.

The normal power-up sequence is:

- Turn on the terminal.

- It should beep once, but the screen remains blank.

- After 35 to 40 seconds, it will beep again.

- The terminal will display the results of the selftest.

There are four types of problems that can occur: functional failures, video failures, communications failures, and keyboard failures. A functional failure means that the terminal will not power up. A video failure means that the terminal seems to power up (it beeps normally), but the resulting video is incorrect. A communications failure means that the terminal does not communicate with the host in a normal fashion. A keyboard failure means that the keyboard does not function.

#### General

All repairs to ATL terminals should be effected on an antistatic mat with a conductive wrist strap in use. An inspection of the interior of the terminal may reveal the cause of a problem:

- Check for loose wires that have come unsoldered.

- Be sure that the power supply and monitor board ribbon cables and the CRT neck connectors are firmly seated. Check the connections with the power off.

- ATL terminals have a large number of socketed chips on the logic board.

Due to the nature of sockets, it is always a good idea to check the seating of all socketed chips before attempting additional troubleshooting. With the power off, gently press each socketed chip.

- It is also a good idea to check the obvious things like power, keyboard, and communications cable connections.

### Functional Failures

The most probable cause of a functional failure is a faulty power supply. If the terminal does not beep normally during power-up, then the logic board is probably not receiving the correct voltages from the power supply. This may result from two causes: either the power supply input voltage is incorrect or the power supply is malfunctioning.

Check for the obvious problem of an unplugged terminal. If the terminal is plugged in, check the input voltage and compare it to the voltage given on the terminal identification plate on the back panel to make sure the power supply and the line voltage are compatible.

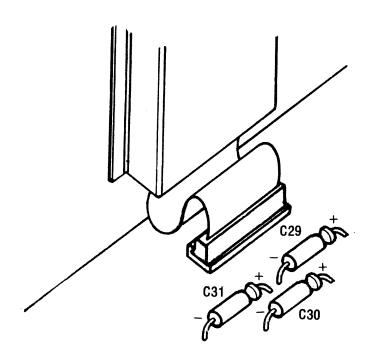

If the line voltage is correct, check the output voltages from the power supply. These voltages are -12, +12, and +5 VDC. Three capacitors near the power supply ribbon cable connector on the logic board are the best places to check these voltages. These three capacitors are identified by the numbers C29, C30, and C31 on the logic board. Figure 2-3 illustrates the relative positions of these capacitors. Compare the measured voltages with those given in Table 2-1. If the measured values are outside the acceptable ranges, replace the power supply.

Figure 2-3

Power Supply

Output Voltage

Locations

| Table 2-1       |

|-----------------|

| Power Supply    |

| Output Voltages |

| VOLTAGE | ACCEPTABLE RANGE       | LOCATION            |

|---------|------------------------|---------------------|

| +5V     | +4.95 V to +5.25 V     | C29 (positive side) |

| +12 V   | +11.4V to $+12.6V$     | C30 (positive side) |

| –12 V   | -13.8  V  to  -10.8  V | C31 (negative side) |

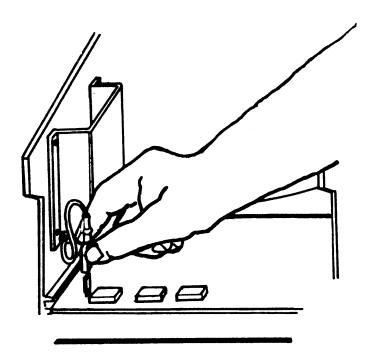

If the +5VDC output drops below 4.85V (approximately), it will trip the reset circuit. The +5 volt supply may be adjusted slightly by tweeking a pot on the power supply printed circuit card. Locate the adjustment pot through the access hole in the side support. It is located immediately above the ribbon cable and requires a small flat-bladed tool. Figure 2-4 illustrates the pot.

### Figure 2-4 +5 VDC Adjustment Pot

### Video Failures

A video failure means that the video output is incorrect. It does not mean that bad data is visible on the screen. Bad data means that there are readable characters on the screen, even if they are not the expected characters. Bad video means that the characters (if any) are not readable. Bad data results from either a communications failure or from a bad logic board. This section deals only with bad video, not bad data.

If the terminal beeps correctly during the power-up sequence but the video is bad, one of three things is happening:

- The logic board is not sending the correct +12VDC, video, horizontal sync, and vertical sync signals to the monitor card, resulting in bad video. If this is the case, replace the logic card.

- The logic board is sending the correct +12VDC, video, horizontal sync, and vertical sync signals to the monitor card, but the monitor card produces bad video. If this is the case, replace the monitor card.

- The cable between the logic card and the monitor card is bad. Check it for shorts and continuity.

Check the video output signals from the logic board with an oscilloscope. Check the  $+12\,\text{VDC}$  signal from the logic board with a voltmeter. The output signals from the logic card to the monitor card are listed in Table 2-2.

Table 2-2 Logic Board Video Output Signals

| SIGNAL          | LOCATION |

|-----------------|----------|

| Video           | Pin 8    |

| Horizontal Sync | Pin 6    |

| Vertical Sync   | Pin 9    |

| +12 VDC         | Pin 7    |

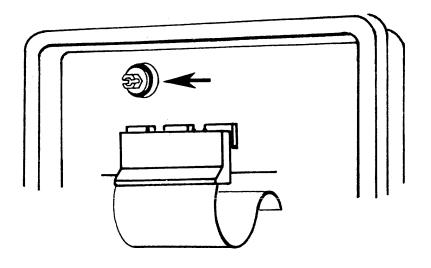

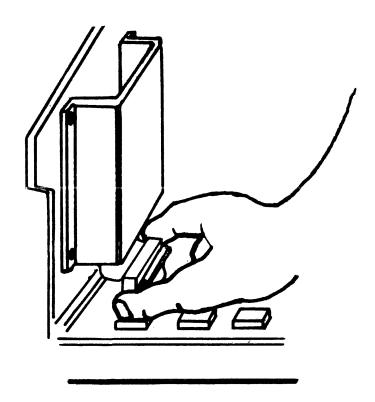

All locations refer to the monitor card ribbon cable connector on the logic board. Pin 1 is closest to the back panel of the terminal and the pins are numbered sequentially as illustrated in Figure 2-5.

Figure 2-5

Logic Card Ribbon

Cable Connector to

Monitor Card

The signals are illustrated in Figures 2-6 through 2-8. Signals may vary slightly from the illustrations, but they should be similar.

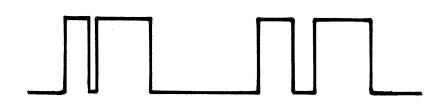

Figure 2-6 Video Output from Logic Card (Pin 1)

.5 millisecond timebase, 2 volts per vertical division

(This illustration shows the video corresponding to the selftest report and the status lines—other displays will have correspondingly different video patterns.)

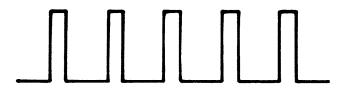

Figure 2-7 Horizontal Sync Output from Logic Card (Pin 6)

20 microsecond timebase, 2 volts per vertical division

Figure 2-8

Vertical Sync Output

from Logic Card

(Pin 9)

5 millisecond timebase, 2 volts per vertical division

### Communications Failures

Communications failures may result from three sources:

- Incorrect Terminal Configuration Manager settings.

- Faulty modem or line.

- Faulty logic card.

Verify that the TCM settings are correct for the particular installation. Place the terminal online. If the TCM settings are correct and the terminal does not communicate, check the problem port to determine if the source of the problem is the logic card or some external factor.

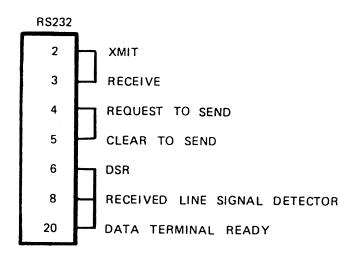

Main Port RS232 - Pin 2 carries the transmitted data. Connect Pin 2 to an oscilloscope and press a few keys. If the logic board data transmitter section is functioning properly, you will see a momentary change in the scope display. RS232 voltage levels should change from  $-12\,\text{VDC}$  to  $+12\,\text{VDC}$ . If the oscilloscope shows no change, then the logic board should be replaced. If the scope shows the correct voltage difference and the terminal is not communicating properly, then the problem is caused by some external factor (host, data line, or modem).

Check the logic board RS232 receivers by looping Pin 2 to Pin 3 with the terminal online, Auto Echo off, and full duplex set. Figure 2-9 shows how to build a loopback connector for this test. Type a few keys; the characters should be transmitted out Pin 2, received at Pin 3, and displayed on the screen. If they are not, then replace the logic board.

Figure 2-9 RS232 Loopback Test Connector

Aux Port RS232 - Pin 3 carries transmitted data from the terminal. Connect Pin 3 to an oscilloscope and press a few keys. If the logic board data transmitter section is functioning properly, you will see a momentary change in the scope display. RS232 voltage levels should change from  $-12\,\text{VDC}$  to  $+12\,\text{VDC}$ . If the oscilloscope shows no change, then the logic board should be replaced. If the scope shows the correct voltage difference and the terminal is not communicating properly, then the problem is caused by some external factor (host, data line, or modem).

Check the logic board RS232 receivers by looping Pin 3 to Pin 2 with the terminal online, Auto Echo off, and full duplex enabled. The same loopback connector illustrated in Figure 2-9 may be used. Type a few keys; the characters should be transmitted out Pin 3, received at Pin 2, and displayed on the screen. If they are not, then replace the logic board.

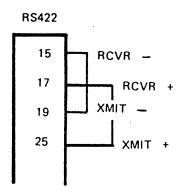

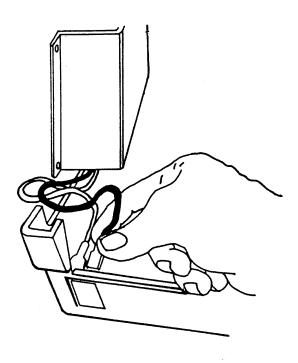

Main Port RS422 - Install a loopback test connector constructed as illustrated in Figure 2-10 to test the transmitters and receivers simultaneously. Type a few characters. If they appear on the screen, the port is functioning correctly and the problem is due to some other part of the communications connection. If they do not, replace the logic board.

Figure 2-10

Main Port RS422

Loopback Test

Connector

Pin 4 is the RECEIVE DATA line. Monitor the communication by connecting an oscilloscope to Pin 4. The signal should change from -6VDC to +6VDC.

**20 mA Current Loop** - Connect a loopback test connector constructed as illustrated in Figure 2-11. Type a few characters. If they appear on the screen, the port is functioning correctly and the problem is due to some other part of the communications connection. If they do not, replace the logic board.

Figure 2-11

20 mA Current Loop

Loopback Test

Connector

Pin 2 is the TRANSMIT MINUS line. Monitor the communication by connecting an oscilloscope with a current probe to Pin 2. The current should change from 0 to 20 mA. If the oscilloscope shows no change, then the logic board should be replaced.

### KEYBOARD FAILURES

f the power supply, logic board, and monitor board are all functioning properly, and typing on the keyboard produces no characters on the screen, the problem may stem from three sources:

- The terminal is online and disconnected from the host.

- The logic board is not supplying the correct power to the keyboard.

- The cable from the keyboard to the terminal is faulty.

- The keyboard is faulty.

Check for the first problem by placing the terminal offline. Turn the terminal on and press the EXTENDED screenkey, then press the OFFLINE screenkey. This will put the terminal offline. Type a few characters. If the keyboard does not work, then one of the other problems is the difficulty. Put the terminal online again. If the keyboard does not work, but it worked when the terminal was offline, check for communications problems.

Check the small wires from the keyboard jack to the logic board for apparent damage. Check the voltages on the orange wire, Pin 7 of the keyboard jack. The orange wire carries  $+12\,\text{VDC}$ . If this voltage is not present, replace the logic board because it is not supplying the correct power to the keyboard.

Checking for a faulty keyboard cable involves checking each end of the cable for the correct voltages. The preceding paragraph contains instructions for checking the logic board end of the cable. Check the keyboard end by taking the keyboard apart and checking the incoming power regulator for correct voltages from the logic board to the keyboard. It is located at the upper left corner of the keyboard printed circuit. Pin 1 carries +12VDC, Pin 3 carries Ground, and Pin 2 carries +5VDC. The pins are numbered from bottom to top. If the voltages are good at the keyboard jack on the logic board and bad at the regulator, replace the cable.

Check the keyboard function by checking the RECEIVE and XMIT DATA lines of the microprocessor in the keyboard. Pin 39 is the RECEIVE DATA signal; Pin 38 is XMIT DATA. (These signals are also present on Pins 3 and 5 of the keyboard cable connectors.) Connect an oscilloscope to each pin in turn and press a few keys. You should see a momentary change in the scope display. If the display does not change, replace the keyboard.

### SUBASSEMBLY REPLACEMENT

ead this section completely before disassembly. It gives step-by-step illustrations and descriptions of removal and replacement of ATL terminal subassemblies, with helpful hints pertaining to each subassembly.

### Tools and Tips

Each of the procedures that follow gives a list of tools needed to perform that particular procedure. The following list is a comprehensive list of all tools needed to replace ATL subassemblies.

Medium flat-bladed screwdriver

Long flat-bladed screwdriver with grounding jumper

Phillips screwdriver

Nut driver set

Adjustable wrench

Pliers

Safety goggles

Use an antistatic mat to protect sensitive integrated circuits. Effect all repairs in a well-lit work area with enough room to accommodate the terminal and the subassemblies being removed. Tilting the screen can sometimes make repairs easier.

In general, reassembly is the reverse process of disassembly; the last portion of each procedure lists any exceptions to this as well as details that make reassembly easier.

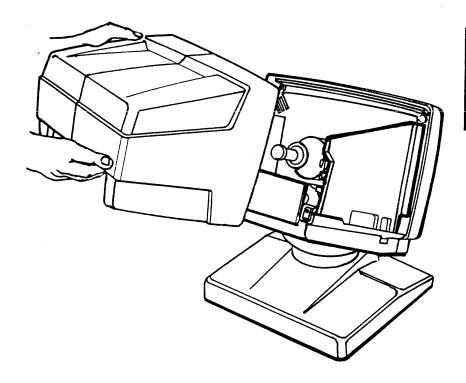

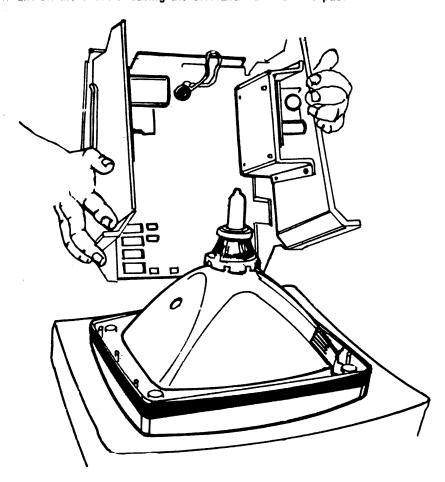

### Removing and Replacing the Cover

The only tool needed to remove and replace the cover is a medium flat-bladed screwdriver.

Before any of the subassemblies except the keyboard are serviced, the rear cover must be removed as follows:

1. Turn the terminal off and remove the power cord from the rear panel. You may also wish to remove the strain relief from the bottom of the terminal if it has been installed.

2. Remove the two cover retaining screws with a flat-bladed screwdriver.

3. Slide the cover away from the front bezel and take it off of the terminal. ATL covers fit quite tightly. It may be necessary to use a bit of force to remove the cover. Just remember that this is a sensitive piece of equipment—crowbars, jackhammers and hydraulic rams are not needed. Your bare hands should suffice.

4. Tilt the rear panel as illustrated and lift it out of the groove that it normally occupies. It may usually be left attached by its ground wire.

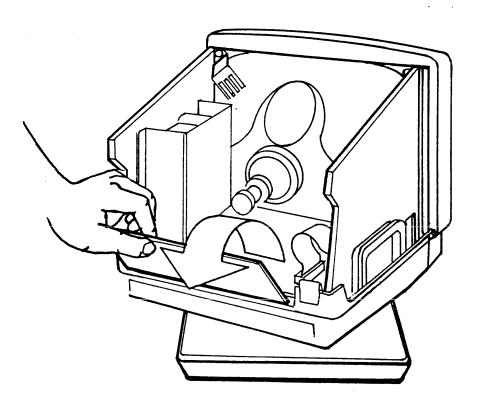

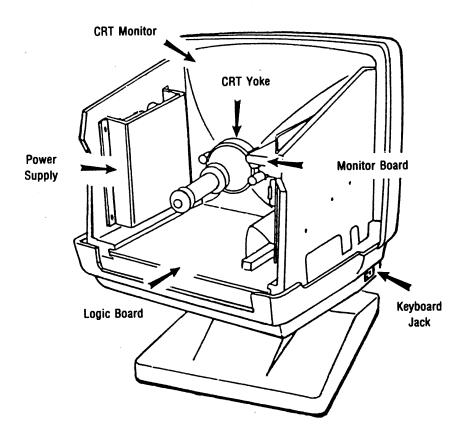

Once the cover is off, the remaining subassemblies of the screen enclosure are readily identified as in this illustration:

Replacing the cover is the reverse process. The only difficulty that may occur is the proper alignment of the cover with the front bezel. Be sure that they are aligned as you slide the cover back on and you should not have any trouble.

Before replacing the cover, make a final inspection of all wires and cables to be sure that everything is properly connected.

### Removing and Replacing the Logic Board

The logic board may be removed with no tools other than your bare hands; however, a medium flat-bladed screwdriver may be useful in separating cable connectors.

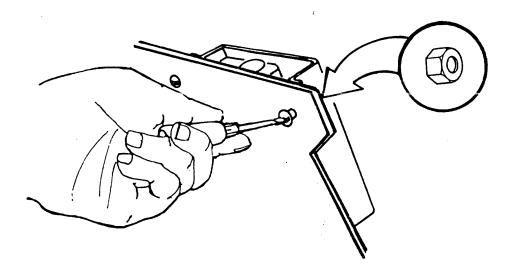

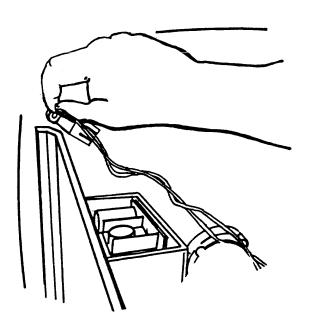

This section assumes that the keyboard cable has been unplugged from the side of the screen enclosure (it works like a telephone jack) and that the rear cover has been removed. The logic board has four connections to the rest of the ATL terminal. Disconnect them as follows:

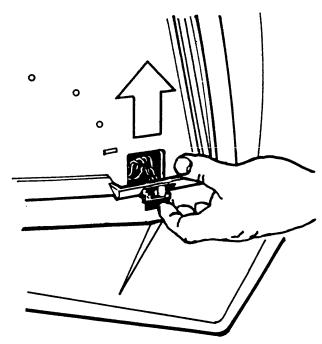

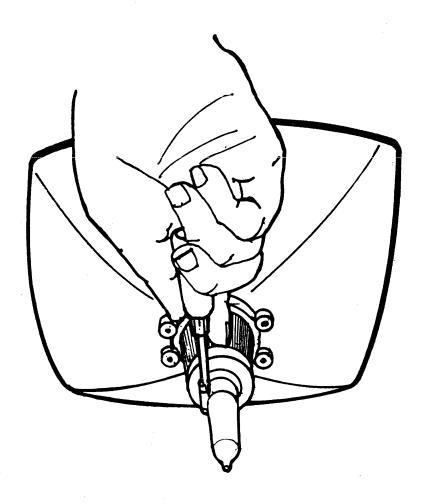

Push up on the keyboard cable jack as shown here and tuck it and its connecting wires inside the terminal so that the cable jack rests on the logic board.

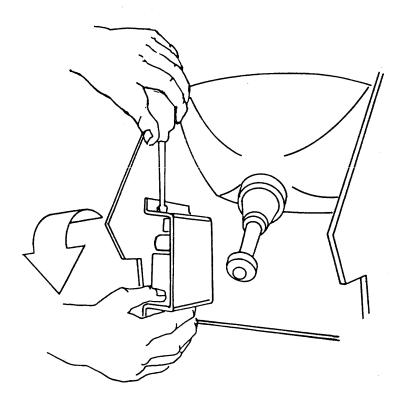

2. Disconnect the ribbon cable from the monitor board at the logic board as shown, lift it up and loop it over one of the wires between the yoke and the monitor board so that it does not snag on any of the logic board components when the board is removed. When reconnecting this cable, be sure to unhook it from the yoke wires first to avoid damage to the fragile neck of the CRT.

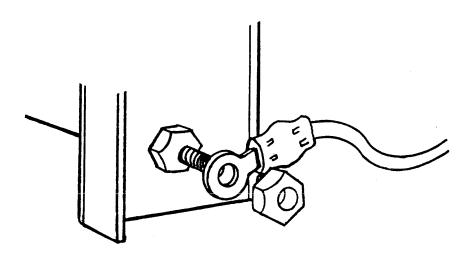

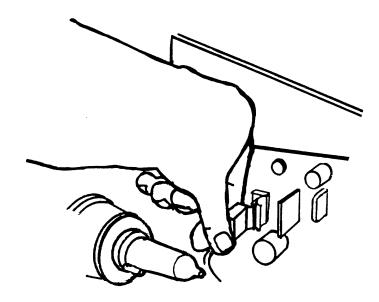

3. Disconnect the ground wire from the logic board to the power supply. Unplug the connector at the logic board as shown.

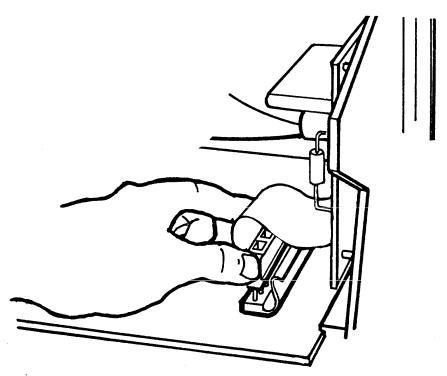

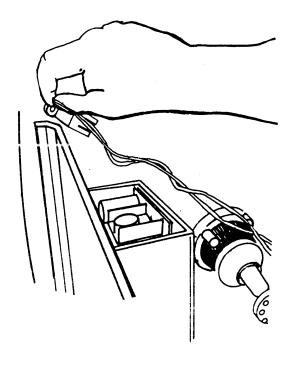

4. Disconnect the ribbon cable from the power supply at the logic board. Disconnect it at the logic board like this:

Hold the power supply ribbon cable so that is does not snag on any of the logic components and slide the logic board out. Take care not to snag the keyboard cable jack and wires.

To replace the logic board, reverse the procedure. The ribbon cable from the power supply is the trickiest to reconnect because of the limited amount of room between the power supply and the logic board. If you hooked the monitor board ribbon cable over a yoke wire during disassembly, be sure to unhook it before reconnecting it to the logic board.

Removing and Replacing the Power Supply

This procedure requires the following tools and parts:

Medium flat-bladed screwdriver Nut driver set

This section assumes that the logic board has been removed. The power supply is the only subassembly that requires prior removal of another subassembly; the monitor and monitor board do not require removal of the logic board.

1. The logic board must be removed to expose the wires that connect the power supply to the on/off switch located on the rear panel below the power supply. They are connected with spade connectors as shown. Unclip the connectors from the switch. Note that the blue wire is on the left side of the switch and the brown wire is on the right side of the switch (when viewed from the back of the terminal) as shown.

2. The power supply chassis is supported by two flanges on the lower corners and by two screws on the upper corners. Remove the screws.

3. Tilt the power supply away from the side support and remove the ground wires from the top and bottom of the power supply.

4. Remove the power supply while threading the wires to the on/off switch through the side support and around the circuit board guide slots. Note the routing of these wires; it is important that they be routed in the same fashion during reassembly.

Installation of a new power supply is the reverse of this procedure. The wires to the on/off switch must be threaded through the side support and under the guides for the circuit boards.

Removing and Replacing the Monitor Board and Yoke This procedure requires the following tools:

Long flat-bladed screwdriver Grounding jumper wire Phillips screwdriver Safety goggles

This section assumes prior removal of the cover. Removal of other sub-assemblies is not required.

DANGER

This procedure involves dealing with the high-voltage connection between the monitor board and the CRT. On ATL terminals, this connection carries about 14KV. This voltage is stored in the CRT even after the terminal has been turned off and the power cord has been removed. Unless you have just removed the charge, assume it to be present.

DANGER

If the glass case of the CRT is damaged, the CRT may implode, resulting in danger from flying glass. Wear safety goggles during this procedure.

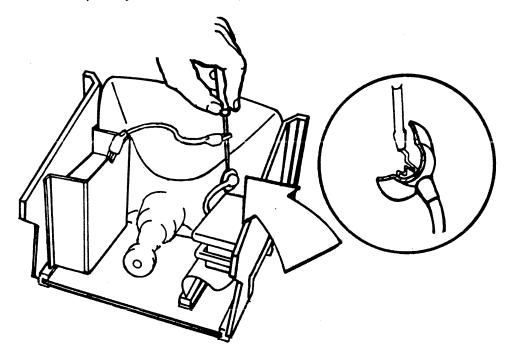

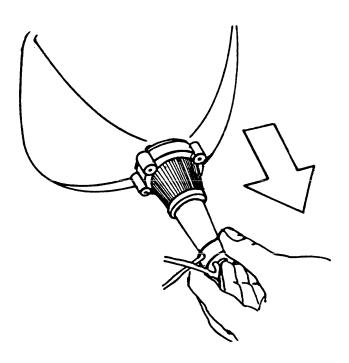

1. To remove the charge from the CRT, connect a jumper wire between a long, flat-bladed insulated screwdriver and ground, insert the tip of the screwdriver under the rubber boot on the side of the CRT and touch the flyback transformer lead with the tip of the screwdriver. It is best that this be done with only one hand so that you do not inadvertently touch the metal portion of the screwdriver or the exposed lead. Handle only the insulated portion of the screwdriver. You will hear a popping sound and may see a spark. This indicates that the charge has been at least partially removed. Part of the charge can still be present so exercise caution. To remove as much of the charge as possible, ground the flyback lead repeatedly until there is no spark or pop.

- Use the same grounded screwdriver to compress the flyback lead spring and remove the lead and the rubber boot. Reconnecting this lead during reassembly is easier if you fold the rubber boot back on the lead wire and compress the spring lead with a screwdriver while reinserting it into the CRT.

- 3. Remove the ground wire that connects the monitor board to the CRT DAG clip. It is connected with a spade connector.

4. Remove the connector from the neck of the CRT. The neck is very fragile; take care not to damage it. Heed the warning about flying glass.

5. There are several wires from the CRT yoke to a connector on the monitor board. Remove the connector from the monitor board.

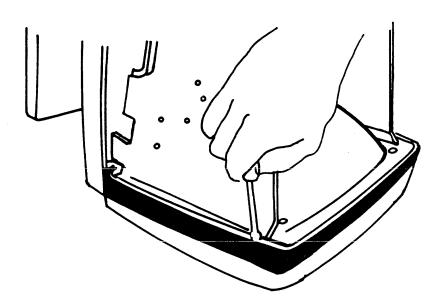

6. The monitor board is supported by two flanges on the lower corners and by two plastic standoffs on the upper corners. Pinch the standoffs as shown,

tilt the monitor board away from the side support and remove it, taking care not to tangle the ground and neck connector wires. If you are only removing the monitor board and do not need to remove the yoke, this is the final step.

7. Loosen the yoke clamp screw (the larger of the two screws on the yoke assembly). Slide the yoke off of the neck of the CRT.

The monitor board is reinstalled by reversing this procedure. Take care when replacing the neck connector. Reinstall the flyback lead by folding the rubber boot back on itself as much as possible and insert one side of the spring in the CRT, then press the spring together with the screwdriver and push it into the CRT.

When reinstalling the yoke, it will be necessary to adjust it with power on so that the raster is properly aligned. This is done by placing the yoke on the neck, aligning it visually and tightening the clamp slightly so that the yoke may still turn on the neck. Make all connections and turn on the terminal. While watching the screen, turn the yoke until the raster is horizontal and tighten the clamp. Take care not to over-tighten the clamp — remember the fragility of the neck. You only need to tighten the clamp enough to prevent the yoke from turning.

### Removing and Replacing the Monitor CRT

This procedure requires the following tools:

Long flat-bladed screwdriver with grounding jumper Phillips screwdriver Nut driver set Adjustable wrench Pliers Safety goggles

This section assumes prior removal of the cover. Removal of other sub-assemblies is not required; however, the monitor board must be disconnected from the CRT. This is accomplished by undoing all connections between the monitor board and the CRT as described in the previous procedure *Removing* and *Replacing the Monitor Board and Yoke*. The connections that must be removed are the flyback lead, DAG ground wire, neck connector, and CRT yoke connector.

DANGER

This procedure involves dealing with the high-voltage connection between the monitor board and the CRT. On ATL terminals, this connection carries about 14KV. This voltage is stored in the CRT even after the terminal has been turned off and the power cord has been removed. Unless you have just removed the charge, assume it to be present.

DANGER

If the glass case of the CRT is damaged, the CRT may implode, resulting in danger from flying glass. Wear safety goggles during this procedure.

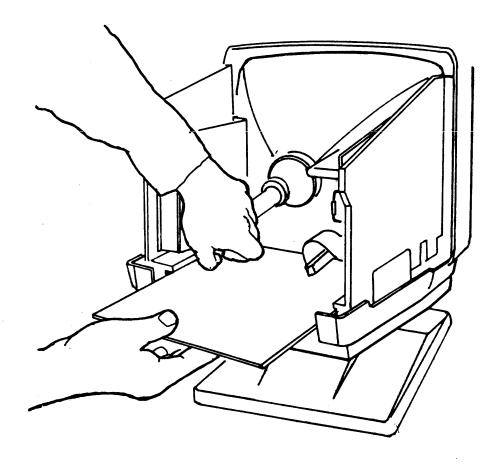

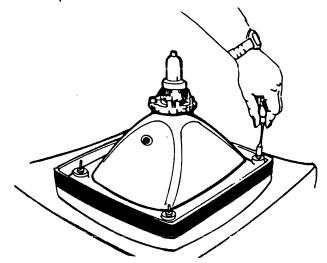

After disconnecting the monitor board from the CRT, remove the ground wire between the power supply and the CRT. It is connected with a spade connector.

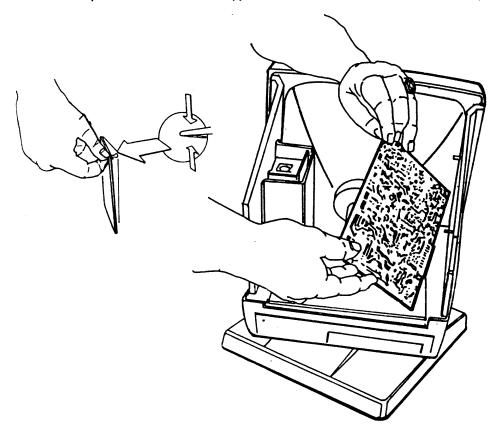

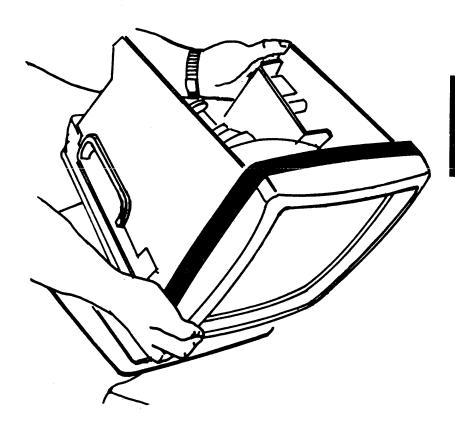

2. Place the screen face down on a soft pad, like this:

3. Remove the six screws that hold the CRT frame to the side supports.

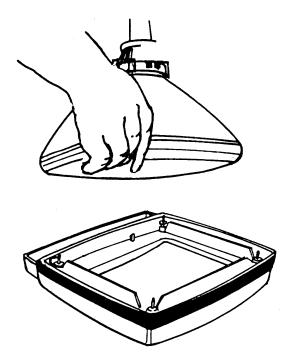

4. Lift off the chassis leaving the CRT and frame on the pad.

5. Remove the four nuts that hold the CRT frame to the front bezel. Note the position of the DAG clip relative to the flyback connector hole; this will serve to orient the new CRT to the rest of the terminal. Remove the DAG clip. When reinstalling the CRT, be sure to put the DAG clip on the same corner. If the studs turn when the you use a nut driver on the nuts, use an adjustable wrench instead of the nut driver and hold the end of the stud with pliers or a special socket.

6. Lift the CRT out of the bezel.

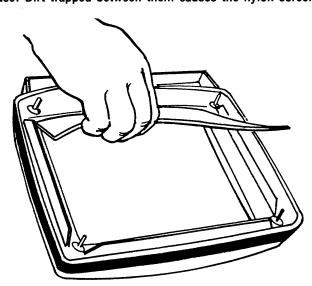

7. The nylon anti-glare screen may be removed from the bezel for cleaning if necessary. During reassembly, be sure that the new CRT screen is clean and that no dirt is trapped between the nylon screen and the CRT glass surface. Dirt trapped between them causes the nylon screen to wrinkle.

There are two possible problems associated with replacing the CRT. They both have to do with the nylon anti-glare screen. The first problem is that of dirt trapped between the nylon mesh and the glass CRT screen. This may be avoided by cleaning the CRT immediately prior to installation.

The second problem involves adjusting the distance between the two screens. This problem usually occurs only when the bezel is being replaced; normally the factory adjustment is adequate. The four mounting studs that fasten the CRT to the front bezel are used for this purpose. The studs are threaded on both ends. The larger end fits into the bezel. The smaller end fits through a mounting tab on the CRT and has a star-shaped end. This star-shaped portion allows you to turn the entire stud with special socket or a pair of pliers.

It also allows you to hold the stud while tightening the nut that fastens the CRT tab to the bezel (this is why the tool list includes the pliers and an adjustable wrench). Turn all four studs completely into the bezel, then back them out half a turn, and attach the CRT. The remainder of the reassembly is the reverse of the removal procedure.

If the replacement CRT does not have a yoke assembly you will also have to remove the yoke from the malfunctioning CRT and replace it on the new CRT. The preceding section, Removing and Replacing the Monitor Board and Yoke, shows how to do this.

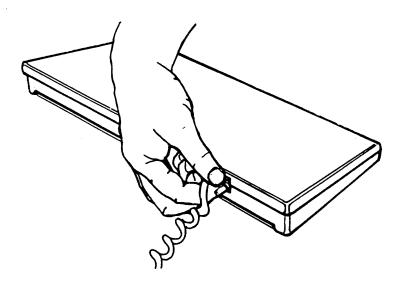

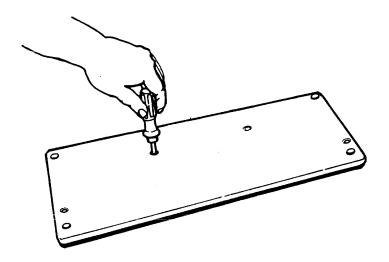

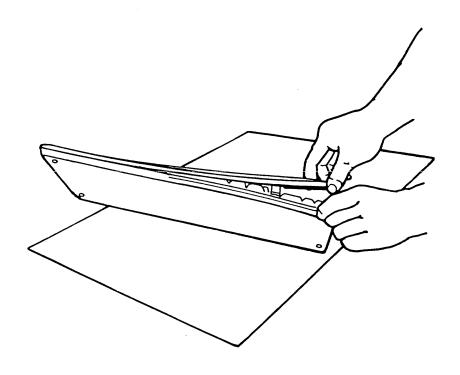

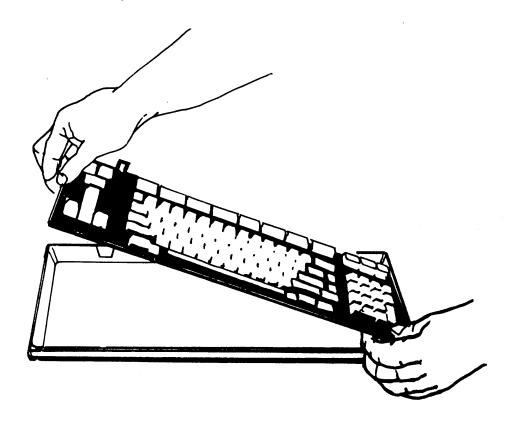

Removing and Replacing the Keyboard You will need a medium Phillips screwdriver for this procedure.

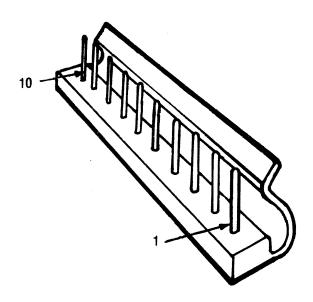

The keyboard enclosure is held together with four screws through the bottom of the case. It comes apart as follows:

1. Unplug the keyboard cord. It works like a telephone jack.

2. Turn the keyboard over and remove the four screws. Then turn the case right side up.

3. At this point, the keyboard is still held together by plastic catches inside the case. Carefully pry the cover open.

4. Lift off the top cover.

5. Lift out the keyboard printed circuit. Some keyboards have a sheet of insulating paper under the printed circuit. Take care not to damage it so that it may be reassembled intact.

6. Most keycaps pull off easily. Larger ones are fastened with a wire clip.

Reverse this process to replace the keyboard. Take care to adjust the keyboard printed circuit board in the case so that the keys do not bind on the edges of the openings in the top cover, then tighten the four screws.

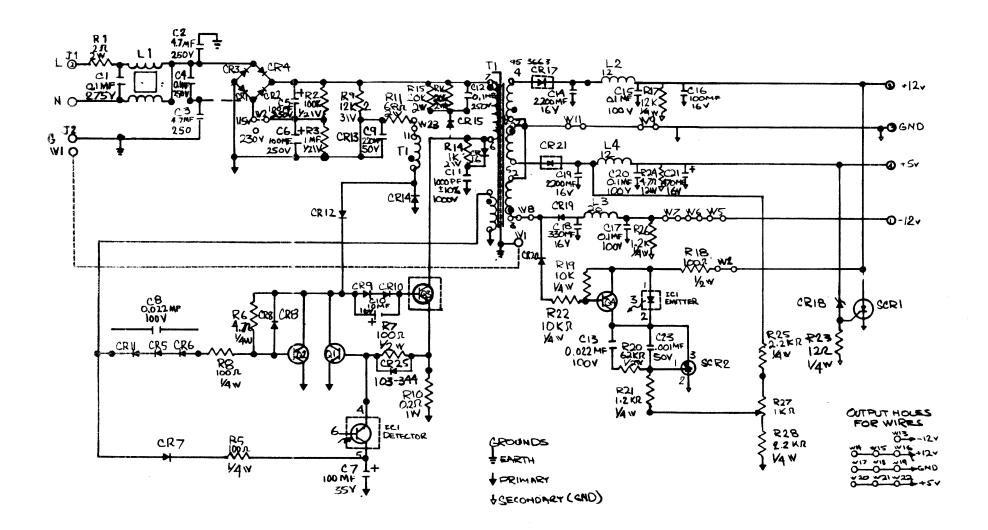

# ATL POWER SUPPLY FUNCTIONAL DESCRIPTION

#### **GENERAL**

he 40W ATL power supply is an offline flyback converter that provides three DC outputs—+5V at 2.5 amps, +12V at 2.0 amps, and -12V at 0.25 amps—from a single 115V/230V AC line. The power supply is constructed on a single PC board measuring 6.0 in. × 3.7 in. × 1.7 in. It is designed to be cooled by convection in an operating range of 0°C to 60°C.

The power supply should not be left connected to the input line voltage without a load on the outputs. Some sort of load should be maintained during testing to prevent burning out the power supply.

#### **FUNCTION**

ffline input voltage is applied to the power supply by line, neutral, and ground inputs. A 2-ohm fuse resistor provides primary over-current protection and limits the primary input surge current during cold start-up. An EMI filter consisting of four capacitors and a ballun provides common and normal filtering between the supply and the AC line. The input line at this point is rectified and filtered to provide a nominal ± 160 VDC primary rail voltage.

Q1, Q2, and T1 form the major components of a self-excited blocking oscillator. An RCL diode network provides sufficient base current to start the main switch transistor Q1 into conduction. Regenerative feedback is derived from a tertiary winding in phase with the primary of tranformer T1 and applied through an RC network to saturate Q1 during 50% of the cycle. Q1 is turned off by either the over-current protection circuit or the opto-coupler depending on whether the supply is in initial start-up or normal operation. Once Q2 is turned off, the secondary rectifier diodes become forward biased and the energy stored in the transformer is delivered to the secondary output filters and load.

Secondary voltage control is sensed off the 5VDC output. This voltage is divided down and applied to the sense pin of a 2.5V shunt regulator. When the 5V output reaches the threshold, the regulator conducts causing the photodiode to conduct which in turn causes Q1 to turn off. The PNP transistor then shunts the shunt regulator, insuring that during start-up, the phototransistor is conducting when Q1 is turned off.

Over-voltage protection is provided in the event that the loop fails to regulate the 5V output. A crowbar SCR conducts between the 5V output Zener threshold voltage and the SCR gate to the cathode threshold to prevent damage to the logic load. This in turn causes an over-current condition and resets the power supply. If the condition persists, the power supply will again reset.

3-1

# ATL-008 MONITOR FUNCTIONAL DESCRIPTION

#### **GENERAL**

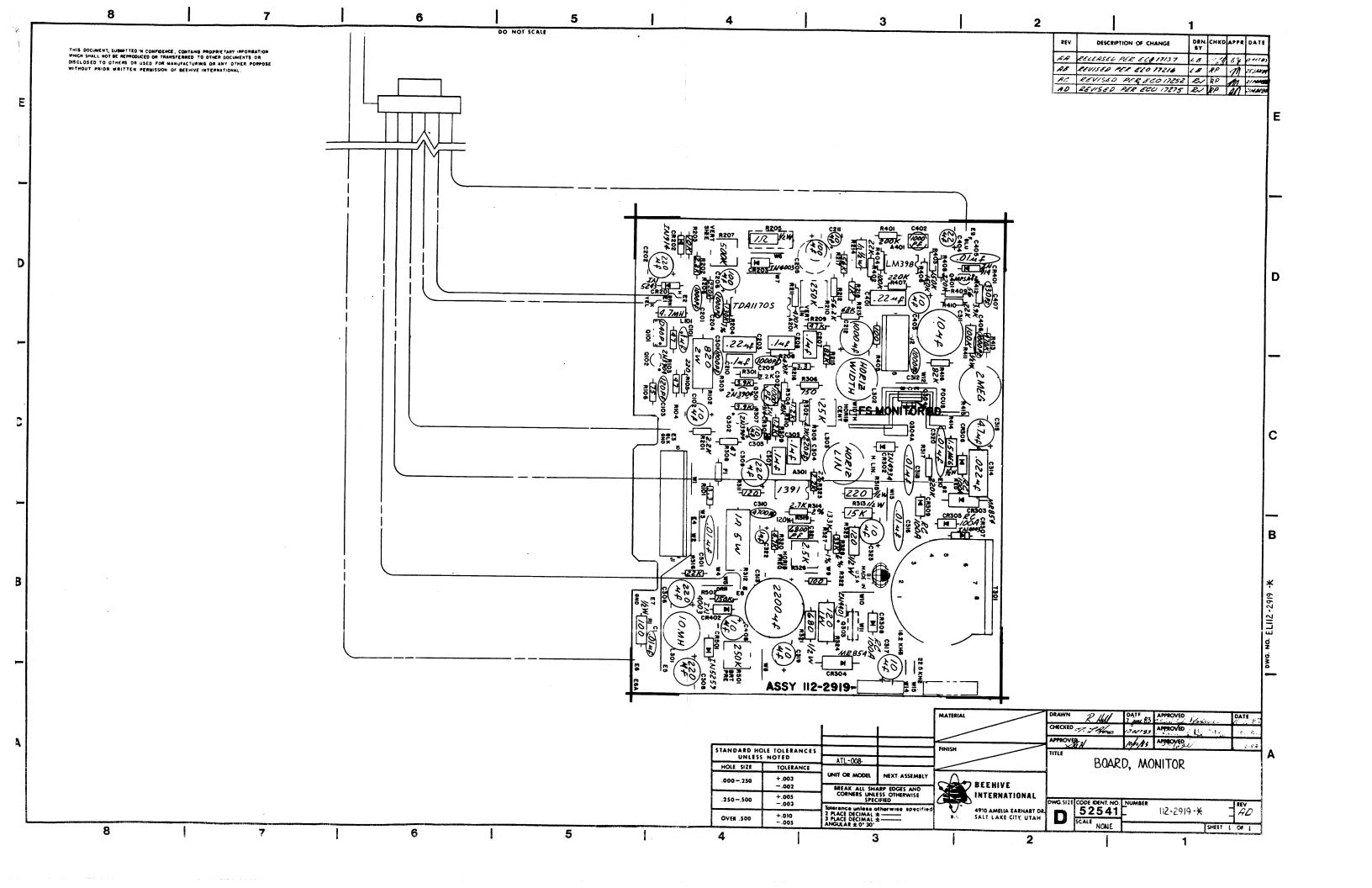

he ATL-008 terminal uses a 90°/20MM, TTL-compatible display requiring separate video, horizontal sync and vertical sync inputs. The +12V monitor operating voltage is supplied through the input signal connector. There is also a provision to connect an external brightness control through the same input signal connector on Pins 2, 3 and 4. The monitor consists of two major assemblies:

- 1. Printed Circuit Board (PCB) Assembly

- 2. Cathode Ray Tube (CRT) Assembly

#### PRINTED CIRCUIT BOARD ASSEMBLY

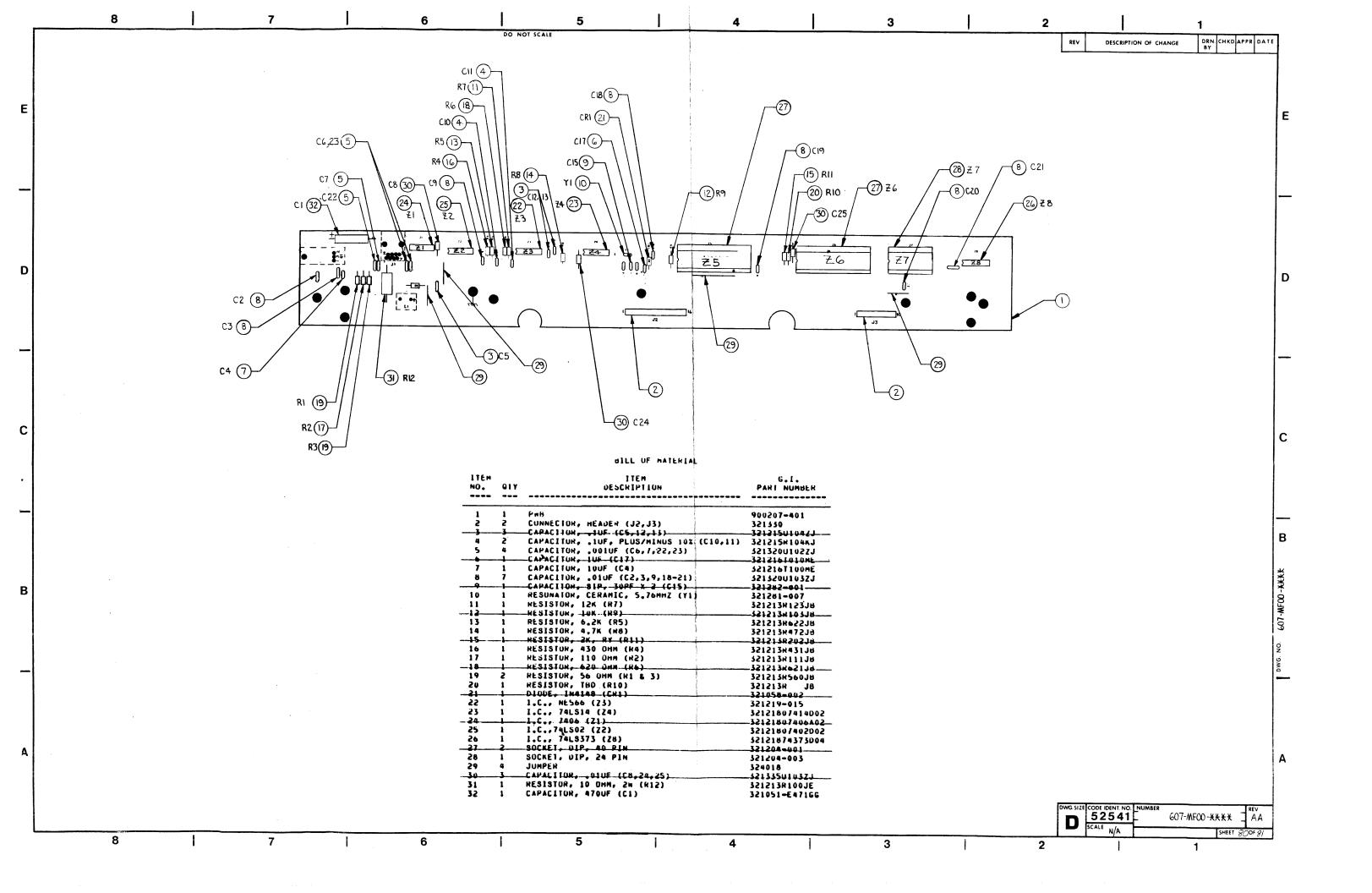

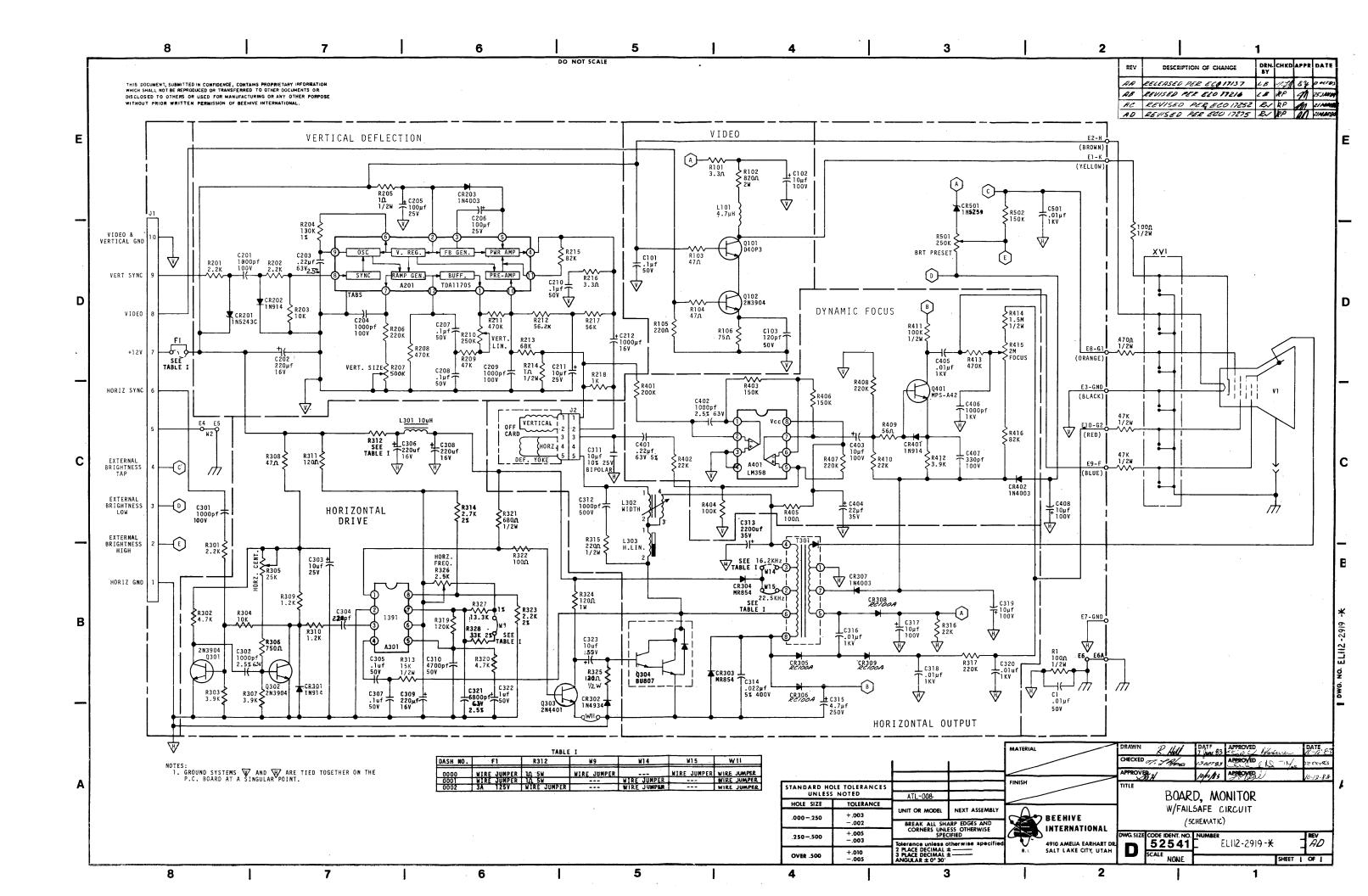

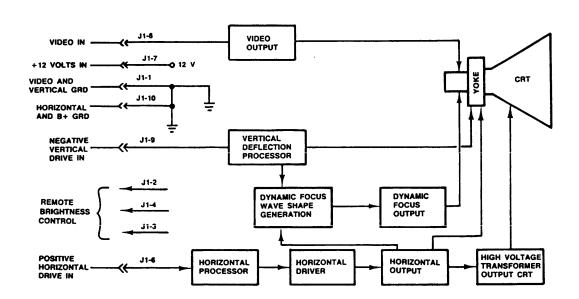

he PCB contains all the monitor electronics. The PCB assembly consists of a video amplifier, a vertical processing stage and a four-stage horizontal deflection circuit. Refer to Figure 4-1, ATL-008 Monitor Board Block Diagram, for the relationship between these four sections. Refer to Drawing EL112-2919-\*, ATL-008 Monitor Schematic, for component identification.

Figure 4-1 Monitor Board Block Diagram

#### Video Amplifier

The two-stage video amplifier consists primarily of Q101 and Q102. Q101 is connected in the common base configuration; Q102 is connected in the common emitter configuration. Together they form a cascode arrangement. This minimizes the Miller effect input capacitance and the breakdown voltage parameter of Q101.

The video amplifier accepts a TTL-compatible, non-composite, positive-going video input signal to produce the CRT cathode signal. R102 and R106 fix the gain of the amplifier at about 20dB. C103 and L101 are used for high frequency peaking to give a bandwidth of about 26MHz. R103 and R104 are limiting resistors to protect Q101 and Q102 from source spikes. R105 is a terminating resistor used to minimize frequency limiting effects of input cable capacitance. A buffering resistor is used in the CRT socket assembly.

In the absence of a video signal, transistor Q101 is non-conducting, thereby turning transistor Q102 off. This gives the same voltage at the CRT cathode as the video supply voltage. The threshold voltage needed to turn on Q101 is one PN-junction voltage (approximately 0.6 V). Once this threshold is passed, the amplifier operates in linear mode. 3.6 V P-P at the input results in a CRT drive voltage of approximately 28 V P-P. This drive voltage provides a video light output of approximately 15 foot-lamberts. Adjusting this voltage adjusts the screen intensity. R101 and C102 provide additional filtering of the video supply voltage.

## Horizontal Deflection

The horizontal deflection circuit consists of four distinct sections:

Horizontal Processor Horizontal Driver Horizontal Output High Voltage Transformer

Horizontal Processor - The horizontal processor circuit consists of a monostable multivibrator circuit (a one-shot) in Q301 and Q302 and an MC1391 horizontal processor, A301, along with their associated circuitry. The horizontal sync pulse is coupled to the base of Q301 through C301 and R301. The output of the multivibrator is differentiated by R310 and C304 and fed to the sync input of A301. R305, R306, C302 and R302 control the timing of the multivibrator pulse between 1 and 12 microseconds.

A301 contains an oscillator, a predriver and a phase detector. R326, R327, R328 and C321 control the RC type oscillator. The sawtooth output of the oscillator goes through a predriver in the MC1391 and comes out on Pin 1 of A301 as a rectangular pulse. This output is coupled through R322 to the base of Q303.

A negative-going sync pulse at the sync input (Pin 3) of A301 allows the phase detector of A301 to compare the phase relationship of the sync pulse at Pin 3 and the sawtooth waveform at Pin 4 (which is derived from Pin 6 of the flyback transformer). When a phase offset occurs, current will flow either in or out of Pin 5. Pin 5 is connected to Pin 7 via R319 and thus controls the oscillator. The ratio of R320 with respect to R319 controls the damping of the feedback loop.

R314 and R323 control the output pulse width of the A301 and ensure stability in the pulse width. R311 and C309 provide ripple rejection.

**Horizontal Driver** - The horizontal driver circuit consists of Q303, R324, C323, R325 and CR202. When the output of A301 is high, Q303 is biased on. It conducts and develops its signal across R324. This signal is coupled through C323 to the base of Q304.

**Horizontal Output** - The horizontal output stage performs two main functions. It generates the necessary drive current for the horizontal yoke and develops supply voltages to drive the CRT.