Filed Nov. 6, 1953 9 Sheets-Sheet 1 BY

.

Filed Nov. 6, 1953

Filed Nov. 6, 1953

Filed Nov. 6, 1953

Filed Nov. 6, 1953

9 Sheets-Sheet 5

BY

INVENTOR.

ROBERT M. BECK,

JOSEPH A. BEEK, JR.

GLENN E. HAGEN

CECIL R. RUSSELL

CHARLES R. WILLIAMS

ATTORNEY

ATTORNEY

Filed Nov. 6, 1953

Filed Nov. 6, 1953

Filed Nov. 6, 1953

9 Sheets-Sheet 8

| CORRECTION | VOLTAGE ON PLATE OF LEFT TUBE IN MULTIVIBRATOR 290 | VOLTAGE ON PLATE OF LEFT TUBE IN MULTIVIBRATOR 270 |  |

|------------|----------------------------------------------------|----------------------------------------------------|--|

| -12 E D Y  | HIGH                                               | LOW                                                |  |

| +22 D Y    | LOW                                                | LOW                                                |  |

| -/2 Y      | HIGH                                               | HIGH                                               |  |

| SERVO      | LOW                                                | HIGH                                               |  |

\_\_\_\_\_\_\_13

BY

INVENTOR.

ROBERT M. BECK,

JOSEPH A. BEEK,

JR.

GLENN E. HAGEN

CECIL R. RUSSELL

CHARLES R. WILLIAMS

W. LIENT E. MELCALL

ATTOCNEY

Filed Nov. 6, 1953

3,007,639 DIGITAL DIFFERENTIAL ANALYZERS Glenn E. Hagen, Manhattan Beach, Charles R. Williams, Palos Verdes Estates, Joseph A. Beek, Jr., Balboa Island, Robert M. Beck, Inglewood, and Cecil R. Rus-sell, Manhattan Beach, Calif., assignors, by mesne assignments, to The Bendix Corporation, North Hollywood, Calif., a corporation of Delaware Filed Nov. 6, 1953, Ser. No. 390,506 16 Claims. (Cl. 235—152)

This invention relates to digital differential analyzers and more particularly to a system for enhancing the accuracy and operation of digital differential analyzers in obtaining the solution of mathematical problems.

In co-pending application Serial No. 217,478, filed 15 March 26, 1951, now Patent No. 2,900,134, by Floyd G. Steele and Wm. F. Collison, a digital differential analyzer is disclosed for solving complex differential equations by digital steps. The analyzer operates like a differential produce variations in the quantities in one integrator in accordance with the values of the quantities from other integrators. The analyzer operates like a digital machine in digitally varying the independent quantity in each integrator on a sequential basis and varying the other quan- 25 tities in the integrator every time that the independent quantity is presented for variation. In this way, the analyzer obtains the advantages of digital computers in producing quick and accurate solutions of mathematical problems and the advantages of differential analyzers in 30 its simplicity and compactness.

Each integrator operates to obtain the differential combination of the value of a dependent quantity for the integrator and each digital variation in the independent quantity for the integrator. However, errors result in obtain- 35 ing the differential combination for each integrator. The errors result from the fact that only an approximation is made in the value of the dependent quantity for each integrator every time that the dependent quantity is differentially combined with a variation in the value of the in- 40 dependent quantity. The errors can often be considerably reduced by limiting the value of each digital variation in the value of the independent quantity. Even when the variations in the independent quantity are held to a relatively low value, substantial errors sometimes result in 45 the solution of a problem. Furthermore, the time required to solve the problem sometimes becomes relatively long. Until now, attempts to minimize such errors without reducing the value of each variation in the independent quantity have not been entirely successful.

This invention provides a digital differential analyzer which minimizes any error in the differential combination for each integrator by accurately approximating the value of the dependent quantity for the integrator every time that a variation in the independent quantity occurs. The 55 analyzer provides circuits for correcting the value of the dependent quantity for each integrator in a manner dependent upon the operation of the integrator and the connections to the integrator from other integrators in the analyzer. In this way, accurate solutions can be obtained in a relatively short space of time for a wide variety of mathematical problems.

An object of this invention is to provide a system for operating in conjunction with a digital differential analyzer to minimize the errors produced by the analyzer in solving a problem.

Another object is to provide apparatus of the above character which can be easily incorporated in a digital differential analyzer to enhance the accuracies in the solutions obtained by the analyzer.

A further object is to provide apparatus of the above

character which obtains a relatively accurate approximation in the value of a dependent quantity for an integrator over the range represented by an increment in the value of an independent quantity for the integrator.

Still another object is to provide apparatus of the above character for controlling the approximation made in the value of a dependent quantity for an integrator in accordance with the function of the integrator and with the connections made to the integrator from other integrators.

A still further object is to provide apparatus of the above character which requires a minimum number of components so that only a relatively small increase is required in the size of the analyzer to obtain the benefits

Other objects and advantages will be apparent from a detailed description of the invention and from the appended drawings and claims.

In the drawings:

FIGURE 1 is a simplified block diagram schematically machine in interconnecting a plurality of integrators to 20 illustrating a digital differential analyzer which includes features forming one embodiment of this invention;

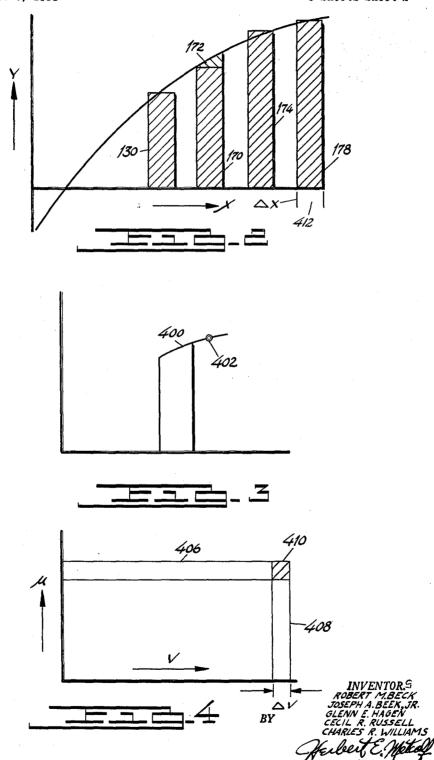

FIGURES 2, 3 and 4 are curves which illustrate the corrections made to different integrators in accordance with the functions of the integrators and the connections from other integrators;

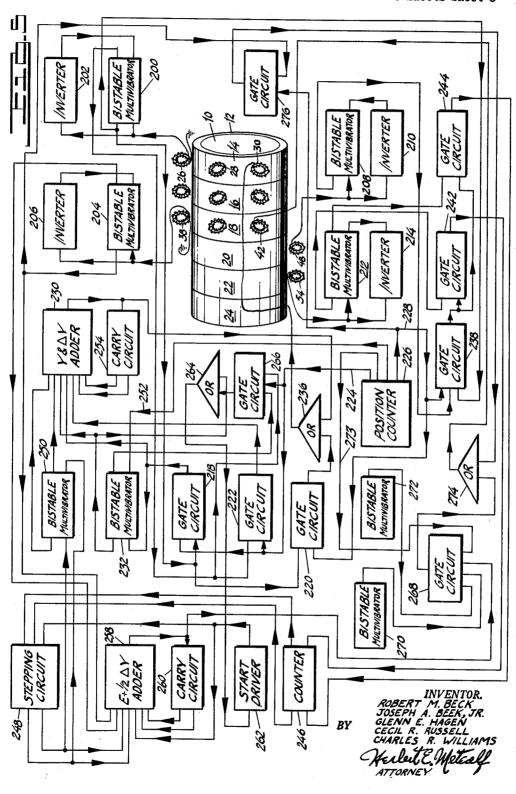

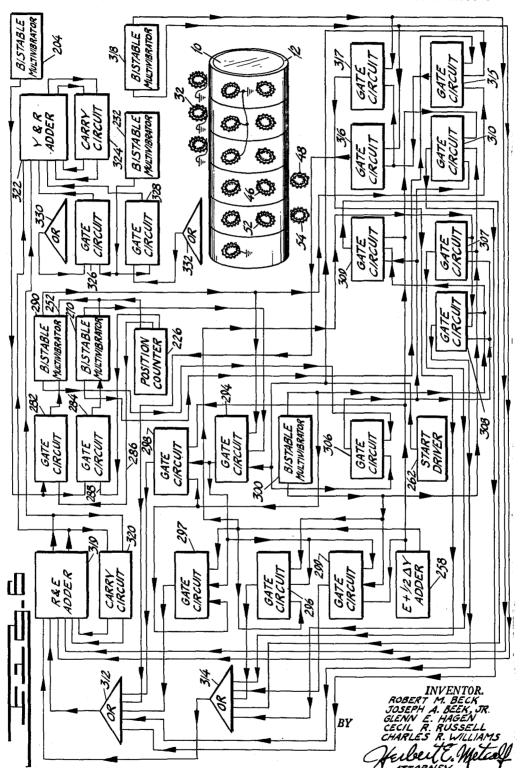

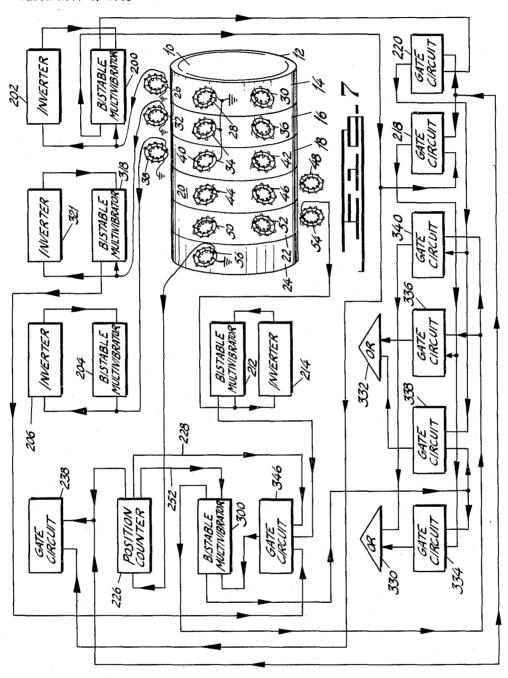

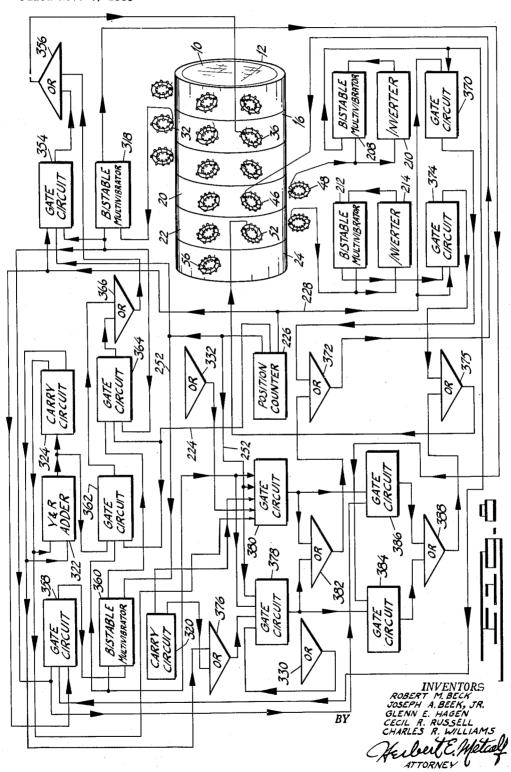

FIGURES 5, 6, 7 and 8 are schematic diagrams, partly in block form and partly in perspective, illustrating in some detail a digital differential analyzer and the components which operate in conjunction with the analyzer to form one embodiment of the invention;

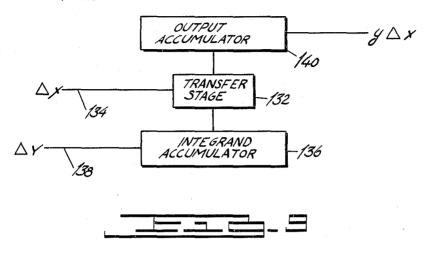

FIGURE 9 is a block diagram illustrating the operation of one of the integrators forming part of the digital differential analyzer shown in FIGURES 5 to 8, inclusive;

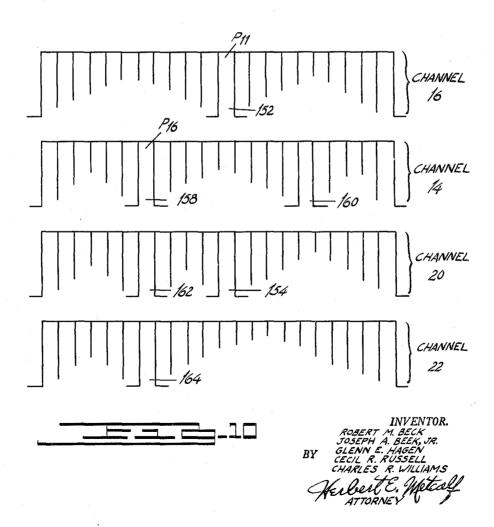

FIGURE 10 is a chart which illustrates how different parts of an integrator such as that shown in FIGURE 9 are coded to control the operation of the integrator;

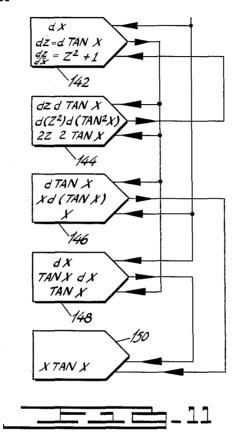

FIGURE 11 is a schematic diagram illustrating the relationship between different integrators forming the digital differential analyzer shown in FIGURES 5 to 8, inclusive when the analyzer is solving a particular problem;

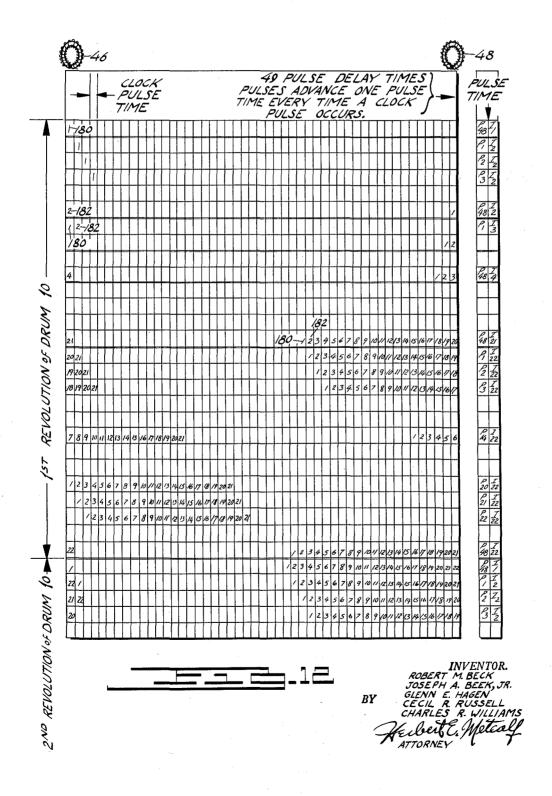

FIGURE 12 is a chart illustrating the operation of certain of the components forming a part of the analyzer shown in FIGURE 1; and

FIGURE 13 is a chart which illustrates the operation of certain of the components shown in FIGURE 6.

A simplified block diagram is shown in FIGURE 1 of an analyzer for solving differential problems by digital steps. The analyzer includes a drum 10 (schematically shown in FIGURES 5 to 8, inclusive) adapted to be rotated by a suitable motor (not shown). A thin coating 12 of magnetic material is applied to the periphery of the drum. The coating 12 can be considered as being divided into a plurality of annular channels 14, 16, 18, 20, 22 These channels are shown schematically in FIGURE 1 in separated relationship for purposes of convenience. Each of the channels is separated by a sufficient distance from its adjacent channel so as to be substantially unaffected by the magnetic information provided in the adjacent channel.

The circumferential distance of each channel may be considered as being divided into a plurality of positions. Each of the positions is sufficiently separated from its adjacent positions to receive a different magnetization than that provided on the adjacent positions. For example, approximately 1160 equally spaced pulse positions may be provided in each channel when the drum has a radius of approximately four inches.

A plurality of toroidal coils are positioned adjacent to each of the channels 14, 16, 18, 20, 22 and 24. For example, coils 26, 28 and 30 are provided in contiguous relationship to the channel 14. These coils are shown schematically in FIGURE 1. Similarly, coils 32, 34 and

36; coils 38, 40 and 42; coils 44, 46 and 48; and coils 50, 52 and 54 are associated with the channels 16, 18, 20 and 22, respectively. A single coil 56 is disposed adjacent the channel 24.

3

The coils 26 and 30 are effectively separated from 5 each other by approximately 104 pulse positions and the coil 28 is disposed at an intermediate position between the coils 26 and 30. The coil 30 is adapted to provide signals in a pattern dependent on the operation of the digital differential analyzer and to induce the correspond- 10 ing magnetic pattern on the drum 10, as the drum rotates. The pattern induced on the drum 10 by the coil 30 is of the binary form in which a magnetization in one circumferential direction indicates one value and a magnetization in the other direction indicates a second value. 15

The coil 26 is adapted to pick up the changes in the direction of magnetization in the channel 14 as the drum rotates. The coil 28 is adapted to produce a substantially constant signal for returning the direction of magnetization on the drum to that representing a value of "0" after the magnetic pattern on the drum has been converted into a corresponding electrical pattern by the coil 26.

The coils 32, 34, and 36 are separated from one another by distances corresponding to the distances between the coils 26, 28 and 30 and are adapted to perform 25 functions similar to those performed by the coils 26, 28 and 30, respectively. The coils 38, 40 and 42 are also separated in the channel 18 in a similar manner to the coils in the channel 14 and are adapted to perform functions corresponding to those performed by the coils 26, 30 28 and 30, respectively.

The coils 46 and 52 are adapted to operate in a manner similar to the coil 30 to provide a magnetic pattern in the channels 20 and 22, respectively, in a pattern dependent upon the problem to be solved. The coils 46 and 52 are effectively separated from the coils 48 and 54, respectively, by approximately 49 pulse positions during the operation of the analyzer to obtain the solution of a mathematical problem.

The coils 48 and 54 are adapted to produce signals in accordance with the magnetic pattern provided in their respective channels by the coils 46 and 52. The coils 44 and 50 are adapted to operate in a manner similar to the coil 28 to produce "zero" direction of magnetization in the channels 20 and 22, respectively after the patterns provided by the coils 46 and 52 have been utilized by the coils 48 and 54, respectively.

The coil 56 is adapted to produce a cycle of a signal approximating a sine wave as each pulse position in the channel 24 moves past the coil. The coil 56 produces 50 sinusoidal signals because of the magnetic pattern permanently provided in the channel 24. This pattern remains constant regardless of the problem to be solved.

A counter 60 is connected to the coil 56 to count the cycles of the sine waves in the channel 24 as the drum rotates. The counter 60 is formed from a plurality of multivibrators connected in cascade arrangement and is adapted to count successive sine signals in a numerical range from "1" to "48." Upon each count of "48," the counter 60 is adapted to return to its initial state for the commencement of a new count. As will be disclosed in detail hereinafter, a new integrator is presented for computation upon the completion of each count of "48."

Similarly, a counter 62 is formed from a plurality of multivibrators in cascade arrangement. The counter 62 is connected to the counter 60 to count the number of times that a full count is obtained in the counter 60. For example, the counter 62 may count up to 22 full counts in the counter 60 before returning to its initial state for the initiation of a new count. In this way, the counters 70 60 and 62 divide the drum 10 into 22 integrator storage sections each having 48 pulse positions and each providing the necessary storage for an integrator, which is described hereinafter with reference to FIGURE 9.

signals induced in the coil 26 are introduced to a gate circuit 64, the operation of which is controlled by a line extending from the counter 60 (not shown for purposes of simplification). A connection is also made from the counter 60 to an input terminal in a bistable multivibrator 66. The output from the circuit 64 is introduced through an "or" network 68 to the coil 30. The output from the coil 26 is also introduced to a gate circuit 69, the operation of which is controlled by an output voltage from a second lead in the multivibrator 66. The output from the gate circuit 69 is applied to an adder 70.

4

In addition to being introduced to the gate circuits 64 and 69, the output from the coil 26 is introduced to a gate circuit 72. Other input terminals of the gate circuit 72 have signals applied to them from the coils 48 and 54. The output from the gate circuit 72 is applied to a counting and stepping circuit 74 which in turn has its output introduced to the adder 70. The output signals from the adder 70 are applied through the "or" network 68 to the coil 30. The output from the adder 70 is also introduced to an input terminal of an adder 80.

A driver circuit 86 is operatively controlled by the signals from the two output terminals of the multivibrator 66. The output from the driver 86 is applied to gate circuits 88 and 90 to control the operation of these circuits. When the gate circuit 88 is opened by signals from the driver 36, signals from the coil 38 pass through the gate circuit to an adder 92 for combination with the signals from the counter and stepper 74.

The output from the adder 92 is introduced to an input terminal of a gate circuit 93. Another input terminal of the gate circuit 93 is connected through an inverter 94 to a gate circuit 95 having input terminals connected to the coils 32 and 48. The output from the gate circuit 93 is applied through an "or" network 96 to the coil 42. The "or" network 96 also passes to the coil 42 signals which pass through a gate circuit 97 from the coil 38.

When the gate circuit 90 opens upon the introduction of a signal from the driver 86, signals pass through the gate circuit from the coil 32. These signals are introduced to an adder 100 for combination with the output signals from the adder 92. The output signals from the adder 100 are in turn introduced to the adder 80 for combination with the numerical information passing through the adder 70. The operation of the adder 80 is controlled by the output signals from the gate circuit 95.

The output signals from the adder 80 are introduced to gate circuits 104, 106, and 108. The gate circuits 104, 106, and 108 are respectively connected to "or" networks 110, 112, and 114 for introduction to the coils 36, 46, and 52 of the signals passing through the networks. The "or" networks 110, 112, and 114 also pass to the coils 36, 46, and 52, respectively, signals passing through gate circuits 116, 118, and 120 from the coils 32, 48. and 54, respectively.

The digital differential analyzer disclosed above is adapted to provide the solution of differential equations. For example, it may provide the solution of the problem of evaluating the integral of a general equation v=f(x)so as to obtain a function  $\int y dx = \int f(x) dx$ , where f(x)represents a function of x and  $\int f(x) dx$  represents the integral of the function. If a curve y=f(x) is plotted with x as the abscissa and y as the ordinate, the analyzer obtains the relationship  $\int y dx = \int f(x) dx$  by computing the area under the curve y=f(x). By determining the area under the curve y=f(x), the analyzer performs electronically operations that may sometimes be performed mentally by a skilled mathematician when the problem to be solved is relatively simple.

The analyzer obtains the value of the function  $\int y dx = \int f(x) dx$  by producing small increments of x. These increments may be represented by the symbol  $\Delta x$ . For each  $\Delta x$  increment, the analyzer determines the value As schematically shown in FIGURE 1, the output 75 of y and obtains the product  $y\Delta x$ . This product  $y\Delta x$

approximates the area under the curve y=f(x) for each  $\Delta x$  increment, as indicated in FIGURE 2 by the shaded area 130 for a particular  $\Delta x$  increment. If the product  $y\Delta x$  is obtained for successive  $\Delta x$  increments and if all of the  $y\Delta x$  increments are added together, the area under the interval of the curve representing f(x) from  $x_0$  to x may be approximated. A relatively accurate approximation may be obtained by decreasing the value of each  $\Delta x$  increment.

An integrator for determining the  $y\Delta x$  increments and 10 for storing the cumulative values of these increments is shown in FIGURE 9. The integrator includes a transfer stage 132 for obtaining  $\Delta x$  increments at periodic intervals through a line 134. The integrator also has an integrand accumulator 136 for storing the value of the dependent quantity y and for receiving  $\Delta y$  increments through a line 138 from its own and from other integrators so as to vary the value of y in accordance with the function y=f(x). An output accumulator 140 is provided to receive  $y\Delta x$  increments, to combine each  $y\Delta x$ increment with the previous increments and to deliver the cumulative value obtained to another integral accumulator or transfer stage while holding the remainder in store. A detailed explanation of this will be given hereafter.

The interrelationship between different integrators is illustrated in FIGURE 11 for a particular problem. This problem starts with a differential equation represented by

$$\frac{d^2y}{dx^2} = y^2 + 1$$

As is methematically known, the differential solution of this problem indicates that  $y=\tan x$ . The integrators involved in the solution of this problem are indicated in FIGURE 11 by blocks 142 and 144. Integrators represented by blocks 146, 148 and 150 then utilize the function  $y=\tan x$  to generate an output function  $y=x\tan x$ . This output function is indicated in the block 150.

In each integrator, the introduction of the  $\Delta x$  increments constituting changes in the independent variable quantity for the integrator is indicated by a line extending into the upper right portion in the block. The  $\Delta y$  increments are introduced into the integrator through a line or a plurality of lines extending into the lower right portion of the block representing the integrator. The output of the integrator is obtained from a line extending from an intermediate position at the right side of the appropriate block.

As will be seen in FIGURE 11,  $\Delta x$  increments of the independent variable for a particular integrator may be obtained from the output of another integrator. For example, in FIGURE 11, the  $\Delta x$  increments for the integrators 144 and 146 are obtained from the output of the integrator 142. Similarly,  $\Delta y$  increments for a particular integrator may be obtained from the output of other integrators as well as from the output of the integrator itself. For example,  $\Delta y$  increments for the integrators 144 and 148 are obtained from the output of the integrators 142.

The  $\Delta x$  and  $\Delta y$  increments for each integrator are actually determined from a coded pattern provided in the channels 16 and 14, respectively. As previously disclosed, the pulse positions in each channel are subdivided into 22 integrator storage sections each having 48 pulse positions. The first 22 positions in each integrator storage section in the channel 16 are coded to indicate a  $\Delta x$  increment. Since the first 22 positions in the channel 16 for each integrator correspond in number to the 22 integrators in the analyzer, each integrator can receive a  $\Delta x$  increment from the output of any of the other integrators. This can be effectuated by providing a pulse in the channel 16 in a particular one of the first 22 positions for the integrator.

For example, the  $\Delta x$  increments for the integrator 144 in FIGURE 11 would be coded in a particular one of the

6

22 positions in the channel 16. As will be disclosed in detail hereinafter, the particular position corresponds to the time at which the output from the integrator 142 appears on the coils 48 and 54. In FIGURE 10, a pulse 152 is shown as being recorded in the channel 16 in the 11th pulse position for a particular integrator.

A pulse in the channel 16 in one of the first 22 positions for a particular integrator indicates that a  $\Delta x$  increment may be made for the integrator. However, such a pulse does not indicate whether an increment will actually be made and, if so, whether the polarity of such increment will be positive or negative. The actual occurrence of a  $\Delta x$  increment for the integrator is indicated by the presence or absence of a coincidental pulse in the channel 20. If a positive pulse is picked up from the channel 20 by the coil 48 at the same time as the pulse representing a possible  $\Delta x$  increment for a particular integrator is picked up by the coil 32, a  $\Delta x$  increment for the integrator actually occurs. For example, the pulse 152 in FIGURE 10 indicates an actual  $\Delta x$  increment for a particular integrator since it coincides in time with a pulse 154 in the channel 20. A  $\Delta x$  increment is not obtained for the integrator if a pulse does not appear in the channel 20 at the same time as the pulse in the channel

The polarity of each  $\Delta x$  increment is determined by the presence or absence of a coincidental pulse in the channel 22. If a pulse is picked up from the channel 22 by the coil 54 at the same time that pulses indicating an actual  $\Delta x$  increment for a particular integrator are picked up by the coils 32 and 48, the  $\Delta x$  increment for the integrator is positive. The  $\Delta x$  increment is negative if a pulse does not appear in the channel 22 at the same time as the pulses in the channels 16 and 20. For example, 35 the pulse 152 in FIGURE 10 indicates a negative  $\Delta x$  increment since a pulse does not appear in the channel 22 simultaneously with the occurrence of the pulses 152 and 154 in the channels 16 and 20, respectively.

The first 22 positions in the channel 14 for each integrator are coded to indicate  $\Delta y$  increments in a manner similar to the coding of corresponding positions in the channel 16 to indicate  $\Delta x$  increments. Since the first 22 positions in each integrator correspond to the 22 integrators in the digital differential analyzer, each integrator is coded in particular ones of the first 22 positions in the channel 14 so as to receive the outputs from certain other integrators in accordance with the problem to be solved. For example, a pulse would be coded in the channel 14 in a particular one of the first 22 positions for the integrator 148 in FIGURE 11 so as to coincide with the time at which the output from the integrator 142 is made available to the coils 48 and 54 in the channels 20 and 22, respectively. Although only one  $\Delta x$  increment can be obtained for an integrator upon each revolution of the drum, several  $\Delta y$  increments can be obtained. This may be seen by the pulses 158 and 160 in the channel 14 in FIGURE 10.

Each pulse in the first 22 positions in the channel 14 for each integrator represents the possibility of a  $\Delta y$  increment but does not indicate the actual occurrence of such an increment or the polarity of the increment. The actual occurrence of the increment is indicated by the presence or absence of a pulse in the channel 20 at the same time that the pulse in the channel 14 is made available to the coil 26. For example, the pulse 158 in FIGURE 10 indicates an actual  $\Delta y$  increment for a particular integrator since it coincides in time with a pulse 162 in the channel 20. However, no  $\Delta y$  increment is obtained when the pulse 160 is picked up by the coil 26 since there is no coincidental pulse in the channel 20.

The sign of each actual  $\Delta y$  increment is indicated by the presence or absence of a pulse in the channel 22 at the time that pulses in the channels 14 and 20 are simultaneously made available to the coils 26 and 48. For example, the pulse 158 in FIGURE 10 indicates a posi-

tive  $\Delta y$  increment for a particular integrator since a pulse 164 appears in the channel 22 at the time that the pulses 158 and 162 are picked up by the coils 26 and 48, respectively.

Since the interrelationship between the different integrators remains constant during the solution of a particular problem, the coding pulses in the channels 14 and 16 for the first 22 positions of each integrator must be retained during the computation. Retention of the pulses in the channel 14 is effectuated by the gate circuit 64, 10 which opens during the first 22 pulse positions in each integrator to pass the coded information in these positions. The gate circuit 64 opens during these pulse positions because of the introduction of a relatively high voltage from the counter 60 through a suitable connection 15 (not shown for purposes of simplification). The signals then pass through the "or" network 68 for recordation in the channel 14 by the coil 30. Similarly, the gate circuit 116 opens during the first 22 positions for each integrator so that the coding information can pass through 20 the "or" network 110 for recordation by the coil 36 in the channel 16.

It should be appreciated that the gate circuits similar to the circuit 64 operate to pass information only when positive voltages are simultaneously introduced to all of 25 the input terminals of the circuit. In computer terminology, such circuits have been designated as "and" networks. The term "or" network is also common in computer terminology. Such circuits operate to pass information when any one of the input terminals receives a 30 relatively high voltage.

During the first 22 positions of each integrator, the gate circuit 72 operates to determine the occurrence of  $\Delta y$  increments for the integrator and the polarity of each minations by comparing the pulses from the coil 26 with the pulses from the coils 48 and 54. Each pulse induced in the coil 26 in the first 22 positions for an integrator indicates that a  $\Delta y$  increment can be obtained. As previously disclosed, the particular position in which a pulse occurs determines for an integrator which of the other integrators in the analyzer provides  $\Delta y$  increments for the integrator. The simultaneous production of a pulse by the coil 48 indicates that a  $\Delta y$  increment has actually occurred. When the coil 54 also produces a simultaneous pulse, the gate circuit 72 indicates that the  $\Delta y$  increment has a positive polarity.

At the same time that the gate circuit 72 operates to determine the occurrence of  $\Delta y$  increments for an integrator and the polarity of each such increment, the circuit 74 50 arithmetically combines each such  $\Delta y$  increment. For example, a signal passing to the circuit 74 from the gate circuit 72 may cause the circuit 74 to provide a numerical indication of +4 when an indication of +3 was previously provided by the circuit. Similarly, the indications 55 in the circuit 74 may change from a value of -3 to a value of -4 upon the introduction of a negative signal from the gate circuit 72.

The circuit 74 retains in binary form the numerical information relating to the cumulative value of the  $\Delta y$ increments for an integrator. The circuit 74 retains the information in binary form since it comprises a plurality of multivibrators arranged in cascade relationship. For example, with a resultant count of +5 for the  $\Delta y$  increments for a particular integrator, the first and third multivibrators in the cascade arrangement may be operated to indicate a binary pattern of 101, where the least significant digit is at the right. In binary form, a pattern of 101 indicates that  $(1)(2^2)+(0)(2^1)+(1)(2^0)=5$ . Similarly, a value of +3 is indicated by a pattern of 011, 70 where the least significant digit is at the right.

The output from the circuit 74 is introduced to the adder 70 for combination with the numerical information in the channel 14. The numerical information in the

integrator. This information is arithmetically combined on a sequential basis for each pulse information with the cumulative value of the Ay increments. The arithmetical combination of the information in the channel 14 and the circuit 74 occurs for each integrator every time that The comthe integrator is presented for computation. putation occurs only after the gate circuit 69 has been opened by a relatively high voltage from the multivibrator 66 so that the signals produced by the coil 26 can pass to the adder 70.

The information obtained for each pulse position by the adder 70 represents the new value of the dependent quantity y for each integrator. This information passes through the "or" network 68 for recordation by the coil 30 in the channel 14. The new information for each computation is thereafter combined with new increments of  $\Delta y$  when the integrator is again presented for computation. In this way, the value of y is subject to continuous variation.

As previously disclosed, the value of the dependent quantity y for an integrator is differentially combined with increments in the independent quantity x for the integrator when the integrator is presented for computation. In co-pending application Serial No. 217,478, filed March 26, 1951 by Steele and Collison, a differential combination is obtained similar to that shown in shaded lines at 170 in FIGURE 2. The differential combination is obtained by combining an increment in the independent quantity x with the value of y at the beginning of the increment. Because of the use of the particular value of the dependent quantity y, an error is obtained in each differential combination. This error is shown at 172 in FIGURE 2.

The error in obtaining  $\int y dx = \int f(x) dx$  can be minisuch increment. The gate circuit 72 makes such deter- 35 mized by making each  $\Delta x$  increment relatively small. In many instances, it also becomes relatively small because of the tendency for different  $y\Delta x$  increments to compensate for one another. This may be seen from the fact that the  $y\Delta x$  increments are lower than their correct value while y is increasing, and they are above their true value while y is decreasing in value. Because of this, some compensation occurs for a curve y=f(x), where y increases and decreases for different intervals along the length of the curve.

Instead of using the value of the dependent quantity y at the beginning of each  $\Delta x$  increment, the value of y at the end of each  $\Delta x$  increment may be used. This system is utilized in the analyzer disclosed in co-pending application Serial No. 263,152, filed December 26, 1951, now Patent No. 2,850,232, by Glenn E. Hagen et al. The differential combination obtained by using such a value of y is indicated at 174 for a particular  $\Delta x$  increment. As may be seen, an error in the differential combination is also produced when the value of y at the end of each  $\Delta x$  increment is utilized. As disclosed above, any errors can be minimized by reducing the value of each  $\Delta x$  increment. Compensation can also be provided for errors in different  $y\Delta x$  increments when y is increasing at times and decreasing at other times.

In this invention, a second order approximation is obtained for the value of the dependent quantity y over the portion of a curve y=f(x) represented by each  $\Delta x$ increment. The approximation is obtained by taking a value of y intermediate between the value of y at the beginning of each  $\Delta x$  increment and the value of y at the end of the increment. When such an approximation is made, a differential combination similar to that shown at 178 is obtained. This differential combination involves errors which are often considerably less than those produced by the differential combinations disclosed in previous applications.

The correction to the value of y for each differential combination is obtained for each integrator by dividing in two the cumulative value of the  $\Delta y$  increments for channel 14 occurs after the 22nd pulse position for each 75 the integrator every time that the integrator is presented

for computation. This is accomplished by making the indications in the circuit 74 available one pulse position earlier than they are made for utilization in the adder 70. For example, an indication that would be introduced from the circuit 74 to the adder 70 in pulse position 25 of an integrator is applied to the adder 92 in pulse position 24 for the integrator. This causes a binary indication of a value such as +6 to appear as an indication of +3 when it is advanced one position in the direction of decreasing significance.

Sometimes a  $\Delta x$  increment does not occur for an integrator when the integrator is presented for computation. When a  $\Delta x$  increment does not occur for the integrator, the corrective factor in the value of y is accumulated until the next  $\Delta x$  increment occurs for the integrator. In this way, the values of  $\frac{1}{2}\Delta y$  may be accumulated for an integrator over several computational cycles so that a value of  $\frac{1}{2}\Delta y$  is obtained. When a  $\Delta x$  increment actually occurs, the value of  $\frac{1}{2}\Delta y$  is subtracted from the value of y at the end of the increment to obtain an intermediate value of y over the range of the  $\Delta x$  increment. Upon the occurrence of a  $\Delta x$  increment, the cumulative value represented by  $\frac{1}{2}\Delta y$  is eliminated so that a new value can be obtained for correcting the value of y over the next  $\Delta x$  increment.

The channel 18 provides binary information for indicating the value of ½ ΣΔy for each integrator. Such information is provided after the 22nd pulse position for each integrator. The information is made available by the coil 38 to the gate circuit 88 which opens after the 30 22nd pulse position for each integrator to pass the information to the adder 92. The adder 92 also receives  $\frac{1}{2}$  of the cumulative value of the  $\Delta y$  increments for an integrator every time that the integrator is presented for computation. The adder then arithmetically combines 35 the information in the channel 18 and the information from the circuit 74 to obtain new indications representing ½ ΣΔy. The new indications obtained by the adder pass through the gate circuit 93 and the "or" network 96 for recordation by the coil 42 in the channel 18 when 40 a  $\Delta x$  increment has not actually occurred.

The occurrence of a  $\Delta x$  increment for each integrator is determined by the gate circuit 95, which compares the coding pulses from the coil 32 with the pulses from the coil 48. Upon the simultaneous occurrence of pulses from the coils 32 and 48 during one of the first 22 positions for an integrator, a  $\Delta x$  increment actually occurs. Such an increment is indicated by a pulse from the gate circuit 95. This pulse is introduced to the inverter 94, which inverts the amplitude of the pulse from a high value to a low value. The inverted pulse is then introduced to the gate circuit 93 to prevent the gate circuit from operating. When a  $\Delta x$  increment does not occur, however, so that a pulse is not produced by the gate circuit 95, a relatively low voltage is produced by the gate circuit. This voltage is inverted by the inverter 94 and is introduced to the gate circuit 93 to open the gate circuit. This causes the information from the adder 92 to pass through the gate circuit 93 and the "or" network 96 to the coil 42.

The indications obtained by the adder 92 are also introduced to the adder 100 for combination with the signals provided by the coil 32. As previously disclosed, the indications provided by the coil 32 after the 22nd pulse position for each integrator represent the cumulative value of the  $y\Delta x$  increment for the integrator. Only the indications after the 22nd pulse position for each integrator pass to the adder 100 because of the operation of the gate circuit 90. The numerical information from the coil 32 and the adder 92 are arithmetically 70 combined by the adder 100 to obtain numerical information designated for future reference as  $R_{\rm s}$ .

As previously disclosed, the value of  $\frac{1}{2}\Sigma\Delta y$  is obtained for certain integrators to provide a corrective factor in the value of y for the integrators. The value of  $\frac{1}{2}\Sigma\Delta y$  75

10

for each integrator may of course be directly combined with the dependent quantity y for the integrator to obtain the proper correction in the value of y over the range of values occurring in each  $\Delta x$  increment. It may 5 also be combined with the cumulative value of the  $y\Delta x$  increments for the integrator, since the cumulative value of the  $y\Delta x$  increments is thereafter combined with the value of y for the integrator. It is the adder 100 which arithmetically combines the value of y for 10 each integrator to obtain the value of y.

The adder 80 in turn operates to combine the value of  $R_s$  for each integrator with the value of the dependent quantity y provided by the adder 70 for the integrator. The information obtained by the adder 80 represents the new cumulative value of the  $y\Delta x$  increments for each integrator. It is obtained only when a  $\Delta x$  increment has actually occurred for an integrator since the operation of the adder 80 is controlled by the introduction of a signal from the gate circuit 95.

The information provided by the adder 80 passes through the gate circuit 104, which opens after the 22nd pulse position for each integrator. The information then passes through the "or" network 110 for recordation by the coil 36 in the channel 16. When the integrator is again presented for computation, the information recorded by the coil 36 appears adjacent the coil 32 to produce a corresponding pattern in the coil. In this way, the information is made available to the adders 100 and 80 to obtain a new value of the cumulative  $y\Delta x$  increments for the integrator.

Since the cumulative value of  $y\Delta x$  increments for each integrator can be stored in only the pulse positions after the 22nd pulse position for the integrator in the channel 16, these indications occasionally overflow. When an overflow occurs for an integrator, the indications for the integrator in the channel 16 represent an intermediate value so that they can build up again to a relatively high value. At the same time, an overflow pulse is produced by the adder 80 in the last pulse position for the integrator. This pulse passes through the gate circuit 106, which opens at the last pulse position for each integrator. The pulse then passes through the "or" network 112 for recordation by the coil 46 in the channel 20.

For example, a first pulse of relatively high voltage may be provided in the channel 20 at the 48th position of integrator "1." This pulse indicates that an overflow has occurred in the cumulative  $y\Delta x$  value stored in the channel 16 for the integrator but the pulse does not indicate whether the overflow is positive or negative. The pulse is indicated at 180 in the chart shown at FIGURE 12.

In all of the vertical columns in the chart shown in FIGURE 12, except for the two at the extreme right, numbers between "1" and "22" are shown corresponding to the 22 integrators in the digital differential analyzer. In the two columns at the extreme right, numbers are shown prefaced by the letters "1" and "P." The letter "1" followed by a number indicates the particular integrator that is moving past the coil 46 at any instant. For example, "I<sub>3</sub>" indicates that a pulse position in the third integrator is moving past the coil 46 in the channel 20. Similarly, a designation such as P<sub>13</sub> indicates that the 13th pulse position in the particular integrator is moving past the coil 46.

After the pulse 180 is recorded by the coil 46 in the channel 20, it advances from the coil 46 towards the coil 48. During this time, the first 47 positions of integrator "2" are passing under the coil 46. At the P<sub>48</sub>I<sub>2</sub> position—or, in other words, the last position of integrator "2"—an indication is recorded by the coil 46 in the channel 20, as indicated at 182 in FIGURE 12. At the P<sub>1</sub>I<sub>3</sub> position, the indication 180 passes through the gate circuit 118 and the "or" network 112 to the coil 46. The pulse passes through the gate circuit 118 since the gate circuit opens in the first 47 pulse positions of each integrator.

After passing through the gate circuit 118 in the "or" network 112, the pulse 180 is again recorded by the coil 46 in the channel 20, this time at the pulse position adjacent to the indication 182.

Similarly, indications are provided in adjacent pulse 5 positions to show whether or not an overflow has occurred in the cumulative  $y\Delta x$  value for each of the other integrators in the analyzer. These indications are recirculated by the gate circuit 118, which remains open during the first 47 pulse positions of each integrator. At the 10 48th position for each integrator, the gate circuit 118 closes and prevents any recirculation of old information for the integrator.

At the same time that the gate circuit 118 closes, the gate circuit 106 opens. When the gate circuit 106 opens, 15 the overflow information for the integrator moving past the coil 46 is recorded in the channel 20. In this way, old overflow information for an integrator is replaced by new overflow information for the integrator every time that the integrator is presented for computation.

After the indications have been provided in the channel 20 for the 48th pulse position of each integrator, integrator "1" is presented for computation a second time. As the drum rotates through the first 22 positions for the integrator, the output indications for the 22 integrators 25 move in sequence past the coil 48. This causes the output indications in the channel 20 to become available for determining whether or not a  $\Delta x$  increment and  $\Delta y$  increments are actually obtained for the integrator during the second computation. The determination of the oc- 30 currence of an actual  $\Delta x$  increment and of actual  $\Delta y$  increments is made by respectively comparing the coding pulses in the channels 14 and 16 with the coding pulses in the channel 20. The operation of the digital differential analyzer to obtain such a determination has been 35 disclosed previously.

In like manner, overflow indications are recorded in the channel 22 to indicate the polarity of each  $\Delta x$  increment and each  $\Delta y$  increment. The overflow indications are positive when pulses are actually recorded in the 40 channel 22 and are negative when pulses are not recorded in the channel 22. As each integrator is presented for computation, the overflow indications in the channel 22 are made available to the integrator in a manner similar to the pulses in the channel 20.

The system disclosed above is shown in some detail in FIGURES 5 to 8, inclusive. The system includes the channels 14, 16, 18, 20, 22 and 24 and the coils respectively associated with the different channels. For example, the coils 26, 28 and 30 are associated with the chan- 50 nel 14. The coil 26 is connected to the grid of the left tube in a bistable multivibrator 200 (FIGURE 5) and to the input terminal of an inverter 202, the output from which is introduced to the grid of the right tube in the multivibrator 200. A multivibrator 204 and an inverter 55 206; a multivibrator 208 and an inverter 210; and a multivibrator 212 and an inverter 214 are respectively associated with the coils 38, 48 and 54 in a manner similar to that in which the multivibrator 200 and the inverter 202 are associated with the coil 26.

Connections are made from the plate of the left tube in the multivibrator 200 to input terminals of gate circuits 218 (FIGURE 5) and 220 and from the plate of the right tube in the multivibrator 200 to an input terminal of a gate circuit 222. The gate circuits 218 and 222 have 65 other input terminals connected through a line 224 to a counter 226, corresponding to the counter 60 shown in FIGURE 1. Voltage is also introduced from the counter 226 through a line 228 to an input terminal of the gate circuit 220.

Signals passing through the gate circuits 218 and 222 are introduced to an adder 230 corresponding to the adder 70 in FIGURE 1. The signals from the gate circuit 218 are also introduced to the grid of the left tube in a bistable multivibrator 232 corresponding to the mul- 75 from a gate circuit 276. Input terminals of the gate

tivibrator 66 shown in FIGURE 1. A connection is made from the output terminal of the gate circuit 220 to the input terminal of an "or" network 236 having its output terminal connected to the coil 30.

12

In addition to being connected to the gate circuits 218 and 220, the plate of the left tube in the multivibrator 200 is connected to an input terminal of a gate circuit 238. Other input terminals of the gate circuit 238 are connected to the plate of the left tube in the multivibrator 208 and through the line 228 to the counter 226. The output from the gate circuit 238 is introduced to input terminals of gate circuits 242 and 244, other input terminals of which are respectively connected to the plates of the left and right tubes in the multivibrator 212.

The signals passing through the gate circuits 242 and 244 are introduced to a counter 246 having its output terminals connected to a stepping circuit 248. counter 246 and stepping circuit 248 operate in a manner similar to that disclosed above for the circuit 74 shown in FIGURE 1. The counter 246 and stepping circuit 248 can be considered as a single stage controlled by a plurality of logical networks. Actually, the counter 246 and stepping circuit 248 are shown as a single unit in FIGURE 29 and described on pages 90 to 97, inclusive, of the specification as a single unit in co-pending application Serial No. 217,478. Output terminals of the stepping circuit 248 are connected to the grids of the left and right tubes in a multivibrator 250, the plates of the left and right tubes in the multivibrator 250 being connected to input terminals of the adder 230.

The operation of the adder 230 is controlled by a signal from the plate of the left tube in the multivibrator 232. As will be disclosed in detail hereinafter the operation of the adder 230 is terminated at the last pulse position of each integrator because of a connection from the counter 226 through a line 252 to the grid of the right tube in the multivibrator 232. The output signals produced by the ladder 230 are introduced to a carry circuit 254 having its output terminals connected to input terminals of the adder 230. The output from the adder 230 is also introduced through the "or" network 236 to the coil 30 for recordation by the coil in the channel 14.

The output terminals from the stepping circuit 248 are not only connected to the multivibrator 250 but also to input terminals of an adder 258 corresponding to the adder 92 in FIGURE 1. Connections are made to other input terminals of the adder 258 from the plates of the left and right tubes in the multivibrator 204 and from a carry circuit 260 which receives its information from the adder 258.

The operation of the stepping circuit 248 and the adder 258 is controlled by signals from a driver circuit 262 having its input terminal connected to the output terminal of an "or" network 264. The driver 262 is adapted to produce signals of the same polarity as the polarity of the signals introduced to it from the "or" network 264. This may be accomplished by a cascade arrangement of two stages each of which inverts the output from the previous stage. The "or" network 264 in turn receives signals from the plate of the left tube in the multivibrator 232 and from a gate circuit 266. Connections are made to input terminals of the gate circuit 266 from the plate of the right tube in the multivibrator 232, from the plate of the left tube in the multivibrator 200 and through the line 224 from the counter 226.

The output from the adder 258 is introduced to a gate circuit 268 having other input terminals connected to the plates of the right tubes in multivibrators 270 and 360 and through a line 273 to the counter 226. The signals passing through the gate circuit 268 are applied through an "or" network 274 to the coil 42 for recordation by the coil in the channel 18. The coil 42 also receives signals passing through the "or" network 274

circuit 276 are connected to the plate of the left tube in the multivibrator 204 and through the line 228 to the counter 226.

In addition to being connected to the gate circuit 276, the plate of the left tube in the multivibrator 204 is connected to gate circuits 282 and 284 (FIGURE 6). Other input terminals of the gate circuits 282 and 284 receive voltages through lines 286 and 288, respectively, from the counter 226. The output terminals from the gate circuits 282 and 284 are respectively con- 10 nected to the grids of the left tubes in a multivibrator 290 and the multivibrator 270. The grids of the right tubes in the multivibrators 270 and 290 are connected through the line 252 to the counter 226.

The plates of the right tubes in the multivibrators 270 15 and 290 are connected to input terminals of a gate circuit 294 having another input terminal connected to the driver circuit 262. The output from the gate circuit 294 is in turn applied to gate circuits 296, 297, 298 and terminals of the adder 258. The gate circuits 296 and 299 also have input terminals connected to the plate of the left tube in a bistable multivibrator 300, and the gate circuits 297 and 298 have input terminals connected The multivibrator 300 will be disclosed in detail hereinafter.

The plate of the left tube in the multivibrator 290 is connected to an input terminal of a gate circuit 306 (FIGURE 6) another input terminal of which is connected to the driver 262. The output from the gate circuit 306 is applied to gate circuits 307, 308, 309 and 310 having other input terminals connected to the output terminals of the adder 258. Signals are also applied to input terminals of the gate circuits 307 and 310 from the plate of the left tube in the bistable multivibrator 300 and to input terminals of the gate circuits 308 and 309 from the plate of the right tube in the multivibrator 300. Connections are respectively made from the gate circuits 308 and 310 to and "or" network 312 and from the gate circuits 307 and 309 to an "or" network 314. Other input terminals of the "or" networks 312 and 314 receive voltages from the gate circuits 297 and 298 and the gate circuits 296 and 299, respectively.

Voltages are applied to an adder 319 from the plates 45 of the left and right tubes in a multivibrator 318.

The adder 319 also receives voltages from a carry circuit 320, the operation of which is in turn controlled by the output from the adder 319. As shown in FIG-URE 7, the grid of the left tube in the multivibrator 318 50 is connected to the coil 32 in the channel 16, and the grid of the right multivibrator tube is connected to an inverter 321 having an input terminal connected to the coil 32.

The output from the adder 319 is introduced to an 55 adder 322, which also receives signals from a carry circuit 324 and from gate circuits 326 and 328. Each of the gate circuits 326 and 328 has an input terminal connected to the plate of the left tube in the multivibrator 232. Connections are also made to an input terminal of the gate circuits 326 and 328 from the output terminals of the "or" networks 330 and 332, respectively.

The "or" network 330 receives voltages from gate circuits 334 (FIGURE 7) and 340, and the "or" network 332 has voltages applied to it from gate circuits 336 and 338. Input terminals of the gate circuits 334 and 338 are connected to the plate of the left tube in the multivibrator 300 and input terminals of the gate circuits 336 and 340 are connected to the plate of the right tube in the multivibrator 300. Connections are made to other terminals of the gate circuits 334 and 336 from the gate circuit 218 (also shown in FIGURE 5) and to other input terminals of the gate circuits 338 and 340 from the gate circuit 220.

The grid of the right tube in the multivibrator 300 is 75 feeds  $\Delta x$  increments into the integrator undergoing com-

connected through the line 252 to the counter 226. The grid of the left tube in the multivibrator 300 receives its voltage from a gate circuit 346 having input terminals connected to the plates of the left tube in the multivibrators 212 and 318 and through the line 228 to the counter 226.

The plate of the left tube in the multivibrator 318 is also connected to a gate circuit 354 in FIGURE 8, the operation of which is controlled by voltages introduced to the gate circuit through the lines 228 and 252 from the counter 226. The output from the gate circuit 354 passes through an "or" network 356 for recordation by the coil 36 in the channel 16.

The voltage on the plate of the left tube in the multivibrator 318 is also introduced to an input terminal of a gate circuit 358 (FIGURE 8) having other input terminals connected to the plate of the left tube in the multivibrator 208 and through the line 228 to the counter 226. The signals passing through the gate circuit 358 299 having other input terminals connected to the output 20 are applied to the grid of the left tube in a bistable multivibrator 360, the grid of the right tube in the multivibrator 360 being connected through the line 252 to the counter 226.

The plate of the left tube in the multivibrator 360 is to the plate of the right tube in the multivibrator 300. 25 connected to an input terminal of a gate circuit 362, other input terminals of which receive voltages from the adder 322 and through the line 224 from the counter 226. The voltage on the plate of the right tube in the multivibrator 360 is applied to an input terminal of a gate circuit 364 having other input terminals connected to the plate of the left tube in the multivibrator 318 and through the line 224 to the counter 226. The signals from the gate circuits 362 and 364 pass through an "or" network 366 and through the "or" network 356 to the coil 36 for recordation by the coil in the channel 16.

The plate of the left tube in the multivibrator 208 is connected to a gate circuit 370, the operation of which is controlled by a voltage applied through the line 228 from the counter 226. The signals from the gate circuit 370 pass through an "or" network 372 to the coil 46 for recordation by the coil in the channel 20. Similarly, the plate of the left tube in the multivibrator 212 is connected to a gate circuit 374 having another input terminal connected through the line 228 to the counter 226. The signals from the gate circuit 374 pass through an "or" network 375 to the coil 52 for recordation in the channel 22.

The outputs from the carry circuits 320 and 324 are applied to input terminals of "or" networks 376, the output terminal of which is respectively connected to gate circuit 378. The gate circuit 378 also receives voltages from the "or" network 330 (also shown in FIGURE 7) from the plate of the left tube in the multivibrator 360 and through the line 252 from the counter 226. Connections are made to the gate 380 from the "or" network 332, the plate of the left tube in the multivibrator 360 and through the line 252 from the counter 226. The output signals from the gate circuits 378 and 380 pass through an "or" network 382 and the "or" network 372 to the coil 46 for recordation by the coil in the channel 20.

The output signals from the gate circuits 378 and 380 are also applied to gate circuits 384 and 386. Other input terminals of the gate circuits 384 and 386 are respectively connected to the plates of the right and left tubes in the multivibrator 318. The output signals from the gate circuits 384 and 386 pass through an "or" network 388 and the "or" network 375 to the coil 52 for recordation by the coil in the channel 22.

As previously disclosed, a pulse is provided in the channel 16 in one of the first 22 positions for each integrator to control the occurrence of  $\Delta x$  increment for the integrator every time that the integrator is presented for computation. The particular position in which the coding pulse is recorded for the integrator undergoing computation is dependent upon which of the other integrators

putation. Since the connections between integrators remains constant during the solution of a problem, the coding pulse in the channel 16 in one of the first 22 positions for each integrator remains constant during the solution of the problem. As a result, these pulses have 5 to be retained during the solution of a problem.

Retention of the pulses in the channel 16 is provided by the multivibrator 318, the gate circuit 354 and the "or" network 356 in FIGURE 8. The pulses in the channel 16 having a first polarity of magnetization are converted 10 by the coil 32 to pulses of relatively high voltage. These voltage pulses are then introduced to the grid of the left tube in the multivibrator 318 so as to cut off the tube. When the left tube in the multivibrator 318 becomes cut off, a high voltage is produced on the plate of the tube 15 and is introduced to the gate circuit 354.

The gate circuit 354 is opened by a signal from the counter 226 when the first pulse in each integrator is picked up by the coil 56. The gate circuit 354 remains open so that information in the channel 16 up to and including the 22nd pulse position for each integrator can pass through the gate circuit. During the time that the gate circuit 354 remains open, the positive pulses from the plate of the left tube in the multivibrator 318 pass through the gate circuit to the "or" network 356. The network 356 in turn passes to the coil 36 any positive pulses introduced to it. In this way, the coil 36 operates to produce a magnetic field in the channel 16 similar to the pattern of the electrical signals induced in the coil 32.

Similarly, the multivibrator 200, the gate circuit 220 30 and the "or" network 236 in FIGURE 5 operate to recirculate in the channel 14 the information provided in the first 22 positions of each integrator. As previously disclosed, pulses may be provided in the channel 14 in the first 22 positions for each integrator to indicate whether any variations in the value of the dependent quantity y will be made of the integrator.

The gate circuit 238 (FIGURE 5) operates to determine whether or not an actual  $\Delta y$  increment is made for an integrator at the time that a coding pulse appears in the channel 14 in one of the first 22 positions for the integrator. The gate circuit 238 receives the coding pulses in the channel 14 because of its connection to the plate of the left tube in the multivibrator 200. The connection from the counter 226 through the line 228 to the gate circuit 238 causes the gate circuit to become open during the first 22 positions of each integrator. The operation of the counter 226 to provide a relatively high voltage during the first 22 positions of each integrator is fully disclosed in co-pending application Serial No. 217,478, filed March 26, 1951, by Steele and Collision.

Since the gate circuit 238 is also connected to the plate of the left tube in the multivibrator 208, it can open for the passage of a signal only when high voltages are simultaneously produced on the plates of the left tubes in the multivibrators 200 and 203. A relatively high voltage is produced on the plate of the left tube in the multivibrator 208 only when a relatively high voltage is induced in the coil 48. As previously disclosed, the coil 48 indicates in adjacent pulse positions any overflow in the value of the cumulative  $y\Delta x$  increments which are obtained for each of the 22 integrators in the analyzer.

The passage of a pulse through the gate circuit 238 indicates only the occurrence of a  $\Delta y$  increment for an integrator, but it does not indicate whether such increment is positive or negative. The polarity of each pulse passing through the gate circuit 238 is indicated by the gate circuits 242 and 244, both of which receive the signals from the gate circuit 238. Since the gate circuit 242 is connected to the plate of the left tube in the multivibrator 212, it receives a relatively high voltage when a relatively high voltage is induced in the coil 54. As previously disclosed, a high voltage from the coil 54 indicates a positive increment. Since the gate circuit 242 passes a signal only when relatively high voltages are simultaneously as

introduced to it from the gate circuit 238 and from the plate of the left tube in the multivibrator 212, the gate circuit 242 passes a signal only when a  $\Delta y$  increment of positive polarity has occurred.

16

Each signal passing through the gate circuit 242 for an integrator causes the numerical indications provided by the counter 246 to increase by an integer in a positive direction. For example, a signal passing to the counter 246 from the gate circuit 242 may cause the counter to provide a numerical indication of +3 when an indication of +2 was provided by the counter. Similarly, the indications in the counter 246 may change from -3 to -2 upon the introduction of a signal from the gate circuit 242.

As previously disclosed, a positive increment in the cumulative  $y\Delta x$  value for an integrator is indicated by the simultaneous occurrence of pulses in the channels 20 and 22. Similarly, a negative increment in the cumulative  $y\Delta x$  value for the integrator is indicated by the absence of a pulse in the channel 22 at the time that a pulse is produced in the channel 20. Because of the absence of a pulse in the channel 22, a relatively low voltage is induced in the coil 54. This voltage is inverted by the inverter 214 and is introduced as a relatively high voltage to the grid of the right tube in the multivibrator 212. The trailing edge of this pulse causes the right tube in the multivibrator 212 to become cut off and a high voltage to be produced on the plate of the tube.

When a high voltage is produced on the plate of the right tube in the multivibrator 212 at the same time that a positive pulse passes through the gate circuit 238, the gate circuit 244 opens and passes a signal to the counter 246. This signal provides an indication of a negative  $\Delta y$ increment. Since the counter 246 is adapted to provide a negative count as well as a positive count of the Ay increments, it operates upon the introduction of signals from the gate circuit 244 to subtract an integer from the resultant value of the counter. For example, the indications in the counter 246 are changed from +4 to +3when a signal is introduced to the counter from the gate circuit 244. The operation of the counter 246 in providing a positive and negative count of digital increments is fully disclosed in co-pending application Serial No. 217.478.

The resultant value of  $\Delta y$  increments accumulated in the counter 246 for each integrator is made available on a step-by-step basis by the stepping circuit 248. For example, when the resultant value of the Ay increment for a particular integrator is +5, the circuit 248 indicates a value of +1 upon the rotation of the drum 10 past the pulse position which indicates the least significant digit of the number. This corresponds to the value of the least significant digit in the binary information of +5. As the drum rotates past the 2nd and 3rd pulse positions, the circuit 248 indicates the values of "0" and "1" respectively. Similarly, for a  $\Delta y$  increment of +3 for a particular integrator the circuit 248 indicates successive values of "1", "1" and "0" as the drum 10 rotates through successive pulse positions. The operation of a stepping circuit similar to the circuit 248 is fully disclosed in copending application, Serial No. 217,478.

The operation of the stepping circuit 248 is controlled by the driver circuit 262, which is in turn operated by signals passing through the "or" network 264. Because of the connection of the "or" network 264 to the plate of the left tube in the multivibrator 232, a signal passes through the "or" network 264 when the left tube n the multivibrator 232 is cut off. The left tube in the multivibrator 232 becomes cut off upon the introduction of a signal from the gate circuit 218.

212, it receives a relatively high voltage when a relatively high voltage is induced in the coil 54. As previously disclosed, a high voltage from the coil 54 indicates a positive increment. Since the gate circuit 242 passes a signal only when relatively high voltages are simultaneously 75 in the coil 26 for an integrator after the initial 22 pulse

positions for the integrator, the gate circuit 218 is opened for the passage of a triggering signal. This signal cuts off the left tube in the multivibrator 232 and causes a high voltage to be produced on the plate of the tube. This high voltage passes through the "or" network 264 and the driver circuit 262 to provide for the operation of the stepping circuit 248.

Since each tube in a multivibrator is triggered by the trailing edge of a pulse, the left tube in the multivibrator 232 becomes triggered only at the end of the first pulse which is induced in the coil 26 after the first 22 pulse positions for each integrator. Because of the control exerted on it by the left tube in the multivibrator 232, the stepping circuit would also be triggered into operation at the end of the first pulse induced in the coil 26 after the first 22 positions for each integrator. For reasons which will be disclosed in detail hereinafter, it is desirable that the stepping circuit 248 be triggered into operation at the beginning of the first pulse in the channel 14 after the first 22 positions for each integrator. This is effectuated 20 by the operation of the gate circuit 266.

The gate circuit 266 operates at the beginning of the first pulse in the channel 14 after the first 22 positions for each integrator, since the plate of the right tube in the multivibrator 232 has a high voltage at this time. The gate circuit 266 is prepared for operation by the counter 226, which introduces a high voltage through the line 224 to the gate circuit 266. The gate circuit passes the first pulse in the channel 14 because of its connection to the plate of the left tube in the multivibrator 200 immediately after the 22nd pulse position for each integrator.

As a result of the operation of the gate circuit 266, the stepping circuit 248 becomes triggered into operation one pulse position before the adder 230 is triggered into operation by the plate of the left tube in the multivibrator 232. In order for the information relating to the  $\Delta y$  increments to pass from the stepping circuit 248 in proper sequence with the operation of the adder 230, the information in the stepping circuit 248 is introduced to the multivibrator 250.

Since the tubes in the multivibrator 250 are triggered into operation by the trailing edge of the pulse indications in the stepping circuit 248, the multivibrator 250 operates to delay by one pulse position the information in the circuit 248. By delaying the information from the stepping circuit 248 by one pulse position, the multivibrator 250 produces a proper synchronization between the information from the stepping circuit and the other information introduced to the adder 230. The left tube in the multivibrator 250 provides an indication of the integer "+1" for each binary position when its voltage is high, and the right tube provides an indication of the value "0" when its voltage is high.

The production of a relatively high voltage on the plate of the left tube in the multivibrator 232 causes the adder 230 to be triggered into operation. After the adder 230 has been triggered into operation, it receives binary indications of the value of the dependent quantity y for each integrator. The adder receives indications representing the integer "1" from the gate circuit 218 and indications representing the value "0" from the gate circuit 222. The operation of the gate circuits 218 and 222 is in turn controlled by the voltages on the plates of the left and right tubes in the multivibrator 200.

The adder 230 arithmetically combines the value of the dependent quantity y for each integrator with the value of the  $\Delta y$  increments passing through the multivibrator 250. The arithmetical combination of the values of y and  $\Delta y$  are obtained for each pulse position in sequence as the drum 10 rotates. For example, the arithmetical combination of the indications of y and  $\Delta y$  in the 25th pulse position for a particular integrator may first be obtained. The arithmetical combination of the values of y and  $\Delta y$  may thereafter be sequentially obtained for 75

the 26th and the following pulse positions for the integrator.

Sometimes, upon the arithmetical combination of the values of y and  $\Delta y$  for a particular pulse position, the adder 230 may obtain a full binary indication of +2. In binary form, an indication of +2 is equivalent to a value of "0" for the pulse position and a carry of +1 to the next highest digit. For example, when a binary indication of "1" for y in the 26th position is added to a binary indication of "1" for  $\Delta y$  in the same position, the resultant value may be "0" in the 26th position with a carry of "1" into the 27th position. This carry is provided by the circuit 254.

A carry may also be provided from a first pulse position to the next position when a carry from the position immediately preceding the first position is added to the integer "1" indicating the value of either y or  $\Delta y$  for the first position. For example, a carry may be provided from pulse position 29 to pulse position 30 as a result of an addition in pulse position 29. The addition of this carry indication with an integer "1" indicating the value of the dependent quantity y for pulse position 30 causes a carry to be obtained for pulse position 31.

By arithmetically combining the values of y,  $\Delta y$  and the carry indication for each pulse position, a new value of y is obtained. The new indication of y for each pulse position passes sequentially through the "or" network 236 and produces a corresponding signal pattern in the coil 30. This signal pattern causes the coil 30 to record in the channel 14 the new value of y for each pulse position. The information relating to the new value of y subsequently passes through the gate circuits 218 and 222 for utilization by the adder 230. After the information has been utilized by the coil 26, it is erased by the coil 28.

The binary information passing through the stepping circiut 248 is not only introduced to the adder 230 but is also introduced to the adder 258. Since the information in the stepping circuit 248 is introduced to the adder 258 one pulse position before it is introduced to the adder 230, the information passing from the stepping circuit 248 to the adder 258 represents a value equal to ½ of that passing to the adder 230. In this way, the information passing from the stepping circuit 248 to the adder 258 for each integrator represents a value equal to ½ of the Ay increments for the integrator upon the presentation of the integrator for computation.

The adder 258 arithmetically combines the information from the stepping circuit 248 with the numerical information in the channel 18. As has previously been disclosed, the numerical information in the channel 18 for certain integrators represents a value equal to  $\frac{1}{2} \Sigma \Delta y$  for the integrators. By combining the information from the stepping circuit 248 with the information in the channel 18 for each integrator, the adder 258 obtains a new value of  $\frac{1}{2} \Sigma \Delta y$  for the integrator. This value is obtained from the time that a previous  $\Delta x$  increment has occurred for the integrator. The new indications obtained by the adder 258 pass through the gate circuit 268 and the "or" network 274 to the coil 42 for recordation by the coil in the channel 18. The operation of the gate circuit 268 will be disclosed in detail subsequently.

The operation of the adder 258 to obtain new indica-65 tions may be represented by the logical equation

$$E_{\rm n} = S_{\rm dr}(B_1 E D_{\rm e} + B E' D_{\rm e} + B_1' E D_{\rm e}' + B_1' E' D_{\rm e})$$

where  $E_n$  represents a relatively high voltage produced by the adder 258 for a pulse position to indicate the integer "1" for the position;  $S_{dr}$  represents a high voltage from the driving circuit 262;  $B_1$  represents a high voltage from the stepping circuit 248 to indicate the integer "1," E represents a high voltage from the plate of the left tube in the multivibrator 204; and  $D_e$  represents a positive carry from the circuit 260; and  $B_1$ ', E' and  $D_e$ ' respec-

tively represent the inverse of  $B_1$ , E and  $D_e$  to indicate the value "0" for a pulse position.

The occurrence of each  $\Delta x$  increment for an integrator and the polarity of each such increment are determined in a manner similar to that disclosed above for the  $\Delta y$  increments. Thus, a  $\Delta x$  increment for an integrator occurs when a pulse of relatively high voltage is induced in the coil 48 (FIGURE 6) at the instant that a pulse is induced in the coil 32 in one of the first 22 positions for the integrator. Similarly, the  $\Delta x$  increment is positive when a pulse is induced in the coil 54 at the instant that pulses are induced in the coils 32 and 48. The  $\Delta x$  increment is negative if a pulse is not induced in the coil 54 at the instant that pulses are induced in the coils 32 and 48.

As previously disclosed, the pulses induced in the coil 32 are introduced to the grid of the left tube in the multivibrator 318 (FIGURE 7) to cut off the tube in a pattern corresponding to the pattern of magnetic pulses in the channel 16. The positive pulses produced on the plate of the left tube in the multivibrator 318 are introduced to the gate circuit 346. Since the gate circuit 346 is also connected through the line 228 to the counter 226, it is prepared to open for the passage of a signal during the first 22 pulse positions of each integrator.

Because of its connection to the plate of the left tube in the multivibrator 212, the gate circuit 346 becomes open only when a pulse appears in the channel 22 simultaneously with the appearance of the coding pulse in the channel 16. Such a simultaneous occurrence of pulses

in the channels 16 and 22 for an integrator indicates that a  $\Delta x$  increment for the integrator is positive.

Upon the passage of a signal through the gate circuit 346, the left tube in the multivibrator 300 becomes cut off. The left tube in the multivibrator 300 remains cut off during the rest of the time that the particular integrator is presented for computation. At pulse position 48 of the integrator, a signal is introduced from the counter 226 through the line 252 to the grid of the right tube in the multivibrator 300 so as to cut off the tube. When the right tube in the multivibrator becomes cut off, the left tube starts to conduct. This causes the left tube in the multivibrator 300 to be prepared for triggering by a signal passing through the gate circuit 346 during the first 22 positions of the next integrator to be presented for computation.

When the left tube in the multivibrator 300 is cut off, a relatively high voltage is introduced from the plate of the tube to input terminals of the gate circuits 334 and 338. The gate circuit 334 also receives signals from the gate circuit 218, which operates after the first 22 positions for each integrator to pass the pulses of high voltage induced in the coil 26. As previously disclosed, these pulses provide an indication representing the integer "1" for different pulse positions in the channel 14 for each integrator. Since such indications represent the dependent quantity y for each integrator, they may be designated by "Y" in conformity with the designations provided in copending application, Serial No. 217,478.

When relatively high voltages are simultaneously introduced to the gate circuit 334 from the gate circuit 218 and the plate of the left tube in the multivibrator 300, the gate circuit passes a signal to the "or" network 330. Since the gate circuit 218 passes signals indicative of "Y" and the left tube in the multivibrator 300 indicates  $+\Delta x$  when its voltage is high, each signal passing to the "or" network 330 indicates the value (Y)  $(\Delta x)$  for a particular pulse position. The value (Y)  $(\Delta x)$  is an "and" proposition which is true when only both Y and  $\Delta x$  are simultaneously true. The value (Y)  $(\Delta x)$  corresponds in binary form to the integer "1" for different pulse positions.

For a value of "0" for a pulse position, a relatively low voltage is induced in the coil 26. This low voltage is inverted by the inverter 202 and is introduced as a rela-75